172095

JPRS 83420

6 May 1983

## **USSR** Report

## CYBERNETICS, COMPUTERS AND AUTOMATION TECHNOLOGY

No. 69

DISTRIBUTION STATEMENT A

Approved for public relates; Distribution Unfinited

# 19980603 123

DTIC QUALITY INSPECTED 2

FOREIGN BROADCAST INFORMATION SERVICE

JPRS publications contain information primarily from foreign newspapers, periodicals and books, but also from news agency transmissions and broadcasts. Materials from foreign-language sources are translated; those from English-language sources are transcribed or reprinted, with the original phrasing and other characteristics retained.

Headlines, editorial reports, and material enclosed in brackets [] are supplied by JPRS. Processing indicators such as [Text] or [Excerpt] in the first line of each item, or following the last line of a brief, indicate how the original information was processed. Where no processing indicator is given, the information was summarized or extracted.

Unfamiliar names rendered phonetically or transliterated are enclosed in parentheses. Words or names preceded by a question mark and enclosed in parentheses were not clear in the original but have been supplied as appropriate in context. Other unattributed parenthetical notes within the body of an item originate with the source. Times within items are as given by source.

The contents of this publication in no way represent the policies, views or attitudes of the U.S. Government.

## PROCUREMENT OF PUBLICATIONS

JPRS publications may be ordered from the National Technical Information Service (NTIS), Springfield, Virginia 22161. In ordering, it is recommended that the JPRS number, title, date and author, if applicable, of publication be cited.

Current JPRS publications are announced in <u>Government Reports Announcements</u> issued semimonthly by the NTIS, and are listed in the <u>Monthly Catalog of</u> <u>U.S. Government Publications</u> issued by the Superintendent of Documents, U.S. Government Printing Office, Washington, D.C. 20402.

Correspondence pertaining to matters other than procurement may be addressed to Joint Publications Research Service, 1000 North Glebe Road, Arlington, Virginia 22201.

Soviet books and journal articles displaying a copyright notice are reproduced and sold by NTIS with permission of the copyright agency of the Soviet Union. Permission for further reproduction must be obtained from copyright owner.

#### \_JPRS REPORTS \_\_

Japan Report Korean Affairs Report Southeast Asia Report Mongolia Report

Near East/South Asia Report Sub-Saharan Africa Report West Europe Report West Europe Report: Science and Technology Latin America Report

## USSR

Political and Sociological Affairs Problems of the Far East Science and Technology Policy Sociological Studies Translations from KOMMUNIST USA: Economics, Politics, Ideology World Economy and International Relations Agriculture Construction and Related Industries Consumer Goods and Domestic Trade Economic Affairs Energy Human Resources International Economic Relations Transportation

Physics and Mathmetics Space Space Biology and Aerospace Medicine Military Affairs Chemistry Cybernetics, Computers and Automation Technology Earth Sciences Electronics and Electrical Engineering Engineering and Equipment Machine Tools and Metal-Working Equipment Life Sciences: Biomedical and Behavioral Sciences Life Sciences: Effects of Nonionizing Electromagnetic Radiation Materials Science and Metallurgy

## EASTERN EUROPE

Political, Sociological and Military Affairs Scientific Affairs

Plant and Installation Data

Economic and Industrial Affairs

## CHINA

RED FLAG

Agriculture

Political, Sociological and Military Affairs Economic Affairs

Science and Technology

#### WORLDWIDE

Telecommunications Policy, Research and Development Nuclear Development and Proliferation

Environmental Quality Epidemiology

####

China Soviet Union South Asia Asia and Pacific

#### Eastern Europe Western Europe Latin America Middle East and Africa

To order, see inside front cover

JPRS 83420

6 May 1983

## USSR REPORT

## CYBERNETICS, COMPUTERS AND AUTOMATION TECHNOLOGY

## No. 69

## Contents

## GENERAL

|         | New High-Performance Elektronika-79 Minicomputer<br>and Efficiency of Use in Schematic Design Systems<br>of Large Integrated Circuits<br>(I. L. Talov, et al.; UPRAVLYAYUSHCHIYE<br>SISTEMY I MASHINY, Nov-Dec 82) | 1  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|         | Problem of Internal Interface in Microprocessor Systems<br>(M. P. Gal'perin, et al.; UPRAVLYAYUSHCHIYE<br>SISTEMY I MACHINY, Nov-Dec 82)                                                                           | 8  |

| HARDWAI | RE                                                                                                                                                                                                                 |    |

|         | Computer Technology and Automation ás the Basis for<br>Intensification of the National Economy<br>(V. A. Myasnikov; UPRAVLYAYUSHCHIYE SISTEMy<br>I MASHINY, Nov-Dec 82)                                            | 26 |

|         | Microprocessor Equipment Complex<br>(B. N. Malinovskiy, et al.; UPRAVLYAYUSHCHIYE<br>SISTEMY I MASHINY, Nov-Dec 82)                                                                                                | 33 |

|         | Some Characteristics of Configuration of SM-2M Complexes<br>(V. P. Kazachenko, et al.; UPRAVLYAYUSHCHIYE<br>SISTEMY I MASHINY, Nov-Dec 82)                                                                         | 44 |

|         | Device for Controlling Coding and Input of Random<br>Processes in a Computer<br>(M. S. Titov; AVTOMETRIYA, Jan-Feb 83)                                                                                             | 47 |

| SOFTWAR | RE                                                                                                                                                                                                                 |    |

|         | Paperless Programming Technology in Dialogue Environment<br>(I. V. Vel'bitskiy; UPRAVLYAYUSHCHIYE SISTEMY I<br>MASHINY, Nov-Dec 82)                                                                                | 52 |

- a - [III - USSR - 21C S&T]

| Organization of Design Process in Paperless<br>Programming P-Technology                            |     |

|----------------------------------------------------------------------------------------------------|-----|

| (A. A. Taranenko, et al.; UPRAVLYAYUSHIYE                                                          | ~ 1 |

| SISTEMY I MASHINY, Nov-Dec 82)                                                                     | 64  |

| Graphical Display of Algorithms in Paperless                                                       |     |

| Programming P-Technology<br>(L. I. Sholmov, et al.; UPRAVLYAYUSHCHIYE                              |     |

| SISTEMY I MASHINY, Nov-Dec 82)                                                                     | 67  |

| DiosimSystem for Simulation of Digital Processes<br>on YES Computer                                |     |

| (T. P. Mar'yanovich, et al.; UPRAVLYAYUSHCHIYE                                                     |     |

| SISTEMY I MASHINY, Nov-Dec 82)                                                                     | 73  |

| Display-Oriented Editor of Symbolic Data for<br>SM-3 and SM-4 Computers                            |     |

| (T. V. Lunina: UPRAVLYAYUSHCHIYE SISTEMY                                                           |     |

| I MASHINY, Nov-Dec 82)                                                                             | 79  |

| Relational Homogeneously-Structured Disconnected<br>Database                                       |     |

| (N. G. Zavtsev: UPRAVLYAYUSHCHIYE SISTEMY                                                          |     |

| I MASHINY, Nov-Dec 82)                                                                             | 83  |

| Scientific and Technical Committee on Computer                                                     |     |

| Programming Languages and Systems<br>(A. N. Maslov; UPRAVLYAYUSHCHIYE SISTEMY I                    |     |

| MASHINY, Nov-Dec 82)                                                                               | 95  |

| APPLICATIONS                                                                                       |     |

| Kiev Automated Control System, Design Features and                                                 |     |

| Prospects for Development                                                                          |     |

| (V. A. Zgurskiy, et al.; UPRAVLYAYUSHCHIYE SISTEMY<br>I MASHINY, Nov-Dec 82)                       | 97  |

| Organization of Data Exchange Between Computer and<br>Remote Users                                 |     |

| (P. M. Ivanov, et al.: UPRAVLYAYUSHCHIYE SISTEMY                                                   |     |

| I MASHINY, Nov-Dec 82)                                                                             | 107 |

| Characteristics of Using Control Computer Complexes in                                             |     |

| Automated Production Process Control Systems in<br>Wide-Strip Rolling Mills With Processor Control |     |

| (I. N. Bogavenko, et al.; UPRAVLYAYUSHCHIYE                                                        |     |

| SISTEMY I MASHINY, Nov-Dec 82)                                                                     | 115 |

## CONFERENCES

| Developing Technology of Scientific Research and<br>Introduction of Results Into National Economy<br>(M. A. Luchka, et al.; UPRAVLYAYUSHCHIYE<br>SISTEMY I MASHINY, Nov-Dec 82) | 120 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Use of Computer Equipment to Control Production<br>Processes in Instrument Building<br>(I. S. Yeremeyev, G. A. Pimenova;                                                        |     |

| UPRAVLYAYUSHCHIYE SISTEMY I MASHINY,<br>Nov-Dec 82)                                                                                                                             | 124 |

| Improving Management of Production Association Based<br>on Standardization and Computer Equipment<br>(P. Y. Kalita; UPRAVLYAYUSHCHIYE SISTEMY<br>I MASHINY, Nov-Dec 82)         | 127 |

| Problems of Developing Programs for Calculating<br>Process Control                                                                                                              |     |

| (B. N. Pan'shin; UPRAVLYAYUSHCHIYE SISTEMY<br>I MASHINY, Nov-Dec 82)                                                                                                            | 131 |

| Problems of Theory and Design of Data Converters<br>(P. S. Klochan; UPRAVLYAYUSHCHIYE SISTEMY<br>I MASHINY, Nov-Dec 82)                                                         | 135 |

| PUBLICATIONS                                                                                                                                                                    |     |

| Table of Contents of Journal 'Automatic Monitoring                                                                                                                              |     |

|     |                    |                  | 0     |     |

|-----|--------------------|------------------|-------|-----|

| and | Measuring', Januar | ry-February 1983 |       |     |

|     | (AVTOMETRIYA, Ja   | n-Feb 83)        | ••••• | 139 |

GENERAL

UDC 681.3

NEW HIGH-PERFORMANCE ELEKTRONIKA-79 MINICOMPUTER AND EFFICIENCY OF USE IN SCHEMATIC DESIGN SYSTEMS OF LARGE INTEGRATED CIRCUITS

Kiev UPRAVLYAYUSHCHIYE SISTEMY I MASHINY in Russian No 6, Nov-Dec 82 (manuscript received 14 Jan 82, after revision 15 Jul 82) pp 105-108

[Article by Candidate of Technical Sciences Igor' Leonidovich Talov, Kiev, engineer Vladimir Vasil'yevich Plotnikov, Voronezh, Candidate of Technical Sciences Vyacheslav Yegorovich Mezhov, Voronezh, and senior scientific associate Gennadiy Grigor'yevich Bondarovich, Kiev Polytechnical Institute]

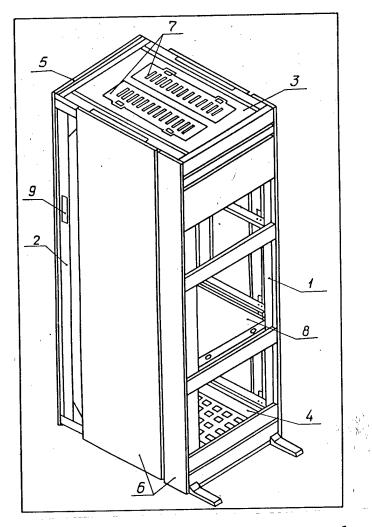

[Text] The new high-performance Elektronika-79 minicomputer (see figure) designed to solve a wide range of problems in automation of control, design and efficiency processing of large data files, has now been developed.

The new minicomputer works with numbers represented in formats with fixed and floating point. The computer instruction system includes instruction in three formats (nonaddress for control and one- and two-address for calculations) and permits eight methods of addressing. The set of instructions consists of 137 basic instructions. A total of 88 instructions is used to process numbers with fixed point with word length of 16 and 32 bits, while 46 instructions are used for numbers with floating point with word length of 32 and 64 bits.

A separate processor connected to the central processor by an internal bus system performs operations with numbers with floating point. The speed of the computer reaches three million operations per second and the main memory capacity is 4 Mbyte. The main memory of the computer is based on dynamic type BIS [large integrated circuit] that require periodic regeneration of the contents, which increases the access time to it and reduces the speed of the computer. A high-speed associative memory with access cycle of 300 ns, the so-called CACHE memory, with small capacity (2 Kbyte), has been introduced to increase the speed of the computer between the main memory and the central processor.

The central processor and interfaces of the external memory and peripheral data input-output devices are connected by a common bus system--by a single channel fully compatible with the channel of the Elektronika 100-25 minicom-puter. However, data are exchanged between the processor and external memory devices (three groups of external memory devices can be connected to the computer) through a separate 32-digit channel, which guarantees high speed of

1

exchange, while only the control registers are accessible from the direction of the unified channel. Access to the main memory from the processor is also gained through a separate 22-digit memory channel.

The central processor communicates with the main memory channel and the unified channel by using a memory dispatcher which converts the 16-digit program address to an 18-digit unified channel address and 22-digit main memory address. Access is gained to the main memory from the peripheral devices through a channel address converter.

Thus, three address zones: a 22-digit with access to the main memory, an 18digit with access to the channel and 16-digit virtual memory that use programs, are used in the minicomputer. The three operating modes of the central processor (internal, supervisor and user), 16 general-purpose registers, large main memory capacity and also the capability of connecting a large number of external memory devices permit organization of multiprogram operation and achievement of high computer productivity in multistation systems.

The computer includes:

a processor based on bipolar circuits with Schottky diodes and designed for storage, processing and control of data flows;

a main memory based on integrated circuits of the K565 or K581 series, which are dynamic type storage devices; the minimum memory capacity is 256 Kbyte;

external memory devices: SM-5400 disk unit (subsequently the YeS-5061) and the IZOT-5003 tape unit;

data input-output peripheral devices that include a floppy disk unit of the PLx-45D type or the GMD-70 Elektronika type, a 15IE-00-002 or 15IE-00-013 alphanumeric display, an SM-6204 papertape station and a DZM-180 or DARO-1156 printer.

The Elektronika-79 is program-compatible with the smallest models of the Elektronika 100-25 and the Elektronika-60M and can also be used efficiently with the SM-3 and SM-4 computers in multiprocessor and multistation design, control and scientific research automation systems.

The results of comparing the efficiency of using the Elektronika-79 minicomputer and the 15 UT-4-017 circuit design complex for solving problems of circuit design of electronic equipment parts are presented in the given article. The hardware and software systems for circuit design are considered in detail in [1-3].

Three methods of input data preparation, entry and processing on circuits of the functional units of BIS were used for an experimental check of the efficiency of using the 15 UT-4-017 system in solving routine circuit design problems.

The first method was comparison of drawings of the functional units of BIS, preparation of input data based on the rules of YaZOS-4 [4] or SAMRIS [5] input languages, punching the data on punchcards or papertape, entry of it into the BESM-6 computer and also program and visual check of the entered data, printout of the input data and checking and editing of it.

In the second method, complete information on the functional diagrams of the BIS units was prepared in text form according to YaZOS-U language and was entered from the alphanumeric display at the circuit designer's work position. Input, checking and editing of information were carried out by using developed software in the interactive mode [3].

The third method (like the second method) included preparation of textual information on the circuits and entry of it from the alphanumeric display according to the rules of YaZOS-U input language. Graphic data was entered from the prepared drawings of the functional diagrams of BIS using the EM-719B graphic data coder. All the software for entry, checking and editing of textual information by using the alphanumeric display was used in the given method, while the 15IG-001 graphic memory display and EM-729A device for controlling the position of the marker of this display [3] was used for graphic data.

3

Comparison of the first method, widely employed at present, and of the developed second and third methods of data preparation, entry and processing on the functional circuits of BIS made it possible to achieve an objective evaluation of the efficiency of developed software-hardware of the circuit designer's work position.

The efficiency of the developed methods and of the hardware-software was determined experimentally on six functional circuits of BIS of various types of technologies, selected for this purpose, with complexity from 5 to 394 components and from 7 to 139 assemblies.

## Table 1.

| Complexity of Circuits  | Data         | File Preparation | Time         |

|-------------------------|--------------|------------------|--------------|

| (Components/Assemblies) | First Method | Second Method    | Third Method |

| 5/7                     | 25 min       | 9 min            | 11 min       |

| 8/7                     | 2 hr 42 min  | 50 min           | 28 min       |

| 76/52                   | 5 hr 45 min  | 2 hr 25 min      | 2 hr 4 min   |

| 89/55                   | 10 hr 20 min | 3 hr 52 min      | 2 hr 17 min  |

| 165/77                  | 8 hr 50 min  | 5 hr 52 min      | 4 hr 38 min  |

| 394/139                 | 12 hr 10 min | 8 hr 54 min      | 7 hr 38 min  |

The time expenditures to perform operations by the three methods of textual and graphic data preparation, input and processing by the operator are presented in Table 1. Comparison of the results shows that the second and third methods permit the laboriousness of performing the operations to be reduced two-fifths to one-third. A considerable reduction of laboriousness, especially with the third method, is achieved with an increase of the complexity of the BIS functional diagrams. This is explained primarily by the fact that the operations are performed in the interactive mode. When entering textual information on the circuits, automatic prompting of the operator's actions and program and visual checking of entered data are carried out. The user is freed of the need to code the drawings and of manual preparation of more complex files on circuit switching. This information is formulated automatically.

The operational editing programs guarantees simplicity and high rate of error correction in the input data. The fact that the errors in the data are determined at earlier stages of the BIS design process is of considerable importance. Automatic formulation of the higher capacity and more complex switching files (from the viewpoint of verification) guarantees a high percentage of data reliability and reduces the probability of losses of machine time on calculation of the electric characteristics of the functional circuits of BIS having undetermined errors in the input data.

The electric characteristics of the functional units of BIS were analyzed using a complex of PRANIS programs (written in Fortran-4 language), the main characteristics of which are presented in [3]. Programs for analysis of the static and dynamic characteristics of the functional units of BIS for the BESM-6 were used as the bases of this complex [6, 7], which permitted correct comparison of the results during the experiment on the Elektronika 100-25 and Eleketronika-79 computers to similar results of calculation on the BESM-6 computer.

The following sequence of conducting the experiment was used: the functional circuits of BIS of different classes were selected, the input information was entered into the computer and processed, the static and dynamic characteristics were calculated on the indicated computers, comparative analysis of the calculating expenditures to calculate the static and dynamic characteristics of the selected functional units of the BIS was carried out and recommendations were worked out on the use of the circuit designer's work position in the autonomous mode and for organization of a circuit design system based on the new minicomputer.

The following circuits were selected to conduct the experiment:

an AND-NOT circuit based on bipolar transistors having five components and seven assemblies;

an AND-NOT circuit based on MDP devices containing eight components and seven assemblies;

an equivalence circuit of the functional unit of the BIS with injection power supply having 76 components and 52 assemblies;

an equivalence circuit of the functional unit of the BIS for control of the microcomputers on the injection devices, containing 89 components and 55 assemblies;

an equivalence circuit of the microcomputer unit based on injection devices, containing 165 components and 77 assemblies.

The time expenditures for calculation of the static and dynamic characteristics of the enumerated circuits on the BESM-6 (first lines), Elektronika 100-25 (second lines) and Elektronika-79 (third lines) computers, respectively, are presented in Table 2.

Summarizing the results of experimental evaluation of the efficiency of using the 15 UT-4-017 system and of the high-speed Elektronika-79 minicomputer to solve routine and engineering problems of circuit design of BIS, one can conclude the following:

the new high-speed Elektronika-79 minicomputer permits solution of complex scientific and technical problems of automation of electronic equipment parts design;

the developed methods of processing textual and graphic information on circuits using the 15 UT-4-017 complex guarantee a two-fifths to one-seventh reduction of BIS design deadlines compared to the methods used.

Table 2.

•

| Time of Calculation of<br>Characteristics<br>static dynamic |       | , www<br>1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1 | s 5 hr 33 min 25<br>s 2 hr 00 min 3 | 42 min 17<br>54 min 17 | 2 hr 10 min<br>36 s 36 min<br>55 s 1 hr 17 min |

|-------------------------------------------------------------|-------|---------------------------------------------------|-------------------------------------|------------------------|------------------------------------------------|

| Number of<br>Points of<br>Transfer<br>Character-<br>istics  | 10    | 11                                                | 6 1 1                               | 21                     | 13<br>1 h                                      |

| Simulation<br>Time, ns                                      | 2,000 | 400                                               | 1,600                               | 1,100                  | 1,000                                          |

| Number of<br>Oscillator<br>Drops                            | m     | ٢                                                 | 16                                  | 13                     | Q                                              |

| Number of<br>Oscillators                                    | 2     | ε                                                 | 12                                  | ω                      | Ŋ                                              |

| Complexity<br>of Circuits<br>(Components/<br>Assemblies     | 5/7   | 8/7                                               | 76/52                               | 89/55                  | 165/77                                         |

6

## BIBLIOGRAPHY

- 1. Mezhov, V. Ye., N. L. Ratmirov, I. L. Talov and B. L. Tolstykh, "Using the Elektronika 100-25 Minicomputer in an Automated Circuit Design System," ELEKTRONNAYA PROMYSHLENNOST', No 10, 1978.

- Mezhov, V. Ye., N. L. Ratmirov, I. L. Talov and B. L. Tolstykh, "The Software of the 15 UT-4-017 System," ELEKTRONNAYA PROMYSHLENNOST', No 6, 1979.

- 3. Mezhov, V. Ye., I. L. Talov and Yu. N. Chernyayev, "The Applied Programs of the 15-UT-4-017 Circuit Design System," ELEKTRONNAYA PROMYSHLENNOST', No 7, 1980.

- 4. Tolstykh, B. L. and V. Ye. Mezhov, "The Graphic-Symbolic Input Language of the 15 UT-4-017 Interactive Graphic System," ELEKTRONNAYA TEKHNIKA, MIKRO-ELEKTRONIKA, No 4, 1979.

- 5. Vasenkov, A. A., G. G. Kazennov, Yu. N. Belyakov and P. P. Avrashkov, "The SAMRIS Automated Simulation and Integrated Circuit Calculation System," MIKROELEKTRONIKA, No 6, 1976.

- 6. Nikishin, V. I., I. L. Talov, V. V. Yur'yev and V. M. Mezhov, "A Universal Program for Analysis of the Static Characteristics of EPAS-U Nonlinear Electronic Circuits," TRUDY INEUM, No 58, 1976.

- 7. Nikishin, V. I., I. L. Talov, V. Ye. Mezhov et al, "An Efficient Program for Analysis of the Dynamic Characteristics of Electronic Circuits and Use of It to Analyze Bipolar Integrated Circuits with Injection Power Supply," Loc. cit.

COPYRIGHT: Izdatel'stvo "Naukova dumka" "Upravlyayushchiye sistemy i mashiny" 1982

6521 CSO: 1863/71

UDC 681.327.11:621.3.049.771.14

PROBLEM OF INTERNAL INTERFACE IN MICROPROCESSOR SYSTEMS

Kiev UPRAVLYAYUSHCHIYE SISTEMY I MASHINY in Russian No 6, Nov-Dec 82 (manuscript received 3 Mar 81, after revision 16 Jun 82) pp 17-24

[Article by Doctor of Technical Sciences Mark Petrovich Gal'perin, engineer Valeriy Viktorovich Gorodetskiy and engineering Anatoliy Fedorovich Dryapak, LOEP Svetlana, Leningrad, and graduate student Vladimir Nikolayevich Oginskiy, Leningrad Institute of Precision Optics and Mechanics]

[Text] Introduction. The problem of working out a unified set of rules for integration of independent computer systems (processor, memory devices and input-output devices), connection of peripheral devices and finally combining several computers into a unified system is an important one for any class of modern computers.

With the appearance of the microcomputer, the problem of the interface became even more timely, having touched on a considerably wider range of sectors of science and technology. First, the microcomputer is the largest class of modern computers. Second, microcomputers are used mainly as built-in devices, with regard to which solution of the interface problem largely determines the process of design of an extremely wide range of devices, machine tools, assemblies and systems.

The importance of the interface problem to microcomputers is also determined by the fact that this problem is divided into two parts: interfaces for microcomputers (in the traditional postulation for computer technology) and "microcomputers for interfaces," i.e., the use of microcomputers as a generalpurpose programmable components for realization of protocols for integration of various types of equipment (of several measuring devices into a unified system, of several automated machine tools into a unified section controlled from a central computer, data transmission apparatus that forms some communications network together with communications channels and so on).

Consideration of this complex and dual problem and also solution of the special problem of selecting the interface when developing a microprocessor set of BIS [large integrated circuit] with increased functional complexity are unthinkable without clear definition of the concept of interface. We shall understand an interface as some set of rules (protocols) that determine integration of electronic devices of different level of complexity.\*

The entire set of interfaces of microcomputers can be divided into external and internal.

The external interfaces of microcomputers, as follows from the name itself, determine integration of the microcomputer with an external medium--with peripheral devices, sensors and actuating mechanisms, control and display members and the data transmission channels of devices, assemblies and systems in which (or jointly with which) the microcomputer (user interfaces) operates.

Internal interfaces of microcomputers determine the integration of the constituent parts of the microcomputer with each other into a system of specific configuration. Two groups of internal interfaces can be distinguished at the given phase of development of microprocessor (MP) and microcomputer technology:

BIS interfaces of the microprocessor set (intracard interfaces);

interfaces of microprocessor functional modules (intercard interfaces).

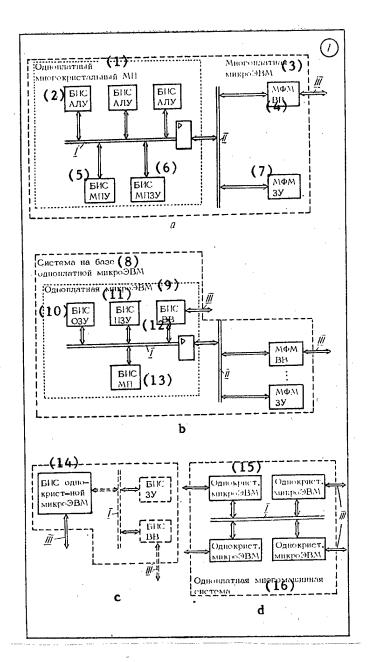

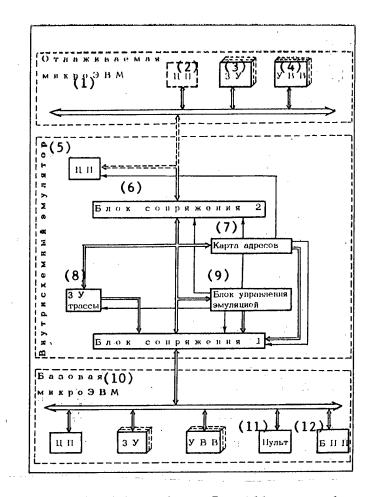

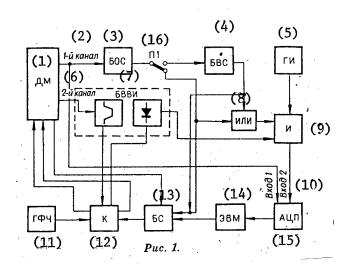

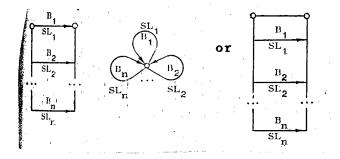

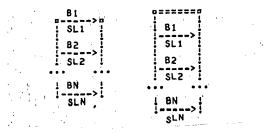

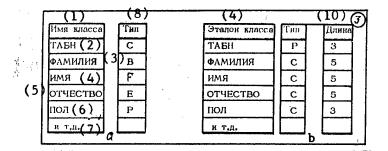

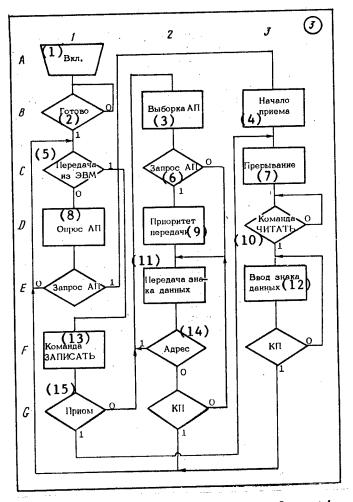

The various types of interfaces are presented in Figure 1.

Multichip microprocessors are usually constructed on the BIS of microprocessor sets produced within a single family and, therefore, no additional equipment is required to realize a "intraprocessor" interface. Due to the sufficient number of leads with low digit capacity of the ALU [arthimetic-logic unit] sections, the intraboard interface of these microprocessors can be more powerful than that of single-chip microprocessors and may require fewer supplementary integrated circuits for integration with ZU [memory] BIS and UVV [inputoutput device]. However, if a multichip microprocessor, memory BIS and UVV cannot be arranged on one board, they are integrated at the level of the interboard interface (Figure 1, a).

When designing single-board microcomputers based on single-chip microprocessors, there must be a different number of supplementary equipment to integrate the microprocessors with memory BIS and UVV (Figure 1, b). Thus, approximately 20 SIS [very high-speed integrated circuit] housings are required to integrate the Intel-8008 microprocessor to external memories and UVV, only six supplementary TTL [transistor-transistor logic] IS, part of which performs only the role of buffer amplifiers, are required for integration of the Intel-8080 microprocessor, in which the greater part of the supplementary equipment required for the Intel-8008 microprocessor is realized in the composition of the microprocessor BIS itself. At the same time, supplementary circuits are not required at all for integration of the 6800 microprocessor (of the

\*The aggregate of firmware understood as an interface by most authors [1] is one of the possible physical realizations of the interface as a protocol for integration of devices.

Examples of Interfaces: a--in multiboard microcomputer; b--in system based on single-board microcomputer; c--in single-board system based on single-chip microcomputer; d--in single-board multimachine system based on single-chip microcomputer (I--intraboard interface; II--external interface of Unibus type; III--external input-output interface)

Key:

- 1. Single-board multichip microprocessor

- 2. Large integrated circuit of arithmetic-logic unit

[Key continued on following page]

## [Key continued from preceding page]:

- 3. Multiboard microcomputer

- 4. Input-output microprocessor functional module

- 5. BIS of microprocessor device

- 6. BIS of microprocessor memory

- 7. Microprocessor functional module of memory

- 8. System based on single-board microcomputer

- 9. Single-board microcomputer

- 10. BIS of main memory

- 11. BIS of ROM

- 12. Input-output BIS

- 13. Microprocessor BIS

- 14. BIS of single-chip microcomputer

- 15. Single-chip microcomputer

- 16. Single-board multimachine system

Motorola Company) with the memory BIS and UVV [2]. It is obvious that the volume of supplementary equipment required to design one or another computer configuration based on BIS of various microprocessor sets is the most important user characteristic of these sets, which in turn is wholly determined by the intraboard interfaces used for the BIS of this set. Moreover, just as important an indicator is the amount of supplementary equipment for conversion from an intraboard to interboard interface.

Design of single-chip microcomputers with the capability of expanding the internal resources (volume of the main memory and of the input-output devices) requires that the greater part of the leads be used for the intraboard interface (Figure 1, c). In this case a single-chip microprocessor actually degenerates into a microprocessor. An example is the single-chip K1801VYel microcomputer, which has a systems mainline controller for integration with the memory BIS and UVV and an external interface in the form of a single sequential channel [3].

Information can be exchanged between the microcomputer through sequential channels (so-called weak communications) and the greater part of the leads to realize the external interface when developing single-chip multimachine systems based on single-chip microcomputers (Figure 1, d).

Internal interfaces of the microcomputer. These interfaces are not dependent on the range of application of the microcomputer and are selected with regard to the following, sometimes contradictory requirements:

achievement of maximum speed during data exchange between the constituent parts of the microcomputer;

low response time to interrupt;

elimination or minimization of the number of circuits of supplementary equipment required to integrate the constituent parts into a unified system; minimization of the number of BIS leads used for the intraboard interface and of the number of plug contacts used for the interboard interface;

the presence of functional capabilities that permit direct access to the memory without supplementary equipment, arbitrage of the systems bus, interrupt priorities and so on;

electric and design compatibility of the interfaces;

independence of the interface from development of the production base.

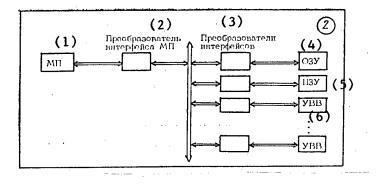

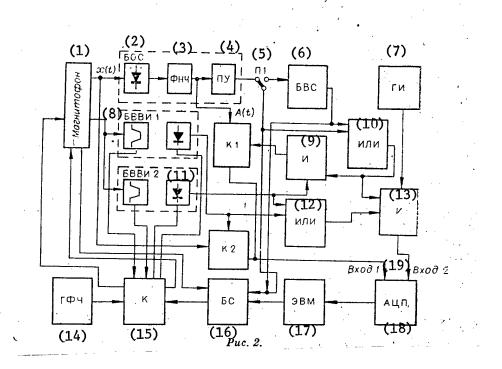

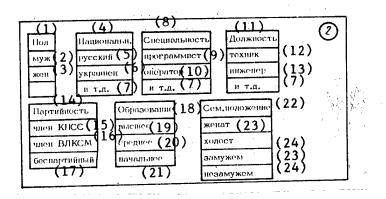

Data exchange occurs between the microprocessor, memory and UVV in any microcomputer. Regardless of the complexity, three types of signals always circulate in the system--data, address and control signals. These signals are either transmitted each through its own bus system or are spatially combined and separated in time. When the BIS (microprocessor functional modules) with different intraboard or interboard interfaces are integrated with each other, supplementary equipment that performs the role of interface converters is required (Figure 2).

Design of System Based on BIS (Microprocessor Functional Modules) with Different Intraboard and Interboard Interfaces

Key:

- 1. Microprocessor

- 2. Interface converter of microprocessor

- 4. Main memory

Input-output device

5. ROM 6. Inpu

3. Interface converters

5. Interface converters

It is obvious that design of microcomputers does not require supplementary equipment when realizing interface converters as the BIS themselves (microprocessor functional modules), but this means that the task of the microcomputer developers is simplified to the maximum extent. Hence, the need to standardize the internal interfaces immediately follows, which guarantees:

the capability of integrating the BIS of microprocessor sets into a unified system without complex analysis of the time and electric characteristics of each BIS and without supplementary equipment;

the compatibility of newly developed BIS (microprocessor functional modules) with existing and future microprocessor products.

## the compatibility of microprocessor BIS of different manufacturers.

Moreover, creation of standards for the internal interfaces of microcomputers will guarantee widespread introduction and study of them, which will make it possible to make the use of microcomputers, microprocessor functional modules and the BIS of microprocessor sets just as simple and widely used as smalland medium-scale integrated circuits are now used.

How then should the internal interfaces be assigned for different devices (microprocessors, main memories and input-output devices) so that these devices are integrated with each other without supplementary equipment? We feel that the more feasible is being given the composition of the systems bus and the sequence of the time and electric characteristics of signals on it, which determines the functional and electric characteristics of the internal interfaces of devices directly connected to the bus.

Different companies have developed a number of standards for systems buses that determine internal interfaces of different levels (intraboard and interboard). However, the characteristics of most of these buses were established historically: microprocessor sets of basic BIS (sets of microprocessor functional modules) were initially developed, it then became necessary to develop BIS or such modules for expansion of the functional capabilities of systems and as a result of this, the need arose for simple integration of newly developed BIS (modules) with existing systems. The composition of existing buses was established with some expansion for future applications, the time and electric characteristics of the signals on the bus were determined and interfaces of newly developed BIS (microprocessor functional modules) were accordingly designed).

Advance standardization of the internal interfaces of microcomputers is feasible with regard to the interconnection of intra- and interboard interfaces and the established quite specific tendency to convert from multiboard to singleboard microprocessor systems and from single-board configurations to realization of them on a single chip, in which the intraboard interface becomes closer to the interboard interface in its functional capabilities.

The large nomenclature of manufactured microprocessors and microcomputers and also the large number of developer companies determined the appearance of the most diverse company and intercompany standards for buses, the most widespread among which are: Microbus [4], Multibus [5], S-100 [6], Q-bus (LSI-11) [7], Versabus [8], STD-bus (Pro-Log), Z-bus (Zilog), TM-990 bus (Texas Instruments) [9, 10].

Let us consider the main limitations of these buses, taken into account in development of the intraboard interface for a microprocessor set of BIS of increased functional complexity.

Bus configuration. Buses can have combined (Q-bus and Z-bus) and separate address and data lines (S-100, Multibus, Microbus and Versabus). Separate buses permit address and data transmission to be combined in time, but reuqire a greater number of leads for the internal interface. If this is insignificant due to the rather large number of plug contacts for the interboard interface, then the use of separate address and data buses limits the digit capacity of these buses or of the control bus for the intraboard interface of the BIS whose housing usually has 40-48 leads [11].

An increase of the digit capacity of microprocessors and microcomputers requires expansion of both the data and address buses. Most buses permit exchange of both 8- and 16-digit data between the devices of the system by introduction of supplementary control signals. The Versabus, for example, provides operation with 8-, 16- and 32-digit data, which permits devices with different digit capacity to be used in the same system. There is also the capability of expanding the address bus (up to 18 in the Q-bus, up to 24 in the S-100 and up to 32 digits in the Versabus) with the lines reserved for this purpose.

Bus arbitrage. Data exchange is organized on most buses on the "master-slave" principle, in which the master device takes control of the bus on itself. The presence of several devices having the capability of becoming master devices in the system gives rise to the problem of distributing the bus resources among these devices (bus arbitrage). This arbitrage is accomplished differently in each bus.

The use of a direct-access controller to the memory or design of a supplementary circuit is assumed by the structure of the microbus in these cases. The number of direct-access interrogation lines to the memory and confirmation of it is not specially stipulated.

A four-digit bus that permits one to determine which of the 16 possible master devices in the system can take over control of the bus at a given moment is used in the arbitrage system of the S-100 bus. The device that has established the highest-order code on the arbitrage bus can take possession of the bus if there is a signal transmitted by the central processor authorizing takeover of the bus in response to a demand for takeover. This method is rather convenient, permits organization of a change of priorities of devices during completion of programs, but limits the total number of devices in the system and requires a rather complex hardware part and requires a greater number of leads from the BIS when used for the intraboard interface.

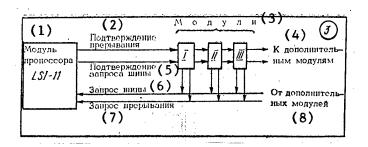

Arbitrage in the Q-bus is simpler (Figure 3), where the device located closest to the "daisy chain" with respect to the processor has the highest priority. The device with the highest priority passes the request confirmation signal of the bus to the device with the lowest priority only if it itself does not require control of the bus. Arbitrage is also accomplished in a similar manner in systems based on the Multibus. This method, although it does not have flexibility in designation of priorities, is simple to realize and requires a small number of lines and when used for the intraboard interface, may fully satisfy the design of complex single-board systems with unlimited number of master devices.

There are five levels of bus inquiry in the Versabus from BR4 (highest priority) to BRO (lowest priority). Organization of the priority scheme is the

Organization of Priority Circuits in System Based on Q-bus

Key:

- 1. Processor module

- 2. Confirmation of interrupt

- 3. Modules

- 4. To supplementary modules

- 5. Confirmation of bus inquiry

- 6. Bus inquiry

- 7. Inquiry

- 8. From supplementary modules

same on each level as in the Q-bus. Having received an inquiry, the arbiter compares its priority to that of the inquiry of the current master device and if the received inquiry has higher priority, it transmits a bus cleaning signal. After the last exchange cycle in the bus has been completed, the current master device frees the bus. The arbiter transmits the signal to make the bus available on one of five BRO-BR4 lines according to the level of priority of the incoming request. The device that has received the BQ signal becomes the master. This version of taking over the bus is unacceptable for the intraboard interface because of the need for a large number of leads from the microprocessor BIS.

Organization of interrupts. The majoriy of microprocessor systems is designed to operate in real time [12]. Therefore, the presence of an interrupt mechanism and also determination of priorities during operation of several interrupt sources in the system are important characteristics of the bus.

There are two main methods of interrupt: interrupt with polling and interrupt by vector [2]. In the first case, when the interrupt signal arrives, the central processor completes the instructions and transmits the signal of confirmation of readiness for interrupt processing, after which all the authorized interrupt sources are polled. Conversion to the corresponding interrupt service program is made after detection of the interrupt source. Polling can be carried out either through the software or hardware method. The priority of the interrupt source is determined by its location in the polling sequence. In the case of vector interrupt, the processor is freed of determination of the interrupt source address and immediately receives instructions for the corresponding service program.

The interrupt signals can be prohibited by program in both cases by using masks (can be masked). This permits control of such interrupt service characteristics as the waiting time and the time the demands are in the system [13] and also dynamically changes the level of the interrupt request priority. Although the vector interrupt method requires supplementary hardware, it is used in most of the mentioned buses since it is higher speed and requires a small number of control signals. It can be used for the intraboard interface.

The INTERBIS interface. The Soviet electronics industry is developing three main families of 16-digit microcomputers: the Elektronika-S5, the Elektronika-60 and the Elektronika-NTs. Investigations are being conducted to standardize the interfaces and software of these devices.

The characteristics of the interboard interface of the Elektronika-60 family are used as the unified functional characteristics. However, BIS having different intraboard interfaces are produced within different families, which makes it difficult to develop systems based on BIS of different families, integration of intraboard and interboard interfaces in these systems and also results in nonproduction expenditures for development of BIS of the same type.

The INTERBIS standard for the intraboard interface of the BIS of microprocessor sets has been suggested to eliminate the indicated deficiencies, within which the composition of the systems mainline, the order and types of interactions of the BIS connected to the mainline, the sequence and time ratios of signals on the mainline with different types of interaction and also the electric characteristics of the BIS receiving and transmitting circuits have been determined.

The proposed interface is oriented primarily toward design of single-board microprocessor systems or parts of them based on BIS with combined address and data buses and with levels of input and output signals compatible with the TTL levels. Functionally complete devices (processors, memory, controllers, input-output devices and so on), realized in the form of one or several BIS, are used as the components of the system.

Time Diagram of Mainline Control Transmission

## Key:

- 1. Mainline request

- 2. Authorization for taking over mainline

- 3. Confirmation of request

- Synchronization of exchange

- 5. Response of device

|                                               |                                 |                        | ····                     |                                                                                                                          |

|-----------------------------------------------|---------------------------------|------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------|

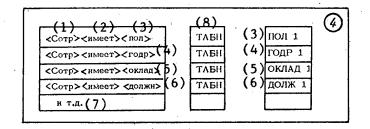

| (1)<br>Наименование линий и сигналов          | (2)<br>Буквенное<br>обозначение | (3)Источник сигналов   | (4)сигналов              | Назначение линий и сигналов (5)                                                                                          |

| (6)<br>Линии передачи информации              | (8)                             | 2 - 14 - 2 - 1<br>-    | (10)                     |                                                                                                                          |

| Шина «адрес — данные»<br>(7)                  | АД (00:15)                      | Ведущий (9)<br>Ведомый | Ведомый<br>Ведущий       | Передача адресов и данных (11)                                                                                           |

| Линии управления обменом<br>информацией (12)  | (14)                            |                        | -                        | (15)                                                                                                                     |

| Синхронизация обмена (13)                     | <b>ODM</b>                      | Ведущий                | Ведомый                  | Указание начала и конца текущего цикла                                                                                   |

| Прием адреса (16)                             | ΠΜA(17)                         | Ведомый                | Ведущий                  | обмена<br>Указание завершения дриема адреса ведо-<br>мым устройством                                                     |

| Ответ устройства (19)                         | OTB(20)                         | *                      | » (21)                   | Указание завершения приема либо выдачи<br>данных ведомым устройством                                                     |

| Чтение данных (22)                            | <u>त्रॅम</u> (23)               | Ведущий                | <sup>Ведомый</sup> (24)  | Указание готовности ведущего устройства<br>к приему данных и завершения приема                                           |

| Запись данных (25)                            | <u>ДЗП(26)</u>                  | * * 1 * 1              | » (27)                   | Указание достоверности данных на шине АД<br>Указание установки на шине АД адреса из                                      |

| Выбор устройства (28)                         | BV(29)                          | <b>*</b>               | * (30)                   | зоны 1600008 — 1777778                                                                                                   |

| Признак «запись — байт»                       | <u>ПЗП</u> (32                  |                        | » (33)                   | Указание формата передаваемых данных<br>(байт—слово) и указание операции записи                                          |

| Ошибка при обмене (34)                        | <u>OIIIB</u> (35                | ) <sub>Ведомый</sub>   | Ведущий (36)             | Указание возникновения ошибки при об-<br>мене                                                                            |

| Линии передачи управления<br>магистралью (37) |                                 |                        |                          |                                                                                                                          |

| Запрос магистрали (38)                        | <u>3M</u> (39)                  | Активные (40)          | Арбитр(41)               | Извещение арбитра о готовности активных устройств к обмену (42)                                                          |

| Разрешенис на захват маги-                    | <b>P3M</b> (44                  | устройства<br>Арбитр   | Активные устройства (45) | Извещение активного устройства о возмож-<br>ности захвата магистрали (46)                                                |

| страли (43)<br>Подтверждение запроса (47      | ) <del>113</del> (48)           | Ведущий                | ройства (45)<br>Арбитр   | ности захвата магистрали (чо)<br>Извещение арбитра о том, что активное уст-<br>ройство стало ведущим                     |

| Линии прерываний (50)                         | · - ·                           | (53)                   | and any day.             | (54)                                                                                                                     |

| Запрос на прерывание (51)                     | <u>311</u> (52)<br>(56)         | Устройства             | Активные устройства      | Указание наличия в системе одного или не-<br>скольких устройств, требующих обслужи-                                      |

| (55)<br>Разрешение прерывания                 | ПРР                             | Ведущий                | Ведомый                  | вания<br>Указание готовности прерванного устройст-<br>ва к чтению вектора                                                |

| Прерывание по внешнему<br>событию (58)        | (59)                            | Устройства             | Процессор<br>(60)        | Указание необходимости перехода процес-<br>сора на процедуру обработки этого преры-<br>вания по фиксированному адресу 61 |

| Дополнительные линии (62)                     |                                 |                        |                          | вания по фиксированному адресу                                                                                           |

| Установка (63)                                | <del>ycr</del> (64)             | Пульт (65)             | Устройства               | Установка всех устройств системы в опре-<br>деленное исходное состояние (66)                                             |

| (67)<br>Авария источника питания              | АИГ (68)                        |                        | Устройства               | Указание выхода постояние соглание и<br>указание выхода постоянного питающего<br>напряжения за допустимые пределы        |

| (71)<br>Авария сетевого питания               | ACT (72)                        | То же <sup>(69)</sup>  | Процессор                | Указание возможности выхода постоянного                                                                                  |

|                                               |                                 |                        |                          | питающего напряжения за допустямые пре-<br>делы, вследствие нарушения сетевого пита-<br>ния (14)                         |

Table 1. Composition and Designation of Signal Lines of INTERBIS Interface

Key:

- 1. Name of lines and signals

- 2. Letter notation

- 3. Signal source

- 4. Signal receiver

- 5. Designation of lines and signals

[Key continued on following page]

- 6. Data transmission lines

- 7. "Address-data" bus

- 8. AD (00:15)

- 9. Master

- 10. Slave

[Key continued from preceding page] 11. Address and data transmission 12. Data exchange control lines 13. Synchronization of exchange 14. OBM 15. Indication of beinning and end of current exchange cycle 16. Address reception 17. PMA 18. Indication of completion of address reception by slave device 19. Response of device 20. OTV Indication of completion of reception or transmission of data by slave 21. device 22. Data readout 23. DChT 24. Indication of readiness of master device to receive data and to complete reception 25. Data recording 26. DZP 27. Indication of data reliability on AD bus 28. Selection of device 29. VU Indication of setting of address from zone  $160000_8$ -1777778 on AD bus 30. 31. "Record-byte" feature 32. PZP Indication of format of data to be transmitted (byte-word) and indication 33. of record operation 34. Error in exchange 35. OShV 36. Indication of error during exchange 37. Mainline control transmission lines 38. Mainline request 39. ZM 40. Active devices 41. Arbiter 42. Informing arbiter about readiness of active devices for exchange 43. Authorization to take over mainline 44. RZM 45. Active devices 46. Informing active device on possibility of taking over mainlines 47. Requestion confirmation 48. PZ 49. Informing arbiter that active device has become master 50. Interrupt lines 51. Interrupt request 52. ZPR 53. Devices Indication of presence of one or several devices requiring servicing in 54. system

[Key continued on following page]

[Key continued from preceding page:

- 55. Interrupt authorization

- 56. PRR

- 57. Indication of readiness of interrupted device to read vector

- 58. Interrupt by external event

- 59. PRS

- 60. Indication of need to convert processor to procedure for processing this interruption according to fixed address

- 62. Supplementary lines

- 63. Setting

- 64. UST

- 65. Console

- 66. Setting all devices of system to specific initial state

- 67. Emergency of power supply source

- 68. AIP

- 69. Power supply unit

- 70. Indication of DC supply voltage going beyond permissible limits

- 71. Emergency of network power supply

- 72. ASP

- 73. Processor

- 74. Indication of capability of DC power supply voltage going beyond permissible limits due to disruption of network power supply

An intermodular parallel interface was taken as a basis according to OST 11 305.903-80 when developing the INTERBIS interface. The main distinguishing features of the INTERBIS interface are:

expansion of the composition of mainline signal lines;

variation of the interaction protocol of the devices in the mainline takeover algorithm;

absence of restriction on minimum time of the address being held by the master device;

capability of using devices with different and unlimited speed in reception and (or) recognition of an address from below in a single system;

independence from continuously developed technology and circuit engineering.

These differences do not introduce discernible difficulties when integrating the intraboard INTERBIS interface with the interboard interface according to OST 11 305.903-80.

Functional characteristics of the INTERBIS. Agreements on organization of communications within system. Communication between two devices connected to the mainline is organized, as in most known buses, on the "master-slave" principle. The basis of exchange is the asynchronous principle; therefore, the algorithm for exchange between devices is not dependent on their speed and

exchange between two devices occurs at a speed determined by the speed of the slower of the existing devices. Devices of two types--active and passive--may be included in the system.

An active device is one which can perform functions of the master device and can receive interrupt requests during data exchange. This does not exclude the capability of designing an active device that performs all or part of the functions of a passive device.

A passive device is one which can perform the functions of only a slave device and can also transmit interrupt requests during data exchange.

The composition and designation of mainline signal lines. The connecting mainline consists of 33 signal lines joined (by functional feature) into five separate groups (Table 1). The level of the logic unit of the signals on all lines is low.

The address reception signal line is supplementarily introduced in the mainline, which permits organization of complete asynchronous interaction between devices, including transmission, reception and recognition of the address.

Agreements on takeover of the mainline. All active devices of the system may participate in takeover of the mainline and the operations should be performed in the following sequence:

each active device ready to become the master in exchange over the mainline transmits a ZM [mainline request] signal;

the mainline arbiter analyzes the status of the ZM line. If there is a ZM signal and if there is no PZ [confirmation of request] signal, the arbiter transmits an RZM [mainline takeover authorization] signal, which should be fed to the device with the highest priority to take over the mainline that has established the ZM signal;

the device that established the ZM signal and that has received the RZM signal sets the PZ signal if there is no OBM [synchronization of exchange] signal and triggers the ZM. The device that has established the PZ signal becomes the master;

the arbiter, having received the PZ signal, triggers the RZM signal. Resetting of the PZ signal is authorized to the master device only after the last of the OTV [response of device] signals in the given exchange cycle has been reset.

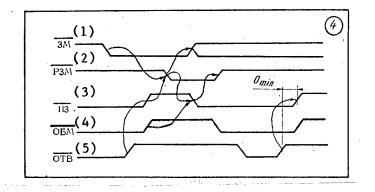

The time diagram of transfer of control to the mainline is presented in Figure 4. The priority of the devices is determined the same as in the interface according to OST 11 305.903-80.

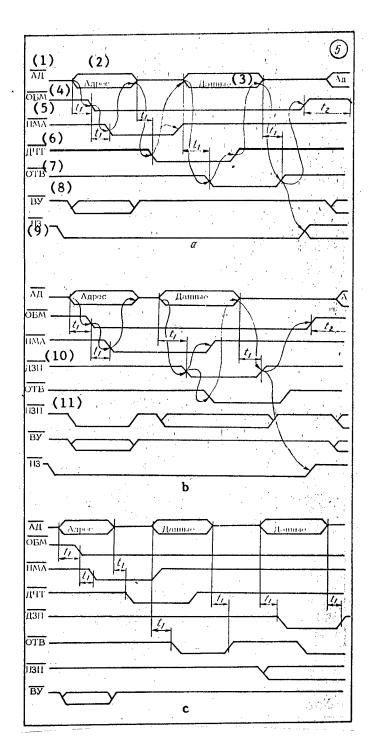

Agreements on data exchange. Three types of data exchange operations--reading, writing and reading-modification-writing--are determined by the standard. The time diagrams of these operations are presented in Figure 5.

Time Diagrams of Exchange Operations: a--reading; b--writing; c--reading-modification-writing ( $t_1 = 0 \text{ min}$ ;  $t_2 = 25 \text{ ns}$ )

Key:

1. Address-data bus

3. Data

2. Address

4. Synchronization of exchange

[Key continued on following page]

[Key continued from preceding page]

- 5. Address reception

- 6. Data readout

- 7. Response of device

- 8. Selection of device

- 9. Confirmation of request

- 10. Data recording

- 11. Record-byte feature

- The maximum access cycle time is limited to  $10 \,\mu$ s by this standard. If the access cycle to the slave device is not completed within  $10 \,\mu$ s, then the master device frees the mainline. If the processor is the master, it converts to the standard interrupt processing procedure. If any other active device is the master, then it ceases exchange and informs the processor of the interruption that has occurred.

The PZP [record-byte feature] in the data recording phases can have both a low and high level, thus determining recording of a byte of any 16-digit word, and recording of a byte corresponds to the active level of this signal.

It should be noted that specific time ratios between signals are not established by the standard--their strict priority is guaranteed by introduction of time intervals of 0 minutes. This permits the use of the proposed interface for a high-speed BIS, whereas the minimum exchange cycle time is limited to 750 ns when using the interface according to OST 11 305.903-80.

Agreements on interruption. Any device in the system can emit interrupt request signals. In this case the interrupted device performs the following operations:

having detected an interrupt request (ZPR signal) on its own line, it performs the procedure of takeover of the mainline;

having received control of the mainline, it transmits PPR (sic) [interrupt authorization] and DChT [data readout] signals and reads the interrupt vector from the interrupt source;

it converts to processing of the interruption according to the vector.

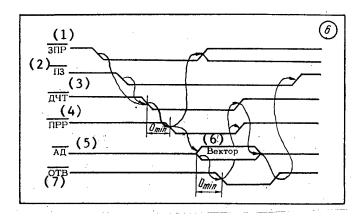

The time diagram of vector readout during interruption is presented in Figure 6.

Electric characteristics of the INTERBIS. The electric characteristics for the receiving and transmitting circuits of the BIS (receivers and transmitters) have been established on the assumption that the length of the communications between BIS does not exceed 0.5 meter (this is quite adequate when the BIS are installed within a single board) and if the level of static noise does not exceed 0.4 V.

General requirements. The electric characteristics of receivers and transmitters should not depend on the characteristics of the BIS manufacturing technology. Transmitters and receivers should be compatible with each other on logic signal levels (with noise stability reserve not below 0.4 V) and on

Time Diagram of Interrupt Vector Readout

## Key:

2.

3.

4.

Interrupt request 1. Request confirmation

Interrupt authorization

Data readout

Address-data bus 5.

Vector 6.

Response of device 7.

levels of current (output for transmitters and input for receivers). The ratio between the logic and electric states of the signals are presented in Table 2.

Table 2. Ratio Between Logic and Electric States of Signals

|                                | Величина логического сигнала (2)          |                                              |  |  |  |

|--------------------------------|-------------------------------------------|----------------------------------------------|--|--|--|

| Логическое<br>состояние<br>(1) | без черты нал буквен-<br>ным обозначением | с чертой над буквенным<br>обозначением       |  |  |  |

| 0                              | (5)<br>не более 0,8 В (низкиї<br>уровень) | (6)<br>не менсе 2,0 В (высо-<br>кий уровень) |  |  |  |

| 1                              | не менее 2,0 В (высо-<br>кий уровень)     | не более 0,8 В (низ-<br>кий уровень)         |  |  |  |

Key:

- 1. Logic state

- 2. Value of logic signal

- Without bar above letter notation 3.

- 4. With bar above letter notation

- 5. Not more than 0.8 V (low level)

- Not less than 2.0 V (high level) 6.

Requirements on transmitters. Three types of transmitter outputs--standard output, output with open collector (channel) and output with three states -have been determined by the standard.

The transmitter should provide a low-level output voltage of not more than 0.4 V with inflow load current up to 3.2 mA, while the high-level output voltage

should not be less than 2.4 V with outflow load current up to 0.1 mA. The spurious capacitance from the transmitter output should not exceed 15 pF. The transition time from the logic zero to the logic one state and the transition time from the logic one to the logic zero state of the transmitter, presented to the receiver input, should be as short as possible and should not exceed 25 ns if the transmission line is 0.5 meter long and if the nominal capacitor load is 100 pF.

Requirements on receivers. The low-level input threshold voltage should not be less than 0.8 V with outflow input current of not more than 0.25 mA. The high-level input threshold voltage should not be more than 2.0 V with inflow input current of not more than 0.04 mA. The spurious capacitance from the receiver input should not exceed 10 pF.

Conclusions. The proposed INTERBIS intraboard interface has rather wide functional capabilities, permits microprocessor systems of different configurations to be developed, is compatible with the intermodular parallel interface according to OST 11.305.903-80 and can serve as the basis for development of a microprocessor set of BIS of increased functional complexity.

## BIBLIOGRAPHY

- 1. Smolov, V. B., V. V. Barashenkov, V. D. Baykov et al, "Spetsializirovannyye TsVM" [Specialized Digital Computers], Moscow, Vysshaya shkola, 1981.

- 2. Hilburn, J. and P. Julich, "MikroEVM in mikroprotsessory" [Microcomputers and Microprocessors], Moscow, Mir, 1979.

- Borshchenko, Yu. I., V. L. Dshkhunyan, Yu. L. Otrokhov et al, "The Elektronika NTs-80-01 Single-Board Computer], ELEKTRONNAYA PROMYSHLENNOST', No 1, 1981.

- 4. Fors, Zh., "A Standard Microprocessor Bus that Simplifies the Tasks of Microcomputer Developers," ELEKTRONIKA, Vol 51, No 15, 1978.

- 5. Ogdin, C. A., "Microcomputer Bus Standardization Makes (Dollars and) Sense," EDN, Vol 23, No 5, 1978.

- Elmquist, K. A., H. Fullmer, D. B. Gustavson and G. Morrow, "Standard Specification for S-100 Bus Interface Devices," COMPUTER, Vol 12, No 7, 1979.

- 7. Digital Microcomputer Handbook, Maynard: Digital Equipment Corporation, 1976.

- 8. Balph, T. and I. Kister, "Microprocessor Bus Gears Up to a 32-Bit Future," ELECTRONIC DESIGN, Vol 28, No 14, 1980.

- 9. Yencharis, L., "But the Right Bus Evokes the System's Best," ELECTRONIC DESIGN, Vol 28, No 10, 1980.

- Cushmann, R. H., "Microcomputer Bus Standardization--Will Designers' Needs be Met?" EDN, Vol 23, No 4, 1978.

- 11. Microprocessor Data Manual, ELECTRONIC DESIGN, Vol 26, No 21, 1978.

- 13. Alekseyevskiy, M. A., M. N. Gal'perin and V. O. Ignat'yev, "A Method of Investigating the Operating Modes of a Control Computer in Real Time," in "Tsifrovaya vychislitel'naya tekhnika i programmirovaniye" [Digital Computer Equipment and Programming], Moscow, Sovetskaya radio, 1968.

COPYRIGHT: Izdatel'stvo "Naukova dumka" "Upravlyayushchiye sistemy i mashiny" 1982

6521 CSO: 1863/72

## HARDWARE

COMPUTER TECHNOLOGY AND AUTOMATION AS THE BASIS FOR INTENSIFICATION OF THE NATIONAL ECONOMY

Kiev UPRAVLYAYUSHCHIYE SISTEMY I MASHINY in Russian No 6, Nov-Dec 82 pp 3-6

[Article by Doctor of Technical Sciences Vladimir Aleksandrovich Myasnikov, USSR State Committee for Science and Technology, Moscow]

[Text] The 26th CPSU Congress determined a need to convert the national economy of the USSR toward a primarily intensive path of development, which will permit fuller use of the country's scientific and technical potential and on this basis will make it possible to conserve all types of resources used for social production. The most important condition for raising the level of intensification is extensive use of data processing, transmission and display devices and efficient use of them in automatic and automated control systems of different problem orientation and different hierarchical levels.

The tasks posed by the 26th CPSU Congress in this field have been solved since 1981 within the framework of 12 scientific and technical programs, including four specific complex programs that have received priority with respect to support of the work with resources, since the main goals of this program should be achieved during the 11th Five-Year Plan. It is planned to complete fulfillment of the basic tasks of the specific complex programs through development of "turnkey" automatic and automated control systems by enterprises, organizations and institutions of various designation with guaranteed efficiency and organization of serial production of computer equipment.

Development of the Unified Program-Compatible Computer System (YeS EVM) in the 1970s in the country laid the basis for industrial development of computer equipment and software and made it possible to forecast the development of computer equipment and to guarantee the most rapid introduction into the national economy.

The main result of work on the SM EVM [International Small Computer System] was to create two families of minicomputers with standardized peripheral devices and software that meet the needs of different sectors of the national economy and that are designed primarily for use in ASU TP [Automated production process control system], SAPR [Automated design system] and ASNI [Automated system for scientific research]. The principles of the problem orientation of SM EVM have been worked out (mainly by specialists of the Institute of Cybernetics imeni V. M. Glushkov, Ukrainian SSR Academy of Sciences), that take into account the specific technology of data processing in the systems and provide a significant reduction of expenditures and time for development and introduction of systems.

One of the achievements of the 10th Five-Year Plan is development and organization of serial production of microprocessors and microcomputers, which will permit the introduction of computer equipment in those sectors of the national economy where considerable capital expenditures were previously required for this. A total of 15 types of microprocessor sets with processing speed from 20 to 0.1 s is now being produced in the country, on the basis of which approximately 30 types of microcomputers, controllers and devices have been developed. The production of control microcomputers will increase approximately twentyfold during the 11th Five-Year Plan.

El'brus multiprocessor computer complexes, which laid the basis for development of new configurations of computer systems, were developed to solve complex scientific and technical and planning and economic problems that require a large volume of calculations. Work is also being completed on development of an essentially new multiprocessor computer with macroconveyor organization of calculations.

The situation in the country has been improved considerably with respect to the peripheral equipment of computers. The nomenclature of peripheral devices of the YeS EVM now numbers approximately 180 products and that of the SM EVM numbers more than 170 products (with regard to the equipment produced in CEMA member countries) and includes data preparation, input-output and storage devices. They include disk units with capacity of 100 and 200 Mbyte, tape units with high recording density, graphic and alphanumeric displays, multiconsole alphanumeric data display systems, various types of sequential and parallel printers, drum and flatbed plotters, data preparation devices based on magnetic carriers and other equipment. The development of operator-computer graphic interaction devices, which permits operational solution of problems of design automation and complex automation of scientific research, is of important significance.

The new peripheral equipment increases the efficiency of computers and of computer systems by increasing the data input-output speed 2-5-fold. Replacing punch cards and papertape with magnetic data carriers reduces the cost of data preparation by 30-50 percent, increases the labor productivity of computer operators by 50-60 percent, reduces the cost of information storage 1/8th to 1/10th and reduces the consumption of data carriers.

Extensive work has also been carried out in software development. Operating systems that provide processing in the packet and dialogue modes and in the multiprogramming mode have been developed for the YeS EVM. Program packs have been developed that expand the functions of operating systems, including the "Real-time supervisor," "Time-sharing mode" for computer multiplexing, the KAMA data remote control system. An operating system for the El'brus multiprocessor complex and a number of tape and disk operating systems for the SM EVM have been developed. Work is being conducted to develop the software for distributed multimachine complexes, for VTsKP [Multiple-user computer center] and computer networks based on the second and third generation YeS EVM and also to develop YeS EVM-SM EVM complexing equipment. The OKA, INES, SIOD-ZOS, BANK-OS and SETOR database control systems and the POISK and ASPID-Z data retrieval systems and a number of others have been developed and recommended for widespread use. Introduction of these systems will make it possible to accelerate development of ASU [Automated control system] and of other data processing systems and will also guarantee interaction between various types of automated systems and will increase the computer load factor.

The appearance of microprocessors and microcomputers advanced the serious problem of developing software related to the wide variety of microprocessors oriented toward different applications. Cross-programming systems and programming automation systems are now employed as microcomputer programming devices.

Whereas cross-programming systems are available for practically all Soviet microprocessors, more or less satisfactory programming automation systems have been developed for only the microprocessor of the K580 series and those based on the SM-1800 and Elektronika K-1-10 microcomputers.

A specific unified program is now being developed which will make it possible to combine the efforts of developers to overcome the difficulties arising in this problem, to increase the reliability of programs for microcomputers and to reduce the cost of their production significantly.

Such specialized production complexes and other programming automation equipment as the RTK, PRIZ and TKP, which increase the labor productivity of programmers twofold or more, were developed during the 10th Five-Year Plan and recommended for introduction. Investigations must subsequently be organized to develop universal multilanguage programming systems that guarantee automation of all phases of program development and operation.

The State Algorithm and Program Fund (gosFAP), consisting of specialized sector and territorial funds, is expanding its activity from year to year. This source of obtaining software will have ever greater significance in the operation of computer systems as the software industry develops.

Extensive use of microprocessor equipment results in serious technical and social consequences, related to a change in the nature of teaching people, a reduction of manual labor and a decrease of the number of workers in industry, commerce and administrative services. Microprocessors will find application in the 11th Five-Year Plan in more than 200,000 different types of industrial and domestic devices and installations, while they will be found in 1.8 million facilities in the 12th Five-Year Plan, which is in itself a technical revolution. Machines and devices equipped with microprocessors have improved technical and economic indicators and new functional capabilities.

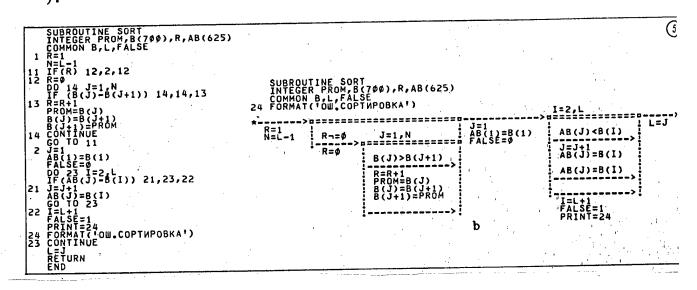

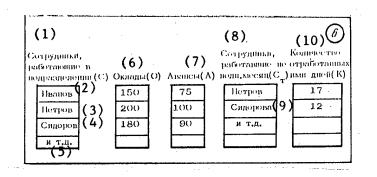

The use of microprocessors instead of ordinary computer equipment in existing or planned automated production complexes is very efficient. Thus, the use of the SM-1800 microcomputer instead of the widely employed SM-4 minicomputer permits a more than tenfold increase of the mean cycles between failures and cost reduction of 1/7th to 1/20th, reduction of consumed power several tenths and a 1/20th to 1/50th reduction of the area occupied by computers. The saving calculated per system will comprise 150,000-200,000 rubles.