#### WL-TR-95-1119

AVIONICS SOFTWARE REENGINEERING TECHNOLOGY (ASRET) PROJECT, VOLUME 1: Project Summary, Account, and Results

D.E. WILKENING J.P. LOYALL

**TASC** 55 Walkers Brook Drive Reading, Massachusetts 01867

MAY 1995 Project Final Report for 5/1/92 – 5/1/95

Approved for public release; Distribution is unlimited.

AVIONICS DIRECTORATE WRIGHT LABORATORY AIR FORCE MATERIEL COMMAND WRIGHT-PATTERSON AIR FORCE BASE, OHIO 45433-7409

DTIC QUALITY INCRESSED &

#### NOTICE

When Government drawings, specifications or other data are used for any purpose other than in connection with a definitely Government-related procurement, the United States Government incurs no responsibility or any obligation whatsoever. The fact that the government may have formulated or in any way supplied the said drawings, specifications, or other data, is not to be regarded by implication, or otherwise in any manner construed, as licensing the holder, or any other person or corporation; or as conveying any rights or permission to manufacture, use, or sell any patented invention that may in any way be related thereto.

This report is releasable to the National Technical Information Service (NTIS). At NTIS, it will be available to the general public, including foreign nations.

This technical report has been reviewed and is approved for publication.

· · · ·

KENNETH LITTLEJOHN, Eroject Engineer Software Concepts Section WL/AAAF-2

WILLIAM R. BAKER, Acting Chief

WILLIAM R. BAKER, Acting Chief Avionics Logistics Branch WL/AAAF

STEPHEN G. PETERS, Lt Col, USAF Deputy Chief System Avionics Division Avionics Directorate

If your address has changed, if you wish to be removed from our mailing list, or if the addressee is no longer employed by your organization, please notify WL/AAAF, WPAFB, OH 45433-7301 to help us maintain a current mailing list.

Copies of this report should not be returned unless return is required by security considerations, contractual obligations, or notice on a specific document.

# **REPORT DOCUMENTATION PAGE**

Form Approved OMB No. 0704-0188

| Public reporting burden for this collection of information is estimated to average one hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188), Washington, DC 20503.                                                                                                                                                                                                                                                                                                           |             |                |                                  |                        |                                  |                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|----------------------------------|------------------------|----------------------------------|--------------------------------------------|

| 1. AGENCY USE ONLY (Leave blank) 2. REPORT DATE 3. REP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                | ORT TYPE ANI<br>al 5/1/92 – 5/1/ | D DATES COVERED<br>/95 |                                  |                                            |

| <ul> <li>4. TITLE AND SUBTITLE<br/>Avionics Software Reengineering Technology (ASRET) Project<br/>Volume I Project Summary, Account and Results</li> <li>6. AUTHOR(S)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                |                                  |                        | PE 78<br>PR 30<br>TA 01          | 5-92-D-1052<br>012 F<br>90                 |

| D.E. Wilkening, J.P. Loyall (TA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                |                                  |                        | WU 14                            |                                            |

| <ol> <li>PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)</li> <li>TASC, Inc.</li> <li>55 Walkers Brook Drive<br/>Reading, MA 01867</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |                |                                  |                        | REPORT                           | MING ORGANIZATION<br>NUMBER<br>R-06661-4   |

| 9. SPONSORING/MONITORING AC<br>Avionic Directorate<br>Wright Laboratory<br>Air Force Materiel Command<br>Wright Patterson AFB OH 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | AND ADDRESS(ES | )                                |                        | 10. SPONSO<br>AGENCY<br>WL-TR-95 | RING/MONITORING<br>REPORT NUMBER<br>5-1119 |

| 11. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                |                                  |                        |                                  |                                            |

| 12a. DISTRIBUTION/AVAILABILITY S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                |                                  |                        | 12b. DISTRIB                     | UTION CODE                                 |

| Approved for public release; distribution is unlimited.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                |                                  |                        |                                  |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                |                                  |                        |                                  |                                            |

| 13. ABSTRACT (Maximum 200 words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5)          |                |                                  |                        |                                  |                                            |

| The objective of the Avionics Software Technology Support (ASTS) program is to perform research and development for enhancing<br>Embedded Computer System (ECS) software development and post-deployment support. The Avionics Software Reengineering<br>Technology (ASRET) project is the second delivery order under ASTS. Under ASRET, we investigated existing reengineering and<br>reverse engineering process, techniques, and software tools. Based upon this study, we developed a process model and environment<br>for reengineering software from one language (FORTRAN) to another (Ada). We designed and implemented a Reengineering Tool<br>(RET) prototype to assist the engineer in this process. We evaluated the RET by translating FORTRAN simulation code for Block 40<br>of the F-16 OFP to Ada. To prove the value of the RET, we recommend that software maintainers participate in an experiment using<br>an enhanced RET to reengineer an application in a production environment rather than in a laboratory. |             |                |                                  |                        |                                  |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                |                                  |                        |                                  |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                |                                  |                        |                                  |                                            |

| 14. SUBJECT TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |                |                                  | ····                   |                                  | 15. NUMBER OF PAGES                        |

| Reengineering, Reverse Engineering, Reuse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |                |                                  |                        |                                  | 82<br>16. PRICE CODE                       |

| 17. SECURITY CLASSIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |                | 40.055                           |                        |                                  |                                            |

| OF REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OF THIS PA  |                |                                  | NTY CLAS               | SIFICATION                       | 20. LIMITATION OF ABSTRAC                  |

| Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Unclassifie | ed             | Unclas                           | sified                 |                                  | UL                                         |

| NSN 7540-01-280-5500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                |                                  |                        |                                  | STANDARD FORM 298 (Rev. 2-8                |

# TABLE OF CONTENTS

| LI            | STOF    | FIGURES                              | v         |

|---------------|---------|--------------------------------------|-----------|

| $\mathbf{LI}$ | ST OF ' | TABLES                               | v         |

| E             | ŒCUT    | IVE SUMMARY                          | vi        |

| 1.            | INTR    | ODUCTION                             | 1         |

|               | 1.1     | Background                           | 1         |

|               | 1.2     | Task Structure                       | 2         |

|               | 1.3     | Accomplishments                      | 3         |

|               | 1.4     | Findings                             | 6         |

|               | 1.5     | Recommendations                      | 7         |

|               | 1.6     | Report Organization                  | 7         |

| 2.            | SOFT    | WARE REENGINEERING STUDY             | 9         |

|               | 2.1     | Literature Survey                    | 9         |

|               | 2.2     | Software Survey                      | 10        |

|               |         |                                      | 10        |

| 3.            | REEN    | GINEERING PROCESS MODEL              | 12        |

| 4.            | REEN    | GINEERING TOOL DEVELOPMENT           | 16        |

|               | 4.1     | RET Design Overview                  | 16        |

|               |         | 4.1.1 The User's Perspective         | 17        |

|               |         | 4.1.2 Representations                | 20        |

|               |         | 4.1.3 Architecture                   | 21        |

|               | 4.2     | Development Activities               | 25        |

|               |         | 4.2.1 Features                       | 25        |

|               |         | 4.2.2 Views                          | 29        |

| 5.            | TOOL    | TESTING AND EVALUATION               | 33        |

|               | 5.1     | Evaluation Summary                   | 33        |

|               | 5.2     | Subject System                       | 33        |

|               | 5.3     | Analysis Process                     | 34        |

|               |         | 5.3.1 SPAG Source Code Preprocessing | <b>34</b> |

|               |         | 5.3.2 REFINE/FORTRAN Analysis        | 34        |

|               |         | 5.3.3 RET Prototype Analysis         | 35        |

|               |         | 5.3.4 Creating Packager Views        | 36        |

|               |         | 5.3.5 Generate DFD Views             | 39        |

|               |         | 5.3.6 Generate Ada Code              | 40        |

.....

| 6. | USIN | G THE RET PROTOTYPE                                  | 43         |

|----|------|------------------------------------------------------|------------|

|    | 6.1  | Developing Program Structure Using the Packager      | 43         |

|    |      | 6.1.1 Definitions                                    | 44         |

|    |      | 6.1.2 Creating a Package Structure                   | 46         |

|    |      | 6.1.3 Editing the Package Structure                  | 48         |

|    |      | 6.1.4 Distributing Data Items                        | 49         |

|    | 6.2  | Translating Program Statements Using the Transformer | 50         |

|    | 6.3  | A Sample Application                                 | 52         |

| 7. | RETI | PROTOTYPE IMPLEMENTATION                             | 53         |

|    | 7.1  | Implementation Characteristics                       | 53         |

|    | 7.2  | Limitations of the RET Prototype Implementation      | 55         |

|    |      |                                                      | 00         |

| 8. | RETI | PROTOTYPE PLATFORM                                   | 58         |

|    | 8.1  | Software Files                                       | 58         |

|    | 8.2  | Data Files                                           | 61         |

| 9. | CONC | CLUSIONS AND RECOMMENDATIONS                         | 62         |

|    | 9.1  | Project Structure Summary                            | 62         |

|    | 9.2  | Conclusions                                          | 62         |

|    | 9.3  | Recommendations                                      | 68         |

|    |      |                                                      | 00         |

| AI | PENI | DIX A VENDOR INFORMATION                             | <b>A-1</b> |

| Ał | PENI | DIX B RECOMMENDED RET ENHANCEMENTS                   | <b>B-1</b> |

| AI | PENI | DIX C ACRONYMS FOR VOLUME I                          | <b>C-1</b> |

| RI | FERE | NCES                                                 | R-1        |

# LIST OF FIGURES

| Figure |                                        | Page |

|--------|----------------------------------------|------|

| 1      | ASRET Reengineering Process Model      | 12   |

| 2      | Developing Ada by Reusing FORTRAN      | 18   |

| 3      | Incorporating Macro and Micro Entities | 19   |

| 4      | RET Architecture                       | 22   |

| 5      | The Packager View                      | 45   |

# LIST OF TABLES

| Table |                                                            | Page |

|-------|------------------------------------------------------------|------|

| 1     | ASRET Task Structure                                       | 2    |

| 2     | Nondevelopmental Software                                  | 16   |

| 3     | Reengineering Tool (RET) Views                             | 20   |

| 4     | RET Prototype Features                                     | 25   |

| 5     | F-16 Block 40 OFP Subsystem Sizes                          | 34   |

| 6     | Unsupported FORTRAN Language Features                      | 57   |

| 7     | Installed Software Product Versions                        | 58   |

| 8     | Commands and Scripts Used During RET Prototype Development | 61   |

| 9     | RET Prototype Evaluation Data Files                        | 61   |

| 10    | RET Enhancements                                           | 69   |

. ...

# **EXECUTIVE SUMMARY**

The Avionics Software Technology Support (ASTS) program is an ongoing activity of the Software Concepts Group, Avionics Logistics Branch at Wright Laboratory (WL/ AAAF-3), Wright Patterson Air Force Base, Ohio. The objective of the ASTS program is to perform research and development for enhancing Embedded Computer System (ECS) software development and postdeployment support.

The Avionics Software Reengineering Technology (ASRET) project is the second delivery order (DO) under ASTS. This document is the final report for the ASRET project which concluded on 1 May 1995. The ASTS program continues beyond ASRET with several active DOs which are treating complementary research topics.

Under ASRET, we investigated existing reengineering and reverse engineering processes, techniques, and software tools. Based upon this study, we developed a process model and environment for reengineering software from one language (FORTRAN) to another (Ada). The approach is to engineer an Ada program by reusing portions of the original FORTRAN design and implementation. We designed and implemented a Reengineering Tool (RET) prototype to assist the engineer in this process. While the process model was developed to treat the specific FORTRAN-to-Ada reengineering, it is easily extensible to other source/target language combinations.

The RET applies reverse engineering techniques that facilitate redocumenting and recovering the design of a legacy system to help the engineer inspect and understand the system. The RET's restructuring capabilities help the engineer develop a program using design and implementation information recovered from the subject system.

The RET automatically translates low-level program statements, relieving the engineer from the tedious syntactical minutia, i.e., differences between the source and target programming language syntax, that divert attention from the more important design and implementation decisions requiring human judgement. By concentrating on tasks that are well-suited to automated support, the RET reduces the resources needed to reengineer avionics support software and helps the human engineer produce a more maintainable system.

We evaluated the RET prototype by translating FORTRAN source code, simulation software for Block 40 of the F-16 Operational Flight Program (OFP), to Ada. We are convinced after exercising the RET that the ASRET process model is sound and the top-down

vi

reengineering style that it encourages is effective. One of our goals for the RET prototype was that it help the engineer capture as much of the existing design from the original program as possible, and we accomplished this with the RET.

The RET is a prototype that we developed to evaluate reengineering technology and we recommend certain improvements that would allow production software maintainers who are not experts in language processing to achieve acceptable productivity. To prove the value of the RET, we recommend that software maintainers participate in an experiment, i.e., a Beta test, using an enhanced RET to reengineer an application in a production environment rather than in a laboratory.

# **INTRODUCTION**

This report presents the findings of the Avionics Software Reengineering Technology (ASRET) project. The ASRET project is the second DO issued to TASC under the Avionics Software Technology Support (ASTS) program.

# 1.1 BACKGROUND

1.

**Context** — The ASTS program is an ongoing activity of the Software Concepts Group, Avionics Logistics Branch at Wright Laboratory (WL/AAAF-3), Wright Patterson Air Force Base, Ohio. The objective of the ASTS program is to perform research and development for enhancing Embedded Computer System (ECS) software development and postdeployment support. The main objective of ASRET was to develop an automated Reengineering Tool (RET) prototype for avionics support software.

The reengineering of software from one language to another is becoming a necessity as Air Force organizations strive to modernize and improve the maintainability of their systems while avoiding the excessive costs of new development. Systems that have been in use for years often incur large maintenance costs (Ref. 1) for a number of reasons.

- Continual maintenance has made the current implementation and original design inconsistent, the code harder to understand and error-prone, and the documentation out-of-date.

- They are written in languages that have fallen out of favor. The limited selection of support tools for these languages, the corresponding expense of these tools, and the shrinking pool of qualified programmers to maintain the software adds to the expense of maintenance.

- They were developed without modern software engineering practices, resulting in code that lacks structure and is difficult to understand.

- Employee turnover has reduced the staff's understanding and "intimate" knowledge of the system.

Wright Laboratory initiated the ASRET project to help reduce maintenance costs for legacy systems and to assist in the evolution to Ada. To this end, we developed an environment for reengineering software from one language to another. We concentrated on the reengineering of avionics simulation software written in FORTRAN to Ada, and designed the RET so that it could support additional languages in the future.

#### 1.2 TASK STRUCTURE

The objective of the ASRET project was to develop an automated Reengineering Tool (RET) prototype for avionics support software. The specific goals included investigating existing reengineering and reverse engineering processes, techniques, and software tools, defining a reengineering process model, and building a RET prototype that supports

- Translating avionics simulation software written in FORTRAN to Ada,

- Improving the software through restructuring techniques,

- Changing the design of the software so that it is consistent with modern software engineering principles, and

- Adding documentation that is consistent with the software.

The ASRET project task structure is shown in Table 1.

|             | ASRETTASK                                 |  |  |  |

|-------------|-------------------------------------------|--|--|--|

| NUMBER NAME |                                           |  |  |  |

| 1           | Software Reengineering Study              |  |  |  |

| 2           | Reengineering Process Model Development   |  |  |  |

| 3           | Reengineering Tool Development            |  |  |  |

| 4           | Reengineering Tool Testing and Evaluation |  |  |  |

Table 1ASRET Task Structure

For Task 1, *Software Reengineering Study*, we conducted an extensive investigation of software reengineering tools and methods. The goal was to collect, organize, and present information on software reengineering tools and methods that might be relevant to ASRET, and to record the information for use in the subsequent tasks. The results of Task1 are documented in the Software Reengineering Study Report (Ref. 2).

During Task 2, *Reengineering Process Model Development*, we developed a reengineering process model based upon the results of Task 1, and developed the Software Requirements Specification (SRS) (Ref. 3) for the Reengineering Tool (RET) prototype.

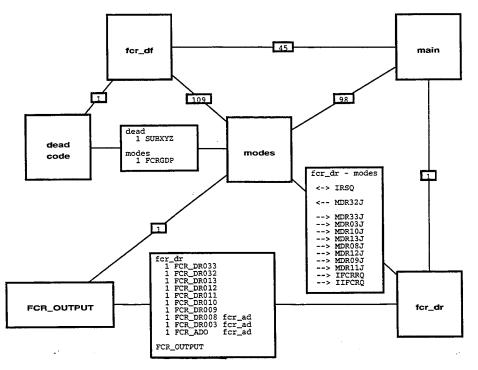

In Task 3, *Reengineering Tool Development*, we designed (Ref. 4) and implemented the RET prototype and exercised the RET by transforming the Fire Control Radar (FCR) subsystem of the F-16 Block 40 OFP simulation software provided to us by Wright Laboratory for this purpose.

We executed the RET prototype and converted most of the other subsystems in the Block 40 code to Ada in Task 4, *Reengineering Tool Testing and Evaluation*. The output that we generated appears in Volume II (Ref. 5).

#### **1.3 ACCOMPLISHMENTS**

This section summarizes the activities that we performed under, and the results of the four ASRET tasks shown in Table 1.

#### Software Reengineering Study

For Task1, Software Reengineering Study, we performed an extensive investigation of existing reengineering and reverse engineering processes, techniques, and tools. The study comprised two parts: the *Literature Survey*, and the *Software Survey*. We documented the results of the study in the Task 1 report, entitled "Avionics Software Reengineering Technology (ASRET) Software Reengineering Study Report" (Ref. 2).

#### **Reengineering Process Model Development**

Based upon the results of the Software Reengineering Study that we conducted in Task 1, we developed a process model that defines reengineering in terms of (nondestructively) engineering a new program by reusing the design and implementation of the original program. The process model is consistent with well-accepted reengineering models (Refs. 6, 7), and improves on them by dividing automated restructuring from restructuring that requires human insight and by defining restructuring tasks in terms of modern software engineering practices.

The ASRET Reengineering Process Model is documented in the "Software Requirements Specification for the Avionics Software Reengineering Tool (RET) Prototype System RET-SRS-01" (Ref. 3). Section 3 summarizes the process model and includes various refinements to the model that we made during Tasks 3 and 4.

#### **Reengineering Tool Development**

We designed and implemented a Reengineering Tool (RET) prototype that automates portions of the process model and incorporates selected techniques from the Software Reengineering Study Report (Ref. 2). Using the RET, the engineer nondestructively *develops* a new Ada program by *reusing* parts of the original FORTRAN design and implementation, as opposed to *changing* the original FORTRAN into Ada.

For example, an engineer can run an automatic packaging routine that extracts FORTRAN subprograms, translates their declarations into Ada, and arranges them into packages based upon their data usage. The engineer can then rearrange the resulting Ada subprograms interactively. When satisfied with the package structure, the engineer can direct the system to translate statements automatically in the bodies of the subprograms.

Most existing reengineering tools fall into one of two categories:

- 1. Reverse engineering and redocumentation tools (Refs. 8, 9) present different views of the structure of a program, such as control flow and data flow graphs, to aid in program understanding and manual reengineering.

- 2. Other tools (Refs. 10, 11) support automatic translation from one language to another or automated restructuring, such as the removal of GOTOs. These tools require little human interaction, but provide little support for design recovery or improvement.

Our approach can be described as *computer-assisted reengineering*. It provides automated reverse engineering, redocumentation, and translation of low-level program entities, and also provides a combination of user interaction and automated analysis to reorganize program statements and data into new modules.

The RET relieves the tedium associated with syntactic details (i.e., differences between the source and target programming language syntax), and allows the engineer to concentrate on more important design and implementation decisions that make the reengineered system more maintainable.

The RET design is documented in the "Software Design Document for the Avionics Software Reengineering Tool (RET) Prototype System RET-SDD-01" (Ref. 4). Section 4 summarizes the RET design.

### **Reengineering Tool Testing and Evaluation**

During the Reengineering Tool Testing and Evaluation task (Task 4), we analyzed simulation software for the F-16 Block 40 OFP. We processed the FORTRAN source code with a commercial control flow restructuring product and analyzed it with REFINE/FOR-TRAN. We analyzed all but one subsystem in Block 40 separately with the RET prototype. Using the RET, we constructed an Ada package structure, created dataflow diagrams, and generated Ada source code.

The testing and evaluation activities that we performed under Task 4 are documented in Section 5.3. The hardcopies that we produced of the Packager and Dataflow Diagram views appear in Vol. II (Ref. 5).

## Interviews, Conferences, and Papers

We conducted requirements interviews and attended workshops to collect information during the Software Reengineering Study task, and presented several papers during the Reengineering Tool Development task.

- 1. We held discussions with Mr. Kenneth Littlejohn (WL/AAAF-3) to discuss AS-RET requirements on 31 August 1992 in Dayton, Ohio. These discussions revealed that the ability to *change the functionality* of the system (as opposed to just restructuring it) was important to Wright Laboratory researchers.

- 2. We attended the third Reverse Engineering Forum sponsored by Northeastern University in Burlington, Massachusetts, 15-17 September 1992, and collected information on reengineering tools.

- 3. We gave a slide presentation on ASRET entitled Avionics Software Reengineering Technologies and Process Model Development (Ref. 12) at the Software Reengineering Workshop sponsored by the National Security Industrial Association's Software Committee and the Embedded Computing Institute, Naval Air Warfare Center, Ridgecrest, California, 12–14 January 1993. We obtained information on current reengineering research and software tools, and made contacts with researchers and practitioners in the field.

- 4. We conducted requirements interviews with avionics software maintainers at the Oklahoma City Air Logistics Center (OC-ALC), Tinker AFB, Oklahoma, 10 March 1993.

- 5. We presented a paper entitled A Reuse Approach to Computer-Assisted Software Reengineering (Ref. 13) at the Fourth Systems Reengineering Technology Workshop, sponsored by the Naval Surface Warfare Center, Dahlgren Division, White Oak Detachment, Monterey, California, 2-10 February 1994. The conference was billed as a workshop, but it was actually conducted as a symposium with little time for discussion.

- 6. We presented a paper entitled An Interactive Reengineering Tool for Constructive Language Translation (Ref. 14) at the Software Engineering Techniques Workshop on Software Reengineering, sponsored by Carnegie Mellon University and the Software Engineering Institute (CMU/SEI), Pittsburgh, Pennsylvania, 2-4 May 1994.

- 7. We wrote a paper entitled A Reuse Approach to Software Reengineering (Ref. 15) which is scheduled for publication in the June 1995 issue of the Journal of Systems and Software.

#### 1.4 FINDINGS

During Task 1, we conducted a broad review of the state of software reengineering. An important insight that we gained during the study is that the motivations, activities, and results that characterize the state of the practice in reengineering are not homogeneous. The implication is that any successful reengineering effort must be highly targeted. We decided to focus the RET prototype development effort and restrict its scope based upon the *primary* needs of our sponsor. The RET prototype would be a language translation aid that automates as much of the job as is practical, leaving the rest to the engineer.

In Task 2, we developed a reengineering process model that specifies a sequence of tasks to reengineer a program written in FORTRAN to Ada. We developed a RET prototype that helps the engineer develop an Ada system by reusing parts of the existing FORTRAN system. We built up the RET capabilities incrementally to mitigate risk by devising transformations as needed for a sequence of FORTRAN programs, chosen to progressively introduce more and more elements of the FORTRAN language.

We are convinced after exercising the RET prototype that the ASRET process model is sound and the top-down reengineering style that it encourages is effective. One of our goals for the RET prototype was that it help the engineer capture as much of the existing design from the original program as possible, and the RET accomplishes this.

The principles embodied in the RET prototype and the techniques that it implements are extensible to other languages, but we are now aware that it is no simple matter to change the RET to translate between other source and target languages. This underscores the importance of selecting reengineering techniques appropriate to the project at hand.

We explored the F-16 OFP simulation system with the RET prototype during Task 4. We found that the RET views are of great practical value despite the technical imperfections that we grappled with in Task 3. We found that they summarized salient features of the subject system and focused our attention on key areas, while providing information that is not directly accessible from the source code.

One of the goals of the ASRET project was to research and develop a prototype for avionics support software reengineering. The RET prototype has the potential for reducing the resources needed to reengineer avionics support software. It would help human engineers produce more maintainable systems if it were developed into a product.

## 1.5 RECOMMENDATIONS

To demonstrate the value of the RET prototype, we recommend that software maintainers participate in an experiment, i.e., a Beta test, using an enhanced RET to reengineer an application in a production environment rather than in a laboratory. The RET prototype needs some improvements before production software maintainers who are not experts in language processing could achieve productivity with it. We have already identified some limitations of the RET prototype in Section 7.2, and we recommend addressing these before the Beta test. We also recommend preparing the RET for the test by improving or adding certain capabilities.

The next step towards inserting the reengineering technology that we have developed is to transform the RET from a laboratory prototype to a production tool that avionics software maintainers will evaluate on mission essential / critical applications.

We will probably have to rely on experience reports to evaluate the RET. An engineer who's goals are consistent with those of the RET should be the final arbiter and must answer the question: "Would you use the tool again?" Based upon our experience with the RET prototype, we would expect a qualified affirmation. The modification of large computer programs will remain a most difficult undertaking, but an enhanced RET will increase the *value* of the end product, where value is a function of quality and cost.

The RET prototype will find a niche in reengineering. It relieves the engineer from syntactical minutia, i.e., differences between the source and target programming language syntax, that divert attention from the more important design and implementation decisions requiring human judgement. By concentrating on tasks that are well-suited to automated support, the RET prototype will reduce the resources needed to reengineer avionics support software and will help the human engineer produce a more maintainable system.

## **1.6 REPORT ORGANIZATION**

Section 1 introduces the ASRET project goals and task structure. Section 2 summarizes the results of the Software Reengineering study that we performed in Task 1. Section 3 defines the ASRET Reengineering Process Model that we created under Task 2. Section 4 provides an overview of the RET design and the RET development activities of Task 3. Section 5 describes how we exercised the RET during Task 4 and narrates our production of several RET views. Section 6 reveals RET prototype capabilities in the context

7

of reengineering a sample application. Section 7 explains certain characteristics of the RET prototype implementation. Section 8 documents the development platform software and hardware. Section 9 presents our conclusions and recommendations.

Appendix A provides vendor information for nondevelopmental software included in the RET prototype. Appendix B describes recommended enhancements to the RET prototype. Appendix C defines acronyms used in this document.

The Avionics Software Reengineering Technology (ASRET) Project Final Report, Volume II, Reengineering Tool (RET) Diagrams (Ref. 5) contains hardcopies of the graphical views that we created during Task 4.

# 2. SOFTWARE REENGINEERING STUDY

For Task1, Software Reengineering Study, we performed an extensive investigation of existing reengineering and reverse engineering processes, techniques, and tools. The study comprised two parts: the *Literature Survey*, and the *Software Survey*. We documented the results of the study in the Task 1 report, entitled "Avionics Software Reengineering Technology (ASRET) Software Reengineering Study Report" (Ref. 2). We briefly summarize the report below.

#### 2.1 LITERATURE SURVEY

For the Literature Survey, we conducted a broad review of the state of software reengineering. We identified existing reengineering tools, software products, and techniques that that we thought were both relevant to ASRET and implementable. We screened and organized reengineering literature to distinguish the most promising methods consistent with the ASRET objectives.

We were most interested in discovering results that had been demonstrated and proven effective in improving software. We reviewed the literature in the areas of software quality metrics, program understanding, restructuring transformations, graphical and internal representations, and hypermedia.

The results that we presented in the Software Reengineering Study Report (Ref. 2) are expository rather than analytic as the requirements and design decisions were to be made during the subsequent tasks. We organized the literature into broad categories and summarized each area. We also provided detailed notes on the literature that we reviewed. For each article, we provided a synopsis of *those aspects* of the work that we thought were *relevant to ASRET*.

An important insight that we gained during the study is that the motivations, activities, and results that characterize the state of the practice in reengineering are not homogeneous. The field is bound by no more specific common interests within the community than is, say, engineering. This is neither a detraction nor a commendation. It is a recognition of diversity.

9

The implication is that any successful reengineering effort must be predicated on a particular class of problems and the work must be tailored to the specific problem domain. A reengineering solution must be directed at the root cause of the problem to be effective, and must not just seek to alleviate the symptoms.

We discovered no broad spectrum reengineering nostrum for improving software. Every method that we investigated involved tradeoffs. We resolved, then, to focus the RET prototype development effort and restrict its scope based upon the *primary* needs of our sponsor. The RET prototype would be a language translation aid that automates as much of the job as is practical, leaving the rest to the engineer.

# 2.2 SOFTWARE SURVEY

**Process** — For the Software Survey, we identified and described a list of software tools relevant to ASRET. We developed a set of screening criteria based on our understanding of WL/AAAF needs in order to reduce the size of the list. We screened the tools, and presented details on the 38 remaining tools which best fit our needs.

We classified the 38 tools into *application domains* according to their principle functions or purposes. Each tool appears in as many domains as needed to describe the tool's functionality. The application domains are:

- 1. Reverse Engineering

- 2. Implementation

- 3. Forward Engineering

- 4. Translation

- 5. Redocumentation

- 6. Restructuring

- 7. Reusability

- 8. Analysis.

We defined a set of software characteristics for each application domain to describe various aspects of the tools. We also defined software characteristics for the following three categories which apply to all tools regardless of their functionality:

- 1. Host Platforms

- 2. Maturity

- 3. Usability.

We defined a total of 28 distinct software characteristics and described the remaining tools in terms of those characteristics.

**Results** — We identified five tools for further investigation.

- 1. REFINE/FORTRAN

- 2. Software Refinery

- 3. SPAG

- 4. Software Reengineering Environment (SRE)

- 5. Arch.

We would eventually include REFINE/FORTRAN, Software Refinery, and SPAG in the RET environment during the Reengineering Tool Development task described below. The Navy evaluated the SRE to translate CMS-2 source code to Ada. Arch is a proprietary tool developed by Robert Schwanke of Siemens Corporate Research, Inc. We provided relatively long abstracts for both SRE and Arch in the Software Survey.

We decided against pursuing SRE because the prototype was language-specific and we would have had to tailor it for FORTRAN in order to use it in ASRET. Our experience on ASRET has vindicated this decision; we have learned while developing the RET that the most difficult aspects of the type of reengineering problem that we chose to address are intimately related to specific programming language features peculiar to the source and target languages.

Arch (Ref. 16) is a proprietary tool and, while we were very interested in its capabilities, we didn't have access to it. We did contact Dr. Schwanke at Siemens, but he told us that he could not provide additional information on Arch. Arch apparently has much in common with the Rigi tool developed by Dr. Hausi Müller.

Rigi (Ref. 17) did not make it through the screening process of the Software Survey, but we became more interested in it prior to the Reengineering Tool Development task. We contacted Dr. Müller and learned that Rigi was also a proprietary tool.

Despite our lack of access to these tools, the Packager component of the RET is inspired by the work of Schwanke and Müller, and also by Hutchens (Ref. 18). Their projects share a common thread of component clustering via similarity metrics and the authors cite much of the same research.

# REENGINEERING PROCESS MODEL

3.

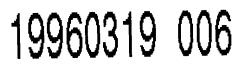

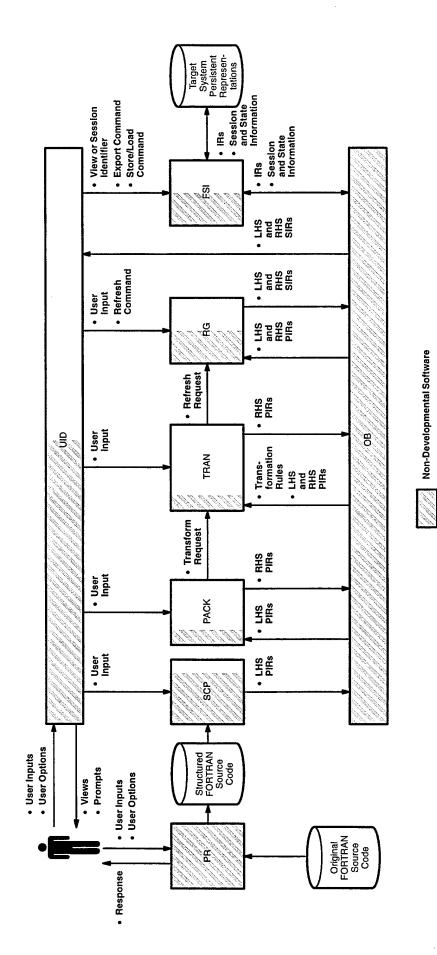

The reengineering process model as applied to the RET domain is illustrated in Figure 1. Steps in the process label the boxes in the figure, and inputs and outputs for each step label the icons between boxes.

The process model specifies a set of tasks (the steps of the process) that should be performed and the sequence in which they should be performed to reengineer a program written in FORTRAN to Ada. The process model also specifies the information necessary

Figure 1 ASRET Reengineering Process Model

and desirable to support these tasks. The process model does not specify how the tasks are to be performed (i.e., they might be automated, as many are in the RET, or they might be performed manually).

The first step in the process model is to perform some preliminary restructuring of the source code of the original implementation. Preliminary restructuring improves the layout of the source code by removing unstructured program constructs, such as GOTO statements, dead code, and implicit types. Preliminary restructuring is separated from the later restructuring step because it can be completely automated by commercial tools, and placed first in the process model because the structured version of the source program is usually easier to analyze, understand, and restructure.

After preliminary restructuring is complete, the RET analyzes the improved source code and constructs representations of the program. Some of the representations, such as abstract syntax graphs (ASGs) and symbol tables, are machine-readable representations used only by automated restructuring and redesign tasks. Others, such as flow graphs and structure charts, aid in program understanding, redocumentation, and manual restructuring. For manual restructuring, the set of representations contains a source code listing.

The engineer performs the restructuring, redesign, and redocumentation steps multiple times, each time building upon the results of the previous pass. A multipass approach is necessary because it is easier and less error-prone to reengineer a large program in stages, verifying the program after each pass. Restructuring (i.e., changing the structure of the program without changing its functionality) is performed first, possibly in several passes. These passes perform the following steps:

- *Macro control restructuring* groups statements and control structures of the program into modules, such as procedures, functions, and packages. This includes recovering modules of the original program, generating new modules, and specifying a declaration nesting structure for modules.

- *Macro data restructuring* groups data items, such as types, variables, and constants, and associates them with modules created during macro control restructuring. This includes recovering data groupings of the original program, creating new groupings, and creating abstract data types and records.

- *Micro control restructuring* manipulates individual control structures. This includes the translation of individual statements and functionality-maintaining alterations, such as code lifting (Ref. 19).

- *Micro data restructuring* manipulates individual data items. This includes actions such as translating, changing names, changing types, creating symbolic constants, and changing the scope of variables.

Macro control and data restructuring should be performed first to develop a modular structure for the target system, followed by micro control and data restructuring to restructure individual components of the program.

After restructuring is complete, the RET generates code in the target language and the program is tested to ensure that the restructuring did not introduce any errors or undesired functional changes. The test data of the original program can be used and the results compared with the results of testing the original program. In many cases, the test data will need to be reengineered to work with the reengineered program.

Any differences in the results of testing indicate the introduction of an unexpected functional change during restructuring. Coverage analysis must be performed during the testing of the target code because restructuring can introduce or alter control and data characteristics of the program. When an error in the target program is indicated, the program can be corrected by amending the target code directly or by restructuring the representations and regenerating the target code.

Once the engineer has restructured the program and created a functionally equivalent program in the target language, he can perform additional restructuring and redesign actions on the program. These steps use the same set of actions (i.e., macro control, macro data, micro control, and micro data), but have different goals.

Further restructuring improves the structure of the program without changing its functionality. The goal of redesign is to change the functionality of the program (e.g., to correct design flaws or improve the design). If the engineer edited the target program code to correct errors indicated during testing, the RET analyzes the code to generate representations before performing subsequent restructuring and redesign.

The RET performs redocumentation simultaneously with the restructuring and redesign steps and can save the generated representations for documenting the program structure and design. Volume II contains samples of documentation generated by the RET prototype. Furthermore, the engineer can add comments and annotations during restructuring and redesign as he gains insights about the code or design.

The RET reengineering process model includes modern software development processes, such as continuous testing, iterative restructuring and redesign, and configuration management. The process model is a specialization of the Chikofsky-Cross process management. The process model is a specialization of the Chikofsky-Cross process model (Refs. 7, 8). The entire Chikofsky-Cross model is represented, although there are differences:

- Program management extensions to the process model (Ref. 20) are included, such as configuration management and testing.

- Easily automated steps, such as preliminary restructuring, are separated so they can be addressed by commercial tools.

- Chikofsky-Cross steps are decomposed, such as restructuring into macro control, macro data, micro control, and micro data restructuring.

- Iteration steps that are implicit in the Chikofsky-Cross process are explicitly introduced.

# 4. **REENGINEERING TOOL DEVELOPMENT**

This section describes Task 3, Reengineering Tool Development. Section 4.1 describes salient features of the RET prototype design. The full design is documented in the Software Design Document for the Avionics Software Reengineering Tool (RET) Prototype System RET-SDD-01 (Ref. 4). Section 4.2 records the major development activities of Task 3.

## 4.1 RET DESIGN OVERVIEW

We implemented the RET prototype by integrating a number of Commercial Off-The-Shelf (COTS) tools and writing transformation rules and user interface code in the environment that they provide. Table 2 lists the nondevelopmental software products that we included in the RET prototype and provides references to the associated documentation. Appendix A contains vendor information. The RET prototype architecture is described in Section 4.1.3.

- Software Refinery is a software development environment from Reasoning Systems that is specialized for language processing applications. It comprises three components: REFINE, INTERVISTA, and DIALECT. The components provide a programming language and database, a tool kit for building user interfaces, and a parser/printer generator, respectively.

- *REFINE* provides Software Refinery with an object-based database and a wide-spectrum specification and programming language. It includes development features for compiling, executing, and debugging REFINE programs, and utilities for browsing and manipulating the object base at a low level.

| REFERENCE | PRODUCTNAME           | SUPPLIER                 | DESCRIPTION                          |

|-----------|-----------------------|--------------------------|--------------------------------------|

| 21        | Software Refinery     | Reasoning Systems        | language processing environment      |

| 21        | REFINE                | Reasoning Systems        | Software Refinery component          |

| 22        | INTERVISTA            | Reasoning Systems        | Software Refinery component          |

| 23        | DIALECT               | Reasoning Systems        | Software Refinery component          |

| 24        | <b>REFINE/FORTRAN</b> | Reasoning Systems        | language processing tool             |

| 25        | REFINE/Ada            | Reasoning Systems        | language processing tool             |

| 26        | plusFORT (SPAG)       | Polyhedron Software      | control flow restructurer            |

| 27        | X-Windows             | MIT X Consortium         | graphical communications protocol    |

| 28        | GNU Emacs             | Free Software Foundation | extensible, customizable text editor |

Table 2

Nondevelopmental Software

- *INTERVISTA* provides Software Refinery with basic Graphical User Interface (GUI) facilities that Reasoning Systems found to be the most convenient for developing language processing interfaces.

- *DIALECT* provides Software Refinery with a grammar specification language, a grammar parser, and parser and printer generators that create parsers and printers from grammars.

- *REFINE/FORTRAN* is an application built on top of Software Refinery by Reasoning Systems. It is used to reverse engineer and redocument FORTRAN code.

- *REFINE / Ada* is an application built on top of Software Refinery by Reasoning Systems. It is used to reverse engineer and redocument Ada code.

- SPAG is a component of the plusFORT product written by Polyhedron Software Ltd. The plusFORT product is a FORTRAN restructuring tool kit and the SPAG component performs control flow restructuring, among other things.

- X-Windows is the ubiquitous graphical communications protocol and the *de* facto standard interface for building GUI applications on Unix systems. The protocol is supported by the MIT X Consortium, but the software that implements it is provided with the hardware platform by the hardware vendor.

- *GNU Emacs* is an extensible, customizable, Lisp-based display editor provided by the Free Software Foundation.

## 4.1.1 The User's Perspective

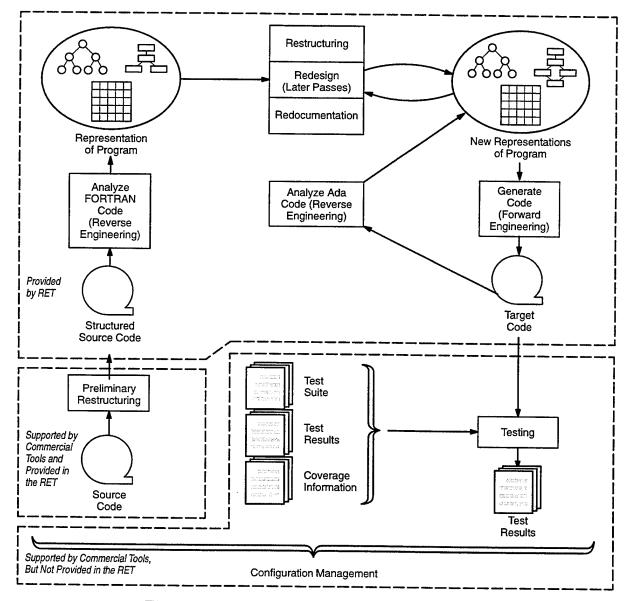

The RET prototype comprises two distinct logical parts called the Left-Hand Side (LHS) and the Right-Hand Side (RHS). The LHS provides views of the original FORTRAN program, or subject system. The RHS provides views of the Ada program being developed (i.e., the target system). The LHS allows the engineer to navigate and view aspects of the subject system, but does not support changing the subject system.

The RHS supports constructing, refining, viewing, and navigating the target system. The engineer constructs a basic structure for the RHS (macro restructuring) using information extracted from the LHS. Once the basic structure of the RHS is established, the engineer refines the target system (micro restructuring) on the RHS.

Semiautomated RET prototype components support construction activities; they suggest large-scale reorganizations of the subject system and populate the RHS with the basic structure of the target system. The components that support refinement allow the engineer to apply knowledge, which is beyond the RET, and human insight, which is lacking in the semiautomated support provided by the RET, to modify and improve the RHS representations. The RET prototype supports engineering an Ada program by reusing and transforming parts of the FORTRAN program. The process is iterative as illustrated in Figure 2.

- The engineer explores views of the original FORTRAN program that the RET generates on the LHS.

- The engineer selects LHS entities such as subroutines, statements, or data elements of the original FORTRAN program.

- The RET transforms the LHS entities and incorporates them into the RHS.

- The engineer may explore views representing the Ada program on the RHS.

- The engineer interactively or automatically refines the RHS through the views.

The engineer repeats the cycle, exploring the LHS to select additional FORTRAN entities to reuse in building the RHS. The graphical user interface presents the LHS and RHS views to the engineer while the object-based database manages the underlying data structures or internal representations.

Figure 2 Developing Ada by Reusing FORTRAN

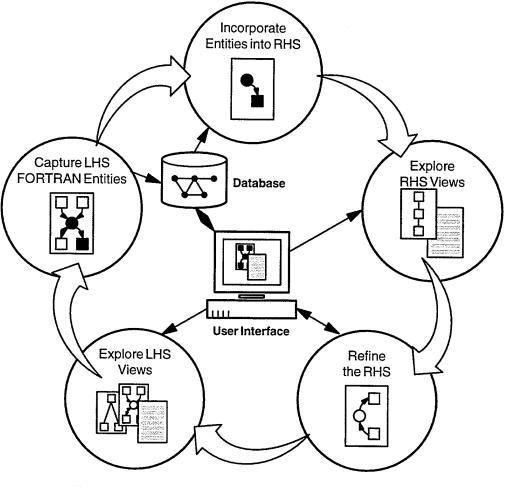

The RET approach to reengineering is to create a new program on the RHS, reusing components of the LHS. Structured design and programming principles are compatible with the RET and the ASRET Process Model described in Section 3. The specific steps that the engineer takes to apply the ASRET Process Model when using the RET prototype are illustrated in Figure 3.

- 1. The RET prototype constructs the package and subprogram structure for the RHS. It captures the subprogram structure from the LHS, transfers it to the RHS, and clusters the subprograms into Ada packages.

- 2. The engineer then refines the RHS structure so that related subprograms and data items are grouped together into packages.

- 3. The RET prototype moves data items and type declarations from the LHS to the packages and subprograms on the RHS to which they are most closely related.

- 4. The engineer then refines and redistributes the declarations. For example, data items that are closely related but used by several subprograms might be in different packages, and thus need to be grouped together. As another example, data items might be moved into or out of a package's private part to reflect their scope.

- 5. At this point, the modular structure of the program has been designed. The RET prototype transforms statements from the LHS and moves them to the bodies of the RHS subprograms and packages.

- 6. The engineer may then refine individual statements on the RHS to tune the RHS structure.

#### Figure 3 Incorporating Macro and Micro Entities

# 4.1.2 Representations

Internal Representations (IRs) are LHS and RHS data structures. The RET prototype provides two primary internal representations (PIRs): the Abstract Syntax Graph (ASG) and the Symbol Table (ST). An ASG is a detailed representation of a program, specifically, a parse tree. It is a data structure formed from objects and attributes. The classes of objects, types of attributes, and rules that define valid representations of FORTRAN (Ada) programs comprise the FORTRAN (Ada) *domain model*. The domain model is an augmented grammar that is input to DIALECT. It is a specification for the parser and printer that DIALECT generates.

The RET prototype uses the parsers and printers supplied by REFINE/FORTRAN and REFINE/Ada. We have made slight extensions to the domain models to store additional analysis information produced by the RET. The RET prototype uses the REFINE/ FORTRAN symbol table, also with slight extensions for analysis information.

Secondary internal representations (SIRs) are derived from the PIRs. The SIRs are the underlying data structures for the views presented to the engineer. The Software Design Document (Ref. 4) describes the SIRs. The RET provides the views listed in Table 3.

| LHS          | RHS | VIEW | NAME                | DISPLAYS                              |

|--------------|-----|------|---------------------|---------------------------------------|

| $\checkmark$ | 1   | SCL  | Source Code Listing | FORTRAN or Ada source code            |

|              | ~   | PACK | Packager Diagram    | Ada package structure                 |

| 1            |     | DED  | Declaration Diagram | FORTRAN declaration nesting structure |

| 1            |     | CD   | Call Diagram        | FORTRAN subprogram calling structure  |

|              | -   | DFD  | Data Flow Diagram   | Data flow through the Ada program     |

Table 3Reengineering Tool (RET) Views

- The Source Code Listing (SCL) shows the FORTRAN source code (after processing by SPAG) on the LHS and the generated Ada code on the RHS.

- The Packager view (PACK) shows the package and subprogram nesting structure, and provides a graphical interface for developing the Ada package structure on the RHS.

- The Declaration Diagram (DED) documents the FORTRAN system declaration structure. The PACK provides similar information for the Ada system, so we did not create an Ada version of the DED.

- The Call Diagram (CD) documents the FORTRAN calling structure. The PACK provides call diagrams for the Ada system, so we did not create an Ada version of the CD.

- The Dataflow Diagram (DFD) documents the Ada system data flow. The PACK provides some data flow information that is derived from the FORTRAN system, so we didn't create a version of the DFD for the FORTRAN system.

Section 4.2.2 describes the RET prototype views in greater detail and recounts our experiences in developing the views.

#### 4.1.3 Architecture

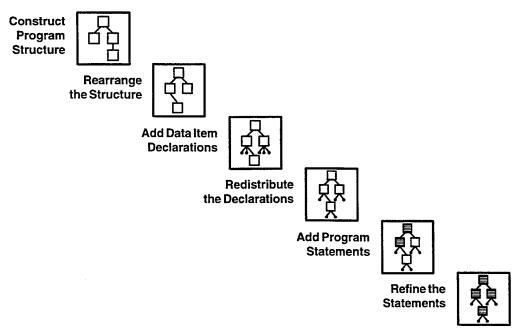

Figure 4 shows the RET architecture. It depicts the organization of major RET components, and indicates the data flow relationships among them. The Preliminary Restructurer (PR) performs control flow restructuring. The Source Code Processor (SCP) generates the LHS PIRs.

The engineer constructs the RHS PIRs using the Packager (PACK) and Transformer (TRAN). The Representation Generator (RG) creates the SIRs on both sides from the PIRs. The User Interface and Display (UID) creates the corresponding views, and provides the means by which the engineer interacts with the views on both sides and alters the views on the RHS. The Transformer implements the changes by transforming the RHS PIRs, and the Representation Generator propagates the changes to the RHS SIRs. The User Interface and Display refreshes the RHS views in response to the changes.

The File System Interface (FSI) manages external persistent data and the Object Base (OB) manages internal data in the form of data objects, attributes on these objects, and relationships between objects.

The views, PIRs, and SIRs are thus interdependent, but the engineer need not be aware that the PIRs and SIRs exist. Any changes that the engineer makes to the target system through the views provided by the User Interface and Display appear to affect the views exclusively. The components are described in more detail below.

**Preliminary Restructurer** — The Preliminary Restructurer (PR) restructures the control flow of the original FORTRAN source code by eliminating branches into or out of loops and decisions. It eliminates all GOTO statements, leaving only the structured programming constructs: sequence, selection, and iteration. We refer to this specialized form of restructuring as control flow restructuring to distinguish it from the more general concept of restructuring described in Section 2.