FINAL REPORT

# SBIR PHASE II

# "ELECTRONICALLY STEERABLE AGILE BEAM ANTENNA"

Contract DAAE07-87-C-R102

USA TANK AND AUTOMOTIVE COMMAND

October 30, 1989

Principal Investigator : Stephen C. Peterson Project Manager : Thomas J. McLaughlin

> TECHNICAL RESEARCH ASSOCIATES 410 CHIPETA WAY SALT LAKE CITY, UTAH 84108 (801) 582 - 8080

> > DTIC QUALITY INSPECTED 3

19950112 056

م تعريم ا

| REPORT DOC                                                                                                                                                                                                                                                                                                                                                   | UMENTATION PA                                                                                                                                                                                                        | GE                                                                                                                                                             |                                                                                                        | orm Approved<br>MB No. 0704-0188                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Public reporting burden for this collection of informa<br>gathering and maintaining the data needed, and com<br>collection of information, including suggestions for re<br>Davis Highway, Suite 1204, Arlington, VA 22202-4302                                                                                                                               | tion is estimated to average 1 hour per i<br>pleting and reviewing the collection of is<br>iducing this burden, to Washington Hear<br>, and to the Office of Management and                                          | esponse, including the time for<br>iformation. Send comments ri-<br>liquarters Services, Directorate<br>Judget, Paperwork Reduction f                          |                                                                                                        |                                                                                                                                               |

| 1. AGENCY USE ONLY (Leave blank)                                                                                                                                                                                                                                                                                                                             | 2. REPORT DATE<br>October 30, 1989                                                                                                                                                                                   | 3. REPORT TYPE A<br>Final 9/8                                                                                                                                  | ND DATES CO                                                                                            | VERED                                                                                                                                         |

| . TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                      | 1 1 1 1 1 1 1 1 1 1                                                                                                                                            |                                                                                                        | G NUMBERS                                                                                                                                     |

| Electronically Steerable                                                                                                                                                                                                                                                                                                                                     | Agile Beam Antenna                                                                                                                                                                                                   | 1                                                                                                                                                              | C DAAEC                                                                                                | )7-87-C-R102                                                                                                                                  |

| . AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                      |                                                                                                                                                                | -                                                                                                      |                                                                                                                                               |

| Stephen C. Peterson<br>Thomas J. McLaughlin                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                      |                                                                                                                                                                |                                                                                                        |                                                                                                                                               |

| PERFORMING ORGANIZATION NAME                                                                                                                                                                                                                                                                                                                                 | (S) AND ADDRESS(ES)                                                                                                                                                                                                  |                                                                                                                                                                | 8. PERFOR                                                                                              | MING ORGANIZATION                                                                                                                             |

| Technical Research Assoc                                                                                                                                                                                                                                                                                                                                     | iates                                                                                                                                                                                                                |                                                                                                                                                                |                                                                                                        | NUMBER                                                                                                                                        |

| 410 Chipeta Way                                                                                                                                                                                                                                                                                                                                              | 100                                                                                                                                                                                                                  |                                                                                                                                                                | N/A                                                                                                    |                                                                                                                                               |

| Salt Lake City, Utah 84                                                                                                                                                                                                                                                                                                                                      | 100                                                                                                                                                                                                                  |                                                                                                                                                                |                                                                                                        |                                                                                                                                               |

| . SPONSORING/MONITORING AGENCY                                                                                                                                                                                                                                                                                                                               | NAME(S) AND ADDRESS(ES)                                                                                                                                                                                              |                                                                                                                                                                | 10. SPONS                                                                                              |                                                                                                                                               |

| US Army Tank-automotive                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                      |                                                                                                                                                                |                                                                                                        | Y REPORT NUMBER                                                                                                                               |

| ATTN: AMSTA-TR-V                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                      |                                                                                                                                                                | N/A                                                                                                    |                                                                                                                                               |

| Warren, MI 48397-5000                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                      |                                                                                                                                                                | N/ A                                                                                                   |                                                                                                                                               |

| 1. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                       | ۰۰.<br>مرکز این می این این این این این این این این این ای                                                                                                                                                            |                                                                                                                                                                |                                                                                                        |                                                                                                                                               |

| 22a. DISTRIBUTION / AVAILABILITY STAT<br>Approved for public rele                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                      | is unlimited.                                                                                                                                                  | 126. DISTR                                                                                             | IBUTION CODE                                                                                                                                  |

| 13. ABSTRACT (Maximum 200 words)                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                      | ·                                                                                                                                                              |                                                                                                        |                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                      |                                                                                                                                                                |                                                                                                        |                                                                                                                                               |

| The Electronically Steerable Ag<br>Small Business Innovative Rese<br>antenna that transmits real-time<br>command center (CC). The ES<br>direction of the incoming VHF<br>the radio frequency (RF) micro<br>eight circular-polarized, helical<br>mechanical system are: 1) bette<br>because of circular-polarized, helical<br>direction to the CC can be done | earch (SBIR) Program.<br>e analog video from an u<br>SABA uses a Very High<br>command link from the<br>wave signal carrying the<br>antennas. The advanta<br>er reliability because the<br>helical design; and 3) bet | The goal of the p<br>inmanned robotic<br>Frequency (VHF)<br>CC. The ESABA<br>e video from the v<br>ges of the ESABA<br>re are no moving p<br>ter performance b | roject is to<br>vehicle (RV<br>) phased arr<br>then elect:<br>ideo transm<br>approach<br>parts; 2) bet | develop a rugged<br>() to a manned<br>ray to determine the<br>ronically switches<br>itter to one of<br>over a conventional<br>ter link margin |

| 14. SUBJECT TERMS                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                      |                                                                                                                                                                |                                                                                                        |                                                                                                                                               |

| Antenna; Microwave; ver                                                                                                                                                                                                                                                                                                                                      | y high frequency (V                                                                                                                                                                                                  | HF);                                                                                                                                                           |                                                                                                        | 5. NUMBER OF PAGES<br>61                                                                                                                      |

| Analog video; Microcont                                                                                                                                                                                                                                                                                                                                      | roller; Robotic Veh                                                                                                                                                                                                  | icle                                                                                                                                                           | 10                                                                                                     | 5. PRICE CODE                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                              | SECURITY CLASSIFICATION                                                                                                                                                                                              | 19. SECURITY CLASSIF                                                                                                                                           | ICATION 2                                                                                              |                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                      | OF ABSTRACT                                                                                                                                                    |                                                                                                        | . LIMITATION OF ABSTRAC                                                                                                                       |

|       | Unclassified     |

|-------|------------------|

| NS: J | 7540-01-280-5500 |

460

and the state of the second state of the secon

in the second

وستصفح المتحج المرتيص والأرا

Come and Standard Form 298 (Rev 2-89) TABLE OF CONTENTS

۸.

I. INTRODUCTION

| I.A.       | BACKGROUND5                             |

|------------|-----------------------------------------|

| I.B.       | PURPOSE OF ESABA AND ADVANTAGES6        |

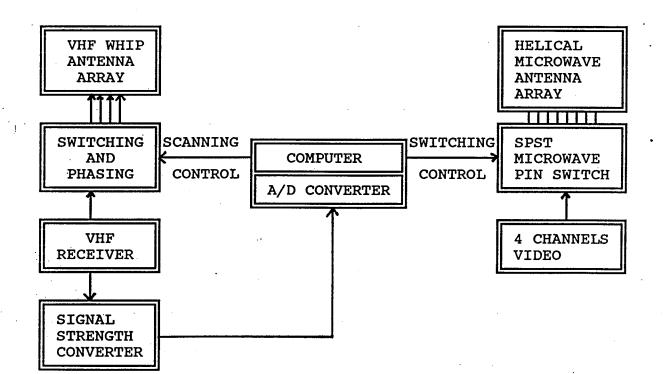

| I.C.       | SYSTEM BLOCK DIAGRAM                    |

|            |                                         |

| II. VHF LI | INK                                     |

| II.A.      | OVERVIEW                                |

| II.A.      |                                         |

|            | 2. THEORY OF PHASED ARRAY               |

| II.B.      | PHASING BOARD (PB)                      |

| II.B.      |                                         |

| II.B.      |                                         |

| II.B.      |                                         |

| II.C.      | PHASING BOARD DRIVER (PBD)              |

|            |                                         |

| II.C.      |                                         |

| II.C.      | · · · · · · · · · · · · · · · · · · ·   |

| II.C.      |                                         |

|            | WHIP ANTENNAS                           |

| II.D.      |                                         |

|            | 2. PICTURE                              |

|            | VHF SYSTEM TEST                         |

|            | 1. VHF PHASED ARRAY ANTENNA PATTERNS25  |

| · II.E.    | 2. PICTURES OF VHF ANTENNA TEST RANGE27 |

|            |                                         |

| III. MICRO |                                         |

| III.A.     | OVERVIEW                                |

|            | HELICAL ANTENNAS                        |

| III.E      |                                         |

| III.E      |                                         |

| III.E      |                                         |

|            | MICROWAVE SWITCH BOARD (UWSB)           |

| III.C      |                                         |

| III.C      |                                         |

| III.C      |                                         |

| III.D.     | MICROWAVE SWITCH DRIVER BOARD (UWSDB)   |

| III.D      |                                         |

| III.D      |                                         |

| III.D      | .3. PICTURE AND SCHEMATICS              |

|            |                                         |

| IV. MICROC | CONTROLLER AND RADIO                    |

|            | OVERVIEW                                |

| IV.B.      | MICROCONTROLLER                         |

| IV.B.      | 1. GENERAL SPECIFICATIONS               |

| IV.B.      |                                         |

| IV.B.      | -                                       |

|            | RADIO                                   |

| IV.C.      |                                         |

| IV.C.      |                                         |

| IV.C.      |                                         |

| IV.C.      |                                         |

| TA.C.      |                                         |

| Á    | vanability Codes          |

|------|---------------------------|

| Dist | Avail and / or<br>Special |

| A-1  |                           |

.....

2

.

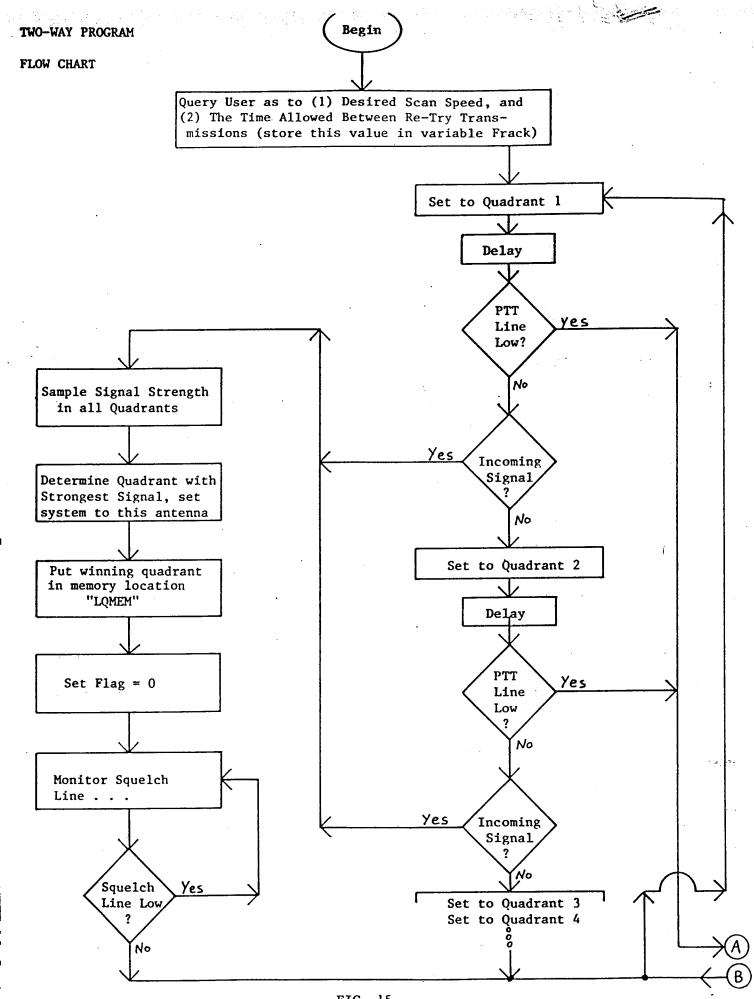

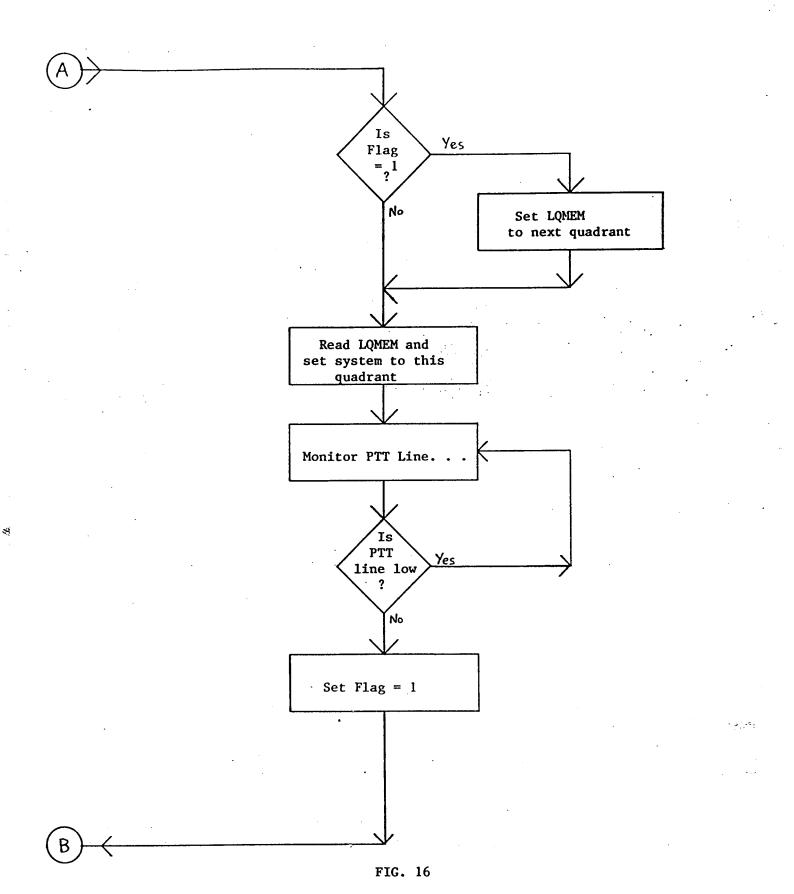

# V. SOFTWARE

| V.A.         | 0       | VERVIEW                                               |  |  |  |  |  |

|--------------|---------|-------------------------------------------------------|--|--|--|--|--|

| V.B.         | М       | ODE SELECTION                                         |  |  |  |  |  |

|              | V.B.1.  | DIP SWITCH SELECTION OF OPERATION MODES47             |  |  |  |  |  |

|              |         | COMPUTER OPERATING PROPERLY (COP) ACTIVATION48        |  |  |  |  |  |

| v.c.         | М       | AIN PROGRAM                                           |  |  |  |  |  |

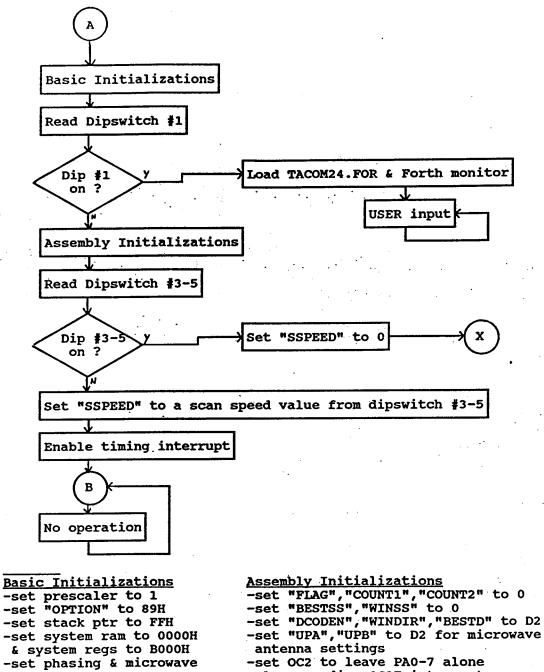

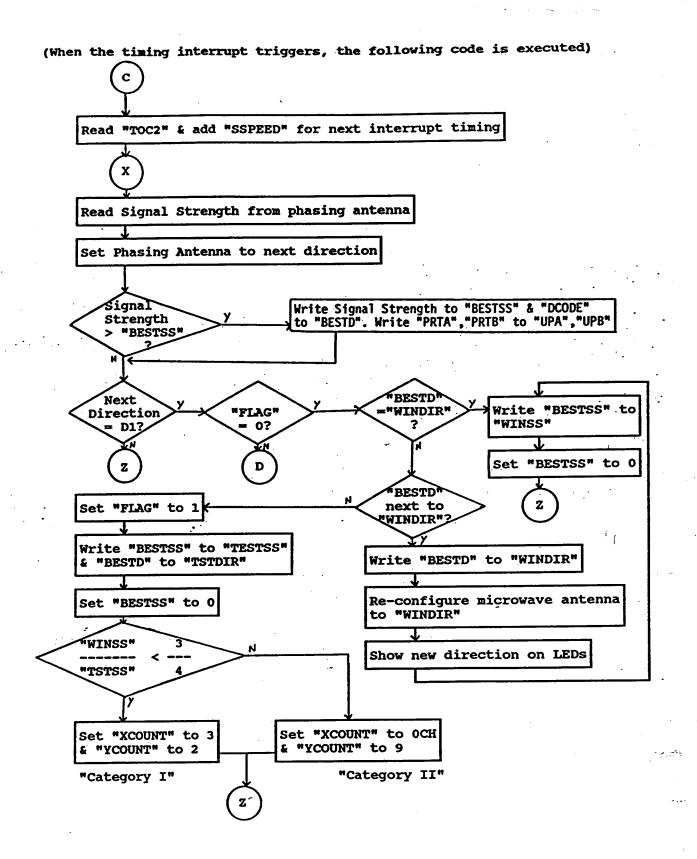

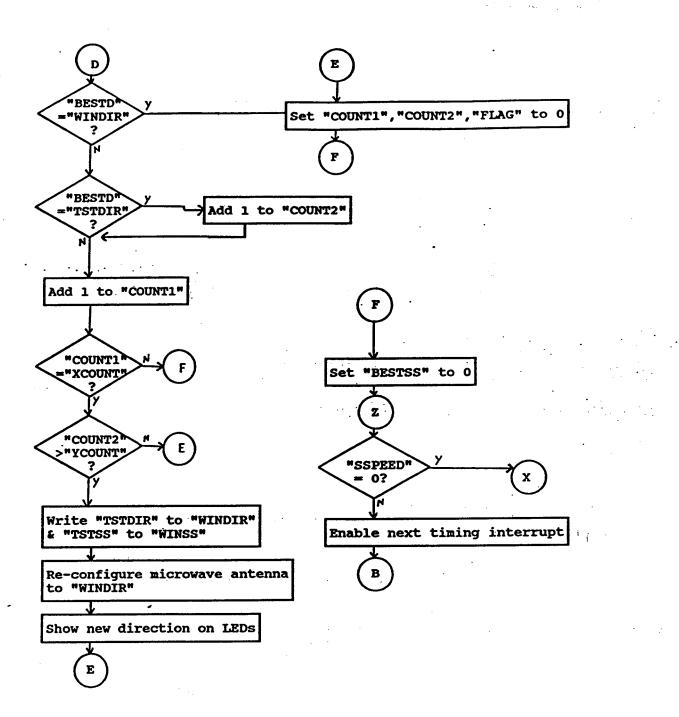

|              | V.C.1.  | FLOW CHART                                            |  |  |  |  |  |

|              |         | EXPLANATION                                           |  |  |  |  |  |

|              | V.C.3.  |                                                       |  |  |  |  |  |

| V.D.         | F       | ORTH MONITOR AND SYSTEM TEST AIDS                     |  |  |  |  |  |

| 2            | V.D.1.  | OPERATION                                             |  |  |  |  |  |

|              | V.D.2.  | FORTH WORDS                                           |  |  |  |  |  |

|              | V.D.3.  | FORTH PROGRAM LISTING                                 |  |  |  |  |  |

| VI. J        | POWER M | ODULE                                                 |  |  |  |  |  |

|              |         |                                                       |  |  |  |  |  |

| VI.A.        | . P     | OWER REQUIREMENTS                                     |  |  |  |  |  |

| VI.B.        | . P     | OWER MODULE SPECIFICATIONS                            |  |  |  |  |  |

| VI.C         | . P     | OWER MODULE PICTURE                                   |  |  |  |  |  |

| <u>vII.</u>  | SYSTEM  | ENCLOSURES                                            |  |  |  |  |  |

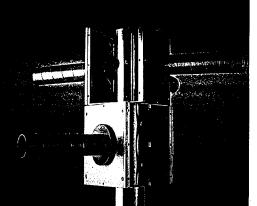

| VII.         | A. M    | AST AND DOME STRUCTURE                                |  |  |  |  |  |

| VII.I        | B. 1    | 9" RACK SYSTEM ENCLOSURE                              |  |  |  |  |  |

| <u>VIII</u>  | . SYSTE | M PERFORMANCE                                         |  |  |  |  |  |

| VIII         | .A. 5   | YSTEM PERFORMANCE AND THE                             |  |  |  |  |  |

| VIII         | .B. S   | REQUIREMENTS OF THE CONTRACT                          |  |  |  |  |  |

| <u>IX.</u> 2 | APPENDI | CES                                                   |  |  |  |  |  |

|              |         | AIN PROGRAM CODE LISTING<br>ORTH PROGRAM CODE LISTING |  |  |  |  |  |

| IX.B.        | . r     | UKTR PROGRAM CODE LISTING                             |  |  |  |  |  |

۰. • ب

- - - - -

- IX.C. PARTS LIST WITH VENDOR AND COST DATA

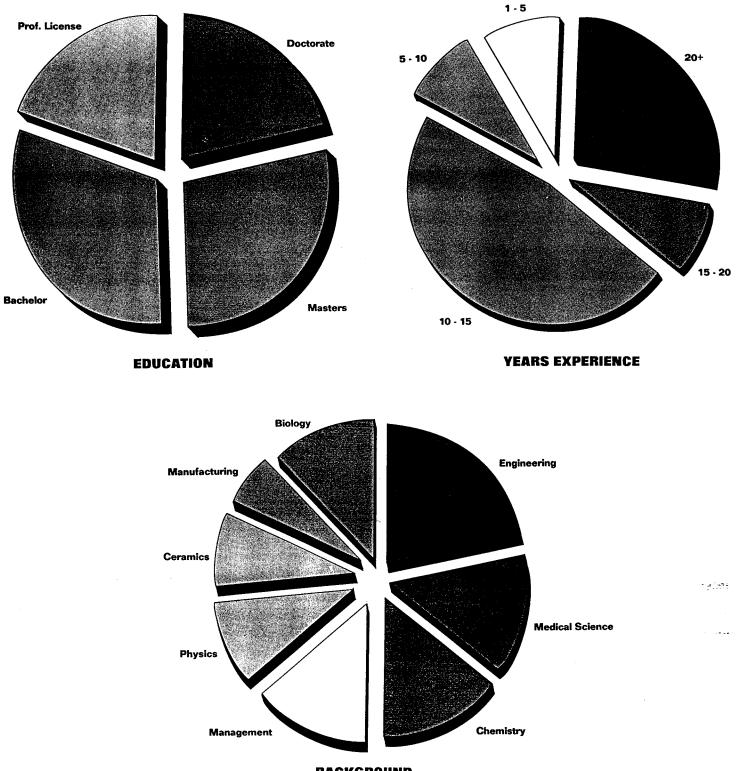

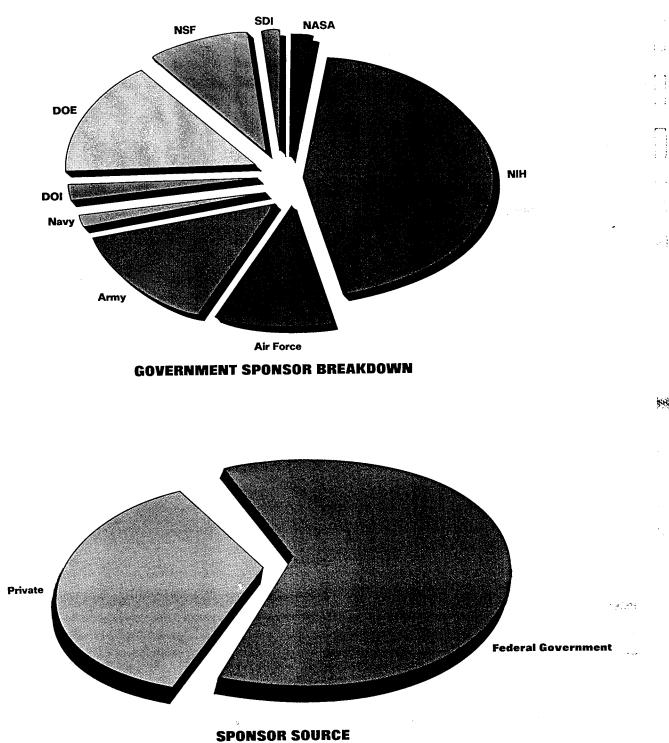

- IX.D. TRA CAPABILITIES GUIDE

- IX.E. PHASE I FINAL REPORT

# LIST OF FIGURES

ι,

. ...

.

|           | BCE                                              |

|-----------|--------------------------------------------------|

| FIGURE 1  | System Block Diagram7                            |

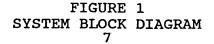

| FIGURE 2  | Two Element Radiation Patterns9                  |

| FIGURE 3  | Azimuthal Pattern from Two Antennas              |

| FIGURE 4  | Diagonal and Broadside Radiation Patterns11      |

| FIGURE 5  | Directional Patterns from Four Element Array12   |

| FIGURE 6  | Computer Generated Directional Patterns          |

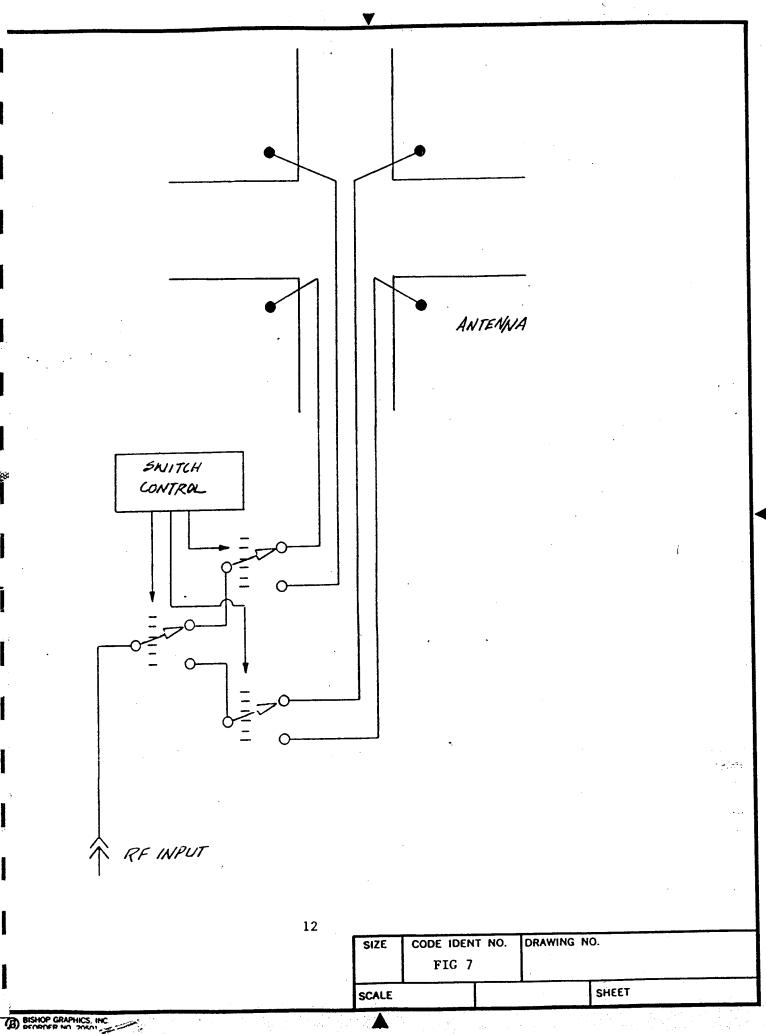

| FIGURE 7  | Block Diagram of Phasing Board14                 |

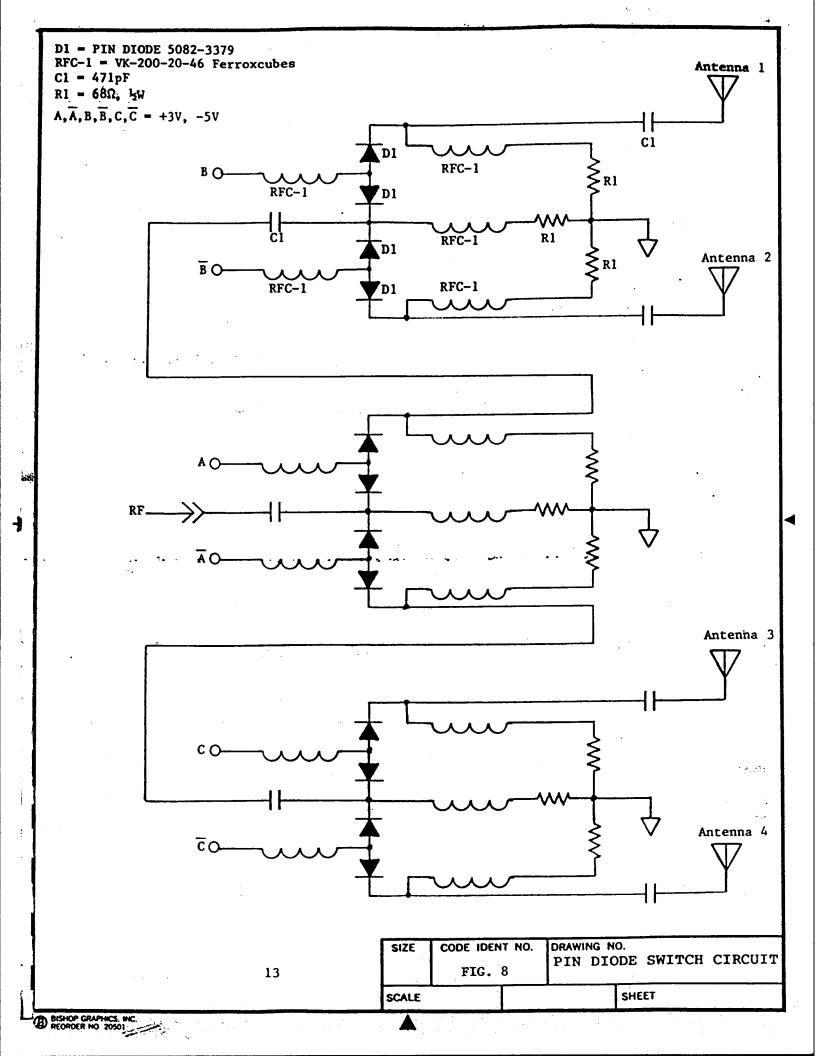

| FIGURE 8  | A PIN Switch in the Phasing Board15              |

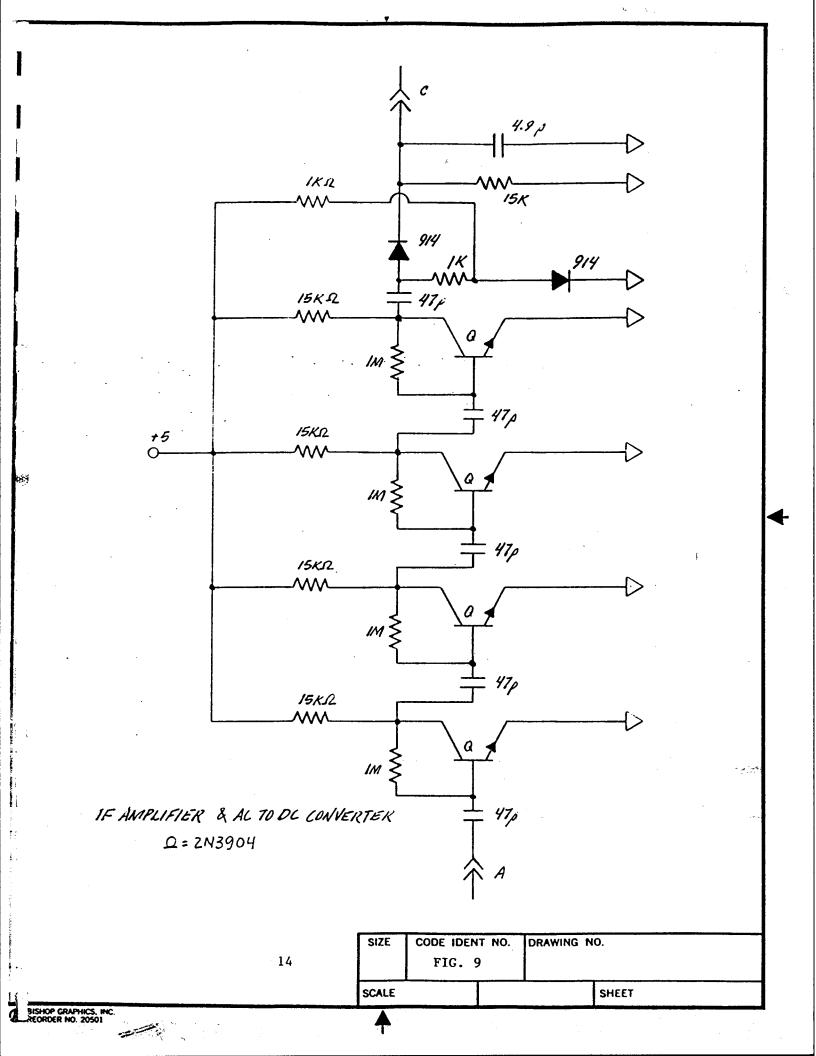

| FIGURE 9  | Logic Levels to Drive Phasing Board              |

| FIGURE 10 | Measured Phased Shifts through Phasing Board17   |

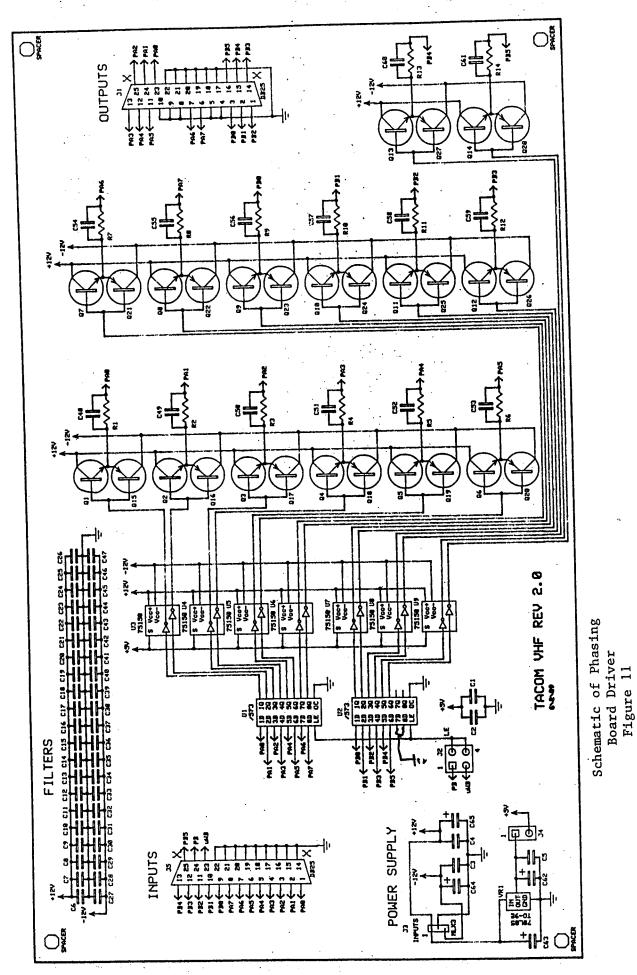

| FIGURE 11 | Schematic of Phasing Board Driver                |

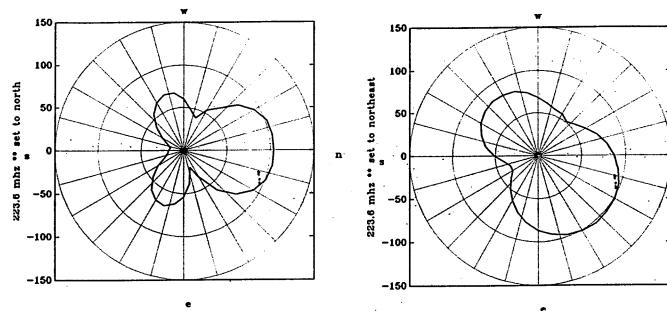

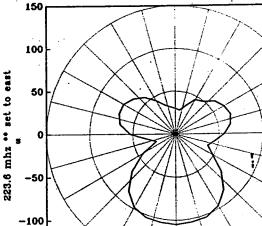

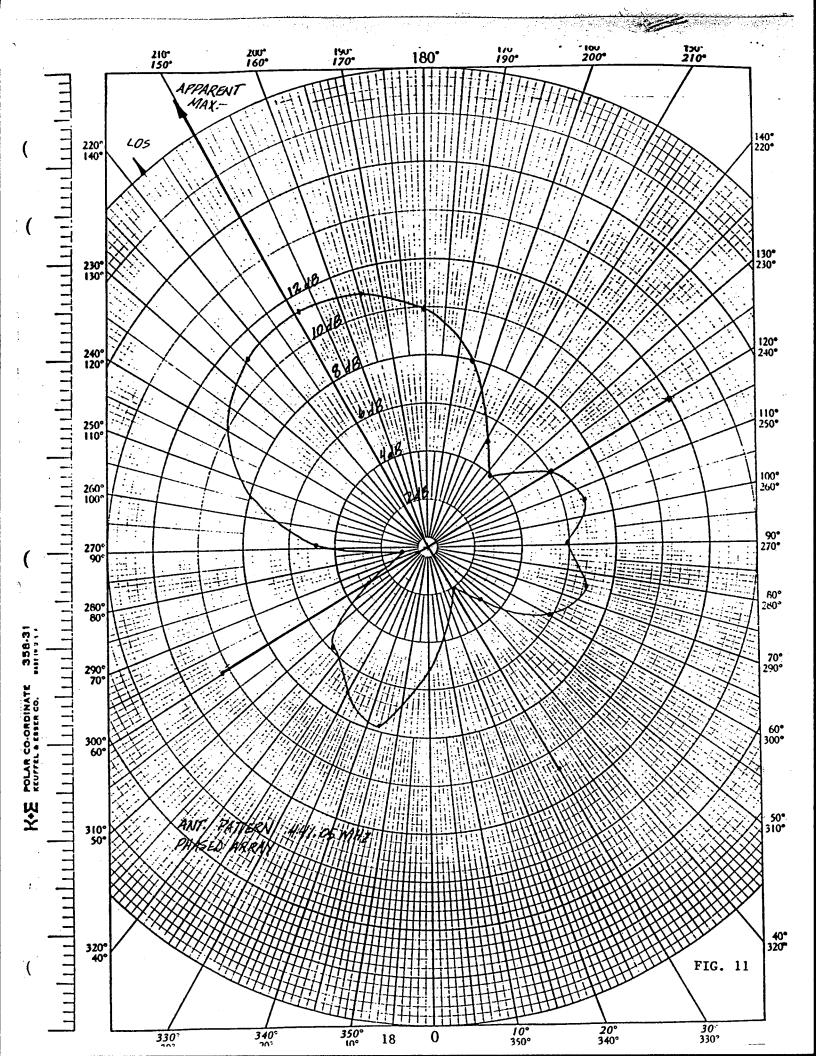

| FIGURE 12 | Radiation Pattern for Phased Array ("N")25       |

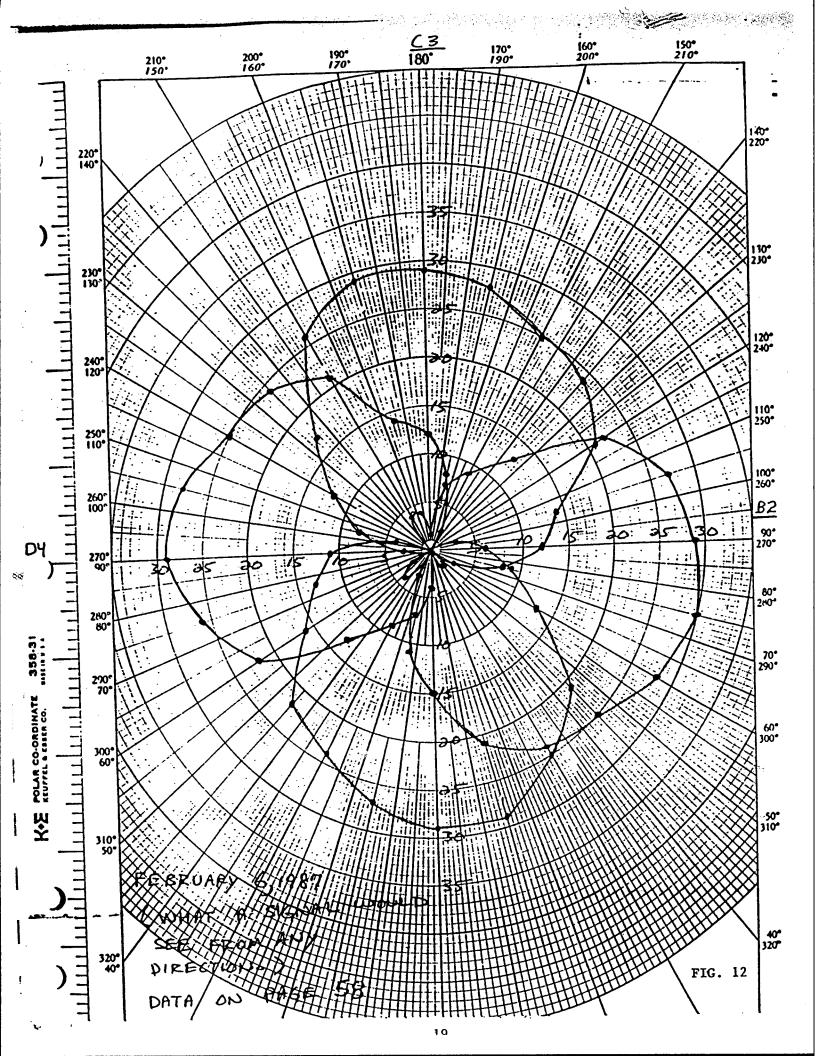

| FIGURE 13 | Radiation Pattern for Phased Array ("NE")25      |

| FIGURE 14 | Radiation Pattern for Phased Array ("E")25       |

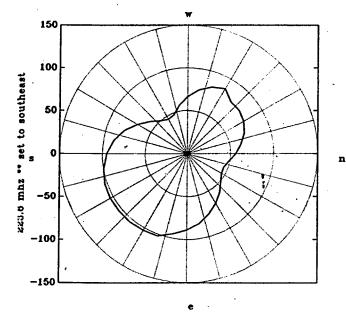

| FIGURE 15 | Radiation Pattern for Phased Array ("SE")25      |

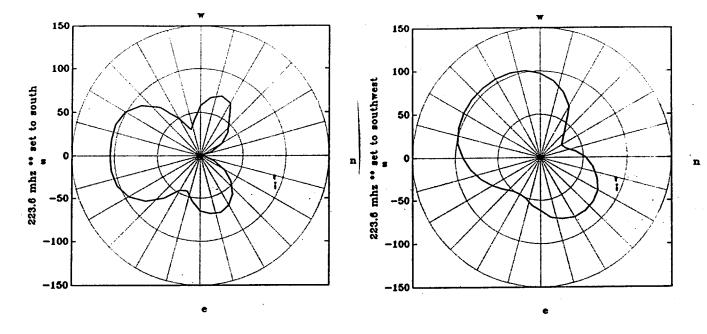

| FIGURE 16 | Radiation Pattern for Phased Array ("S")26       |

| FIGURE 17 | Radiation Pattern for Phased Array ("SW")26      |

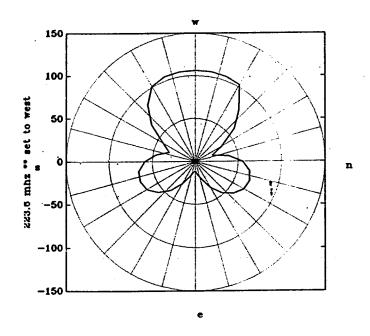

| FIGURE 18 | Radiation Pattern for Phased Array ("W")26       |

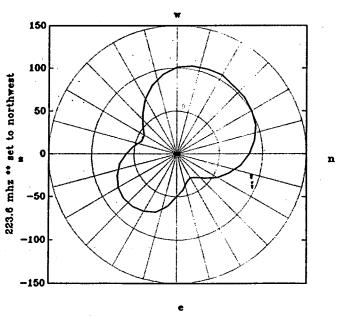

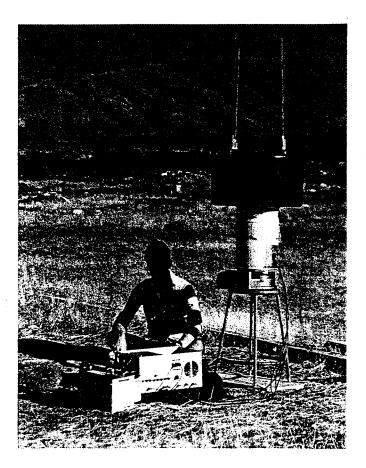

| FIGURE 19 | Radiation Pattern for Phased Array ("NW")26      |

| FIGURE 20 | Typical Radiation Pattern from Helical Antenna30 |

| FIGURE 21 | Radiation Pattern, 2.2 GHz, Top Helical          |

| FIGURE 22 | Radiation Pattern, 2.2 GHz, Bottom Helical31     |

| FIGURE 23 | Radiation Pattern, 1.71 GHz, Top Helical31       |

| FIGURE 24 | Radiation Pattern, 1.71 GHz, Bottom Helical32    |

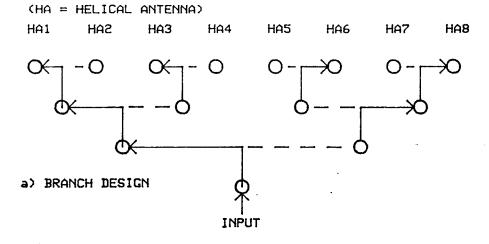

| FIGURE 25 | Branched and Spoke Design of Microwave Switch34  |

| FIGURE 26 | Shunt Type Design of Microwave Switch            |

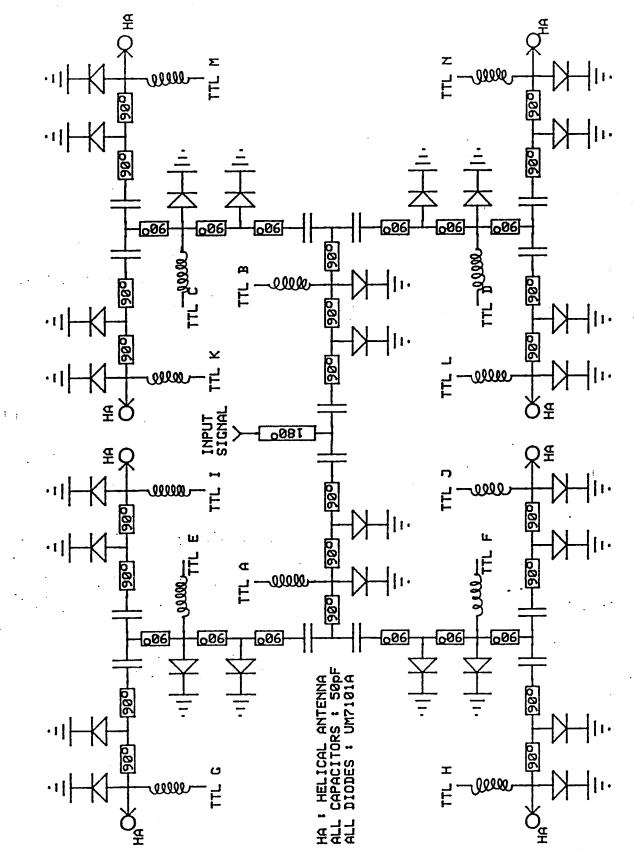

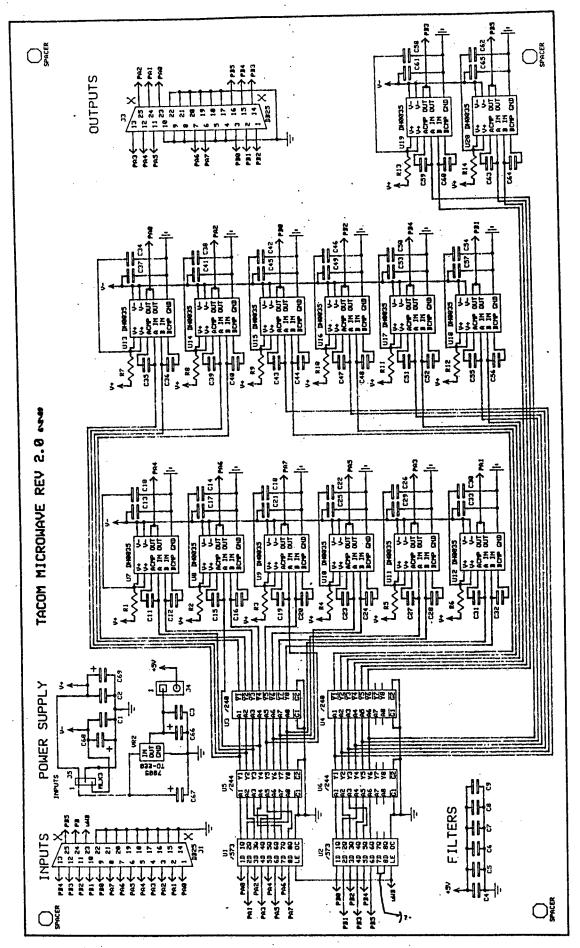

| FIGURE 27 | Schematic of Microwave Switch Board              |

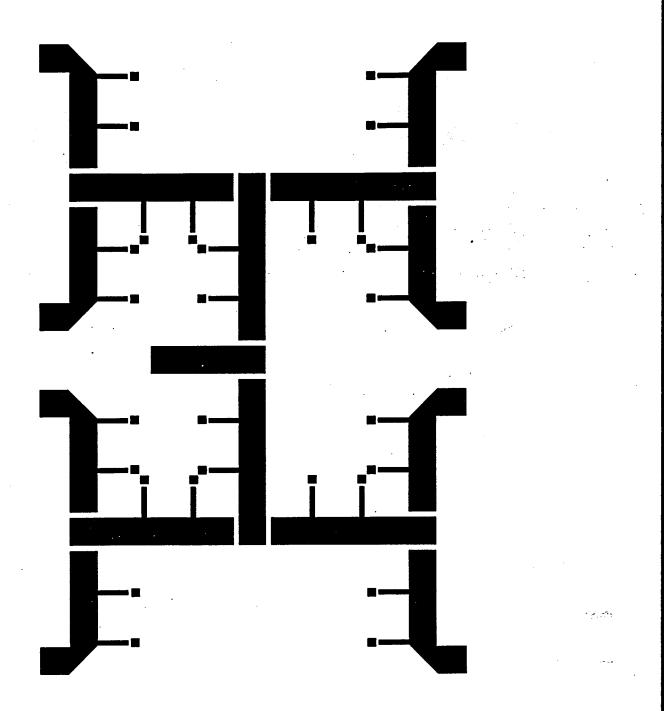

| FIGURE 28 | Artwork for Microwave Switch Board               |

| FIGURE 29 | Logic levels for microwave switch driver board39 |

| FIGURE 30 | Schematic of Microwave Switch Driver Board41     |

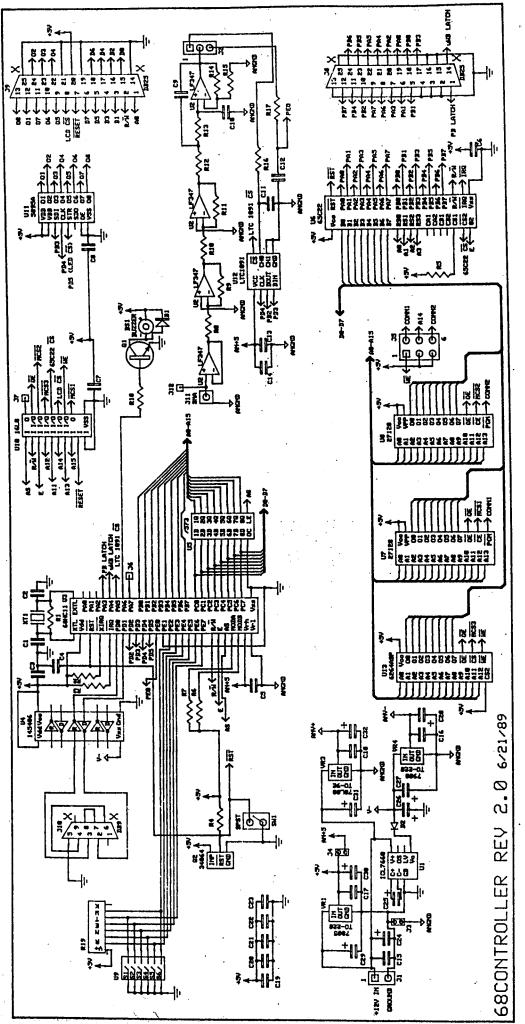

| FIGURE 31 | Schematic of Microcontroller Board45             |

| FIGURE 32 | Flow Chart of Main Program                       |

|           |                                                  |

# LIST OF PHOTOGRAPHS

| PHOTOGRAPH | 1  | Phasing Board20                 |

|------------|----|---------------------------------|

| PHOTOGRAPH | 2  | Phasing Board Driver            |

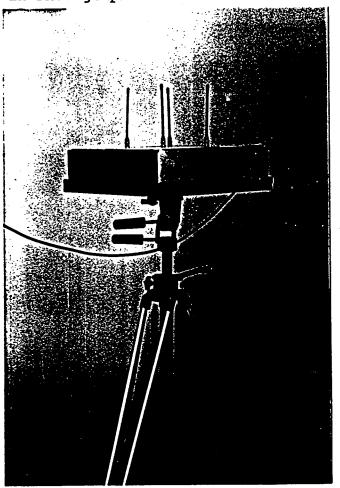

| PHOTOGRAPH | 3  | Whip Antennas24                 |

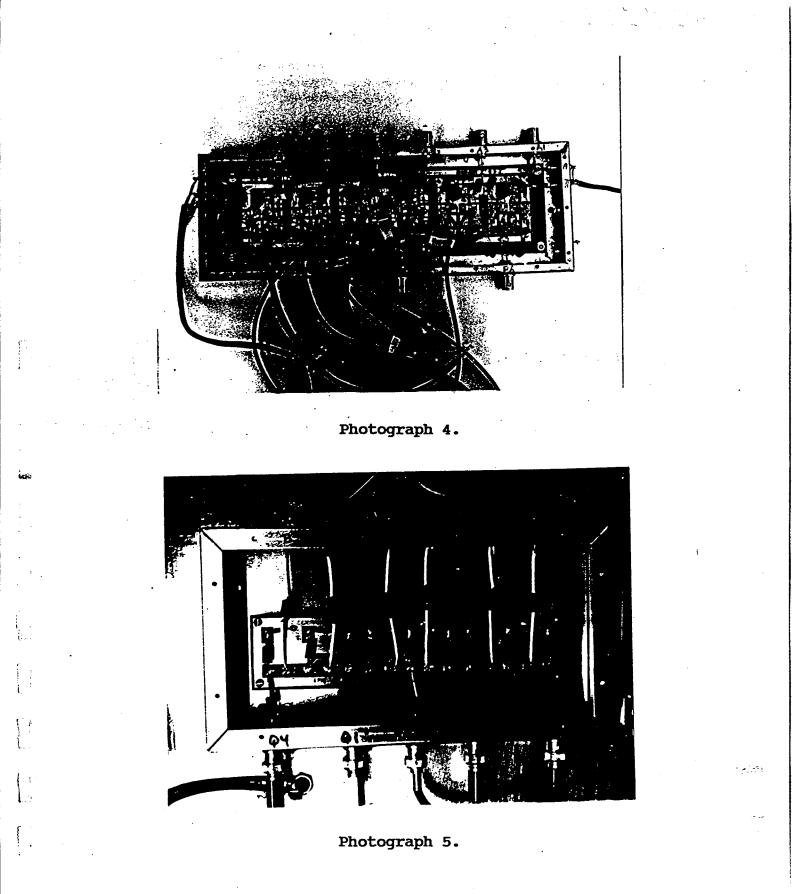

| PHOTOGRAPH | 4  | VHF Antenna Test Range          |

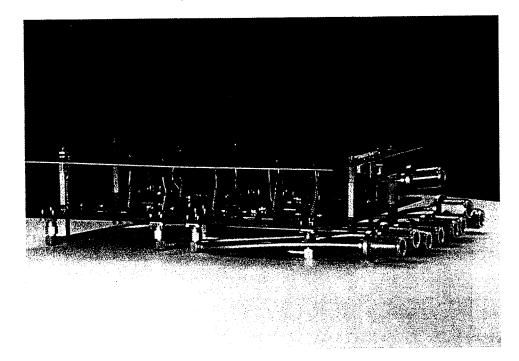

| PHOTOGRAPH | 5  | Helical Antennas                |

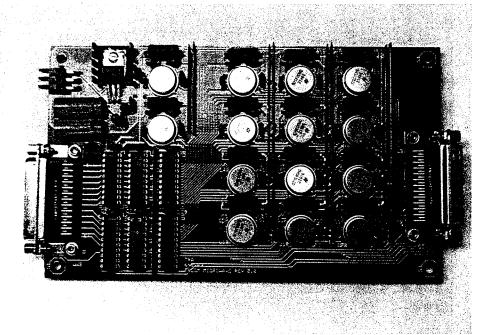

| PHOTOGRAPH | 6  | Microwave Switch Board          |

| PHOTOGRAPH | 7  | Microwave Switch Driver Board40 |

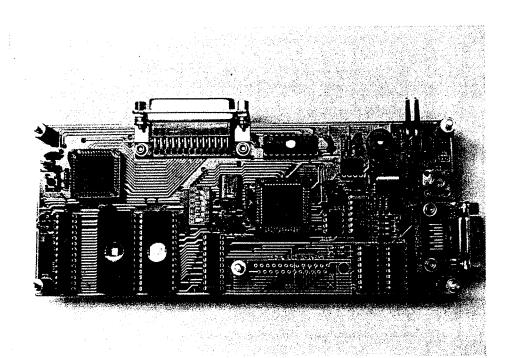

| PHOTOGRAPH | 8  | Microcontroller Board           |

| PHOTOGRAPH | 9  | Power Module                    |

| PHOTOGRAPH | 10 | Helical Antenna Support         |

| PHOTOGRAPH | 11 | Dome Enclosure                  |

| PHOTOGRAPH | 12 | 19" Rack Enclosure60            |

4

$\mathbf{X}$  .

i

## I. INTRODUCTION

## I.A. BACKGROUND

The Army Tank and Automotive Command (TACOM) is developing robot vehicles for reconnaissance into hazardous areas. The vehicle is controlled remotely by an operator who can see the terrain in which the vehicle is operating as well as hear engine noises to help in the control of the robot. The operating terrain is monitored by several video cameras, some of which are specialized. The video and other data are transmitted from the vehicle (RCV) to the base station (RCC) by four channels in the frequency band of 1700 to 2500 MHz. This link is called the microwave link. Data used to control the vehicle are transmitted from the base station (RCC) to the vehicle on a VHF link at 225 to 235 MHz.

Early AGVT robots used a mechanically pointed horn type microwave antenna to relay the video and other data to the base station. The antenna had to be pointed both in azimuth and elevation towards the base station. It used a signal from the RCC to track the base as the vehicle maneuvered. The mechanical system was cumbersome and had no potential to use reflected signal propagation if the line of sight path was lost. TRA proposed to TACOM that an electrically steerable agile beam antenna (ESABA) could be constructed that would have no movable mechanical parts and would have the potential for reflected signal linking. Further, since the antenna would be controlled electronically, tracking the base station would occur very fast, allowing for rapid vehicle turns and rapid signal reacquisition.

TRA was awarded a SBIR Phase I contract to prove the feasibility of the idea. The details of this work are included as Appendix Briefly, a four antenna azimuthal array operating at 440 MHz X.E. A dedicated computer controlled a PIN switch which was built. caused the array to electronically sweep in a circular azimuthal When a radio signal was heard, the computer would pattern. determine in which quadrant the signal was strongest and route Upon completion of the radio communication to that sector. communication, the scanning would resume until the next signal was The prototype antenna worked well and was tested in one of heard. The antenna could switch from a direct down the local canyons. canyon path to a stronger reflected signal if the direct path was weaker due to intervening obstructions. Because of the success of the Phase I feasibility study and hardware TRA was awarded a Phase II contract to develop two prototype ESABA antenna systems. This work started in late August 1987, was delayed for four months due to federal budget delays, and was completed at the end of October 1989 ahead of schedule considering the four month delay.

## I.B. PURPOSE OF ESABA AND ADVANTAGES

The purpose of the ESABA is to provide TACOM with a more effective steerable microwave antenna for the robot vehicle (RCV). The ESABA has several advantages:

1. The ESABA is a completely electronic antenna and has no moving parts to wear out, break, or jam.

2. The ESABA antenna system is designed to have an equal or better gain than the mechanical horn antenna that it replaces. Thus it will provide a better link margin.

3. If for some reason the base station (RCC) "beacon" signal is lost, for example the vehicle goes behind an obstruction, reacquisition of the video signals by the RCC will be much faster because the robot, with its rapid electronic scanning in azimuth, will be able to find the RCC in milliseconds.

4. The ESABA allows for the use of reflected signals as the communication link when the direct line of sight signal is lost as the RCV passes behind an obstruction, since the ESABA directs the microwave link at the strongest RCC signal.

# I.C. SYSTEM BLOCK DIAGRAM

.

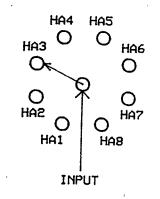

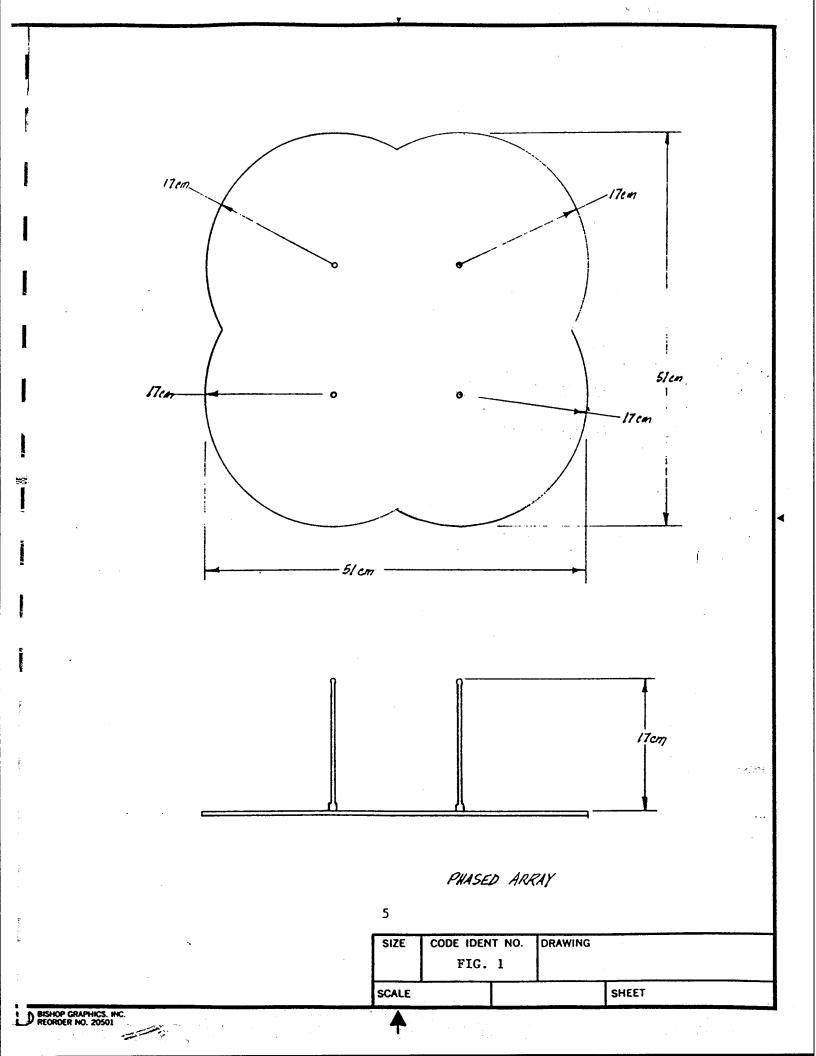

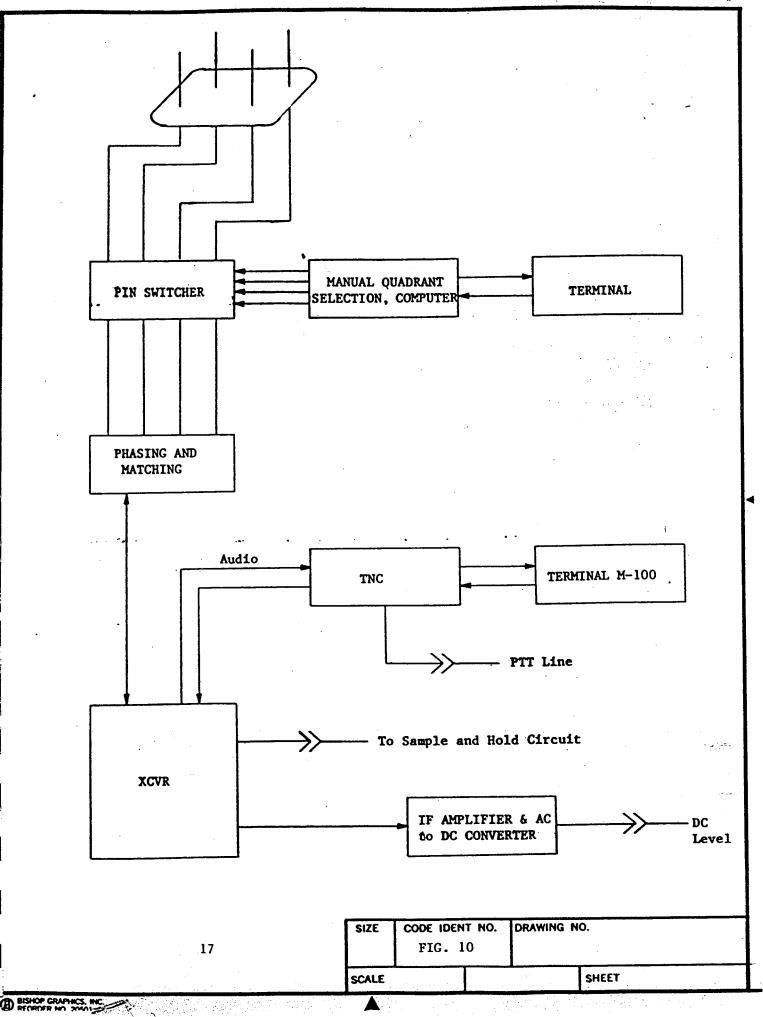

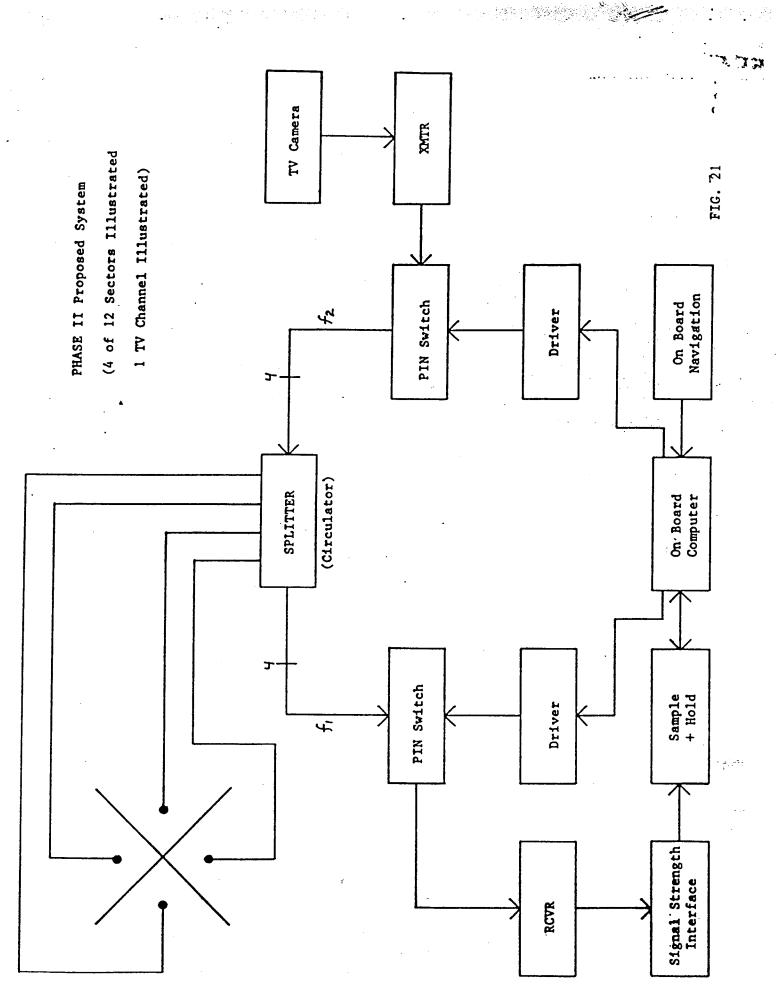

Figure 1 shows the ESABA system block diagram. Four end fed half wave length dipole whip type antennas form a phased array. This array of four antennas can be configured by switching and phasing into eight different directional antennas. Each of these antennas covers a separate 45 degree sector in azimuth. Only one of the eight antennas is active at any one time but all eight are formed at up to 2500 times per second, depending upon the signal strength response time (see Section V.B.1). This scanning allows the RCV ESABA computer to determine in which of the eight sectors the RCC is and thus in which sector to direct the video.

The switching and phasing board electronically creates the eight different VHF array antennas which are used in a direction finding mode. The switching and phasing board is controlled by the ESABA system computer. Received RF is passed through to the VHF ESABA dedicated receiver (IMSCO Model ADX-MR).

The VHF receiver listens to the RCV control signals sent by the RCC. Signal strength information is sent from the receiver to a signal strength converter on the CPU board.

The signal strength converter provides level shifting, gain adjustment and filtering. This processed signal is then converted into digital information by an A/D converter and accessed by the

## ESABA dedicated computer.

The ESABA computer controls the configuration of the eight VHF antennas and compares the strength of the received RCC signal in each of the eight sectors. This sector/signal strength information is used to control a single pole eight throw microwave PIN switch. The PIN switch thus routes the video data to one of eight helical microwave antennas that is pointing to the RCC at that moment.

## II. VHF LINK

# II.A. OVERVIEW

# II.A.1. PURPOSE OF VHF LINK

The purpose of the VHF link is allow the ESABA system to find the direction of the RCC from the RCV. Since the RCV is continually moving through the terrain this information is constantly changing especially during RCV turns.

## II.A.2. THEORY OF THE PHASED ARRAY

A single vertical antenna radiates a radio wave equally well in all azimuthal directions. Two vertical antennas can be spaced at various distances and fed in various phase relationships to produce azimuthal radiation patterns that vary in strength. In Figure 2a we see that if two antennas are located in the same place (0 degrees separation) and fed in phase their radiated waves superpose and produce a wave that has twice the amplitude of either single wave.

Figure 2b shows the case of separating the two antennas by 1/4 wavelength (90 degrees of phase) and feeding them in phase. In the direction of interest one gets a signal that is somewhat greater in amplitude than the individual signals due to superposition. This superposed signal is lower in amplitude than the superposed signal shown in Figure 2a.

Figure 2c shows antennas A1 and A2 separated by 1/4 wavelength but this time fed minus 90 degrees out of phase. Note that the individual waves superpose to provide twice the signal in the direction of interest.

In Figure 2d the antennas are still separated by 1/4 wavelength but we have reversed the phase of the feeding signals to plus 90 degrees. Note that the superposed signals completely cancel. Here one is "looking" at the same array as in 2c but from the back of the array where the array is fed as in 2c,that is antenna 1 is fed at 0 phase and antenna 2 is fed at minus 90 degrees phase.

# FIGURE 2C

FIGURE 2D

FIGURE 2 TWO ELEMENT RADIATION PATTERNS

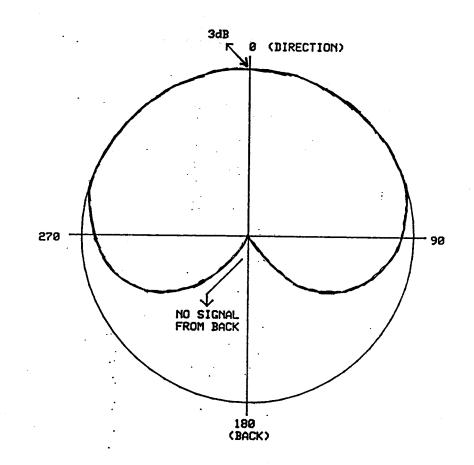

Figure 3 shows the azimuthal radiation pattern from the two antennas separated by 1/4 wavelength with A1 fed at 0 degrees phase and A2 fed at minus 90 degrees. A strong 2X (3 dB) signal is radiated in the 0 degree direction and no signal is radiated in the back, 180 degree direction. A similar but even stronger forward radiation pattern can be formed by spacing three antennas in a straight line each spaced at 1/4 wavelength and fed at 0 degrees, -90 degrees and -180 degrees.

FIGURE 3 AZIMUTHAL PATTERN FROM TWO ANTENNAS

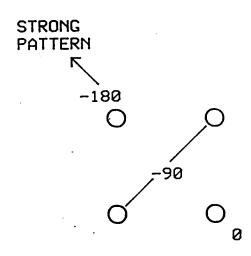

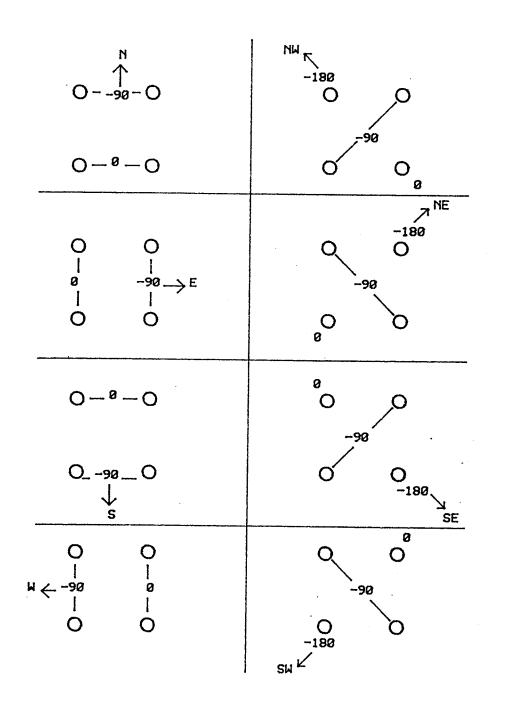

Figure 4 shows how directional (gain) antenna arrays can be formed from four single antennas spaced on the corners of a 1/4 wavelength square. In Figure 4a two opposite antennas are fed at -90 and the other opposite antennas at 0 and -180 degrees respectively. This produces strong radiation in the 315 (NNW) direction. Figure 4b shows two adjacent antennas fed at 0 degrees and the other two adjacent antennas fed at -90 degrees. Now a strong pattern is generated in the 0 degree (N) direction and no signal is radiated off the back of the antenna array.

STRONG PATTERN

FIGURE 4A

FIGURE 4B

# FIGURE 4

# DIAGONAL AND BROADSIDE RADIATION PATTERNS

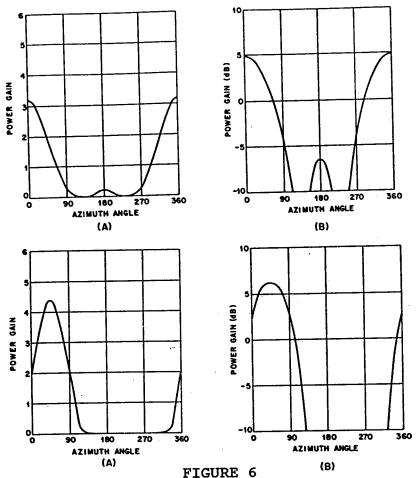

Figure 5 shows how eight different directional patterns can be formed by four antennas spaced 1/4 wavelength and fed with different phasing. This is basically how TRA can sample radio signals from eight sectors of azimuth. Because the antennas that comprise the array interact the radiation patterns actually obtained differ slightly from those computer generated. Figure 6 shows computer generated radiation patterns for the 0,-90 and 0,-90,-180 fed four square arrays.

FIGURE 5 DIRECTIONAL PATTERNS FROM FOUR ELEMENT ARRAY

e. - - - -

· · · · ·

COMPUTER GENERATED DIRECTIONAL PATTERNS

II.B. PHASING BOARD (PB)

II.B.1. REQUIREMENTS AND THEORY OF THE PHASING BOARD

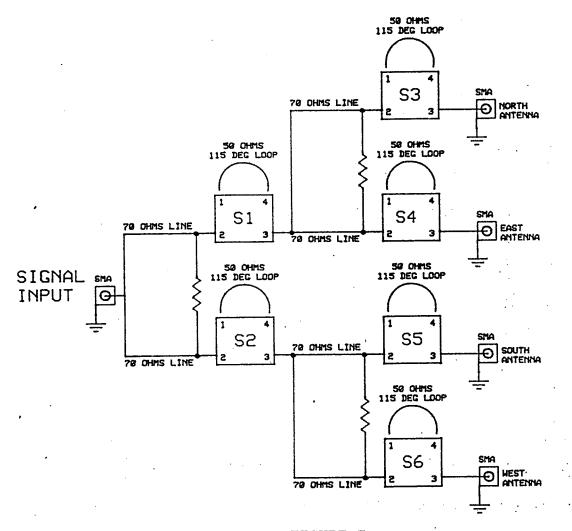

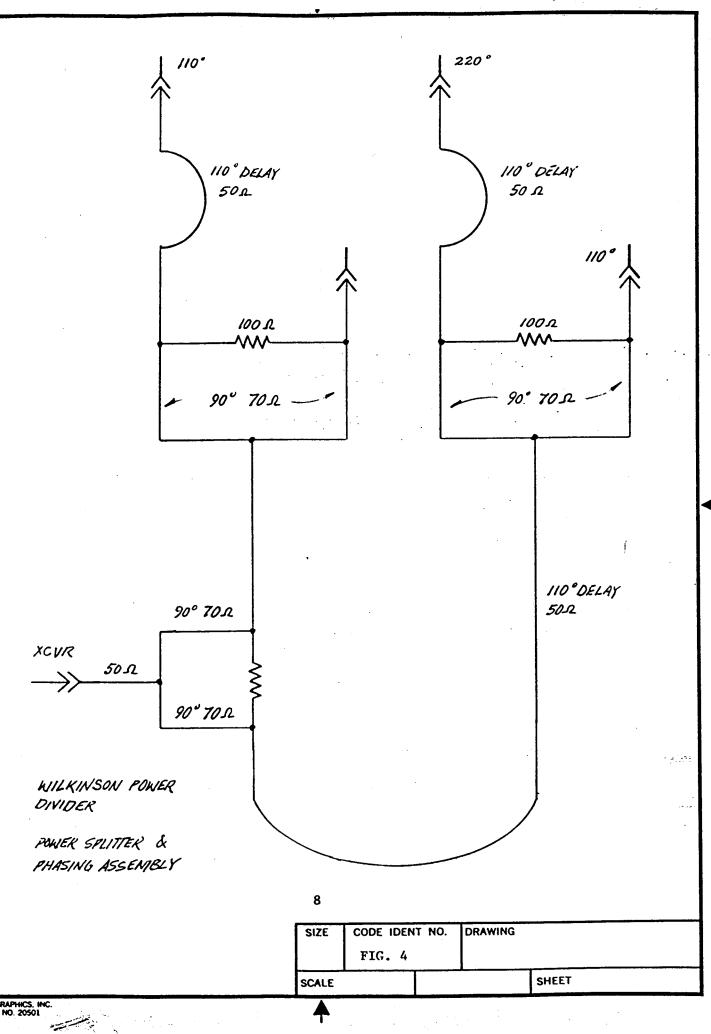

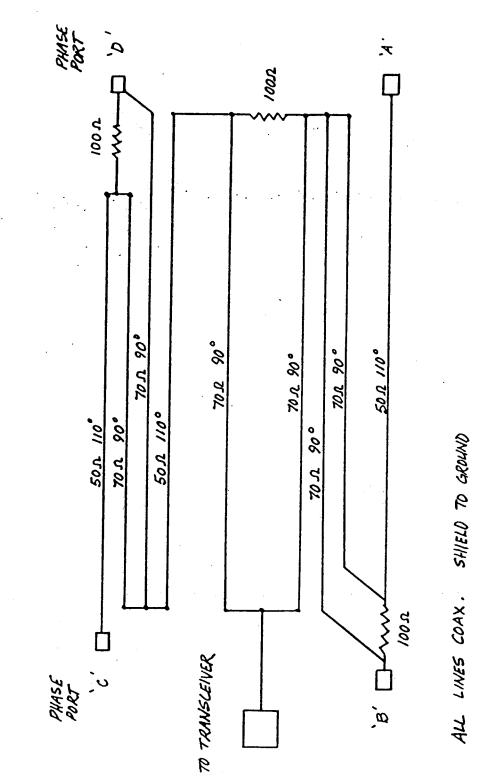

The phasing and switching board, as its name suggests, fulfills multiple functions. The board switches the individual antennas, changes the phase to the array, provides proper impedance matching and divides the RF power equally among the antennas comprising the array. Figure 7 shows the block diagram for the PB. Starting at the receiver, the signal is split by a Wilkinson power divider. The two 70 ohm 1/4 wavelength cables provide impedance matching and the 100 ohm resistor absorbs any reflected power from antenna mismatch.

Next are two switches S1 and S2 that provide either straight through routing of RF or routing through a quarter wave section of 50 ohm transmission line. The quarter wave section provides 90 degrees of phase shift as needed. The straight through configuration introduces no phase shift. The output of the switches S1 and S2 is further split, impedance matched by additional Wilkinson power dividers and fed to switches S3,S4,S5 and S6. Again these switches can introduce no phase shift or 90 degrees of shift.

FIGURE 7 BLOCK DIAGRAM OF PHASING BOARD

As an example let us program the system to provide the pattern shown in Figure 5 (SE). Antenna A1 (N) needs 0 shift so both S1 and S3 route straight through . Antenna A2 (E) needs -90 degrees so S4 routes through the additional quarter wave 50 ohm line. Antenna A3 (S) needs -180 degrees of shift so both S2 and S5 route through the quarter wave sections. Antenna A4 (W) needs only -90 degrees, obtained by the S2 routing with S6 straight through. By selecting the correct combination of routing all the eight configurations of Figure 5 can be obtained. Figure 8 illustrates the construction of the electronic routing switches. Mechanical relays could have been used but could not operate at the speed needed and would arc and wear quickly. The straight through and -90 degree delay configurations are shown in Figure 8a. The actual schematic is shown below in Figure 8b.

### Figure 8a

000000

- 65-

### Figure 8b

# FIGURE 8 A PIN SWITCH IN THE PHASING BOARD

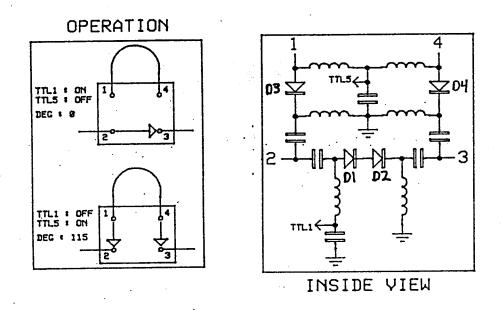

In the straight through mode, PIN (P doped, Intrinsic, N doped) diodes are biased on by TTL1 set positive. The DC blocking capacitors pass RF while the RF blocking inductors pass the DC. Thus RF passes from port 2 to port 3. At the same time diodes D3 and D4 are reversed biased (negative at TTL5) to block the RF from ports 1 and 4 and thus preventing the RF from passing through the quarter wave shifter.

To route the RF through the section of quarter wave transmission line D1 and D2 are reversed biased (TTL1 negative)thus blocking the RF from passing from port 2 to port 3. Diodes D3 and D4 are forward biased (TTL5 positive) allowing the RF to traverse the quarter wave section. While only one diode is needed at D1/D2, two are used to preserve the phase symmetry of the switch since two diodes are needed at D3/D4. Figure 9 presents the TTL signals needed to form the various antenna arrays.

| PHASING BOARD                  | DRTVI  | ER PAT     | TERN      | CODES   | 5 FOR      | EACH       | DIREC | TION      |

|--------------------------------|--------|------------|-----------|---------|------------|------------|-------|-----------|

| FIRSTING DOMID                 | D1     | D2         | D3        | D4      | D5         | D6         | D7    | D8        |

| S1 : PA0                       |        |            |           | +       | +          | +          | +     | +         |

| S1 : PA1                       | +      | +          | +         | -       | -          | -          | -     | -         |

| S2 : PA2                       | +      | +          | +         | +       | -          | -          | -     | +         |

| S2 : PA3                       | -      |            | -         | -       | +          | +          | +     | . —       |

| S3 : PA4                       | -      | ÷          | +         | +       | +          | +          | -     | -         |

| S3 : PA5                       | +      |            | -         | -       | -          | -          | +     | +         |

| S4 : PA6                       | +      | +          | <b></b> . | <b></b> | <b>-</b> ' | +          | +     | +         |

| <b>S4</b> : <b>PA7</b>         | -      | -          | +         | +       | +          | -          | -     | -         |

| S5 : PB0                       | +      | +          | -         | -       | -          | +          | +     | +         |

| S5 : PB1                       | -      | -          | +         | +       | ++         | +          |       | _         |

| S6 : PB2 $\overline{36}$ , PB2 | -<br>+ | +          | т<br>     | т<br>-  | -          | -          | +     | +         |

| S6 : PB3                       | т<br>  |            |           |         |            |            |       |           |

| PORT A CODE                    | 99     | A9         | 69        | 6A      | 66         | <u>A6</u>  | 96    | <u>9A</u> |

| 65C22<br>PORT B CODE           | 06     | <u>0</u> A | 09        | 09      | 09         | <u>0</u> A | 06    | 06        |

# FIGURE 9 LOGIC LEVELS TO DRIVE PHASING BOARD

# II.B.2. MEASURED VALUES FOR THE PHASING BOARD

MEASURED PHASE SHIFTS THROUGH THE PHASING BOARD : Figure 10 shows the phase shift through the board for different configurations of the switch. Note that TRA designed the phase shift to be 0, -110 and -220 degrees rather than the 0,-90 and -180 as discussed earlier. This difference compensated for the interaction of the antennas as mentioned earlier. The figure shows that the worst case phase errors are less than 10 degrees.

16

# CABLE #1

|    | N    | Е    | S    | W    |

|----|------|------|------|------|

| N  | -219 | -114 | -2   | -109 |

| NE | -106 | -110 | 1    | 2    |

| E  | -110 | -222 | -108 | -1   |

| SE | -4   | -111 | -111 | -6   |

| S  | 0    | -108 | -220 | -113 |

| SW | 4    | 2    | -110 | -110 |

| W  | -106 | -2   | -112 | -221 |

| NW | -110 | -7   | -7   | -111 |

|    |      |      |      |      |

ς.

----

. . . .

# CABLE #2

|    | N    | Е    | S    | W    |

|----|------|------|------|------|

| N  | -220 | -115 | -5   | -110 |

| NE | -107 | -110 | 0    | 0    |

| E  | -110 | -222 | -110 | -4   |

| SE | -5   | -112 | -113 | -8   |

| S  | -1   | -109 | -221 | -114 |

| SW | 3    | 1    | -110 | -110 |

| w  | -107 | -4   | -114 | -223 |

| NW | -110 | -8   | -8   | -113 |

|    |      |      |      |      |

# FIGURE 10a MEASURED PHASED SHIFTS THROUGH PHASING BOARD

| N        | -219 | -113 | -3   | -109 |

|----------|------|------|------|------|

| NE       | -106 | -110 | 1    | 2    |

| Е<br>Е   | -110 | -221 |      | -2   |

| SE       | -4   | -111 | -111 | -7   |

| S        | 0    | -108 | -220 | -114 |

| SW       | 4    | 2    | -110 | -110 |

| W        |      | -3   | -112 | -222 |

| NW       |      |      | -7   | -112 |

|          |      |      |      |      |

|          |      |      |      |      |

| CABLE #4 | N    | E    | S    | W    |

| N        | -219 | -115 | -4   | -110 |

|          |      |      |      |      |

-110

-221

-111

-108

-----

1

-4

-8

----

S

W

1

-4

-8

-115 \_\_\_\_

-111

\_ \_ \_ \_

-221

\_ \_\_ \_\_ .

-113

CABLE #3

NE

\_ \_ Ε

----

SE

\_\_\_

S

--

SW

W

NW

N

-108

-111

-5

-2

----

\_\_\_\_

-107

-110

3

----

Έ

۸.,

| FIGURE 10b |        |        |         |         |       |  |

|------------|--------|--------|---------|---------|-------|--|

| MEASURED   | PHASED | SHIFTS | THROUGH | PHASING | BOARD |  |

0

-108

-112

-220

-112

-114

-9

\_ \_ \_

\_ \_ \_

The measured VSWR, S<sub>21</sub>, and isolation for prototype #1 is shown below. Measured values for both prototypes are included with the Operations Manual shipped with each prototype.

| VSWR | PROTOTYPE | <b>#</b> 1 |

|------|-----------|------------|

|      | PROTOTICE | π.         |

| <u> </u> | <u> </u>   |       |

|----------|------------|-------|

|          |            |       |

| ANT      | 1          | 2.8:1 |

| ANT      | 2          | 3.0:1 |

| ANT      | 3          | 2.3:1 |

| ANT      | 4          | 2.2:1 |

| ANT      | 5          | 2.8:1 |

| ANT      | 6          | 2.5:1 |

| ANT      | <b>7</b> . | 2.9:1 |

| ANT      | 8          | 2.5:1 |

|          |            |       |

<u>s</u>21

PROTOTYPE #1

| ANT | 1 | -2.8 |

|-----|---|------|

| ANT | 2 | -3.6 |

| ANT | 3 | -1.6 |

| ANT | 4 | -1.8 |

| ANT | 5 | -2.6 |

| ANT | 6 | -2.2 |

| ANT | 7 | -3.2 |

| ANT | 8 | -2.9 |

|     |   |      |

ي و ا

# **ISOLATION**

| <u>PROTOTYPE #1</u> |        |     |                    |    |

|---------------------|--------|-----|--------------------|----|

| BETWEEN             | LEGS 1 | AND | 216 0              | ЗB |

| BETWEEN             | 1 OR 2 | AND | ALL OTHER LEGS25 d | ЗB |

| BETWEEN             | LEGS 3 | AND | 416 0              | ЗB |

| BETWEEN             | 3 OR 4 | AND | ALL OTHER LEGS25 d | ЗB |

| BETWEEN             | LEGS 5 | AND | б14 с              | ЗB |

| BETWEEN             | 5 OR 6 | AND | ALL OTHER LEGS20 d | ЗB |

| BETWEEN             | LEGS 7 | AND | 815 d              | ЗB |

| BETWEEN             | 7 OR 8 | AND | ALL OTHER LEGS25 d | ЗB |

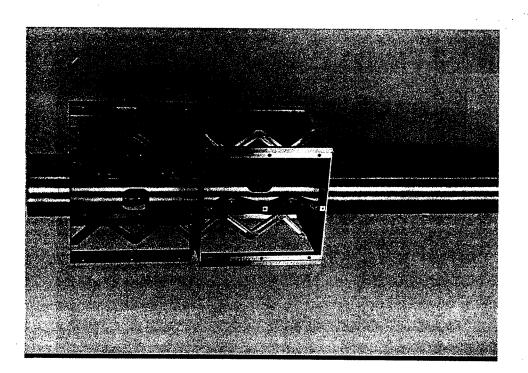

# II.B.3. PICTURE OF THE PHASING BOARD

The Phasing Board is shown in Photograph 1.

PHOTOGRAPH 1 PHASING BOARD

a -5-

II.C. PHASING BOARD DRIVER (PBD) II.C.1. REQUIREMENTS AND THEORY OF PHASING BOARD DRIVER

The phasing board driver circuitry was not designed for the same fast switching speed as the microwave switch driver. This was due to two reasons : (1) There is no reason for very fast switching times on the VHF signal as the maximum scan rate of the VHF antenna is set by the signal strength output of the radio and there is no signal "glitching" to consider as there is with the microwave signal, and (2) the LR time constant of the phasing board is the critical determinant of the VHF switching time.

The phasing board driver was, however, designed to provide twelve reasonably fast independent dual level outputs which can change state simultaneously. The first stage of the phasing board driver is two 74573 latches. In order to reconfigure the phasing board driver the microcontroller first performs two independent writes to two eight bit ports of the 65C22 PIO device. A separate PIO pin then transfers these two bytes simultaneously to the output of the 74573 latches. The latch outputs are routed to 75150 devices which convert the 0 or 5 volt outputs to +12 or -12 volts. The outputs of the 75150 devices are routed to a push - pull arrangement of RF NPN/PNP transistors which provide current gain. The output current passes through a current limiting resistor and leaves the board through a connector. The 68 ohm output resistors limit the current provided to the PIN diodes to the desired 100 mA.

## II.C.2. MEASURED VALUES FOR PHASING BOARD DRIVER

Measured output current : 103 mA

Measured switching time, no load Forward bias to backward bias : 40 ns Backward bias to forward bias : 40 ns

Measured switching time, phasing board as load Forward bias to backward bias : 215 microseconds Backward bias to forward bias : 47 microseconds

II.C.3. PICTURE AND SCHEMATICS OF PHASING BOARD DRIVER

The schematic of the phasing board driver circuitry is shown in Figure 11.

A photograph of the phasing board driver is shown in Photograph 2.

# PHOTOGRAPH 2 PHASING BOARD DRIVER

23

1 g. 274

I.D. WHIP ANTENNAS

TYPE

II.D.1. Larsen brand end fed half wave dipole antennas were selected for the 230 MHz phased array. The antennas consist of a half wave radiator and a discrete component matching The dipole antenna does not require a ground plane device. and the array is thus suitable for mounting atop the array with minimum effect on the radiation pattern of the helical array. Center fed dipole antennas would require a central supporting structure that would interfere with the phasing of the four radiators. Thus the best solution was obtained with the end fed dipoles.

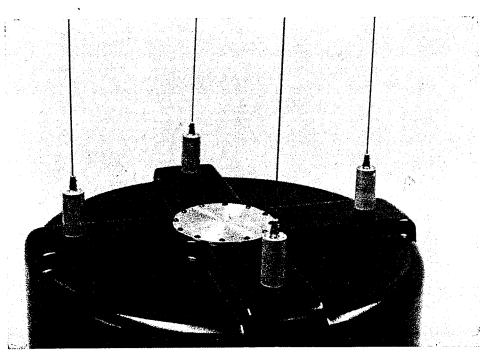

During vehicle motion there will be some swinging movement between the four whip antennas. Computer calculation reveals that the radiation pattern is relatively insensitive to such motion as long as the spacing stays within the limits of 0.167 to 0.33 wavelengths. Hence, a spacing of 0.25 wavelengths was chosen. The whip antennas are trimmed to the center frequency of 230 MHz but since the whips are replaceable any frequency in the 225-235 MHz band can be optimized. The whip antennas are affixed to the top of the helical antenna dome which is reinforced. Their cables are routed down through the central mast along with the cables for the microwave helical antennas.

#### PICTURE OF WHIP ANTENNAS 2.

PHOTOGRAPH 3 WHIP ANTENNAS

# II.E. VHF SYSTEM TEST

# II.E.1. VHF PHASED ARRAY ANTENNA PATTERNS

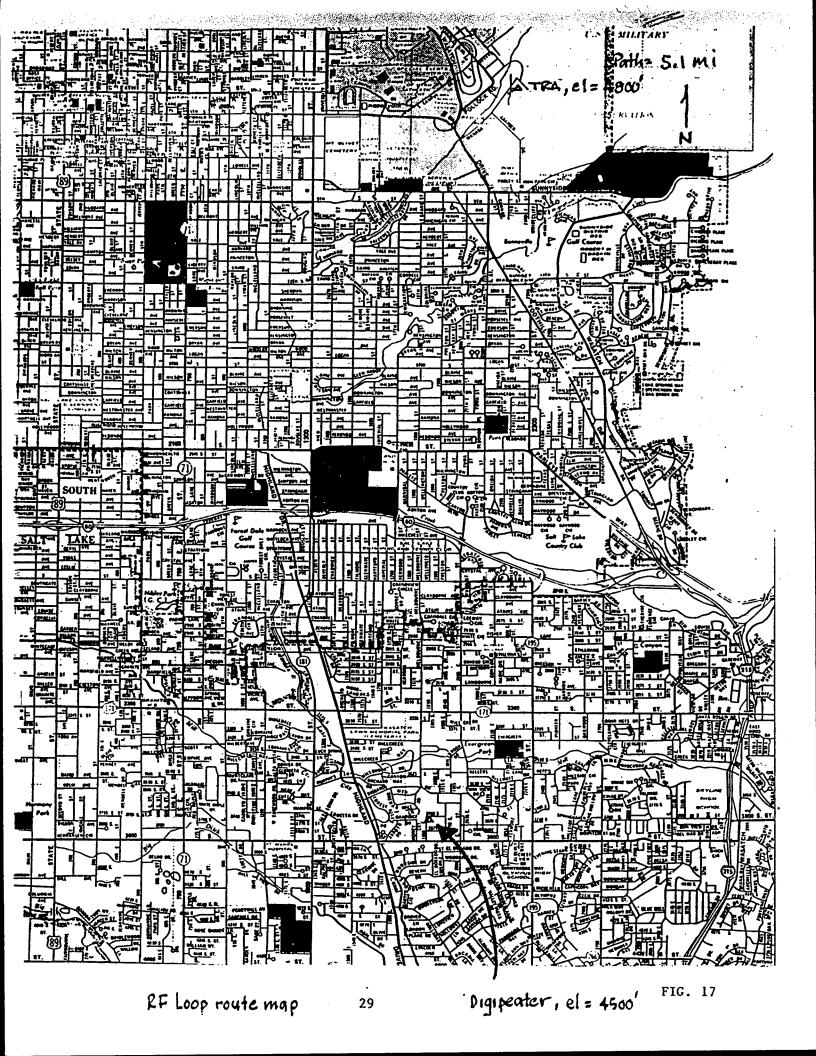

Figures 12 through 19 show the measured antenna radiation patterns produced by the phased antenna array. The patterns are quite uniform and more than adequate to provide the direction finding needed for the ESABA system.

FIGURE 13

\_\_\_\_

n

. n

e

25

-150

FIGURE 16

FIGURE 17

FIGURE 18

Ľ,

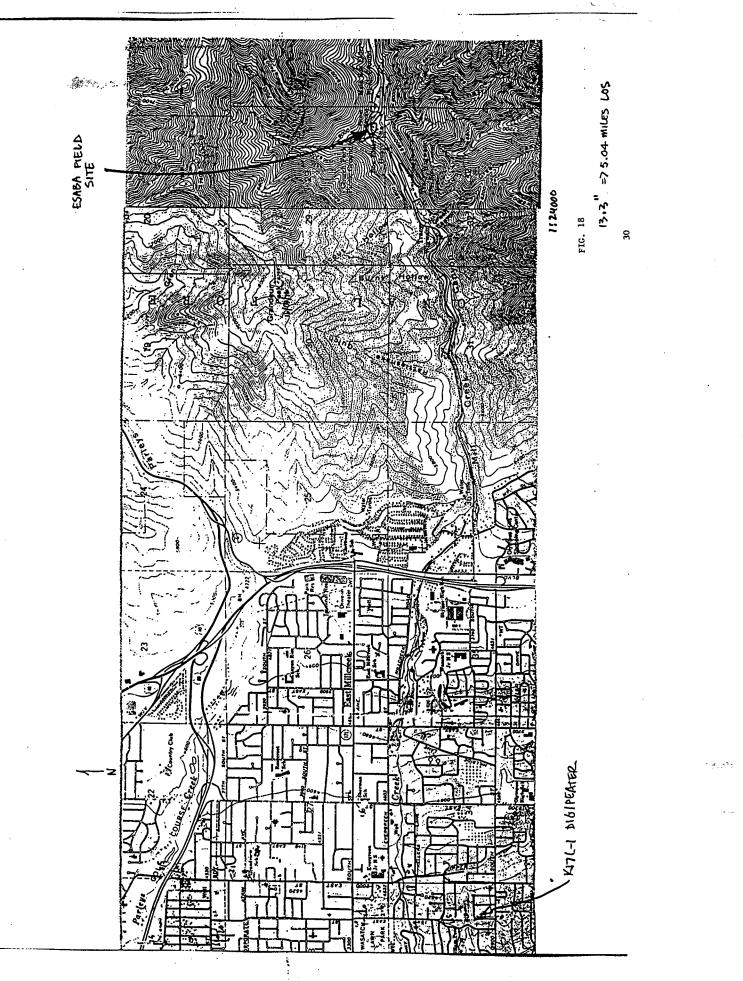

# II.E.2. PICTURES OF VHF ANTENNA TEST RANGE

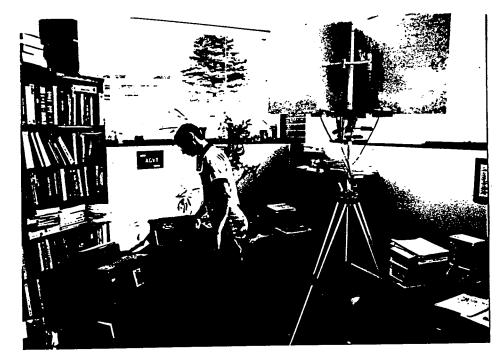

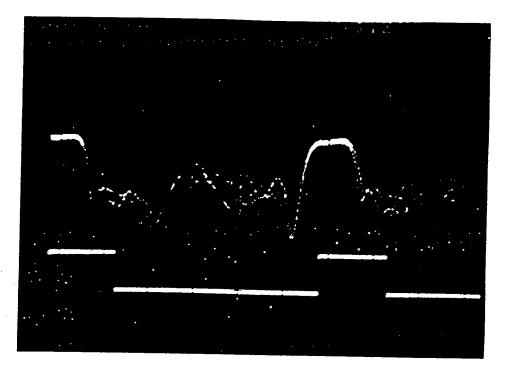

Photograph 4a shows the VHF antenna test range used by TRA. Figures 12 through 19 above were obtained in this location. Photograph 4a shows the range as seen from the transmitter. Photograph 4b was taken during final system test.

# PHOTOGRAPH 4a ANTENNA TEST RANGE

PHOTOGRAPH 4b VHF SYSTEM TEST

### III. MICROWAVE LINK

# III.A. OVERVIEW OF THE MICROWAVE LINK

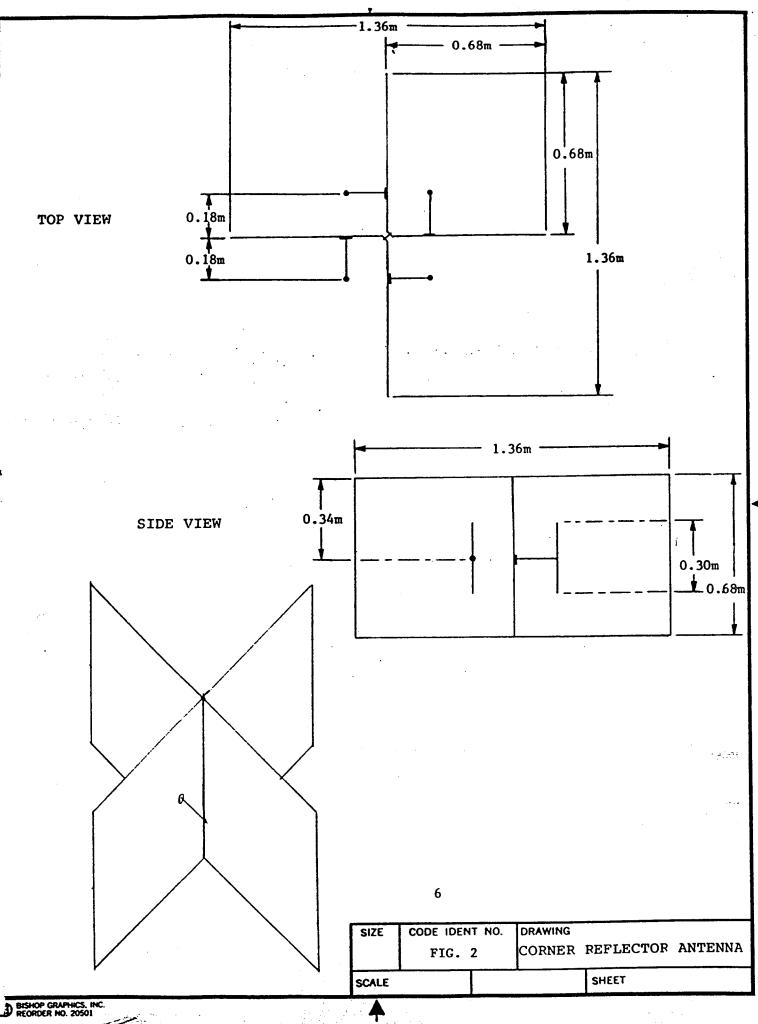

The microwave link in many respects was the most difficult component of the ESABA system. Firstly, the antenna system has to operate over a 40% bandwidth (1700-2500 MHz), which is very wide for any gain antenna system. Secondly, the microwave antennas had to provide circular polarization so as to minimize multipath flutter. Thirdly, since the phased array can only resolve eight sectors, the microwave antenna array must transmit in the same eight sectors, thus fixing the beamwidth. Fourthly, the PIN switch has to transition very rapidly so as to minimize video glitching during switching. Finally, the PIN switch has to carry up to 40 watts of RF power from the RCV's video transmitters. Single pole eight throw with this power handling capability are not commercially available.

TRA chose the axial mode monofilar helical antenna. This antenna was invented by John Kraus in 1946. It is a travelling wave type of antenna with wide band width and whose gain and beamwidth can be adjusted by altering the number of turns. Further, the antenna produces circular polarization. It is the only antenna that fits the requirements.

The microwave PIN switch requirements presented great difficulties. Although single pole multiple throw switches are available their power handling capability is of the order of one watt continuous. TACOM's requirement was for up to 40 watts. Additionally, switching has to occur very rapidly so as to minimize glitching of the video signal. If only a single video signal was being transmitted, switching could be done during flyback between frames. However, up to four independent video channels will be transmitted from the RCV.

## III.B. HELICAL ANTENNAS III.B.1. REQUIREMENTS AND THEORY

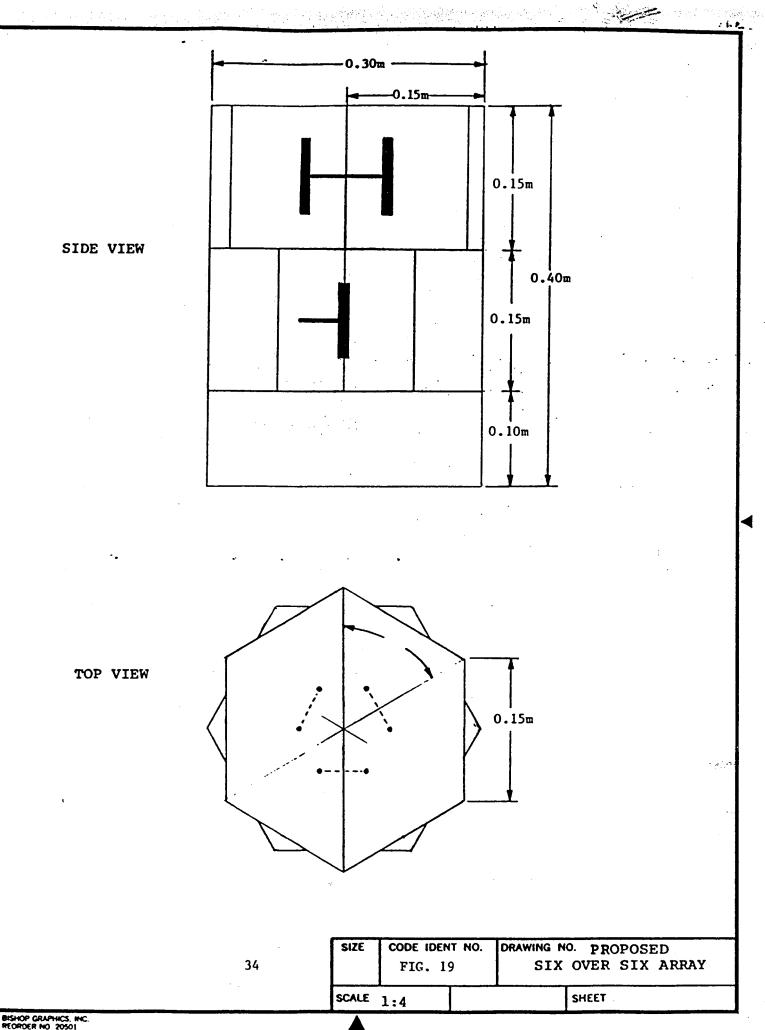

TRA chose the axial mode helical antenna because it 1. ideally suited the requirements of beamwidth, and bandwidth. A six turn helix of circumference equal to one wavelength has a half power beamwidth of 45 degrees, exactly that needed for transmitting into the eight sectors that the phased array can The axial ratio for this antenna is very close to resolve. 1 over the wide frequency range needed. This means that the circularity will remain good throughout the microwave band. The 6 turn helix has realistic gain of about 15 dBi. Since there is a 3 dB ripple in azimuth where the half power points overlap, the array should have at least 12 dBi gain at any point in azimuth. Further, the RCV will be able to pitch +/-22.5 degrees and still have 12 dBi on axis gain in elevation.

The eight individual helical antennas used in the array are stacked in a 4 over 4 configuration. This stacking is convenient and produces a compact structure. The mounting cube faces also function as a reflector for each helix. The upper and lower cubes are displaced 45 degrees from each other so as to provide eight sector coverage.

Note that the helical antennas generate right circular polarized waves. When such a wave is reflected from a conductive surface polarization is reversed. Thus a right circular polarized receive antenna will not respond to the reflected wave but only the direct wave. This prevents multipath flutter. The ESABA system has the potential for using reflected signal paths with the ability of the RCC to switch polarization of the receive antenna as follows.

Suppose the RCV is transmitting and drives behind an obstruction, losing direct line of sight contact with the RCC. If there is a reflective object, such as a rock face or building nearby, the RCV's phased array will find the reflected path is the strongest and will attempt to route the microwave signal via the reflector. Since the reflection changes polarization the RCC will not receive the microwave unless its receive antenna can change polarization. In future RCC receive antennas it would be desireable to build in this polarization switching capability as was apparently originally proposed.

# III.B.2. MEASURED VALUES OF HELICAL ANTENNAS

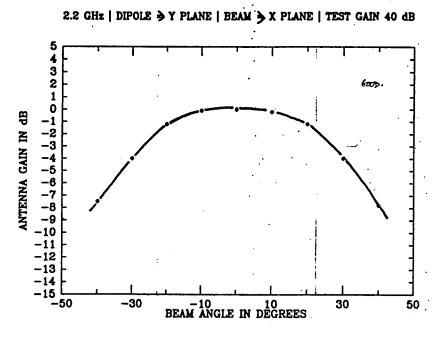

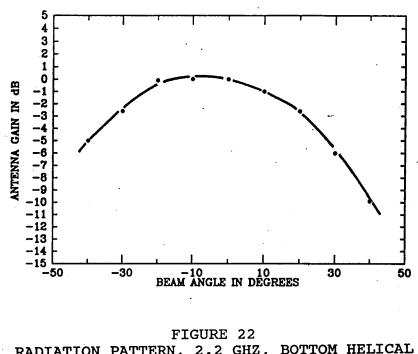

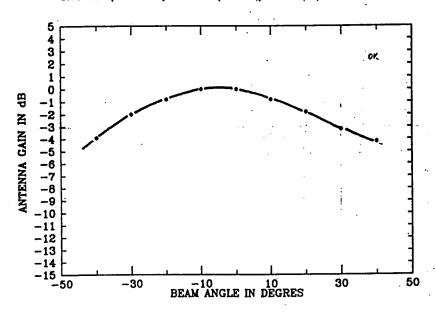

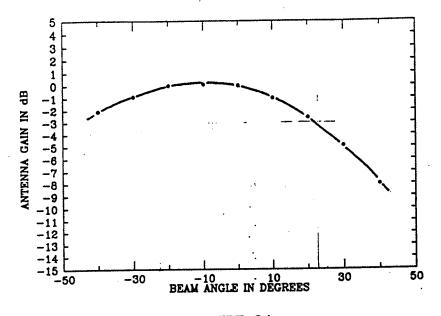

Figure 20 illustrates a typical radiation pattern for a unit helical antenna. The boresight axial ratio is 1.05 with some deterioration (to 1.26) at the half power points. The pattern is symmetrical about boresight. Figures 21 through 24 show that the antennas suffer little degradation of performance when stacked in the array. Figures 21 and 22 compare the radiation patterns of adjacent top and bottom antennas when in the array at 2.2 GHz. Note that the -3dB (half) power points exceed 45 degrees. Figures 23 and 24 show a similar result at 1.7 GHz. These measurements suggest that the stacking does not degrade individual performance.

FIGURE 20 TYPICAL RADIATION PATTERN FROM HELICAL ANTENNA

FIGURE 21 RADIATION PATTERN, 2.2 GHZ, TOP HELICAL

2.2 GHz | DIPOLE  $\Rightarrow$  y plane | beam  $\Rightarrow$  x plane | test gain 40 dB

RADIATION PATTERN, 2.2 GHZ, BOTTOM HELICAL

1.71 GHz | DIPOLE > X PLANE | BEAM > X PLANE | TEST GAIN 25 dB

- ----

FIGURE 23 RADIATION PATTERN, 1.71 GHZ, TOP HELICAL

1.71 GHz | DIPOLE  $\Rightarrow$  x plane | beam  $\Rightarrow$  x plane | test gain 26 dS

FIGURE 24 RADIATION PATTERN, 1.71 GHZ, BOTTOM HELICAL

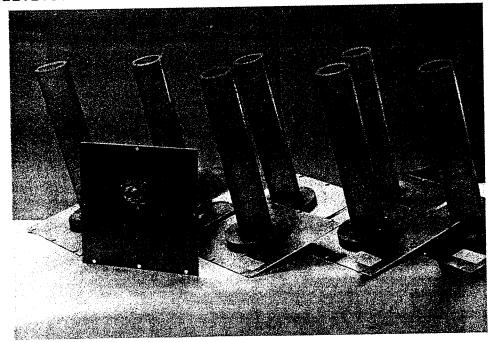

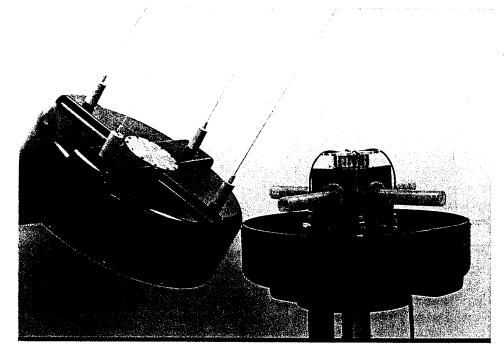

III.B.3. PICTURE OF HELICAL ANTENNAS

PHOTOGRAPH 5 HELICAL ANTENNAS

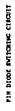

# III.C. MICROWAVE SWITCH BOARD (UWSB) III.C.1. REQUIREMENTS AND THEORY

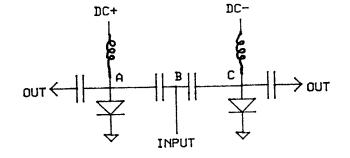

The microwave switch board needs to switch 40 watts of RF (frequency multiplexed from up to 4 transmitters) to one of the eight helical antennas depending on information from the phased array antenna. The switch is driven by the microwave driver board which in turn is controlled by the microcontroller. TRA chose to design a branched switch after it was determined from computer simulation that that design would be more efficient than spoke type design (see Figure 25). Simulation showed that the branched design was superior with respect to loss and isolation.

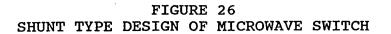

The power handling requirement precluded the use of the PIN diodes as direct switches as they were in the Phasing Board receive switch. TRA chose a shunt type switch whose operating principle can be seen in Figure 26. The switch is based on the fact that a quarter wavelength transmission line That is if one end of a quarter wave "inverts" impedance. line is shorted, the other end presents an open (high impedance) and vice versa. In Figure 26 PIN diodes at A and C are spaced one quarter wavelength from the switch input at If the diode at A is turned on it effectively shorts A to в. ground. A signal entering at B "sees" high impedance. The PIN diode.at C is reverse biased and creates an open at point C thus a signal at B "sees" a normal transmission line (50 ohms in our design) when looking at C. With high impedance one way and matched impedance the other way the signal is conducted towards C. The structure forms a single pole double throw switch.

This type of switch design has another advantage over the through diode switch. The diodes do not pass any RF so the power handling capacity of the switch is much greater. When diode A is conducting virtually no RF enters the leg from B. When diode at C is off no RF passes through it since the RF "prefers" the lower impedance transmission line path.

The switch that TRA designed actually has two quarter wave sections in series in each leg of the switch to increase the isolation. A novel approach was taken in mounting the diodes. Holes were drilled in the microstrip line at the quarter wave points and the diodes were mounted in these holes and grounded to the ground plane. This preserved the symmetry of the shunted transmission line and provided good heat sinking for the diodes. Because of the width of the microstrip transmission line, full width homemade DC blocking capacitors were fabricated to prevent impedance bumps. The Milar film was tested to 5000 volts.

34

FIGURE 25 BRANCHED AND SPOKE DESIGN OF MICROWAVE SWITCH

b) SPOKE DESIGN

$N_{\rm ell}$

III.C.2. MEASURED VALUES FOR THE MICROWAVE SWITCH BOARD

Exact measured values of VSWR, S<sub>21</sub>, and isolation for each prototype are included in the Operations Manual included with each prototype.

Typical VSWR values for the microwave switch board are 2.6:1 in the low band (1.71 - 1.8 GHz) and 1.8:1 in the high band (2.2 to 2.45 GHz). Typical S<sub>21</sub> values are -2.5 dB (-3.7 dB worst case) in both bands. Typical isolation is 20 to 25 dB, with 15 dB worst case.

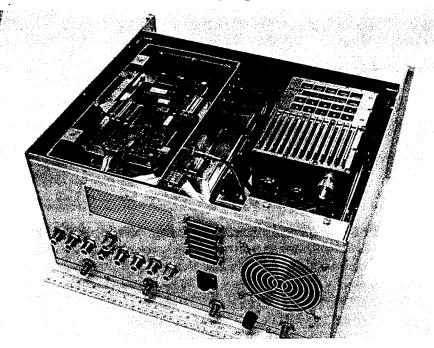

III.C.3. PICTURE AND SCHEMATICS OF MICROWAVE SWITCH BOARD

PHOTOGRAPH 6 MICROWAVE SWITCH BOARD

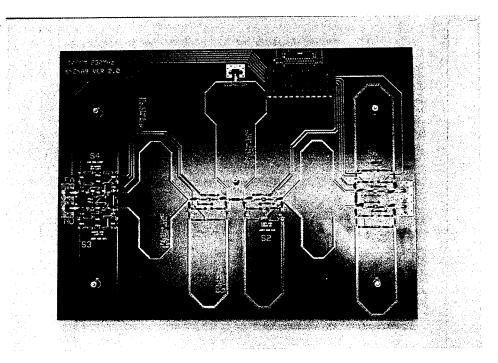

Schematic of Microwave Switch Board FIGURE 27 A copy of the layout artwork used in making the microwave switch board is shown below. This image was reduced 25% in order to fit on the page.

FIGURE 28 ARTWORK FOR MICROWAVE SWITCH BOARD

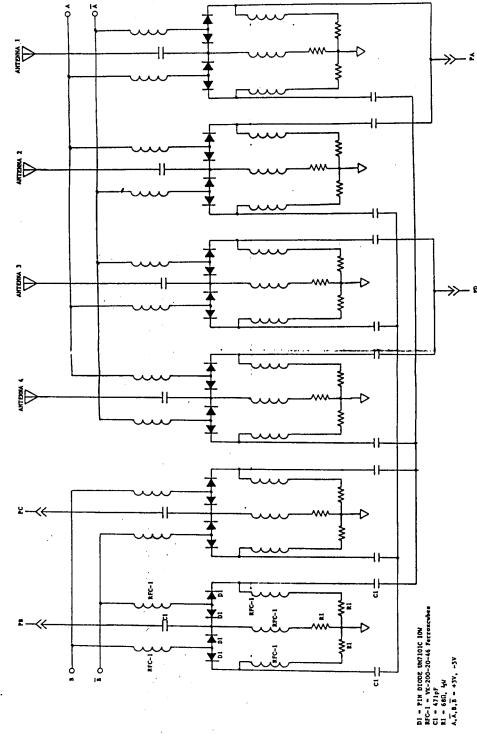

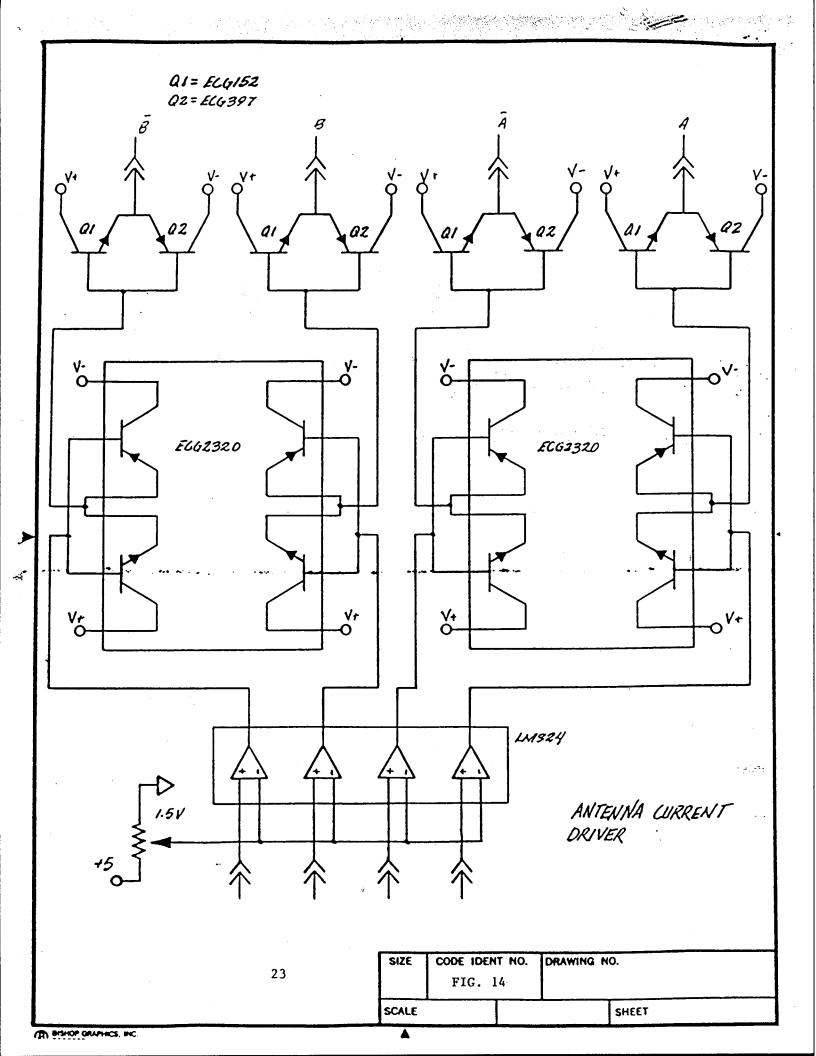

## III.D. MICROWAVE SWITCH DRIVER BOARD (uWSDB) III.D.1. REQUIREMENTS AND THEORY

The microwave switch driver board was designed to provide fourteen dual level outputs which can simultaneously switch the PIN diodes on the microwave switch board as fast as possible. Fast switching is needed to minimize "glitches" in the video signal when the ESABA system changes microwave antennas.

In order to turn a PIN diode "on" a charge  $Q = I_{DC} * \tau$  is applied to the diode, where  $I_{DC}$  is the steady state "on" current and  $\tau$  is the mean life time of the minority carriers. The amount of time needed to provide the charge Q can be shortened by applying a current spike,  $I_{pk}$ , for an optimum period given by  $t = \tau * I_{DC} / I_{pk}$  before reducing the current output to  $I_{DC}$ . If the current spike is maintained longer than this duration then an excess charge will be placed on the PIN diode and the turn off time of the diode will be lengthened since this excess charge has to be removed for turn off. Conversely, optimum turn off time will occur when a large peak current in the opposite direction of  $I_{pk}$  is achieved.

The National Semiconductor DH0035 PIN diode driver device is specially manufactured to provide the current levels and timing intervals needed for optimum PIN diode switching, and one of these devices has been incorporated into each channel of the microwave switch driver board.

As with the phasing board driver the microwave switch board driver was designed so that all fourteen of the PIN diode bias outputs switch simultaneously. In order to effect a change in the microwave switch driver board output configuration the ESABA microcontroller first does two separate writes to the 65C22 PIO. A separate PIO output then causes this configuration to latch across the two 74HC573 devices on the driver board simultaneously. The outputs of the 74HC573's are routed to 74240/74244 devices which provide the differential higher current outputs needed by the DH0035 devices, and the DH0035 devices then provide the current and timing relationships as discussed above.

The logic levels used by the microwave switch driver board are shown in Figure 28. Note that because of different construction methods the logic levels are different between the two prototypes. As documented in Section V.B.1, the software is alerted to this difference by the setting of DIP switch 2 on the CPU board.

| PROTOTYPE                               | #1    |            |       |                |       |       |      |           |

|-----------------------------------------|-------|------------|-------|----------------|-------|-------|------|-----------|

| MICROWAVE                               | BOARD | DRIVI      | ER PA | TTERN          | CODES | 5 FOR | EACH | DIRECTION |

|                                         | D1    | D2         | D3    | D4             | D5    | D6    | D7   | D8        |

| • • • • • • • • • • • • • • • • • • • • |       |            |       |                |       |       |      |           |

| A: PA4                                  | -     | -          | +     | +              | +     | +     | -    | -         |

| B : PA5                                 | +     | +          |       | -              | -     | -     | +    | +         |

| C : PB4                                 | +     | +          | -     | -              | +     | +     | +    | +         |

| D: PA6                                  | +     | + '        | +     | +              | -     | -     | +    | +         |

| E : PA1                                 | -     | -          | +     | +              | +     | +     | +    | +         |

| F: PB1                                  | ·+    | +          | +     | +              | +     | +     |      | -         |

| G: PA2                                  |       | +          | +     | +              | +     | +     | +    | +         |

| H : PB2                                 | +     | +          | +     | +              | +     | +     | -    | +         |

| I: PAO                                  | +     | · <u>-</u> | +     | +              | +     | +     | +    | +         |

| <b>J</b> : PB0                          | +     | +          | +     | +              | +     | +     | +    | -         |

| K : PB5                                 | +     | +          | -     | + 1            | +     | +     | +    | +         |

| L: PA7                                  | +     | +          | +     | +              | +     | -     | +    | +         |

| M : PB3                                 | + •   | .+ .       | +     | <del>.</del> . | -     | +     | +    | +         |

| N: PA3                                  | +     | +          | +     | +              | +     | +     | +    | +         |

|                                         |       |            |       |                |       |       |      |           |

| 65C22 POR                               | T     |            |       |                |       |       |      |           |

| A CODE                                  | 16    | 13         | 20    | 20             | 68    | EO    | 10   | 10        |

| 65C22 POR                               | T ·   |            |       |                |       |       |      |           |

| B CODE                                  | . 00  | 00         | 30    | 18             | 00    | 00    | 06   | 03        |

PROTOTYPE #2

MICROWAVE BOARD DRIVER PATTERN CODES FOR EACH DIRECTION D1 D2 D3 D4 D5 D6 D7 D8

i

|            |         |        | <u> </u> | <u> </u> | 04     | 0.0 |          | 21   |     |

|------------|---------|--------|----------|----------|--------|-----|----------|------|-----|

|            |         |        |          |          |        |     |          |      |     |

| A :        | PA4     | · •••  | -        | +        | +      | +   | +        | -    | -   |

| в:         |         | +      | +        | -        |        |     | -        | +    | +   |

| с:         |         | +      | +        | -        | -      | +   | +        | +    | +   |

| D :        | PA6     | +      | +        | +        | +      | -   | -        | +    | +   |

| Е:         | PA1     | -      | -        | ÷        | +      | +   | +        | +    | +   |

| <b>F</b> : | PB1     | +      | +        | +        | +      | +   | +        | -    |     |

| G:         |         | +      | -        | +        | +      | + - | +        | +    | +   |

| н:         | PB2     | +      | +        | +        | +      | +   | +        | -    | +   |

| I          | PAO     | -      | +        | +        | +      | +   | +        | +    | +   |

| J :        |         | +      | +        | +        | +      | +   | +        | +    | -   |

| к :        |         | +      | +        | -        | +      | +   | +        | +    | +   |

| L :        | PA7     | +      | +        | +        | +      | +   | -        | +    | +   |

| м :        | PB3     | +      | +        | +        | -      | -   | +        | +    | +   |

| N :        |         | +      | +        | +        | +      | +   | +        | +    | +   |

|            |         |        |          |          |        |     | <u> </u> |      |     |

|            | C22 POR |        |          | • •      | • •    | 60  | ΠO       | 10   | 10  |

|            | CODE    | 13     | 16       | 20       | 20     | 68  | <u> </u> | 10   | 10  |

|            | C22 POR | 27S    |          |          |        |     |          |      | • • |

| B          | CODE    | 00     | 00       | 30       | 18     | 00  | 00       | 06   | 03  |

| ("-        |         | a digi | tal O    | and      | "-" i: | sad | igita    | 1 1) |     |

#### FIGURE 29

LOGIC LEVELS FOR MICROWAVE SWITCH DRIVER BOARD

III.D.2. MEASURED VALUES FOR THE MICROWAVE SWITCH DRIVER BOARD

Measured output current : 200 mA

- Measured switching time, no load Forward bias to backward bias : 40 ns Backward bias to forward bias : 10 ns

- Measured switching time, microwave switch as load Forward bias to backward bias : 160 ns Backward bias to forward bias : 10 ns

The above measured values are typical. Exact parameters for each prototype are included in the Operation Manual shipped with each prototype.

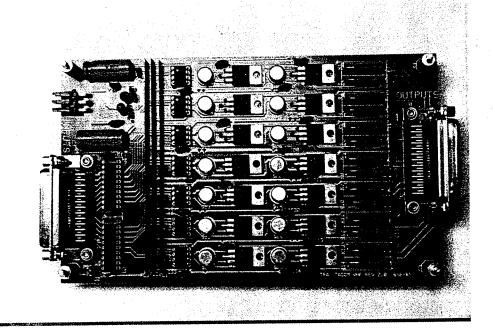

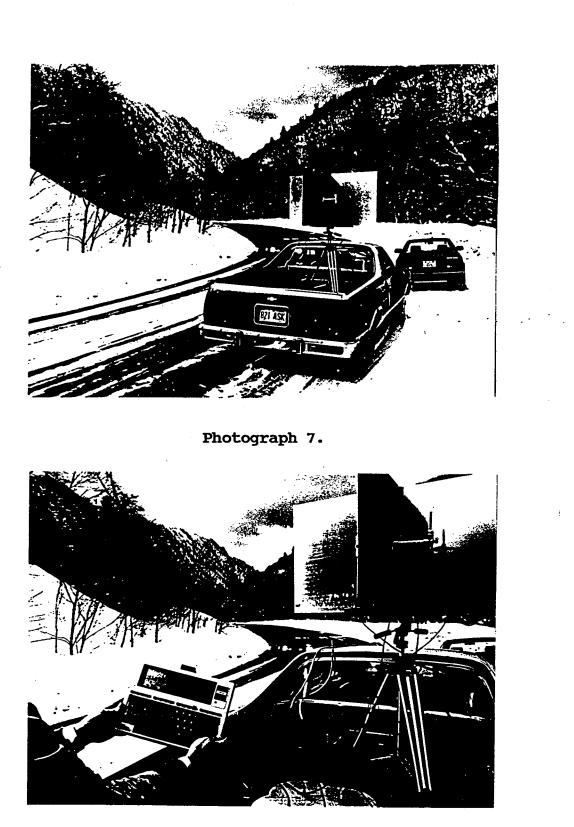

III.D.3. PICTURE AND SCHEMATICS FOR THE MICROWAVE SWITCH DRIVER BOARD

PHOTOGRAPH 7 MICROWAVE SWITCH DRIVER BOARD

a - 1976 -

## IV. MICROCONTROLLER AND RADIO

#### IV.A. OVERVIEW

The microcontroller board (uCB) controls and directs system operation. As shown in the system block diagram of Section I.C., the uCB controls both the microwave switch board and the phasing board and controls which particular sector is chosen for both the VHF and microwave links.

In actual operation the radio presents a voltage proportional to the strength of the VHF signal it is receiving in a particular sector. The uCB uses a 10 bit A/D converter to capture this information. The signal strength in each of the eight sectors is captured in this way. The uCB analyzes this information to determine the direction of the RCC, and the uCB may decide to change the current sector in which the microwave video signal is being transmitted. The actual logic used in making this decision is detailed in Section V.B.1.

#### IV.B. MICROCONTROLLER

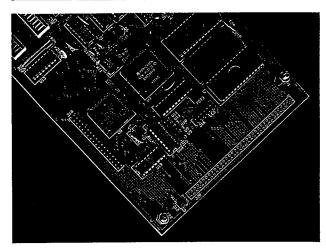

#### IV.B.1. GENERAL SPECIFICATIONS

The microcontroller board (uCB) is based on a Motorola MC68HC11A1 microcontroller. This device has 512 bytes of on chip EEPROM, parallel I/O, two types of serial I/O (SCI and SPI), 8 bit A/D channels, sophisticated 16 bit timers, Computer Operating Properly (COP) Watchdog system, etc.

The uCB features :

---Three memory sockets (Can accommodate any device up to 64kx8 by reprogramming the PLD device)

---10 bit serial A/D converter (Linear Technology LTC1091)

---PLD (Programmable Logic Device) allows flexible control signals and decoding

---On-board voltage regulation and inverting allows operation from a single +12 V supply

---Analog ground plane and separate analog voltage regulation.

---On board DIP switch allows control of scan speed and operation modes.

----

---Parallel output lines allow control of phasing board driver and microwave switch board driver.

---Separate connector allows a debugging module to be connected. The debugging module has an LCD display for error messages, LED's for visual indication of VHF and microwave sector position, DIP switch for operational mode selection, and a reset switch.

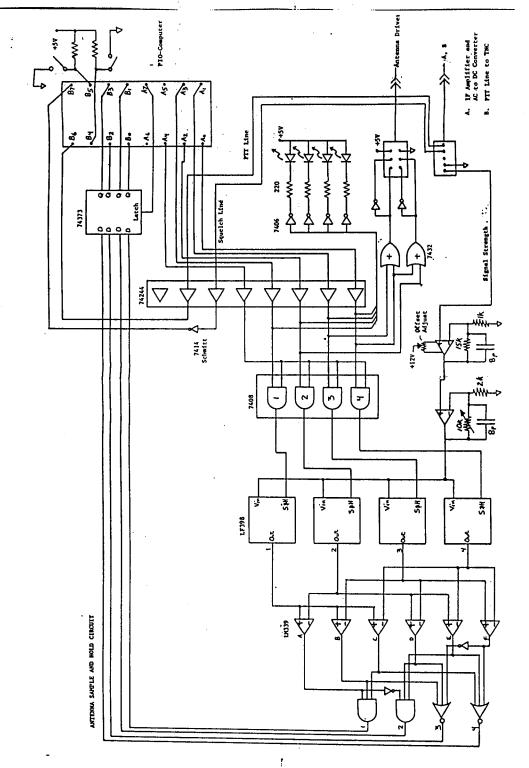

---The DC signal strength in circuitry includes voltage