Wright-Patterson Air Force Base, Ohio

## AFIT/GAP/ENP/94D-01

| Accesi               | on For         | · | ) |

|----------------------|----------------|---|---|

| DTIC                 | ounced         |   | ] |

| By<br>Distribution / |                |   |   |

| Availability Codes   |                |   |   |

| Dist                 | Avail a<br>Spe |   |   |

| A-1                  |                |   |   |

## TOTAL IONIZING DOSE EFFECTS IN MOSFET DEVICES AT 77 K

THESIS

Kevin J. Daul, Captain, USAF

AFIT/GAP/ENP/94D-01

Line of the Decomposition of the

Approved for public release; distribution unlimited

The views expressed in this thesis are those of the author and do not reflect the official policy or position of the Department of Defense or the U. S. Government.

### TOTAL IONIZING DOSE EFFECTS IN MOSFET DEVICES AT 77 K

### THESIS

Presented to the Faculty of the Graduate School of Engineering of the Air Force Institute of Technology Air University In Partial Fulfillment of the Requirements for the Degree of Master of Science in Nuclear Engineering

> Kevin J. Daul Captain, USAF

December 1994

Approved for public release; distribution unlimited

#### Preface

MOSFET technology is currently used extensively in the majority of electronic systems. When a MOSFET is exposed to ionizing radiation, the resulting effects from this radiation can cause severe degradation of the device performance and of its lifetime. This research investigated total ionizing dose effects on MOSFET devices, which utilized different oxide processes, while operating at 77 K.

I would like to express my thanks and appreciation to a number of people who assisted and supported me during the course of this project. Special thanks goes out to my faculty advisor, Major Paul Ostdiek, for his support and assistance throughout this research. In addition, I would also like to thank Dr. Bright and Captain Jeff Martin for their assistance and advice. I would also like to thank Mr. Lewis Cohn of the Defense Nuclear Agency, for sponsoring this research. Invaluable support and assistance was provided by Mr. Steven Clark and Mr. Patrick Cole of the Naval Surface Warfare Center during the experimental stages of this thesis. Furthermore, I would like to thank Mr. Jim Pickel of Maxwell Laboratories S-cubed division for his assistance during this research. Perhaps most of all, I would like to thank my wife Susan, and daughters Ambrosia and Kellsie, for their understanding and patience throughout the entire project.

Kevin J. Daul

ii

# Table of Contents

|                 |                                                                                    | Page                |

|-----------------|------------------------------------------------------------------------------------|---------------------|

| Preface         |                                                                                    | ii                  |

| List of Figures | · · · · · · · · · · · · · · · · · · ·                                              | V                   |

| List of Tables  |                                                                                    | . vii               |

| Abstract        | ·<br>· · · · · · · · · · · · · · · · · · ·                                         | . viii              |

| I. Introducti   | on                                                                                 | .1-1                |

| II. Literature  | Review                                                                             | . 2-1               |

|                 | 2.1 Literature Review of Hole Transport                                            | .2-1                |

|                 | 2.1.1 Review of Hole Transport in SiO <sub>2</sub>                                 |                     |

|                 | 2.1.2 Review of Hole Transport in RNO                                              |                     |

|                 | 2.2 Literature Review of Trapped Charge                                            |                     |

|                 | 2.2.1 Review of Hole Traps in Thermal Oxides                                       |                     |

|                 | 2.2.2 Review of Charge Traps in RNO                                                |                     |

|                 | 2.2.3 Review of Trapped Charge in Interface States.                                |                     |

|                 | 2.3 Literature Review of Interface Trap Generation                                 |                     |

|                 | 2.3.1 Review of Two-Stage Hydrogen Model in SiO <sub>2</sub>                       |                     |

|                 | 2.3.2 Review of Experiments Supporting Two-Stage                                   |                     |

|                 | Hydrogen Model in SiO <sub>2</sub> $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ | 2-10                |

|                 | 2.3.3 Review of Interface State Formation                                          |                     |

|                 |                                                                                    | <u>~</u> 1 <u>~</u> |

| III. Theory     |                                                                                    | .3-1                |

|                 | 3.1 Types of MOSFETs                                                               | .3-1                |

|                 | 3.2 Threshold Voltage                                                              |                     |

|                 | 3.3 MOSFET Operation                                                               |                     |

|                 | 3.4 Transconductance.                                                              |                     |

|                 | 3.5 Ionizing Radiation                                                             |                     |

|                 | 3.6 Total Dose Effects                                                             |                     |

|                 | 3.6.1 Hole Transport                                                               |                     |

|                 | 3.6.2 Trapped Charge                                                               | 3-18                |

|                 | 3.6.3 Interface States                                                             |                     |

|                 | 3.7 Bias Effects                                                                   | 3-29                |

### page

| 3.8              | Oxide Processing                           |

|------------------|--------------------------------------------|

| IV. Experimental |                                            |

| 4.1              | Equipment                                  |

|                  | 4.1.1 Test Devices                         |

|                  | 4.1.2 Shepherd Test Cell                   |

|                  | 4.1.3 Cryogenic Dewar                      |

|                  | 4.1.4 Keithley Transistor Parameter System |

|                  | 4.1.5 Thermoluminescent Dosimeters         |

| 4.2              | Experimental Procedures                    |

|                  | 4.2.1 Dosimetry                            |

|                  | 4.2.2 Total Dose Testing                   |

| V. Results and D | Discussion                                 |

| 5.1              | Threshold Voltage Shift                    |

|                  | 5.1.1 Drain Bias Effects                   |

|                  | 5.1.2 Threshold Voltage Determination      |

|                  | 5.1.3 N-Channel Transistors                |

|                  | 5.1.4 P-Channel Transistors                |

| 5.2              | Transconductance                           |

| 5.3              | Gate Bias Effects                          |

| 5.4              | Radiation Hardness                         |

| VI. Summary and  | Recommendations                            |

| Bibliography     | BIB-1                                      |

| Vita.            |                                            |

# List of Figures

| Figu          | Page                                                                                                                                                                                                                                                                                                        |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

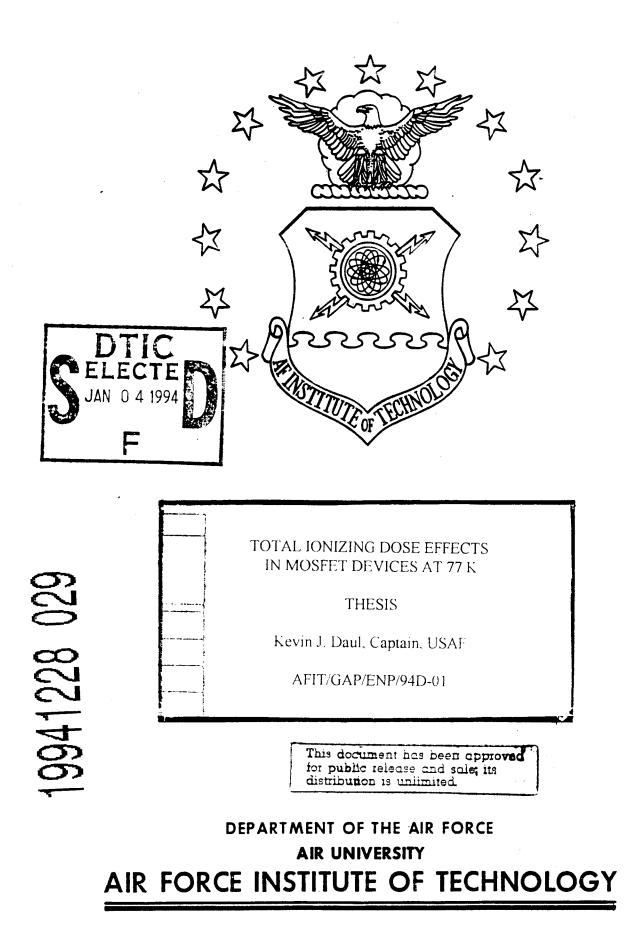

| 2-1.          | Flatband voltage recovery data following pulsed LINAC electron<br>irradiation of 96.5 nm wet-grown oxide capacitor under 1 MV/cm<br>oxide field for series of temperatures between 124 and 293 K.<br>The data are normalized to the initial flatband voltage shift<br>immediately after the radiation pulse |

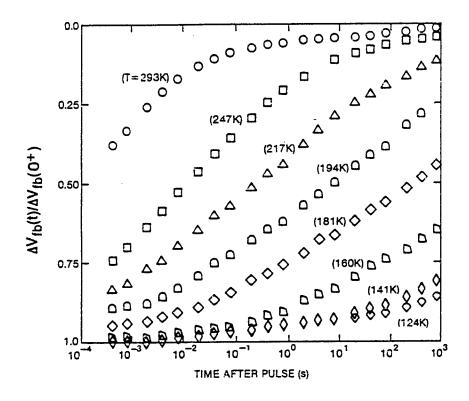

| 2 <b>-</b> 2. | Normalized flatband voltage recovery data following pulsed<br>LINAC electron-beam exposure for 96.5 nm oxide at 79 K and<br>for oxide fields from 3 to 6 MV/cm                                                                                                                                              |

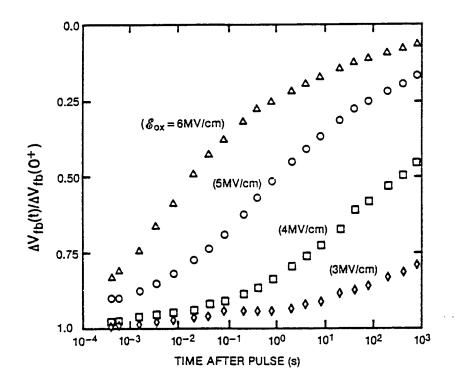

| 2-3.          | Schematic diagram of microscopic defects in SiO <sub>2</sub> and RNO                                                                                                                                                                                                                                        |

| 3-1.          | Cross Section of a simplified n-channel MOSFET showing the basic elements                                                                                                                                                                                                                                   |

| 3-2.          | An energy band diagram for a p-type semiconductor at threshold<br>inversion                                                                                                                                                                                                                                 |

| 3-3.          | Diagram of an n-channel MOSFET showing the conduction<br>channel after the device is turned on                                                                                                                                                                                                              |

| 3-4.          | Diagram showing a Compton interaction                                                                                                                                                                                                                                                                       |

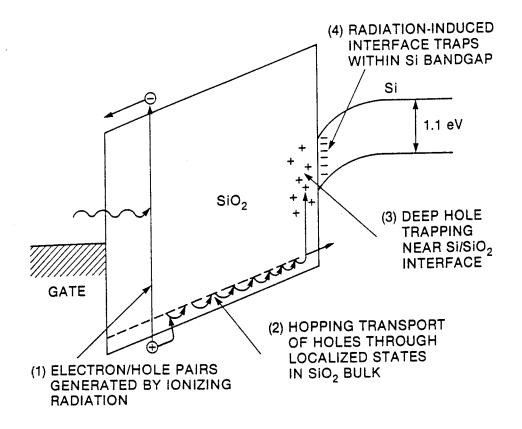

| 3-5.          | The basic ionizing radiation-induced effects in MOS structures,<br>for a positive applied bias                                                                                                                                                                                                              |

| 3 <b>-</b> 6. | Energy-band diagram for a p-type semiconductor showing the trapped charge in the interface states when biased                                                                                                                                                                                               |

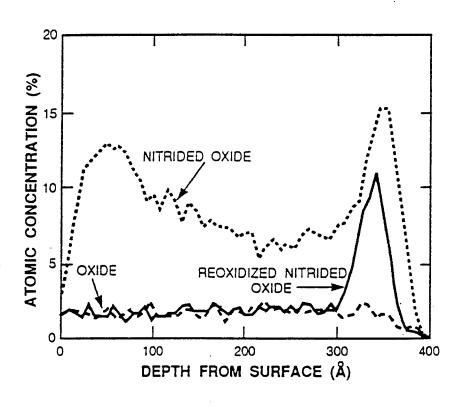

| 3-7.          | Depth profile of nitrogen concentration in the thermal oxide,<br>nitrided oxide, and reoxidized nitrided oxide based on Auger<br>electron spectroscopy measurements                                                                                                                                         |

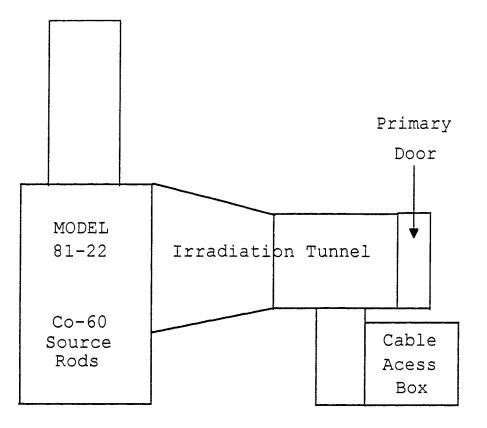

| <b>4-</b> 1.  | Diagram of the Shepherd 484 <sup>60</sup> Co irradiator                                                                                                                                                                                                                                                     |

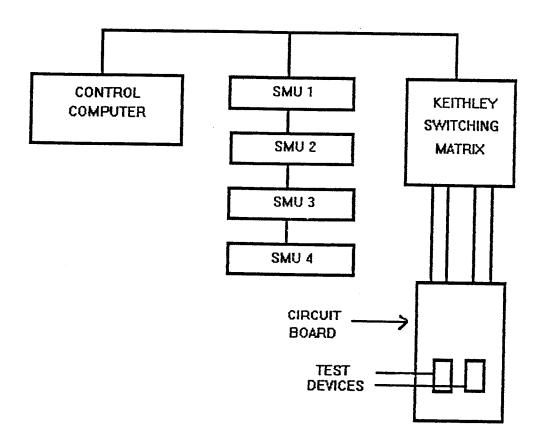

| <b>4-</b> 2.  | Block diagram showing the configuration of the experiment                                                                                                                                                                                                                                                   |

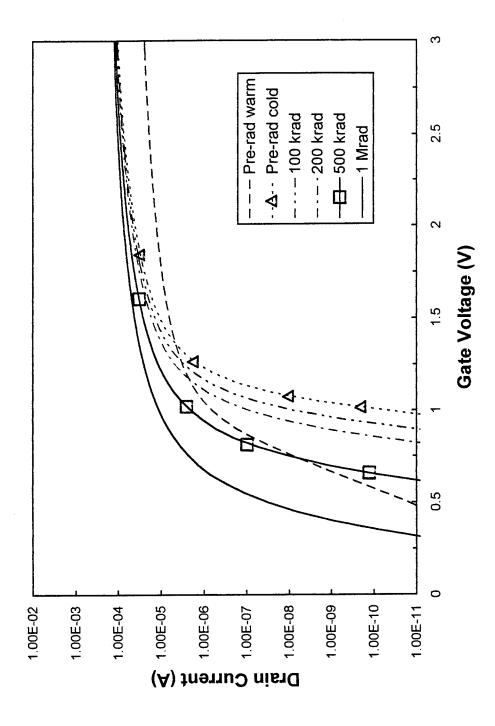

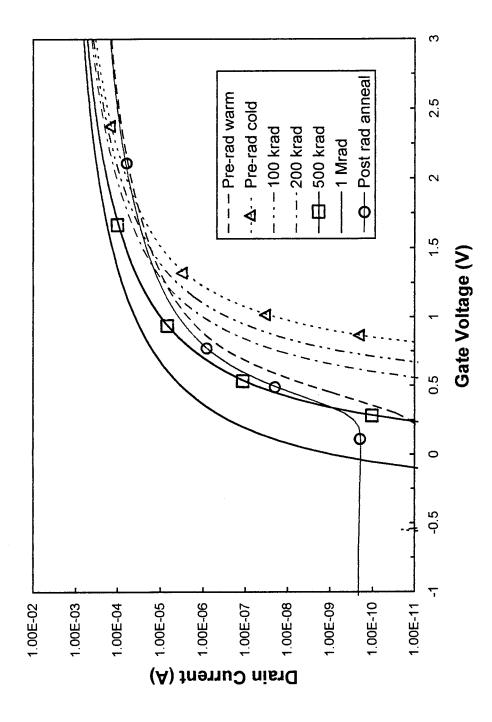

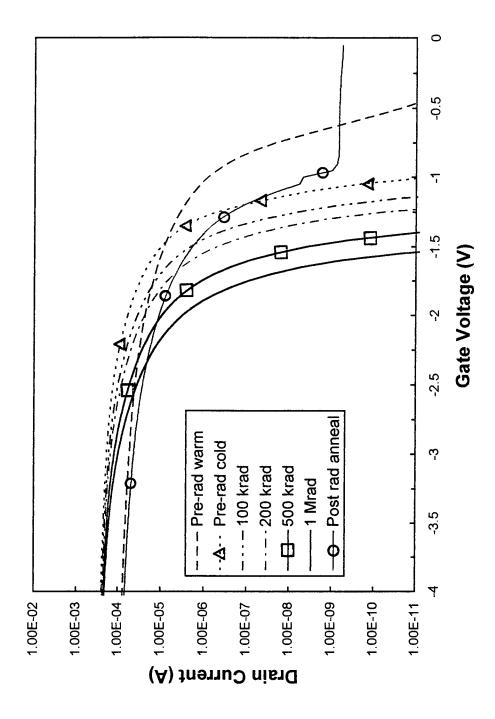

| 5-1.          | $I_D - V_G$ characteristics of transistor 9NTO, $V_D = 0.1 V$                                                                                                                                                                                                                                               |

Figure

| 5-2.          | $I_D - V_G$ characteristics of transistor 9NTO, $V_D = 1.0 V \dots \dots \dots \dots$                              | .5-3 |

|---------------|--------------------------------------------------------------------------------------------------------------------|------|

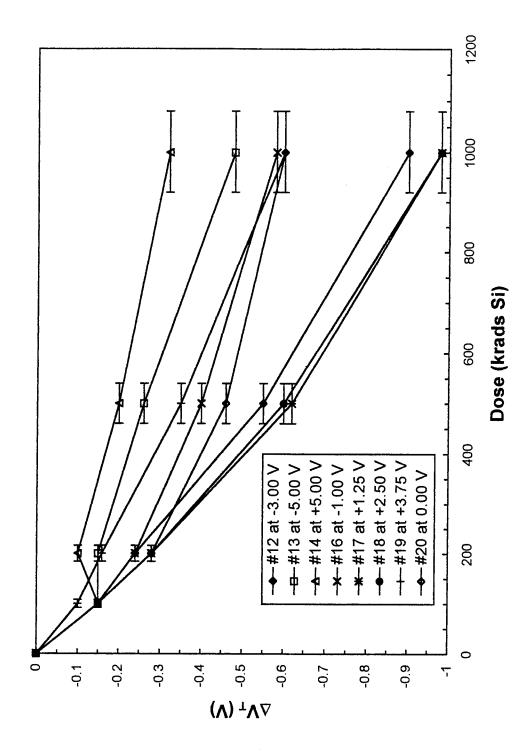

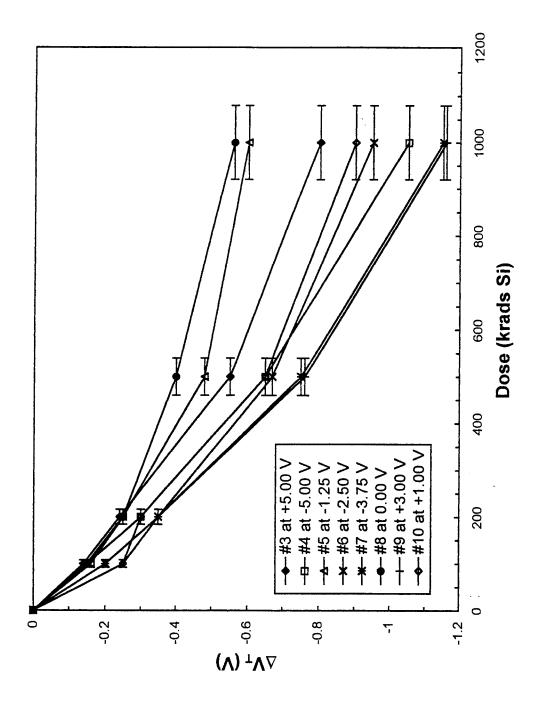

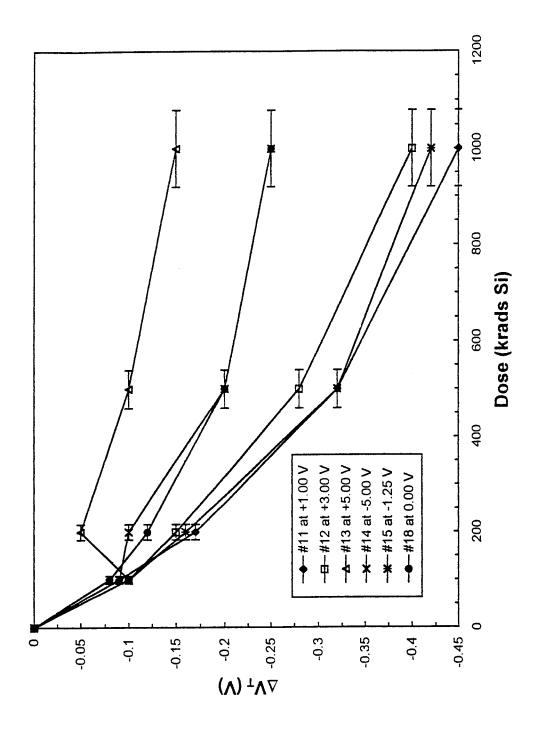

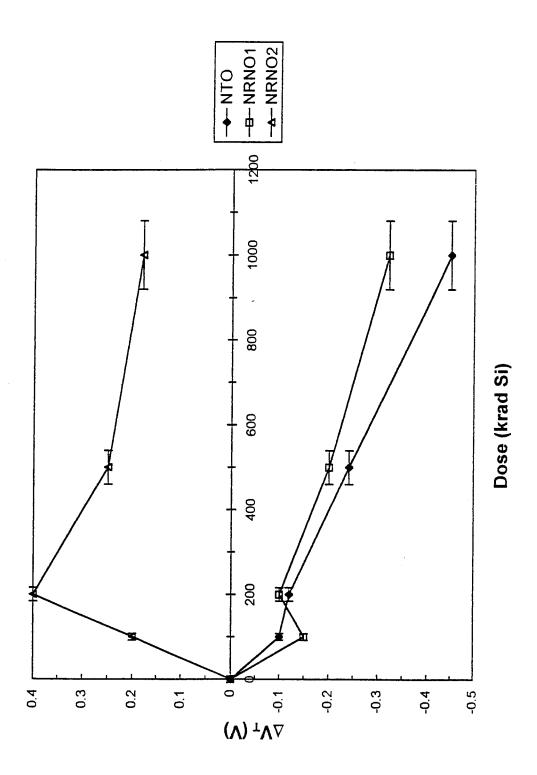

| 5 <b>-</b> 3. | Threshold voltage shift versus total dose for the NTO transistors                                                  | .5-7 |

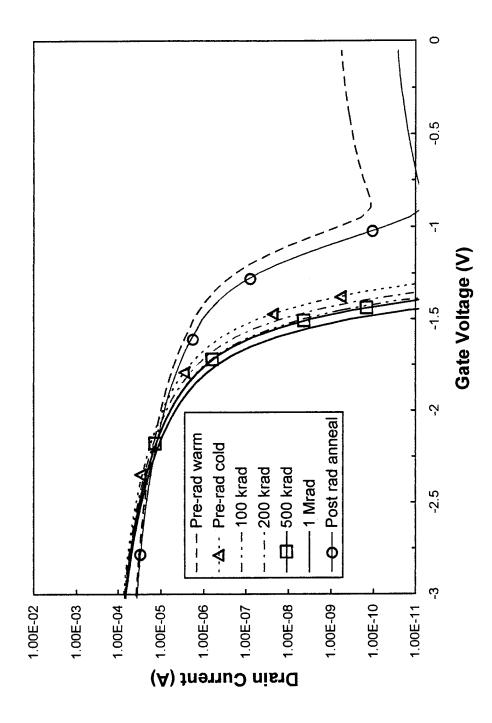

| 5-4.          | $I_D$ - $V_G$ characteristics of transistor 12NRNO1                                                                | .5-9 |

| 5-5.          | Threshold voltage shift versus total dose for the NRNO1 transistor                                                 | 5-11 |

| 5 <b>-</b> 6. | $I_D$ - $V_G$ characteristics of transistor 2NRNO2                                                                 | 5-12 |

| 5-7.          | Threshold voltage shift versus total dose for the NRNO2 transistors.                                               | 5-14 |

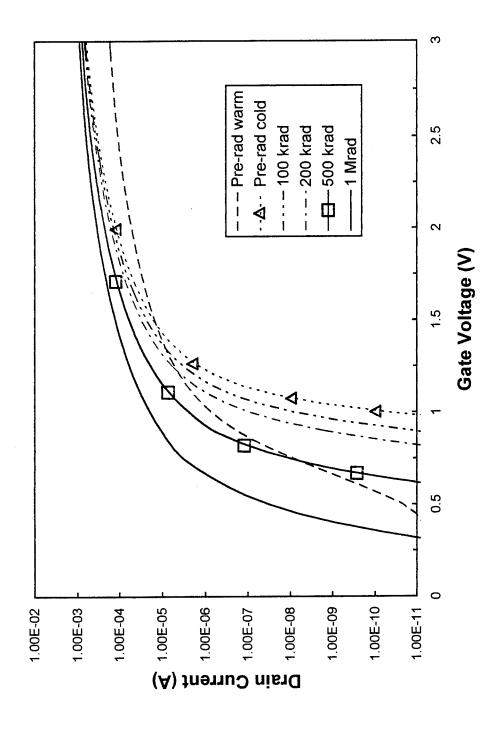

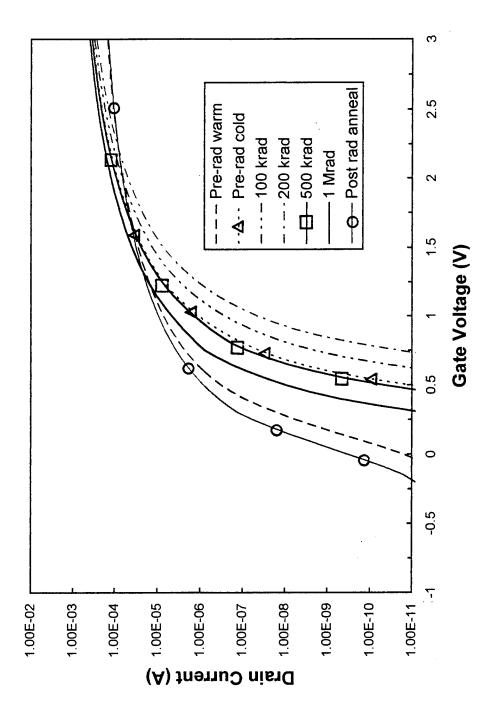

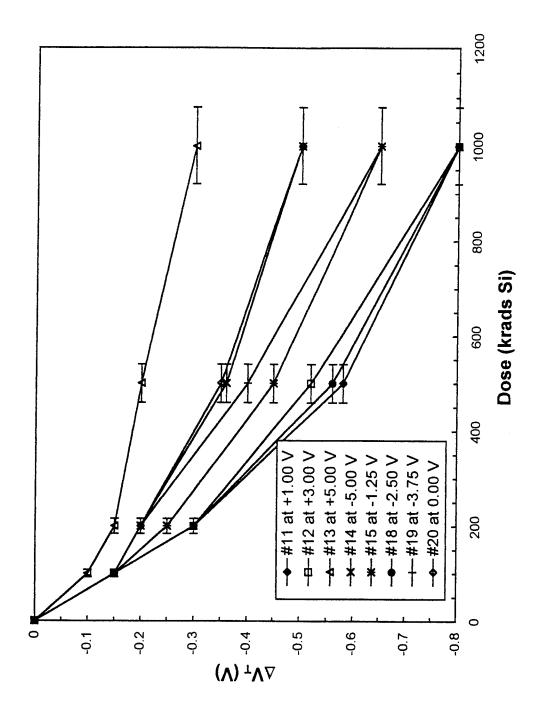

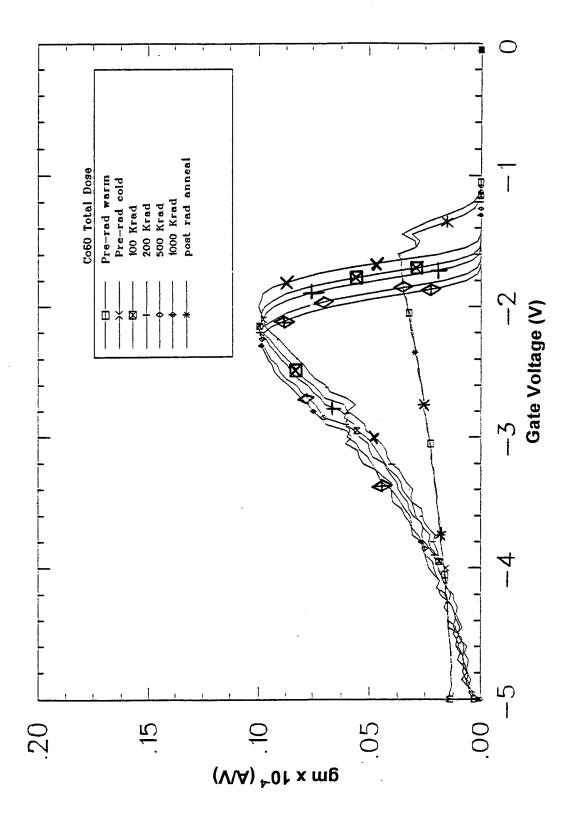

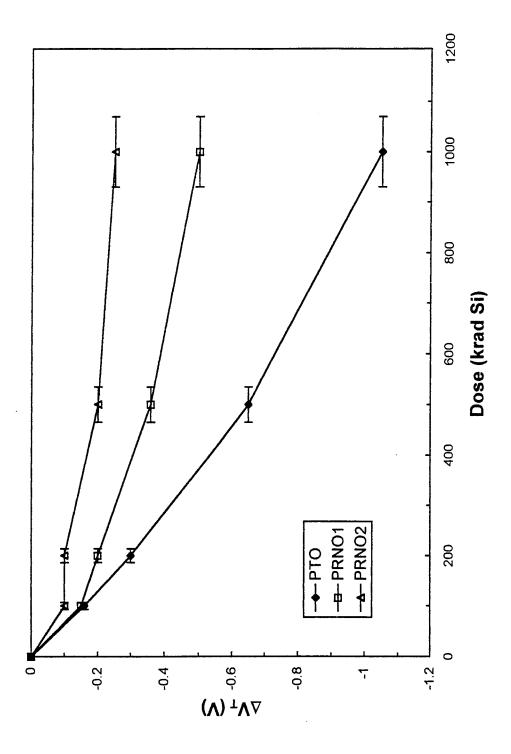

| 5-8.          | $I_D - V_G$ characteristics of transistor 8PTO                                                                     | 5-17 |

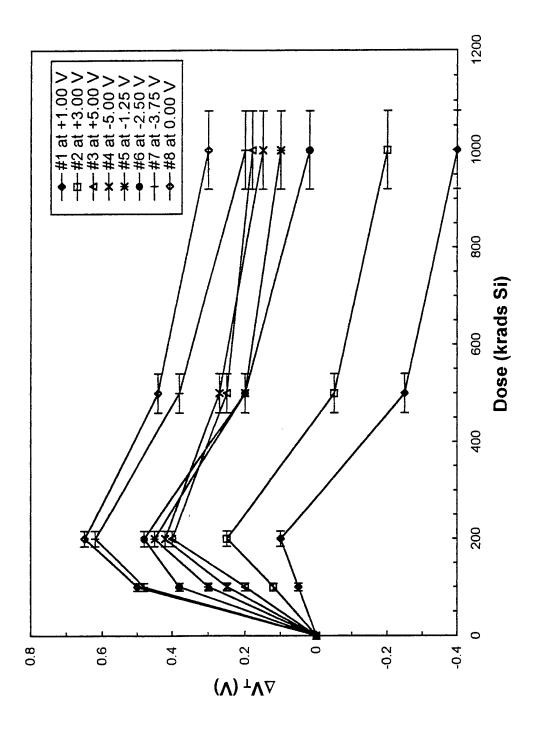

| 5-9.          | Threshold voltage shift versus total dose for the PTO transistors.                                                 | 5-19 |

| 5-10.         | Threshold voltage shift versus total dose for the PRNO1 transistors                                                | 5-20 |

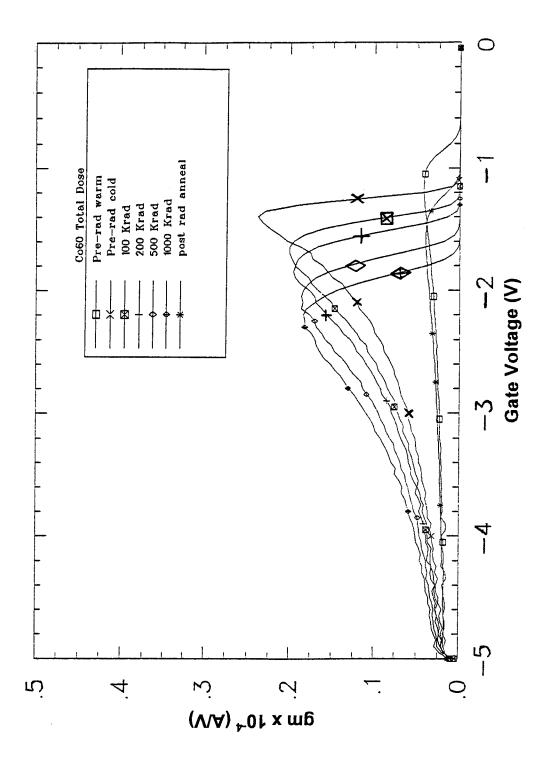

| 5-11.         | $I_D - V_G$ characteristics of transistor 13PRNO2                                                                  | 5-21 |

| 5-12.         | Threshold voltage shift versus total dose for the PRNO2 transistors                                                | 5-22 |

| 5-13.         | Transconductance versus gate voltage for transistor 18PRNO2                                                        | 5-24 |

|               | Transconductance versus gate voltage for transistor 8PTO                                                           | 5-25 |

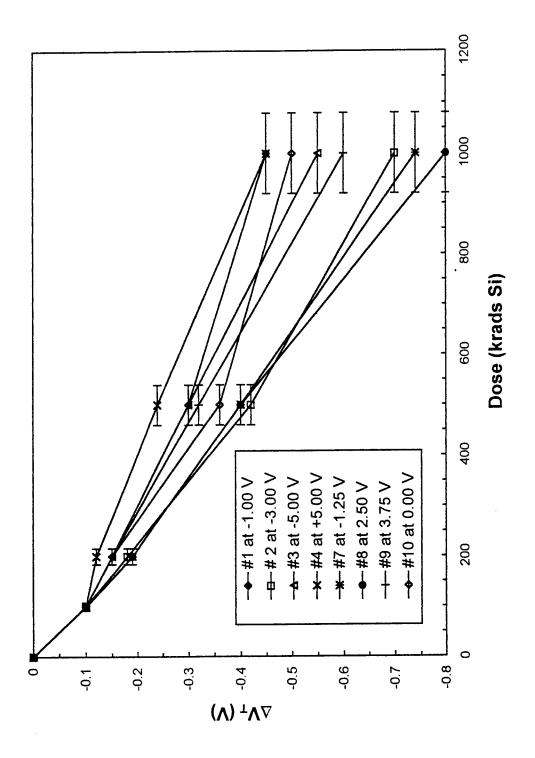

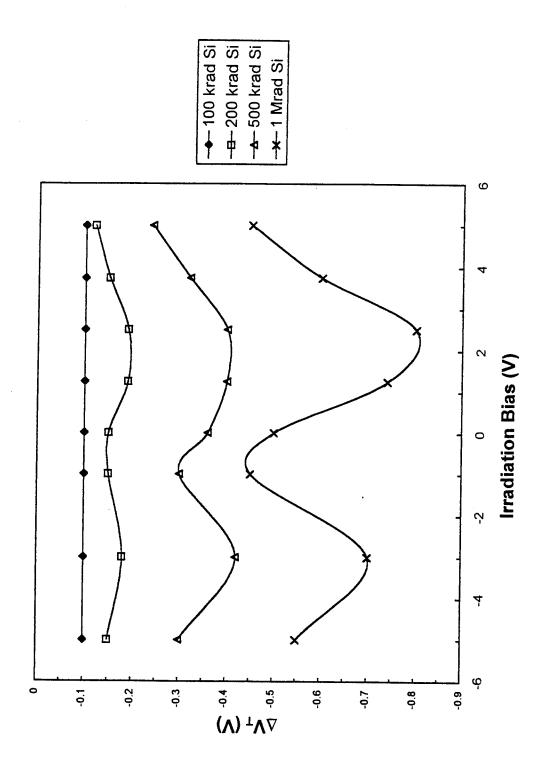

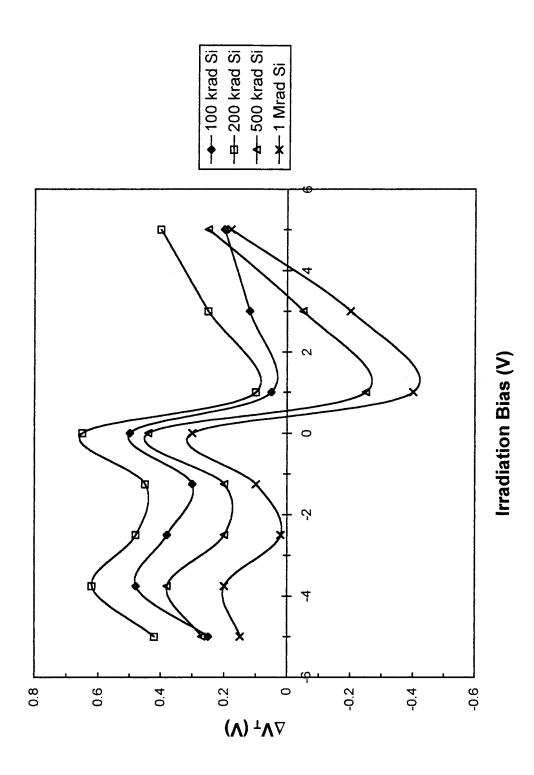

| 5-15.         | Threshold voltage shift versus bias during irradiation for the NTO transistors                                     | 5-27 |

| 5-16.         | Threshold voltage shift versus bias during irradiation for the NRNO2 transistors                                   | 5-29 |

| 5-17.         | Threshold voltage shift versus total dose for n-channel devices<br>which were biased at +5.00 V during irradiation | -32  |

| 5-18.         | Threshold voltage shift versus total dose for p-channel devices which were biased at -5.00 V during irradiation    | -34  |

page

# List of Tables

| Tabl         | le P                                                                  | Page         |

|--------------|-----------------------------------------------------------------------|--------------|

| 4-1.         | Results of the TLD irradiation                                        | .4-9         |

| <b>4-</b> 2. | Results of the TLD irradiation in the Gammacell 220                   | .4-9         |

| <b>4-</b> 3. | Test devices and their bias during irradiation on the first test day  | <b>1-</b> 13 |

| 4-4.         | Test devices and their bias during irradiation on the second test day | -14          |

| 4-5.         | Test devices and their bias during irradiation on the third test day  | -14          |

#### AFIT/GAP/ENP/94D-01

#### Abstract

Total ionizing dose effects on thermal oxide and reoxidized nitrided oxide (RNO) MOSFET devices operating at 77 K were studied. The MOSFETs were immersed in liquid nitrogen and irradiated, using a <sup>60</sup>Co source, up to 1 Mrad(Si) at a dose rate of 107 rads(Si)/sec. Drain current-gate voltage characteristics were obtained and used to determine threshold voltage and transconductance. At 77 K the subthreshold slopes indicated no observed buildup of interface states in any of the transistors. Furthermore, all transistors experienced very little change in the transconductance. Typical negative shifts in threshold voltage as dose increased were observed in all of the thermal oxide devices. The threshold voltage shifts of the RNO devices were typically less than those for thermal oxide devices.

#### TOTAL IONIZING DOSE EFFECTS IN MOSFET DEVICES AT 77 K

#### I. Introduction

The metal oxide semiconductor field effect transistor (MOSFET) is used extensively in digital circuit applications and is considered to be the core of integrated circuit design. By operating MOSFETs at cryogenic temperatures it may be possible to improve the efficiency or optimize some desirable characteristic of a device compared to operating at higher temperatures. There are several advantages of operating MOSFETs and integrated circuits at low temperatures. These advantages include: faster switching speeds due to increased mobility and decreased electrical resistance; increased reliability due to exponential slow down of thermally activated processes such as diffusion, electromigration, and chemical reactions; improved noise behavior due to reduced thermal noise; and greater packing density due to improved heat removal (1; 2). Furthermore, operation at low temperatures may be necessary if the semiconductor devices are to be used in conjunction with a system that operates at cryogenic temperatures.

As just mentioned, there are several reasons for using MOSFETs at cryogenic temperatures. However, ionizing radiation induced degradation effects in MOSFETs are a major concern. Ionizing radiation produces electron-hole pairs in the gate oxide. In a

1-1

thermal oxide the electrons are relatively mobile and are readily swept out of the oxide through the gate for a positive gate bias. The holes are relatively immobile and, under a positive applied gate potential, undergo a stochastic hopping transport process through the oxide to the oxide-semiconductor interface. Some of these holes will be captured in trapping sites near this interface, producing a negative shift in the threshold voltage. Additional interface states can also be generated during this process. This buildup of interface states occurs over a relatively long period of time and is a strong function of the electric field applied in the oxide. These radiation-generated interface states can cause additional shifts in threshold voltage as well as a reduction in carrier mobility.

Electronic systems that utilize MOSFETs may have to operate in environments consisting of low temperatures and ionizing radiation. Examples of these systems include, satellite systems, weapon systems, instrumentation for nuclear power plants, and detectors used in high energy physics experiments. Satellite systems require certain electronic components that must operate at cold temperatures while being exposed to ionizing radiation. For example, the signal processing electronics used for infrared focal plane arrays operate in a cryogenic/vacuum system. Infrared focal plane arrays are of importance to the military since they are used on Air Force surveillance and seeker systems. The military needs satellites for meteorological, communication, and navigation operations, as well as for surveillance and command-and-control operations. These operations are essential to the national security of this country. Many weapon systems also contain electronic components that may encounter severe radiation environments. Instrumentation and detectors that are used at nuclear power plants and at

1-2

experimental facilities can encounter similar environments that a satellite or weapon system may experience.

Satellites are exposed to naturally occurring ionizing radiation while passing through the Van Allen radiation belts. In addition to this natural environment, satellite systems, as well as weapon systems, may be exposed to a nuclear-enhanced environment created from the detonation of nuclear weapons.

Recently, in order to improve the hardness of MOSFETs to ionizing radiation, researchers have begun using nitrided oxides and reoxidized nitrided oxides (RNO) for the gate oxide. Nitrided oxides and RNO have demonstrated a reduction in threshold voltage shift after total ionizing dose, as well as suppressing the formation of radiation generated interface states, at both room and cryogenic temperatures (3-7). Furthermore, studies have found that nitrided oxides and RNO are superior to thermal oxides in terms of better process yield, greater dielectric strength, improved resistance under electrical stress, and better resistance to the diffusion of dopants or contaminants (4; 8). The oxide growth process is critical to the total dose hardness of nitrided oxides and RNO. Specifically, the time and temperature of the nitridation and reoxidation play a critical role in the susceptibility to total dose damage.

Ionizing radiation effects may degrade MOSFET performance and the useful lifetime of the device may be severely limited. Degraded MOSFET performance can have an adverse effect on total system performance. Thus, it is necessary to have electronic components exposed to an operational environment continue to function properly. Furthermore, MOSFETs need to be reliable and dependable when exposed to low temperatures and ionizing radiation. Recently, nitrided oxides and RNO have been shown to be superior to thermal oxides in radiation hardness, offering promise in their future use.

This research investigates total ionizing dose effects in MOSFET devices, fabricated using different oxide processes, while operating at 77 K. Devices utilizing both thermal oxide and RNO processing were studied up to total doses of 1 Mrad(Si). The specific radiation effects that were investigated are threshold voltage shifts and changes in transconductance. These changes can be used to predict the performance of similar devices exposed to similar environments. Therefore, the goal of this study is to further the understanding of ionizing radiation effects and oxide processing in MOSFET devices operating at 77 K.

This first chapter provided an introduction into the problem of radiation effects in MOSFETs. The next chapter gives a select review of the literature in the area of total dose effects in MOS devices. Then, chapter 3 discusses the theory of basic MOSFET device physics, and of total dose effects. Included in this chapter are concepts involving charge generation, transport, and trapping in the gate oxide, as well as the creation of interface traps at the Si-oxide interface. Chapter 4 provides a description of the experimental research that was performed. This chapter contains descriptions on the test devices, equipment, and procedures used for this research. The results of the experimental research are presented and discussed in chapter 5. The final chapter, chapter 6, summarizes the research and offers recommendations and comments regarding future work into this area of study.

#### II. Literature Review

This chapter contains a review of the literature on the total dose effects in MOSFETs. The vast amount of information that has been published in this area is beyond the scope of this effort, so only the material directly related to this research is presented here. There are three major areas, each area comprises its own section, that are reviewed in this chapter. The first section contains a review on the important features of hole transport in both thermal and reoxidized nitrided oxides. The second section presents material on the concepts involved with the trapping of charge in oxides. The third section reviews the literature which deals with the formation of interface states at the Si-oxide interface.

#### 2.1 Literature Review of Hole Transport

<u>2.1.1 Review of Hole Transport in SiO</u><sub>2</sub>. The 1970's saw a relatively large scale investigation into the hole transport properties in SiO<sub>2</sub>. An important focal point of this investigation was the dispersive features of hole transport in SiO<sub>2</sub>. This section presents several representative experiments which were taken from the literature which illustrate several important characteristics of hole transport in thermal oxides.

Much of the research into hole transport in  $SiO_2$ , performed by Boesch, McLean, and colleagues (9-13), consisted of irradiating MOS capacitors with a pulsed electron source. Flat band voltage shifts versus the time after the radiation pulse as a function of temperature and electric field were determined. Only negative flatband voltage shifts were observed due to the net positive charge induced in the oxide layer.

Boesch and McLean proposed that radiation generated electrons, due to their relatively high mobility, are swept out of the oxide while the radiation generated holes are left remaining near their point of generation. This results in rigid negative shifts along the voltage axis in the capacitance-voltage or current-voltage characteristics of the devices compared to their preirradiation characteristics. The voltage shift is proportional to the first spatial moment of the radiation-induced charge distribution relative to the gate. As the holes execute their relatively long transport toward the negative electrode, the changing charge distribution is reflected in the time dependence of the voltage shifts. The holes are collected at the negative electrode, resulting in the relaxation of the flatband voltage toward its preirradiation value.

From these experiments (9-13) it was observed that in every case the recovery, or hole transport, is very dispersive in time. This large dispersion was attributed to a wide distribution of individual hole transit times across the oxide layers. The effects of temperature and oxide field on hole transport in  $SiO_2$  are shown in Figures 2-1 and 2-2 respectively. A feature common to all of the data is that changes in temperature and field did not have much effect on the shape of the recovery curves. Rather, the major effect of changes in these parameters is simply to produce a translation of the curves along the time axis. This means that only the time scale for the transport is affected and not the amount of dispersion. Both Boesch and McLean successfully employed a stochastic model of hole transport based on the Continuous-Time Random Walk (CTRW) formalism of Montroll and Weiss to describe the time dispersion of their data (14).

Figure 2-1. Flatband voltage recovery data following pulsed LINAC electron irradiation of 96.5 nm wet-grown oxide capacitor under 1 MV/cm oxide field for series of temperatures between 124 and 293 K. The data are normalized to the initial flatband voltage shift immediately after the radiation pulse (10).

As a result of the strongly temperature-activated nature of the transport, it was seen that very little transport occurred at low temperatures until relatively long times on the scale of the experiments. For example (see Figure 2-2), at 79 K and for a field of 3 MV/cm, the recovery only begins after 10 seconds and was not complete up to the longest measurement time of 1000 seconds (13). In addition, for fields less than 2 MV/cm, essentially no recovery took place for times of the order of thousands of seconds.

Figure 2-2. Normalized flatband voltage recovery data following pulsed LINAC electron-beam exposure for 96.5 nm oxide at 79 K and for oxide fields from 3 to 6 MV/cm (13).

2.1.2 Review of Hole Transport in RNO. Very little information on hole transport in reoxidized nitrided oxides (RNO) has been published. However, in 1991 Boesch and Dunn measured the charge generation and hole transport in both reoxidized nitrided oxides and radiation-hard thermal oxides (TO) (15). They measured these processes as a function of temperature from 77 to 295 K and applied fields from 1 to 5 MV/cm using pulsed irradiation and fast time-resolved current-voltage measurement techniques. It was determined that the radiation-generated charge yield in TO and RNO are essentially equal. In addition, the hole transport in RNO is qualitatively similar to that in TO. However, the temperature and field dependence of hole transport in RNO is quantitatively different from the dependencies in TO. It was observed that hole transport in RNO at low fields and near room temperature is significantly retarded with respect to that in TO, while the transport in RNO at 77 K for applied fields between 2 and 5 MV/cm

#### 2.2 Literature Review of Trapped Charge

This section is concerned with the published literature regarding the microscopic nature of hole traps in TO, charge traps in RNO, and interface states. These areas of study are relatively new and there is still some uncertainty into exactly which microscopic point defects are responsible for the trapping of charge.

2.2.1 Review of Hole Traps in Thermal Oxides. Several microscopic point defects have been observed in irradiated TO (14; 16-18). The most important defect in thermal oxides has been determined to be the E' center (14; 16-18). The E' center was identified by Lenahan and Dressendorfer (17) to be the primary hole trap in TO. They showed a strong correlation between the E' center and radiation-induced positive charge for thermal oxides by using electron spin resonance (ESR) measurements. The E' center is a trivalent silicon defect associated with an oxygen vacancy in the SiO<sub>2</sub> structure. Figure 2-3(a) is a schematic diagram of the E' center in SiO<sub>2</sub>. In addition to identifying the microscopic nature of the hole traps, the ESR measurements showed that the E' centers are concentrated near the Si-SiO<sub>2</sub> interface.

2.2.2 Review of Charge Traps in RNO. In 1992 Yount et al. (19) used ESR to study the radiation-induced point defects in thermal oxides, nitrided oxides (NO), and reoxidized nitrided oxides. It was determined that nitridation reduces the density of radiation-induced E' centers, and creates bridging nitrogen center precursors. A schematic diagram of a bridging nitrogen center is shown in Figure 2-3(b). A bridging nitrogen center is a nitrogen atom bonded to two silicon atoms, leaving two nitrogen bonds available for trapping charge. It is suggested that these bridging nitrogen centers are probably electron traps, but this has not been conclusively proven. The reoxidation results in a reduction of the bridging nitrogen centers and an increase in the amount of E' centers. These E' centers were determined to be neutral (not positively charged as in thermal oxides) and did not seem to play an important role in hole trapping in RNO. The E' center in RNO is shown in Figure 2-3(c). It is currently uncertain as to which defect center does play an important role in hole trapping in RNO.

Figure 2-3. Schematic diagram of: (a) positive E' center in SiO<sub>2</sub>; (b) bridging nitrogen center; (c) neutral E' center in RNO; (d) P<sub>b</sub> center. The arrows indicate the direction of Jahn-Teller distortion (19).

2.2.3 Review of Trapped Charge in Interface States. ESR was used once again by Lenahan and others to identify the  $P_b$  center and associate it with the radiation-induced interface state (16; 18). Figure 2-3(d) is a schematic diagram of the  $P_b$  center. The  $P_b$ center was identified as an interface trap defect composed of a trivalent silicon bonded to three silicon atoms at the Si-oxide interface. Lenahan and Dressendorfer (17; 20) determined that the number of observed  $P_b$  centers correlated to the number of interface traps measured using capacitance-voltage measurements during irradiation and during post irradiation anneals.

### 2.3 Literature Review of Interface Trap Generation

In recent years, a great deal of electrical and microscopic information about radiation-induced interface traps has been obtained. Based on this information several models have been proposed to explain the generation of interface traps following exposure to ionizing radiation. The most accepted models are variations of a two-stage hydrogen transport model. Based on the results of several time-dependent and field-dependent experiments, it was determined that a positive ion (probably  $H^+$ ) is responsible for the formation of interface states (21; 22). One common feature among almost all of the models is that they begin with the transport and /or trapping of radiation-generated holes.

This section is divided into three subsections. First, a description of the two-stage hydrogen model in  $SiO_2$  is discussed. Second, experiments which support the two-stage hydrogen model in  $SiO_2$  are presented. Third, a review of interface state formation in both TO and RNO is presented.

2.3.1 Review of Two-Stage Hydrogen Model in SiO<sub>2</sub>. Svensson was the first to propose a two-stage hydrogen model for the buildup of interface traps (4). In the first stage of his model, radiation-generated holes react with some hydrogen containing species in the oxide causing the release of neutral hydrogen. The free hydrogen atoms diffuse to the Si-SiO<sub>2</sub> interface in the second stage, and break Si-H bonds at the interface to create the interface traps.

Winokur (23) modified this two-stage model to suggest that hydrogen ions,  $H^+$ , were released instead of neutral hydrogen. The first stage determines the saturated value of interface traps (i.e. the peak value of interface traps), and occurs during the period of charge generation and hole transport through the oxide. The saturated value is related to the production of electron-hole pairs in the oxide. Then, in the second stage, the liberated  $H^+$  ions undergo a dispersive hopping transport which controls the rate of interface formation. The  $H^+$  ions that reach the interface can break Si-H bonds at the interface creating the interface traps. This two stage hydrogen transport model is now believed to be the main process for radiation-induced interface state buildup. In the previously described hydrogen transport model  $H^+$  ions were released as holes transport through the oxide. In this model, an increase in electric field increases the energy a hole imparts to the oxide lattice as it transports through the oxide, causing more  $H^+$  to be released. This would produce more interface traps with increasing field. This increase is true up to a point and then the interface trap buildup follows an approximate  $E^{-1/2}$  field dependence.

A model to account for this field dependence was proposed by Shaneyfelt et al. (24). This model was called the hole-trapping/hydrogen transport  $(HT)^2$  model. In this model the number of holes trapped determines the total number of interface traps (i.e. the saturated value) that buildup at a given electric field. Because the number of holes trapped scales as  $E^{-1/2}$ , the saturated value of interface trap buildup will follow the same field dependence. The  $(HT)^2$  model involves, for positive gate bias, hole trapping near the Si-oxide interface, and the release of mobile H<sup>+</sup> ions near the interface. The H<sup>+</sup> ions transport to the interface and react to form interface traps. In the  $(HT)^2$  model, H<sup>+</sup> transport is the rate limiting process.

2.3.2 Review of Experiments Supporting Two-Stage Hydrogen Model in SiO<sub>2</sub>. A set of field switching experiments performed by Saks (25) supports a type of two-stage hydrogen model. Interface trap formation was measured using charge pumping on MOSFETs irradiated at 78 K and subjected to 20 minute isochronal anneals up to 350 K. It was concluded that interface traps are produced during the annealing by two different processes at widely separated temperatures. The small process (< 10% of the total buildup) occurred around 120 K and was dependent on gate bias. The large process (> 90% of the total buildup) occurred between 200 and 300 K and was strongly dependent on gate bias. Saks proposed that the small process was caused by the reaction of radiation-induced neutral hydrogen with an interface state precursor at the Si-SiO<sub>2</sub> interface to produce an interface trap. He further suggests that the large process is caused by the reaction of radiation-induced neutral hydrogen and holes to produce H<sup>+</sup>, which drifts to the interface region in response to the applied field, and reacts at the interface to produce the interface traps.

Shaneyfelt (24) performed a study of radiation-induced interface trap buildup rates in wet and dry oxides (20 nm to 100 nm) for both positive and negative bias irradiations followed by positive bias anneals. The observed buildup rates were consistent with the predictions of the  $(HT)^2$  model. For the case of positive bias during irradiation and anneal, he observed that the time-dependent buildup of interface traps is nearly independent of oxide thickness for both wet and dry gate oxides. For the case of negative gate bias during irradiation and positive bias anneal, he observed a thickness dependence for both the wet and dry oxides. These thickness dependencies suggest that the way in which hydrogen is incorporated in the oxide during processing may play a key role in determining whether  $H^+$  is released in the bulk of the oxide or near the interface.

The details of the mechanisms for the buildup of interface traps still needs to be resolved. It is apparent that hole transport and/or trapping either in the bulk of the oxide or near the interface is important for interface formation. In addition, the release of hydrogen also seems to be involved in one way or another with the buildup of interface states.

2.3.3 Review of Interface State Formation. It has been demonstrated that the formation of interface states is suppressed in thermal oxides at low temperatures. Saks et al. (25; 26) measured the formation of interface traps in thermal oxides using a charge pumping technique on MOSFETs irradiated at temperatures ranging from 78 to 285 K. They found that interface states are not formed by radiation at the low temperatures in thermal oxides. However, when the MOSFETs were warmed up to 295 K after irradiation at 80 K, interface states then formed with approximately the same density as would have been observed for irradiation at 295 K. They concluded that the process of interface state formation is not eliminated at 80 K, but rather is effectively frozen out. Based on the current understanding of interface state formation (two-stage hydrogen models), it seems that the reason why Saks et al. did not observe any interface state formation is because at 80 K the hydrogen ions would be immobile, and therefore incapable of transporting to the interface and reacting to form interface states.

Dunn and Wyatt (6) performed an experiment in which p-channel MOSFETs with 37 nm reoxidized nitrided oxides were irradiated using 10 keV X-rays at room temperature. These devices exhibited only a -1.45 V shift in the midgap voltage after irradiation up to 55  $Mrad(SiO_2)$ . Furthermore, no change in subthreshold slope was measured, even at this extremely high dose. This indicates that the interface state generation was completely suppressed in the reoxidized nitrided oxides.

Terry et al. (7) exposed nitrided oxide devices to 1.5 MeV electrons up to a total dose of 1 Mrad(Si) at room temperature. They did observe a very small distortion of the capacitance-voltage curve at 1 Mrad(Si). This is attributed to a very small buildup of interface states. They suggested that the suppression of interface state generation in the nitrided oxides may be related to the buildup of nitrogen near the insulator-silicon interface.

Bhat and Vasi (5) irradiated reoxidized nitrided oxide MOS capacitors at room temperature with a  $^{60}$ Co source at a dose rate of 380 krad(Si)/hr up to 2.2 Mrad(Si). They observed very little interface state generation even at such high dose levels. They suggest that this implies that hydrogen does not play a role in interface state generation in RNO and the transport of H<sup>+</sup> ions is inhibited due to the oxynitride layer near the Si-SiO<sub>2</sub> interface. They conclude that the major interface state component in thermal oxides (H<sup>+</sup> transport) is suppressed in RNO and the small buildup is due to trapped hole recombination. Trapped hole recombination suggests that radiation-generated holes get trapped near the Si-oxide interface and are converted into interface traps by electron injection. Electrons tunnel from the substrate to annihilate the trapped holes producing a structural change at the interface and resulting in a weak or dangling silicon bond that acts as the interface trap (36; 39).

#### III. Theory

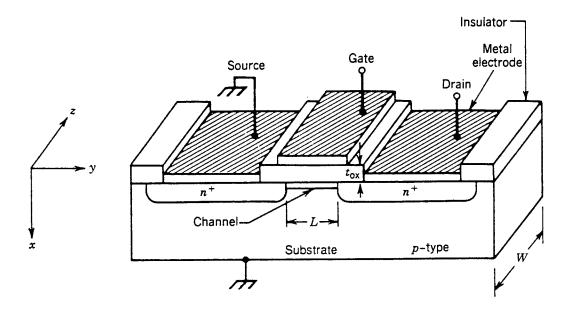

MOSFETs are unipolar devices since current is transported predominately by carriers of one polarity only, holes in a p-channel device and electrons in an n-channel device. The MOSFET consists of a silicon substrate, an insulator (gate oxide) region, and a conducting gate. It is a four terminal device with an n-channel device consisting of a p-type semiconductor substrate terminal, source and drain terminals which are heavily doped  $n^+$  regions, and a gate terminal. The gate is formed by placing a metal contact onto the insulator. Heavily doped polysilicon can be used instead of a metal to form the gate. Figure 3-1 is an example of a n-channel device. A p-channel device would consist of a n-type semiconductor substrate with the source and drain being heavily doped  $p^+$  regions. This chapter provides a description of the different types of MOSFETs, threshold voltage, MOSFET operation, transconductance, ionizing radiation, total dose effects on MOSFETs, bias effects, and concepts involving different oxide processes.

#### 3.1 Types of MOSFETs

There are basically four types of MOSFETs. There are n-channel enhancement mode and depletion mode devices as well as p-channel enhancement and depletion mode devices. In the enhancement modes the semiconductor substrate is not inverted directly under the oxide with zero applied gate voltage. In the depletion modes the substrate is inverted directly under the oxide for zero applied gate voltage.

Figure 3-1. Cross-section of a simplified n-channel MOSFET showing the basic elements (14:4).

For the n-channel enhancement (normally off) MOSFET a positive gate voltage induces an electron inversion layer, which forms the channel between the n-type source and drain regions. In an n-channel device the electrons will flow from the source to the drain region. If an n-channel exists at zero gate bias then a negative bias must be applied to the gate in order to deplete carriers in the channel, reducing the channel conductance. This is the n-channel depletion (normally on) MOSFET. The n-channel can be an electron inversion layer or an intentionally doped n-region. In the p-channel enhancement mode MOSFET a negative gate voltage needs to be applied to create an inversion layer of holes which forms the channel between the p-type source and drain regions. A positive gate voltage is needed to "turn off" the p-channel depletion mode device since a p-channel exists for zero gate voltage. Holes flow from the source to the drain in a p-channel device.

In an n-channel device the concentration of electrons in the channel increases with increasing gate voltage so the magnitude of the current for a given drain voltage can therefore be modulated by changing the gate voltage. A p-channel device is similar except the concentration of holes in the channel increases with a negative increase in voltage. The gate voltage that is required to cause appreciable current to flow is called the threshold voltage and is described next.

#### 3.2 Threshold Voltage

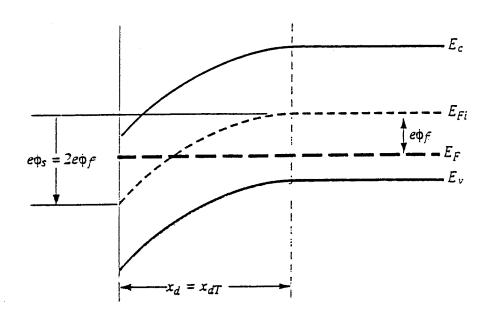

In order to understand the threshold voltage consider a p-type semiconductor substrate where a positive gate voltage is applied. An energy band diagram of such a device is shown in Figure 3-2. The surface of such a device has been inverted from a p-type to an n-type region so that there is an inversion layer of electrons at the oxide-semiconductor interface.  $E_{Fi}$  is the intrinsic Fermi level and  $E_F$  is the Fermi level.  $E_c$  is the conduction band energy and  $E_v$  is the valence band energy.  $\phi_s$  is the surface potential and is the difference between  $E_{Fi}$  measured in the bulk semiconductor and  $E_{Fi}$  measured at the surface.

Figure 3-2. An energy-band diagram for a p-type semiconductor at threshold inversion (27: 497).

The bulk potential,  $\phi_f$ , is the difference between the intrinsic Fermi level and the Fermi level and is expressed by (27)

$$\phi_f = \frac{kT}{q} \ln\left(\frac{N_a}{n_i}\right) \tag{3-1}$$

$N_a$  is the acceptor doping concentration and  $n_i$  is the intrinsic carrier concentration. The intrinsic carrier concentration is strongly dependent on temperature and is given by (27)

$$n_i^2 = N_C N_V \exp\left[\frac{-E_g}{kT}\right]$$

(3-2)

The Boltzmann constant, k, is  $1.38 \times 10^{23}$  J/K, T is the temperature, and q is the electronic charge.  $E_g$ , the bandgap energy, increases as temperature decreases and is about 1.17 eV at 77 K for silicon (30).  $N_c$  and  $N_v$  are the effective densities of states in the conduction band and valence band respectively. Figure 3-2 shows the case for which  $\phi_s = 2\phi_f$  so that  $E_F$  at the surface is as far above  $E_{Fi}$  as  $E_{Fi}$  is above  $E_F$  in the bulk semiconductor. The concentration of electrons at the surface is the same as the hole concentration in the bulk semiconductor. This condition is known as inversion and the gate voltage that creates this condition is defined as the threshold voltage,  $V_T$ . The threshold voltage can be looked at as being the gate voltage required to cause an appreciable current to flow.

The threshold voltage is a function of several parameters including semiconductor material, oxide material, temperature, and semiconductor doping. The threshold voltage is a very important parameter which must be within the voltage range of a circuit's design. Since the threshold voltage is the point at which the transistor "turns on", any shifts in  $V_T$  could prevent the device from being turned on with the operable circuit

voltages. The equation which represents the threshold voltage is presented here without any derivation. The threshold voltage is expressed by (14; 27)

$$V_T = 2\phi_f + \phi_{ms} + \frac{1}{C_{ox}}(Q_{sd} - Q_{ox} - Q_{ii})$$

(3-3)

where  $Q_{sd} = 2(qN_a \epsilon_s \phi_f)^{1/2}$ , and is the maximum space charge density per unit area of the depletion region,

$\varepsilon_s$  is the permittivity of the semiconductor,

Q<sub>ox</sub> is the trapped oxide charge,

Q<sub>it</sub> is the interface trapped charge, and is discussed in a further section,

$C_{ox} = \varepsilon_{ox}/d_{ox}$  is the oxide capacitance per unit area, where  $\varepsilon_{ox}$  is the permittivity of the oxide and  $d_{ox}$  is the oxide thickness,

and  $\phi_{ms}$  is the metal-semiconductor work function difference.

Positive trapped oxide charge will cause negative shifts in the threshold voltage for both n-channel and p-channel devices, whereas negative trapped oxide charge produces positive threshold voltage shifts. The interface trapped charge can cause either positive or negative shifts in the threshold voltage depending on the type of carrier present in the interface trap. Later sections present a more detailed discussion on both the trapped oxide charge and interface trapped charge and their effects on threshold voltage. The temperature dependence of  $V_T$  mainly arises from the temperature dependence of the

bulk potential which in turn is caused primarily by the strong temperature dependence of the intrinsic carrier concentration. Therefore, the threshold voltage will increase as the temperature of a device decreases since  $\phi_f$  increases as temperature decreases.

#### 3.3 MOSFET Operation

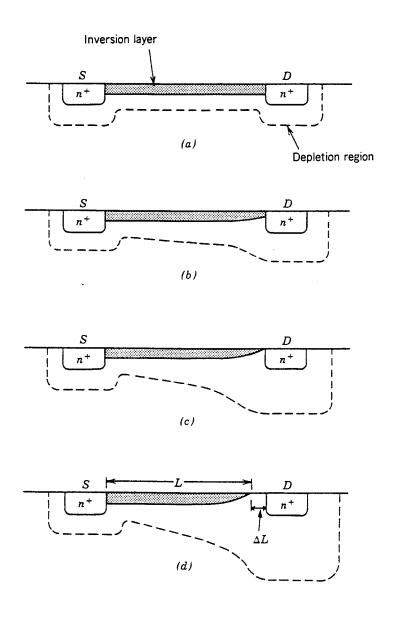

This section describes the basic operation of a MOSFET. To understand the basic operation of a MOSFET an n-channel enhancement mode device is used as an example. When the gate voltage,  $V_G$ , is less than the threshold voltage, the channel region contains very few electrons and many holes. Under these conditions no appreciable current can flow between the source and drain. When the gate is biased so that inversion occurs ( $V_G > V_T$ ), a significant number of mobile electrons are present in the channel region producing a conduction channel for electrons, which connects the source and drain regions. The conduction channel is the gray region in Figure 3-3(a). The number of mobile electrons, and therefore the channel conductance, increase with increasing gate voltage. It is therefore possible to modulate the source-drain conductance by changing the applied gate voltage.

Next look at the effect of drain bias,  $V_D$ , after the inversion channel has been formed. For small applied drain voltages the conduction channel will behave as a simple resistor, so that the drain current,  $I_D$ , will be directly proportional to  $V_D$ . This is called

3-7

the linear region of operation. As  $V_D$  is increased the potential drop along the channel due to the channel current starts to negate the inverting effect of the gate which means

Figure 3-3. Diagram of an n-channel MOSFET showing the conduction channel after the device is turned on: (a)  $V_D = 0$ ; (b)  $V_{Dsat} > V_D > 0$ ; (c)  $V_D = V_{Dsat}$ ; (d)  $V_D > V_{Dsat}$  (14:24).

that the induced inversion charge density near the drain also decreases. Therefore the inverted channel narrows near the drain and the number of channel electrons decreases as shown in Figure 3-3(b). In addition, the conductance of the channel at the drain decreases which means that the slope of the  $I_D$ - $V_D$  curve will decrease. The greatest increase in the depletion region width, which corresponds to the greatest decrease in number of channel electrons, occurs near the drain terminal. When  $V_D$  increases to the point where the potential drop across the oxide at the drain terminal is equal to  $V_{T}$ , the induced channel inversion charge is zero at the drain terminal. This is referred to as "pinch off" because the normal conduction channel disappears next to the drain, this is shown in Figure 3-3(c). When the channel pinches off, current saturation occurs so that the slope of the  $I_D$ - $V_D$  curve is approximately zero. This region is referred to as the saturation region. For drain voltages greater than the pinch off voltage,  $V_{Dsat}$ , the pinched-off portion off the channel widens from just a point into a depleted channel section,  $\Delta L$ , and the drain voltage in excess of  $V_{Dsat}$  is absorbed almost entirely across  $\Delta L$ , as shown in Figure 3-3(d). Electrons will enter the channel at the source, travel through the channel to the point where the charge goes to zero and then get injected into the depleted region where they are swept by the electric field to the drain.

## 3.4 Transconductance

The transconductance, gm, is the change in drain current with respect to the corresponding change in gate voltage and is given as

$$gm = \frac{\partial I_D}{\partial V_G} \tag{3-4}$$

The transconductance is also referred to as the transistor gain.

For an n-channel MOSFET operating in the nonsaturation region we have (28)

$$gm = \mu_n C_{ox} \frac{W}{L} V_D \tag{3-5}$$

The transconductance in the saturation region is given by (28)

$$gm = \mu_n C_{ox} \frac{W}{L} (V_G - V_T)$$

(3-6)

Where W and L are the channel width and channel length respectively. It is observed from the above equations that the transconductance is proportional to the effective carrier mobility,  $\mu_n$ , in the channel. The carrier mobility will vary with applied gate voltage and the temperature. For temperatures down to 77 K, both the electron mobility and hole mobility in silicon will increase as the temperature is lowered (1; 2; 27; 28). This increase in mobility is due to a decrease in phonon scattering as temperature is lowered (27; 28). Since the mobility increases with decreasing temperature the transconductance will also increase as the temperature decreases.

The carrier mobility also depends on the carrier scattering due to oxide and interface charge (14). Ionizing radiation can cause trapped oxide charge and interface state buildup. The interface states cause a distortion, change in slope, in the characteristic  $I_D$ -V<sub>G</sub> curve (14; 27; 29; 30), thus, a change in the transconductance is observed. At 77 K very few, if any, radiation-generated interface states build up at the Si-oxide interface (25; 26; 31; 32), which is discussed in more detail in section 3.6.3. Therefore, at 77 K any change in the transconductance can be attributed to the mobility dependence on carrier scattering due to the radiation-generated trapped charge in the oxide. The next section discusses ionizing radiation, specifically the ionizing radiation resulting from the decay of <sup>60</sup>Co to stable <sup>60</sup>Ni.

#### 3.5 Ionizing Radiation

As a charged particle, such as an alpha or a beta particle, passes through matter it will occasionally approach close enough to an atom (or molecule) for the electrical interaction to be sufficient to completely remove an orbital electron from the atom. This complete removal of an electron from the atom is called ionization. What is left of the atom, after the electron is removed, is a positively charged ion. Therefore, an electron and ion are formed, and the combination of the two particles is called an ion pair. Gamma rays and x-rays do not carry any electrical charge; however, as they pass through matter these rays still cause the ejection of electrons. These ejected electrons are electrically charged and can produce considerable ionization (i.e., create electron/hole pairs).

Ionizing dose from gamma rays, which are produced in the decay of  ${}^{60}$ Co to stable  ${}^{60}$ Ni, can be used to simulate operational environments encountered by MOSFETs. Gamma rays are quanta of electromagnetic radiation with wavelengths ranging from  $10^{-13}$ m to  $10^{-11}$ m (29). Gamma rays occur in a radioactive change when a nucleus is formed in an excited state. The excess energy of this excited nucleus is released as gamma radiation. In the decay of  ${}^{60}$ Co to stable  ${}^{60}$ Ni two gamma rays of 1.17 and 1.33 MeV are released (33; 34).

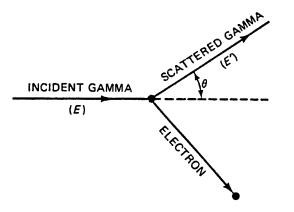

There are three principle ways in which gamma rays interact with an absorbing material. These interactions are; the photoelectric effect, the Compton effect, and pair production. At low energies the photoelectric effect dominates the other interactions. As the photon energy increases the Compton effect becomes the dominate form of interaction. For very high energy gamma rays, minimum of 1.02 MeV, pair production occurs. All three interactions are ionizing processes in that electron/hole pairs are produced. Gamma rays from <sup>60</sup>Co interact with a MOSFET primarily by Compton scatter. This is due to the energy of the gamma rays and the nature of the interacting materials, mostly Si and SiO<sub>2</sub>. Figure 3-4 is a diagram of a Compton interaction. It

3-12

shows a gamma ray making an elastic collision with an electron of the absorbing material. In the collision, part of the energy of the incident gamma ray is transferred to the electron. Another (scattered) gamma ray of lower energy then moves off in a new direction, so that it is scattered from its initial path. Both the recoil electron and scattered gamma ray can produce more ionization. The average energy of the gamma rays from <sup>60</sup>Co is 1.25 MeV and the Compton cross section for these gamma rays in Si and SiO<sub>2</sub> is 0.06 cm<sup>2</sup>/g which is 0.999 of the total interaction cross section (33; 34). In Si and SiO<sub>2</sub>, because of similar cross sections, an equal number of electrons will be produced. The range of these electrons can be several millimeters since it is dependent on the energy of the electron.

Figure 3-4. Diagram showing a Compton Interaction (33).

This section described the ionizing radiation that can be used to simulate the operational environment of MOSFETs. The absorption of this radiation by the MOSFET materials is referred to as the ionizing dose. The next section discusses the total dose effects of this ionizing radiation on MOSFETs operating at cryogenic temperature.

## 3.6 Total Dose Effects

The gate oxide is the most sensitive part of a MOSFET to ionizing radiation. The basic radiation-induced processes are presented in Figure 3-5. In the first process, gamma rays (ionizing radiation) interact with the oxide material producing electron-hole pairs. In the presence of an electric field, either internal or applied, these radiation generated electrons and holes can move through a material. The generated electrons are much more mobile than the holes, and are swept out of the oxide within a few picoseconds. However, a certain fraction of the electrons and holes will recombine within the first picosecond (34). The amount that recombine depends on the applied electric field and on the energy and type of ionizing radiation. The holes which escape this initial recombination are relatively immobile and remain near their point of origin, producing a negative threshold voltage shift. However, over a period of time extending to about one second at room temperature and to tens of thousands of seconds at cryogenic temperatures, the holes undergo a stochastic hopping transport through the oxide in response to any electric field present (9-13).

Figure 3-5. The basic ionizing radiation-induced effects in MOS structures, for a positive applied gate bias (34: 89).

<u>3.6.1 Hole Transport</u>. The second process shown in Figure 3-5 is the transport of the holes, under positive applied bias, to the Si/oxide interface by the hopping transport. This

hole transport is temperature activated and very dispersive in time, and gives rise to a short-term, transient recovery in the voltage shift (9-13). A Continuous Time Random Walk (CTRW) model is used to describe hole transport in the oxide (9-13; 34). The specific intersite charge transfer hopping mechanism is a polaron-like hopping of the holes between localized, energetically shallow trap states having a random spatial distribution (9; 10; 13). Polaron is the term given to the situation in which the charge carrier (in this case a hole) interacts with the lattice, inducing a distortion near the carrier. As the carrier moves through the lattice it carries the distortion with it. The hopping is a phonon-assisted tunneling transition between two localized trap sites.

The radiation response is a function of a disorder parameter,  $\alpha$ , and a characteristic transit time. The disorder parameter, which describes the dispersion, is proportional to the density of localized states and has a value between zero and one (12; 34). The smaller the value of  $\alpha$ , corresponding to a lower density of hopping sites, the more dispersive the transport becomes. The characteristic transit time depends strongly on oxide thickness, temperature, and electric field.

Dispersive charge transport is directly attributed to a wide distribution of transit times of the individual carriers through the material. Some carriers will transit the material very rapidly through a succession of rapid hops, while other carriers are immobilized at some point for relatively long periods of time (10; 12; 13; 34). Dispersive transport is non-Gaussian and has the feature of an apparent time-dependent mobility or a thickness-dependent mobility. As a carrier travels further it has a greater chance of finding itself in a trapping site where the next hop is a relatively far away site, resulting in longer waiting times between hops. These long waiting times are due to the random spatial distribution of the traps. Therefore, the effective mobility of the carriers decreases with time so that the average transit time of carriers through the material varies superlinearly with thickness.

Hole transport is temperature activated, and the activation energy is temperature dependent. There are two distinct temperature regions: a high-temperature region in which the transport is strongly activated, and a low-temperature region in which the transport becomes essentially nonactivated. The transition temperature from activated behavior to nonactivated behavior is given by (34)

$$T_T = \frac{T_D}{v} \tag{3-7}$$

where  $T_D$  is the Debye temperature and is approximately 600 K for SiO<sub>2</sub>, and v is a numerical factor, depending primarily on the phonon spectra of the solid, and is about 4 for SiO<sub>2</sub> (34). Therefore,  $T_T$  is approximately 150 K for SiO<sub>2</sub>. The transition temperature for a given material increases with increasing density of localized sites. Therefore, in SiO<sub>2</sub> at temperatures below 150 K the hole transit time is much greater then transit times above 150 K. Thus, there is very little hole transport below  $T_T$  until extremely long times so that the holes are essentially frozen in place very near their point of origin. Hole transit time is strongly dependent on the electric field strength. At low field strengths the hole transport is relatively long compared to times at high field strengths. At low temperatures holes are relatively immobile unless a large electric filed is present. For example, in SiO<sub>2</sub> at 80 K and for  $E_{ox} = 3$  MV/cm, the transport only begins after about 10 s, but for  $E_{ox} < 2$  MV/cm, essentially very little transport takes place for times on the order of thousands of seconds (13). It has been shown that hole transport is a complex function of several variables including the applied electric field, temperature, and oxide thickness. The next section discusses the trapping of the charge within the oxide.

<u>3.6.2 Trapped Charge</u>. For positive gate voltages the holes move toward the Si-oxide interface where some become captured in long-term trapping sites, while the others flow into the silicon substrate. This long-term trapping of the holes is illustrated as the third process in Figure 3-5. A hole trap is a neutral oxide defect that can capture a hole and retain it for long periods of time. Based on electron spin resonance (ESR) spectroscopy studies, the microscopic structure of the trapped holes has been determined to be the E' center (16-18). The E' center is a trivalent silicon defect associated with an oxygen vacancy in the oxide structure. The Si-oxide interface region is characterized by local strain associated with the sudden change in material composition and the presence of oxygen vacancy defects (strained Si-Si bonds). A hole that encounters a strained bond, may break the bond and recombine with one of the bonding electrons. The resulting

positively charged structure relaxes into the E' center, with one of the silicon atoms retaining the remaining electron from the broken bond.

The radiation generated holes encounter a distribution of hole traps that starts at the Si-oxide interface and extends several nanometers into the oxide (16-18). Up to this point, two types of radiation-induced defects in the oxide (trapped oxide charge and interface traps) have been discussed. Oxide traps that are very close to the interface can transfer charge back and forth from the silicon relatively easily. These near interfacial oxide traps behave like interface traps, and are called border traps (4). For the purpose of this study, border traps are considered to be identical to interface traps, which are addressed in the next section. Depending on the density and the hole capture cross-section of the hole traps a fraction of the holes incident on the trap distribution will be captured. The remainder continue into the Si and eventually recombine. The hole trap densities depend on the oxide and device processing. The efficiency of hole capture by the traps is a function of the electric field in the oxide. The effective hole trap cross section has been observed to vary as the inverse square root of the electric field ( $E^{-1/2}$ ) in the oxide for fields above about 1 MV/cm (34; 35). The trapped holes cause a negative threshold voltage which can last for several hours to years. This effect dominates the other radiation damage processes such as negative charge trapping and interface trap buildup effects. Interface traps, their buildup, and their effect on MOSFETs will be covered in the next section.

Most of the holes which get captured by hole traps within 2 to 5 nm of the silicon are removed by a tunneling process thought to be primarily responsible for the long-term annealing of the threshold voltage shift (4; 14). Electrons from the silicon tunnel to, and recombine with, the trapped holes contained in the distribution of traps near the Si-oxide interface. In addition, electrons which are generated in the oxide, either within the distribution of hole traps or between the distribution and the silicon, are swept through the distribution of traps for positive gate voltages. Some of the electrons will recombine with the trapped holes. This recombination depends on the density of trapped holes and the electron capture cross-section of trapped holes. The radiation generated holes and their long-term trapping produce negative threshold voltage shifts. The electron and trapped hole recombination, and the tunneling process reduce this threshold voltage shift.

For negative applied gate voltages, the radiation generated holes move toward the gate terminal. Now the holes can become trapped near the oxide-metal interface. The trapped charge in this region near the oxide-metal interface has less effect on the threshold voltage. This difference is due to the fact that the threshold voltage shift not only depends on the amount of trapped charge, but also on the location of the charge. The shift in threshold voltage due to oxide charge is (14)

$$\Delta V_T = -\frac{1}{C_{ox}} \int_0^{d_{OX}} \frac{x}{d_{ox}} \rho(x) dx$$

(3-8)

Where x is the distance from the oxide-metal interface to the trapped charge and  $\rho(x)$  is the spatial distribution of the oxide charge density. It needs to be made clear that this trapped charge can be either positive or negative. Trapped charge located near the oxide-metal interface produces a minimum threshold voltage shift where as that same charge placed at the Si-oxide interface produces a maximum threshold voltage shift. In most cases the trapped oxide charge tends to be in the form of a sheet charge (14). For a sheet charge located a distance x from the oxide-metal interface the shift in threshold voltage due to the oxide charge is

$$\Delta V_T = -\frac{x \, Q_{ox}}{d_{ox} \, C_{ox}} \tag{3-9}$$

There are two main reasons why radiation generated electrons usually do not play a significant role in the irradiation response of MOSFETs. First, the electrons are highly mobile in comparison to the holes for all electric fields and temperatures, and therefore are swept out of the oxide very quickly (34). Second, due to the relatively low concentration and small capture cross section of electron traps, the amount of electron trapping in SiO<sub>2</sub> is up to six orders of magnitude less than for hole trapping (34). Therefore, in SiO<sub>2</sub>, the hole trapping will dominate any effects associated with electron trapping. However, in nitrided oxides and reoxidized nitrided oxides, electron trapping can have a significant effect. Radiation-generated holes at low temperatures are immobilized near their point of origin in the oxide bulk. The holes are not trapped at defect sites in the oxide, as is the case for long-term hole trapping observed at room temperature, but are trapped in polaronic states that have a very low effective mobility at low temperatures. It will be pointed out that the term effective mobility is both time and oxide thickness dependent. The holes stay trapped, causing negative  $V_T$  shifts, for minutes to hours. These polaronic hole traps can be emptied by raising the oxide temperature to a level at which the polarons become reasonably mobile or by applying a large electric field.

<u>3.6.3 Interface States</u>. Ionizing radiation can generate additional interface states (or traps) which can lead to shifts in the threshold voltage. The radiation-generated interface traps are shown as the fourth process in Figure 3-5. Interface traps are electronic energy levels located at the Si-oxide interface that can capture or emit electrons (or holes). The electronic levels are due to the lattice mismatch at the interface, disconnected chemical bonds, or impurities (14; 27). The occupancy of the interface traps is determined by Fermi statistics. The net charge of these interface traps is a function of the position of the Fermi level in the bandgap.

The two types of interface traps are donor traps and acceptor traps. A donor trap is an interface trap that is neutral when filled with an electron and positively charged when empty. The donor trap can be looked at as being neutral if the Fermi level is above the state and is positively charged if the Fermi level is below the state. An acceptor trap is negatively charged when filled with an electron and neutral when empty. The acceptor trap is negatively charged if the Fermi level is above the state and is neutral if the Fermi level is below the state. Usually interface traps below the middle of the silicon band gap (midgap) are donor-like and those above are acceptor-like, this point is discussed in more detail later in this section (27; 36).

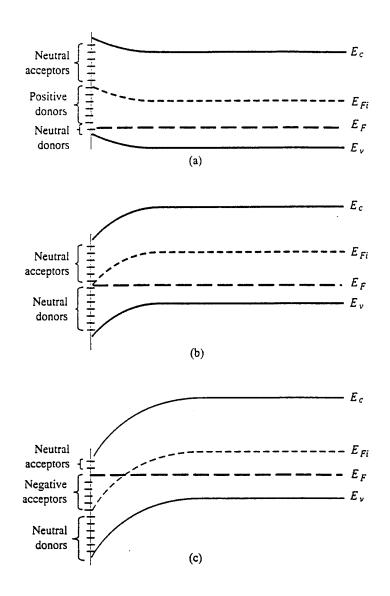

An example of the energy band diagram for a p-type semiconductor in accumulation is shown in Figure 3-6(a). There is a net positive charge trapped in the donor states. As the gate voltage is increased, the Fermi level corresponds to the intrinsic Fermi level at the surface, this is known as the midgap condition. The energy band diagram for the midgap condition is shown in Figure 3-6(b). For the midgap condition all of the interface states are neutral. Figure 3-6(c) shows the energy band diagram for the inversion condition. There is now a net negative charge in the acceptor states. Thus, the charge of the interface state is a function of the applied gate voltage. In other words the charge depends on the energy band bending. The presence of interface states causes the threshold voltage to shift by some amount and direction depending on the gate voltage being applied.

As with the trapped oxide charge defect center, ESR spectroscopy has been used in order to identify the interface trap defect center. Based on ESR spectroscopy studies, the microscopic structure of interface trap defect center has been determined to be the  $P_b$ center (16; 17). The  $P_b$  center is an interface trap defect composed of a trivalent silicon bonded to three silicon atoms at the Si-oxide interface. The  $P_b$  center is similar to the E' center except that the  $P_b$  center is back bonded by three silicon atoms instead of three

Figure 3-6. Energy-band diagram for a p-type semiconductor showing the trapped charge in the interface states when biased (a) in accumulation, (b) at midgap, (c) at inversion (27: 521).

The distribution of  $P_b$  centers is peaked at midgap and decreases toward both the conduction band and valence band edges. In the lower part of the band gap, the  $P_b$  center is a donor-like, positively charged interface state defect. As the Fermi level moves toward midgap, the positively charged  $P_b$  centers accept an electron and become paramagnetic and neutral. As the Fermi level moves from midgap towards the conduction band edge, the  $P_b$  center picks up another electron, becoming negatively charged and again diamagnetic. In the upper part of the band gap the  $P_b$  center is therefore an acceptor-like negatively charged interface state defect. The  $P_b$  center is paramagnetic only when it has an unpaired spin (one electron). Therefore, interface traps below the middle of the silicon band gap are donor-like and those above midgap are acceptor-like.

For an n-channel device the interface traps are predominately acceptor traps since for a positive bias the energy bands will bend down, and the Fermi level will be above several acceptor states. These negatively charged acceptor traps will produce a positive shift in threshold voltage. In the n-channel device the negative charge from the interface traps compensates the positive charge from trapped holes. In a p-channel device the interface traps are predominately donor states. The positively charged donor states will cause a negative shift in the threshold voltage. The positively charged interface traps of a p-channel device add to the positive charge from the trapped holes producing a larger net threshold voltage shift.

3-25

Presently there is uncertainty in exactly how interface traps buildup at the Si-oxide interface. Several models have been proposed over the years with the two most accepted being a hydrogen transport model and a trapped hole recombination model. One common feature among almost all of the models is that they begin with the transport and /or trapping of radiation-generated holes. The hydrogen transport model is described next followed by a description of the trapped hole recombination model.

A two-stage hydrogen model was developed where in the first stage radiation-generated holes react with some hydrogen containing species in the oxide causing the release of hydrogen ions (23; 36-38). This first stage determines the saturated value of interface traps and occurs during the period of charge generation and hole transport through the oxide. Then, in the second stage, the liberated  $H^+$  ions undergo a dispersive hopping transport, similar to the hole transport previously described, which controls the rate of interface formation. The  $H^+$  ions that reach the interface can react to form interface traps. It is almost certain that  $H^+$  is the ion causing interface buildup, but the nature of the hydrogen containing species in the oxide, the chemical reaction which produces the  $H^+$ , and the resulting spatial distribution of the  $H^+$  ions through the oxide, are all uncertain.

Once the  $H^+$  ions have reached the interface they can react with H-Si trap precursors and electrons from the substrate to produce silicon dangling bonds (interface traps) and neutral H<sub>2</sub>. This reaction is given by (38)

$$H^+ + e^- + H - Si \equiv Si \longrightarrow H_2 + \bullet Si \equiv Si$$

(3-10)

where  $H - Si \equiv Si$  is a silicon atom bonded to a hydrogen atom and back bonded to three silicon atoms, and  $\bullet Si \equiv Si$  represents a silicon atom with a dangling bond back bonded to three silicon atoms.

This two stage hydrogen transport model is believed to be the main process for radiation-induced interface state buildup, where the first stage determines the saturated value of the traps and the hopping transport of  $H^+$  ions (second stage) determines the time scale of interface state buildup. In the previously described hydrogen transport model  $H^+$  ions were released as holes transport through the oxide. In this model, an increase in electric field increases the energy a hole imparts to the oxide lattice as it transports through the oxide, causing more  $H^+$  to be released. This would produce more interface traps with increasing field. This increase is true up to a point and then the interface trap buildup follows an approximate  $E^{-1/2}$  field dependence (24; 35).

A model to account for this field dependence is a hole-trapping/hydrogen transport  $(HT)^2$  model (35). In this model the number of holes trapped determines the total number of interface traps (i.e. the saturated value) that buildup at a given electric field. Because the number of holes trapped scales as  $E^{-1/2}$ , the saturated value of interface trap buildup will follow the same field dependence. This model involves, for positive gate bias, hole trapping near the Si-oxide interface, and the release of H<sup>+</sup> ions near the interface. The H<sup>+</sup> ions transport to the interface and react according to Equation (3-10) to form interface traps. In the  $(HT)^2$  model,  $H^+$  transport is the rate limiting process.

The trapped hole recombination models suggest that radiation-generated holes get trapped near the Si-oxide interface and are converted into interface traps by electron injection. It is proposed that electrons tunnel from the substrate to annihilate the trapped holes producing a structural change at the interface and resulting in a weak or dangling silicon bond that acts as the interface trap (36; 39). In this model the conversion of trapped holes to interface traps is the rate limiting step. The temperature effects of interface state buildup will be covered next.

The formation of interface traps depends on the transport and/or trapping of holes as well as the transport of  $H^+$  through the oxide. At low temperatures the holes and  $H^+$ ions will be immobile due to the nature of their transport. Therefore, at low temperatures the buildup of interface states is greatly restricted. As the temperature is raised, some of the holes and  $H^+$  ions will become thermally detrapped. It is only after this detrapping occurs that any significant interface traps will buildup.