9

JHU/APL TG 1386 SEPTEMBER 1994

# Technical Memorandum

# PROCEEDINGS OF THE FOURTH SYSTEMS REENGINEERING TECHNOLOGY WORKSHOP

BRUCE I. BLUM, editor

DTIC QUALITY INSPECTED 2

THE JOHNS HOPKINS UNIVERSITY APPLIED PHYSICS LABORATORY

Approved for public release; distribution is unlimited.

JHU/APL TG 1386 SEPTEMBER 1994

# Technical Memorandum

# PROCEEDINGS OF THE FOURTH SYSTEMS REENGINEERING TECHNOLOGY WORKSHOP

Monterey Marriot Hotel Monterey, California February 8–10, 1994

**BRUCE I. BLUM, editor**

Sponsored by NAVAL SURFACE WARFARE CENTER DAHLGREN DIVISION-WHITE OAK DETACHMENT

Silver Spring, MD 20903-5640

With the Cooperation of JOHNS HOPKINS UNIVERSITY APPLIED PHYSICS LABORATORY

Laurel, MD 20723-6099

Approved for public release; distribution is unlimited.

The Systems Reengineering Technology Workshop is sponsored by the Navy Surface Warfare Center, Dahlgren Division, as part of the Complex Systems Engineering Block Program. The organizers of this workshop wish to express their appreciation to CDR Grace Thompson and Dr. Harry Crisp for their continuing guidance and assistance. Mr. Blum is supported by ONR tasks under contract N00039-91-C-0001 with SPAWAR.

# UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                              |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------|--------------------------------------|-----------------------------------------|----------------------|-------------|------------------------------|

| 1a. REPORT SECURITY CLASSIFICATION<br>UNCLASSIFIED                                                                                                                                                                                     |                                                                                                                                                                                                                                    |                     | 1b. RESTRICTIVE           | MARKINGS                             |                                         |                      |             |                              |

| 28.                                                                                                                                                                                                                                    | 28. SECURITY CLASSIFICATION AUTHORITY                                                                                                                                                                                              |                     |                           | 3. DISTRIBUTION                      | AVAILABILITY OF RE                      | PORT                 |             |                              |

| 2b.                                                                                                                                                                                                                                    | DECLASSIFIC                                                                                                                                                                                                                        | ATION/DOWNGR        | ADING SCHEDULE            | <u> </u>                             | Approved for                            | r public release; c  | listributi  | on unlimited                 |

| 4.                                                                                                                                                                                                                                     | PERFORMING                                                                                                                                                                                                                         | ORGANIZATION        | REPORT NUMBER(S)          |                                      | 5. MONITORING C                         | RGANIZATION REPO     | ORT NUME    | JER(S)                       |

|                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                  | HU/APL TG-1         | 1386                      |                                      | лп                                      | J/APL TG-1386        |             |                              |

| 6a.                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    | REALING ORG         |                           | 6b. OFFICE SYMBOL<br>(If applicable) | 78. NAME OF MONITORING ORGANIZATION     |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    | Hopkins Univ        |                           | ,                                    | NAVTECHREP<br>Lourd Mariland            |                      |             |                              |

| 6c.                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    | hysics Laborat      |                           | RCO                                  | To. ADDRESS (City, State, and ZIP Code) |                      |             |                              |

| <b>~</b> ~.                                                                                                                                                                                                                            |                                                                                                                                                                                                                                    | kins Road           | ,                         |                                      | Johns Hopkins Road                      |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    | d. 20723-6099       | )                         |                                      | Laurel, Md.                             |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

| 8a.                                                                                                                                                                                                                                    | NAME OF FUI                                                                                                                                                                                                                        | NDING/SPONSOR<br>DN | IING                      | 8b. OFFICE SYMBOL<br>(If applicable) | 9. PROCUREMEN                           | T INSTRUMENT IDEN    | TIFICATIO   |                              |

|                                                                                                                                                                                                                                        | Naval Sur                                                                                                                                                                                                                          | face Warfare (      | Center                    |                                      | N00039-91-0                             | 2-0001               |             |                              |

| 8c.                                                                                                                                                                                                                                    | ADDRESS (C                                                                                                                                                                                                                         | ty, State. and ZIP  | Code)                     |                                      | 10. SOURCE OF FU                        |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |                     |                           |                                      | PROGRAM<br>ELEMENT NO.                  | PROJECT<br>NO.       | TASK<br>NO. | WORK UNIT                    |

|                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                  |                     | ite Oak Detachme          | nt                                   |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    | ing, MD 2090        |                           |                                      | l                                       |                      |             |                              |

| 11.                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    | Security Classific  | 200m)                     |                                      |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        | Proceedin                                                                                                                                                                                                                          | gs of the Fourt     | th Systems Reengi         | neering Technology Wo                | rkshop (U)                              |                      |             |                              |

| 12.                                                                                                                                                                                                                                    | PERSONAL A                                                                                                                                                                                                                         |                     |                           |                                      |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        | Bruce I. B                                                                                                                                                                                                                         | lum. editor         |                           |                                      |                                         |                      |             |                              |

| 13a                                                                                                                                                                                                                                    | . TYPE OF REP                                                                                                                                                                                                                      | ORT                 | 13b. TIME CO              | VERED                                | 14. DATE OF REPO                        | RT (Year, Month, Day | ) 18        | 5. PAGE COUNT                |

|                                                                                                                                                                                                                                        | Technical                                                                                                                                                                                                                          | Memorandum          | FROM                      | TO                                   | September 19                            | 94                   |             | 410                          |

| 16.                                                                                                                                                                                                                                    | SUPPLEMENT                                                                                                                                                                                                                         | TARY NOTATION       |                           |                                      |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        | Presented                                                                                                                                                                                                                          | at Fourth Syst      | ems Reengineering         | g Technology Workshop                | , Monterey, Calif.                      | , 8-10 Feb. 1994     |             |                              |

| 17.                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    | COSATI CODES        |                           | 18. SUBJECT TERMS (Con               |                                         |                      | block numt  | hert                         |

|                                                                                                                                                                                                                                        | FIELD                                                                                                                                                                                                                              | GROUP               | SUB-GROUP                 | -                                    |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |                     |                           | Reengineering                        | Software re                             | engineering          |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |                     |                           | Systems reengineeri                  | ng                                      |                      |             |                              |

| 19.                                                                                                                                                                                                                                    | ABSTRACT (C                                                                                                                                                                                                                        | Continue on reverse | e if necessary and identi | ity by block number)                 |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |                     |                           | ces in the development of            |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |                     |                           | ments. However, many o               |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        | gies that do not support modern hardware and software engineering methodologies or maintenance strategies. Conse-<br>quently, system modification has become increasingly complex. To reduce the complexity, developers can employ |                     |                           |                                      |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

| reengineering techniques to create new systems. This report contains the papers presented at the Fourth Systems<br>Reengineering Technology Workshop sponsored by the Naval Surface Warfare Center. The papers discuss theoretical and |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

| applied techniques that can be used to facilitate systems reengineering efforts. Specific topics include design issues in                                                                                                              |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

| systems reengineering, reuse in reengineering and forward engineering, experience reports, reengineering translation and                                                                                                               |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

| transformation, evaluating a reengineering project, tools for reengineering, engineering science and reengineering, the                                                                                                                |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

| impact of object orientation, and approaches to reengineering.                                                                                                                                                                         |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

| 20. DISTRIBUTION/AVAILABILITY OF ABSTRACT 21. ABSTRACT SECURITY CLASSIFICATION                                                                                                                                                         |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    | FIED/UNLIMITED      |                           |                                      |                                         | ASSIFIED             |             | 0.000.000                    |

| 22a                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    | SPONSIBLE INDIN     |                           |                                      | 22b. TELEPHONE (<br>(301) 953-54        |                      |             | . OFFICE SYMBOL<br>AVTECHREP |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    | REP Security        | Unicer                    |                                      | (3017933-34                             |                      | 1 14/       |                              |

| D                                                                                                                                                                                                                                      | FORM 14                                                                                                                                                                                                                            | 73, 84 MAR          | 83 A                      | PR edition may be used until ex      |                                         | SE                   | CURITY C    | LASSIFICATION OF THIS PAGE   |

|                                                                                                                                                                                                                                        | All other editions are obsolete. UNCLASSIFIED                                                                                                                                                                                      |                     |                           |                                      |                                         |                      |             |                              |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |                     |                           |                                      |                                         |                      |             |                              |

The Johns Hopkins University

Applied Physics Laboratory Laurel, Maryland 20723-6099

## ABSTRACT

The Navy has invested significant resources in the development of large and complex systems that must be modified and extended to respond to changing requirements. However, many of these systems are based on archaic automation technologies that do not support modern hardware and software engineering methodologies or maintenance strategies. Consequently, system modification has become increasingly complex. To reduce the complexity, developers can employ reengineering techniques to create new systems. This report contains the papers presented at the Fourth Systems Reengineering Technology Workshop sponsored by the Naval Surface Warfare Center. The papers discuss theoretical and applied techniques that can be used to facilitate systems reengineering efforts. Specific topics include design issues in systems reengineering translation and transformation, evaluating a reengineering project, tools for reengineering, engineering science and reengineering, the impact of object orientation, and approaches to reengineering.

| Acces                | ion For                |    |  |  |

|----------------------|------------------------|----|--|--|

| NTIS CRA&I           |                        |    |  |  |

| By<br>Dist.ib.ition/ |                        |    |  |  |

| Availability Codes   |                        |    |  |  |

| Dist                 | Avail (1.d)<br>Special | or |  |  |

| A-1                  |                        |    |  |  |

# Foreword

This is the fourth of a series annual workshops sponsored by the Naval Surface Warfare Center (NSWC). These Systems Reengineering Technology Workshops are motivated by the fact that the Navy has invested billions of dollars in the development of systems that may be modified and extended to respond to changing requirements. Systems reengineering technology is necessary if the Navy (as well as the other users of large-scale, complex systems) are to benefit from their extensive investments.

The workshop brings together representatives of government, industry, and academia to address the issues confronting this technology. Although the principal interest of the sponsors is the reegineering of embedded, real-time systems that include hardware, software, and humancomputer interaction, the workshop encourages the participation of all individuals and organizations concerned with the reengineering of large-scale, complex systems.

These participant's proceedings contain the papers accepted for presentation at the workshop. They have been organized to according to the order of the program. The workshop begins with a keynote address by Andrew P. Sage. His paper, "Systems Engineering and Management for Reengineering," provides an introduction to the issues to be discussed during the workshop. The paper is abstracted from *Systems Management for Information Technology and Software Engineering*, which will be published by Wiley later in 1994. This opening paper is complemented by Robert S. Arnold, "A Road Map Guide to Software Reengineering Technology," which is included as an appendix. It is the introduction to R. Arnold (ed.), Software Reengineering, IEEE Computer Science Press, 1993. Thus, this volume begins and ends with two very important surveys that present a conceptual context for reengineering and this workshop.

The papers in the volume have been grouped into units with common themes. The commonality, of course, often is more apparent than real. With the decision not to have parallel sessions and a commitment to accept all the relevant, quality papers that could be accommodated in the time available, the workshop organizers were not always able to focus a session on a central theme. We overcame this difficulty, in part, by structuring some of the workshop sessions as panels rather than paper presentations. In those cases, the papers in these proceedings constitute an extended discussion of concepts that may have been presented only briefly in the workshop.

By the standards of most academic conferences, these proceedings are long. Because the literature on systems (as opposed to software or organizational) reengineering is sparse, we elected not to place any page limits on the papers. Thus, the papers are as long (or short) as they needed to be to convey what the authors believe is important. As the organizers of this workshop, we hope that those who read these proceedings will concur with this decision.

Mark Wilson, Workshop Chair Bruce Blum, Program Co-Chair Gilbert Myers, Program Co-Chair The Johns Hoj  $\mathbb{L}$  is University

Applied Physics Laboratory Lauret Maryland 20723-6099

# Table of Contents

| Foreword iv                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keynote Address                                                                                                                                                                                                                                                      |

| Systems Engineering and Management for Reengineering<br>Andrew P. Sage (George Mason University) 1                                                                                                                                                                   |

| Design Issues in Systems Reengineering                                                                                                                                                                                                                               |

| Design Capture and Optimization Issues for System-Level Reengineering<br>Steven Howell, NgocDung Hoang, Cuong Nguyen (Naval Surface Warfare<br>Center, Dahlgren Division), and Nicholas Karangelen (Trident Systems,<br>Inc.)                                        |

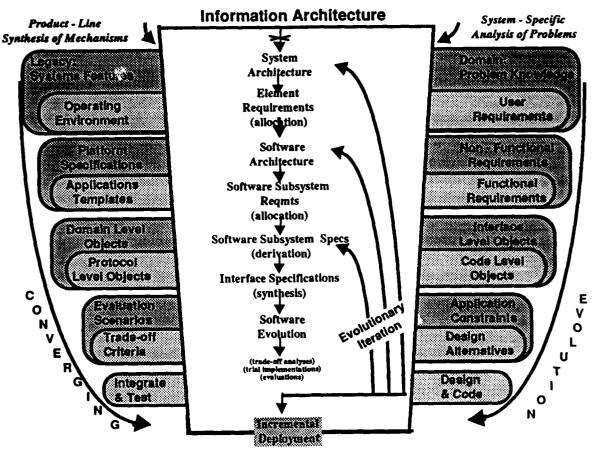

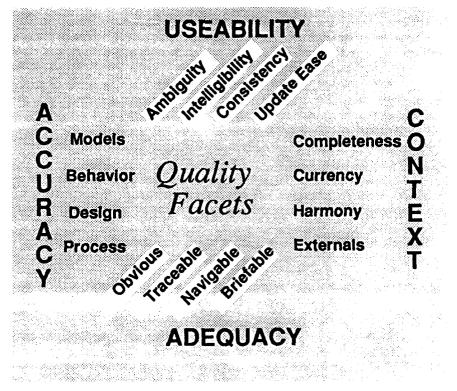

| Information Architecture, An Architectural Basis for Evolution of Large<br>Scale Software Systems<br>John Leary (SEI Washington Office)                                                                                                                              |

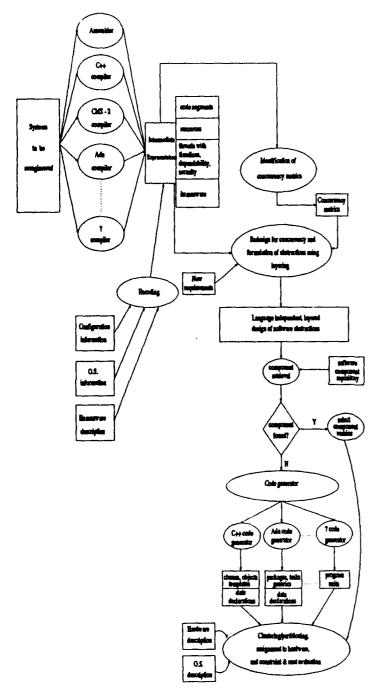

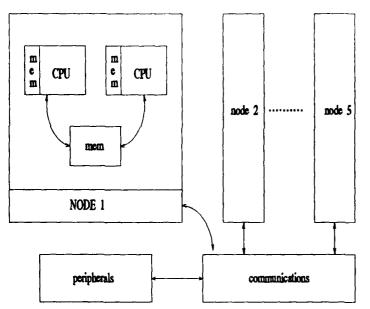

| A Framework for Automated Reengineering of Complex Computer Systems<br>Lonnie R. Welch (NJIT), Antonio L. Samuel, Michael W. Masters, Robert L.<br>Harrison (Naval Surface Warfare Center, Dahlgren Division), Alexander D.<br>Stoyenko (NJIT), and Joe Caruso (CSC) |

| Dynamic (Re)Generation of Software Documentation<br>W. Lewis Johnson (USC/Information Sciences Institute)                                                                                                                                                            |

| Reuse in Reengineering and Forward Engineering                                                                                                                                                                                                                       |

| A Case Study of Software Reuse in Vertical Domain<br>Vaclav Rajlich and João Silva (Wayne State University)                                                                                                                                                          |

| Reengineering to Increase Maintainability and Enable Reuse<br>Grady H. Campbell, Jr. (Software Productivity Consortium)                                                                                                                                              |

| A Reuse Approach to Computer-Assisted Software Reengineering<br>Daniel E. Wilkening, Joseph P. Loyall (TASC), Marc J. Pitarys, and<br>Kenneth Littlejohn (USAF Wright Laboratory)                                                                                    |

| Formal Specification and Software Reuse in Reengineering Embedded<br>Real-Time Systems<br>Farnam Jahanian (University of Michigan)                                                                                                                                   |

# **Experience Reports and Discussion (Panel)**

| <ul> <li>MK 86/UYK-7 Enhanced Memory Unit Project: Jacking the Computer Up and</li> <li>Putting a Powerful Engine Under it!</li> <li>Joe S. Ganes, Richard W. Williams and Jay Roske (Naval Surface</li> <li>Warfare Center, Crane Division)</li></ul>                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

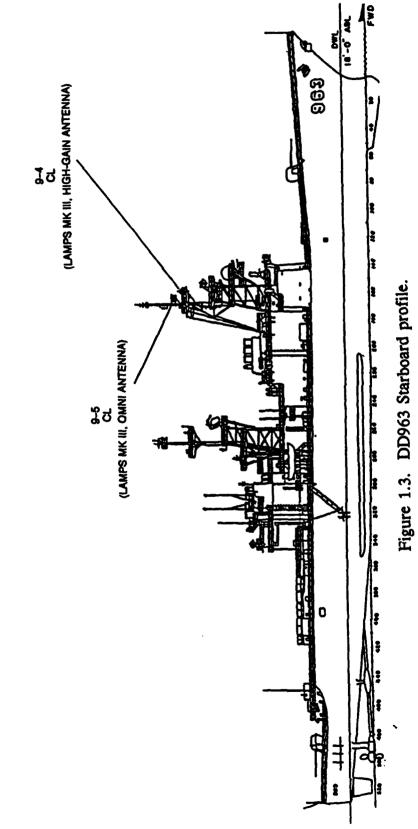

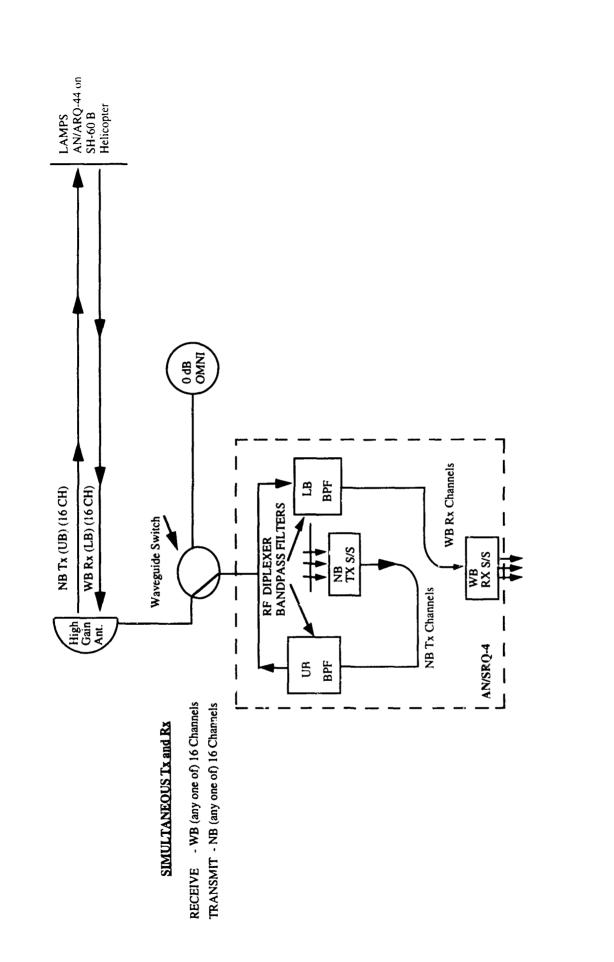

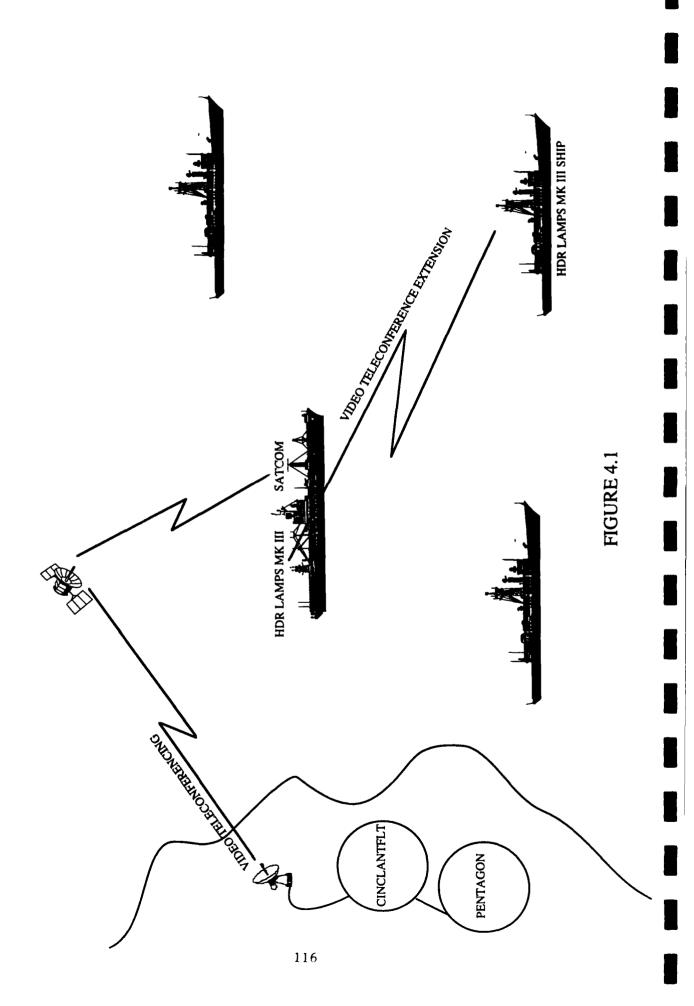

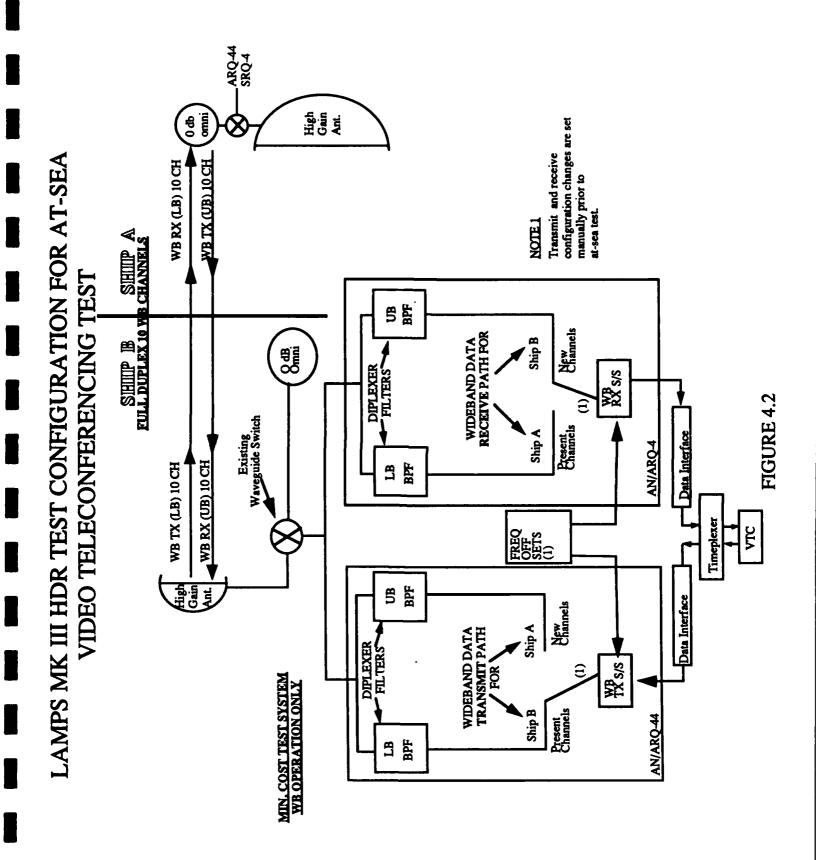

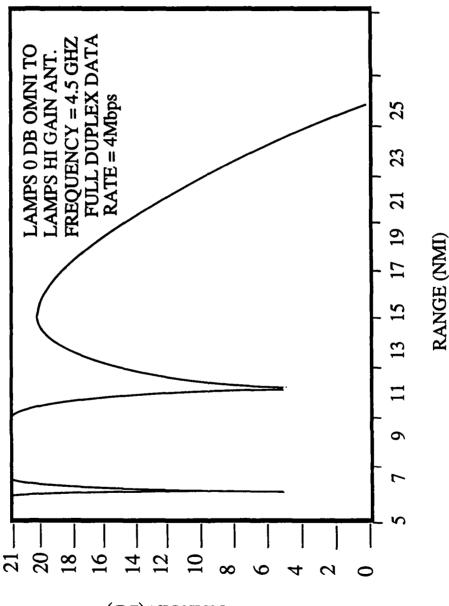

| Reengineering the LAMPS Mark III to Provide a LOS Ship-to-ship<br>Teleconferencing Mode<br>James P. Rahilly (Naval Command, Control and Ocean Surveillance Center) 107                                                                                                                                                                                                |

| A Successful Process Improvement Effort Using Cleanroom Software Engineering<br>S. Wayne Sherer (AMCCOM LCSEC), Paul Arnold (IBM), and Ara<br>Kouchakdjian (SET),                                                                                                                                                                                                     |

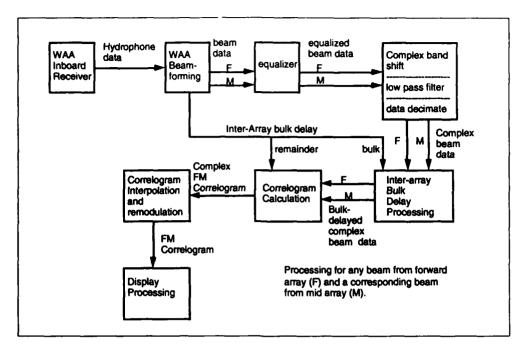

| Design Capture Views Applied to the WAA System<br>Daniel J. Organ (Naval Undersea Warfare Center, Newport Division)                                                                                                                                                                                                                                                   |

| <b>Reengineering Translation and Transformation (Panel)</b>                                                                                                                                                                                                                                                                                                           |

| Translating CMS-2 to Ada<br>Charles H. Sampson (Computer Sciences Corporation)                                                                                                                                                                                                                                                                                        |

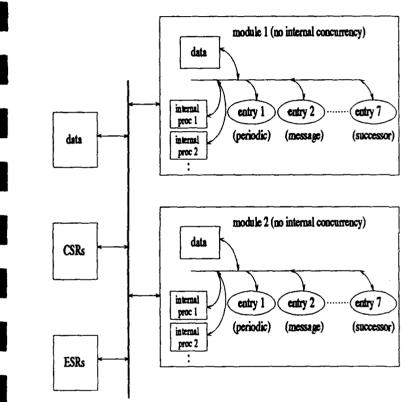

| Reengineering Concurrent Software Into Ada<br>Noah Prywes, Giorgio Ingargiola, Insup Lee, and Moon Lee<br>(Computer Command and Control Company)                                                                                                                                                                                                                      |

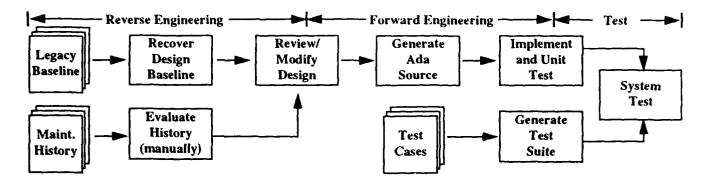

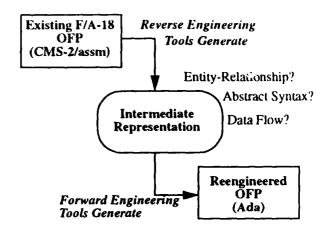

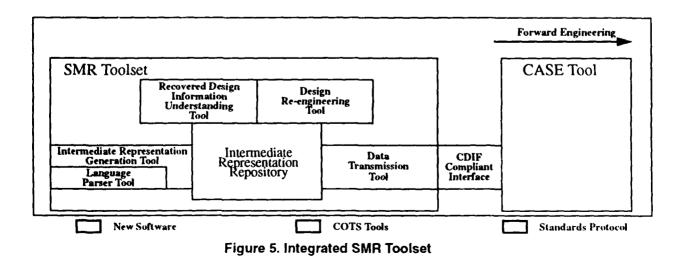

| Software Migration and Reengineering (SMR): A Pilot Project in Reengineering<br>Stephen R. Mackey (MCC) and Lynn M. Meredith (Computing Devices<br>International)                                                                                                                                                                                                     |

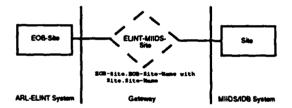

| Reverse Engineering Complex Databases to Support Data Fusion<br>R. D. Semmel (Applied Physics Laboratory) and R. Winkler (U. S.<br>Army Research Laboratory)                                                                                                                                                                                                          |

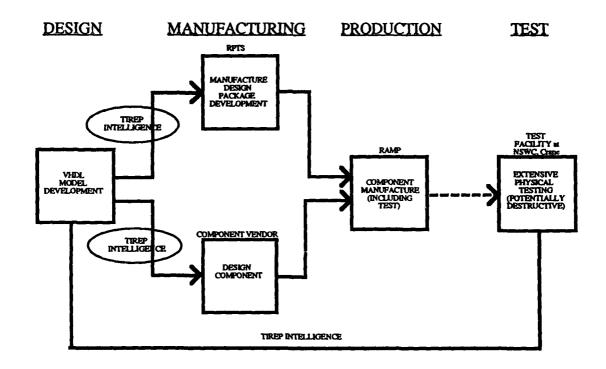

| <ul> <li>VHDL Board-Level Modeling To Expedite Redesign</li> <li>L. J. Ceder (Naval Research Laboratory), Charles Rogers, Louie Kitcoff,</li> <li>James Michaud (Naval Air Warfare Center, Aircraft Division), John Miles,</li> <li>Gary Hout, Ed Woods, Darin York (Naval Surface Warfare Center, Crane</li> <li>Division), and Peter Everitt (CACI, Inc.)</li></ul> |

# **Evaluating a Reengineering Project**

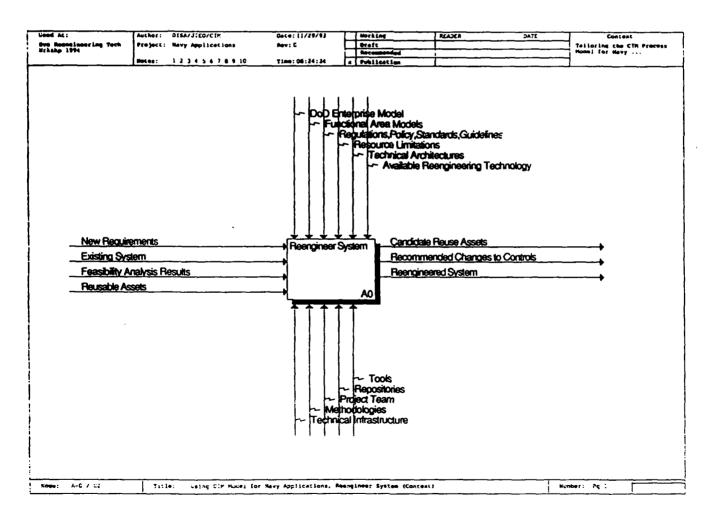

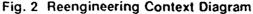

| Using the CIM Reengineering Process Model in National States and S | vy Reengineering Efforts |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Tamra Moore (Defense Information Systems Age                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ency) 205                |

Reengineering Assessment Handbook (MIL-HDBK-SRAH)

| The | lohns | Hopkins | University |

|-----|-------|---------|------------|

|     | 10    |         | ••••••     |

| John Clark, Barry Stevens (COMPTEK Federal Systems), John Donald<br>(Air Force Cost Analysis Agency), and Sherry Stukes (Management<br>Consulting & Research, Inc.)                           | 16  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| System Reengineering Evaluation: A Design Dependent Parameter Approach<br>Wolter J. Fabrycky (Virginia Polytechnic Institute and State University)2                                           | 24  |

| Metrics for Reengineering of Software Systems<br>Annette R. Ashton and William H. Farr (Naval Surface Warfare Center,<br>Dahlgren Division)                                                   | .34 |

| Tools for Reengineering                                                                                                                                                                       |     |

| Customized Software Evaluation Tools: Application of an Enabling Technology<br>for Reengineering<br>Lawrence Markosian, Russell Brand, and Gordon Kotik<br>(Reasoning Systems, Inc.)          | 48  |

| Using Design Knowledge to Extract Real-Time Task Models<br>Lester Holzblatt, Richard Piazza, Howard Reubenstein, and Susan Roberts<br>(The MITRE Corporation)                                 | 56  |

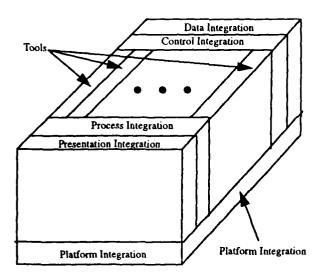

| Maintenance Process Reengineering: Toward a New Generation of CASE Technology<br>Judith Ahrens, Noah Prywes, and Evan Lock (Computer Command and<br>Control Company)                          | 63  |

| A Syntax-Directed Tool for Program Understanding and Transformation<br>William G. Griswold and Darren C. Atkinson (University of California,<br>San Diego)                                    | .74 |

| Engineering Science and Reengineering                                                                                                                                                         |     |

| Software Reengineering in the SF Framework<br>A. T. Berztiss (University of Pittsburgh) 2                                                                                                     | 83  |

| Efficient Methods for Validating Timing Constraints in Multiprocessor and<br>Distributed Systems<br>Jane W. S. Liu and Rhan Ha (University of Illinois)                                       | 292 |

| Massively Parallel Systems Design for Real-Time Embedded Applications<br>Thomas C. Choinski (Naval Undersea Warfare Center, Newport Division) and<br>Chin-Hwa Lee (Naval Postgraduate School) |     |

| Knowledge-Based, Metalanguage-Based Object Abstraction for Automatic                                                                                                                          |     |

| The | Johns | Hopkins | University |

|-----|-------|---------|------------|

|-----|-------|---------|------------|

# The Impact of an Object Orientation

| Iss  | ues in Re-engineering from Procedural to Object-Oriented Code<br>Ricky E. Sward and Robert A. Steigerwald (USAF Academy)                                                               |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

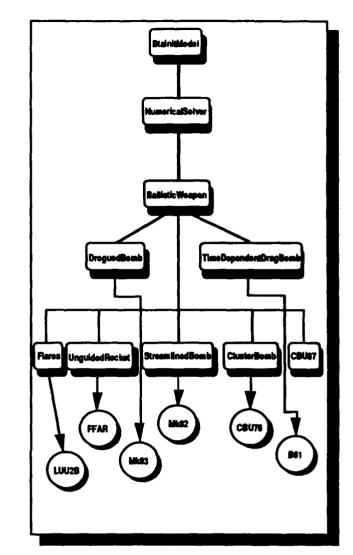

| Aı   | n Object-Based Framework for Reengineering Avionics Software<br>Noble N. Nkwocha and John J. Zenor (Naval Air Warfare Center Weapons<br>Division)                                      |

| Ar   | n Object-Oriented Paradigm for Reengineering Complex Real-Time Systems<br>Kwei-Jay Lin (University of California, Irvine)                                                              |

| Аррг | roaches to Reengineering (Panel)                                                                                                                                                       |

| Th   | e Next Generation Computer Resources Program: Strategic Direction<br>Rex Buddenberg (Naval Postgraduate School)                                                                        |

| Re   | euse-based Reengineering: Notes From the Underground<br>Frank Svoboda (Unisys Government Systems Group)                                                                                |

|      | eengineering as an Engineering Problem: Conceptual Framework and<br>oplication to Community Problems<br>Peter Feiler, Walt Lamia, and Dennis Smith (Software Engineering<br>Institute) |

| Re   | arrent STSC Reengineering Projects: MIL-HDBK-RAH Application Findings,<br>eengineering Project Planning <sup>D</sup> rocess, and STSC Reengineering Survey<br>esults                   |

# Appendix

| A Road Map Guide to Software Reengineering Technology (From R. Arnold (ed.), Software Reengineering, IEEE CS Press, 1993, reprinted with permission.) |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Robert Arnold (SEVTEC)                                                                                                                                | 381 |

| Author Index                                                                                                                                          | 401 |

Michael R. Olsem (SAIC) and Chris Sittenauer (USAF Software Technology

# Systems Engineering and Management for Reengineering

Andrew P. Sage

School of Information Technology and Engineering George Mason University Fairfax, VA 22030-4444

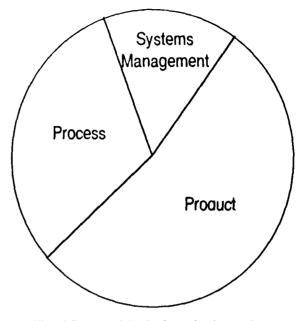

Abstract This paper presents and overview and perspective on systems engineering and systems management for reengineering and related approaches towards organizational and technology revitalization. As we will see, there are at least three types of reengineering that can be considered: reengineering at the levels of product, process, and systems management. We claim that all three are generally needed and an approach at one level only may not be satisfactory.

#### L INTRODUCTION

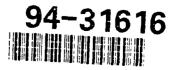

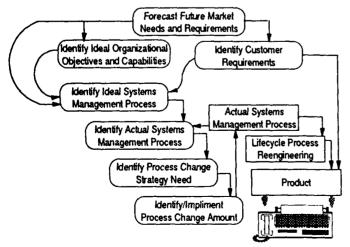

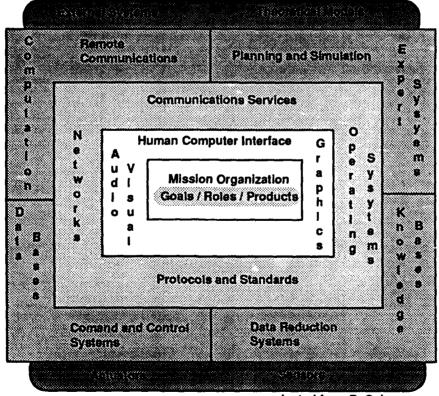

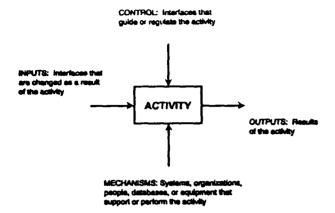

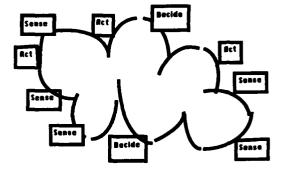

Responsiveness is very clearly a critical need today. By this, we mean of course, organizational responsiveness in providing products and services of demonstrable value to customers, and thereby to the organizations own stakeholders. This must be accomplished by efficiently and effectively employing leadership and empowered people, such that systems management strategies, organizational processes, human resources, and appropriate technologies are brought to bear on the production of high quality and trustworthy goods and services. We also mean responsiveness in supplying appropriate technologies and systems to meet these objectives. Figure 1 illustrates these ingredients and some of their linkages in the production of products and services. It is a composite representations that indicates some of the many ingredients responsible for trustworthy and high quality products.

Many recent papers [1] have indicated the need for continual revitalization in the way in which we do things, such that they are always done better. This is the case, even if the external environment were static and unchanging. However, when we are in a period of high velocity environments, then continual organizational change and associated change in processes and product must be considered as a fundamental rule of the game for progress.

In many ways, past progress can act to impede future progress. This is especially the case when we become very accustomed to a particular way of doing things, and have allowed a very large overhead situation to accumulate around what were once highly successful efforts at the production of quality products and services. It is especially difficult to change when what we are doing now is done very well. Yet, it is entirely possible that a competitor may be able to do it better, in any of a number of ways. Also, what we do well now may well not be what we will need to be doing in the future.

In many if not most cases, improvement needs come about not because of human inattention to the tasks they perform. Rather, and more often than not, it suggests that the tasks themselves are in need of restudy and renovation. These tasks may be strategic in nature, or they may be tactical, or they may be purely operational. Most often, however, attempts at improvement through attention at only operational levels will yield very modest improvements for the effort invested. As many have indicated, *it is the* (strategic and tactical, and not the operational) system that is at fault.

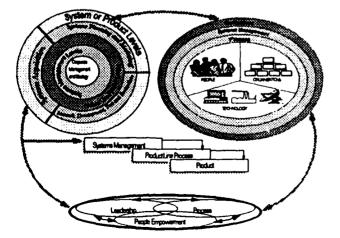

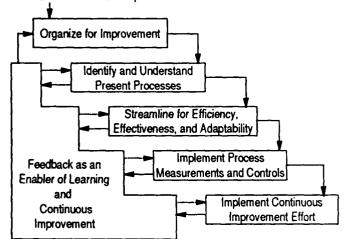

Figure 2 indicates some improvement approaches, each of which relate to reengineering. They are interrelated and our listing is not complete. One of our objectives in this paper is to provide a perspective and overview of some of the many reengineering

Fig. 1 Some of the Many Major Ingredients in Reengineering

Fig. 2 Some Approaches to Reengineering

approaches and methodologies that have been suggested. A much more complete dissuasion is contained in [2], and this paper is a summary of Chapter 8 which discusses reengineering.

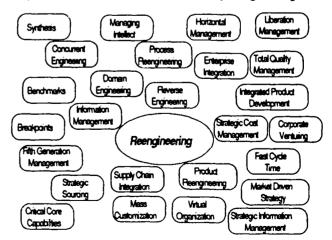

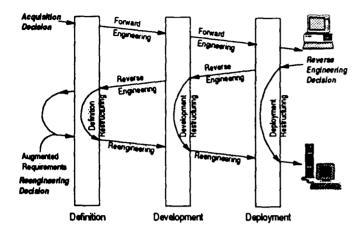

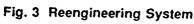

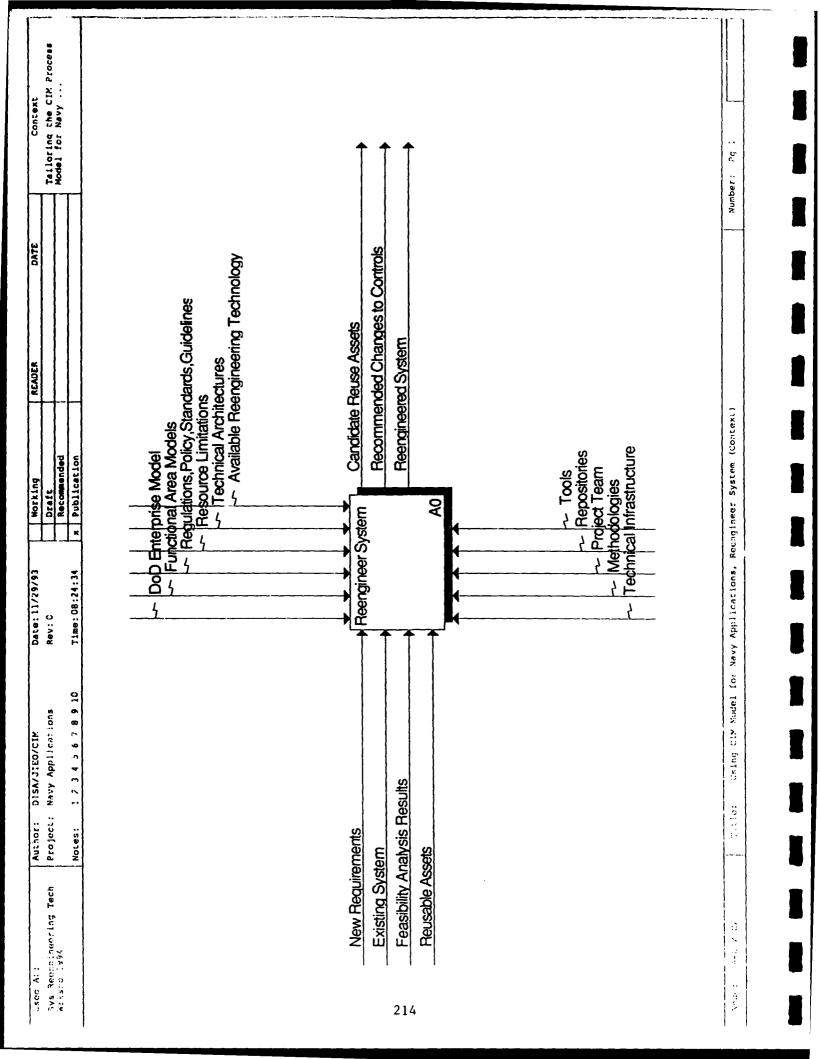

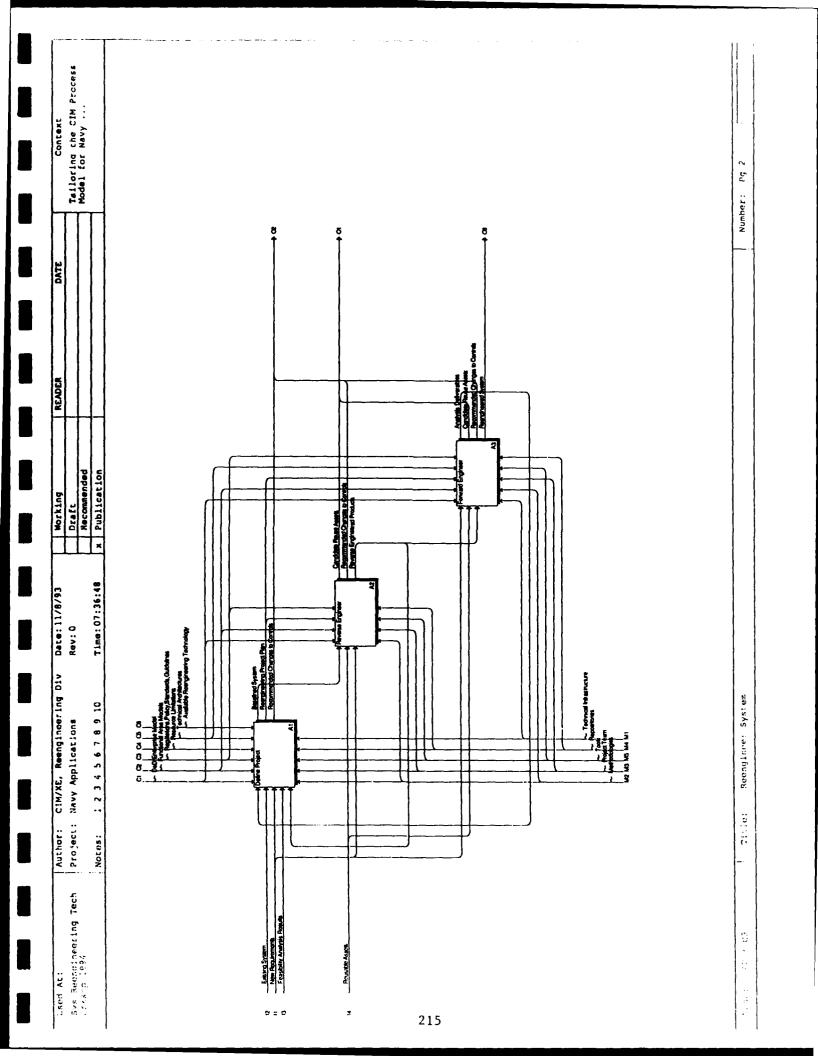

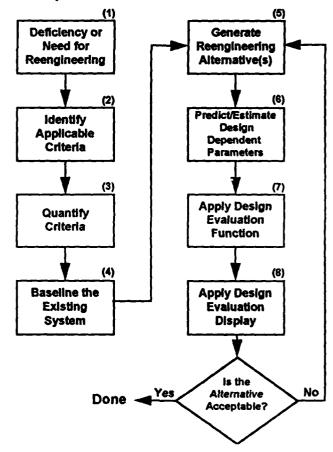

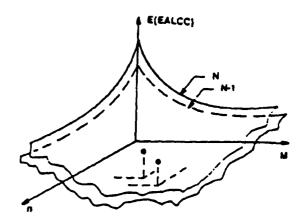

Figure 3 represents a generic view of reengineering. The entity to be reengineered can be either systems management, process, or product, or some appropriate combination of these. We will expand on this illustration and its interpretation in our discussions to follow.

Fig. 3 A Three Phase Approach to Generic Reengineering

We can approach a discussion of reengineering from several perspectives. First, we can discuss the

- structural,

- functional, and

- purposeful

aspects of reengineering. Alternately, or in addition, we can examine reengineering at the level of

- systems management,

- process, or

- product.

We may examine reengineering issues at any, or all, of the three fundamental systems engineering lifecycles:

- research, development, test, and evaluation (RDT&E);

- systems acquisition, procurement, or production; or

- systems planning and marketing.

Within each of these lifecycles, we could consider reengineering at any or all of the three generic phases of definition, development, or deployment. At the level of systems management, we reengineer each of these phases and potentially all other processes within the company for integrated improvement. At the level of process reengineering only, as we define it, only a single process is redesigned, and with no fundamental changes in the structure or purpose of the organization as a whole. Changes, when they occur, may be radical and revolutionary, or incremental and evolutionary at the levels of systems management, processes, or products.

One fundamental notion of reengineering is, however, the reality that it must be top down directed if it is to achieve the significant and long-lasting effects that are possible. Thus, there should be a strong purposeful and systems management orientation to reengineering, even though it may have well major implications for such lower level concerns as structural facets of a particular product.

Our paper is organized as follows. We first provide some definitions of reengineering. Then, we discuss some five of the many perspectives that have been taken relative to reengineering. Then, we provide some summary comments.

#### IL PERSPECTIVES ON REENGINEERING

In this section, we provide definitions and perspectives on what we consider to be three related but different types of systems reengineering; reengineering at the levels of

- product,

- process or product line, and

- systems management.

There have been a number of definition, formal and informal, of reengineering. The word is occasionally spelled as re-engineering. We choose the former spelling here; both are correct.

#### A. Product Reengineering

The term reengineering could mean some sort of reworking or retrofit of an already engineered product. This could well be interpreted as maintenance or refurbishment. As we have noted previously [3], maintenance can be viewed from reactive or corrective, interactive or adaptive, and proactive or perfective perspectives. Or, reengineering could be interpreted as reverse engineering, in which the characteristics of an already engineered product are identified, such that the product can perhaps be modified or reused. Inherent in these notions are two major facets of reengineering.

- It improves the product or system delivered to the user for enhanced reliability, maintainability, or for an evolving user need.

- 2. It increases understanding of the system or product itself.

Thus, this interpretation of reengineering is almost totally product focused. We will call it product reengineering.

Thus, we might say that

Product reengineering is the examination, study, capture, and modification of the internal mechanisms or functionality of an existing system or product in order to reconstitute it in a new form and with new features, often to take advantage of newly emerged technologies, but without major change to the inherent functionality and purpose of the system.

This definition indicates that product reengineering is basically structural reengineering with at most, minor changes in purpose and functionality of the product that is reengineered. This mengineered product could be integrated with other products having rather different functionality than was the case in the initial deployment. Thus, reengineered products could be used, together with this accomentation, to provide new functionality and serve new purposes. A number of synonyms for product reengineering easily come to mind. Among these are: renewal, refurbishing, rework, repair, maintenance, modernization, reuse, redevelopment, and ret: ofit.

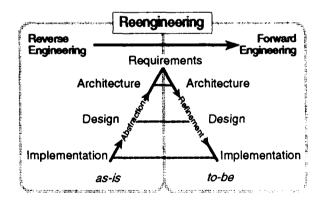

A specific example of a product reengineering effort might be that of taking a legacy system written in Cobol or Fortran, reverse engineering it to determine the system definition, and then reengineering it in C<sup>\*\*</sup> or Ada. Depending upon whether or not any modified user requirements are to be incorporated into the reengineered product, we would either reengineer the product, through a forward engineering effort, just after reverse engineering had determined either the initial development (technical) system specifications, or after reverse engineering far enough to determine user requirements and user specifications, and then updating these. This reverse engineering concept [4], in which salient aspect of user requirements or technological specifications are recovered frum examination of characteristics of the product, predates product reengineering.

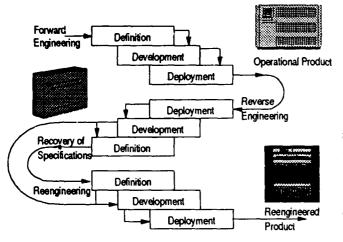

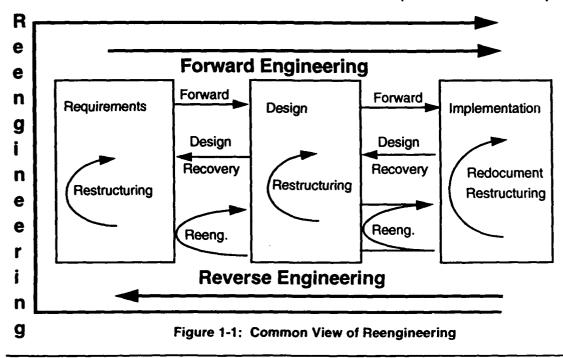

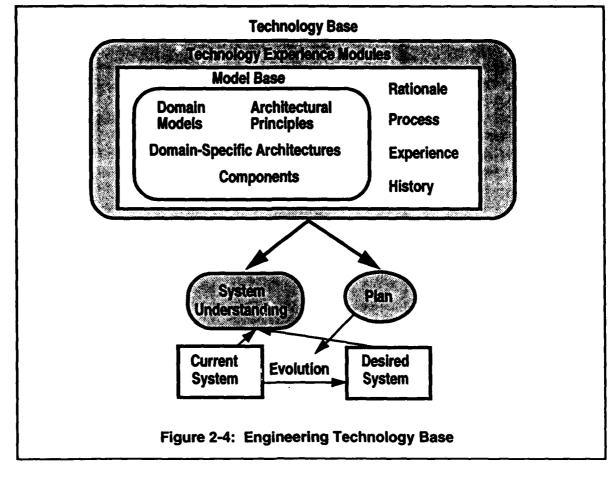

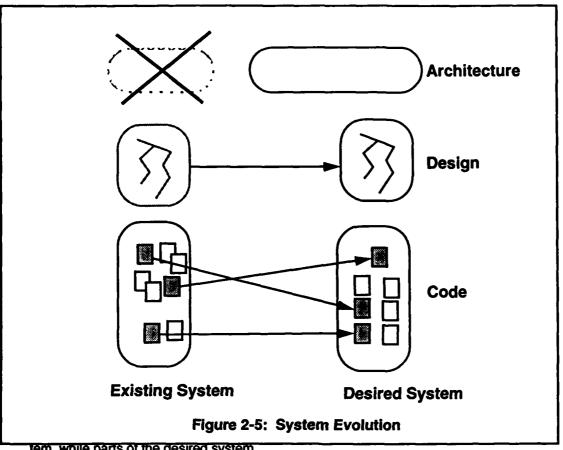

Figure 4 illustrates product reengineering conceptually. An IEEE software standards reference [5] states that "reengineering is a complete process that encompasses an analysis of existing applications, restructuring, reverse, and forward engineering." The IEEE standard for software maintenance [6] suggests that reengineering is a subset of software engineering that is comprised of reverse engineering and forward engineering. We have no disagreement with the sort of definition at all, we prefer to call it product reengineering for the reasons just stated. It is also necessary to consider reengineering at the levels of processes and systems management if we are to take full advantages of the major opportunities offered. Thus, the qualifier "product" appears appropriate and desirable in the context used here.

#### **B.** Process Reengineering

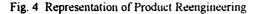

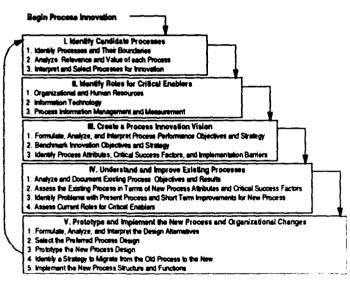

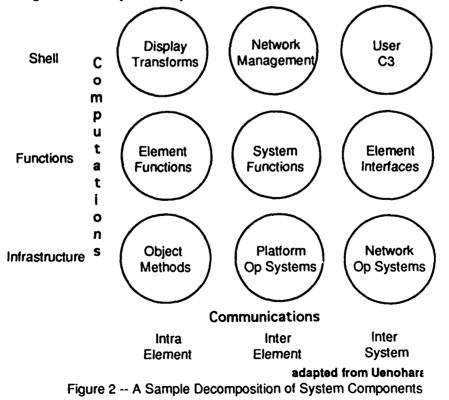

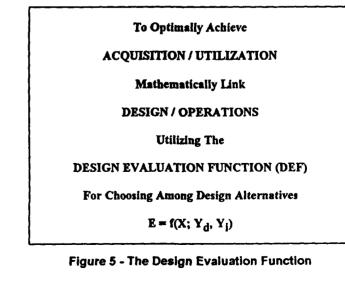

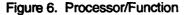

Reengineering can also be considered at the levels of processes and systems management. At the level of processes only, the effort would be almost totally internal. It would consist of modifications to whatever standard lifecycle processes are in use in a given organization in order to better accommodate new and emerging technologies or new customer requirements for a system. For example, an explicit risk management capability might be incorporated at several different phases of a given lifecycle and accommodated by a revised configuration management process. This could be implemented into the processes for RDT&E, acquisition, and systems planning and marketing. Basically, reengineering at the level of processes would consist of the determination, or synthesis, of an efficacious process for ultimately fielding a product on the basis of a knowledge of generic customer requirements, and the objectives and critical capabilities of the systems engineering organization. Our Figure 5 illustrates, conceptually, some of the facets of process reengineering.

Fig. 5 Conceptual Illustration of Process Reengineering

In accordance with this discussion, we offer the following definition.

Process reengineering is the examination, study, capture, and modification of the internal mechanisms or functionality of an existing process, or systems engineering lifecycle, in order to reconstitute it in a new form and with new features, often to take advantage of newly emerged capabilities, but without changing the inherent functionality and purpose of the process itself that is being reengineered.

We could reengineer either the process for RDT&E, system acquisition or production, or systems planning and marketing. Among the first discussions of this sort of effort at business process reengineering, although the word redesign was used rather than reengineering, is in a contemporary paper by Davenport and Short [7]. This was greatly expanded upon in a recent and seminal text by Davenport [8] which does make use of the term reengineering. We will provide an overview of this major work in a later section.

These and other authors recognize, of course, that redesign of processes only and without attention to reengineering at a higher level than processes only may, in many instances, represent an incomplete and not fully satisfactory way to improve organizational capabilities. Thus, the process considered as candidates for reengineering are high level managerial as well as operational processes. Information technology is considered to be a major enabling catalyst for process reengineering. Continuous process improvement and institutionalization is advocated.

Reengineering at the process level, and the resulting improvement in product that results from improvement in the product line, is essentially what the AT&T Bell Laboratories has used to identify a common taylorable systems acquisition process for Federal Systems Advanced Technology (FSAT) use as a deployment methodology for all Process Management Teams (PMTs) at this organization [9]. The indicated benefits to using a common and understood lifecycle include:

- shorter development cycles,

- fewer engineering change orders,

- products that fulfill customer expectations, and

- reduced program and product development costs throughout the lifecycle.

Thus, the process improvement results ultimately in an increase in effectiveness of product for the same cost, or a reduction in cost for the same effectiveness, or some blend of these two.

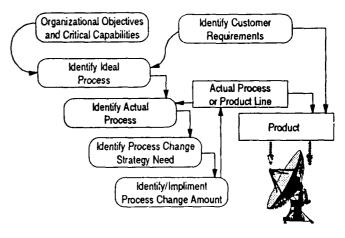

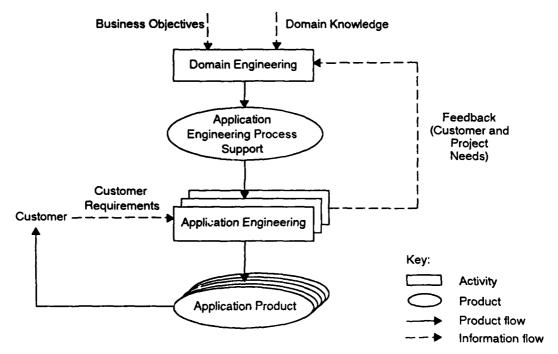

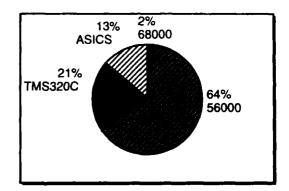

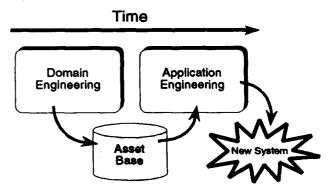

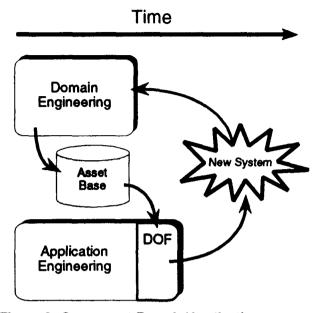

Essentially what we call process reengineering here is termed "domain engineering" by the Software Productivity Consortium [10]. The combination of domain engineering with the "application engineering," or lifecycle, effort needed to product the actual product is termed "synthesis." It is intended for use in the systems acquisition, procurement, or production lifecycle. Figure 6 illustrates the synthesis concept which is intended, in part, to facilitate the incorporation of reusable software products in new software systems. The synthesis process proceeds as follows.

Fig. 6 The Software Productivity Consortium Synthesis Process

- A set of 6 domain engineering phases is used to develop the product line. In the first phase, process, or product line, planning is accomplished. This is presumably based on knowledge of the organization and its critical core capabilities, and customer needs, as illustrated in Figure 5.

- This is followed by a process definitional phase, called product line analysis by SPC, in which the requirements for the process or product line are specified.

- 3. This leads to product-line, or lifecycle process, development.

- A modeling and simulation environment is next constructed such that it will be possible to accomplish prototyping in the actual lifecycle for production of the product.

- A product library is next constructed. This is comprised of reusable software modules and code generators which can

produce executable code from a set of input technical specifications. A code generator can be viewed as a special type of reusable software product.

- 6. A process, or product line, test and evaluation facility is constructed next. This has the capacity for test and evaluation of products from the product line. Following this phase, the applications engineering lifecycle begins. This involves actual definition, development, and deployment on the basis of the just engineered product line, or process, lifecycle.

- Product definition is the first phase in actual production of the software product. This is achieved by identifying the user requirements for a software product and translating them into a set of specifications.

- 8. Product prototyping occurs in the second phase of the applications engineering lifecycle. Here, a prototype is built and, with user interaction presumably, used to refine the technical specifications for the software product. The modeling and simulation environment, built earlier in domain engineering, is used for this purpose.

- New product development occurs next. In this particular instance, this refers to the production of custom built executable code for those portions of the software product that are not to be comprised of reusable code.

- 10. Reuse development occurs next. In this phase, the reengineered code that has become reusable code and code produced by applications generators in phase 5 of domain engineering is integrated in with the customized code to result in a complete functioning product.

- In the final phase, integration and test of this functional software occurs. This generally involves use of the test suites produced by the product line test and evaluation facility.

12. The deployed product results from this effort.

As indicated in Figure 6, there are several entry points from domain engineering to application engineering as several of the results of intermediate phases of domain engineering (at phases 5, 5, and 8) are used in the actual lifecycle that is developed as a result of domain engineering.

#### C. Reengineering at the Level of Systems Management

At the level of systems management, reengineering is directed at potential change in all business or organizational processes, including the systems acquisition process lifecycle itself. Many authors have discussed reengineering the corporation. Arguably, the earliest use of the term *business reengineering* was by Hammer [11], in 1990, and more fully documented in a more recent work on *Reengineering the Corporation* [12]. There are a small plethora of related works, as we will soon discuss.

Hammer's definition of reengineering "Reengineering is the fundamental rethinking and radical redesign of business processes to achieve dramatic improvements in critical, contemporary measures of performance, such as cost, quality, service and speed" is a definition of what we will call reengineering at the level of systems management. There are four major terms in this definition.

Fundamental refers to a large scale and broad scope examination of virtually everything about an organization and how it operates. The purpose is to identify potential weakness that are in need of diagnosis and correction.

- Radical redesign suggests disregarding existing organizational processes and structures, and inventing totally new ways of accomplishing work.

- Dramatic improvements suggests that, in Hammer's view, reengineering is not about making marginal and incremental improvements in the status quo. It is about making "quantum" leaps in organizational performance.

- Processes represent the collection of activities that are used to take input materials, including intellectual inputs, and transform them into outputs and services that have value to the customer.

Hammer suggests that reengineering and revolution are almost synonymous terms. His identification of the three types of firms that attempt reengineering - those in trouble, those who see trouble coming, and those who are ambitious and seek to avoid impending troubles.

He indicates that one major catalyst for reengineering is the creative use of information technology. Reengineering, is not just automation however, it is the ambitious and nule breaking study of everything about the organization to enable more effective and efficient organizational processes to be designed.

We essentially share this view of reengineering at the level of systems management. Our definition is similar.

Systems management reengineering is the examination, study, capture, and modification of the internal mechanisms or functionality of existing system management processes and practices in an organization in order to reconstitute them in a new form and with new features, often to take advantage of newly emerged organizational competitiveness requirements, but without changing the inherent functionality and purpose of the organization itself.

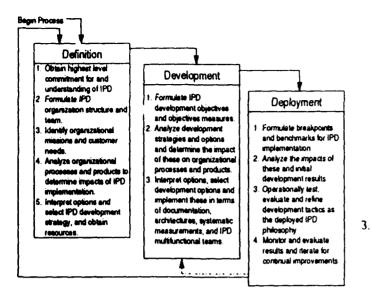

We make no representation that this definition, or the other two for that matter, of reengineering is at all the same across the many works that we discuss. Figure 7 represents this conception of reengineering at the level of systems management.

Fig. 7 Reengineering at the Level of Systems Management

Lifecycle process reengineering occurs as a natural byproduct of reengineering at the level of systems management. This may or may not result in the reengineering of already existing products. Generally, it will as new products and competitive strategies are a major underlying objective of reengineering at the level of systems management, or organizational reengineering as it is more commonly called.

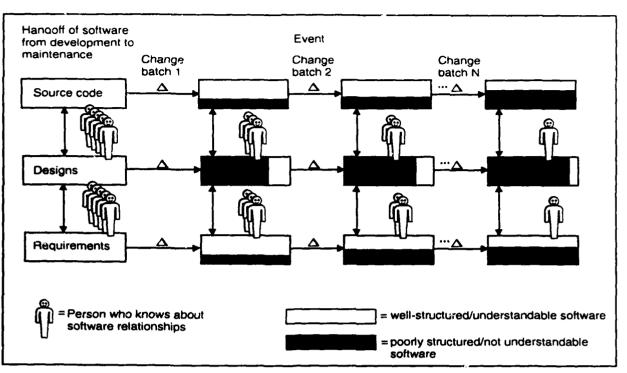

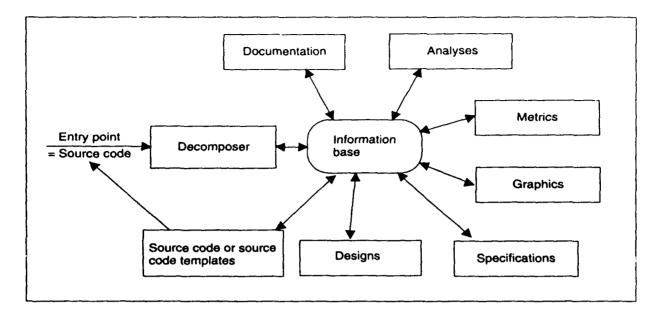

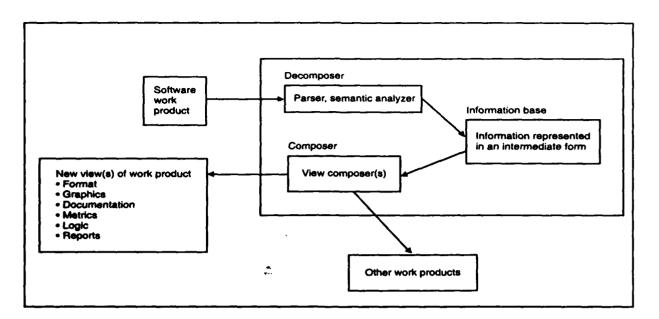

#### **D.** Perspectives of Reengineering