AD-A280 275

RL-TR-94-41 Final Technical Report May 1994

# PROTO CODE GENERATION TECHNIQUES

International Software Systems, Inc.

Dr. Ramon D. Acosta

94 6 16 071

APPROVED FOR PUBLIC RELEASE: DISTRIBUTION UNLIMITED.

Copyright 1994 International Software Systems, Inc. This material may be reproduced by or for the U.S. Government pursuant to the copyright license under clause at DFARS 252.227-7013 (April 1988).

~

DTIC QUALTTY INSPECTED 2

DTIC

ELECTE JUN 1 7 1994

Rome Laboratory Air Force Materiel Command Griffiss Air Force Base, New York

This report has been reviewed by the Rome Laboratory Public Affairs Office (PA) and is releasable to the National Technical Information Service (NTIS). At NTIS it will be releasable to the general public, including foreign nations.

RL-TR-94-41 has been reviewed and is approved for publication.

William E. Rushe APPROVED:

WILLIAM E. RZEPKA Project Engineer

FOR THE COMMANDER: Your Summer

JOHN A. GRANIERO Chief Scientist Command, Control & Communications Directorate

If your address has changed or if you wish to be removed from the Rome Laboratory mailing list, or if the addressee is no longer employed by your organization, please notify RL (C3CB) Griffiss AFB NY 13441. This will assist us in maintaining a current mailing list.

Do not return copies of this report unless contractual obligations or notices on a specific document require that it be returned.

| REPORT DO                                                                                                                                                                                                          | DCUMENTATI                                                                                                                                            | ON PAGE                                                                                                 | Form Approved<br>OMB No. 0704-0188                                                                            |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|

| Public reporting burden for this collection of inform<br>gathering and meintaining the data needed, and                                                                                                            | completing and reviewing the collection of info                                                                                                       | Innation. Send comments regarding to                                                                    | his burden estimate or any other aspect of this                                                               |  |

| colection of information, including suggestions fo<br>Davis Highway, Suite 1204, Arlington, VA 22202-4                                                                                                             |                                                                                                                                                       |                                                                                                         |                                                                                                               |  |

| 1. AGENCY USE ONLY (Leave Blank)                                                                                                                                                                                   | 2. REPORT DATE<br>May 1994                                                                                                                            | 3. REPOR<br>Fina                                                                                        | <b>RT TYPE AND DATES COVERED</b><br>1 Sep 91 - Jan 94                                                         |  |

| 4. TITLE AND SUBTTLE<br>PROTO CODE GENERATION TECHNIQUES                                                                                                                                                           |                                                                                                                                                       |                                                                                                         | UNDING NUMBERS<br>- F30602-91-C-0012<br>- 62702F<br>- 5581                                                    |  |

| 6 AUTHOR(S)<br>Dr. Ramon D. Acosta                                                                                                                                                                                 |                                                                                                                                                       |                                                                                                         | - 22<br>- 26                                                                                                  |  |

| 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)<br>International Software Systems, Inc.<br>9430 Research Blvd, Bldg 4, #250<br>Austin TX 78759-6543                                                             |                                                                                                                                                       |                                                                                                         | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER<br>ISSI-C91A00013                                                 |  |

| Rome Laboratory (C3CB)<br>525 Brooks Read                                                                                                                                                                          |                                                                                                                                                       |                                                                                                         | PONSORING/MONITORING<br>AGENCY REPORT NUMBER<br>-TR-94-41                                                     |  |

| 11. SUPPLEMENTARY NOTES<br>Rome Laboratory Project                                                                                                                                                                 | : Engineer: William E                                                                                                                                 | . Rzepka/C3CB/(315                                                                                      | ) 330-2762                                                                                                    |  |

| 12a DISTRIBUTION/AVAILABILITY ST                                                                                                                                                                                   | ATEMENT                                                                                                                                               | 12b.                                                                                                    | DISTRIBUTION CODE                                                                                             |  |

| Approved for public release; distribution unlimited.                                                                                                                                                               |                                                                                                                                                       |                                                                                                         |                                                                                                               |  |

| 13. ABSTRACT (Mailmum 200 words)                                                                                                                                                                                   |                                                                                                                                                       |                                                                                                         |                                                                                                               |  |

| Proto is an integrated<br>requirements for concur<br>level software and hard<br>comprises a comprehensi<br>object-based data model<br>prototyping, software/h<br>generation. This repor<br>languages, tools, and m | rrent systems. Proto<br>dware archite:tures ea<br>lve tool set for editi<br>ling, component reuse,<br>hardware allocation, i<br>rt contains a summary | supports codesign<br>rly in the system<br>ng hierarchical da<br>resource modeling<br>nteractive simulat | and analysis of high-<br>life cycle. The system<br>taflow specification,<br>, user-interface<br>ion, and code |  |

|                                                                                                                                                                                                                    |                                                                                                                                                       |                                                                                                         |                                                                                                               |  |

| 14. SUBJECT TERMS<br>Software, rapid prototy<br>generation, software/ha<br>resource moduling                                                                                                                       | vping, object oriented<br>ardware allocation, in                                                                                                      | , reuse, code<br>teractive simulati                                                                     | 15 NUMBER OF PAGES<br>42<br>OR, 16 PRICE CODE                                                                 |  |

| 17. SECURITY CLASSIFICATION<br>UNCLASSIFIED                                                                                                                                                                        | 18 SECURITY CLASSIFICATION<br>OF THIS PAGE<br>UNCLASSIFIED                                                                                            | 19. SECURITY CLASSIFIC<br>OF ABSTRACT<br>UNCLASSIFIED                                                   | ATION 20. LIMITATION OF ABSTRACT                                                                              |  |

| NSN 7540-01-280-5500                                                                                                                                                                                               |                                                                                                                                                       |                                                                                                         | Standard Form 299 (Rev. 2019)<br>Prescribed by ANSI Std. 239 (<br>299-192                                     |  |

A-i

# **Table of Contents**

| 7 CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ABSTRACT1                                     |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---|

| 3 SOFTWARE AND HARDWARE PROTOTYPING LANGUAGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 INTRODUCTION1                               |   |

| 3.1 SOFTWARE SPECIFICATION USING SSDL       6         3.2 HARDWARE SPECIFICATION       9         4 PROTO TOOLS       11         4.1 SYSTEM DESCRIPTION       11         4.1.1 User Interface Manager       14         4.1.2 Object Manager       14         4.2.1 Project Manager       15         4.2.2 Graph Editor       18         4.2.3 Behavior Editor       18         4.2.4 Type Editor       18         4.2.5 Variable Editor       18         4.2.6 Dynamic Loader       19         4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.11 Architecture Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31 | 2 FUNCTIONAL OVERVIEW                         |   |

| 3.2 HARDWARE SPECIFICATION       .9         4 PROTO TOOLS       11         4.1 SYSTEM DESCRIPTION       11         4.1.1 User Interface Manager       14         4.1.2 Object Manager       14         4.2.1 Project Manager       15         4.2.1 Project Manager       15         4.2.2 Graph Editor       18         4.2.5 Variable Editor       18         4.2.6 Dynamic Loader       19         4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.10 Import Facility       20         4.2.11 Architecture Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                | 3 SOFTWARE AND HARDWARE PROTOTYPING LANGUAGES |   |

| 4 PROTO TOOLS       11         4.1 SYSTEM DESCRIPTION       11         4.1.1 User Interface Manager       14         4.1.2 Object Manager       15         4.2 TOOLS       15         4.2.1 Project Manager       15         4.2.2 Graph Editor       15         4.2.3 Behavior Editor       18         4.2.4 Type Editor       18         4.2.5 Variable Editor       18         4.2.6 Dynamic Loader       19         4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.11 Architecture Editor       21         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       30         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                | 3.1 SOFTWARE SPECIFICATION USING SSDL         |   |

| 4.1 SYSTEM DESCRIPTION       11         4.1.1 User Interface Manager       14         4.1.2 Object Manager       14         4.2 TOOLS       15         4.2.1 Project Manager       15         4.2.2 Graph Editor       15         4.2.3 Behavior Editor       18         4.2.4 Type Editor       18         4.2.5 Variable Editor       18         4.2.6 Dynamic Loader       19         4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.11 Architecture Editor       21         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                               | 3.2 HARDWARE SPECIFICATION                    |   |

| 4.1.1 User Interface Manager       14         4.1.2 Object Manager       14         4.2 TOOLS       15         4.2.1 Project Manager       15         4.2.2 Graph Editor       15         4.2.3 Behavior Editor       18         4.2.4 Type Editor       18         4.2.5 Variable Editor       18         4.2.6 Dynamic Loader       19         4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.11 Architecture Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                              | 4 PROTO TOOLS                                 |   |

| 4.1.2 Object Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.1 SYSTEM DESCRIPTION                        |   |

| 4.2 TOOLS       15         4.2.1 Project Manager       15         4.2.2 Graph Editor       15         4.2.3 Behavior Editor       18         4.2.4 Type Editor       18         4.2.5 Variable Editor       18         4.2.6 Dynamic Loader       19         4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                                                                                                                       | 4.1.1 User Interface Manager14                |   |

| 4.2.1 Project Manager       15         4.2.2 Graph Editor       15         4.2.3 Behavior Editor       18         4.2.4 Type Editor       18         4.2.5 Variable Editor       18         4.2.6 Dynamic Loader       19         4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                                                                                                                                                  | 4.1.2 Object Manager14                        |   |

| 4.2.2 Graph Editor       15         4.2.3 Behavior Editor       18         4.2.4 Type Editor       18         4.2.5 Variable Editor       18         4.2.6 Dynamic Loader       19         4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                                                                                                                                                                                         | 4.2 TOOLS                                     |   |

| 4.2.3 Behavior Editor       18         4.2.4 Type Editor       18         4.2.5 Variable Editor       18         4.2.6 Dynamic Loader       19         4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                                                                                                                                                                                                                             | 4.2.1 Project Manager                         |   |

| 4.2.4 Type Editor       18         4.2.5 Variable Editor       18         4.2.6 Dynamic Loader       19         4.2.6 Dynamic Loader       19         4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.11 Architecture Editor       20         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                                                                                                                                                                                  | 4.2.2 Graph Editor15                          |   |

| 4.2.5 Variable Editor       18         4.2.6 Dynamic Loader       19         4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.11 Architecture Editor       20         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         N       30         8 REFERENCES       31                                                                                                                                                                                                                                                                                                                                                                                       | 4.2.3 Behavior Editor                         |   |

| 4.2.6 Dynamic Loader       19         4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.11 Architecture Editor       20         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.2.4 Type Editor                             |   |

| 4.2.7 Rapid Interface Prototyping System       19         4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.11 Architecture Editor       20         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.2.5 Variable Editor                         |   |

| 4.2.8 Reuse Library Manager       20         4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.10 Import Facility       20         4.2.11 Architecture Editor       20         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         N       30         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.2.6 Dynamic Loader                          |   |

| 4.2.9 Export Facility       20         4.2.10 Import Facility       20         4.2.11 Architecture Editor       20         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         N       30         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.2.7 Rapid Interface Prototyping System      |   |

| 4.2.10 Import Facility       20         4.2.11 Architecture Editor       20         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.2.8 Reuse Library Manager20                 |   |

| 4.2.11 Architecture Editor       20         4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.2.9 Export Facility20                       |   |

| 4.2.12 Mapping Editor       21         4.2.13 Interpreter       21         4.2.14 Ada Code Generator       23         5 METHODOLOGY OVERVIEW       23         6 EXAMPLE       27         7 CONCLUSIONS       30         8 REFERENCES       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.2.10 Import Facility                        |   |

| 4.2.13 Interpreter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.2.11 Architecture Editor                    |   |

| 4.2.14 Ada Code Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.2.12 Mapping Editor                         |   |

| 5 METHODOLOGY OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.2.13 Interpreter                            |   |

| 6 EXAMPLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.2.14 Ada Code Generator23                   |   |

| 7 CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5 METHODOLOGY OVERVIEW                        | _ |

| 8 REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6 EXAMPLE                                     |   |

| , Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7 CONCLUSIONS                                 |   |

| Avail and/or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8 REFERENCES                                  |   |

| Avail and/or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |   |

| Avail and/or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |   |

| Avail and/or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | , Codes                                       |   |

| Dist Special                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Dist Special                                  |   |

International Software Systems, Inc.

# ABSTRACT

Proto is an integrated system for specifying, analyzing, and validating software requirements for concurrent systems. The system was developed under Air Force Rome Laboratory Contract No. F30602-91-C-0012, Proto Code Generation Techniques. Proto supports codesign and analysis of high-level software and hardware architectures early in the system life cycle. The system comprises a comprehensive tool set for editing hierarchical dataflow specifications, object-based data modeling, component reuse, resource modeling, user-interface prototyping, software/ hardware allocation, interactive simulation, and code generation. This report contains a summary of Proto's functional capabilities, languages, tools, and methodology.

# **1 INTRODUCTION**

Requirements are precise statements of need intended to convey a specific understanding about a desired result. Regardless of whether requirements specify needs for airline reservation systems, process control software, or automobiles, ideally they describe external, user-visible characteristics rather than internal system structure. Requirements also specify the constraints placed on what is needed. Performance, reliability, safety, cost, schedule and the reuse of existing designs are typical constraints. Requirements engineering is the activity of forming a model based on the requirements and then validating that the model accurately represents what is needed [Rzepka and Ohno 1985].

The importance of requirements engineering for software systems has been widely recognized in many application domains, including medical diagnosis, command and control, information systems, avionics, and emergency management. The inherent complexity of establishing an unambiguous, complete, and consistent set of requirements prior to system design and construction has led software engineering researchers and practitioners to propose and adopt rapid prototyping techniques and spiral development as part of the requirements engineering process.

Rapid prototyping techniques support specification and design analysis of critical software elements early in the system lifecycle [Boehm 1988; Gordon and Bieman 1991]. Development of evolutionary prototypes, with continuous user involvement and review, can provide significant improvements to the requirements specification process for complex software systems. The importance of improving this process cannot be overemphasized: doing so will reduce the risk, cost, and time associated with developing a software system and will lead to improved quality, reliability, reusability, and maintainability of the resultant system.

The greatest payoff in employing rapid prototyping techniques for requirements engineering is obtained by using environments integrated around a common underlying representation model that supports requirements elicitation and capture tightly coupled with high-level executable specification languages. Such an environment facilitates the electronic transfer of requirements into the prototyping context to initiate the design and development process. Progress in developing rapid prototyping environments, however, has been slowed by the lack of unifying models and technology capable of representing the complex data relationships associated with requirements. Moreover, few attempts have been made in extending rapid prototyping techniques for requirements specification and design of concurrent, parallel, and distributed systems.

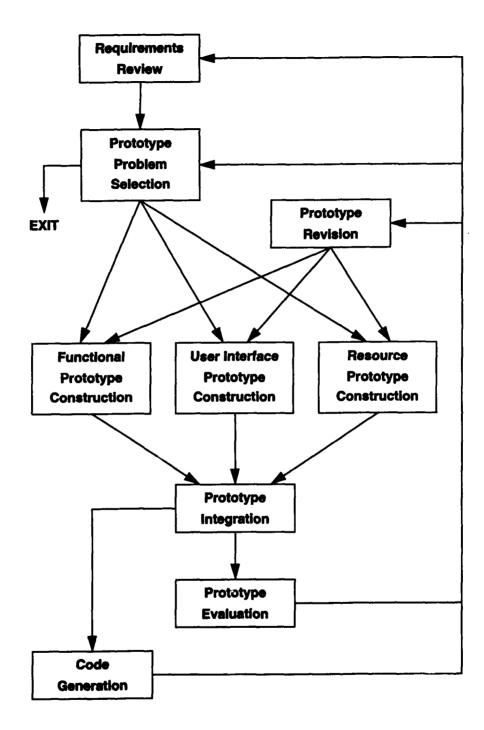

The Requirements Engineering Environment (REE) provides an integrated toolset for rapid construction of executable prototypes to model and analyze software system requirements. REE contains interactive simulation-based facilities to allow systems analysts to rapidly represent. build, and execute models of critical aspects of complex systems [Rzepka et al. 1993]. Functional, user interface, and performance models can be constructed easily, and at varying levels of abstraction or granularity, depending on the specific behavioral aspects of the system being exercised. REE is being developed as part of Rome Laboratory's research program in requirements engineering which has been in place since 1985 [Rzepka 1992].

The major components of REE include Proto, the Rapid Interface Prototyping System (RIP), and an interface routine package that integrates Proto and RIP. Proto is a rapid prototyping computeraided software engineering (CASE) system that supports functional and performance prototyping of systems incorporating both sequential and parallel processing elements. RIP is a collection of tools that support building, executing, and analyzing user interface prototypes. Access to all of the RIP capabilities is accomplished through graphic, menu, and template driven interfaces, allowing requirements engineers who are not programmers to readily utilize the system.

This report concentrates on describing the functional capabilities, languages, tools, and methodology of Proto. It provides a complete summary of the system and serves a starting point for readers interested in understanding Proto and its underlying rapid prototyping technology.

In addition to this report, a full complement of documentation materials is available for gaining a greater understanding of using Proto and its underlying implementation:

- Functional Description for Proto [Acosta 1993a]

- System/Subsystem Specification for Proto [Acosta 1993b]

- Program Specification for Proto [ISSI 1994]

- Proto User's Manual, Volumes 1 and 2 [ISSI 1993d]

- Proto Methodology [Acosta and Beal 1994]

Additional documentation associated with the project includes [Acosta and Liu 1993; ISSI 1993b, 1993c; Cechovic 1993; Box 1993].

The main source of information for those wishing to explore the user interface prototyping facilities of RIP are referred to:

• Software User's Manual for the Rapid Interface Prototyping (RIP) System of the Requirements Engineering Environment [ISSI 1993a]

Titles of recent papers that provide more in-depth coverage of specific functional and implementation aspects of Proto, RIP, and REE which may be of interest to readers include:

- Parallel Proto A Prototyping Tool for Analyzing and Validating Sequential and Parallel Processing Software Requirements [Burns 1991]

- A Requirements Engineering Testbed: Concept and Status [Rzepka 1992]

- Specification Prototyping of Concurrent Ada Programs in Proto [Acosta 1992]

- Requirements Engineering Technologies at Rome Laboratory [Rzepka et al. 1993]

- Use of Simulation Techniques in a Prototyping Environment for Requirements Engineering [Sidoran and Acosta 1993]

• A Case Study of Applying Rapid Prototyping Techniques in the Requirements Engineering Environment [Acosta et al. 1994]

Subsequent sections of this report are structured as follows. In Section 2, an overview of the Proto functionality is provided. Section 3 describes the software and hardware prototype specification languages. Section 4 contains a high-level description of the Proto system and its tools. An overview of the Proto prototyping methodology is presented in Section 5. Section 6 contains a simple example to suggest how Proto facilities are employed for rapid prototyping of requirements. Finally, Section 7 contains summarizing conclusions and directions for future work.

# **2 FUNCTIONAL OVERVIEW**

The goal of the Proto Code Generation Technique contract is to develop Proto, a rapid prototyping computer-aided software engineering (CASE) system that supports specification and design of systems incorporating both sequential and parallel processing elements [RADC 1990]. The system supports codesign and analysis of high-level software and hardware architectures early in the system life cycle. Proto comprises a comprehensive tool set for window-based graphical editing of hierarchical dataflow graph specifications, object-based data modeling, component reuse, graphical hardware resource modeling, user-interface prototyping, software/hardware allocation, interpreted execution using simulation, functional animation, interactive debugging, and code generation. The system is built on top of a substrate for managing user interfaces and database objects to provide consistent views of design objects across system tools.

Proto builds upon previous work sponsored by Rome Laboratory, including:

- **Proto.** Feasibility prototype of a rapid functional prototyping environment [Hartman et al. 1988].<sup>1</sup>

- **Proto+.** Prototyping tool for specification and design of software systems based on dataflow concepts [ISSI 1992].

- **PProto (Parallel Proto).** Upward-compatible extension of Proto+ with capabilities for hardware architecture modeling and software/hardware allocation [Acosta 1991].

Proto provides a design environment for systems analysts through the use of a high-level prototyping language called the System Specification and Design Language (SSDL). In addition, it incorporates significant domain-specific reuse and code-generation capabilities necessary to support *domain users*. Other areas of emphasis in Proto include modeling tools for parallel and distributed processing, user interface prototyping, and methodological foundations. An important goal of the project is to validate the effectiveness of the Proto methodology and tools by constructing two domain-specific reuse libraries and a demonstration of a representative Air Force application.

SSDL is a high-level prototyping language based on visual dataflow abstractions. In SSDL, a clear distinction is made between the following portions of a design:

• Dataflow Specification. Graphical model of a prototype.

<sup>1.</sup> Note that the term Proto, which was used as the name of the original VHLL prototyping system, is being used as the name of the system described in this document (which is an enhancement of Proto/Proto+/PProto). When this project started, DProto was used to refer to the enhancements system.

#### ISSI-C91A00013

- **Behavior Specification.** Data transformations effected by leaf nodes of a dataflow graph.

- Data Specification. Dynamic object-based data definitions.

SSDL contains many features that are useful in building prototype models of concurrent, parallel, and distributed systems, including several message-passing protocols and shared data stores that facilitate describing systems containing concurrent cooperating processes. Data modeling in SSDL is accomplished with a highly flexible object-based design paradigm. Dynamic modification of object features, such as relations to other objects and inheritance, is simple and valuable for rapid prototyping. Behaviors can access user-defined C functions, which allows SSDL to be used for defining prototypes as compositions of previously developed components.

Functional capabilities of Proto are summarized below:

**Software Prototyping.** Software systems are specified and designed using an enhanced version of the SSDL prototyping language. SSDL is a hierarchical dataflow language that provides constructs for describing visual dataflows, object-based data models, and textual behaviors. SSDL has concurrent execution semantics, which support simulation-based interpretation of specifications and code generation. Software modeling primitives include process nodes, connections, ports, and stores. These components can be configured to model a wide variety of concurrent systems, including those whose communication and synchronization is based on message passing or on shared memory. Explicit user-specified control connection mechanisms to enable node execution are also available. Data types include integers, reals, strings, enumerations, classes (with attributes, methods, and inheritance), and arrays. SSDL designs are organized into independent *projects* under user control.

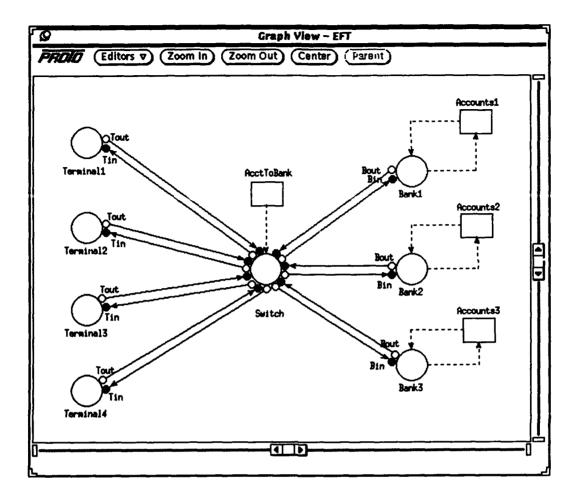

A sophisticated multiwindow dataflow graph editor supports rapid construction of SSDL prototypes. This editor provides integrated access to facilities for reuse, software/hardware allocation, editing and parsing of behaviors, and editing of variables and types. The editors for variables and types employ graphical and menu-based displays for supporting development of complex data models. All of the SSDL editing tools are integrated via an underlying structure of semantic database objects that is accessed by other tools of the system.

**Component Reuse.** Management and browsing of libraries containing domain-specific reusable components are integrated with the system editors. The primary reusable components consist of leaf and hierarchical library process nodes, and user-specified data types. Reusable data types include classes (with their methods), enumerations, and arrays. Capabilities that assist in component reuse include explicit control connections, cut/copy/paste of class method nodes and library process nodes, and keyword search. Systems analysts can access facilities for developing reusable SSDL prototype components and adding the components to domain-specific libraries. Libraries can also be combined by invoking a merge operation. Domain users are supported by capabilities to modify and integrate reusable components into domain-specific prototypes.

Another capability that supports reuse is a dynamic loading tool for linking externally developed C functions into a prototype under construction. These functions can be called from SSDL behaviors. Proto also contains export and import tools that use a file-based ASCII format for representing SSDL specification prototypes. This format is a convenient mechanism for transferring designs between databases, sending designs using electronic mail, cleaning up databases, performing regression testing, and providing an interface between Proto and other tools.

4

User Interface Prototyping. The system incorporates the REED RIP tool [ISSI 1993] to construct graphical input and output interfaces for SSDL prototypes. The user is provided with an functional application programmer interface (API), termed DRI, to manipulate RIP objects by referencing and modifying their state attributes from SSDL behaviors. In this manner, generic and application-specific user-interface prototypes can be developed in conjunction with functional prototypes. RIP supports not only interface graphics but also form3-based devices, such as buttons and text fields.

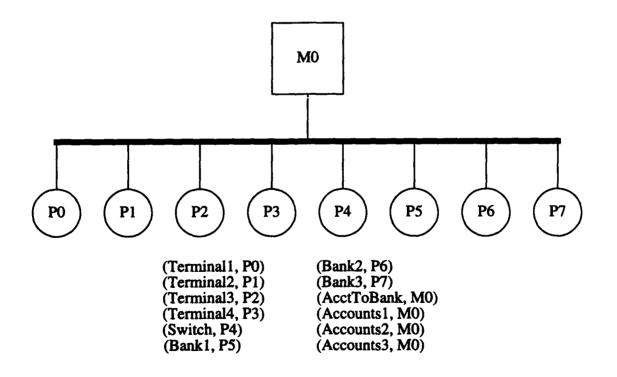

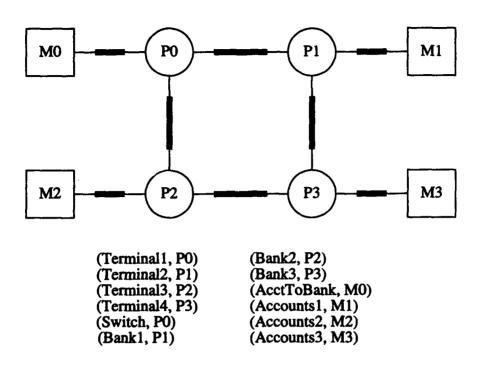

Architecture Modeling. Proto provides a generic mechanism for specifying several kinds of MIMD architectures. These include shared-memory multiprocessors, distributed-memory multiprocessors, and hybrid machines consisting of shared-memory and distributed-memory components. Hardware modeling primitives include processors, memories, and buses. User-specified parameters are supplied for selection of hardware resource characteristics, including machine topology, processor execution speed, memory-access time, and bus delays. Hardware component timings are specified in terms of simulation time units. An algorithm for automatically computing static message routing is also provided.

Architectural features are described with a graphical architecture definition language. Editing of this visual language is accomplished by a graphical editor. The editor also supports automatic layout of parameterized mesh architectures containing an arbitrary number of rows and columns of processors interconnected by buses. Architecture specifications are stored as database entries for subsequent use with mapping and simulation tools.

An editor for allocating software (logical) components to hardware (physical) components is available. This editing facility is integrated with the dataflow graph editor. A mapping consists of pairs of software and hardware components taken from their respective definitions. This is accomplished by associating graphical objects that denote software activities with the graph that captures the actual hardware. Thus, a mapping is an embedding of the graph of logical connections into the graph of physical connections. More than one mapping per software specification is possible. Automatic heuristic and random allocation algorithms are also provided.

Simulation-Based Prototype Execution. Subsystems to support interactive execution of prototypes include an SSDL interpreter, a scheduler, and an architecture modeler. These functions are controlled by a simulation kernel that implements a simulation cycle using a time-based event queue. The interpreter directly executes SSDL behaviors. Using a time-based algorithm, the scheduler arbitrates among process nodes that are competing to execute on a single processor. Software design simulation is constrained by an architecture resource model according to the software/hardware mapping that is specified. The architecture modeler manages resource simulation, including message routing, serialization of memory and bus requests, and display of utilization statistics.

Interactive debugging and performance evaluation features provided in Proto include dataflow graph animation, node breakpoints, single-stepping of behaviors, dynamic data display instruments, dynamic resource utilization instruments, and object browsing facilities. In addition, functions for debugging concurrent specifications are provided. One of these event-based tools implements automatic detection of deadlocks. A generic conditional breakpoint facility provides support for detection of exceptional concurrent event sequences, such as data corruption and data unavailability.

**Code Generation.** In support of specification and design for both systems analysts and domain users, Proto incorporates an automatic code generation tool for generating Ada implementations from SSDL prototypes. Multitasked Ada code that can be easily integrated with other systems is generated for all components of an SSDL specification prototype. Communication and synchronization between process nodes are accomplished with Ada's rendezvous mechanism, thus providing a model appropriate for distributed applications. The generated code employs the same scheduling algorithm as the Proto simulator, which results in code that is semantically equivalent to the original SSDL, except for timing dependencies and inherent nondeterminism.

User Interface Management. Interfaces to the editing, simulation, and code generation tools are managed by a common graphical interface substrate that implements the OPEN LOOK user interface standard. The user interface manager guarantees a clear and consistent interface across tools.

**Object Management.** Management of persistent design objects is implemented by a commercial object-oriented database commonly accessible to all system tools. Examples of objects stored in the database include SSDL visual representations, semantic structures, resource architectures, and reuse libraries.

# **3 SOFTWARE AND HARDWARE PROTOTYPING LANGUAGES**

Proto employs SSDL as its notation for specifying the prototype of a software component. A specialized hardware architecture definition notation is used to define resource prototypes. This section describes these two representations.

# 3.1 SOFTWARE SPECIFICATION USING SSDL

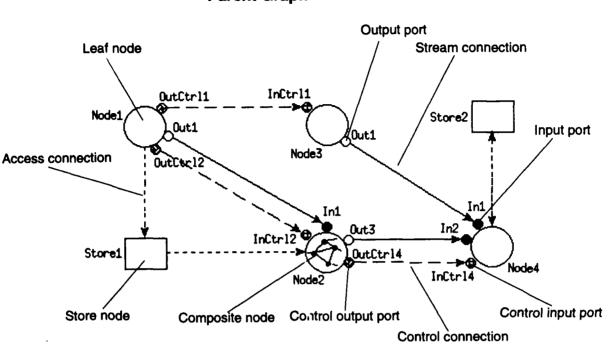

Software system prototype specifications in SSDL are modeled as hierarchical dataflow graphs that contain the following primitives (Figure 1):

- Process Nodes. Sequential or concurrent processes, functions, operators

- Stores. Shared memory to store state information

- Connections. Communication channels between process nodes and stores

- Ports. Interfaces between process nodes and connections

Each process node in the hierarchy may be structurally specified by a decomposition, or refinement, which is itself a dataflow graph. This nested graph receives all its inputs from and sends all its outputs to the ports on its enclosing node. The *behavior* of each leaf node of a graph defines the functional transformation that takes place inside a process node.

A dataflow description corresponds to a functional specification, where dataflow process nodes denote system functions. Data is transient and passes from node to node along connections in the form of messages. It is possible, however, to save data across process node executions using stores. Thus, there are two kinds of data in SSDL: *activation data* that fires the output-triggering data-transforming computation inside a process node, and *reference data*, resident in stores, that is read and written by a process node and is preserved across node executions. This basic computation model of concurrent cooperating processes thus supports both shared-variable and message-passing communication styles.

**Parent Graph**

**Refinement of Node2**

Figure 1. Graphical Symbols Used in SSDL

Concurrency is introduced into an SSDL model by mapping process nodes onto different *processors* defined in the hardware architecture model. A process node, which is always mapped to some processor, can execute in parallel with nodes mapped onto other processors as long as (1) its activation data is available, (2) the processor it is mapped to is idle, and (3) it has higher precedence than other activated process nodes that are mapped onto its same processor. Precedence is determined by a *scheduling algorithm* that arbitrates among multiple process nodes competing to execute on an single processor. This algorithm considers node activation times, execution counts, and node priorities in making the scheduling decision.

Data modeling uses the object-based concepts of *class* and *instance*. A class is a type definition of a set of objects that defines attributes, or slots, that describe the features of members of the set. A class can have subclasses that inherit attributes from their parent class and can have additional attributes not present in their parent class. An instance of a class is a specific application object that belongs to the set of objects defined by the class and contains a unique version of its inherited attributes. In addition to classes, other types supported by SSDL include integers, reals, strings, arrays, and enumerations. An *unspecified* type is also provided which, although requiring dynamic type checking during execution, allows delaying type constraint decisions during the prototype construction process.

SSDL supports three kinds of *variables*: ports, stores, and locals. By default, variables are of the unspecified type, i.e., they can assume values of any type. Stores are variables that preserve state across process node executions. Stores are also marked with a *lock* attribute that can be used to restrict concurrent access in such a manner as to prevent inadvertent shared data corruption. Node ports are denoted as being either input ports or output ports. Input ports have attached first-in-first-out (FIFO) queues that store incoming data. Ports are visible to their containing process node and its decomposition, if any. Visibility of locals is strictly limited to their containing process node.

Asynchronous communication between process nodes is available using *stream* connections, which provide unbounded buffer channels. Synchronous communication is modeled with *synchronized* connections between process nodes, which provide automatic generation of acknowledgments when node behaviors that process the incoming "synchronized" data messages complete execution. *Sampled* communication connections, which implement a sample-and-hold communication protocol, are also available. Read and write access from process nodes to stores is achieved over explicit *access* connections.

Sequential or concurrent process node behaviors in SSDL are described with a simple structured programming notation whose statements are interpreted by the Proto simulator. Behaviors consist of one or more *behavior rules*, which contain a *trigger*, or guard, and an *action*. Thus, the general structure of a node behavior is the following:

#### initial

```

-- Port queue and store initialization.

end initial

```

#### behavior

```

<trigger1> :- <action1> !

<trigger2> :- <action2> !

...

```

#### **Final Report for Proto**

```

<triggerN> :- <actionN> !

end behavior

```

If a trigger is empty, the behavior rule is said to be an *independent* behavior, otherwise, the behavior rule is a *dependent* behavior. Independent behavior rules do not depend on input data and are always eligible to execute. Conditional trigger expressions for dependent behaviors specify how data messages are accepted, or received, by a process node (i.e., **accept** operations) and the input data conditions under which a process node is activated. Even though the triggers of multiple behavior rules within a process node may be true simultaneously, at most one behavior rule within a process node can be executing at any given time. In this manner, use of the behavior rule construct allows specification of nondeterministic selection of alternative actions, which subsequently influences scheduling decisions during simulation and generated code execution.

High-level SSDL constructs for specifying behavior rule actions include iteration, conditional statements, assignment, message-passing primitives (i.e., **send** operations), and variable accesses. Behavior constructs are also available to initialize port queues and stores, and provide access to external procedures written in C. A functional interface to a comprehensive math library is also available.

A **read** operation for a variable is carried out whenever the variable is referenced in evaluating an expression (e.g., the expression on right-hand-side of an assignment statement or a conditional expression in an iteration statement). Variable **write** operations occur whenever the variable appears on the left-hand-side of an assignment statement.

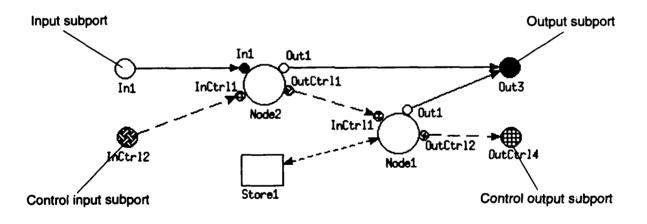

## 3.2 HARDWARE SPECIFICATION

Proto provides a generic mechanism for specifying parallel and distributed MIMD architectures. These include shared-memory multiprocessors, distributed-memory multiprocessors, and hybrid machines consisting of shared-memory and distributed-memory components. Hardware resource modeling primitives include (Figure 2):

- Processors. Execute process node behaviors

- Memories. Contain store values

- Buses. Transfer messages for node communication and store accesses

Users are free to specify any machine topology consisting of these components. The only topological restrictions are that buses must be used to connect processors to other processors or to memories; i.e., processors and memories cannot be directly connected to each other. Proto also provides a mechanism for automatically generating mesh architectures consisting of rows and columns of processors interconnected by buses.

User-specified parameters for selection of hardware resource characteristics include processor execution speed, read and write memory-access times, and message delays. All of these parameters are defined in terms of simulation time units. Specification of processor execution speed involves designating delays for the following behavior operations:

- **add/subtract** addition and subtraction (+, -)

- accept accepting from stream, sampled, and synchronized connections

#### Figure 2. Graphical Symbols Used in Architecture Definitions

- assign writing of port, store, and local variables (:=)

- **c\_call** calls to predefined and external user-defined C functions

- **divide** division (/)

- jump if, loop, and exit statements

- index array indexing ([])

- logical\_op logical operators (not, and, or)

- **multiply** multiplication (\*)

- **new** creation of new class instances (**new** and **copy** operators)

- read reading of port, store, and local variables, and constants

- relational\_op relational operators (>, >=, <, <=, =, !=)</li>

- **attribute** access to class instance attributes (.)

- send sending to stream, sampled, and synchronized connections

- stop stop statement

Static minimum delay routing between primitives is automatically computed by the system using Floyd's shortest path algorithm [Aho et al. 1983]. During simulation, these routings are used to process message-passing (sond) and data-store access (road/write) requests as high-level constructs. Consequently, a software design does not have to be changed when it is ported from one architecture to another, or when different software/hardware mappings are used for the same architecture. For example, a software specification that assumes a logical shared-memory model

can be mapped onto a shared-memory multiprocessor or a distributed-memory multiprocessor without changing any code. In the latter case, the physical model is one of distributed shared memory.

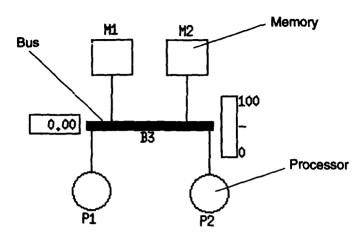

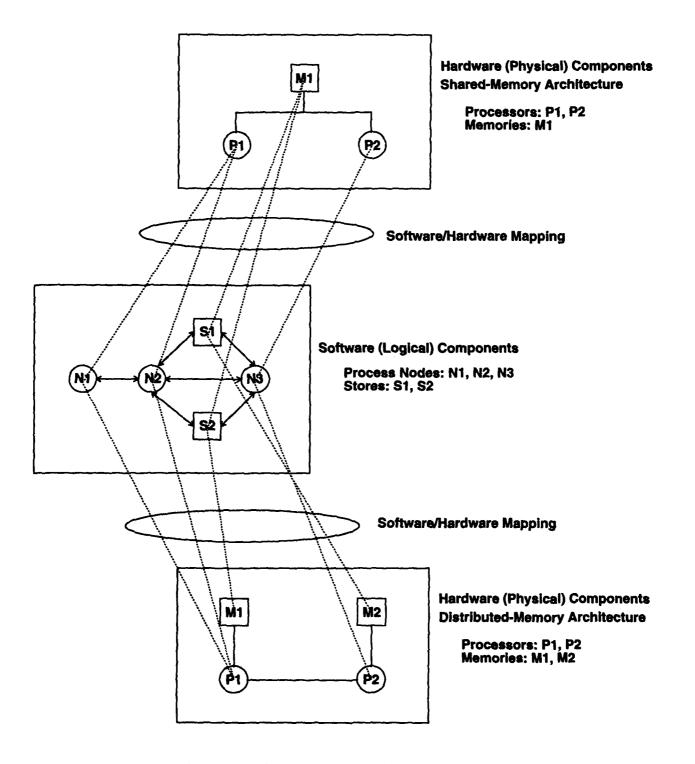

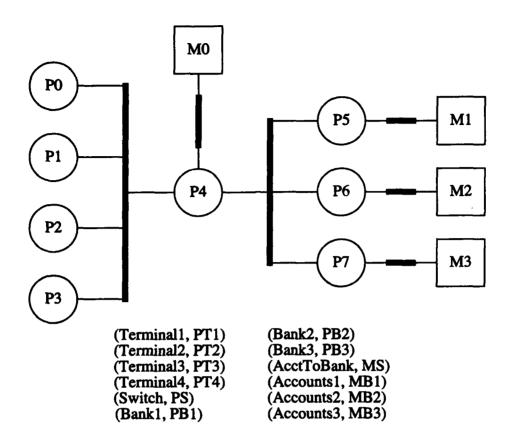

The system includes a simple mechanism for mapping software (logical) components to hardware (physical) components. A mapping consists of pairs of software components (processes and stores) and hardware components (processors and memories) taken from their respective definitions. Such a mapping results in an embedding of the dataflow graph of logical connections into the architecture graph of physical connections. A simple illustration of the flexibility afforded by having distinct software and hardware models with explicit allocation appears in Figure 3.

# **4 PROTO TOOLS**

This section describes Proto in terms of its user tools and high-level architecture. These tools are used to build software and hardware prototype models, perform simulations, and generate code.

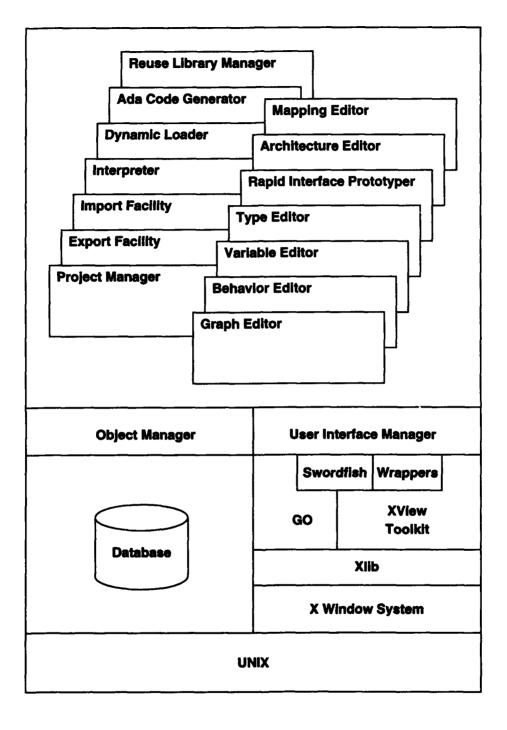

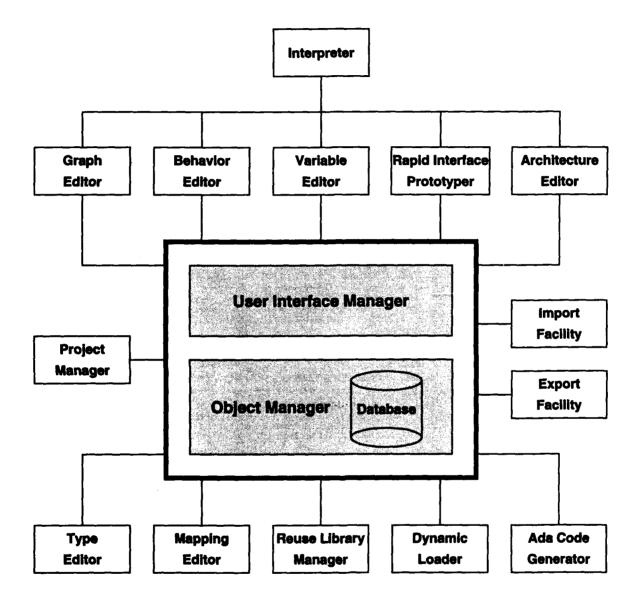

# 4.1 SYSTEM DESCRIPTION

Figure 4 depicts the high-level implementation architecture of Proto. The system is primarily implemented in C++ and built on top of the Unix operating system. There are also a number of implemented Ada modules for support of the code generation tool. Database management services are provided by the Object Manager (OM), which is based on a commercial object-oriented database. The User Interface Manager (UIM) supplies graphical and textual interface services to most system tools. This manager is based on capabilities of the X Window System server, which provides low-level, device-independent network graphics services.

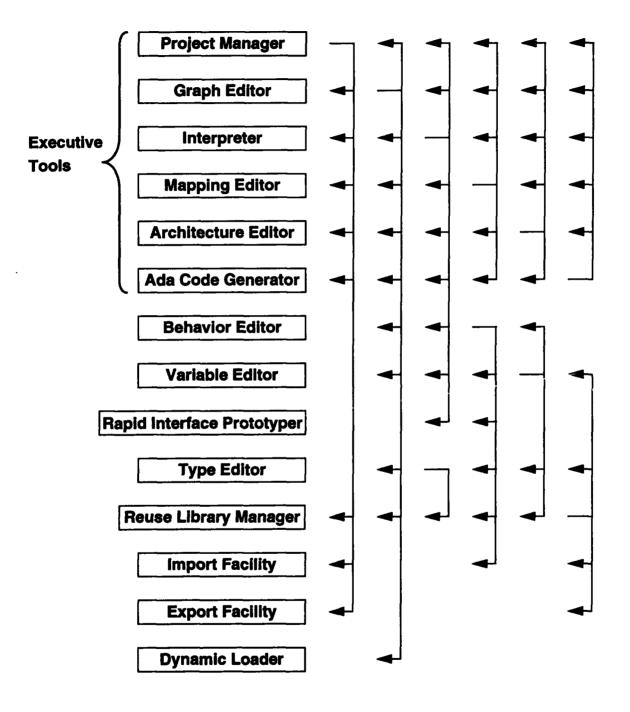

Proto contains 14 tools, which are categorized into six functional areas and briefly described below. More complete explanations of the tool functions appear in subsequent sections.

## Software Prototyping

- Project Manager. Creation, renaming, and deletion of SSDL prototypes

- Graph Editor. Multiwindow graphical editing of SSDL dataflow graphs

- Behavior Editor. Textual editing of SSDL process behaviors

- Type Editor. Multiwindow menu-based and graphical editing of object-based types

- Variable Editor. Multiwindow menu-based editing of scoped variable specifications

## Component Reuse

- Reuse Library Manager. Management and access to SSDL component libraries

- Dynamic Loader. Loading and linking of external C routines

- Export Facility. Generation of an ASCII file representation for a project

- Import Facility. Recreation of a project from an ASCII file representation

## User Interface Prototyping

• **Rapid Interface Prototyping System.** REED tool that provides graphical definition of application user interface prototypes

**Final Report for Proto**

Figure 3. Software/Hardware Allocation Example

International Software Systems, Inc.

Figure 4. Proto Implementation Architecture

#### Architecture Modeling

- Architecture Editor. Graphical editing of multiple instruction, multiple data stream (MIMD) hardware component topologies

- Mapping Editor. Software/hardware component mappings

### Simulation-Based Prototype Execution

• Interpreter. Functional execution and performance evaluation using simulation, animation, and debugging mechanisms

### Code Generation

• Ada Code Generator. Generation of multitasked Ada from SSDL specification prototypes

## 4.1.1 User Interface Manager

The UIM collects graphical and textual user inputs and distributes them to appropriate tools. The UIM also manages the multiwindow display screen. In this manner, Proto keeps a clean separation between user-interface functions and application functions that operate on application data. Consequently, the system shields tool applications from modifications and enhancements to the user interface.

The UIM provides Proto tools direct access to

- GO (Graphic Objects). C++-based graphic object manipulation package that references graphics rendering capabilities obtained from Xlib. GO gives application developers access to higher-level graphical primitives and editing operations than those available with Xlib and the X Window System standard.

- XView Toolkit. Sun Microsystems presentation-layer library widgets (user interface objects) for window management that facilitate tool integration based upon the OPEN LOOK protocol standard.

- Wrappers. C++-based object interface package that references the widget manipulation capabilities obtained from the XView Toolkit. Wrappers gives application developers a higher-level interface to OPEN LOOK style widgets than is available from the XView Toolkit.

- Swordfish. Graph editor builder capability that supports construction of customizable graph editors from descriptions containing information about abstract-graph connectivity, icon-based renderings, and C++ semantic classes.

## 4.1.2 Object Manager

Proto uses an object-oriented database, or object base, to manage persistence and sharing of specification artifacts, including SSDL prototypes, architecture descriptions, and reuse libraries. The OM provides an application-level interface for controlled access to the database. Proto supports simultaneous access to multiple databases by multiple users in order to acquire reusable component libraries. Because of database limitations, however, opening of a database is limited to a single user at any given time. The OM is based on the ONTOS Object Database, a commercial

object-oriented database for C++ class instances. A save capability for explicitly storing user data in the database is available from most Proto editing tools.

# 4.2 TOOLS