Ordering No.: CRTA-CE

# Introduction to Concurrent Engineering: Electronic Circuit Design and Production Applications

# 1992

Prepared by:

Reliability Analysis Center PO Box 4700 Rome, NY 13440-8200

Under contract to:

Rome Laboratory Griffiss AFB, NY 13441-5700

DTIC GUALLY LICTICIED 3

# **Reliability Analysis Center**

A DoD Information Analysis Center

Approved for Public Release, Distribution Unlimited

The information and data contained herein have been compiled from government and nongovernment technical reports and from material supplied by various manufacturers and are intended to be used for reference purposes. Neither the United States Government nor IIT Research Institute warrant the accuracy of this information and data. The user is further cautioned that the data contained herein may not be used in lieu of other contractually cited references and specifications.

Publication of this information is not an expression of the opinion of the United States Government or of IIT Research Institute as to the quality or durability of any product mentioned herein and any use for advertising or promotional purposes of this information in conjunction with the name of the United States Government or IIT Research Institute without written permission is expressly prohibited. The Reliability Analysis Center (RAC) is a Department of Defense Information Analysis Center sponsored by the Defense Technical Information Center, managed by the Rome Laboratory (formerly RADC), and operated by IIT Research Institute (IITRI). RAC is chartered to collect, analyze and disseminate reliability information pertaining to systems and parts used therein. The present scope includes integrated circuits, hybrids, discrete semiconductors, microwave devices, optoelectronics and nonelectronic parts employed in military, space, industrial and commercial applications. The scope of the reliability activities include the related disciplines of Maintainability, Testability, Statistical Process Control, Electrostatic Discharge, and Total Quality Management.

The data contained in the RAC databases are collected on a continuous basis from a broad range of sources, including testing laboratories, device and equipment manufacturers, government laboratories and equipment users (government and industry). Automatic distribution lists, voluntary data submittals and field failure reporting systems supplement an intensive data solicitation program. Users of RAC data are encouraged to submit reliability data to RAC to enhance these data collection efforts.

Reliability data and analysis documents covering most of the device types mentioned above are available from the RAC. Also, RAC provides reliability consulting, training, technical and bibliographic inquiry services which are noted at the end of this document.

REQUEST FOR TECHNICAL ASSISTANCE AND INFORMATION ON AVAILABLE RAC SERVICES AND PUBLICATIONS MAY BE DIRECTED TO:

Reliability Analysis Center 201 Mill Street Rome, NY 13440

# TQM Inquiries: (800) 526-4804 Non-Technical Inquiries: (315) 330-4151 (315) 337-0900 (315) 337-9933 Technical Inquiries: (315) 337-9933 TeleFax: (315) 337-9932

#### ALL OTHER REQUESTS SHOULD BE DIRECTED TO:

Rome Laboratory ERSS/Duane A. Gilmour Griffiss AFB, NY 13441-5700

| (800) 526-4804<br>(315) 330-4151               | Telephone:<br>Autovon: | (315) 330-2660<br>587-2660                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                                                | -<br>i                 | Accession For                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| (315) 337-9933                                 | 1                      | RTIS JEARI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1     |

| (315) 337-9932                                 |                        | ille 125 D<br>Unapponnet D<br>Justicostica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                |                        | By                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1<br> |

| © 1992, IIT Research Ins<br>All Rights Reserve |                        | North Contraction of the second secon |       |

| iii                                            | ŕ                      | X-1 AN AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| REPORT DOCU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MENT                         | ATION                      | PAC           | GE                  | Form Approved                                                            |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------|---------------|---------------------|--------------------------------------------------------------------------|--|

| OMB No. 0704-0188<br>Public reporting burden for this collection of information is estimated to                                                                                                                                                                                                                                                                                                                                                                                                                                                                | o average 1 hour per re      | sponse, including the time | for reviewing | g instructions, see | urching, existing data sources, gathering and                            |  |

| maintaining the data needed, and completing and reviewing the colle-<br>including suggestions for reducing this burden, to Washington Headq<br>VA 22202-4302, and to the Office of Management and Budget. Paperwo                                                                                                                                                                                                                                                                                                                                              | ction of information. S      | Send comments regarding    | this burden a | etimate or any of   | ther aspect of this collection of information.                           |  |

| VA 22202-4302, and to the Office of Management and Budget. Paperwo<br>1. AGENCY USE ONLY (Leave Blank)                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2 REPORT D                   |                            |               |                     | AND DATES COVERED                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                            |               |                     |                                                                          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Septer                       | mber 1992                  |               |                     |                                                                          |  |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |                            |               | 5.                  | FUNDING NUMBERS                                                          |  |

| Introduction to Concurrent Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | : Electronic Ci              | rcuit Design and           |               |                     | 6528                                                                     |  |

| Production Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                              |                            |               | I                   |                                                                          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                            |               |                     |                                                                          |  |

| Norman B. Fuqua                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                            |               |                     |                                                                          |  |

| 7. PERFORMING ORGANIZATION NAME(S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ) AND ADDRE                  | SS(ES)                     |               | RFORMING            | ORGANIZATION                                                             |  |

| Reliability Analysis Center                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |                            |               |                     |                                                                          |  |

| P.O. Box 4700                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |                            |               | CR                  | RTA-CE                                                                   |  |

| Rome, NY 13440-8200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ANE AND                      | ADDRESS                    | L             | 10 0001             |                                                                          |  |

| 9. SPONSORING/MONITORING AGENCY N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IAME(5) AND                  | auukess(es)                |               |                     | NSORING/MONITORING                                                       |  |

| Defense Technical Information Center                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (DTIC-AI)                    |                            |               |                     |                                                                          |  |

| Cameron Station                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                            |               | F                   | F30602-91-C-0002                                                         |  |

| Alexandria, VA 22314-6145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |                            |               |                     | <u></u>                                                                  |  |

| Hard copies available from the Reliab<br>(Price: \$75.00 U.S., \$85.00 Non-U.S.).                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | oility Analysis              | Center, 201 Mil            | ll Street,    | Rome, NY            | ′ 13440- <del>6</del> 916.                                               |  |

| 12a. DISTRIBUTION/AVAILABILITY STATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MENT                         |                            | 12b. D        | DISTRIBUTI          | ON CODE                                                                  |  |

| Approved for public release; distribution unlimited.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |                            | Unclassified  |                     |                                                                          |  |

| 13. ABSTRACT (Maximum 200 words)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              | ·····                      |               |                     |                                                                          |  |

| This document presents an overview of Concurrent Engineering (CE), i.e., the use of <u>Multi-discipline Design Teams</u> to perform the simultaneous design of the product and the process to produce the product. The intent is to encourage product developers, from the outset, to consider all elements of the product life cycle from conception through disposal, including quality, cost, schedule and the user requirements. The document also explores a number of specific tools which may be used to assist the reader in the implementation of CE. |                              |                            |               |                     |                                                                          |  |

| 14. SUBJECT TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |                            | T             | 15. NUMB            | ER OF PAGES                                                              |  |

| Concurrent Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                            | pline Design Tea           | ams           |                     | 120                                                                      |  |

| Product Life Cycle<br>Automated Design Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Robust Design<br>Design, Dev | gn<br>relopment, Prodi     | action        |                     |                                                                          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 200.611, 200                 |                            |               | 16. PRICE COD       | Æ                                                                        |  |

| 17. SECURITY CLASSIFICATION 18. SECURITY CLASSIFIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CATION 19.                   | SECURITY CLASSIFICAT       |               |                     | DN OF ABSTRACT                                                           |  |

| NSN 7540-01-280-5500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |                            | I             | P                   | itandard Form 298 (Rev. 2-89)<br>rescribed by ANSI Std. Z349-18<br>8-102 |  |

#### FOREWORD

Concurrent Engineering (CE) utilizes Multi-discipline Design Teams to perform the simultaneous design of the product and all of the life-cycle processes associated with the product that are required to meet the user's needs. CE begins with a complete identification of these user needs, some of which may be conflicting in nature, and then seeks to optimize the design of both the product and the process over this entire spectrum of needs to assure maximum customer satisfaction. Organizations, which fail to take advantage of CE's benefits and fail to utilize CE in their design process, may eventually cease to be competitive in the world marketplace.

CE, which emphasizes Multi-parameter Optimization of the design, is still an emerging concept which means that not all facets of the technology are firmly in place. The automated tools, used as one means of implementing CE, are incomplete or non-existent in some areas, and highly fragmented in others. However, they will continue to be improved, integrated, and made accessible to multi-user engineering workstations. This trend will continue to enhance the synergistic relationship between the various technical disciplines.

The demonstrated effectiveness of a CE design approach in reducing development time and development cost while at the same time enhancing customer satisfaction for commercial products has made this approach prudent for Department of Defense (DoD) also. MIL-STD-499B "Systems Engineering" (when approved) will implement the technical essence of Concurrent Engineering in new DoD procurement contracts by requiring: a) the simultaneous development of system products and life-cycle processes to satisfy user needs, b) the utilization of multidisciplinary teams, and c) a systems engineering methodology. Separate DoD procurement requirements (CALS) also obligate the contractor to consider some form of automated interchange of technical information in lieu of paper deliverables. Combined together, these factors will have significant contractual impact upon Reliability, Maintainability, Safety and Logistics requirements.

vi

•

## **TABLE OF CONTENTS**

| SECTI  | ON 1: THE NEED FOR CONCURRENT ENGINEERING                 | Pa |

|--------|-----------------------------------------------------------|----|

|        | E NEED FOR CONCURRENT ENGINEERING                         |    |

|        | The Problem - Loss of Markets and Loss of Competitiveness |    |

|        | The Solution: Concurrent Engineering                      |    |

| 1.4    | 1.2.1 The Essence of Concurrent Engineering               |    |

|        | 1.2.2 The Process: Translation of the Requirements Into   |    |

|        | The Product                                               |    |

|        | 1.2.3 The Philosophy: Continuous and Aggressive Design    |    |

|        | Incrovement                                               |    |

| Ì.3    | Improvement<br>Some Common Misconceptions Regarding CE    |    |

| 1.5    | The Benefits of Congument Engineering                     |    |

|        | The Benefits of Concurrent Engineering.                   |    |

| 1.5    | Management Challenges of Concurrent Engineering           |    |

| 1.6    | The Multi-Discipline Team Concept                         |    |

| 1.7    | The Need for Concurrent Engineering References            |    |

| SECTI  | ON 2: ROBUST CIRCUIT DESIGN                               |    |

| 2.0 RC | BUST CIRCUIT DESIGN                                       |    |

| 2.1    | Robust Circuit Design Parts Database                      |    |

| 2.2    | Environmental Considerations                              |    |

|        | Robust Circuit Analysis                                   |    |

|        | 2.3.1 Extreme Value Analysis (EVA) or Absolute Worst Case |    |

|        | 2.3.2 Root-Sum-Squared                                    |    |

|        | 2.3.3 Monte Carlo Simulation.                             |    |

|        | 2.3.4 Application of the Various Methods                  |    |

| 2.4    | Taguchi Methods and Design of Experiments                 |    |

| 2.5    |                                                           |    |

| 2.0    | Robabi Cheur Design References                            | •  |

| SECTI  | ON 3: RELIABILITY AND MAINTAINABILITY CONSIDERATIONS      |    |

| 3.0 RE | LIABILITY AND MAINTAINABILITY CONSIDERATIONS              |    |

| 3.1    | Reliability Program                                       |    |

|        | 3.1.1 Reliability Modeling and Prediction                 |    |

|        | 3.1.1.1 Reliability Modeling Methods                      |    |

|        | 3.1.1.2 Reliability Prediction Methods                    |    |

|        | 3.1.1.3 Tailoring Reliability Models and Predictions      |    |

|        | 3.1.2 Part Derating                                       |    |

|        | 3.1.3 Failure Mode, Effects and Criticality Analysis      |    |

|        | 3.1.4 Fault Tree Analysis                                 |    |

|        | 3.1.4.1 Fault Tree Construction                           | 4  |

|        | 3.1.4.2 Qualitative Evaluations - Cut Sets                |    |

|        | 3.1.4.3 Qualitative Importances                           |    |

|        |                                                           |    |

## **TABLE OF CONTENTS (Cont'd)**

|     | _                                       |                                                                | <u>Page</u> |

|-----|-----------------------------------------|----------------------------------------------------------------|-------------|

| 3.0 | RE                                      | LIABILITY AND MAINTAINABILITY CONSIDERATIONS (Cont'd)          |             |

|     |                                         | 3.1.4.4 Common Cause Susceptibilities                          | 44          |

|     |                                         | 3.1.4.5 Quantitative Evaluations                               |             |

|     |                                         | 3.1.4.6 Additional Reference Source                            |             |

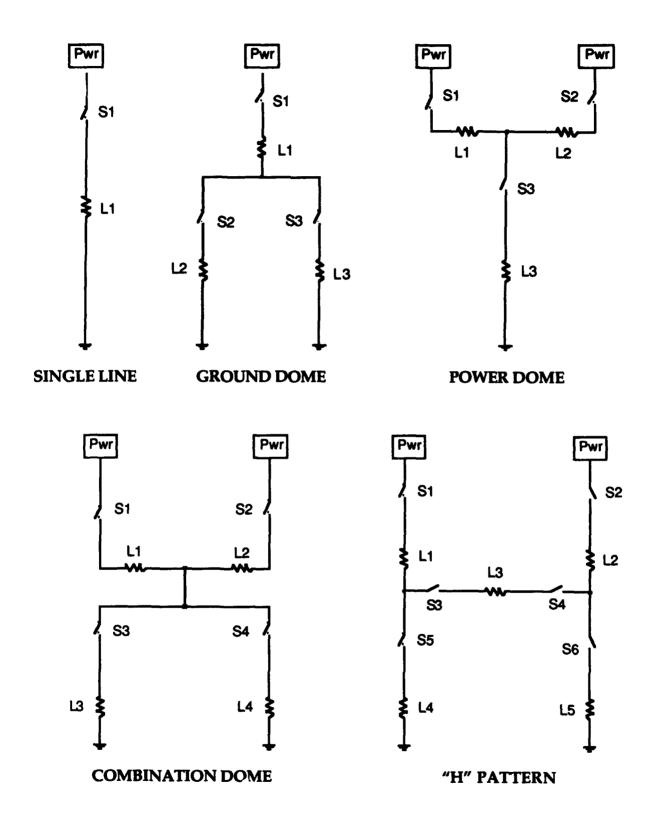

|     |                                         | 3.1.5 Sneak Circuit Analysis                                   | <b>46</b>   |

|     |                                         | 3.1.5.1 Topological Pattern Identification                     |             |

|     |                                         | 3.1.5.2 Clue Application                                       |             |

|     |                                         | 3.1.5.3 Recent SCA Developments                                | 47          |

|     |                                         | 3.1.6 Finite Element Analysis                                  |             |

|     |                                         | 3.1.6.1 Fatigue Life Prediction                                |             |

|     |                                         | 3.1.6.2 Creep and Stress Relaxation                            |             |

|     |                                         | 3.1.7 Failure Reporting Analysis and Corrective Action Systems | 51          |

|     |                                         | 3.1.7.1 DoD FRACAS Requirements                                | 54          |

|     |                                         | 3.1.7.2 FRACAS In Industry Applications                        | 55          |

|     | 3.2                                     | Maintainability Program                                        |             |

|     |                                         | 3.2.1 Maintainability Prediction                               |             |

|     | 3.3                                     | Reliability and Maintainability References                     |             |

|     |                                         | 3.3.1 DoD Specifications, Standards, and Handbooks             | 58          |

|     |                                         | 3.3.2 Other Source Documents                                   |             |

|     |                                         | 3.3.3 References                                               | 60          |

|     |                                         |                                                                |             |

|     |                                         | ON 4: PRODUCTION CONSIDERATIONS                                |             |

|     |                                         | ODUCTION CONSIDERATIONS.                                       |             |

|     | 4.1                                     | Producibility Engineering                                      |             |

|     |                                         | 4.1.1 Specific Characteristics of the Design                   |             |

|     |                                         | 4.1.2 Characteristics of Production Planning                   |             |

|     | 4.2                                     | ······································                         |             |

|     | 4.3                                     | Environmental Stress Screening                                 |             |

|     |                                         | 4.3.1 The MIL-STD-2164 Approach to ESS                         |             |

|     |                                         | 4.3.2 The DOD-HDBK-344 Approach to ESS                         |             |

|     |                                         | 4.3.3 Institute of Environmental Sciences                      | 70          |

|     | 4.4                                     | Producibility References                                       | 70          |

| CT/ | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |                                                                |             |

|     |                                         | DN 5: TESTABILITY CONSIDERATIONS                               | -           |

|     |                                         | STABILITY CONSIDERATIONS                                       |             |

|     | 5.1                                     | Design for Testability Objectives and Requirements             |             |

|     | 5.2                                     | Testability Program Monitoring and Control                     | 76          |

|     | 5.3                                     | Testability Design and Analysis                                | 77          |

|     | 5.4                                     | Tailoring a Testability Program                                |             |

|     | 5.5                                     | ANSI/IEEE Standard 1149.1                                      | 79          |

|     | 5.6                                     | Testability References                                         | 80          |

## **TABLE OF CONTENTS (Cont'd)**

Page

| SECTI  | ON 6: COMPLEMENTARY EFFORTS AND ACTIVITIES                  |           |

|--------|-------------------------------------------------------------|-----------|

| 6.0 CC | MPLEMENTARY EFFORTS AND ACTIVITIES                          | 83        |

| 6.1    | Computer-Aided Acquisition and Logistics (CALS)             | 83        |

| 6.2    | MIL-HDBK-59 Requirements                                    | 83        |

| 6.3    | •                                                           | 85        |

| 6.4    | •                                                           | 86        |

|        | 6.4.1 DICE                                                  | 86        |

|        | 6.4.2 CAD Framework Initiatives                             | 86        |

| 、      | 6.4.3 RAMCAD                                                | 87        |

| 6.5    | Complementary Efforts and Activities References             | 87        |

|        | ON 7: CURRENTLY AVAILABLE AUTOMATED TOOLS                   |           |

| 7.0 RE | PRESENTATIVE SAMPLE OF AVAILABLE AUTOMATED TOOLS            | 91        |

| 7.1    | Electrical and Electronic Design Analysis Tools             | 92        |

|        | 7.1.1 Schematic Capture Packages                            | 92        |

|        | 7.1.2 Analog Circuit and Digital Logic Simulation and       |           |

|        | Analysis Tools                                              | <b>93</b> |

| 7.2    |                                                             | 96        |

| 7.3    |                                                             | 97        |

| 7.4    | Reliability Analysis Software Tools                         | <b>98</b> |

|        | 7.4.1 Detail Stress Electronic Reliability Prediction       | 99        |

|        | 7.4.1.1 MIL-HDBK-217 Based Predictions                      | 100       |

|        | 7.4.1.2 Non-MIL-HDBK-217 Based Predictions                  | 100       |

|        | 7.4.2 Reliability Prediction - Part Count                   | 101       |

|        | 7.4.3 Mechanical Reliability Prediction                     |           |

|        | 7.4.4 Nonoperating Reliability Prediction                   |           |

|        | 7.4.5 Failure Modes, Effects and Criticality Analysis Tools |           |

|        | 7.4.6 Fault Tree Analysis Tools                             | 104       |

|        | 7.4.7 MARKOV Reliability Modeling Tools                     | 105       |

|        | 7.4.8 Failure Reporting Analysis and Corrective Action      |           |

|        | System Tools                                                | 106       |

|        | 7.4.9 Automated Sneak Circuit Analysis                      |           |

| 7.5    | Maintainability Analysis Tools                              |           |

| 7.6    | Mathematical/Graphical Analysis Tools                       | 108       |

| 7.7    | Testability Analysis Tools                                  |           |

| 7.8    | Finite Element Analysis Tools                               |           |

| 7.9    | Automated Tool References                                   |           |

|        |                                                             |           |

## TABLE OF CONTENTS (Cont'd)

| SECTION 8: SOME CHALLENGES FOR CE IN TODAY'S AUTOMATION<br>ENVIRONMENT | Page |

|------------------------------------------------------------------------|------|

|                                                                        |      |

| 8.0 SOME CHALLENGES FOR CE IN TODAY'S AUTOMATION<br>ENVIRONMENT        | 115  |

| 8.1 Present Database Limitations                                       | 115  |

| 8.2 Limitations of Today's Automated Tools                             | 115  |

| 8.3 Challenges for CE References                                       | 116  |

## APPENDIX A: RAC PRODUCTS

## LIST OF FIGURES

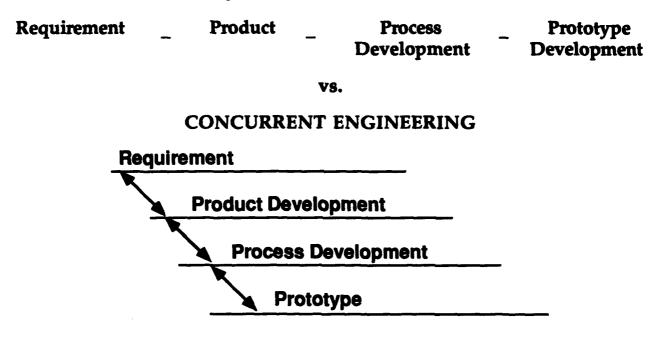

| A COMPARISON OF SEQUENTIAL AND CONCURRENT    |              |

|----------------------------------------------|--------------|

| ERING                                        | 2            |

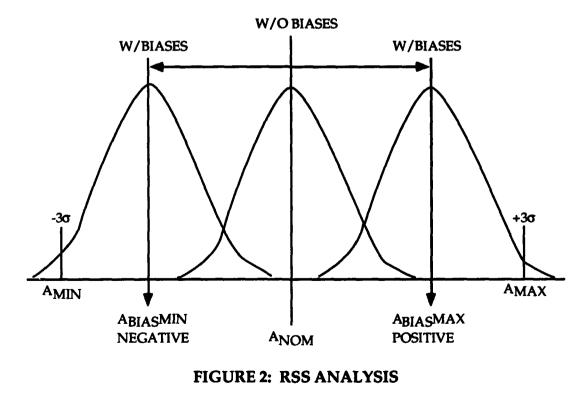

| RSS ANALYSIS                                 | 18           |

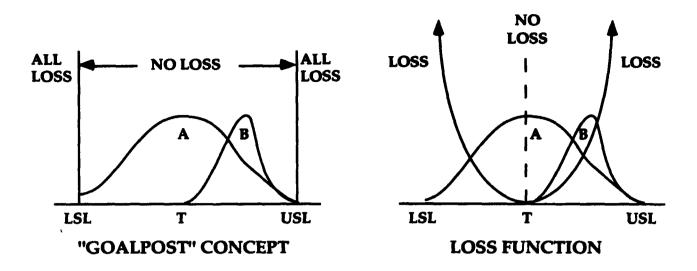

| TAGUCHI LOSS FUNCTION                        | 20           |

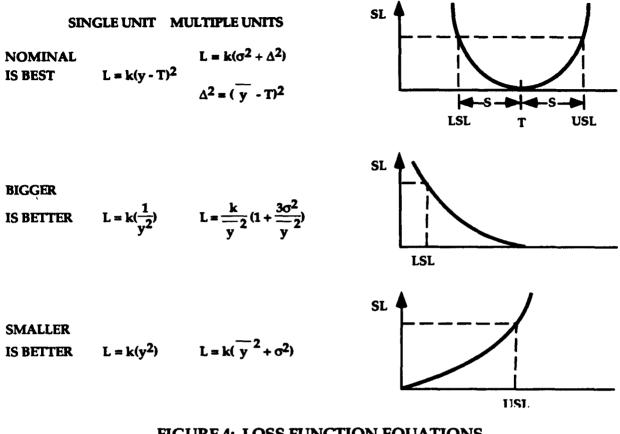

| LOSS FUNCTION EQUATIONS                      | 20           |

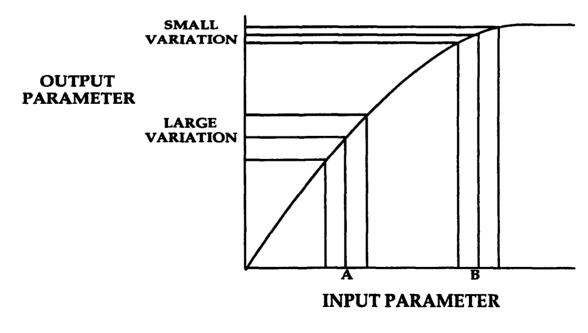

| PARAMETER DESIGN                             | 21           |

| SIGNAL-TO-NOISE RATIOS                       | 22           |

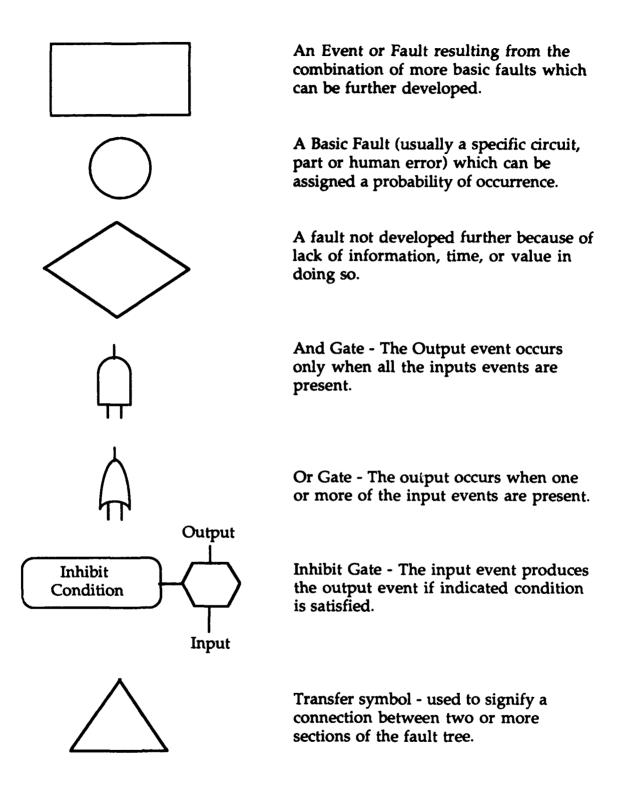

| FAULT TREE SYMBOLS                           | 43           |

| BASIC TOPOGRAPHS                             | 48           |

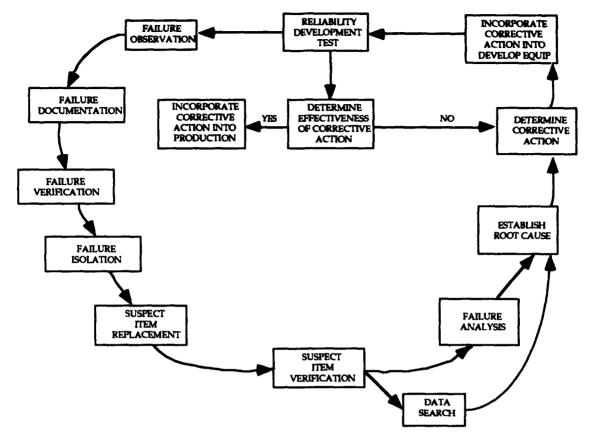

| CLOSED LOOP FAILURE REPORTING AND CORRECTIVE |              |

| SYSTEM.                                      | 53           |

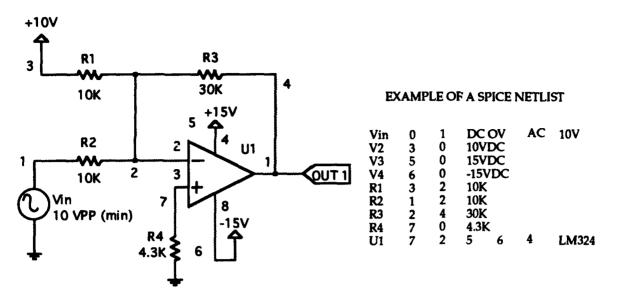

| EXAMPLE CIRCUIT AND APPLICABLE NETLIST       | <b>93</b>    |

|                                              | RSS ANALYSIS |

## LIST OF TABLES

| TABLE 1: | PARTS TYPES VS. PRINCIPLE SOURCES OF VARIATION | 16 |

|----------|------------------------------------------------|----|

| TABLE 2: | MIL-STD-785B APPLICATION MATRIX                | 28 |

| TABLE 3: | USES OF RELIABILITY MODELS AND PREDICTIONS     | 32 |

| TABLE 4: | OBJECTIVES OF A FRACAS PROGRAM                 | 52 |

| TABLE 5: | MIL-STD-470 APPLICATION MATRIX                 | 57 |

# **SECTION 1**

# THE NEED FOR CONCURRENT ENGINEERING

## **1.0 THE NEED FOR CONCURRENT ENGINEERING**

Engineering and production organizations all over the world are under increasing pressure to become more profitable in today's business environment. Defense, non-defense and commercial industries are all facing similar competitive pressures.

#### 1.1 The Problem: Loss of Markets and Loss of Competitiveness

Some of the major deterrents to competitiveness in world markets today are: the failure to meet the user's needs, excessive cost, perceived poor quality and excessive time, required to design and introduce a new product. CE ceeks to improve customer satisfaction by a recognition of all of the user's sometimes conflicting requirements and optimizing the design over the entire spectrum of user needs including cost and quality.

The delays in product introduction are due largely to the serial nature of the historic design process. In this serial structure each speciality labors on the design alone until they have completed their portion of the effort and then passes the design on to the next speciality. This further reinforces a "stovepipe mentality" whereby each technical speciality is interested only in optimizing the design for their specific concern.

With this scenario in place, the individual contributions of each of the various "ilities" (Reliability, Maintainability, Testability, Producibility, etc.) to the total design effort is not coordinated. Each engineer may be an expert in his field and very talented in his own right, but until they all work well together, the development process is inefficient and less than ideal.

Too frequently the perceived philosophy is for the product designers to complete their preliminary design then pass it on to the next discipline when they are satisfied with it and move on to something new. The design process today is much too complex for any one person to totally accomplish alone. Many years ago, a single designer might be expected to have an intuitive knowledge of all of the necessary areas of expertise, but with the higher levels of complexity of today's products, human intuition is less than effective. Today, inputs from experts with experience in a variety of diverse disciplines is needed to assure a viable product design.

## **1.2** The Solution: Concurrent Engineering

CONCURRENT ENGINEERING IS A SYSTEMATIC APPROACH TO THE INTEGRATED, CONCURRENT DESIGN OF PRODUCTS AND THEIR RELATED PROCESSES, INCLUDING MANUFACTURING AND SUPPORT. THIS APPROACH IS INTENDED TO CAUSE THE DEVELOPERS, FROM THE OUTSET, TO CONSIDER ALL ELEMENTS OF THE PRODUCT LIFE CYCLE FROM

# CONCEPTION THROUGH DISPOSAL, INCLUDING QUALITY, COST, SCHEDULE, AND USER REQUIREMENTS. [Reference 2].

As shown in Figure 1, this is in marked contrast to the traditional design approach which fragments product development into a series of isolated engineering specialities, each speciality working on the product in a sequential development manner. The intent of CE is to cause product developers to consider all elements of the product life cycle from conception through disposal, including: quality, cost, schedule, and user requirements.

## SEQUENTIAL ENGINEERING

#### FIGURE 1: A COMPARISON OF SEQUENTIAL AND CONCURRENT ENGINEERING

CE of a Product includes concurrent application of each of the various engineering specialities including the traditional electrical design, mechanical design and thermal design as well as all of the other applicable "ilities": reliability, maintainability, testability, producibility, supportability, safety, logistics, etc.

## 1.2.1 The Essence of Concurrent Engineering

CE utilizes Multi-discipline Design Teams to perform the simultaneous design of the product, the production process and all of the associated product support processes. It emphasizes multi-parameter optimization of the design. CE recognizes that the manufacturing options are often dictated by design choices that may be arbitrary in nature. It seeks to correct this situation by mandating and implementing closer communication between the product design staff and the process design staff. A Multi-discipline Design Team approach accelerates the synergistic relationships between all of the various functional disciplines.

There are three critical elements [Reference 2] related to CE which should be explored in greater depth; The Timing, The Process and The Philosophy.

#### 1.2.2 <u>The Process: Translation of the Requirements Into the Product</u>

The effective and timely contribution of all responsible participants in the design, manufacturing and use cycle, together with the objective identification and evaluation of any necessary trade-offs between potential conflicting requirements, is imperative.

CE may sometimes be viewed as serving at least three different customers: a) the end user of the product being developed, b) the manufacturer of the product, and c) the service organization that will ultimately support the product. Since customers often do not understand the subtleties of their needs and even more frequently the limits of technology, realistic product development becomes a problem-solving process among multiple customers and multiple functional experts working as a team. [4]

A technique that has been found to be effective in assuring that the customers' diverse requirements are adequately reflected in the design of the product is that of Quality Function Deployment (QFD). "Deployment" in this sense means "an extension or broadening of the quality activity" beyond its historical bounds of inspection and process control into the sphere of product development as well. The QFD process begins by considering the product or service from the customer's perspective, i.e., elucidate what the customer would like if the product or service were ideal. These nonparametric "customer perceived quality characteristics" are then translated, by the multi-discipline design team, into "quantifiable design characteristics." QFD thus enables the design team to transition smoothly from the "world of the customer" to "the world of the engineer." [5]

Some of the major elements of this translation process include:

- INTEGRATED PARTICIPATION Continuing integrated participation of multi-function teams in the design of the product, the process and the product's support is essential.

- ITERATION AND CLOSURE OF PRODUCT AND PROCESS DESIGN -The process of integrating multiple engineering, manufacturing, and management functions must provide for the efficient iteration and closure of both the product design and the process design.

- CONFLICT RESOLUTION The methodology must also identify conflicting requirements and support their effective resolution through an objective choice of options based upon a quantitative or a qualitative comparison or trade-off, as appropriate.

- OPTIMIZATION OF BOTH THE PRODUCT AND PROCESS DESIGN It must assure the best possible design, within the given constraints.

## 1.2.3 The Philosophy: Continuous and Aggressive Design Improvement

The philosophy of CE contains a number of key elements including:

- CONTINUOUS, OPEN COMMUNICATION This inclucommunication between customer and vendor, both within customer's organization and the vendor's organizations.

- COMPLETE UNAMBIGUOUS STATEMENT OF USER REQUIREMENTS -This statement of requirements must include definitive priorities of the various requirements to be applied in case a trade-off analysis becomes necessary.

- COMPLETE UNAMBIGUOUS DESCRIPTION OF THE PRODUCT AND ITS RELATED PROCESSES - The goal should be to establish a close working relationship and open lines of communication between the customer and the vendor.

- BASELINE PRODUCT AND PROCESS EVALUATION This evaluation must be completed prior to full scale production. It should include benchmarking of the proposed product against similar world-class products.

#### 1.3 Some Common Misconceptions Regarding CE

There are a number of common misconceptions relating to CE that should be addressed and corrected. The truths regarding CE include the following:

• CE IS NOT A MAGIC FORMULA FOR SUCCESS - A talented design and production team and a lot of hard work is still necessary to assure a successful end product. It means using a scientific approach, making decisions based on data rather than hunches, looking for antecedent causes of problems rather than reacting to superficial symptoms, seeking permanent solutions rather than relying on quick fixes. This is accomplished by utilizing techniques such as experimental design, simulation modeling, and mathematical analyses to seek to provide a

4

deeper understanding of interrelationships and determine root cause effects.

- CE DOES NOT ELIMINATE ANY ENGINEERING FUNCTION In CE all downstream processes are co-designed toward a more all-encompassing, cost-effective design solution. Specialty engineering contributions should accentuate finding root causes and solutions to these problems.

- CE DOES NOT SIMPLY OVERLAP THE DESIGN AND PRODUCTION TASKS The design of both the product and the downstream processes are to be completed prior to the start of any production.

- CE IS NOT JUST DESIGN FOR PRODUCIBILITY, OR DESIGN FOR RELIABILITY, OR DESIGN FOR MAINTAINABILITY - CE involves the optimization and integration of all design disciplines within a costeffective design process.

- CE IS NOT SIMPLY CONSERVATIVE DESIGN CE attempts to optimize the design over a larger set of processes and determines how to achieve the requirements using the lower costs.

- CE DOES NOT IMPLY CONSERVATISM IN THE INCORPORATION OF NEW TECHNOLOGIES IN THE PRODUCT - Thorough understanding of the design and control of their applicable manufacturing processes are the essential elements.

- CE DOES NOT REQUIRE CONSERVATIVE TESTING STRATEGY CE tries to approach one-pass designs; rather than repeated test-and-fix design cycles. In software design, a negative correlation has actually been found [Reference 3] between the reliability of the software and the number of trial debugging runs performed by the designer (i.e., DO IT RIGHT THE FIRST TIME!).

- CE DOES NOT IMPLY CONSERVATIVE INSPECTION STRATEGIES CE seeks to achieve production repeatability through design robustness of both the product and its production process, i.e. a production process that provides adequate means for the monitor and control of its essential parameters.

## **1.4** The Benefits of Concurrent Engineering

Some of the benefits derived from using a concurrent engineering design approach rather than the conventional serial design approach include:

• A SIGNIFICANT REDUCTION IN THE TIME NECESSARY TO ITERATE A DESIGN - Design analyses which formerly took several engineers weeks to determine, can now be accomplished in several hours using automated design tools.

- DEVELOPMENT OF RAPID REPRESENTATIVE PROTOTYPES A prototype which accurately reflects both the design and the manufacturing process becomes easier to accomplish as the design process is moved out of the laboratory and onto engineering workstations. Using modern digitally based manufacturing techniques such as flexible manufacturing, stereo-lithography (e.g., 3-D printing) and selective laser sintering it is possible to quickly and economically execute prototypes, from a variety of materials, which accurately reflect the form, fit, and function of the final production configuration. The necessary digital design data comes directly from the applicable CAD workstation.

- ELIMINATION OF "FUNCTIONAL STOVEPIPE" MENTALITY -Sophisticated computerized tools permit designers to begin considering the implications of each "ility" much earlier in the design cycle.

- PHYSICAL PROXIMITY IS NOT NECESSARILY REQUIRED A common electronic database may eliminate the need to consolidate the design team at a single location. CE promotes an improved interchange of information between the various engineering disciplines.

- DESIGN CHANGES ARE IMMEDIATELY AVAILABLE TO ALL TEAM MEMBERS With a common electronic database, design changes made by one team member are immediately available for evaluation by all of the team members.

- REDUCED TOOLING IMPACT CAD/CAM-based flexible manufacturing configurations minimize the tooling impact of changes and permit rapid correction of most design-oriented problems.

- REDUCED NEED FOR MOCK-UPS Effective computerized models frequently reduce or eliminate a need for mock-ups. This becomes more obvious as the design process is moved out of the laboratory and onto engineering workstations with enhanced graphic presentations.

- WITH CE QUALITY ASSURANCE BECOMES A PROBLEM SOLVER RATHER THAN A "POLICEMAN" - The major role of QA, is changed from simply finding bad parts to reducing process variability which ensures the stability of the manufacturing process and prevents the making of bad parts.

6

## 1.5 Management Challenges of Concurrent Engineering

The implementation of CE within an organization familiar with a serial design process is not going to be easy.

#### CE REQUIRES A BASIC CHANGE IN THE WAY COMPANIES CONDUCT BUSINESS

In contrast to the historic philosophy, manufacturing and tooling personnel must now be an integral part of the design team. Also, Statistical Process Control (SPC) is absolutely essential to control and reduce process variability.

Middle Management is frequently the most difficult sector to get involved in this revolutionary change. The associated cultural and management changes are usually harder to direct than are the technical changes.

#### 1.6 The Multi-Discipline Team Concept

A fundamental tenet of CE is that an organization's most valuable resource is its people. Yet to be successful, these people must work together effectively in teams.

The formation of a multi-discipline product/process development team and the molding of these various individual specialists into a productive working relationship (i.e., team building) are critical to the success of CE. The team must be composed of individuals who have the vision and the ingenuity to do things differently, and yet interface harmoniously. The success of a CE project clearly depends upon the ability of these team members to work together.

Problem solving is the key role of the team. Problem solving in the product and process definition of a complex system goes beyond decision making - it includes defining the problem, generating alternate solutions, re-evaluating alternatives, selecting alternatives, and implementing the solution. These problems are multileveled, multi-dimensional, and multi-disciplinary - all of the information required to form a solution may not be available, and the available information may be based on judgment and experience. Hence, initial concentration will be placed on blending human rather than technical aspects of the team.

The multifunctional nature of the team further complicates group dynamics because of language barriers, perceptions of unequal status, and general cultural barriers to teamwork. Yet achieving consensus among members of a CE team, i.e., arriving at a product and process definition that every team member accepts, is the goal. Thus all team members must be satisfied with the design, accept ownership of it, and become responsible for it.

There are various methods and management practices to help overcome these difficulties and to accomplish CE product and process definition. These different

methods must be adequately explored to find those methods which are most effective for a given organization. Every effort should be made by management to enable the team and remove existing barriers to ensure that the various team members individually accept ownership of the CE processes and the responsibility, authority, and accountability for the CE product.

A cornerstone of this emphasis on human resources and teamwork is training in the underlying philosophy of continual improvement, the tools and techniques of the scientific approach to problem solving, and the skills required to work together effectively in a team setting.

As processes become more sophisticated and automated, corporate success becomes people dependent rather than technology dependent. Instead, human skills and especially team working skills must be developed simultaneously with computer software and equipment hardware, and then managed in such a way that they reinforce each other. [6]

In the final analysis the success of CE in any organization depends largely on the success of the building and operation of these multi-discipline teams. [7]

#### **1.7** The Need for Concurrent Engineering References

- [1] Hall, D., et al, "CALS Technical Report 001 Integration of R & M into the Automated Design Process," CALS Industry Steering Group, March 1988.

- [2] Winner, R. J., et al, "The Role of Concurrent Engineering in Weapons Systems Acquisition," Institute for Defense Analysis, Report R- 338, December 1988

- [3] Keene, S., "Software Reliability Directions," Reliability Review, ASQC, March 1991

- [4] Richter, Dr. K.J., "Concurrent Engineering Some Definitions and Issues," '92 Product Assurance Forum, April 1992

- [5] Smith, L.C., "Quality Function Deployment and Its Application in Concurrent Engineering," '92 Product Assurance Forum, April 1992

- [6] Hays, R.L., et al., "Dynamic Manufacturing: Creating the Learning Organization," The Free Press, New York, NY, 1988

- [7] Richter, Dr. K.J., "Organization and Management of Concurrent Engineering Team," '92 Product Assurance Forum, April 1992

Reliability Analysis Center (RAC) • 201 Mill St., Rome, NY 13440-6916 • 315-337-0900

8

# SECTION 2 ROBUST CIRCUIT DESIGN

#### 2.0 ROBUST CIRCUIT DESIGN

Robust Circuit Design is an integral part of concurrent engineering. A robust design minimizes less-than-optimal interactions among a product's parts caused by external factors such as manufacturing process variations, abusive operation and the environment. A robust design seeks to reduce product sensitivity to the sources of variability through careful selection of design values. Besides minimizing deviations within a product, a robust design seeks to insulate the product against outside sources of variability in manufacturing and use [Reference 1].

In a similar manner the production processes utilized can also be designed for robustness. An example, for electronic circuits, might be the selection of a specific soldering process i.e., vapor-phase reflow soldering, versus wave-flow soldering, versus hand soldering and then the subsequent optimization of that specific soldering process. Unfortunately however, a detailed study of production process robustness is beyond the scope of this treatise. Two excellent sources for this type of information are: the Electronic Manufacturing Productivity Facility (EMPF) [Reference 2] and the Manufacturing Technology Information Analysis Center [Reference 3].

The goal of robust circuit design is to select design values that maximize key product characteristics in relation to expected variations. The problem is that it is hard to select optimum design values because there are so many variations. Interaction between design values and external factors are often so complex, that the cost and difficulty of analyzing them is overwhelming.

To overcome this obstacle of complexity, a robust circuit design approach seeks to integrate the outputs of various analytical tools to address not only the concerns of design functionality but also its reliability, testability, producibility, environmental sensitivity and long-term life of the electronic circuits and systems.

#### A ROBUST DESIGN IS A DESIGN THAT EXHIBITS MINIMAL SENSITIVITY TO BOTH EXTERNAL AND INTERNAL INFLUENCES.

These influences include (but are not limited to):

| Temperature                  | Voltage   |

|------------------------------|-----------|

| Cooling Changes              | Vibration |

| Part Manufacturing Variation | Shock     |

| Part Aging Characteristics   | Radiation |

| Load Changes                 | EMI       |

A robust design approach addresses the potential variability of the individual components from which the circuit is assembled and the manner in which these parts typically fail, the effect of environmental influences upon the proper

Reliability Analysis Center (RAC) • 201 Mill St., Rome, NY 13440-6916 • 315-337-0900

functioning of the circuit, and the ability to successfully test the circuit after it has been manufactured.

In theory CE does not require automation, but modern electronic design is heavily dependent upon automation as a practical necessity. Therefore, in this case, CE is dependent upon the effective use of automated tools. Specific objectives in the use of these automated tools in a Robust Circuit Design approach are:

- To identify and utilize Modern Analytical Tools to optimize the circuit design from a functional, reliability, maintainability and testability viewpoint. The majority of these analysis techniques have now been automated. Specific examples of commercial software tools to aid in the performance of these and other related analyses are discussed in greater detail in Section 7.0, "Currently Available Automated Tools."