SAFECOMP '93

Edited by Janusz Górski

AD-A278 165

94-11252

Distribution United

# SAFECOMP '93

The 12th International Conference on Computer Safety, Reliability and Security

Poznań-Kiekrz, Poland 27-29 October 1993

> Edited by Janusz Górski

#### **Sponsor**

European Workshop on Industrial Computer Systems Technical Committee 7 (EWICS TC7)

#### Co-Sponsored by

IFIP Technical Committee 5 WG 5.4. Franco-Polish School of New Information and Communication Technologies

Polish Council for Scientific Research European Research Office, USARDSG-UK OCG, the Austrian Computer Society

## Organized by

Franco-Polish School of New Information and Communication Technologies

| Acces           | ion For              |

|-----------------|----------------------|

| NTIS            | CRA&I                |

| DTIC            | TAB                  |

| Unanr           | nounced i            |

| Justifi         | cation               |

| By_<br>Distrib  | ution /              |

| A               | vailability Code     |

| Dist            | Avail and/or Special |

| $\mathcal{O}$ . |                      |

Springer-Verlag

London Berlin Heidelberg New York

Paris Tokyo Hong Kong

Barcelona Budapest

DITC COALITY INSPECTED 3

Janusz Górski Franco-Polish School of New Information and Communication Technology 60-854 Poznań Poland

ISBN 3-540-19838-5 Springer-Verlag Berlin Heidelberg New York ISBN 0-387-19838-5 Springer-Verlag New York Berlin Heidelberg

British Library Cataloguing in Publication Data A catalogue record for this book is available from the British Library

Library of Congress Cataloging-in-publication Data A catalogue record for this book is available from the Library of Congress

Apart from any fair dealing for the purposes of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act 1988, this publication may only be reproduced, stored or transmitted, in any form or by any means, with the prior permission in writing of the publishers, or in the case of reprographic reproduction in accordance with the terms of licences issued by the Copyright Licensing Agency. Enquiries concerning reproduction outside those terms should be sent to the publishers.

© Springer-Verlag London Limited 1993 Printed in Great Britain

The use of registered names, trademarks etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant laws and regulations and therefore free for general use.

The publisher makes no representation, express or implied, with regard to the accuracy of the information contained in this book and cannot accept any legal responsibility or liability for any errors or omissions that may be made.

Typesetting: camera-ready by author Printed and bound by Antony Rowe Ltd., Chippenham, Wiltshire 34/3830-543210 Printed on acid-free paper

## SAFECOMP '93

## INTERNATIONAL PROGRAM COMMITTEE

| J. Górski (Chairman) | PL |                         |    |

|----------------------|----|-------------------------|----|

| R. E. Bloomfield     | UK | J. Lindeberg            | N  |

| S. Bologna           | I  | S. LHansen              | DK |

| W. Cellary           | PL | M. J. P. van der Meulen | NL |

| G. Cleland           | UK | G. Rabe                 | D  |

| B. Cronhjort         | S  | F. Redmill              | UK |

| P. Daniel            | UK | M. Rodd                 | UK |

| B. K. Daniels        | UK | B. Runge                | DK |

| G. Dahl              | N  | G. H. Schildt           | Α  |

| W. Ehrenberger       | D  | E. Schoitsch            | Α  |

| H. Frey              | CH | I. C. Smith             | UK |

| K. Kanoun            | F  | A. Toola                | SF |

| F. Koornneef         | NL | W. M. Turski            | PL |

| H. Krawczyk          | PL | U. Voges                | D  |

| R. Lauber            | D  | W. Zamojski             | PL |

## National Organizing Committee

J. Górski (Chairman),

T. Doroszewski, L. Gimzicka, K. Ratajczak, E. Rosłanowski

The safe operation of computer systems continues to be a key issue in many applications where people, environment, investment, or goodwill can be at risk. Such applications include medical, railways, power generation and distribution, road transportation, aerospace, process industries, mining, military and many others.

This book represents the proceedings of the 12th International Conference on Computer Safety, Reliability and Security, held in Poznań, Poland, 27-29 October 1993. The conference reviews the state of the art, experiences and new trends in the areas of computer safety, reliability and security. It forms a platform for technology transfer between academia, industry and research institutions. In an expanding world-wide market for safe, secure and reliable computer systems SAFECOMP'93 provides an opportunity for technical developers, users, and legislators to exchange and review the experience, to consider the best technologies now available and to identify the skills and technologies required for the future. The papers were carefully selected by the International Program Committee of the Conference. The authors of the papers come from 16 different countries. The subjects covered include formal methods and models, safety assessment and analysis, verification and validation, testing, reliability issues and dependable software technology, computer languages for safety related systems, reactive systems technology, security and safety related applications. As to its wide international coverage, unique way of combining participants from academia, research and industry and topical coverage, SAFECOMP is outstanding among the other related events in the field.

The reader will get insight into the basic status of computer safety, reliability and security (through invited presentations) and will receive a representative sample of recent results and problems in those fields presented by experts from both industrial and academic institutions.

The response to the Call for Papers produced many more good papers than could be included in the programme. I must thank all the authors who submitted their work, the presenters of the papers,

vi Preface

the International Program Committee and National Organising Committee, the Sponsor and Co-sponsors for their efforts and support. Through their strong motivation and hard work the Conference and this book have been enabled.

Janusz Górski

Poznań, Poland August 1993

## **Contents**

| Invited paper: T. Anderson(UK): Safety—Status and Perspectives                                                         | 3  |

|------------------------------------------------------------------------------------------------------------------------|----|

| •                                                                                                                      |    |

| Session 1: Formal Methods and Models                                                                                   | 7  |

| Chair: G. Cleland (UK)                                                                                                 |    |

| C. Bernardeschi, L. Simoncini, A. Bondavalli (I): Data Flow<br>Control Systems: an Example of Safety Validation        | 9  |

| G. Bruns, S. Anderson (UK): Validating Safety Models with                                                              |    |

| Fault Trees                                                                                                            | 21 |

| Z. Liu (UK), J. Nordahl, E. V. Sørensen (DK): Composition and Refinement of Probabilistic Real-Time Systems            | 31 |

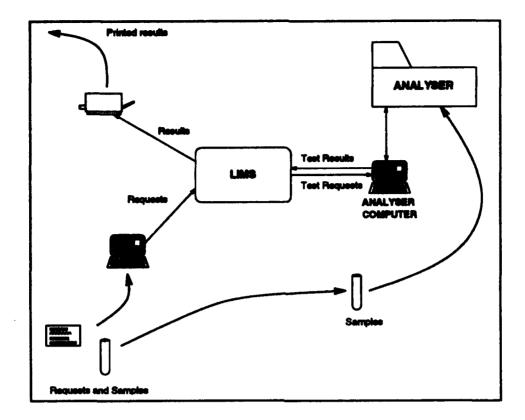

| P. Collinson, S. Oppert, S. Hughes (UK): The Application of Formal Methods for the Redevelopment of a Laboratory       |    |

| Information Managment System                                                                                           | 41 |

| Session 2: Applications                                                                                                | 51 |

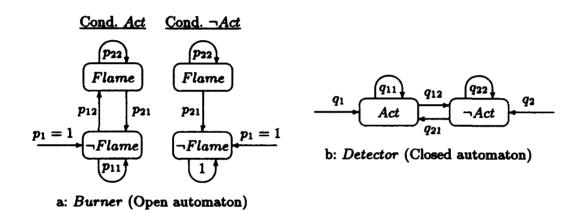

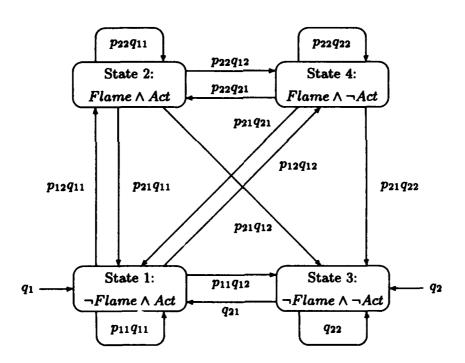

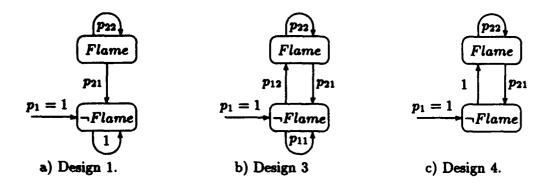

| W.A. Halang, (D) J. Scheepstra (NL): PLC-Implementation of Emergency Shut-Down Systems                                 | 53 |

| G. A. Mutone (USA), M. Rothfelder (D): The Fast Cost                                                                   |    |

| Effective Design and Concurrent Certification of the Safe                                                              | (2 |

| Computer for a Real Time Train Control Application                                                                     | 63 |

| H.E. Rhody (USA), V. Manoni (1), J.R. Hoelscher (USA): Design and Analysis of a Failsafe Algorithm for Solving Boolean |    |

| Equations                                                                                                              | 73 |

| Session 3: Safety Assessment                                                                                           | 83 |

| M.J.P. van der Meulen (NL), T. Stålhane (N), B. Cole (UK):                                                             |    |

| Programmable Electronic System Analysis Technique in Safety Critical Applications                                      | 85 |

| C. J. Goring (UK): Safety Assessment—The Critical System                                                               |    |

| Suppliers View                                                                                                         | 91 |

viii Contents

| M. Chudleigh (UK): Hazard Analysis Using HAZOP: A Case Study                                                       | 99  |

|--------------------------------------------------------------------------------------------------------------------|-----|

| Session 4: Safety Analysis                                                                                         | 109 |

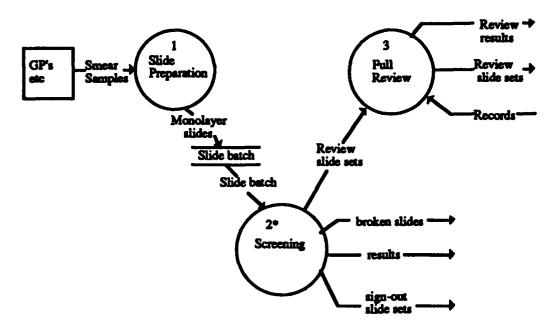

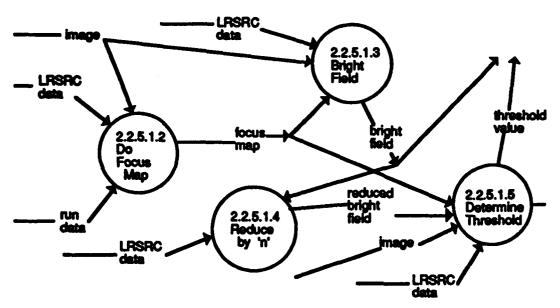

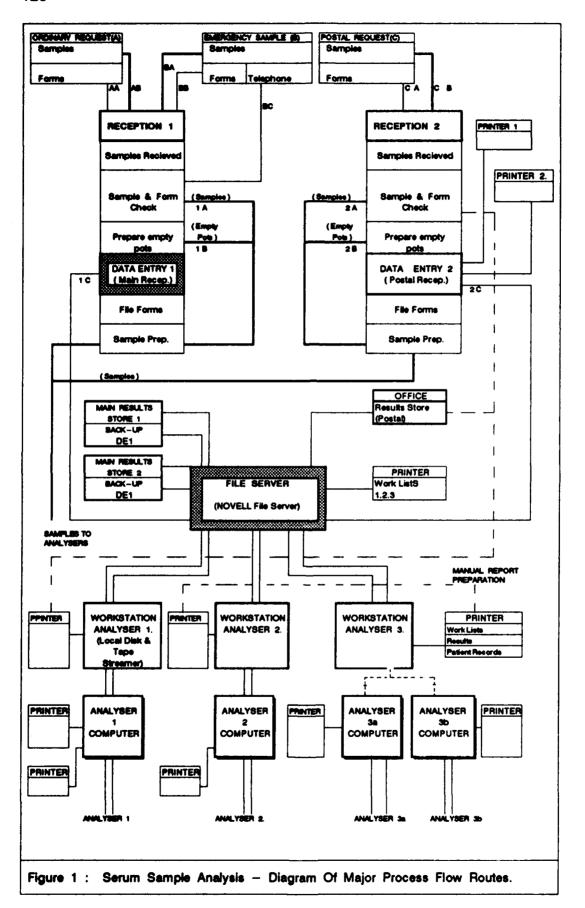

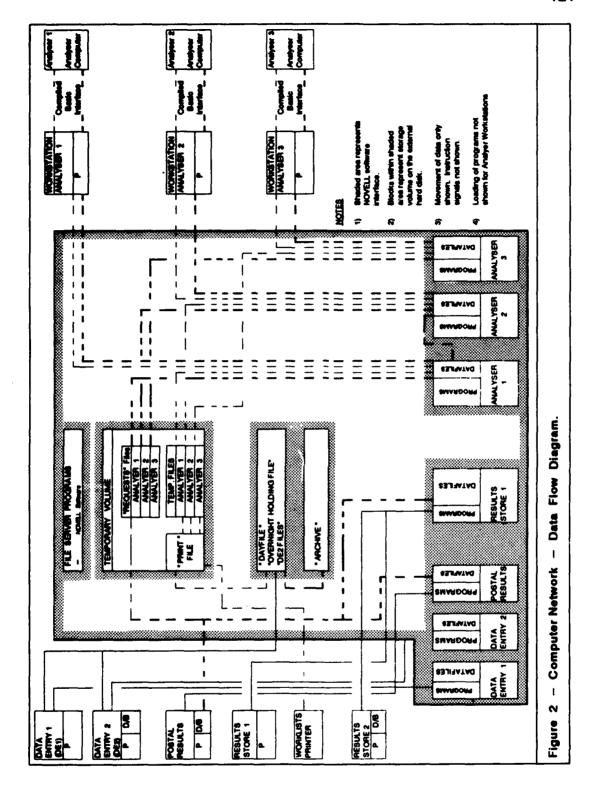

| S.S. Dhanjal, R. Fink (UK): Safety Analysis of Clinical Laboratory Systems                                         | 111 |

| M.F. Chudleigh, J.N. Clare (UK): The Benefits of SUSI: Safety Analysis of User System Interaction                  | 123 |

| Panel Session: Technology Transfer Between Academia and Industry  Moderator: F. Redmill (UK)                       | 133 |

| F. Redmill (UK): Issues Affecting Technology Transfer and Experience with a Community Club                         | 135 |

| JP. Banâtre (F): Subsidiaries and Start-up Spin-off Companies of Inria                                             | 142 |

| W. Cellary (PL): Human Medium in Technology Transfer  B. Malcolm (UK): Technology Transfer—from Purpose to         | 145 |

| Practice                                                                                                           | 147 |

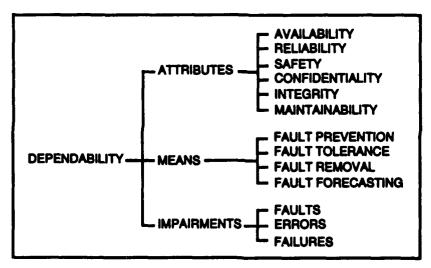

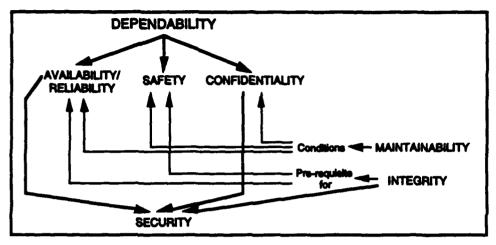

| Invited Paper: JC. Laprie (F): Dependability: from Concepts to Limits                                              | 157 |

| Session 5: Verification and Validation                                                                             | 169 |

| N. J. Ward (UK): The Rigorous Retrospective Static Analysis of the Sizewell 'B' Primary Protection System Software | 171 |

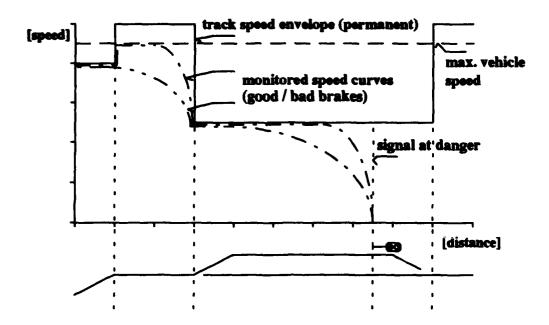

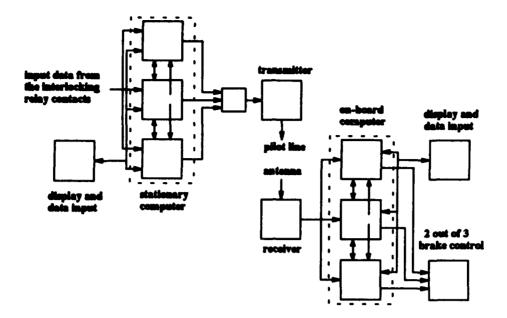

| B. Stamm, R. Baumann, M. Kündig-Herzog (CH): A Safety Critical Computer System in a Railway Application            | 182 |

| Session 6: Testing                                                                                                 | 195 |

| J. M. Voas, C. C. Michael, K. W. Miller (USA): Confidently<br>Assessing a Zero Probability of Software Failure     | 197 |

| I. M. Galkin (Belarus): A Knowledge-Based Approach to Program Testing and Analysis                                 | 207 |

| Session 7: Dependable Software                                                                                     | 217 |

| A. Saeed, R. de Lemos, T. Anderson (UK): Robust Requirements  Specifications for Safety-Critical Systems           | 219 |

**Contents** ix

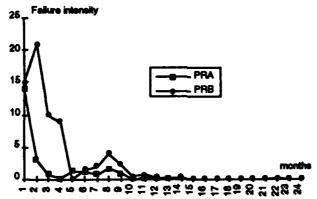

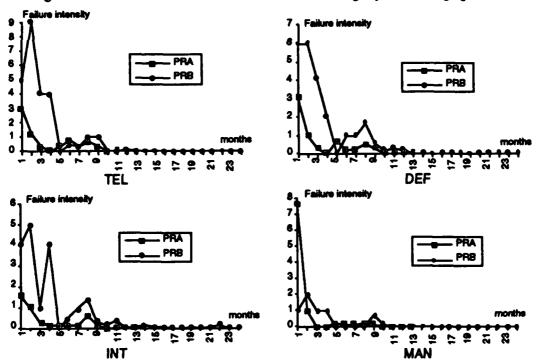

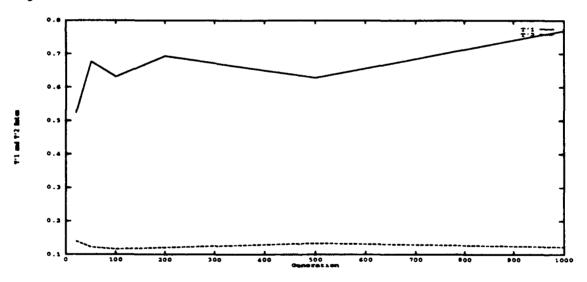

| M. Kaâniche, K. Kanoun (F): Software Failure Data Analysis of                                                                       | 220 |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| two Successive Generations of a Switching System                                                                                    | 230 |

| J. Rainer (A): Software validation with CASE-TOOLS                                                                                  | 240 |

| Session 8: Reliability Issues                                                                                                       | 251 |

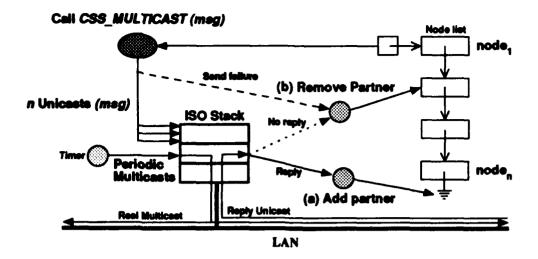

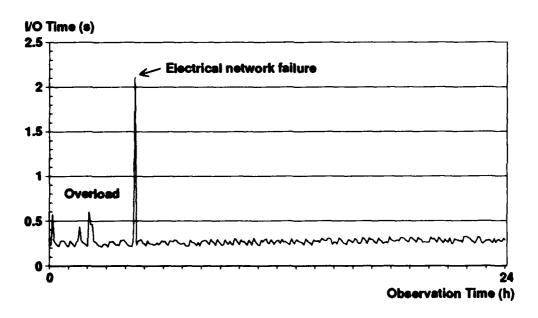

| W. Kuhn, E. Schoitsch (A): Dependability of Scaleable, Distributed Systems: Communication Strategies for Redundant Processes        | 253 |

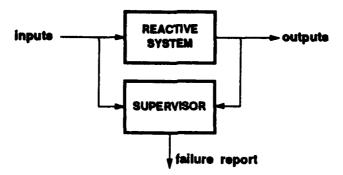

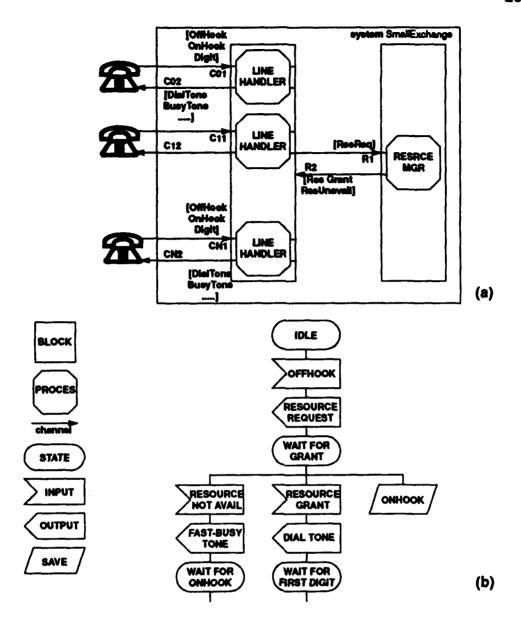

| R. E. Seviora (Canada): Real-Time Detection of Failures of Reactive Systems                                                         | 265 |

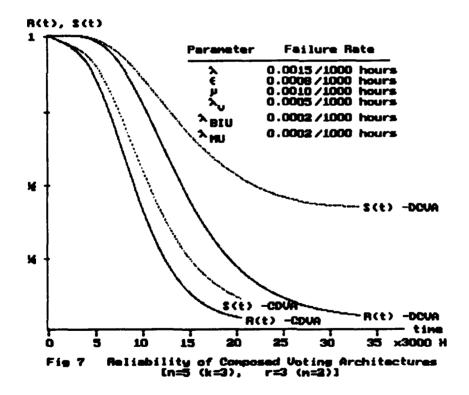

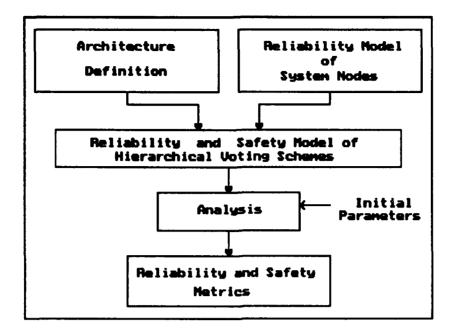

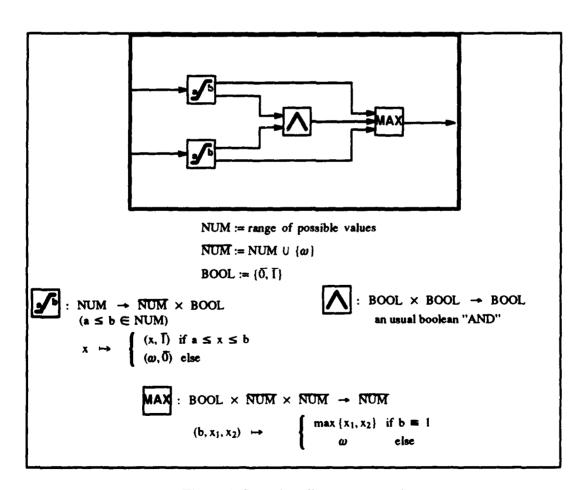

| H. Krawczyk, S. Al-Karaawy (PL): Reliability and Safety Analysis of Hierarchical Voting Schemes                                     | 276 |

| Session 9: Languages                                                                                                                | 287 |

| G. Sen (India), J. Brummer (D): Designing a High-level  Language for Safety Systems                                                 | 289 |

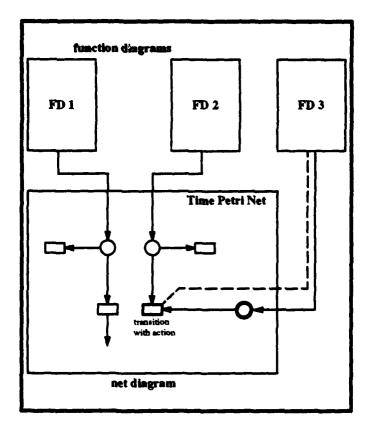

| P. Molinaro, O. H. Roux (F): Oreste: a Reliable Reactive Real-<br>Time Language                                                     | 302 |

| Invited Paper: C.E. Landwehr (USA): How Far Can You Trust a Computer?                                                               | 313 |

| Session 10: Security                                                                                                                | 327 |

| L. Mé (F): Security Audit Trail Analysis Using Genetic Algorithms                                                                   | 329 |

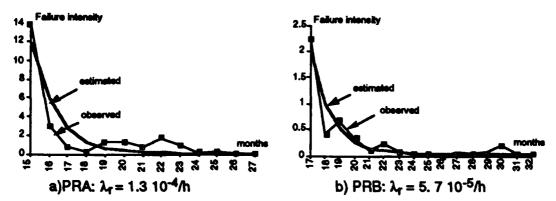

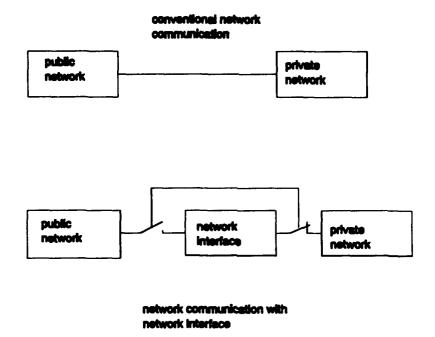

| R. Posch (A): MRSA—a New Public Key Encription Method M. Witte, W.A. Halang (D): A Virus-Resistant Network                          | 341 |

| Interface                                                                                                                           | 349 |

| Session 11: Reactive Systems                                                                                                        | 359 |

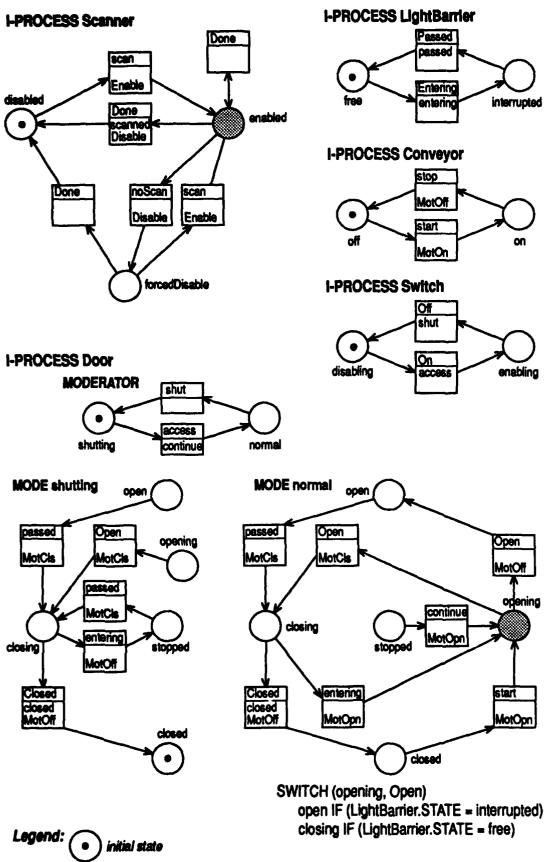

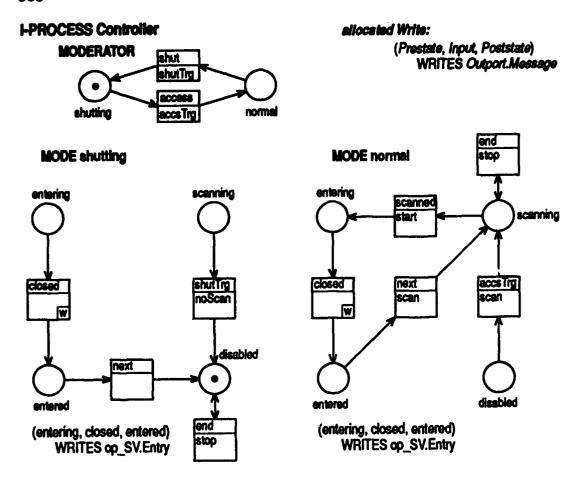

| H. Fierz, H. Müller, S. Netos (CH): CIP - Communicating Interacting Processes: A Formal Method for the                              | 2/1 |

| Development of Reactive Systems                                                                                                     | 361 |

| M. Colnarič (Slovenia), W.A. Halang (D): Exception Handling and Predictability in Hard Real-Time Systems                            | 371 |

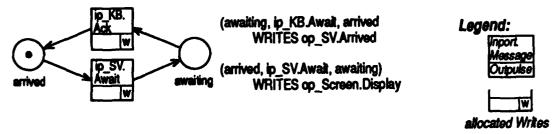

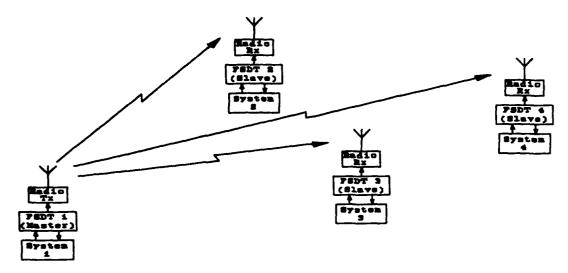

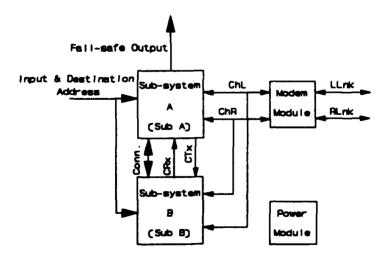

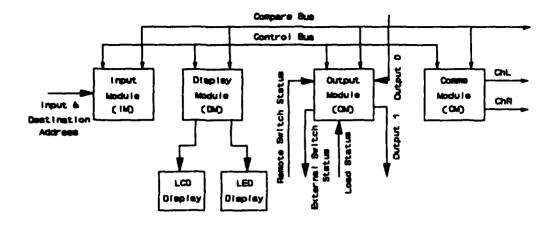

| M.B. Schrönen, M.R. Inggs (South Africa): Development of a Fail-Safe Data Transmission System for Use in Life-Critical Applications | 379 |

| Author Index                                                                                                                        | 389 |

|                                                                                                                                     |     |

## **List of Contributors**

S. Al-Karaawy

Faculty of Electronics

Technical University of

Gdańsk

Poland

S. Anderson

Department of Computer

Science

University of Edinburgh

Edinburgh EH9 3JZ, UK

T. Anderson

Department of Computing

Science

University of Newcastle

Newcastle upon Tyne

NE1 7RU, UK

J.-P. Banâtre Inria-Rennes/Irisa Campus de Beaulieu 35042 Rennes cedex, France

R. Baumann Siemens Integra Verkehrstechnik AG 8304 Wallisellen, Switzerland

C. Bernardeschi

Department of Information

Engineering

University of Pisa

Via Diotisalvi 2

56100 Pisa, Italy

A. Bondavalli CNUCE-CNR Via S. Maria 36 56126 Pisa, Italy J. Brummer

Institute for Safety

Technology (IST)

Gesellschaft für Anlagen- und

Reaktorsicherheit (GRS)mbH

Garching, Germany

G. Bruns

Department of Computer

Science

University of Edinburgh

Edinburgh EH9 3JZ, UK

W. Cellary Franco-Polish School of New Information and Communication Technology 60-854 Poznań, Poland

M.F. Chudleigh Cambridge Consultants Limited Science Park, Milton Road Cambridge CB4 4DW, UK

J.N. Clare Cambridge Consultants Limited Science Park, Milton Road Cambridge CB4 4DW, UK

B. Cole Software Metrics Laboratory Glasgow Caledonian University Glasgow, Scotland, UK P. Collinson

Department of Chemical

Pathology

Mayday University Hospital

Croydon

Surrey CR7 7YE, UK

M. Colnarič Faculty of Technical Sciences University of Maribor Maribor, Slovenia

S.S. Dhanjal Lloyd's Register of Shipping 29 Wellesley Road Croydon Surrey CR0 2AJ, UK

H. Fierz

Institut für Technische

Informatik und

Kommunikationsnetze

ETH-Zentrum

CH-8092 Zurich, Switzerland

R. Fink

West Middlesex University

Hospital

Twickenham Road

Isleworth

Middlesex TW7 6AF, UK

I. M. Galkin Computer Center Academy of Sciences Minsk 25 Scorina str. Republic of Belarus 220072

C.J. Goring August Systems Limited Jenner Road Crawley West Sussex RH10 2GA, UK

W A. Halang Fern Universität Department of Electrical Engineering P.O. Box 940 D-58084 Hagen, Germany J. R. Hoelscher General Railway Signal Corporation Rochester, NY 14620, USA

S. Fughes Lloyd's Register of Shipping 29 Wellesley Road Croydon Surrey CR0 2AJ, UK

M.R. Inggs

Department of Electrical

Engineering

University of Cape Town

Private Bag Rondebosch

South Africa, 7700

M. Kaâniche LAAS-CNRS 7 Avenue du Colonel Roche 31077 Toulouse Cedex, France

K. Kanoun LAAS-CNRS 7 Avenue du Colonel Roche 31077 Toulouse Cedex, France

H. Krawczyk Faculty of Electronics Technical University of Gdańsk Poland

M. Kündig-Herzog Siemens Integra Verkehrstechnik AG 8304 Wallisellen Switzerland

W. Kuhn Austrian Research Center Seibersdorf Department of Information Technology A-2444 Seibersdorf Austria

C. E. Landwehr

Center for High Assurance

Computing Systems

Naval Research Laboratory

Washington D.C., USA

J.-C. Laprie LAAS-CNRS 7 Avenue du Colonel Roche 31077 Toulouse Cedex, France

R. de Lemos

Department of Computing

Science

University of Newcastle

Newcastle upon Tyne

NE1 7RU, UK

Z. Liu

Department of Computer

Science

University of Warwick

Coventry CV4 7AL, UK

B. Malcolm Malcolm Associates Ltd. Savoy Hill London, UK

V. Manoni SASIB Signalamento Ferroviario 40128 Bologna, Italy

L. Mé Laboratoire d'Informatique SUPÉLEC Avenue de la Boulaie B.P. 28 F-35511 Cesson Sévigné Cedex France

M.J.P. van der Meulen Department of Industrial Safety Institute for Environmental and Energy Research The Netherlands Organization for Applied Scientific Research TNO Apeldoorn, The Netherlands

H. Müller Institut für Technische Informatik und Kommunikationsnetze ETH-Zentrum CH-8092 Zurich, Switzerland C. C. Michael Reliable Software Technologies Corporation Penthouse Suite 1001 North Highland Street Arlington, VA 22201 USA

K. W. Miller Department of Computer Science College of William & Mary Williamsburg, VA 23187 USA

P. Molinaro Ecole Centrale de Nantes Université de Nantes Laboratoire d'Automatique de Nantes URA 823 Nantes, France

G.A. Mutone AEG Transportation Systems, Inc. Pittsburgh, PA, USA

S. Netos

Institut für Technische

Informatik und

Kommunikationsnetze

ETH-Zentrum

CH-8092 Zurich, Switzerland

J. Nordahl

Department of Computer

Science

Technical University of

Denmark

DK-2800 Lyngby, Denmark

S. Oppert

Department of Clinical

Biochemistry

West Middlesex University

Hospital

Isleworth

Middlesex, UK

R. Posch Institute for Applied Information Processing Graz University of Technology Klosterwiesgasse 32/I A-8010 Graz, Austria

J. Rainer

Austrian Federal Test &

Research Centre Arsenal

(BVFA)

Department System

Reliability & Traffic

Electronics

A-1030 Vienna

Faradaygasse 3, Austria

F. Redmill

Redmill Consultancy

and Co-ordinator of the

Safety-Critical Systems Club

22 Onslow Gardens

London N10 3JU, UK

H.E. Rhody RIT Research Corporation Rochester Institute of Technology Rochester, NY 14623, USA

M. Rothfelder

Institute for Software,

Electronics,

Railroad Technology (ISEB) of

TÜV Rheinland

P.O. Box 91 09 37

Cologne

D-5000 Koeln 91, Germany

O. H. Roux Ecole Centrale de Nantes Université de Nantes Laboratoire d'Automatique de Nantes URA 823 Nantes, France A. Saeed

Department of Computing

Science

University of Newcastle

Newcastle upon Tyne NE1

7RU, UK

J. Scheepstra

Rijksuniversiteit Groningen

Department of Computing

Science

P.O. Box 800

NL-9700 AV Groningen

The Netherlands

E. Schoitsch Austrian Research Center Seibersdorf Department of Information Technology A-2444 Seibersdorf, Austria

M.B. Schrönen

Department of Electrical

Engineering

University of Cape Town

Private Bag Rondebosch

South Africa, 7700

G. Sen Reactor Control Division Bhabha Atomic Research Centre Bombay, India

R. E. Seviora

Department of Electrical and

Computer Engineering

University of Waterloo

Ontario,

Canada N2L 3G1

L. Simoncini

Department of Information

Engineering

University of Pisa

Via Diotisalvi, 2

56100 Pisa, Italy

E. V. Sørensen

Department of Computer

Science

Technical University of

Denmark

DK-2800 Lyngby, Denmark

T. Stålhane SINTEF DELAB O.S. Bragstads Plass NTHN-7034 Trondheim Norway

B. Stamm Siemens Integra Verkehrstechnik AG K517 Industriestr. 24 8304 Wallisellen, Switzerland J. M. Voas Reliable Software Technologies Corporation Penthouse Suite 1001 North Highland Street Arlington, VA 22201 USA

N.J. Ward TA Consultancy Services Ltd The Barbican East Street Farnham Surrey GU9 7TB, UK

M. Witte

Fern Universität

Department of Electrical

Engineering

P.O. Box 940

D-58084 Hagen, Germany

## **INVITED PAPER**

## Safety - status and perspectives

Tom Anderson

Department of Computing Science

The University of Newcastle upon Tyne, NE1 7RU, UK

#### **Abstract**

Safety can be all things to all men - that is, different people in different situations will, quite legitimately, interpret the term "safety" in different ways. This paper expresses a personal perspective on safety as an engineering concern.

#### 1 Introduction

Delegates will be aware that this is the 12th occasion of presenting SAFECOMP, a conference which, under the auspices of EWICS Technical Committee 7, has laid stress on the importance of safety in the context of computing systems since the very first SAFECOMP in 1979. Consequently, the event has an enviable lineage with respect to a topic that is recognised to be of rapidly increasing significance, commensurate with the growth in automatic control of critical applications. It seems inevitable that these trends will continue and accelerate, given current projections for the semiconductor and telecommunication industries. Over the past 15 years, work on both research and system development has enhanced our understanding of the issues and techniques relating to safety in computing systems. However, much remains to be done, in further advancing the discipline and in more widely promulgating the current state of the art. In this brief perspective I have taken the opportunity to make some elementary observations on the tenets of safe computing systems; if any of these are considered provocative or unsound I welcome correction.

## 2 Definition

Because "safe" and "safety" are words in everyday use, they have dictionary definitions and popular interpretations. These interpretations can differ widely: for the general public, for politicians, for professionals (lawyers, engineers, regulators etc), across industrial sectors, and over time (especially after a major accident). A scientist or engineer recognises the range of interpretations, but must nevertheless adopt a specific working definition - and thus accepts the consequence that because others may select an alternative definition, conflicts may need to be resolved if confusion is to be avoided.

The usual starting point for a definition of safety is that a system is safe if it will not kill anyone. However, numerous points then need clarification, such as "what about multiple deaths?", "what about injuries, severe and minor?", "what about environmental damage, with implications for human well-being?", "what about vast

financial losses, with implications for the well-being of some?". An (inadequate) escape route is to assert that a system is safe if it will not harm anyone. But does this mean never harm anyone, under any possible circumstances? Only when these, and other, questions are answered would we have a semblance of a definition. (There is, of course, no single "correct" definition, so these questions will not be answered here!) One way forward is to define a system to be safe if it will not cause an accident, thereby postponing (albeit briefly) the definition of what constitutes an accident. Even given an agreed definition of a safe system, it is then vital to examine how degrees of unsafeness should be characterised, which leads on to the notion of risk to capture the likelihood and magnitude of losses incurred through use of the system.

From an engineer's viewpoint, ensuring that these issues are addressed and resolved is much more important than the details of their resolution in a particular case.

## 3 Misconceptions

Despite, or perhaps because of, the widespread use of safety concepts, a number of misconceptions are frequently encountered in the wider computing community - SAFECOMP delegates will, I trust, concur with my critique of the following aberrant assertions.

- (a) Safety is paramount. If this were true, then in almost all cases, the proper course of action would be not to implement the system, or at least not to operate it. Safety is an attribute of a system which frequently conflicts with other desirable attributes. The design engineer has the difficult task of striving to achieve the optimum compromise between safety and the other required characteristics for the system, all within budgetary and other resource constraints.

- (b) Safety is an absolute. The notion of absolute safety can be formulated and discussed if necessary, but the real engineering issues concern levels of safety and tradeoffs between safety and other system properties. Consider the following questions: How safe should the system be designed to be? How unsafe could the system be and still be considered adequately safe? How safe is the implemented system? How safe has the system been during operation? By comparison the question "Is the system absolutely safe?" seems pointless.

- (c) Safety can't be quantified (less extreme versions: safety ought not to be quantified; avoid quantification in safety analyses). On the contrary, it is essential that safety be quantified to the extent that this is feasible, and fully acknowledging the limitations and imprecision of measurement techniques. Quantified analysis of safety should be viewed as the normal engineering goal, and consequently the inability to quantify safety should be recognised as a deficiency in which case subjective rankings or objective comparisons may be employed as a weaker alternative.

- (d) Safety must be guaranteed. Since safety does not equate to death or taxes such a guarantee must be regarded as a forlorn hope, other than in the sense of a warranty establishing corporate liability.

(e) Safety is unique. Safety is a highly significant system attribute because of the importance we rightly attach to the lives of others. Nevertheless, it has very much in common with other system attributes such as reliability and security, and safety engineering can and does benefit greatly from the techniques developed for other aspects of dependability in systems - and vice-versa of course. [A personal aside. At SAFECOMP'83 in Cambridge I asserted (as a panellist) that the concepts of safety and reliability were essentially identical, differing only in the criterion which specified success. Although I still believe this to be true, I have learned a little in the last ten years, and do not expect to reiterate this academic and potentially misleading observation in Poznan at SAFECOMP'93.]

#### 4 Axioms

In contrast to the above, the following truths are held to be self-evident.

- (a) Safety is a system attribute. This is sometimes taken to imply that safety is solely a property of the overall application system (e.g. nuclear power plant) operating in the real-world environment; a very narrow interpretation then misleads by inferring that subsystems do not have this property (contradicted by axioms b and c below). A more generic use of the term system is much to be preferred, encompassing subsystems, units, modules, components etc., in which case axiom a is almost tautological.

- (b) Computing systems can kill. See Leveson and Turner [2].

- (c) Software can kill. See Leveson and Turner [2]. Obviously, the software directs the computing system which in turn acts via the controlled equipment analogously, most murderers make use of a weapon.

- (d) Perfection is unattainable. Samuel Butler advised "Strive for imperfection there's some change of getting it". Dijkstra warned "Testing can show the presence, but never the absence of faults". Lebesgue cautions "Logic makes us reject certain arguments, but it cannot make us believe any argument". Juvenal asked "But who is to guard the guards themselves?". Brookes summed it all up "There is inherently no silver bullet".

- (e) There's safety in numbers. Although this is a well known English phrase it is perhaps a little too ambiguous to be axiomatic. A literal interpretation is unusual and the benefits of quantification have already been suggested; here I wish to take the standard usage, which suggests that members within a group are less exposed to attack than isolated individuals, and thereby make the standard argument in favour of redundancy. Any single entity can fail, and to avoid a single point of failure alternative mechanisms should be available (eg. retry, or a spare, or diversity, or fail-safe).

## 5 Engineering Safe Computing Systems

The tasks of safety engineering are clearly manifold: to establish the safety requirements for the system and its subsystems, to formulate safety policies, specifications and strategies, to design for safety, to conduct hazard and safety analyses, to compose the safety case and gain certification for the system, to

implement, install, operate and maintain the system in accordance with all of the preceding. All are of vital importance (literally), which makes prioritisation rather difficult. I would place particular emphasis on achieving safety, and feel that the specific topics of requirements, validation and fault-tolerance deserve special mention - but this may merely be a consequence of personal prejudice. In any case, the above list of topics is driven by system life-cycle stages, and we should also include: management, procedures, documentation, standards, human factors and real-time considerations.

My position in 1989 was stated as:

"I would commend three attributes to those involved in the construction of [safe] computing systems. First, vigilance, in avoiding and eliminating faults; second, diversity, to provide protection against the consequences of faults; and third, simplicity, the hand-maiden of dependability" [1].

Almost five years on, the only change I wish to make is to reverse the ordering. Lastly, I would like to refer readers to the most enjoyable text on system safety I have encountered [3], which happens to be in the domain of railway safety and the lessons to be learnt from accidents; as well as being highly instructive, the book provides this closing quotation to emphasise that even safety engineers can learn from their mistakes:

Out of this nettle, Danger We pluck this flower, Safety Henry IV (Part I)

#### References

- 1. Anderson T (ed). Safe & Secure Computing Systems Preface. Blackwell Scientific, Oxford, 1989

- 2. Leveson NG, Turner CS. An Investigation of the Therac-25 Accidents. IEEE Computer 1993; 26,7:18-41

- 3. Rolt LTC. Red for Danger (3rd edition). Pan Books, London, 1976

## Session 1

# FORMAL METHODS AND MODELS

Chair: G. Cleland University of Edinburgh, UK

# Data Flow Control Systems: an Example of Safety Validation

Cinzia Bernardeschi, Luca Simoncini

Department of Information Engineering, University of Pisa

Pisa, Italy

Andrea Bondavalli CNUCE-CNR Pisa, Italy

#### Abstract

In this paper a methodology to develop safety-critical control systems is proposed. These systems continuously interact with the physical environment, and those admitting at least one failure causing a catastrophe are classified as safety-critical. Our methodology takes into account both the control system (controller) and the physical environment (plant). After the requirements analysis, the system is developed following data flow model, i.e., described as a static data flow network of nodes executing concurrently and communicating asynchronously. The plant is used as the test case for the validation of the controller and their composition is analysed to show whether hazards are reached. To this purpose we apply a transformation from data flow networks to LOTOS specifications. The transformation preserves the semantics of the original network and data flow network properties can be derived and proved on the LOTOS specification using available support tools. A train set example for the contact-free moving of trains on a circular track divided into sections is shown as an application of the methodology.

## 1 Introduction

Control systems are computing systems which continuously interact with the physical environment, e.g. traffic control or industrial process control systems. Many control systems are safety-critical, i.e. systems for which at least one failure exists that can cause a catastrophe. Therefore, in addition to their functional capabilities, these systems require specified levels of dependability. In the framework of safety-critical systems, one approach to improve the level of dependability is to use formal specification and verification in conjunction with other methods of software development such as testing and fault tolerance. The analysis of the critical issues of a control system plays a vital role in the development of safety-critical systems. Critical issues address what the system should not do and allow to concentrate on the elimination and control of the hazards. The study of the critical

issues of the system, allows us to derive the constraints necessary to guarantee a safe behaviour of the system (safety constraints) and the strategies to realise it (safety strategies) [1]. The validation phase is as important as requirements analysis. Validation is the activity that aims to check that the actual behaviour of the developed system is as expected.

Data flow is a paradigm for concurrent computations. A data flow network is composed by a set of nodes (or processes) all executing concurrently and asynchronously. They communicate by exchanging messages, representing data items, over asynchronous communication channels (following a FIFO policy). The computation proceeds in a data driven manner: a node of the network is ready to execute as soon as the required data tokens are available. Data flow is receiving great attention being known for its suitability for achieving a high degree of execution parallelism, thus allowing to improve performance, but has other useful characteristics as well. A data flow network is usually very close to the intuitive representation of a control system, that is the translation from the conceived system to a data flow graph is straightforward, as well as to inspect the data flow graph to determine which aspects of the system are represented [2], [3]. This makes data flow generally recognised as a convenient programming paradigm for the development of control systems. The referential transparency property admitted when nodes compute functions, by which two executions of the same node with the same input data produce equal output results, makes data flow "inherently fault tolerant": it is possible to tolerate simple failures by re-evaluating the same function on the same input data [4], [5]. If a non deterministic behaviour of nodes is allowed, still the strong isolation and information hiding enforces a good confinement useful for setting error confinement areas around modules by means of appropriate consistency checks. The property of composability which puts in direct relation the general behaviour of a system from its constituent parts [6], [7] helps verification and validation. Lastly, structural models for software reliability assessment can be applied since all data necessary to their use can be obtained by a simple instrumentation of software code [8].

In this paper a systems development methodology is proposed. After the requirements analysis, the system is developed following the computational model based on the Jonsson's formalism [7]. In the validation phase, the specification of the physical environment is assumed as the test case for the control system: the plant and the controller are composed and the resulting behaviour is analysed to be sure that hazards are never reached in the system. To this purpose, we apply a transformation from data flow networks to LOTOS (Language Of Temporal Ordering Specification) [9] specifications. The transformation maintains the data flow network properties which can be derived and proved on the LOTOS specification. Available LOTOS software support tools are then used [10]. The adequacy of the proposed methodology is shown through the design and the validation of a simple control system: a train set example for the contact-free moving of trains on a circular track divided into sections [1], [11]. The rest of this paper is as follows. Section 2 is devoted to the definition of our methodology, including a description of the data flow formalism adopted, the transformation and its properties. Section 3 develops the example of the train set to show how the methodology can be applied. Lastly, Section 4 contains our conclusion.

## 2 System Development Methodology

The proposed development methodology takes into account the parallel interaction between a plant and a controller which must eliminate unsatisfactory behaviours of the plant. The interface between the plant and the controller contains sensors and actuators. Sensors detect events in the plant and send signals to the controller. Upon reception of the signals the controller can take actions by issuing appropriate control commands through actuators. The analysis of the critical issues addressing what the system should not do, allow to define the hazards for the system into consideration and their elimination and control. The analysis is performed in two phases: the first phase to identify the real world properties relevant to the critical behaviour of the system and the second phase to specify the system behaviour required at the interface with the environment, i.e. the sensors and actuators. Thus the constraints necessary to guarantee a safe behaviour of the system (safety constraints) and the strategies to realise it (safety strategies) may be derived.

Then the system realising the safety strategy is developed following a data flow computational model. Since we shall use the specification of the physical environment as the test case for the control system in the validation, we shall model also the plant. As previously mentioned we adopt the formalism for the specification of data flow network proposed in [7] in which the semantics of the networks is based on *traces*. Here we give some definitions and a brief explanation on this model. Given a data flow network N, let V be the set of data items exchanged over the channels. We denote by V\* the set of finite sequences on V and by  $\diamond$  the empty sequence.

**Definition:** A data flow node P is a tuple <Ip, Op, Sp, s<sup>0</sup>p, Rp, FAIRp> where:

Ip is the set of input channels;

Op is the set of output channels with  $(Ip \cap Op) = \emptyset$ ;

Sp is the set of states;  $s^{0}p$  is the initial state,  $s^{0}p \in Sp$ ;

Rp is the set of firings. A firing F is a tuple F=<s,  $\chi_{in}$ , s',  $\chi_{out}$ > where s, s' $\in$  Sp,

$\chi_{in}$  is a mapping from Ip to V\* and  $\chi_{out}$  is a mapping from Op to V\*.

FAIRP  $\subseteq \mathcal{P}$  (RP) is a finite collection of fairness sets. If FAIRP=RP, then the node executes firings until no more data are present on the input channels.

For the sake of this paper, the meaning of a firing  $\langle s, \chi_{in}, s', \chi_{out} \rangle$  can be assumed as follows: when the node is in state s and for each input channel inp $\in$  Ip the sequence  $\chi_{in}(inp)$  is a prefix of the content of the channel (i.e. the firing is executable), then these sequences may be consumed, while the node changes its state to s' and the sequence  $\chi_{out}(out)$  is produced on each output channel out  $\in$  Op. Note that the empty sequence  $\langle s \rangle$  is a prefix of each sequence of data.

A data flow network N consists of a set PN of data flow nodes such that in PN each channel occurs at most once as an input channel and at most once as an output

channel. The network is obtained connecting input channels to output channels with the same name and a network transition can be generated by the firing of a node or by a communication event, where a communication event can be either an input event or an output event. Communication events occur when a data item is inserted (removed) into (from) an input (output) channel of the network. CN denotes the set of all the channels of the network. A computation of the network is a sequence of transitions of the network. Informally a computation of the network is a complete run of the network in which all nodes perform firings according to their definition and all channels behaves like unbounded FIFO channels. The semantics of the network is the set of its traces; a trace represents the interleaving of the communication events during a computation.

The use of information about the presence/absence of data items and the data driven asynchronous execution of data flow nodes in data flow networks, make reasoning about these networks and their semantics very difficult. To perform the semantic analysis of data flow networks, we apply a transformation from data flow networks to process algebras specifications using the LOTOS formal specification language [9]. LOTOS represents recent work on the combination of CCS (with some extension) [12] to describe the behaviour of the system and an algebraic formalism for the definition of data types. Software support tools have been developed allowing the simulation, the compilation and the proof of properties of a LOTOS specification [10].

The transformation is obtained by mapping each node and each channel of the network into a process in the process algebras and then all the processes are composed in parallel with synchronisation on the proper set of actions to realise the global behaviour of the network [13]. The names of gates in the specification are directly derived from the names of the channels. For each channel "a" ∈ CN, "a#" is the gate corresponding to get a data from the channel "a" while "a" is the gate corresponding to put a data on the same channel "a". Let CP be the process which simulates the behaviour of a channel "a" of N (CP behaves like a FIFO buffer) and nodeP be the process that realises the behaviour of the data flow node P, the specification of the network is:

```

specification netN[EgatesN]: noexit

<data type definition>

behaviour

hide |[CgatesN-EgatesN]| in

(CP[a, a#] || ...<∀c∈CN>... ||| CP[b, b#])

```

||[CgatesN-EgatesN]|| (nodeP[Ip#, Op]  $|||| ... < \forall Q \in P_N > ... ||| nodeQ[Ip#, Op])$  endspec (\* netN \*)

where CgatesN are the gates corresponding to get (put) from (onto) the whole sets of channels of N, EgatesN are the gates corresponding to get (put) from (onto) the input (output) external channels of N. Furthermore, the notation Ip# (Op) is used to denote the set of "a#" ("a") gates for the input (output) channels of the node P. The set of processes associated to channels execute disjoint actions, so they are put in parallel with an empty set of synchronisation gates (||| operator). The same applies to the set of processes associated to the nodes. These two sets of processes

synchronise on the set of all the actions defined for the two behaviour expressions. The network specification has the same behaviour of the original data flow network and the formal verification methods of the process algebras can be applied to prove properties of the original network. Interested readers may find more details on the transformation itself and a prove that the transformation preserves the data flow network properties, i.e., the LOTOS specification has the same behaviour of the network from which it has been derived, in [13]. The previous transformation is defined for a class of data flow networks in which the firings of the nodes do not require sophisticated synchronisation mechanisms between the processes associated to the channels and the processes which simulates the behaviour of the nodes. The transformation for general networks is described in [14].

To summarise, our methodology is based on:

- modelling the physical environment as a part of the overall system (plant);

- executing the requirements analysis for both the mission and the critical issues of the system;

- specifying safety constraints and a safety strategy for the system to eliminate hazards;

- developing the control system in the data flow computational model;

- applying the transformation to the data flow specification of the system (both the control system and the plant) obtaining a LOTOS specification which maintains all the relevant properties (and doing some expression transformation if necessary for their automatic analysis);

- verifying the correct behaviour of the system composed by the *plant* and the *controller* through an automatic analysis of the LOTOS resulting expression using the available tools.

## 3 The Train Set Example

The train set example consists of a simple control system for the contact-free moving of trains on a circular track [1], [11]. Suppose to have one directional moving of two trains on a circular track divided in six sections, with the constraint that trains are less than one section in length. Hazardous states are the states in which a train may be involved in a collision. In our system, a state is hazardous if the front of one train is in the same or adjacent section as the front of another train. They are avoided in a system if the following condition (safety condition) always holds: the heads of the trains differ at least by 2 sections. The concept of reserved section is introduced and our safety strategy is based on: 1) a section can be reserved by only one train; 2) for any train the section of the front of the train and the section behind must be reserved; 3) a train must always reserve a section before entering it. We use  $\Theta$  and  $\Theta$  to represent the operation of subtraction modulo 6 and the operation of addition modulo 6, respectively.

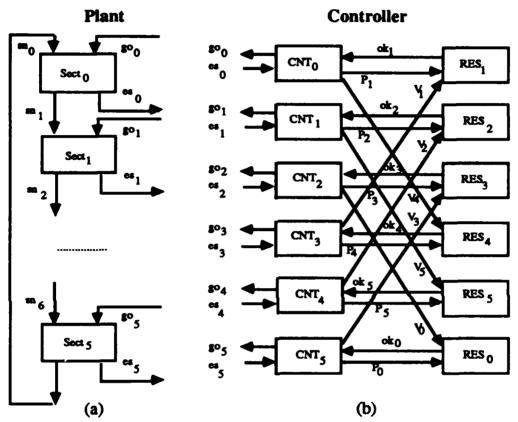

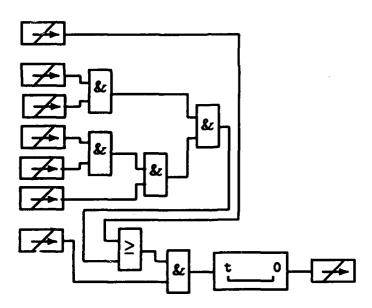

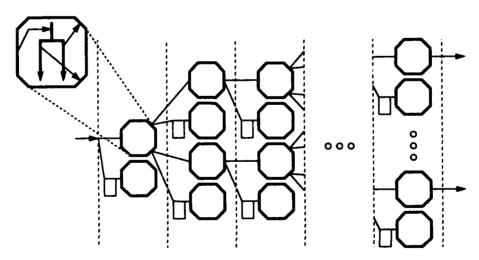

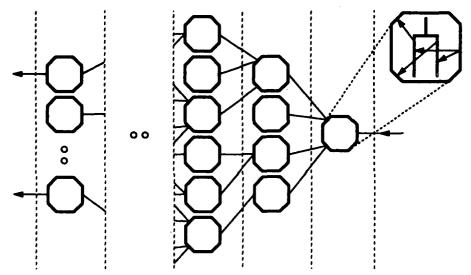

We divide the system under development into the physical plant and the controller which communicate by sending control signals and then we apply the data flow model based on the Jonsson's formalism [7]. The plant is composed by six sections {Secto, ..., Secto} shown in Figure 1 (a). In each section a sensor detects a train entering in the section and an actuator has the task to stop a train before leaving the

section when necessary. We model the flow of the train by messages sent by one section to the next (channel  $sn_i$ ). On receipt of this message the section sends a signal to the controller to notify the passage of a train (channel  $es_i$ ). Then before the train is allowed to move on the section, it waits for a message from the controller with the meaning that the train is allowed to leave the section (channel  $go_i$ ). On receipt of this message, the section sends a message to the next section in the circular track to simulate the movement of the train (channel  $sn_{i\oplus 1}$ ).

Figure 1: The Data Flow Network of the Train Set System.

The controller interacts with the plant and is composed by the data flow nodes reported in Figure 1 (b): six CNT<sub>i</sub> nodes and six RES<sub>i</sub> nodes. Each CNT<sub>i</sub> realises the communication with the section Sect<sub>i</sub> of the plant while each RES<sub>i</sub> implements the correct reservation mechanism of the corresponding section Sect<sub>i</sub>. The CNT<sub>i</sub> node, after having received a signal from section Sect<sub>i</sub> that a train has arrived (channel es<sub>i</sub>), sends a signal to RES<sub>i\theta2</sub> to mark section Sect<sub>i\theta2</sub> as free (channel V<sub>i\theta2</sub>), and then it tries to book the section (i\theta1) for the train sending a signal to RES<sub>i\theta1</sub> (channel P<sub>i\theta1</sub>). CNT<sub>i</sub> waits for a positive answer from RES<sub>i\theta1</sub> (the next section has been reserved) (channel ok<sub>i\theta1</sub>); and then it sends a signal to Sect<sub>i</sub> for allowing the train to leave section Sect<sub>i</sub> (channel go<sub>i</sub>). Each RES<sub>i</sub> node controls the status of the corresponding section which can be reserved for one train or free. It receives signals from the CNT<sub>i\theta1</sub> (channel P<sub>i</sub>) and reserves the section by sending an acknowledgement (channel ok<sub>i</sub>). After the section has been reserved it accepts

only a signal through the channel V<sub>i</sub> to free the section before accepting (and making) any further reservation.

The resulting data flow network N, composed by the controller and the plant, is shown in Figure 1. Let A and B be natural numbers representing the identifiers for the trains running over the track, we suppose an initial state with train A in section Sect1 and train B in section Sect5; it follows that the sections 1 and 0 (for train A) and the sections 5 and 4 (for train B) must be reserved. The initialisation is used to define the initial state of the data flow nodes. For those communications which are signals we associate the dummy value 1 in defining of the firings of the nodes (another way is to allow any data value). The definition of the data flow nodes is:

```

Section node Secti

O_{Sect_i} = \{es_i, sn_{(i \oplus 1)}\}

I<sub>Secti</sub>={sn<sub>i</sub>, go<sub>i</sub>}

S_{Secti}=\{s, s_a, s_b\}

R<sub>Secti</sub>={F1, F2, F3, F4} FAIR<sub>Secti</sub>=R<sub>Secti</sub>

F1=<s, [sn_i->A], s_a, [es_i->1]>

F3=<s_a, [go_i->1], s, [sn_{(i\oplus 1)}->A]>

F4=<s_b, [go_i->1], s, [sn_{(i\oplus 1)}->B]>

F2=<s, [sn_i->B], s_b, [es_i->1]>

s^{0}_{Sect_{1}}=s_{a}, s^{0}_{Sect_{5}}=s_{b} and s^{0}_{Sect_{i}}=s for i=\{0,2,3,4\}.

Controller node CNT;

O_{CNT_i}=\{go_i, P_{(i\oplus 1)}, V_{(i\ominus 2)}\} S_{CNT_i}=\{s, s'\}

I_{CNT_i}=\{es_i, ok_{(i\oplus 1)}\}

RCNT;={F5, F6} FAIRCNT;=RCNT;

F5=<s, [es_i->1], s', [V_{(i\oplus 2)}->1, P_{(i\oplus 1)}->1]> F6=<s', <math>[ok_{(i\oplus 1)}->1], s, [go_i->1]>

s^{0}_{CNT;=s'} for i=\{1,5\} and s^{0}_{CNT;=s} for i=\{0,2,3,4\}.

Controller node RESi

I_{RES_i} = \{P_i, V_i\}

O_{RES_i}=\{ok_i\}

S_{RES} = \{s, s'\}

R_{RES_i}=\{F7, F8\} FAIR_{RES_i}=R_{RES_i}

F7=<s, [P_i \rightarrow 1], s', [ok_i \rightarrow 1]>

F8=<s', [V_i -> 1], s, []>

s^{0}_{RES_{i}}=s^{1} for i=\{0, 1, 4, 5\} and s^{0}_{RES_{i}}=s for i=\{2,3\}.

```

To apply the transformation we specify the maximum size of the channels which may be assumed equal to two, while the signal communications can be transformed in pure synchronisation action in LOTOS. We give here the LOTOS process definition for the single data flow nodes obtained applying the transformation described in Section 2. The process definitions for the Sect, CNT and RES nodes and that for the CP which simulates a FIFO buffer of length two are:

```

process nodeCNT[es, P, ok, V, go](actstate:state): noexit:=

([actstate=s] -> es?X:nat; i; V!1; P!1; nodeCNT[es, P, ok, V, go](s')

[] [actstate=s'] -> ok?X:nat; i; go!1; nodeCNT[es, P, ok, V, go](s))

endproc (* nodeCNT *)

process nodeRES[P,ok,V](actstate:state): noexit:=

([actstate=s] -> P?X:nat; i; ok!1; nodeRES[P,ok,V](s')

[] [actstate=s'] -> V?X:nat; i; nodeRES[P,ok,V](s))

endproc (* nodeRES *)

process CP[inp, out]: noexit:=

hide mid in oneslot[inp, mid] |[mid]| oneslot[mid, out]

where

process oneslot[a, b]: noexit:= a?X:nat; b!X; oneslot[a, b]

endproc (* oneslot *)

endproc (* CP *)

```

Since LOTOS specifications belonging to the subset of LOTOS without data (basic LOTOS) can be completely analysed by the verification tools, while for specifications with data values we can only simulate and/or compile and run them, we will restrict ourselves to basic LOTOS whenever possible without loosing properties. The LOTOS behaviour analyser AUTO [15], allows us to build the automaton of a basic LOTOS specification to prove strong and weak bisimulation between specifications. Although it fails when running on large specifications, simple ones like ours can be successfully run and the LOGIC CHECKER tool [16] can be used to prove action-based logic formulas ACTL, over the specification. To this purpose we make some manipulations of the specification obtained directly by the data flow to LOTOS transformation, trying to synchronise processes and to hide actions as soon as possible. This allows AUTO to reduce the number of the states during the generation of the automaton of the specification. The LOTOS "Regrouping Parallel Processes" correctness preserving transformation can be applied automatically by the LOTOS structure editor to regroup processes differently. The transformation preserves the strong bisimulation equivalence. All the previous tools are included in the LOTOS integrated tool environment Lite [10] developed inside the LOTOSPHERE ESPRIT project. Since all the nodeSect, nodeCNT and nodeRES processes execute all the actions in state s and then the actions in the state s' (nodeSect executes actions either in s<sub>a</sub> or s<sub>b</sub>) before repeating, we assume s as the initial state and rewrite the processes as:

```

process nodeSect[sn, es, go, nextsn]: noexit :=

(sn?X:nat [X=A]; i; es!1; go?X:nat; i; nextsn!A; nodeSect[sn, es, go, nextsn]

[] sn?X:nat [X=B]; i; es!1; go?X:nat; i; nextsn!B; nodeSect[sn, es, go, nextsn])

endproc (* nodeSect *)

p. cess nodeCNT[es, P, ok, V, go]: noexit :=

es?X:nat; i; V!1; P!1; ok?X:nat; i; go!1; nodeCNT[es, P, ok, V, go]

endproc (* nodeCNT *)

```

```

process nodeRES[P,ok,V]: noexit :=

P?X:nat; i; ok!1; V?X:nat; i; nodeRES[P,ok,V]

endproc (* nodeRES *)

```

To keep into account the initial position of trains, the corresponding processes must contain a prefix behaviour expression representing the action to be performed at system start. This lead to the definition of the following processes: nodeSectA and nodeSectB for the sections where train A and train B are at the beginning, respectively; nodeICNT for the controllers that have to reserve the next section for allowing the trains to move (1 and 5 in our case) and nodeIRES for the sections that are reserved at the beginning (0, 1, 4 and 5 in our case). We have:

```

process nodeSectA[sn, es, go, es, nextsn]: noexit :=

go?X:nat; i; nextsn!A; nodeSect[sn, es, go, nextsn]

endproc (* nodeSectA *)

process nodeSectB[sn, es, go, es, nextsn]: noexit :=

go?X:nat; i; nextsn!B; nodeSect[sn, es, go, nextsn]

endproc (* nodeSectB *)

process nodeICNT[es, P, ok, V, go]: noexit :=

P!1; ok?X:nat; i; go!1; nodeCNT[es, P, ok, V, go]

endproc (* nodeICNT *)

process nodeIRES[P,ok,V]: noexit :=

V?X:nat; i; nodeRES[P,ok,V]

endproc (* nodeIRES *)

```

We can now map our specification into basic LOTOS. Lite, provides many mappings from a full LOTOS specification onto a basic LOTOS one. They differ for the data value information that are removed. We can apply the simplest transformation named "trans\_np0" where all data are dropped, keeping simply the original gate identifiers as basic LOTOS actions. The transformation can be directly invoked by the behaviour analysis menu entry. In order to apply this mapping without loosing information, we modify the specification defining one gate for train A and another one for train B when they run over the track (i.e. substituting each action  $sn_i$  with two actions  $asn_i$  and  $bsn_i$ ). The new process nodeSect is simply a non deterministic choice between the actions corresponding to the passage of the two trains. This is the only communication channel where data are important, in all the others the value of the data are not significant and can be dropped. The basic LOTOS specification of the section is:

```

process nodeSect [asn, bsn, es, go, nextasn, nextbsn] :noexit :=

(asn; i; es; go; i; nextasn; nodeSect [asn, bsn, es, go, nextasn, nextbsn]

[] bsn; i; es; go; i; nextbsn; nodeSect [asn, bsn, es, go, nextasn, nextbsn])

endproc (* nodeSect *)

```

The behaviour expression of the whole specification of the system is reported in the Appendix; where the observable actions are the actions corresponding to the movement of the trains over the track (gates asni# and bsni#). Note that there are not external channels of the network and the set of processes associated to the nodes must synchronise with the set of channel processes on the whole set of gates. The LOTOS behavioural analyser AUTO can be run over the specification allowing to easily prove our safety strategy. The automaton (considering the weak bisimulation equivalence) has 18 states and 24 transitions and it is deadlock free. We proved automatically, by using the LOGIC CHECKER over the automaton, the following logic formulas to be true for train A:

- 1) train A can enter any section: A[true{true}U(asn;#}true];

- 2) train A can only move from section i to section i⊕1:

$AG([asn_i#]A[true\{cond\}U\{\neg asn_{(i\oplus 1)}#\}true]);$

where  $cond=((-asn_0#)&(-asn_1#)&(-asn_2#)&(-asn_3#)&(-asn_4#)&(-asn_5#));$

3) for each path such that train A enters section i, train B cannot enter section (i $\Theta$ 1) until train A enters section (i $\Theta$ 1):

AG([asn<sub>i</sub>#]A[true{ $-bsn(i\Theta1)$ #}U{bsn( $i\Theta1$ )#}A[true{ $-bsn(i\Theta1)$ #}U{asn( $i\Theta1$ )#}true]]). The same formulas can be proved to be true for the train B.

From these we have that when train A is in section i, train B is never in section  $i\Theta 1$ , i,  $i\Theta 1$ . This holds also for train B, thus satisfying the safety condition.

#### 4 Conclusions

In this paper we have presented a methodology which can be used for the design of safety-critical systems and for the validation of the design. Quite apart the modelling of the physical environment as a part of the overall system which can be used as test case for the control system, the use of the data flow computational model for the description of the system specification allows the designer to use notations which are very natural and which can be made even more user friendly by the use of development tools like a graphical editor [4]. The transformation into process algebras specification allows the use of the analysis tools available in LOTOS, making the entire process from specification to verification and validation fully automated.

The proposed approach has been applied to a simple control system where advantage could be taken by the use of the basic LOTOS tools like the behavioural analyser AUTO for the generation of the automaton and the LOGIC CHECKER. The extension of the proposed approach to the validation of control systems LOTOS specifications with data value involves the use of the simulator tool [10] and the compiler available in the full LOTOS environment, which allows to derive the possible traces of execution of the original data flow network. This extension is anyway limited by the fact that tracing the behaviour of a general network may be very lengthy and unfeasible in case of infinite input sequences. Nevertheless for control systems where the possible input sequences are constrained either on data value or on periodicity, the proposed approach can be used for problems of larger size than that presented in this paper.

#### References

- 1. Saced A, de Lemos R, Anderson T. The role of formal methods in the requirements analysis of safety-critical systems: a train set example. Proc. of FTCS-21, Montreal, Canada, 1991, pp. 478-485

- 2. Kavi K, Buckles B, Bhat U. Isomorphism between Petri nets and data flow graphs. IEEE TSE 1987; SE-13: 1127-1134

- 3. Bondavalli A, Strigini L, Simoncini L. Data-flow like languages for real-time systems: issues of computational models and notation. Proc. of SRDS-11, 11th Symposium on Reliable Distributed Systems, Houston, Texas, USA, 1992, pp. 214-221

- 4. Bondavalli A, Simoncini L. Functional paradigm for designing dependable large-scale parallel computing systems. Proc. of ISADS 93 International Symposium on Autonomous Decentralized Systems, Kawasaki, Japan, 1993, pp. 108-114

- 5. Jagannathan R, Ashcroft E A. Fault tolerance in parallel implementations of functional languages. Proc. of FTCS-21, Montreal, Canada, 1991, pp. 256-263

- 6. Kahn G. The semantics of a simple language for parallel programming. Proc. of IFIP 74, 1974, pp. 471-475

- 7. Jonsson B. A fully abstract trace model for data flow networks. Journal of ACM 1989; 36: 155-165

- 8. Mellor P. Modular structured software reliability modelling. Private communication, 1992

- 9. Bolognesi T, Brinskma E. Introduction to the ISO specification language LOTOS. In: The Formal Description Technique LOTOS. Elsevier Science Publishers B.V. (North-Holland), 1989, pp. 23-73

- 10. van Eijk P. The Lotosphere integrated tool environment LITE. Proc. of IFIP TC6/WG6.1 4th International Conference on Formal Description Techniques for Distributed Systems and Communication Protocols FORTE 91, Sydney, Australia, 1991, pp. 473-476

- 11. Genrich H J. Predicate/transition nets. In: LNCS 254. Springer Verlag, 1986, pp. 207-247

- 12. Milner R. Communication and concurrency. Prentice Hall, Englewood Cliffs, NJ, 1989

- 13. Bernardeschi C. An approach to the analysis of data flow networks by LOTOS. Proc. of Congresso annuale AICA'93 (to appear), Lecce, Italy, 1993

- 14. Bernardeschi C, Bondavalli A, Simoncini L. From data flow networks to process algebras. Proc. of PARLE 93, Munchen, Germany, 1993.

- 15. Madeleine E, Vergamini D. AUTO: a verification tool for distributed systems using reduction of finite automata networks. Proc. of IFIP TC6 2nd International Conference on Formal Description Tecniques for Distributed Systems and Communication Protocols FORTE 89, Vancouver, B.C., Canada, 1989, pp. 61-66

- De Nicola R, Fantechi A, Gnesi S, Ristori G. An action-based framework for verifying logical and behavioural properties of concurrent systems. Computer Networks and ISDN Systems 1993; 25: 761-778

#### Appendix

<u>specification</u> SYSTEM [asn0#, asn1#, asn2#, asn3#, asn4#, asn5#, bsn0#, bsn1#, bsn2#, bsn3#, bsn4#, bsn5#]: noexit

#### beiraviour

#### hide

asn0, asn1, asn2, asn3, asn4, asn5, bsn0, bsn1, bsn2, bsn3, bsn4, bsn5, es0, es1, es2, es3, es4, es5, es0#, es1#, es2#, es3#, es4#, es5#, go0, go1, go2, go3, go4, go5, go0#, go1#, go2#, go3#, go4#, go5#, P0, P1, P2, P3, P4, P5, P0#, P1#, P2#, P3#, P4#, P5#, ok0, ok1, ok2, ok3, ok4, ok5, ok0#, ok1#, ok2#, ok3#, ok4#, ok5#,V0, V1, V2, V3, V4, V5, V0#, V1#, V2#, V3#, V4#, V5# in

(nodeSect[asn0#,bsn0#,es0,go0#,asn1,bsn1] ||| nodeCNT[es0#,P0,ok0#,V0,go0] ||| nodeSectA[asn1#,bsn1#,es1,go1#,asn2,bsn2] ||| nodeICNT[es1#,P1,ok1#,V1,go1] ||| nodeSect[asn2#,bsn2#,es2,go2#,asn3,bsn3] ||| nodeCNT[es2#,P2,ok2#,V2,go2] ||| nodeSect[asn3#,bsn3#,es3,go3#,asn4,bsn4] ||| nodeCNT[es3#,P3,ok3#,V3,go3] ||| nodeSect[asn4#,bsn4#,es4,go4#,asn5,bsn5] ||| nodeCNT[es4#,P4,ok4#,V4,go4] ||| nodeSectB[asn5#,bsn5#,es4,go0#,asn1,bsn1] ||| nodeICNT[es5#,P5,ok5#,V5,go5] ||| nodeIRES[P0#,ok0,V0#] ||| nodeIRES[P1#,ok1,V1#] ||| nodeRES[P2#,ok2,V2#] ||| nodeRES[P3#,ok3,V3#] ||| nodeIRES[P4#,ok4,V4#] ||| nodeIRES[P5#,ok5,V5#]) || (\* full synchronisation \*)

(CP[asn0,asn0#] III CP[asn1,asn1#] III CP[asn2,asn2#] III CP[asn3,asn3#] III CP[asn4,asn4#] III CP[asn5,asn5#] III CP[bsn0,bsn0#] III CP[bsn1,bsn1#] III CP[bsn2,bsn2#] III CP[bsn3,bsn3#] III CP[bsn4,bsn4#] III CP[bsn5,bsn5#] III CP[es0,es0#] III CP[es1,es1#] III CP[es2,es2#] III CP[es3,es3#] III CP[es4,es4#] III CP[es5,es5#] III CP[go0,go0#] III CP[go1,go1#] III CP[go2,go2#] III CP[go3,go3#] III CP[go4,go4#] III CP[go5,go5#] III CP[p0,p0#] III CP[p1,p1#] III CP[p2,p2#] III CP[p3,p3#] III CP[p4,p4#] III CP[p5,p5#] III CP[ok0,ok0#] III CP[ok1,ok1#] III CP[ok2,ok2#] III CP[ok3,ok3#] III CP[ok4,ok4#] III CP[ok5,ok5#] III CP[V0,V0#] III CP[V1,V1#] III CP[V2,V2#] III CP[V3,V3#] III CP[V4,V4#] III CP[V5,V5#])

#### where

## Validating Safety Models with Fault Trees

Glenn Bruns and Stuart Anderson

Department of Computer Science University of Edinburgh Edinburgh EH9 3JZ, UK

Abstract. In verifying a safety-critical system, one usually begins by building a model of the basic system and of its safety mechanisms. If the basic system model does not reflect reality, the verification results are misleading. We show how a model of a system can be compared with the system's fault trees to help validate the failure behaviour of the model. To do this, the meaning of fault trees are formalised in temporal logic and a consistency relation between models and fault trees is defined. An important practical feature of the technique is that it allows models and fault trees to be compared even if some events in the fault tree are not found in the system model.

#### 1 Introduction

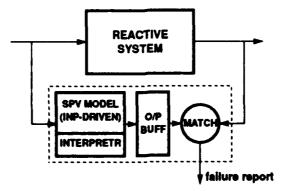

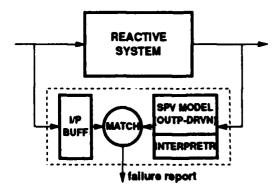

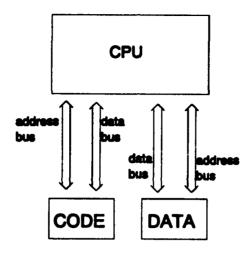

Safety-critical systems often have mechanisms designed to prevent, detect, or tolerate system system faults. To ensure that these mechanisms work as intended, a model of the system can be built from two parts: a model of the basic system and a model of the safety mechanisms (see Figure 1). Important properties of the system are then verified of the model. For example, if a component failure occurs, then it is detected.

Fig. 1. A Model of a Safety-Critical System

For the verification results to be valid, the basic part of the model should reflect the true connection between component failures and system faults in the system. We are aware of a study of a rail interlocking system in which the preliminary system model allowed only one train per track section, thus making collisions impossible. Less obvious problems may be harder to discover, such as when a particular combination of failures leads to a system fault in the real system but not the system model.

We propose a validation technique in which a system model is compared to its fault trees. If a system model and its fault trees are not consistent in a sense that we will define, then the system model may not be valid. Fault trees are well suited for this purpose because they are specifically intended to capture the relationship between component failure and system faults.

The two main sections of the paper cover the precise meaning of fault trees and our proposed relationship between fault trees and system models. First, however, we present an example.

#### 2 Example

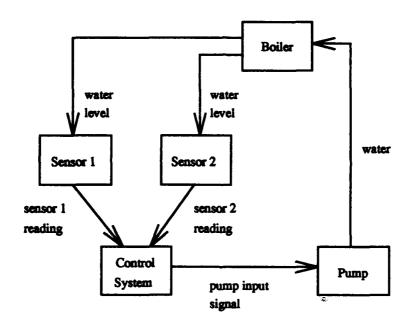

To make discussion of the problem more concrete, we present a simple boiler system example (see Figure 2).

Fig. 2. A Simple Boiler System

Steam is produced by water contained in the boiler vessel. The water level in the vessel is read by two sensors, which pass their readings to a control system. If the readings are below a certain value, the pump is turned on, delivering water to the vessel. If the level readings are above a certain value, the pump is turned off.

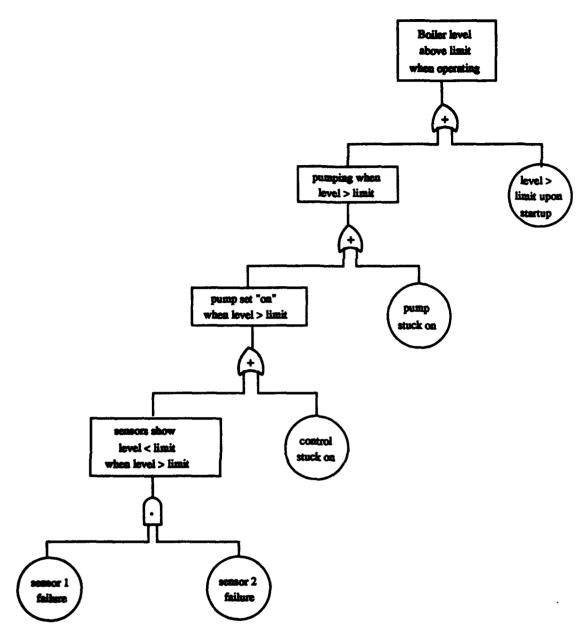

One safety-critical fault of the system is a boiler level that is too high. A fault tree for this fault is given in Figure 2.

A fault tree represents how events in a system can lead to a particular system fault. The event symbols used here are either basic events (which are drawn as circles and represent component failures) or intermediate events (which are drawn as rectangles and represent events which occur because of lower-level

Fig. 3. A Fault Tree for the Boiler System

events). The system fault is shown as the event at the root of the tree. Event symbols are connected in the tree by gate symbols, which are either and-gates or or-gates.

The full fault tree notation has many more event and gate symbols, but if we do not consider the probabilistic meaning of fault trees then the symbols we have described are enough.

#### 3 Fault Tree Semantics

If we are to compare fault trees and system models, we need to understand precisely what a fault tree means. Unfortunately, even the most definitive sources (e.g., the Fault Tree Handbook [5]) are vague on some critical points.

One issue is the nature of events. Are they to be regarded as conditions having duration or as instantaneous occurrences? The example event "contacts fail to open" from the Fault Tree Handbook suggests the former, but the example "timer reset" suggests the latter.

The second issue is the gate condition: does "and" mean that both input events happen at once, or only that one happens and then the other?

A third issue is the nature of causality. A gate models a sufficient cause if the output must occur if the gate condition is satisfied by the inputs. A gate models a necessary cause if the gate condition must be satisfied by the inputs if the output occurs. According to the Fault Tree Handbook, fault trees model sufficient and necessary causes. However, Figure IX-10 of the Handbook shows an event labelled "wire faults in K3 relay & comp. circuitry" as a cause of "K3 relay contacts fail to close", but one can imagine circumstances in which wire faults occur in such a way that the relay contacts do not fail to close. Therefore the cause as stated is not a sufficient one.

Causes of an event are also supposed to be *immediate*. This term seems related to the notion of flow, and may not be relevant in systems that cannot be captured easily with flow models. All examples in the Fault Tree Handbook are illustrated with flow diagrams. Immediacy also suggests time. For our purposes, a gate models an immediate cause if no time passes between a cause and its effect.

We now present a formal semantics for fault trees. Events are treated as conditions having duration, and the gate condition is taken to be that both inputs to an and-gate must occur at once. Three different formalisations of gates are given, corresponding to different stances on the issue of gate causality.

Formally, fault trees are interpreted as formulas of temporal logic. We use the modal mu-calculus (see Appendix A), but nearly all temporal logics are expressive enough for our purposes. Similarly, the kinds of structures that temporal logics are interpreted over are very general. We assume only that a system model can be represented as a transition system or as a set of sequences of states.

Events are formalised as atomic propositions, which are interpreted as sets of states. For example, the event "sensor failure" could be modelled as the atomic proposition SF, which is interpreted as all states in which the sensor has failed. This formalisation of events fits with most of the examples of the Fault Tree Handbook, and is consistent with the meaning of the term "event" in probability theory. Since fault tree are subject to probabilistic analysis, a consistent view of events is desireable.

Next we will formalise the meaning of gates. We will let  $+(in_1, in_2, out)$  stand for an or-gate with inputs  $in_1$  and  $in_2$  and output out. Similarly,  $\bullet(in_1, in_2, out)$  stands for an and-gate. The semantics of a gate g, denoted [g], gives the logical relationship between the input and output events of g.

#### 3.1 A Propositional Semantics for Gates

Formalising gates with propositional logic is a simple approach that is reasonably close to the informal description of gates in the Fault Tree Handbook. In terms of the issues just discussed, this interpretation requires and-gate inputs to occur at the same time for the gate condition to be satisfied, and takes causality to be necessary, sufficient, and immediate. The subscript p on the semantic function stands for "propositional".

$$[+(in_1, in_2, out)]_p \stackrel{\text{def}}{=} out \Leftrightarrow in_1 \vee in_2$$

$$[\bullet(in_1, in_2, out)]_p \stackrel{\text{def}}{=} out \Leftrightarrow in_1 \wedge in_2$$

Informally, the first statement says that the output of an and-gate is true whenever both inputs are true. Remembering that events are treated as sets of states, the statement alternatively says that the set of states denoted by out is the intersection of the sets denoted by  $in_1$  and  $in_2$ . The concept of causality here is truly immediate: whenever both causes are present the effect is also present.

#### 3.2 Two Temporal Semantics for Gates

The greatest weakness of the propositional interpretation of fault trees is the assumption that no time can pass between cause and effect. This assumption violates a common intuition about causality. Since the examples in the Fault Tree Handbook mostly concern examples in which flow is virtually instantaneous (as in an electric circuit), the problem rarely arises there. In cases where flow is not instantaneous, events are modelled so that causes can be made immediate, albeit somewhat unnaturally. For example, in the pressure tank analysis of Chapter VII continuous pump operation can lead to a pump failure. This cause is modelled as the event "tank ruptures due to internal over-pressure caused by continuous pump operation for t > 60 sec". Since the idea of a cause leading to an event is natural, it is worthwhile to try to view fault trees in this way.

Our first temporal semantics requires that and-gate inputs occur at the same time to satisfy the gate condition, and takes causality to be only sufficient, not necessary or immediate. This means that once the gate condition is satisfied, the gate output must eventually occur. The temporal logic operator even is used to express the temporal condition of eventuality. Thus even( $\phi$ ) means that the property expressed by formula  $\phi$  will hold in the future.

The temporal relation between input and output events for gates can be defined as

$$[+(in_1, in_2, out)]_{i1} \stackrel{\text{def}}{=} (in_1 \lor in_2) \Rightarrow \text{even}(out)$$

$$[\bullet(in_1, in_2, out)]_{i1} \stackrel{\text{def}}{=} (in_1 \land in_2) \Rightarrow \text{even}(out)$$

The first definition says that it is always the case that if input events  $in_1$  and  $in_2$  occur together, then eventually output event out will occur.

Our second temporal semantics treats causality as only necessary. The temporal operator  $\mathbf{prev}(\phi)$  means that the property expressed by formula  $\phi$  held in the past.

$$[+(in_1, in_2, out)]_{t2} \stackrel{\text{def}}{=} out \Rightarrow \operatorname{prev}(in_1 \vee in_2)$$

$$[\bullet(in_1, in_2, out)]_{t2} \stackrel{\text{def}}{=} out \Rightarrow \operatorname{prev}(in_1 \wedge in_2)$$

However, these definitions allows the gate output out to occur many times for a single occurrence of  $in_1 \wedge in_2$ . A better interpretation might require that if out happens, then  $in_1 \wedge in_2$  must have happened at least as recently as the previous occurrence of out.

There are other possible interpretations based on other choices about the basic semantic issues. For example, combining the two temporal semantics we have presented would give one modelling sufficient and necessary causality.

Fault tree gates have been interpreted temporally before (see [1]), but the use of temporal logic here allows much simpler semantics. This simplicity makes comparison between alternative interpretations easier.

#### 3.3 Putting Gates Together

We now present the semantics of a fault tree t based on the set of gates contained in the tree (written as gates(t)). We use the temporal operator always( $\phi$ ), which means that the property expressed by  $\phi$  holds in every state.

$$[t] \stackrel{\text{def}}{=} \mathbf{always}(\bigwedge_{g \in gates(t)} [g])$$

In English, this definition says that it is always the case that every gate condition is satisfied. Note that the meaning of a fault tree is given in terms of the meaning of its gates.