Carriege Melo Landwood,

Software Engineering Institute

Formal Specification and Verification of Concurrent Programs

**Curriculum Module SEI-CM-27-1.0**

SMAY 14 1993

93-10707

93 5 1 1

# Formal Specification and Verification of Concurrent Programs

SEI Curriculum Module SEI-CM-27-1.0 February 1993

Daniel M. Berry

Technion and Software Engineering Institute

This work was sponsored by the U.S. Department of Defense.

Approved for public release. Distribution unlimited.

This technical report was prepared for the

SEI Joint Program Office ESC/AVS Hanscom AFB, MA 01731

The ideas and findings in this report should not be construed as an official DoD position. It is published in the interest of scientific and technical information exchange.

#### **Review and Approval**

This report has been reviewed and is approved for publication.

FOR THE COMMANDER

Thomas R. Miller, Lt Col, USAF

**SEI Joint Program Office**

The Software Engineering Institute is sponsored by the U.S. Department of Defense.

This report was funded by the U.S. Department of Defense.

Copyright © 1993 by Carnegie Mellon University.

This document is available through the Defense Technical Information Center. DTIC provides access to and transfer of scientific and technical information for DoD personnel, DoD contractors and potential contractors, and other U.S. Government agency personnel and their contractors. To obtain a copy, please contact DTIC directly: Defense Technical Information Center, Attn: FDRA, Cameron Station, Alexandria, VA 22304-6145.

Copies of this document are also available through the National Technical Information Service. For information on ordering, please contact NTIS directly: National Technical Information Service, U.S. Department of Commerce, Springfield, VA 22161.

Copies of this document are also available from Research Access, Inc., 3400 Forbes Avenue, Suite 302, Pittsburgh, PA 15213.

Use of any trademarks in this report is not intended in any way to infringe on the rights of the trademark holder.

# Formal Specification and Verification of Concurrent Programs

# **Acknowledgements**

Thanks to Nancy Leveson, Bob Glass, and Norm Gibbs for pushing me to write this module and thanks to Mark Ardis, Allison Brunvand, Dave Bustard, Lionel Deimel, Gary Ford, Linda Pesante, and Mary Zoys for their detailed assistance in its writing. Thanks to Pamela Zave and Jeannette Wing for reading parts or all of earlier drafts of this module; their comments were helpful in getting the module to its present state.

### Contents

| Capsule Description            | 1  |

|--------------------------------|----|

| Philosophy                     | 1  |

| Objectives                     | 2  |

| Prerequisite Knowledge         | 2  |

| <b>Module Content</b>          | 3  |

| Outline                        | 3  |

| Annotated Outline              | 4  |

| Glossary                       | 46 |

| <b>Teaching Considerations</b> | 49 |

| Suggested Schedules            | 49 |

| Worked Examples                | 49 |

| Exercises                      | 49 |

| Caveats                        | 51 |

| Bibliography                   | 53 |

| Tables and Figures             | 81 |

DITIC QUARTER OF THE TOTAL B

| Accessi                                                                                                                                                                                                                    | on For          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NTIS CONTRACTOR OF THE CONTRACTOR OF T | 13              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| by Distri                                                                                                                                                                                                                  | bution/         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Titot                                                                                                                                                                                                                      | Section Section | :/or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A-1                                                                                                                                                                                                                        |                 | The same of the sa |

# Formal Specification and Verification of Concurrent Programs

## **Capsule Description**

This module introduces formal specification of concurrent software and verification of the consistency between concurrent programs and their specifications. First, what one might want to be able to prove about a concurrent program is discussed. Then, a number of formal descriptions of the concept are presented. These vary in their coverage of the phenomena, and some can be used as the bases of formal specifications of programs. Next, techniques for carrying out the proof of consistency between the specification and the program are described. Finally, it is noted that some of these techniques have automated tools such as verifiers associated with them.

# **Philosophy**

Programming concurrent software is a complex, error-prone task. Because of the inherent nondeterminism, it is difficult for the programmer to understand the effect of his or her own program. It is even more difficult for others, such as the client and the maintainer, to understand this effect.

Formal specification of concurrent software and verification of the consistency of the software with respect to these specifications are useful if for no other reason than they force a closer examination of the software. Sometimes, the formal models exhibit aspects of the nondeterministic behavior that were not otherwise apparent. Other times, just the plain fact of redundancy—the specification and the program are two statements of the same thing, but in different languages—is what is useful.

It is clear that the cost of carrying out formal specification and consistency verification is high. It is so high that formal specification and verification will not be used in a software development unless they are perceived as reducing the total cost of the development. That is, they must be perceived as reducing the number of eventual errors, and the perceived cost of the residual errors were they not done must be higher than the cost of carrying them out.

Consistent with this utilitarian view is the observation that very often the process of writing the formal specification of a system is the same as the process of designing the system's functionality. That is, the act of writing the formal specification is simply recording the requirement decisions that have been made, and most changes taking place in a specification before the first verification attempt are made for the purpose of getting the function of the system right.

This philosophy dictates what material is included in this module. Material is included if, in the opinion of the author, it is oriented toward the practice of software development, that is, if the author believes that the material can be used to help the software engineer develop systems or applications that exhibit concurrency. Hence material describing development methods and specification and verification environments is included. Theoretical work is described to the extent that it provides the logical basis for practical work. Deep theoretical issues—such as axiomatic completeness, formal modeling of fairness, which are important in their own right—are not covered here because they do not have an impact on the applicable work.

Another issue dictating what is covered herein is the simple fact that as this module is being written, the field is expanding! Indeed, the release of this module has been delayed more than once by the discovery of recent new material. An arbitrary decision was taken to release the module now with what is already in it. Surely, the document is thick enough!

Finally, there is still other not-so-recent material that is consistent with the philosophy and is nevertheless not covered in more detail than a mere mentioning with a bibliographical citation. These citations point to approaches that are so similar to approaches covered in detail, that not enough would be gained by discussing them in detail. The choice of which approach to cover among similar approaches was arbitrary, reflecting what was known first to the author, and should not be construed as saying that the presented approach is any better than the others.

In any case, this module discusses neither VDM [Bekic74] nor Z [Hayes87] because

- 1. VDM is covered in another module [Pedersen89] in detail, and

- neither is really intended for use in dealing with concurrency; they both aim at treating programs as functions, and most concurrent programs, being nonhalting systems, are just not describable as functions.

## **Objectives**

The student who has absorbed the material of this module can be expected to

#### Know

of the various tools and environments of tools for carrying out specification and consistency verification

#### Comprehend

- the basic terminology of concurrency

- the various properties that concurrent systems may or may not satisfy and the meanings of and differences between these properties

- the various formal models of concurrency and their relations to each other and their coverage

- the various formal specification languages

- the methods for proving programs consistent with specifications

#### Apply

at least one of the specification languages to a problem of moderate size

#### Analyze

specifications in any of the various specification languages  verifications of consistency carried out in any of the proof systems

#### Synthesize

- a specification of a program in at least one specification language

- a verification of the consistency of a program to specifications in the above language

#### Evaluate

the coverage of any of the above or new formal models, specification languages, and environments

## Prerequisite Knowledge

The student should be fully familiar with the material of the curriculum module Formal Verification of Programs [Berztiss88] and of all of its prerequisites, especially those of programming and mathematical maturity. The student should also be familiar with the of the curriculum modules Concepts of Concurrent Programming [Bustard90] and Languages and System Support for Concurrent Programming [Feldman90] and their support materials.

It is useful, but not essential, to have some familiarity with the material in the curriculum modules Formal Specification of Software [Berztiss87], Software Specification: A Framework [Rombach87], and Software Development using VDM [Pedersen89].

# **Module Content**

#### **Outline**

- I. Unifying Model

- II. Properties of Concurrent Programs

- 1. Safety Properties

- a. Deadlock Freeness

- b. Mutual Exclusion

- c. Data Security

- d. Proper Termination

- e. Partial Correctness

- 2. Liveness Properties

- a. Fairness

- b. Receiving Requested Data

- c. Sent Message Will Arrive

- d. Each Request Serviced

- e. Termination

- f. Total Correctness

- 3. Others

- III. Formal Models

- 1. Operational NDISM

- a. Description of NDISM by Program

- b. Formal Mathematical Descriptions of NDISMs

- c. Redundant Specification of Properties

- d. Formal Verification of Redundantly Specified Properties

- e. Graph Models of Concurrent Computation

- 2. Axiomatic

- 3. Temporal Logic

- 4. Denotational

- 5. Comparisons of the Coverage of the Approaches

- IV. Actual Specifications of Software

- 1. Operating System Security

- 2. Database Integrity

- 3. Protocols

- 4. Other Problems

- V. Doing the Verifications

- VI. Specification Languages and Verification Environments

- 1. AFFIRM

- 2. FDM

- 3. Gypsy

- 4. HDM

- 5. P-NUT

- 6. SARA

- 7. PAISLey

- 8. STATEMATE

- 9. Process Algebras

- 10. ASTRAL

- VII. Current Status

### **Annotated Outline**

#### I. Unifying Model

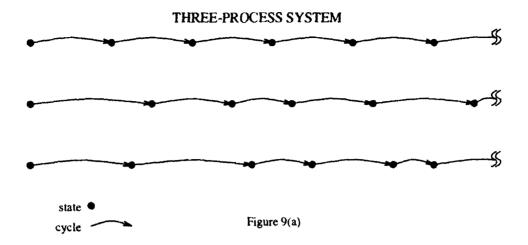

For the purpose of unifying the discussion of all of the formal models of concurrency covered in this module and for providing a basis for comparing them with each other, this module uses the formal model of computation, known as the Nondeterministic Information Structure Model (NDISM) [Wegner68]. It is a state machine formalism in which the content of the state is left unspecified but can be made as simple or as complex as desired. The same pictorial version of this formal model is used in the textbook *Programming Language Structures* [Organick78] and in "A Visual Execution Model for Ada Tasking" [Dillon92].

In NDISMs, concurrency is modeled by supposing the existence of process items in the state and nondeterministically selecting one such process to execute one instruction at each state transition. In other words, concurrency is modeled by interleaving process computations at the granularity of the single instruction.

For the purpose of establishing the notation used in this module, the basic definitions given in the support materials are repeated in this section.

The formal model is that of a nondeterministic information structure model (NDISM) [Wegner68].

$M=(I, I_0, F)$  is an NDISM if and only if

- 1. I is a countable set

- 2. *I*₀⊈*I*

- 3.  $F: I \rightarrow \mathcal{P}(I)$

The elements of the set I are called snapshots.

A possibly infinite sequence  $C=(s_0, \ldots, s_{r-1}, s_i, \ldots)$  is a computation in an NDISM  $M=(l, l_0, F)$  if and only if

- 1.  $\forall s_i \text{ in } C, s_i \in I$

- 2.  $s_0 \in I_0$

- 3.  $\forall i > 0, s_i \in F(s_{i-1})$

- 4. C is a proper initial subsequence of no other sequence meeting conditions 1-3

Note that the  $i^{th}$  snapshot is one of the elements yielded by applying the *transformation F* to the  $i-1^{th}$  snapshot. Herein lies the nondeterminism; in each step of each computation, the next step is chosen from among possibly several candidate next steps. Condition 4 assures that no finite subcomputation of a computation is considered a computation; thus infinite computations must be carried out forever.

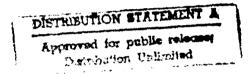

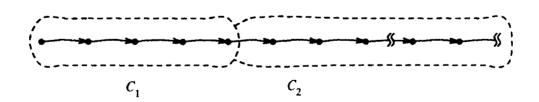

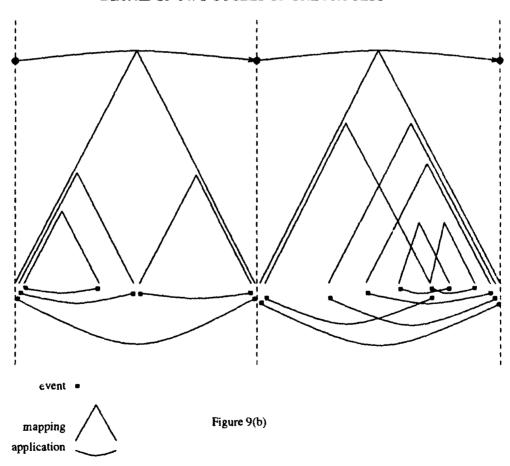

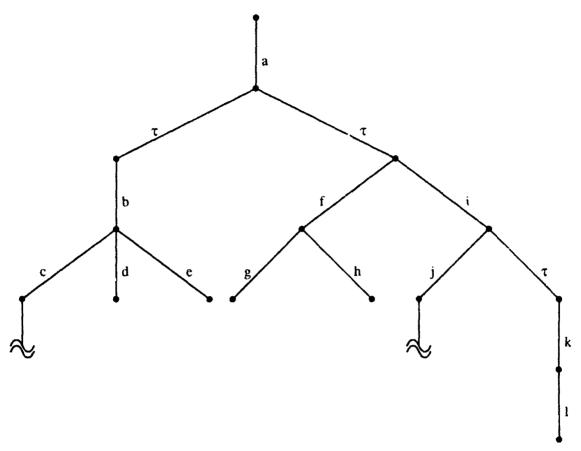

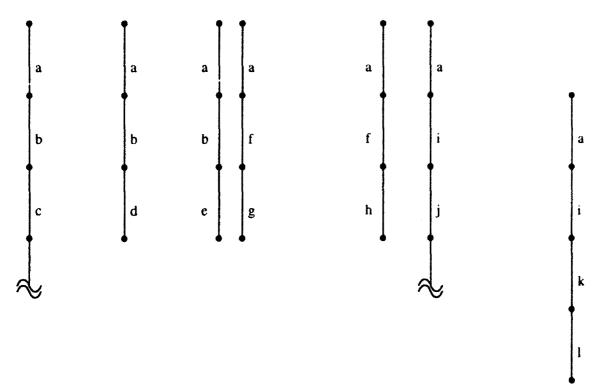

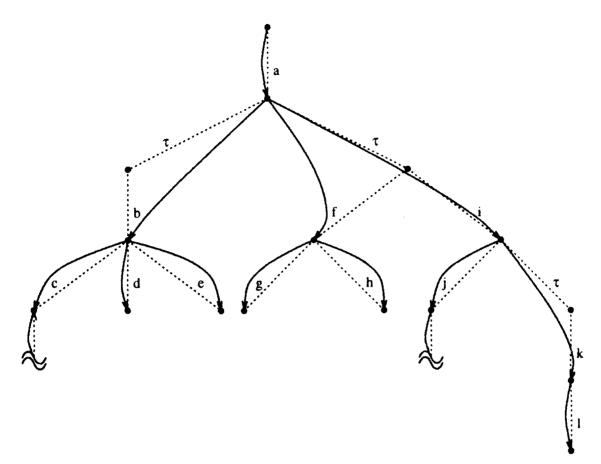

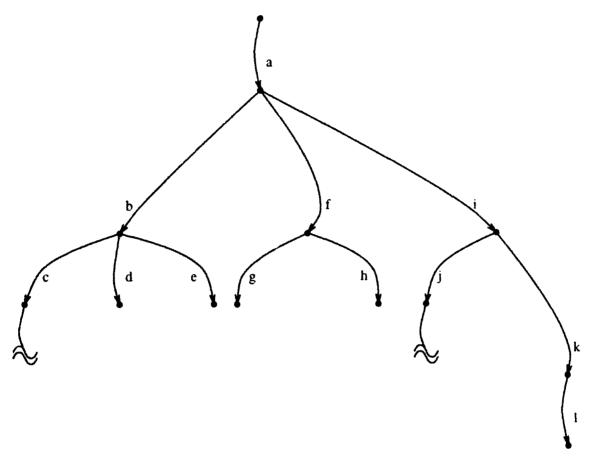

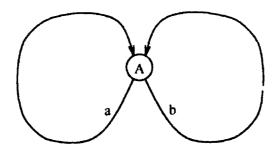

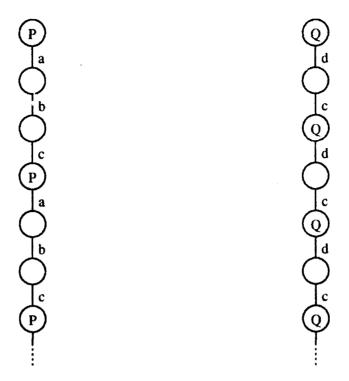

Because of this nondeterminism, one may view an NDISM M as giving rise to a tree of potential computations from each initial snapshot, as Figure 1 illustrates. (All figures and tables are gathered at the end of this document starting on page 100.) The point in the far

left represents an initial snapshot, and each forking point represents the choice of successor snapshots. A computation is a path from left to right along the tree. Note that the nondeterminism that represents concurrency is different from the traditional automata theoretic nondeterminism [Hopcroft79]. Automata theoretic nondeterminism is an abstraction of either (1) trying all possible computations at once until one is found that gives an answer to the problem that the automaton solves or (2) always choosing the right successor snapshot that leads directly to an answer. In concurrency, one is choosing only one path, and there is no notion that any one is more correct than the other.

A computation  $C=(s_0, \ldots, s_{i-1}, s_i, \ldots)$  in an NDISM  $M=(I, I_0, F)$  is said to halt at snapshot  $s_n$  if and only if

- 1.  $s_n$  is in C

- 2.  $F(s_n) = \emptyset$

Note that Condition 4 of the definition of a computation guarantees the uniqueness of  $s_n$ ; it is the first and only snapshot in C that can satisfy Condition 2 of the same definition.

The execution of a program p in the presence of input i is a computation beginning from an initial snapshot  $s_0$ , which contains some representation of p and i. For a given p and i, there may be more than one computation, some of which halt and some of which do not halt. If a computation halts, the computation is said to yield an output, namely a portion of the final snapshot designated as the output o. There are some special situations that have special names.

- If for all input i, all computations arising from i and a program p halt, then p is said to be a halting program.

- If for all input i, all computations arising from i and a program p do not halt, then p is said to be a looping program.

- If for all input i, the initial snapshot built from i and a program p gives rise to at most one computation, then p is said to be a deterministic program.

Note that a program that is not a halting program is not necessarily a looping program, as it may have some computations that do halt and some that do not halt.

A deterministic halting program, which is actually not the subject of this module, is said to implement a function because for each input, the program yields a unique final snapshot from which a unique output may be extracted. A deterministic non-halting program is said to implement a partial function; one assigns undefined as the result of the function for those inputs giving rise to non-halting computations. A nondeterministic halting program can also be considered a function, on the inputs to sets of all possible outputs for the inputs. A nondeterministic non-halting program can likewise be considered a function to sets some of which may contain undefined as elements corresponding to non-halting computations.

A looping program considered as a function is a very uninteresting function, as all of its results are *undefined* or singleton sets containing *undefined*. More usually, looping programs are called *systems*. Normally an operating system is supposed to be a looping program. In reality, operating systems are really non-halting, non-looping, nondeterministic programs. Their halting computations are considered erroneous! A challenge of program verification is to prove that programs that are supposed to implement functions do and that programs that are supposed to implement systems do.

In the usual formal model of concurrency, the snapshots contain some structure representing processes, each of which is in one of the three abstract statuses, awake, asleep, and terminated. When F is applied to a snapshot  $s_i$ , the resulting set of snapshots contains one element for each awake process in  $s_i$ . The result snapshot for a given process shows the changes caused by having that process execute one instruction. Thus choosing an element of  $F(s_i)$  amounts to selecting one process in  $s_i$  to have it execute one instruction. The formal model then models the concurrency with an interleaving at the level of one instruction.

The question can be asked "Is this interleaving model an accurate depiction of concurrency that may include genuine parallelism?" To see that the answer is "Yes!" observe that if the processes shared no data objects (communications channels included) then no process can affect another, and the results of a computation involving these (independent) processes is indistinguishable from those of any, even serial, ordering of the processes. The only way processes can affect each other is through shared data objects. As an example of access to shared data, consider now two processes, being run by two processors, trying to write to the same memory location. In all machines known to this author, there is some hardware arbiter that prevents two processors from writing to the same memory location at the same time and serializes these writes so that one is finished entirely before the other begins. The net effect will be the effect of the second write. This arbiting occurs on every device and guarantees that every possible interaction of otherwise independent processes is serialized to the level of the machine instruction. Thus, any possible concurrent, even parallel, behavior can be simulated by an interleaving model that interleaves at the instruction level. This unit of interleaving is called the granularity of the interleaving. Thus, it is legitimate to use an interleaving formal model to represent concurrency.

#### II. Properties of Concurrent Programs

Recall the discussion about safety and liveness properties in [Bustard90]. Here, this discussion is recast in terms of the NDISM model. Later, when other formulations of these properties are given in other formal models, these formulations will be seen as expressing the same ideas.

Any property that one may wish to verify about concurrent programs may be categorized according to the nature of the property involved. The property may usually be classified as a *safety* property or a *liveness* property. The difference between them, as described in detail below, is in the nature of the quantifiers used over snapshots in their formal expression. This classification captures most of what is desired to prove. There are other properties that cannot be classified as either safety or liveness properties.

For each property described below, enough of a formal statement is given to show why it is a property of the type claimed. The only quantification shown explicitly is that over snapshots. The assertions in the scopes of these quantifiers are given in English. These assertions may obviously contain implicit quantifiers, but none of them are over snapshots; rather they are over elements within a snapshot. Such quantification does not change the nature of the property.

All the kinds of properties are described in terms of the NDISM model introduced earlier.

#### 1. Safety Properties

A safety property is one that can be expressed in an assertion involving universal quantification over snapshots. Examples, in the abstract, of such properties are those that can be expressed thusly

- P is true in all snapshots, i.e.,  $\forall s \text{ in } C(P(s))$

- P never happens, i.e.,  $\forall s \text{ in } C(\neg P(s))$

- Whenever P happens Q is true, i.e.,  $\forall s \text{ in } C(P(s) \supset Q(s))$

Note that the C mentioned is implicitly universally quantified over all computations of the program about which the property is being proved. The program together with any set of input files determines an initial snapshot which, in turn, determines a set of computations of that initial snapshot.

Historically these properties are quite familiar, because they can be demonstrated by inductive means [King80, Cousot82, Manna72]. That is, they are shown to hold for initial snapshots and then they are shown to be preserved by the transition function F of the NDISM. They are very otten expressed without the quantifier, relying on implicit universal quantification of free variables.

#### a. Deadlock Freeness

In no snapshot are all processes as leep or terminated, i.e.,  $\forall s$  in C, there is at least one awake process in s.

#### b. Mutual Exclusion

In no snapshot are two or more processes in their critical region, i.e.,  $\forall s$  in C, if one process in s is in its critical region then no other process in s is in its critical region.

#### c. Data Security

In no snapshot are there unauthorized disclosures, i.e.,  $\forall s$  in C, if a process in s is writing data to a file in s, then the data it is writing is from an object in s to which the process has access.

#### d. Proper Termination

If and when the computation halts, then all processes are terminated (i.e., none are asleep), i.e.,  $\forall s$  in C, if  $F(s)=\emptyset$  then no process in s is asleep. Note that if  $F(s)=\emptyset$ , then no process in s can possibly be awake. Were there an awake process in s, it would be selected for execution to yield a next snapshot.

#### e. Partial Correctness

If at the beginning of the computation, the input is legitimate, and if the computation halts, then the output is what is required. In other words, if at the beginning of the computation, the input is legitimate, then in any final snapshot, the output is as required. In other words, if the input of  $s_0$  in C satisfies input condition I and  $\forall s_i$  in C, if  $F(s_i)=\emptyset$ , then the output of  $s_i$  satisfies output condition O.

Alternatively if at the beginning of the computation the input is in the range of the function to be implemented and if the computation halts, then the output is the result of applying the function to the input, i.e., if the input i of  $s_0$  in C is in the domain of the function f, and  $\forall s_j$  in C, if  $F(s_j) = \emptyset$ , then the output o of  $s_i$  is such that  $o \in f(i)$ .

Note that the second definition accommodates nondeterministic functions.

#### 2. Liveness Properties

A liveness property is one that can be expressed in an assertion involving existential quantification over snapshots. Examples of such properties are those that can be expressed as the following:

- There exists a snapshot in which P is true, i.e.,  $\exists s \text{ in } C(P(s))$

- There exists a snapshot in which P is not true, i.e., ∃s in C(¬P(s))

- Whenever P happens then at some later time Q is true, i.e.,  $\forall s_i \text{ in } C(P(s) \supset (\exists s_i \text{ in } C(j > i \land Q(s_i))))$

The difficulty with liveness properties is that they cannot be demonstrated directly by the familiar inductive methods. They must be demonstrated by showing that each step in the computation brings the computation closer to a snapshot in which the desired property is true. One typically finds a well ordering (that is, a partial ordering with a least element) [Manna74] and program variables, or a function thereof, such that the variable or function values are related by that well ordering such that

- within every n steps, with n fixed, the variables decrease with respect to that ordering, and

- that the variable has reached the minimum implies that the desired property holds

Since a well ordered set has a least element, it is inevitable that the computation will eventually reach a snapshot with the desired property. One typically shows that the variables decrease by appeal to some safety, i.e., invariant, property. There is the need for considerable creativity in finding variables, some function of them, and a relation over the range of that function that allow one to carry out the proof. It should be clear from the complexity of the above description that showing liveness is considered much harder than showing safety.

Because proofs of liveness properties usually require showing some invariant properties along the way, it is no problem if the existential quantifier is within the scope of a universal quantifier.

#### a. Fairness

In all snapshots for all ready processes, eventually the process will become running; i.e.,  $\forall s_i$  in C, for all  $\Pi$ , a ready process in s,  $\exists s_j$  in C, such that  $j \ge i$  and  $\Pi$  is running in  $s_i$ .

#### b. Receiving Requested Data

In all snapshots, if a request for information has been received, then there is a future snapshot m which this information, if legitimate to do so, is released, i.e.,  $\forall s_i$  in C, if  $\Pi$  in  $s_i$  has requested data from an object o in  $s_i$  and  $\Pi$  has access to the object o, then  $\exists s_j$  in C, such that  $j \ge i$  and  $\Pi$  in  $s_j$  receives the data.

#### c. Sent Message Will Arrive

In all snapshots, if a message is sent, then in some future snapshot, the message will be received, i.e.,  $\forall s_i$  in C, if a message m is sent in  $s_i$  then  $\exists s_j$  in C, such that  $j \ge i$  and m is received in  $s_i$ .

#### d. Each Request Serviced

In all snapshots, if a service is requested, then there is a future snapshot in which this request is granted, i.e.,  $\forall s_i$  in C, a service is requested in  $s_i$ , then  $\exists s_j$  in C, such that  $j \ge i$  and the request is granted in  $s_i$ .

#### e. Termination

Eventually the computation halts, i.e.,  $\exists s_i \text{ in } C$ , such that  $F(s_i) = \emptyset$

#### f. Total Correctness

If at the beginning of the computation the input is

legitimate, then eventually the computation halts and the output is what is required, i.e., if the input of  $s_0$  in C satisfies input condition I, then  $\exists s_i$  in C, such that  $F(s_i) = \emptyset$  and the output of  $s_i$  satisfies output condition O.

Alternatively if at  $ii^{n-1}$  beginning of the computation the input is in the range of the function to be implemented, then the computation halts and the output is the result of applying the function to the input, i.e., if the input i of  $s_0$  in C is in the domain of the function f, then  $\exists s_j$  in C, such that  $F(s_i) = \emptyset$  and the output o of  $s_i$  is such that  $o \in f(i)$ .

#### 3. Others

These properties cannot be described either as universal quantification over unquantified snapshot assertions or as possibly universally quantified existential quantification over snapshot predicates. A non-exhaustive list follows:

- P happens infinitely often for all snapshots, there exists a later snapshot such that P, i.e.,  $\forall s_i$  in  $C(\exists s_i \text{ in } C(j>i \land P(s_i)))$ .

- Whenever P happens, within n steps, Q happens, i.e.,  $\forall s_i$  in  $C(P(s_i) \supset \exists s_i$  in  $C(j \ge i + n \land Q(s_i))$ .

- Whenever P happens, within x seconds, Q happens, that is,  $\forall s_i$  in  $C(P(s_i) \supset \exists s_j$  in  $C(Time(s_i) Time(s_i)) \leq x \land Q(s_i))$

- The transition satisfies constraint P [Locasso80, Scheid86a] every transition satisfies P, i.e.,  $\forall s_i, s_{i+1}$  in  $C(P(s_i, s_i))$

#### III. Formal Models

This section describes several well-known formal models of concurrency. Each of these is intended for and has been used for formal verification of properties of concurrent programs. A later section details the proofs that have been done with each. In this section, each is described in terms of its relation to the NDISM model described in Section I. Two considerations dictated the choice of the NDISM as the model of Section I.

- 1. The NDISM, which turns out to be an operational model, is one of the most fundamental in that it can capture all known phenomena, it corresponds to what is implementable and thus what will be found in implementations, and it can be used to model all the others.

- 2. In fact, models similar to NDISMs are used by other authors to describe their formal systems.

For each formal model, the description includes definitions of the basics and a brief discussion of what can be proved using it.

#### 1. Operational — NDISM

Operational models attempt to specify the system

behaviorally, that is by describing what happens during its computations. In every operational model is lurking an NDISM of some form. That is, in every operational model one will find a description of the snapshots or states, a description of initial snapshots, and a description of how to obtain a next snapshot from the current one. Some operational models are described with programs and others are described by other formal means.

#### a. Description of NDISM by Program

When one uses a program to describe an operational model, one is in effect writing an interpreter program which computes from initial snap-The snapshots are described by the declarations of the data structures needed by the interpreter; the initial snapshots are described implicitly as that configuration of the snapshot data structures that are accepted by the interpreter as being legitimate to begin a computation. The transformation is defined implicitly as what the interpreter does in modifying one snapshot into the next. Usually, in the interpreter there is a single identifiable point at which the configuration of the snapshot data structures are considered to form a new snapshot; in a normal interpreter this would usually be at the top of the loop in which instructions are fetched and executed. Examples of these kinds of definitions are the origand several later LISP definitions [McCarthy65] [Reynolds72] and the definition of Euler [Wirth66]. Such definitions are in general hard to use for verification. The transformation function is only implicit. Thus, one is forced to use the formal methods of verifying normal, sequential program behavior [Berztiss88] just to show that the interpreter is doing what it is claimed to, so that one can show that the interpreted program is doing what it is claimed to. An NDISM in which the transformation function is expressed more directly is preferable.

#### b. Formal Mathematical Descriptions of NDISMs

The other languages for writing NDISMs have more mathematical notations for expressing the transformation in a manner that allows a more direct use of parts of its definition in proofs. These languages provide some notation for describing the set of all snapshots and the set of initial snapshots as a subset of the set of all snapshots. In these languages, snapshots have been described as trees with labeled nodes and/or edges, lists, ordered tuples, sets, functions, etc.

There are a number of different ways of specifying the F of a particular NDISM. These ways may be classified by a number of different dimensions. There are direct methods in which F itself

is described and there are indirect methods in which a program P which computes F is described. A program P computes F if and only if each computation of P is a computation induced by F and vice versa.

#### (i) Direct Description of F of NDISM

Within the former methods, there are two different approaches to directly describing F:

- Write a function which given a snapshot yields the set of next snapshots, and

- write a predicate satisfied by legitimate pairs of successive snapshots.

In these approaches of direct specification of F, it is easy to see the individual snapshot transitions but hard to visualize a program P computing the transitions. It may, however, be explicitly stated along with the NDISM that the transition F is not intended to represent primitive or indivisible transitions of the specified system. In this case, one cannot know the individual primitive snapshot transitions. Some examples of languages of the first kind are VDL [Lucas69, Wegner72], and SPECIAL [Silverberg79]. Some examples of languages of the second kind are Ina Jo<sup>TM3</sup> [Locasso80, Scheid86a], and AFFIRM [Thompson81].

#### (ii) Indirect Description of F of NDISM

Within the latter method, any programming language, either of the implemented or gedanken variety can be used. In the gedanken variety, e.g., the language of the Euler definition [Wirth66], one finds languages with sets as data types and not-so-easily-implemented set theoretic operations, including quantification, as operations. In these methods of writing a program P, the program computing F is explicit, but it is hard to see the individual transitions. Indeed, it is usually left unspecified as to what are the indivisible operations in order to give the compiler the right to choose the primitive operations. For example, for

$$x := x + 1$$

the indivisible steps depend on the machine for which the code is generated. Usually the code is something like

resulting in three indivisible steps for the assignment. On the other hand, if the machine has a special instruction for incrementing a

memory location by one, the statement might indeed be compiled into a single indivisible step,

Lamport [Lamport80a] has suggested a way to indicate indivisible operations at the source language level by use of angle brackets, "<, >", around indivisible steps. A decomposition equivalent to the first translation above would be specified as

$$< x : = << x > + 1 >>$$

,

while a decomposition equivalent to the second translation would be specified as

$$\langle x := x+1 \rangle$$

.

#### c. Redundant Specification of Properties

In all of these methods of specifying F, it is sometimes allowed to specify non-algorithmic properties as a redundant description of what the computation is supposed to be doing. For example, one may have specified in F a database system in which each transition represents an update of or a query to the database. The redundant description might describe integrity properties that the data of the database always satisfy. The purpose of this redundant specification is to allow checking or even verification that the operations as specified preserve these properties.

#### **Redundant Properties**

In the direct methods of specifying F, one might give assertions that are to be satisfied by initial snapshots, by all snapshots, and by final snapshots. In the indirect methods, one might give a number of program point-assertion pairs such that every time execution goes through a point, its assertion is to hold. For example, consider a program to sort the elements of an array into ascending order. Attached to the entry point of the outermost loop, which steps through the array in ascending order, might be an assertion claiming that the portion of the array between the beginning and the element indexed by one less than the current loop index value are sorted and are less than all elements in the rest of the array.

Many of the methods of verifying what systems or programs do consists in verifying that the F or P are consistent with their redundant descriptions. Typically for the direct methods of specifying F, an inductive approach is taken to prove that a specified property holds in all snapshots. It is shown that the property holds in all initial snapshots, and then it is shown that if the property holds in any snapshot S, then it holds in any snapshot yielded by applying F to S.

<sup>&</sup>lt;sup>3</sup>Ina Jo is a trademark of Unisys Corporation.

#### **Safety Properties**

In principle any expressible property can be proved in these operational models. However, because of the inductive nature of the typical proof, they have been used primarily for safety properties. It is quite straightforward to express a safety property as an assertion that must be true in every snapshots. One proves the property inductively by showing that all initial snapshots satisfy the assertion and then showing that if it holds at any snapshot, it will hold again at any next snapshot. Showing the latter amounts to showing that the transformation preserves the holding of the assertion.

#### **Liveness Properties**

Generally, liveness properties are not specified and proved. In some cases, the formal basis is not even in the model. For example, in the Ina Jo language, there is explicitly no requirement that any transform (the transformation of the NDISM is the disjunction of the transforms) be done. All one is allowed to show is what will happen if a transfe is done. Moreover, at any snapshot, there is no guarantee that any transform will be applied. In any case, even if the necessary assumptions are present, liveness properties require existential quantification over snapshots. This is considered more difficult than plain universal quantification. Indeed if one has only universal quantification over snapshots, one is not obliged to work with any quantification over snapshots; the properties that hold on these un versally quantified snapshots are proved invariant by inductive means. In fact in the cases of the Ina Jo language, AFFIRM, and SPECIAL, the accompanying interactive or semi-automatic proof system simply cannot handle quantification over snapshots; and there is no way to express them in the language of the system.

Operational models can handle both halting and looping programs. Unlike a functional treatment which assigns undefined to each non-halting computation, operational models consider the sequence of snapshots in a computation as the meaning of any initial snapshot. Hence non-halting computations are distinguishable by the adividual infinite computation sequences.

#### d. Formal Verification of Redundantly Specified Properties

There are a number of approaches to verifying properties of NDISMs. The approaches depend on how the F of the NDISM is specified, either directly or indirectly.

(i) For Directly Specified F of NDISM

If F is specified directly, the usual interests are either of the following:

- Verify certain properties hold about the NDISM specified by F, or

- verify that an implementation of the NDISM is correct.

If one is to verify a property of the NDISM itself, one states the property in the language of the NDISM, say as an assertion involving elements of the snapshot or as a property that F must satisfy or a combination of both. Then the assertion is proved by induction over the length of the computation.

If one is to prove that an implementation of the NDISM is correct, then one must first specify the implementation either as another NDISM or as a program P implementing the computation induced by F.

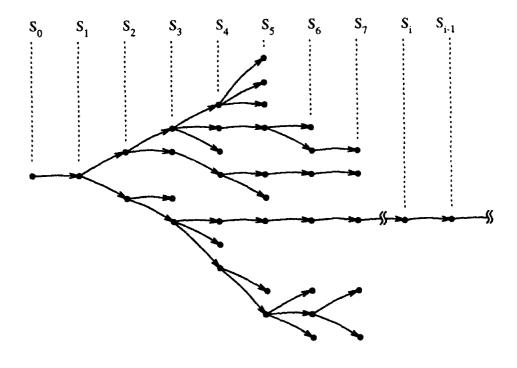

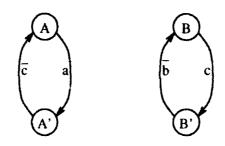

If the implementation of an NDISM  $M_d$  is given as another NDISM  $M_g$ , then the proof is carried out by showing that  $M_g$  simulates  $M_d$  by a proof technique [McGowan71, Berry72] that is similar to that used in automata theory work.

One shows that for each computation  $C_d$  in  $M_c$ , there exists a computation  $C_g$  in  $M_g$  which behaves the same way. By behaving the same way is meant that there is a function  $\psi: I_g \to I_d$  which builds each snapshot of  $C_d$  from its corresponding snapshot in  $C_g$ . That  $\psi$  has this property is shown by mathematical induction on the length of the computation  $C_d$ .

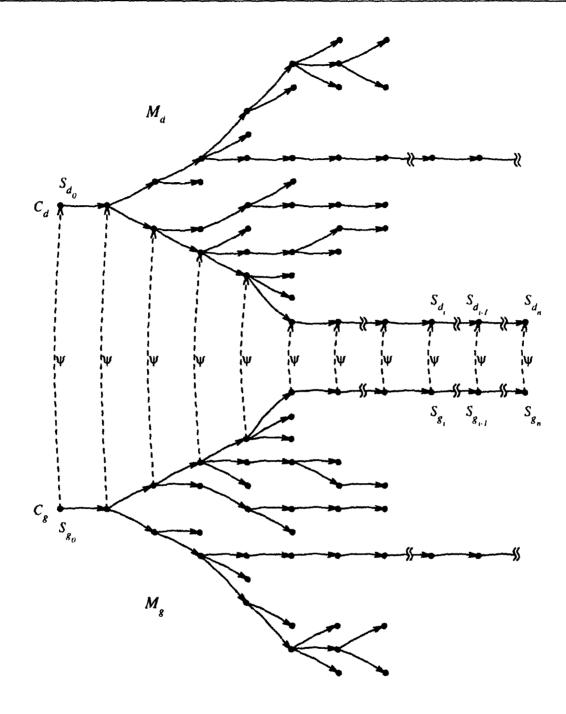

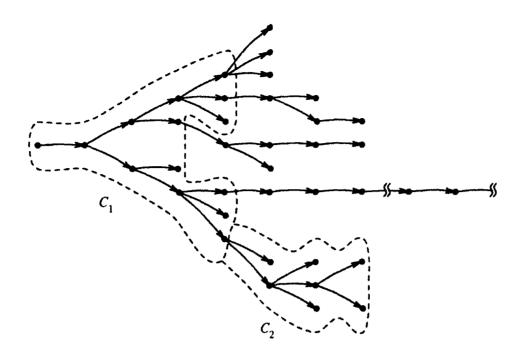

Many times,  $C_g$  simulates  $C_d$  in a lock-step snapshot-by-snapshot fashion. However, many times, this lock-step simulation is not possible; it takes several steps in  $C_g$  to implement a single step in  $C_d$ . The meaning of correspondence can be changed to allow  $\psi$  to build only some of the snapshots of  $C_d$  out of only some of the snapshots of  $C_g$ . The constraint is that a gap of no more than some fixed number is allowed between successive building snapshots in  $C_g$  and between successive built snapshots in  $C_g$ .

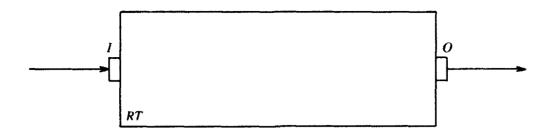

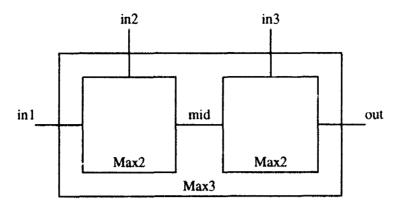

The lock-step situation is illustrated in Figure 2. The Support Materials for Concepts of Concurrent Programming has a full formal definition of simulation of one NDISM by another.

<sup>&</sup>lt;sup>4</sup>The subscript "d" signifies implementeD, and the subscript "g" signifies implementinG.

If on the other hand, the implementation of the NDISM is not another NDISM, but is in fact code in some programming language, then two possibilities exist:

- The whole NDISM is implemented by a single program P. The correctness issue is whether P implements the whole of F down to the nondeterministic choices and the potential unbounded computation length.

- The F can be decomposed into a collection of individual operations, each of which does one of the possible transformations. The operation of F consists, in each application, of selecting one of these transformations and executing only it. In this case, the usual implementation is built of a collection of procedures for the individual operations and of a previously cooked shell which chooses the right operation at each step and invokes the corresponding procedure. The correctness issue is then whether the individual procedures implement the individual operations, the shell being presumed correct.

In either case, one ends up using the various program verification techniques, such as that of Hoare [Hoare69] in which one shows an actual program to satisfy certain properties [Berztiss88].

# (1) NDISM Implemented by Single Program

In the first possibility, if the NDISM truly exhibits non-deterministic behavior and the non-determinism is part of the specified behavior, e.g., to specify concurrency as opposed to possible allowed non-concurrent computations, then the program will have to exhibit the same non-determinism in the form of concurrency. The NDISM specification will have to be converted somehow into a specification that is used by one of the various methods to prove program behavior. If the NDISM halts for all desirable computations, then input, output, and most likely invariant assertions will have to be generated to describe the program's behavior. If the NDISM intentionally does not halt for all desirable computations, then output assertions are useless, as they vacuously hold. Moreover, invariant and so-called "eventually" assertions, i.e., liveness assertions, will have to be generated to describe the program's behavior. Then the chosen proof method is used to verify that the program has the desired behavior. If on the other hand the NDISM's non-determinism is merely to state allowable computational orders, any allowed order is considered correct, and it is not required to be able to do them all, then standard methods for nonconcurrent programs are to be used. These are outside the scope of this module and the reader should consult [Berztiss88] for more details.

# (2) NDISM Implemented by a Collection of Invokable Procedures

In the second possibility, the problem has been reduced to showing the correctness of a collection of non-concurrent subroutines implementing non-concurrent transitions, whose only non-determinism is for the purpose of allowing any one of several possible results. The concurrency has been pushed down into the process of selecting which of the available transitions will be invoked next. If one verifies that the procedures do implement the transitions, then to the extent that the basic invoking shell works, the collection of procedures plus the shell implements the NDISM. The meaty part of this verification has been reduced to the standard non-concurrent variety which is outside the scope of this module.

#### (ii) For Indirectly Specified F of NDISM

If F is specified indirectly with a program P, the interests are the same as for a directly specified F, i.e.,

- to verify that an implementation of the NDISM is correct, or

- to verify certain properties hold about the NDISM specified by P.

It is rare that one has to prove the correctness of an implementation of an NDISM specified by a program, particularly when the specifying program is executable. However, when it is done, particularly when the specifying program is not executable, it is done by proving the implementing and the defining programs equivalent. This proof can be done by showing that

- both compute the same function,

- both satisfy the same formal specifications, albeit input/output or temporal logical,

- a series of correctness preserving transformations [Balzer81, Balzer85] modifies one (usually the defining one) into the other, or

- one is compiled into the other.

Verifying that certain properties hold involves specifying these properties in the form of assertions which are attached to the program as a whole or to various places in the program, depending on the method being used. Then the code is proved consistent with the assertions by

the method being used. For example, if one is using Hoare logic, the assertions will be sprinkled around the program, while if one is using temporal logic, the assertions will be attached to the program as a whole. Assertions attached to the program as a whole describe properties of the program's computation as a whole in terms of particular snapshots that exist at various times during the computation. Assertions attached to points in the program describe the snapshot at any time execution passes through that point.

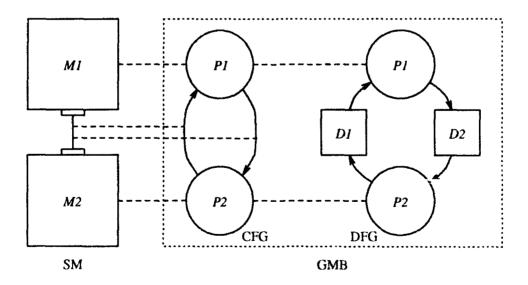

#### e. Graph Models of Concurrent Computation

The various graph-based systems such as controland data-flow schemes, Petri nets [Peterson81], etc. are also operational. However, the language for expressing the parts of the NDISM is pictorial. Associated with each is a description of how a diagram is to be interpreted as specifying a computation. Usually this description says something to the effect of

Select some process node, all of whose input arcs contain tokens. Fire that node, remove one token from each input arc, and deposit one token on each output arc.

That description may be stated in natural language, some programming language, some mathematical language or some mixture of all of these. Generally what the processes in the nodes do is left unspecified or, to use the terminology, of the models uninterpreted. Those that model data flow as well as control flow state which data objects are used, but in the uninterpreted domain, they say nothing about the actual values of the data. Because there are no interpretations as to what the processes do, the set of computations that can be described is limited. One uses such models strictly to focus on the concurrency and synchronization issues. The philosophy behind these uninterpreted models is that if a property can be proved of an uninterpreted model then it holds for all interpretations of that model. One might be able to prove mutual exclusion for a program just on the basis of its control structures. independent of any values of any objects. Because of the limited functionality in the models, it is generally easier to carry out proofs; there are fewer operations to consider. On the other hand, this lack of functionality may prevent proving properties that hold only because of the values of objects and not strictly because of the structure of the programs.

Because of the limited functionality, not all properties expressible in other operational models are expressible in these pictorial models. For example, it is impossible to demonstrate partial or total correctness without knowing the values of

objects. However, one can express proper termination as termination, i.e., having no fireable node (no node has tokens on all of its input arcs) while having less than some fixed number of tokens on each arc. For such control flow schemes, proper termination is even decidable.

#### 2. Axiomatic

Axiomatic systems for dealing with concurrency provide three main ingredients,

- an assertion language for describing snapshots at arbitrary points in a program's execution, usually the language of first order predicate calculus with equality,

- a set of axioms for describing the behavior of primitive statements,

- rules of inference for combining behaviors of constituent statements into behaviors of the containing constructs such as loops, conditionals, programs, etc.

#### Hoare Logic and its Limitations

Axiomatic systems for dealing with concurrency are generally based on Hoare's logic [Hoare69] or Dijkstra's weakest precondition logic [Dijkstra76]. The main difficulty in using these logics directly for dealing with concurrent programs is that because of the potential of interference, their axioms do not work. For example, the axiom for assignment is

$$\{P_e^x\}\,x{:=}e\,\{P\}$$

which when adapted to the assignment statement

$$x := x+1$$

under the condition that

$$x=1$$

prior to the assignment yields

$$\{x=1\} x:=x+1 \{x=2\}$$

.

However, as mentioned in Section II.3.d, when this assignment is executed in the presence of other interfering processes, the value used to compute x+1 may not be the same as is mentioned in the input assertion.

The various extensions to the axiomatic logics deal with this interference problem in different ways. The axiomatic systems surveyed are

- the Owicki-Gries extension of Hoare logic,

- the Lamport extension of Hoare logic, and

- the Lamport extension of Dijkstra's weakest precondition logic.

#### Owicki-Gries's Extension of Hoare Logic

Owicki and Gries [Owicki76a, Owicki76b] use ordinary Hoare logic axioms but put non-interference

requirements into the antecedents of rules of inference. For example, the rule they give for the parallel-execution statement

resource  $r_1(variable\ list), ..., r_m(variable\ list)$ cobegin  $S_1 \parallel ... \parallel S_n$  coend

is as follows.

If  $\{P_1\}S_1\{Q_1\}$  and ...  $\{P_n\}S_n\{Q_n\}$  and no variable free in  $P_i$  or  $Q_i$  is changed in  $S_j$  with  $i\neq j$ , and all variables in I(r) belong to resource r, then

$$\{P_1 \wedge \ldots \wedge P_n \wedge l(r)\}\$$

resource  $r_j(variable\ list), \ldots, r_m(variable\ list)$

cobegin  $S_1 \parallel \ldots \parallel S_n$  coend

$\{Q_1 \wedge \ldots \wedge Q_n \wedge l(r)\}.$

This rule says that in the case of parallel execution of statements, the normal axioms and rules may be used for the individual statements if there is no chance of interference between them. The rule puts upon the prover the obligation to show non-interference.

#### Lamport's Extension of Hoare Logic

Lamport takes sort of an opposite approach, of changing the meaning of the assertions and the axioms for primitive statements so that they catch interference in a slightly different way. In the Lamport logic,

$$\{P\}S\{Q\}$$

means, "if execution is begun anywhere in S with the predicate P true, then executing S will leave P true while control is inside S, and will make Q true if and when S terminates." Thus, Lamport's treatment of the assignment

x := x+1

under the condition that

x=1

prior to the assignment is

$${x=1 \land [after('') \supset value(')=2]}$$

:= {x=2}

In this, angle brackets are used to surround operations that are atomic, i.e., cannot be interrupted and are guaranteed to be done within a single NDISM step both in the abstraction and in any implementation. The rule says that if x starts off as 1, and after doing x+1 the value of that subexpression, x+1, is still 2, then the assignment causes x to get 2. In other words, if there was no interference with x during the assignment, it behaves as an assignment in the normal nonconcurrent situation. Of course, it is on the prover to demonstrate that there is no interference. In this sense, this approach is equivalent to Owicki's.

Because these axiomatic methods prove that assertions which are attached to specific places in the program are invariant, they really address only safety properties.

#### Dijkstra's Weakest Precondition Logic

Dijkstra introduced a variation of the Hoare axiomatic system when he introduced a proof-directed discipline of programming [Dijkstra76]. The approach, that of weakest precondition, attempts to find the weakest conditions under which a given statement is guaranteed to halt and to yield a snapshot satisfying a given postcondition. For example,

$$wp(x:=x+1, x=2)$$

ÍS

x=1.

because only when x=1 is x:=x+1 guaranteed to halt and yield x=2. The general rule for the assignment statement is

$$wp(x:=e,P)\equiv P_e^x$$

,

the obvious correspondent to the Hoare rule,

$$\{P_e^x\} x := e\{P\}.$$

There is a dual for the weakest precondition called the *strongest postcondition*. The strongest postcondition, sp(S, P), of a statement S and a precondition P is the strongest condition describing any snapshot yielded by the execution of S from any snapshot satisfying P.

The Hoare rule is a partial correctness rule, as its meaning carries no requirement that the statement halts. It provides only that if the statement halts then the postcondition is true; if the statement does not halt, then any postcondition is accepted as vacuously true. The weakest precondition formulation, on the other hand, finds preconditions which guarantee halting as well.

#### Lamport's Extension of Weakest Precondition Logic

Recall that most concurrent programs are systems that are supposed never to halt. For such programs, the weakest precondition would be false for any postcondition. Therefore, Lamport has developed a variant of the weakest precondition approach that is more useful for concurrent non-halting systems. For concurrent programs that do not halt, the interest would be to prove some invariant property, i.e., a safety property. Accordingly, Lamport [Lamport87] defines the concepts of weakest invariant, win, and strongest invariant, sin, and gives rules for deriving them for programs given the wp, sp, win, and sin for constituent statements.

I is an invariant of S if

$\{I\}S\{I\}$ .

Lamport then defines S as leaving an assertion l invariant if and only if

$$I \supset wp(S, I)$$

;

it is also the case that

$$sp(S,I)\supset I$$

.

Then, win(S,Q) is the disjunction of all predicates I such that  $I \supset Q$  and S leaves I invariant, and

sin(S,P) is the conjunction of all invariants I of S such that  $P \supset I$ .

Lamport is able to extend the Owicki-Gries method to be able to reason about programs for which the atomic operations are not specified. However, note that the weakest and strongest invariants do not give the power to work with liveness properties.

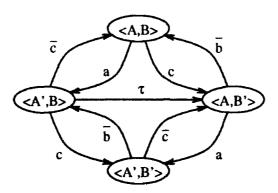

#### 3. Temporal Logic

Temporal logic [Pnueli77, Pnueli81] is an attempt to deal with the logic of computation sequences without succumbing to the difficulties of quantification. One is able to talk directly about sequences of snapshots, all snapshots, and the existence of a snapshot that have desired properties. The direct expression is based on an axiomatized logic of time that obviates the necessity to quantify over snapshots.

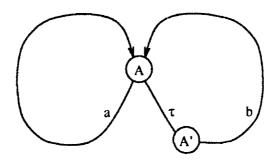

In temporal logic, one is provided temporal operators, "henceforth" ( ) and "eventually" ( $\Diamond$ ) which can be applied to the standard assertions about snapshots. While they can be defined relative to each other axiomatically, any model of them makes use of some underlying NDISM. Hence, they are described here in that manner.

#### **Basic Temporal Operators**

Temporal semantics talks about assertions that hold true in the current snapshot or all or some future snapshots. Therefore, it will be necessary to identify which snapshot in a computation is the current one. The current snapshot will be called  $s_c$  in the following discussions.

$$\Diamond P \equiv \exists s_i (i \geq c \land P(s_c))$$

Note that occurring henceforth includes occurring in the current snapshot. That something eventually occurs includes the possibility of it occurring in the current snapshot.

Just as the universal quantifier and the existential quantifier are duals of each other so are  $\square$  and  $\lozenge$ .

$$\begin{array}{|c|c|c|c|c|}

\hline

P = \neg \lozenge \neg P \\

\lozenge P = \neg

\end{array}$$

It is useful to define some other operators that correspond to often used temporal relations. One such useful relation is "leads to" (-->).

$$A \longrightarrow B \equiv A \supset \Diamond B$$

With these temporal operators it is easy to express both safety properties and liveness properties. To do these, it is necessary to let *INIT* be an assertion that is true at all and only proper initial snapshots; that assertion is needed to anchor the time to the start of the computation rather than to any arbitrary current snapshot.

#### **Expressing Properties with Temporal Operators**

Recall the general safety properties introduced in Section II.4.a.i.

- P is true in all snapshots, i.e., INIT

- P never happens, i.e.,  $INIT \supset \neg P$

- Whenever P happens Q is true, i.e.,  $INIT \supset (P \supset Q)$

Recall also the general liveness properties introduced in Section II.4.a.ii.

- There exists a snapshot in which P is true, i.e.,  $INIT \supset \Diamond P$

- There exists a snapshot in which P is not true, i.e.,  $INIT \supset \Diamond \neg P$

- Whenever P happens then at some later time Q is true, i.e.,  $INIT \supset P \longrightarrow Q$

Temporal logic can even capture some properties that are neither safety nor liveness, such as the concept of P happening infinitely often.

$$INIT \supset \Box \Diamond P$$

Provided with the temporal logic is a system of axioms and rules of inference for reasoning directly in the temporal domain without having to fall back on a model. In order to be able to prove things about a program using temporal logic it is necessary to provide a temporal logic-based semantics of one's programming language. Besides saying what each kind of statement does, the semantics provides a basic liveness property for each primitive statement that says that it eventually finishes. From this liveness property and the semantics of the various constructs, the prover is able to prove liveness properties of whole programs.

#### Linear and Branching Time

There are, in fact, two alternative models of time in temporal logic, linear time and branching time. Both are intended to be used with nondeterministic computations. Recall in Section I, that two kinds of nondeterminism were identified, the kind that models concurrency and the kind that is used for automata-theoretic investigations of algorithms. Linear time corresponds to the concurrency-modeling nondeterminism, and branching time corresponds to the automata-theoretic nondeterminism. The temporal logic described above is in fact linear time, as it was stated that

$$\Diamond P \equiv \neg \Box \neg P$$

That is, if it is not true that P never occurs, it eventually occurs. This statement is true only if there is only one possible future, namely a single path down the tree of computations. "Not occurring never" means that it must eventually occur. However, in branching time, automata theoretic nondeterminism, the fact that it is not true that P never occurs means that there exists some computation in which P does occur; it may not occur in all possible futures, i.e., all possible computations from now. The formal treatment of branching time is to distinguish between the "eventually" and the "not never" operators. The former has the meaning implied by the operational model and the latter is the dual of the "henceforth" operator. However, since branching time is not really a good model of concurrency, it will be discussed no more in this module.

#### **Another Temporal Operator**

There is a third temporal operator used by some authors, e.g., Ben-Ari, Manna, and Pnueli [Ben-Ari81] and Hailpern [Hailpern82], namely the "next" (0) operator. It applies its argument predicate to the next snapshot.

$$\circ P \supset P(s_{c+1})$$

As the use of o implies an explicit time scale or an explicit sequential progression of time, the tendency is not to use it. Using it would overspecify a computation to the point of saying that a certain event has to happen in the next snapshot and would not be acceptable if it were implemented as a multi-step procedure.

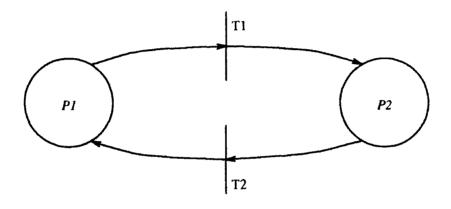

#### **Temporal Logic Specification of Concurrency**

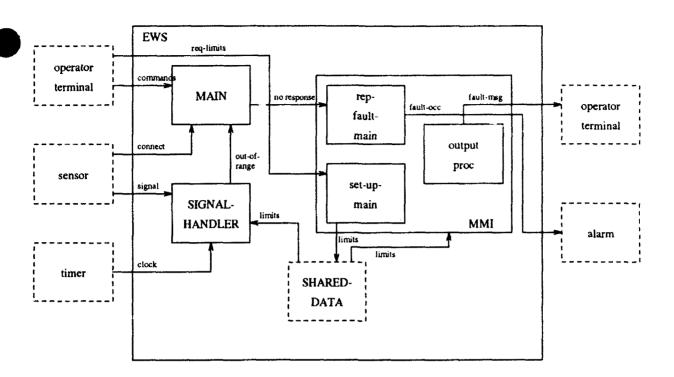

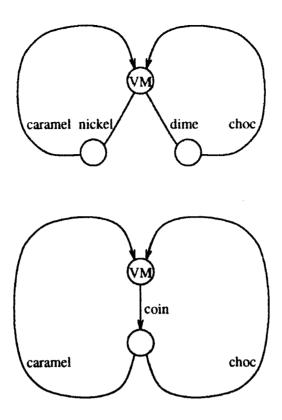

Hailpern's Ph.D. thesis [Hailpern82] defines a useable version of temporal logic, describes a programming language, VALET, with processes and monitors, gives a temporal logic semantics for the language, and demonstrates how properties of programs in this language may be specified and verified. These ideas are then applied to specify and verify the correctness of programs implementing a number of network protocols and resource allocation systems.

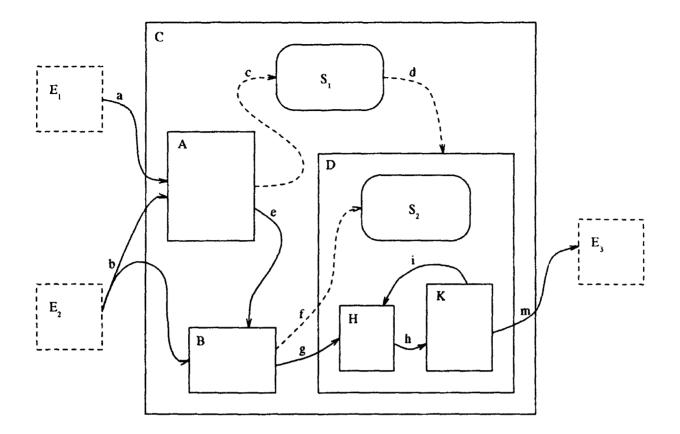

In VALET, processes and monitors are written in the ferm of separate modules that may see and invoke each other. The form of a process module is similar to that of a Pascal program. It declares local variables and has a body consisting of a sequence of statements which may contain calls to procedures offered by the monitor modules. Generally, the body of a process module is an infinite loop. A monitor module declares local variables and a collection of procedures invokable from outside the monitor, in fact, in general, no module's local variables are visible from outside the module. The semantics of these modules is that all process modules are invoked to run concurrently at the beginning of the computation. All monitors are invoked also in order to have their initialization code executed. Then the monitors sit and wait until monitor procedures are called by the processes. The operational rule is that no more than one process can be executing the body of any procedure inside a given monitor. The at most one process that is executing inside a monitor procedure is said to currently own the monitor.

For a particular system involving process and monitor modules one gives specifications as follows for each module:

- For each process, one gives an invariant and a commitment.

- For each monitor as a whole, one gives an invariant.

- For each monitor procedure, one gives a service specification and a commitment.

#### Invariants

Among the invariants above, there are two kinds which are somewhat different from the more familiar loop invariant, which is true each time control passes through the loop cut point and which may not be true at other points in the loop. A loop invariant would be specified as the following kind of safety property:

where *l* involves only variables visible at the cut point. The invariant of a process is a property of variables visible to the process which is true at *all* times. It would be specified more simply:

where I involves only variables visible to the process. A monitor invariant is a property of the local variables of the monitor which is true at all times, except possibly during the execution of the body of

a monitor procedure. This exception allows monitor procedure bodies to make temporary changes that may invalidate the invariant so long as they restore the holding of the invariant upon exit. For example, in a monitor which keeps a linked list of the resources it is managing, the invariant would describe a well-formed linked list. The monitor procedure to remove an item from the list would temporarily invalidate the invariant as it performed the pointer manipulations to rebuild the list after removing the item. However, after the list is rebuilt, the invariant would once again hold. It is safe to let the monitor procedures invalidate the invariant temporarily because it is guaranteed that at most one process can be inside any procedure of a monitor at any given time. Therefore, it is not possible that any other process's concurrent operation can mess up the list while it is not in proper form. It is on the monitor writer to insure that all invariants still hold whenever a process can relinquish ownership of the monitor, namely upon a wait statement or upon return from a monitor procedure. It is this invariant that is called I in the rule for the monitor procedure body.

The invariant of a process is proved by standard safety assertion verification methods. That is, it is shown that the invariant holds upon initiation of the process and that each statement inside the process preserves its holding. The invariant of a monitor is demonstrated to hold after the end of its initialization part, and then each monitor procedure is demonstrated to preserve the invariant's holding across, but possibly not within, its body.

#### Service Specification

A service specification for a monitor procedure is simply its input/output specification, i.e., the P and Q of the rule for the monitor procedure body. This is demonstrated by standard safety assertion verification methods.

#### Commitment

A commitment is a liveness assertion, as it states properties that are guaranteed to happen. Note that a service specification does not really guarantee very much since it is only a statement of partial correctness, i.e., what happens if the body halts. A commitment, being a liveness assertion can carry a guarantee of something happening, especially if it contains an occurrence of the eventually operator. Indeed, it is for this reason that processes, which generally loop and do not halt, do not have service specifications. A process's commitment states the progress that it guarantees to have as it loops indefinitely.

The liveness assertions of a process are proved by composing the liveness assertions of its statements and the liveness assertions of the monitor procedures it calls. As mentioned, liveness assertions of the

monitor procedure bodies are verified by composition of the liveness assertions of their constituent statements.

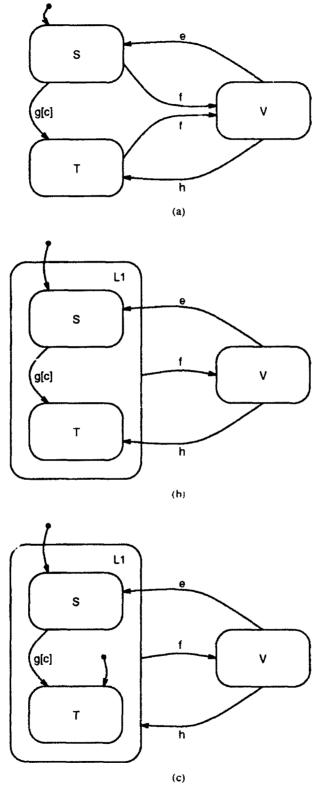

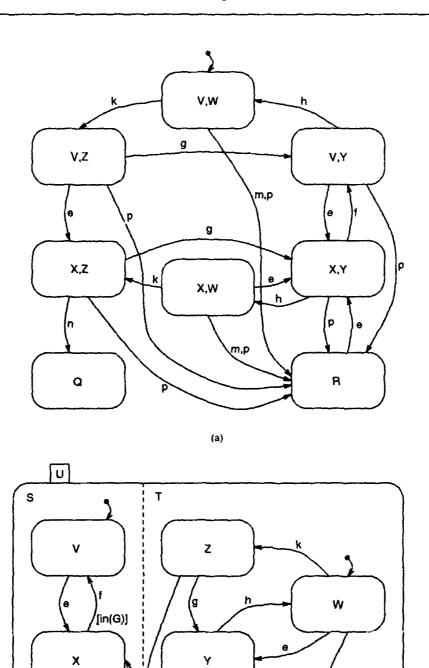

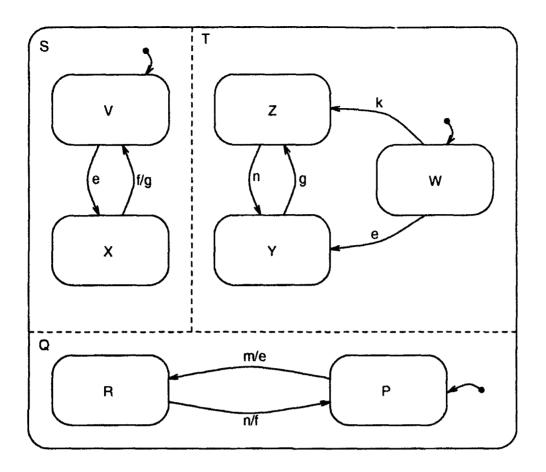

#### Advantage of Temporal Logic