| ΔD-Δ                                                                                                                                                                                                                                     | 257 684                                                                                                                                                                                               | ON P                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                  | Form Approved<br>OMB No. 0704-0188                                                                                                                                                                                                                                                                                   |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Public repoi<br>sources, ga<br>other aspec<br>Operations :<br>Project (070                                                                                                                                                               |                                                                                                                                                                                                       | reviewing<br>ucing this                                                                                         | srage 1 hour per response, including the time for reviewing instructions, searching existing data<br>reviewing the collection of information. Send comments regarding this burden estimate or any<br>using this burden, to Washington Headquarters Services, Directorate for Information<br>atom, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction |                                                                                                                                                                                                                                                                                                                      |  |  |

| 1. AGENCY USE ONLY (Leave blank)                                                                                                                                                                                                         | 2. REPORT D<br>10/29/9                                                                                                                                                                                |                                                                                                                 | 3. REPORT TYPE AND DAT<br>Quarterly Technic<br>7/01/92 - 9/30/92                                                                                                                                                                                                                                                                                                                 | cal Report                                                                                                                                                                                                                                                                                                           |  |  |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                    | 5. FUNDING NUMBERS                                                                                                                                                                                    |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                      |  |  |

| RF Vacuum Microelectro                                                                                                                                                                                                                   | onics                                                                                                                                                                                                 |                                                                                                                 | 14                                                                                                                                                                                                                                                                                                                                                                               | MDA972-91-C-0030                                                                                                                                                                                                                                                                                                     |  |  |

| 6. AUTHOR(S)<br>A.I. Akinwande, P. Bauha                                                                                                                                                                                                 | ahn. B. Speldrich, D.                                                                                                                                                                                 | Arch                                                                                                            | NOV05 1992                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                      |  |  |

| 7. PERFORMING ORGANIZATION NA<br>Honeywell Sensor and Sy<br>10701 Lyndale Avenue So<br>Bloomington, Minnesota                                                                                                                            | stem Development Ce                                                                                                                                                                                   | enter                                                                                                           | E                                                                                                                                                                                                                                                                                                                                                                                | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER                                                                                                                                                                                                                                                                          |  |  |

| 9. SPONSORING/MONITORING AGE<br>Defense Advanced Resear<br>3701 N. Fairfax<br>Arlington, Virginia 22203                                                                                                                                  | ch Projects Agency D                                                                                                                                                                                  |                                                                                                                 | SO                                                                                                                                                                                                                                                                                                                                                                               | 10. SPONSORING/MONITORING<br>AGENCY REPORT NUMBER<br>92-28812                                                                                                                                                                                                                                                        |  |  |

| 11. SUPPLEMENTARY NOTES                                                                                                                                                                                                                  |                                                                                                                                                                                                       |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                  | 400                                                                                                                                                                                                                                                                                                                  |  |  |

| 122. DISTRIBUTION/AVAILABILITY ST                                                                                                                                                                                                        | ATEMENT                                                                                                                                                                                               |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                  | 12b. DISTRIBUTION CODE                                                                                                                                                                                                                                                                                               |  |  |

| Approved for public rele                                                                                                                                                                                                                 | ase: distribution is unl                                                                                                                                                                              | imited                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                      |  |  |

| 13. ABSTRACT (Maximum 200 words)                                                                                                                                                                                                         |                                                                                                                                                                                                       |                                                                                                                 | · · ·                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                      |  |  |

| emitter based vacuum t<br>than 250V and which c<br>of field emitter diodes<br>measured on diode edg<br>edge emitter diode whi<br>results we have design<br>requirements. The first<br>fabrication run of the e<br>Equivalent circuit and | riode with performance<br>an be modulated at 1 (<br>were completed. Curre<br>ch is a factor of 25 gr<br>ned a diode array str<br>ist fabrication run of<br>edge emitter vacuum<br>FEM modeling of the | ce goals<br>GHz for<br>urrent de-<br>ent emiss<br>reater tha<br>ructure to<br>this arra<br>triode was<br>vacuum | of 10 $\mu$ A/ $\mu$ m emission<br>1 hour. Fabrication of<br>nsitites of up to 10 p<br>sion of 380 $\mu$ A was m<br>n at the start of the p<br>o achieve the 5 mA<br>y is completed and<br>as completed this qua-<br>edge emitter triode i                                                                                                                                       | development of an edge<br>on current density at less<br>of two more process runs<br>$\mu A/\mu m$ have now been<br>measured for a thin film<br>program. Based on these<br>A total current program<br>I now in test. The first<br>parter and is also in test.<br>indicates that we should<br>e device is mechanically |  |  |

| 14. SUBJECT TERMS<br>Vacuum microelectroni<br>high frequency devices.                                                                                                                                                                    |                                                                                                                                                                                                       | film tech                                                                                                       | nology,                                                                                                                                                                                                                                                                                                                                                                          | 15. NUMBER OF PAGES                                                                                                                                                                                                                                                                                                  |  |  |

| Bu nodaana) garraas                                                                                                                                                                                                                      | ,                                                                                                                                                                                                     |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                  | 16. PRICE CODE                                                                                                                                                                                                                                                                                                       |  |  |

| 17. SECURITY CLASSIFICATION                                                                                                                                                                                                              | 3. SECURITY CLASSIFIC                                                                                                                                                                                 | ATION                                                                                                           | 19. SECURITY CLASSIFICA                                                                                                                                                                                                                                                                                                                                                          | ATION 20. LIMITATION OF ABSTRACT                                                                                                                                                                                                                                                                                     |  |  |

| OF REPORT<br>Unclassified                                                                                                                                                                                                                | Unclassified                                                                                                                                                                                          |                                                                                                                 | Unclassified                                                                                                                                                                                                                                                                                                                                                                     | UL                                                                                                                                                                                                                                                                                                                   |  |  |

| NSN 7540-01-280-5500                                                                                                                                                                                                                     | 92                                                                                                                                                                                                    | 1 7                                                                                                             | 088                                                                                                                                                                                                                                                                                                                                                                              | Standard Form 298 (Rev. 2-89)<br>Prescribed by ANSI Std. 239-18<br>298-102                                                                                                                                                                                                                                           |  |  |

## **Quarterly Technical Report**

## **RF Vacuum Microelectronics**

## 7/01/92 - 9/30/92

Sponsored by: Defense Advanced Research Projects Agency Defense Sciences Office (DSO) RF Vacuum Microelectronics DARPA Order No. 8162 Program Code No. 1M10 Issued by DARPA/CMO under Contract #MDA972-91-0030

| 10701 Lyndale Avenue South   | -                                                          |                                                                                                                                       |                                                                                                                                                                               |

|------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bioomington, Minnesota 55420 | NTIS<br>DTIC<br>Unanr                                      | CRA&I<br>TAB<br>nounced                                                                                                               |                                                                                                                                                                               |

| DTIC QUALTING                | By<br>Distribution /                                       |                                                                                                                                       |                                                                                                                                                                               |

|                              | Α                                                          | Availability Codes                                                                                                                    |                                                                                                                                                                               |

| THE PROPERTY &               | Dist                                                       | Avail a<br>Spec                                                                                                                       | nd / or<br>sial                                                                                                                                                               |

|                              | A-1                                                        |                                                                                                                                       |                                                                                                                                                                               |

|                              | 10701 Lyndale Avenue South<br>Bloomington, Minnesota 55420 | 10701 Lyndale Avenue South<br>Bloomington, Minnesota 55420 Acces<br>NTIS<br>DTIC<br>Unanr<br>Justifi<br>By<br>DTIC QUALITY INSPERSENT | Bloomington, Minnesota       55420       Accesion For         NTIS       CRA&I         DTIC       TAB         Unannounced       Justification         By       Distribution / |

"The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the Defense Advanced Research projects Agency or the U.S. Government"

## **RF Vacuum Microelectronics Quarterly Technical Report** 7/01/92 - 9/30/92

## I. Background

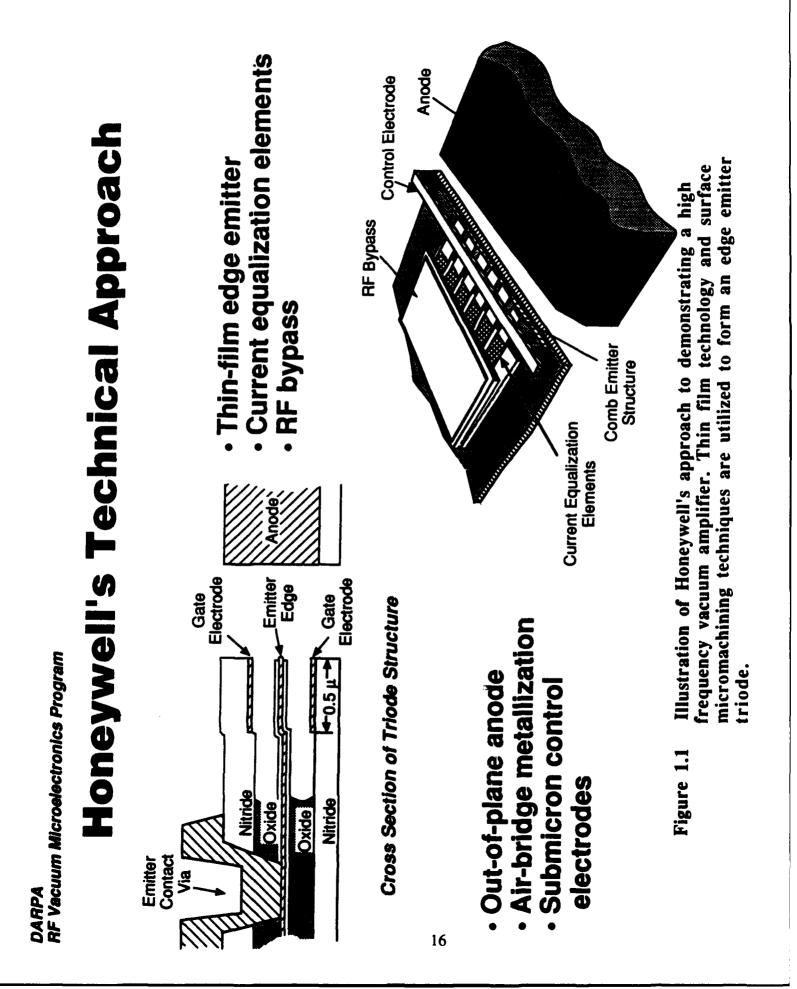

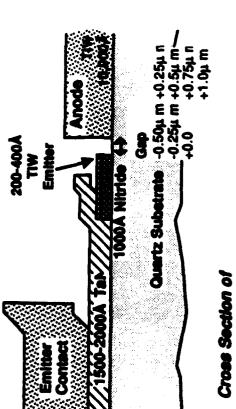

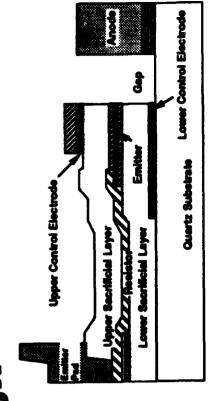

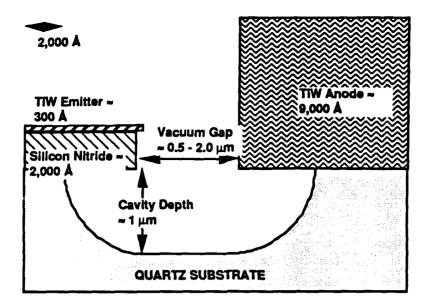

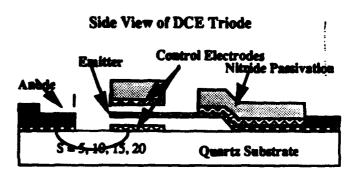

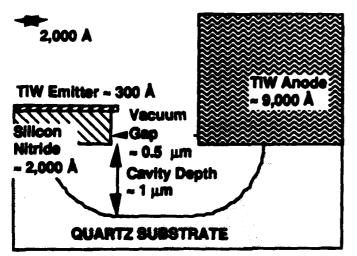

The objective of the RF Vacuum Microelectronics Program is to establish the technology base for the fabrication of practical, high performance gated vacuum emitters and to develop a new class of RF amplifiers based on these vacuum microelectronic emitters. Our technical approach is to utilize thin film technology and surface micromachining techniques to demonstrate an edge emitter based vacuum triode with emission current density of 10  $\mu$ A/ $\mu$ m at less than 250V which can be modulated at 1 GHz continuously for 1 hour. Figure 1 shows a schematic cross section of our thin film edge emitter approach.

The edge emitter triode approach offers several potential advantages to achieving high frequency device operation (compared to cone emitters and wedge emitters):

- The fabrication process is a planar process, compatible with most silicon IC manufacturing.

- Thin film processes for the films used in the triode process are well controlled and reproducible. Control of film thicknesses to within 5% for the emitter film thickness is easily attainable resulting in a well-controlled edge emitter.

- Device capacitance for the edge emitter is less than that achievable for cones or wedges resulting in higher frequency operation.

Based on our experience with fabricating and testing edge emitter devices, our efforts on this program will be focussed on developing a highly stable, uniform and reliable current emission from the edge. We intend to achieve these qualities by

- use of thin film (200Å) edge emitters with small uniform radius of curvature

- use of refractory metal emitter structure to prevent electromigration and burnout

- use of comb emitter structures to prevent premature emitter burnout during edge formation

- use of current equalization series elements to set bias currents.

This program to develop an edge emitter triode started on October 1, 1991. The baseline portion of the program is for 18 months with the above mentioned objectives as goals. Upon successful completion of this phase, an option phase for 12 months can be implemented by DARPA with the objective to achieve 10 GHz modulation with the edge emitter device.

## II. Technical Progress During Quarter

## Key Achievements (7-01-92 to 9-30-92)

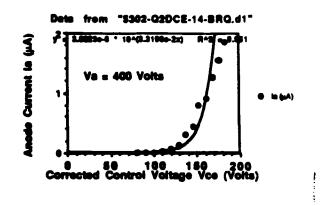

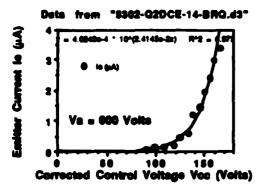

- Demonstrated current densities of up to 10 µA/µm (at ~120 V anode voltage) for a diode field emitter.

- Achieved maximum current emission of 380 µA for a single diode edge emitter.

- Designed a diode array device to demonstrate total device emission current of 5 mA and 5A cm<sup>-2</sup>.

- Completed first fabrication run of diode arrays.

- Completed first fabrication run of edge emitter triodes.

- Continued equivalent circuit analysis of field emitter triode showing that present triode design will achieve >1 GHz modulation with gain. Also carried out finite-element modeling (FEM) electrostatic analysis of triode for mechanical stability under high fields.

- Presented paper on edge emitter diode/triode technology at International Vacuum Microelectronics meeting in Vienna.

## III. Technical Progress

## Task 1.0 Field Emitter Development

The objective of this task is to develop an an edge emitter structure with high emission current and high reliability. The goal is to achieve a current density of 5A cm<sup>-2</sup> operating continuously for one hour at a gate voltage less than 250 Volts.

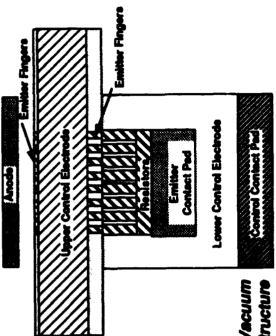

The technical approach is to fabricate field emitter diodes using the comb edge emitter structure shown in Figure 1-2. Each comb element has a series resistor for bias stabilization. Several emitter materials and configurations will be used to determine the structure to be used in the vacuum transistor.

During this quarter we demonstrated field emission from continuous and comb edge emitters. The highest current demonstrated is 380  $\mu$ A from a continuous edge emitter. We have also demonstrated emission current density of 10  $\mu$ A /  $\mu$ m of edge width. The devices also operated for longer period of time ( $\approx$  70 hours) without burn out than previously reported. We have completed six fabrication runs.

There are three sub-tasks - test structure design, Emitter Fabrication and Emission Testing. We have completed the test structure design sub-task and 75 % of the emitter fabrication and emission testing sub-tasks. Below is a discussion of the accomplishments under these sub-tasks.

## Sub-Task 1.1 Test Structure Design

We made design changes to the diode mask set to make arrays of edges that will meet the 5 A  $cm^{-2}$  and 5 mA total current program objective. The new mask set consists of five layers. A discussion of the design of this diode array is presented in Technical Progress, Task 3.

## Sub-Task 1.2 Emitter Fabrication

We have completed the fabrication of two more runs of edge emitter diodes and two runs of diode arrays. A description of the runs and the device or material properties the devices are intended to study is given below.

## Run 5316 O5 - Fifth Diode Run

The primary objective of the run is to study the influence of emitter material on the performance of the devices. The run compares three refractory metals which have work functions of about 4.5 eV. - TiW, WNx, WSix. The secondary objective of the run is to compare TaN and sputtered boron doped polysilicon resistors. The run consists of 12 wafers - 9 quartz substrates and 3 silicon substrates with 1.4 µm of thermally grown oxide. The emitters of the devices are split into three groups (i) 250 Å TiW, (ii) 250 Å WNx and (iii) 250 Å WSix, each consisting of three quartz wafers and one silicon wafer. Each group of wafers are further split into two sub-groups. The first sub-group has 2500 Å of TaN resistors and consists of two quartz wafers and one silicon wafer. The second sub-group

consisting of one quartz wafer has 2500 Å of sputtered boron doped poly silicon. The devices are in testing now.

## Run 5316 - O6 - Sixth Diode Run

The objective of the run is study the effects of different materials on the emission current. The materials are TaN and (Si,Ta)Nx cermet. The run also had TiW/WSix/TiW layered emitters. This run is completed and is in testing.

## Run 5331 - 01 - First Diode Array Run

The primary objective of the run is to fabricate an array of diodes that have comb emitters with and without series resistors. There are several emitter splits. (a) 300 Å TiW, (b) 300 Å WSix, (c) Al/TiW/Al, (d) Al/WSix/Al. Fabrication of the wafers will be completed in early October.

## Run 5331 -02 - Second Diode Array Run

The objective of the run is to study the effect of Cs implants on the emission characteristics of TiW and WSix emitters. We expect that Cs will lower the work function and lead to increased emission currents at low voltages. Fabrication of this diode array run should be completed by mid-to-late October.

## Sub-Task 1.3 Emission Testing

We continued testing, evaluation and analysis of the edge emitter diodes. With the field emitter diode structure we have demonstrated record performances from our edge emitters which include

- Highest current ever reported for a single edge ( $\approx 380 \,\mu$ A)

- Highest current densities ever reported for edge emitters  $(\approx 9.6 \,\mu\text{A} / \mu\text{m})$

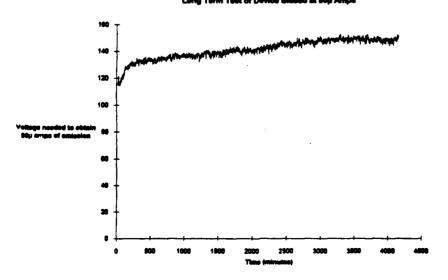

- Long term current emission (50 µA emission from a single edge for greater than 70 hours)

- Current areal densities that have similar performance to field emitter arrays based on Mo cones.

- Comb structure emitters with and without current equalization series resistors

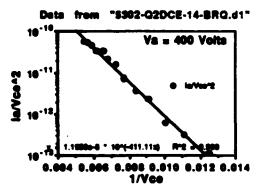

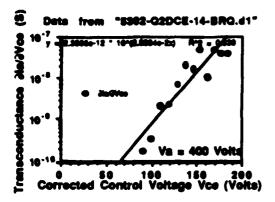

Below is a summary of the best results to date obtained from diodes of different device sizes and different emitter and resistor materials.

## Summary of Best Data to Date

| Device Width | Resistor    | Max Current | <b>Current Density</b> |

|--------------|-------------|-------------|------------------------|

| <u>5 μm</u>  | No Resistor | 48 µA       | 9.6 µА / µт            |

| 10 µm        | No Resistor | 59 µA       | 5.9 µА/µт              |

| 20 µm        | No Resistor | 165 µA      | 8.25 μA / μm           |

| 50 µm        | No Resistor | 288 µA      | 5.75 µA / µm           |

| 100 µm       | No Resistor | 383 µA      | 3.8 µA / µm            |

300 Å TiW Emitters

| Emitter Material | Max Current | Max Current Density |

|------------------|-------------|---------------------|

| TiW              | 380 µA      | 9.6 µA/µm           |

| Pt               | 6 µА        | 0.6 μA/μm           |

| Мо               | 10 µA       | 1 μA/μm             |

| WSix             | 250 µA      | 7.8 μA/μm           |

| WNx              | 118 µA      | 9.1 µA/µm           |

## Summary of Results of Different Emitter Materials

As indicated by the dependence of burn-out current on edge width, we can conclude that the emission current is not coming from the two corners of the edge, but rather the emission current is coming from the length of the edge though it does not scale linearly. We see a decrease in emission current density at burn-out as the edge width decreases. We will investigate this further during the next quarter.

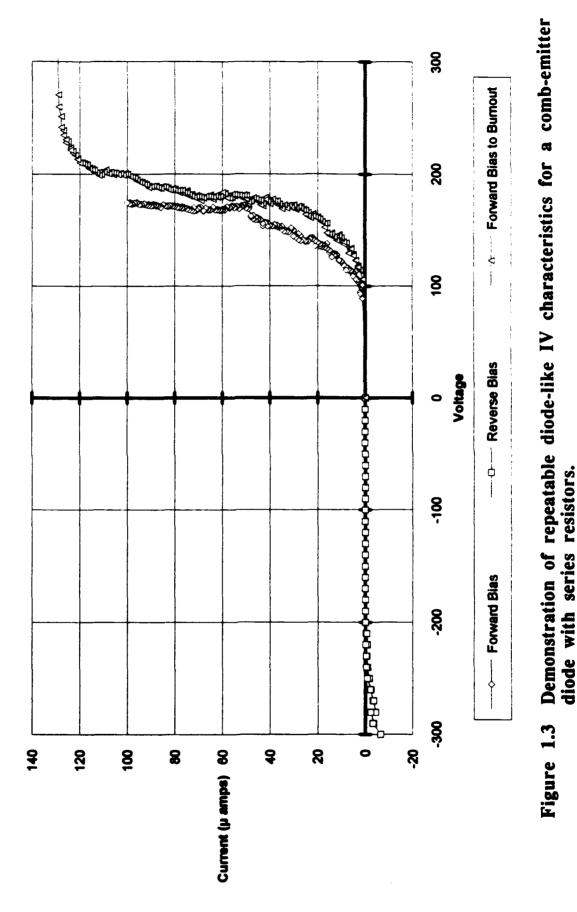

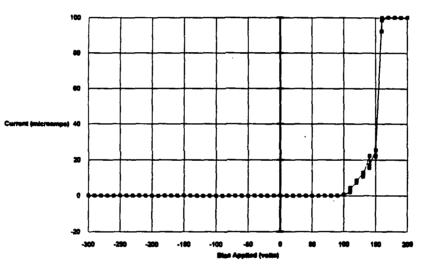

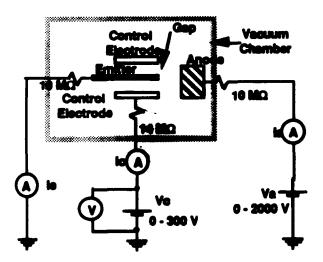

We also demonstrated repeatable diode-like IV characteristics. The device is a two terminal device (vacuum diode) with the anode / emitter separation determined by a PECVD silicon dioxide sacrificial layer. The gap is about 4000 Å. The device has eight fingers. Each finger is 5  $\mu$ m wide and it is separated from the next finger by 5  $\mu$ m space. Each finger has a 10 square resistor in series and the sheet resistance of the resistors is  $\approx 1 M\Omega$ /square.

The device was first tested in the forward direction by sourcing current and measuring the voltage necessary to maintain the emission. The current was increased in steps of 1  $\mu$ A from 0 to 100  $\mu$ A. The device was then reversed biased and tested sourcing voltage and measuring current. In the reverse direction voltage was increased in steps of 10 V from 0 to 300 V. The forward bias characteristics was then repeated by sourcing current and measuring voltage. Current was increased in steps of 1  $\mu$ A from 0 till the device burnt out.

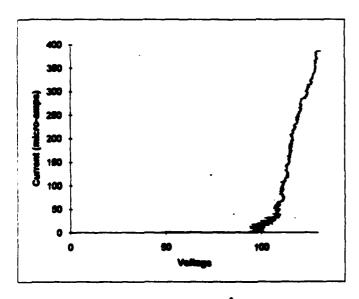

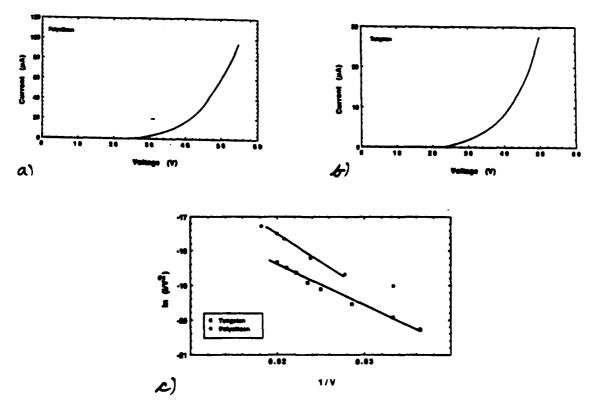

Figure 1.3 is a plot of the device characteristics. We observe from the plot that we do indeed have diode like IV characteristics that are repeatable. The gradual bend in the final forward bias IV may indicate that the resistance of the resistor was changing because of the current flowing leading to burn-out of either the resistor or the emitter. This is speculative at present and needs to be investigated further.

## Task 2.0 Process Development

The focus of this task is to conduct a careful study of materials and processes used to fabricate vacuum microelectronic devices and investigate the best combination of approaches to obtain the desired device characteristics including high transconductance, low capacitance, low leakage currents and high reliability.

## Sub-Task 2.3 Triode Process Development

The post-processing parametric inspection and testing of the first vacuum transistor run indicated that there are several processing steps that affect the yield of the run. These are the definition of the comb emitters and resistors, the trade-off between the emitter layer thickness and radius of curvature, and the trade-off between the sacrificial layer removal rate and the etch rate of the nitride support layer for the emitter. Experiments were conducted to solve the issues and below is a summary of these experiments.

## **Comb Definition Experiment**

A critical step in the process is the definition of the comb emitter. At this point, we are etching both the emitter and the resistor. Since there is an overlap between the emitter and the resistor it implies that there will be some region of the underlying nitride layer that will be exposed for longer times than others. We developed processes to have an etch stop such as  $ZrO_2$  and  $Al_2O_3$ as etch stops. Both materials were characterized in regular laboratory chemicals and etching processes. We are also examining the possibility of using AlN.

## Lavered Emitter Structures

There is a trade-off between the emitter thickness and emitter radius of curvature. For the maximum emission current possible, the radius of curvature must be minimized. A distinct advantage of the thin-film-edge emitter approach is that the maximum radius of curvature is about half the thickness of the deposited thin-film-edge. Thus, for maximum emission current, the emitter should be as thin as possible. This, however, implies that current density in the emitter film will be high and the film will be susceptible to electromigration. An approach to fabricate a thin-film-edge with small radius of curvature that is not susceptible to electromigration is to deposit Al/TiW/Al layered emitter structure. We developed a process for depositing a Al/TiW/Al layered emitter structure. The Al is etched by a wet chemical process after the definition of the edge by ion mill.

## PECVD Oxide Sacrificial Layer

We are making a change in future runs from using BSQ as the sacrificial layer to PECVD oxide because of the faster etch rate of PECVD Oxide (4,000 Å/min for PECVD Oxide vs 500 Å/min for BSQ). The slower etch rate means that the nitride support layers of the emitter and the control electrodes are exposed to BOE for longer etch. We discovered in the first vacuum transistor run that the nitride support layers were completely etched because of the long etch times of the sacrificial layers. We have also developed another approach for obtaining low stress while maintaining etch resistance to BOE. We are using layered nitride structures consisting of two outer layers of etch resistant nitrides and an inner layer of low stress nitride.

## **TASK 3.0 Triode Development**

The objective of this task is to develop a vacuum transistor with an edge emitter structure with high emission current and high reliability. The goal is to achieve a current density of 5A cm<sup>-2</sup> operating at a gate voltage less than 250 Volts operating for one hour.

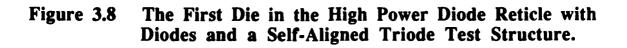

Our technical approach is to fabricate vacuum transistors using the comb edge emitter structure shown in Figure 3.0. Each comb element has a series resistor for bias stabilization. Several emitter materials and configurations will be used to determine the structure to be used in the vacuum transistor.

We completed the design of the vacuum transistor and the first fabrication run during this reporting period. Devices from this run are presently in test. A second triode fabrication run has been initiated. Also, device modeling of the thin film edge emitter vacuum transistor (triode) continued.

## Task 3.1.1 Triode Design Considerations

## Device Theory

The ratio of transconductance  $g_m$  to parasitic input capacitance  $C_{in}$  is the most important factor in microwave device gain at high frequencies. This is generally expressed as the current gain cutoff frequency f above which the magnitude of the power gain is reduced. At this point the current gain falls to unity. This parameter is approximately defined by

$$f_{\tau} = g_m / (2\pi C_{in})$$

However, power gain is still available up to  $f_{max}$  where the power gain also falls to unity. This is

$$f_{max} = f_{\tau} / (2 \sqrt{(r_1 + f_{\tau} \tau_3)})$$

where  $r_1$ , the input-to-output resistance ratio, is

$$r_1 = (R_g + R_i + R_e)/R_{ae}$$

and the time constant  $\tau_3$  is

$$\tau_3 = 2\pi R_g C_{ag}$$

The edge emitter has the advantage that its parasitic capacitances can be reduced to very low levels by decreasing control electrode lengths and increasing the separation between the the control grid and anode. The first can be carried out by employing somewhat more complex lithography and etching procedures while the latter is just a matter of device design. However, at the present time the higher priority and more difficult issue of enhancing the device transconductance through raising the emitter current density while decreasing the bias voltages is being addressed. The expected performance characteristics based on recent results are discussed in the following pages.

If the transconductance is known, a precise calculation of the performance to be expected from a field emission triode design is straightforward since parasitic capacitances are readily determined using finite element techniques and similar modeling tools to solve Laplace's equation. On the other hand, simple approximations can also be employed to determine these parasitics which will give us an almost equally accurate estimate of device performance with the uncertainty in transconductance characteristics. This also has the advantage that the results can easily be verified by anyone using readily available software. Such an approach will be used here to generate an equivalent circuits for some field emission triode designs. The equivalent circuit will then be used to investigate device characteristics.

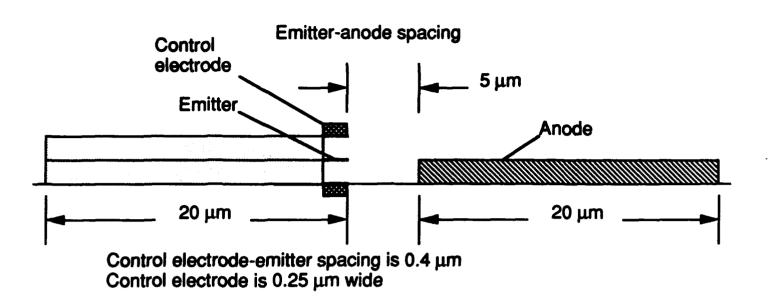

Figure 3-1 describes the cross section of a single cell of an edge emitter triode. Assuming that the capacitance between one of the control electrodes and the emitter is similar to that between a microstrip with similar geometry and ground--if anything it is higher--the impedance of the microstrip line is  $Z_0 = 84$  ohms and its relative effective dielectric constant  $_{eff} = 2.69$ . This implies that the capacitance between the one control electrode and the emitter is

$$C_{ge}/2 = 1/(vZ_0) = e_{ff}/(c_0Z_0) = 2.69/(30 \times 10^9 \times 84) = 0.65 \text{ pF/cm}$$

Assuming an equal amount of capacitance for both control electrodes gives a total capacitance to the emitter of 1.3 pF/cm. The capacitance between the control electrodes and the anode can be estimated using software which calculates the impedance between parallel strips. Using the geometries in Figure 3-1 and applying them to parallel strips we obtain  $Z_0 = 141$  ohms and eff = 6.40. This implies that the capacitance between the control electrode and the anode is quite high for a silicon substrate with coplanar electrodes

$$C_{ga} = eff/(c_0Z_0) = 6.40/(30 \times 10^9 \times 141) = 0.6 \text{ pF/cm}$$

If the silicon has a 5 m thick layer of oxide on it the capacitance is significantly lower

$$C_{ga} = eff/(c_0Z_0) = 2.23/(30 \times 10^9 \times 246) = 0.2 \text{ pF/cm}$$

and further reductions can be achieved by moving the anode to a separate substrate. The latter also has the advantage of improved heat sinking as well as better high frequency performance. The capacitance from the anode to the emitter can be calculated in a similar fashion. For edge emitters this capacitance is somewhat larger than for point emitters but it is not very significant in either case. Using the geometries in Figure 3-2 it is

$$C_{ea} = eff/(c_0Z_0) = 6.40/(30 \times 10^9 \times 78.4) = 1.08 \text{ pF/cm}$$

on silicon and

$$C_{ea} = eff/(c_0 Z_0) = 1.85/(30 \times 10^9 \times 146) = 0.31 \text{ pF/cm}$$

on silicon dioxide.

Metallization resistance depends primarily on the geometry and secondarily on the frequency of operation. Since this resistance is not a dominant factor at the present time and the overall resistance can be reduced by geometry changes, frequency effects will be ignored. The resistances are then based on the geometries in Figure 3-2 with tungsten metallization.

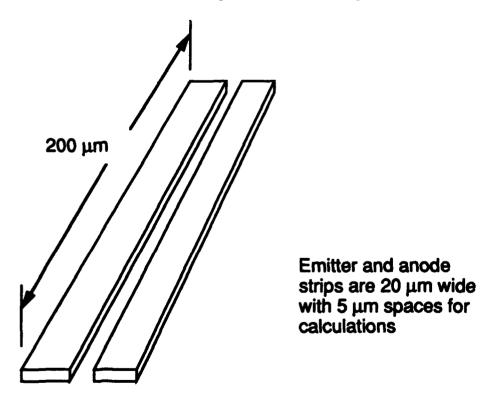

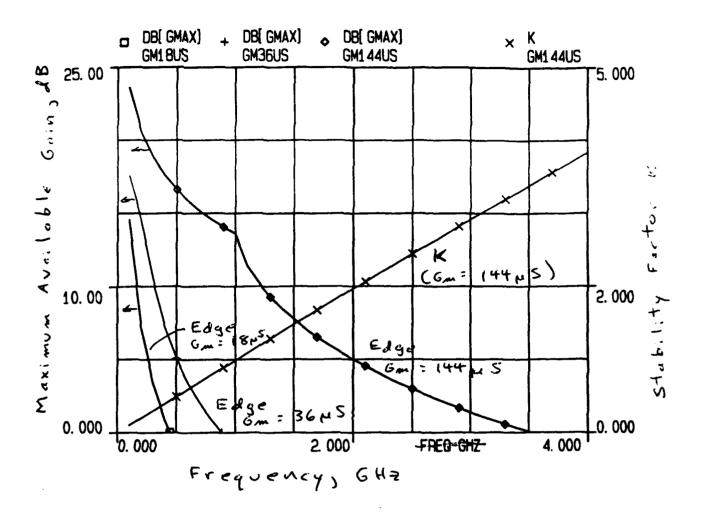

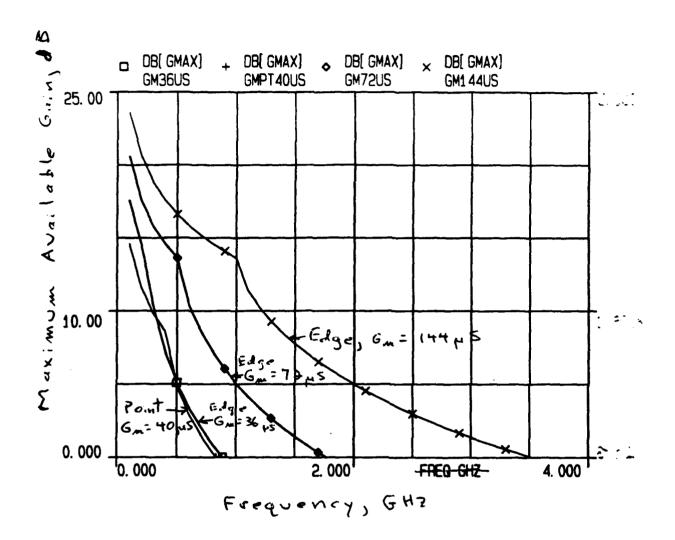

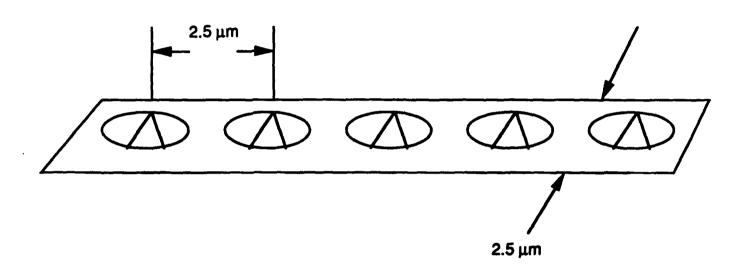

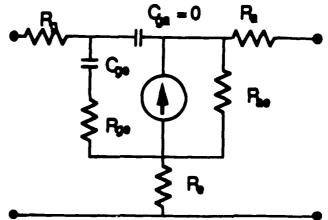

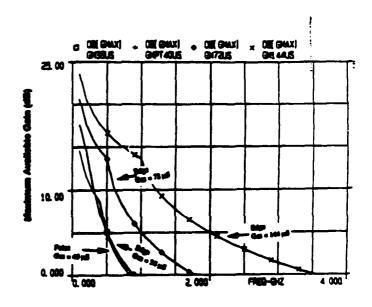

Table 3-1 contains the calculated parameters for the equivalent circuit in Figure 3-3 for the structures listed in Table 3-2. All edge emitter parameters are based on unit cells that are 200  $\mu m$  wide. The control electrode emitter resistance  $R_{ge}$  is derived from an assumed control electrode-emitter capacitive "Q" of 50 at 1 GHz. The anode-emitter resistance used is just a selected parameter which is large enough that it will have negligible effect on the maximum available gain. The transit time is an upper limit on this number which, in practice, has little effect. The other resistances are based on parameters for tungsten films similar to those presently used. The lowest transconductance listed is estimated to be equal to the conductance for diodes at currents of 10 A/m which is probably a lower limit since triodes will have smaller spacings between electrodes. Based on these parameters, the maximum available gain listed by the transconductances for the first three devices in Table 3-1 is plotted in Figure 3-4 for all frequencies where they are stable. At lower frequencies where this is not the case and the stability factor K is less than one, the maximum stable gain is plotted. The stability factor for the 144 µS transconductance device is also indicated in Figure 3-4. When it is equal to one there is a break in the corresponding (GM144US) maximum available gain curve. This power gain assumes that the input and output impedances of the device are matched at each frequency. Better performance is certainly achievable, but these numbers approximately correspond to the present state of the art. Figure 3-5 compares some of the same numbers with those for an aggressively designed 10 A/point array on 2.5 µm cell centers described in Figure 3-6. This spacing from the control electrode to the emitter contact is 1.0 micron in this point array for minimum capacitance with 0.4 µm point to control electrode spacing. From this comparison one might conclude that similar performance can be obtained from point or edge emitter devices. While this is true on paper, the dominant limitation is still the achievable average current density versus the input capacitance and edge emitters are believed to have greater potential for reproducible results.

The transconductance is closely related to the magnitude of the average current per unit area and operating voltage of the device. The capacitance between the anode and control electrodes has been ignored for edge emitters largely due to shielding effects of the emitter but it will slightly reduce the high frequency performance.

| Device   | C <sub>ge</sub><br>(pF) | C <sub>ae</sub><br>(fF) | R <sub>g</sub><br>(Ω) | R <sub>e</sub><br>(Ω) | R <sub>a</sub><br>(Ω) | R <sub>ge</sub><br>(Ω) | R <sub>ae</sub><br>(Ω) | gm0<br>(uS) | (pS)          |

|----------|-------------------------|-------------------------|-----------------------|-----------------------|-----------------------|------------------------|------------------------|-------------|---------------|

| GM18US   | 0.026                   | 23                      | 30                    | 0.56                  | 0.56                  | 122                    | 10,000                 | 18          | $\frac{1}{1}$ |

| GM36US   | 0.026                   | 23                      | 30                    | 0.56                  | 0.56                  | 122                    | 10,000                 | 36          | 1             |

| GM72US   | 0.026                   | 23                      | 30                    | 0.56                  | 0.56                  | 122                    | 10,000                 | 72          | 1             |

| GM144US  | 0.026                   | 23                      | 30                    | 0.56                  | 0.56                  | 122                    | 10,000                 | 144         | 1             |

| GMPT40US | 0.044                   | 0.0                     | 2                     | 0.56                  | 0.56                  | 72                     | 10,000                 | 40          | 1             |

Table 3.1

Equivalent Circuit Parameters Used in Vacuum Microelectronic Simulations

| Device  | Anode<br>Length<br>(µm) | Emitter<br>Length<br>(µm) | Gate<br>Length<br>(µm) | Anode<br>Height<br>(µm) | Substrate<br>Material | Horizontal<br>Gate-<br>Anode<br>Space<br>(µm) |

|---------|-------------------------|---------------------------|------------------------|-------------------------|-----------------------|-----------------------------------------------|

| GM18US  | 20                      | 20                        | 0.25                   | 0                       | Si                    | 5                                             |

| GM36US  | 20                      | 20                        | 0.25                   | 0                       | Si                    | 5                                             |

| GM72US  | 20                      | 20                        | 0.25                   | 0                       | Si                    | 5                                             |

| GM144US | 20                      | 20                        | 0.25                   | 0                       | Si                    | 5                                             |

Table 3.2

Device Geometries Used to Calculate Equivalent Circuit Parameters

## 3.1.2 Diode Array Designs

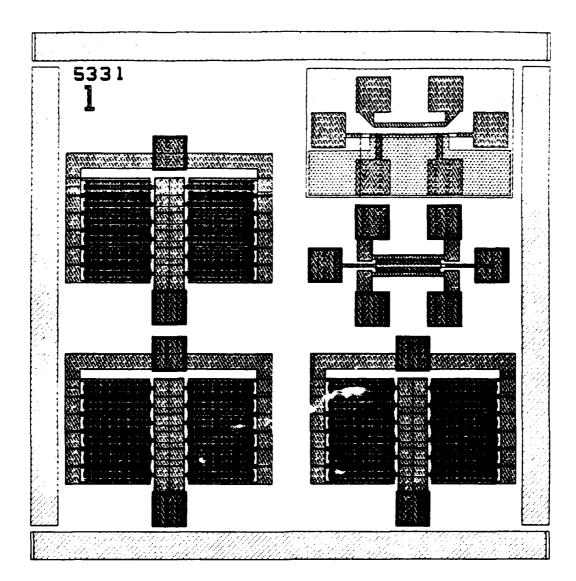

Since the most important limitation on microwave field emitter triode performance which is not completely understood is the achievable transconductance or emitter current density, an array of high current <u>diodes</u> is probably one of the more effective tools for its development. These devices can be used to demonstrate high average and elevated total currents for improved emitter characteristics. A mask containing a number of diode arrays designed to deliver total currents per diode of greater than 5 mA and average current densities greater than 5 A/cm<sup>2</sup> is described in Figure 3-7 and Table 3-3. Figure 3-8 has an expanded view of the first die for greater clarity. The diode arrays contain multiple fingers approximately 200 microns long with varying numbers of emitters, with or without resistors connected in series with them. Interdigitated anode fingers in the same plane result in complete diodes without any external anode required. All of these devices employ tungsten metal for pads and with refractory metal emitters for high temperature and high current operation.

## 3.1.3 FEM Analysis of Triode Mechanical Stability

## **Objective:**

The objective of this study is to determine the VME structure's mechanical response to both electrostatic and intrinsic stress loading. There are three main goals: an analysis of the deflections caused by electrostatic loading, an analysis of the deflections resulting from the residual stress of deposition found in the thin films (intrinsic stress), and an evaluation of the fault tolerance of these parameters to manufacturing variations in geometry and in film deposition stress.

## **Conclusion Summary:**

The triode structure appears to be very robust in its construction. In all three study areas, the device remained little affected: electrostatic loading produced a nominal deflection of the upper control electrode of <u>less than 10 Å</u>, intrinsic stress caused a maximum deflection of only -84 Å, and process variations of significant proportions were able only to increase the maximum deflection to -141 Å.

| Die | Description                                                                                                                    | Purpose                                                   |

|-----|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 1   | $5 \mu m$ finger and $5 \mu m$ space diodes<br>with series resistors. A heated<br>electrode diode and a self-aligned<br>triode | Maximize total current and current density                |

| 2   | 5 μm finger and 10 μm space, 20 m<br>finger and 5 m space diodes with<br>series resistors.<br>Dielectric test structures       | As above                                                  |

| 3   | with series resistors and point<br>emitter test arrays                                                                         | As above with test structures for<br>emission diagnostics |

| T1  | Material measurement structures                                                                                                | Process characterization                                  |

| 7   | Uniform edge diodes and level one serpentine                                                                                   | Comparison with previous designs<br>and heating tests     |

| T2  | Alignment marks, leakage test patterns                                                                                         | Alignment for lithography, process monitoring             |

| 4   | 5 $\mu$ m finger and 5 $\mu$ m space diodes<br>without series resistors and heated<br>electrode diode                          | High total current and high cur-rent density              |

| 5   | finger and 5 m space diodes <u>without</u><br>series resistors<br>Etching test structures                                      |                                                           |

| 6   | 10 µm finger and 5 µm space<br>diodes <u>without</u> series resistors and<br>point emitter test arrays                         | High total current and high current density               |

Table 3-3Summary Description of Individual Die

## Model:

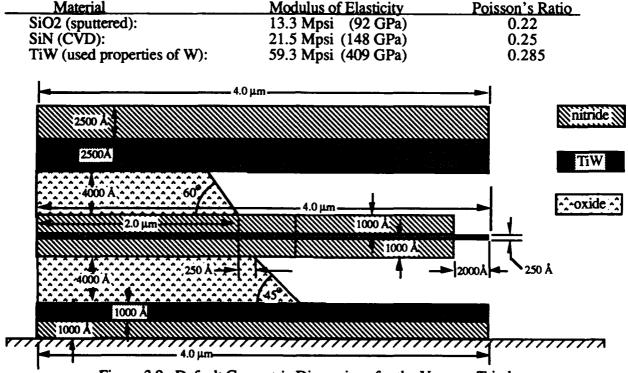

These results were achieved through finite element modeling of the structure in two dimensions using the Ansys FEM program from Swanson analysis systems. The structure is shown in figure 3.9. The electrostatic loading was calculated in the following way:

The force of attraction between two parallel capacitor plates is as follows:

$$F = \partial E/\partial x$$

,  $E = 1/2C^*V^2$ ,  $C = k'e_{o}A/d$ ,  $==>F = 1/2k'e_{o}AV^2/d^2$

Pressure = F/A,  $==>P = 1/2k'e_{o}V^2/d^2$

k' is the effective dielectric constant. Since the gap between the emitter and control electrodes contains both vacuum ( $e = e_o$ ) and nitride ( $e = k_m e_o$ ), the resulting dielectric constant is a combination of the two. Using the equations for two capacitors in series, the effective dielectric constant has been determined as follows (the vacuum gap is the same dimension as the oxide thickness):

$$k' = ((t_{ux}+t_{ui})*k_{ui})/(t_{ui}+t_{ux}*k_{ui}) =$$

= ((0.1µm +0.4µm)\*7.5)/(0.1µm+0.4µm\*7.5)

= 1.2097

Using the geometrical values from figure 1, the magnatude of the electrostatic "pressure" is:

$$P = 0.5*1.2097*(8.854e-12 C^2N/m^2)*(100 V)^2/(0.5 \mu m)^2 = 2.1421 e-7 N/um^2$$

Intrinsic stress effects have been included also. This is accomplished by adjusting each material's TCE such that over a given temperature rise the resulting stress is equal to input target values. The target values are intrinsic stress levels for a particular film as determined from sample measurement in the lab. This method has been verified by fixing the boundaries of all films, turning off the electrostatic loading, and running the solution; when this is done, each film has a resulting stress identically equal to the input value of intrinsic stress.

The following material properties were used:

| <b>Results</b> :                                                                   |                                                        |                               |                           |  |  |  |  |

|------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------|---------------------------|--|--|--|--|

| Model                                                                              | Geometry/Loading Description                           | Emitter tip<br>deflection (Å) | UCE tip<br>deflection (Å) |  |  |  |  |

| Baseline                                                                           |                                                        |                               |                           |  |  |  |  |

| 1 I.S., but no electrostatic load; default geometry (except upper and lower oxides |                                                        |                               |                           |  |  |  |  |

| -                                                                                  | meet nitride emitter sheath at the same vertical posi  |                               | -83.5 Å                   |  |  |  |  |

| 2                                                                                  | I.S., but no electrostatic load; nitride sheath upper  |                               |                           |  |  |  |  |

|                                                                                    | lower 1000Å:                                           | 20.6 Å                        | -83.8 Å                   |  |  |  |  |

| LICE mos                                                                           | vement (vary the amount of UCE extension):             |                               |                           |  |  |  |  |

| 3                                                                                  | I.S. and electrostatics; $\Delta UCE = 0 \mu m$ :      | 6.5                           | -89.0                     |  |  |  |  |

| 4                                                                                  | I.S. and electrostatics; $\Delta UCE = -0.2 \ \mu m$ : | -3.4                          | -72.1                     |  |  |  |  |

|                                                                                    | I.S. and electrostatics; $\Delta UCE = -0.2 \ \mu m$ : | -11.5                         | -56.7                     |  |  |  |  |

| 5<br>6                                                                             | I.S. and electrostatics; $\Delta UCE = -0.6 \mu m$ :   | -18.0                         | -43.0                     |  |  |  |  |

| 7                                                                                  | I.S. and electrostatics; $\Delta UCE = -0.8 \ \mu m$ : | -22.2                         | -30.8                     |  |  |  |  |

| 8                                                                                  | I.S. and electrostatics; $\Delta UCE = -1.0 \ \mu m$ : | -26.3                         | -20.1                     |  |  |  |  |

|                                                                                    |                                                        |                               |                           |  |  |  |  |

| Increased                                                                          | Voltage (including I.S. and electrostatic loads):      |                               |                           |  |  |  |  |

| 9                                                                                  | UCE and LCE = $200$ Volts:                             | 6.2                           | -105.8                    |  |  |  |  |

| 10                                                                                 | UCE and LCE = 300 Volts:                               | 1.2                           | -133.8                    |  |  |  |  |

| 11                                                                                 | UCE/LCE = 200 V; UCE 0.2 $\mu$ m shorter than LC       | E: -33.2                      | -84.4                     |  |  |  |  |

| Modify C                                                                           | xide Length (vary UCE, emitter, and LCE lengths):      |                               |                           |  |  |  |  |

| 12                                                                                 | $\Delta Oxide length = +0.500 \ \mu m$ :               | 7.3                           | -48.5                     |  |  |  |  |

| 13                                                                                 | $\Delta Oxide length = +0.333 \ \mu m$ :               | 7.1                           | -60.8                     |  |  |  |  |

| 14                                                                                 | $\Delta Oxide length = +0.167 \ \mu m$ :               | 6.8                           | -74.3                     |  |  |  |  |

| 15                                                                                 | $\Delta Oxide length = -0.167 \ \mu m$ :               | 6.3                           | -105.2                    |  |  |  |  |

| 16                                                                                 | $\Delta Oxide length = -0.333 \mu m$ :                 | 6.1                           | -122.5                    |  |  |  |  |

| 17                                                                                 | $\Delta Oxide length = -0.500 \ \mu m$ :               | 5.9                           | -141.0                    |  |  |  |  |

|                                                                                    | mitter Clamp Point (vary the difference between whe    | ere the                       |                           |  |  |  |  |

|                                                                                    | lower oxides attach to the nitride emitter sheath):    |                               |                           |  |  |  |  |

| 18                                                                                 | I.S. and Electrostatics, $\Delta$ clamp pt. = 0.025 Å: | 6.4                           | -89.1                     |  |  |  |  |

| 19                                                                                 | I.S. and Electrostatics, $\Delta$ clamp pt. = 0.050 Å: | 6.4                           | -89.1                     |  |  |  |  |

| 20                                                                                 | I.S. and Electrostatics, $\Delta$ clamp pt. = 0.100 Å: | 6.4                           | -89.1                     |  |  |  |  |

| 21                                                                                 | I.S. and Electrostatics, $\Delta$ clamp pt. = 0.150 Å: | 6.4                           | -89.0                     |  |  |  |  |

| 22                                                                                 | I.S. and Electrostatics, $\Delta$ clamp pt. = 0.200 Å: | 6.5                           | -89.0                     |  |  |  |  |

| Modify U                                                                           | pper Oxide Layer Thickness:                            |                               |                           |  |  |  |  |

| 23                                                                                 | I.S. and Electrostatics; Upper oxide $t = 3750$ Å:     | 12.0                          | -88.9                     |  |  |  |  |

| 24                                                                                 | I.S. and Electrostatics; Upper oxide t = 3500 Å:       | 18.5                          | -88.8                     |  |  |  |  |

| 25                                                                                 | I.S. and Electrostatics; Upper oxide $t = 3250$ Å:     | 26.2                          | -88.8                     |  |  |  |  |

| 26                                                                                 | I.S. and Electrostatics; Upper oxide $t = 3000$ Å:     | 35.5                          | -88.6                     |  |  |  |  |

| 27                                                                                 | I.S. and Electrostatics; Upper oxide t = 2750 Å:       | 46.8                          | -88.3                     |  |  |  |  |

|                                                                                    |                                                        |                               |                           |  |  |  |  |

## **Conclusions:**

The current triode design is extremely stable under the influence of both electrostatic loads and intrinsic stresses. In the nominal configuration (see figure 3.9), the upper control electrode (UCE) exhibits deflection of only -89.0 Å while the emitter deflects only +6.5 Å (see figure 2)--the emitter deflection is practically zero because the electrostatic pull from the UCE and LCE balance out and cancel. Intrinsic stresses account for most of the deflection--of the -89.0 Å in load case 3, -83.5 Å are due to intrinsic stress, while the remaining fraction are due to electrostatic loads. The deflection of the emitter and upper control electrode are roughly linear with load (for small deflections--at large deflections, stiffness increases) whereas electrostatic loading is proportional to the inverse square of gap size. If the deflection is great enough, the electrostatic load will supercede the magnitude of the emitter/UCE bending restoring force, instability will occur, and the emitter and UCE will short together. Results indicate however, that the magnitude of the electrostatic forces are much smaller than the bending restoring force, and therefore the above scenario is not a concern. [Compare load cases 1 and 3]

- In the baseline configuration, the emitter deflection is negligible due to a balancing of electrostatic forces from the upper and lower control electrodes. Thus, shortening the UCE tends to unbalance the emitter and cause deflection. However, even when the UCE has been shortened 50%, the deflection at the emitter tip is still only -26.3 Å. Thus, from a mechanical point of view at least, a shorter UCE has little detrimental effect on device life. [Compare load cases 3 through 8]

- Shortening or lengthening the control electrodes and emitter structures by +/- 0.5 μm (due to a longer oxide etch for example) has a small overall effect. In the worst case, that of a 0.5 μm extension (a 25% increase in length), the UCE deflection increases from -89.0 Å at nominal to -141.0 Å when the UCE has been increased--this is a minor change in light of an overall gap size of 4000 Å. [Compare load cases 3 with 12-17]

- The lateral spacing between where the upper and lower oxides attach to the emitter structure was also varied. This geometrical study was done to examine the effects on performance due to varying oxide etch rates--if the etchant was slower on the bottomside, a small difference in clamp points could result (the default geometry in figure 1 shows an offset of 250 Å). The lateral distance was varied from 0 through 2000 Å. The result was that there was nearly zero sensitivity for both the emitter and UCE deflections in response to this change. Although this parameter is difficult to control anyway, these results show that it may be left uncontrolled with impunity. [Compare load cases 3 with 18-22]

- The TiW layer of the emitter is encased in a nitride sheath, a layer of 1000 Å of nitride above and below it. The upper layer was decreased to 800 Å to examine the sensitivity of the emitter to such process variations. Under this modification, the emitter deflection changes an insignificant amount from +6.6 Å to +20.6 Å. Thus, nitride thicknesses for the emitter sheath do not need to be controlled with exceptional accuracy--what is more important is that low stress nitride films (or those films which are balanced) are used for the emitter sheath. [Compare load case 1 and 2]

- The upper and lower oxide layers are nominally both controlled at 4000 Å in thickness. If these thicknesses differ, then the upper and lower gaps are different and the electrostatic attractive forces on the emitter will be unbalanced. To evaluate this effect, the upper oxide thickness was varied from the nominal 4000 Å down to 2750 Å. The thinner the oxide, the greater the electrostatic loading--at its thinnest, 2750 Å, the electrostatic load is about double the baseline configuration. At an oxide thickness of 2750 Å, the emitter deflection increased from +6.6 Å to +46.8 Å. This is a small response given such a large change in oxide thickness and it suggests that the emitter design as it stands is very robust in light of these types of process variations. Note also that the deflection seen is due to intrinsic stress and not electrostatic loading which shows again that the triode structure is fairly well mechanically designed to weather the overall loads that can be expected to be placed upon it. [Compare load cases 3 with 23-27]

## Sub-Task 3.2 Triode Fabrication

## 5313 - O1 First Vacuum Transistor Run

We completed the first run of the vacuum transistor. The run had four emitter splits. (a) 200 Å TiW, (b) 400 Å TiW, (c) 200 Å WSix and (d) 400 Å WSix. There were several fabrication issues that we encountered along the way and all of them have been addressed in the process development tasks. Some were solved by making changes in the mask set. We have two wafers with potentially working devices. They have been loaded into the vacuum system and will be tested in early October. Below is a summary of the changes made in the fabrication process :

- The emitter layer support nitride thickness was increased or an etch stop was used between the emitter and the lower nitride layer

- The sacrificial layer was changed to PECVD Oxide for faster emitter layer release. and the thickness was reduced in samples where the emitter nitride layer thickness was increased

- The nitride layer is now layered with two outer nitride layers which are resistant to buffered HF and inner layer of low stress nitride.

- The comb definition step and the emitter cap definition steps have been revised to have proper inspections to prevent incomplete etching at critical steps necessary for the self alignment of the emitter to the control electrodes.

A second triode device fabrication run been initiated with the above changes and should be ready for test in early November.

## IV. Plans for Next Quarter

- Test triodes from first triode fabrication run.

- Complete 2nd fabrication of edge triodes.

- Evaluate diode arrays from first diode array fabrication run.

- Complete 2nd diode array fabrication run and test diode arrays for current levels.

- Complete high frequency test set-up for vacuum triodes.

- Demonstrate 1 GHz modulation of a vacuum edge emitter triode.

## V. Attachments

- Abstract entitled "Nanometer Thin-Film-Edge Emitter Devices" by A.I. Akinwande, P. Bauhahn, H. Gray presented at the International Vacuum Microelectronics Conference in Vienna in July, 1992.

- Abstract entitled "Nanometer Scale Thin-Film-Edge Emitter devices with High Current Density Characteristics" by A.I. Akinwande, P.E. Bauhahn, H.F. Gray, T.R. Ohnstein and J.O. Holmen. Accepted for presentation at the International Electron Devices Meeting (IEDM) San Francisco, 12/92.

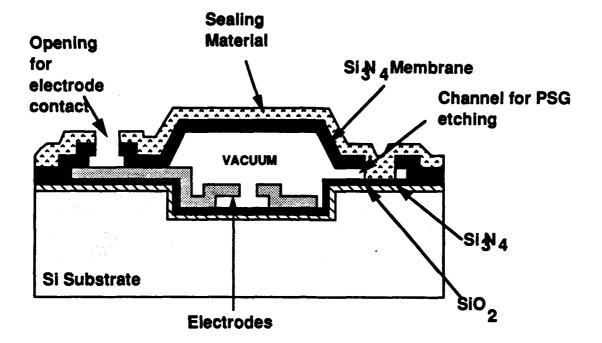

- University of Minnesota Subcontractors Report on Vacuum Sealed Microdiodes.

Microelectronics

# **Field Emitter Test Structure**

Comb structure

17

- Thin-film emitter

- Thin-film resistor

- Emitter Emitter Emitter Contact Ped Ped Ped Contact Ped Contact Ped Contact Contact Ped Contact Contac

- Anode

- # of Emitter Fingers 1, 5, 10, 20

- **Gaps** -0.5, -0.25, 0, 0.25, 0.5, 0.75. 1.

Top View of Field Emitter Test Structure

- Emitter with and without combs

- Emitters with and without resistors

- Novel structures to determine electron trajectory

- Novel structures to determine positive ions or secondary electrons

Figure 1.2 Field Emitter Diode Configuration.

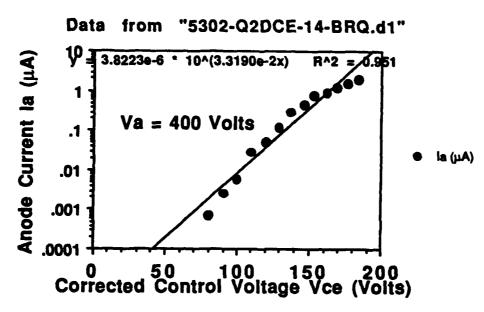

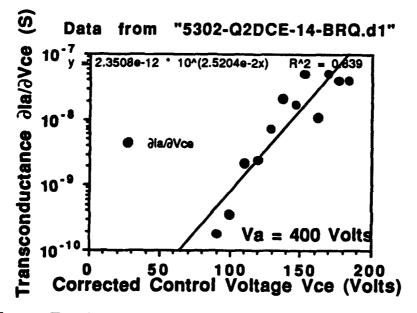

## Q1 5316 Wafer 2 Device 1-1-1

**Microelectronics**

## Vacuum Transistor Structure and Design

- Comb emitter

- Thin-film resistor

- Refractory metal emitter

- Heat—sink emitter

Layout of Vacuum Transistor Structure Figure 3.0 Vacuum Transistor with Comb Emitters and Series Resistors.

Figure 3-1 Cross Section of a Single Cell of an Edge Emitter Triode

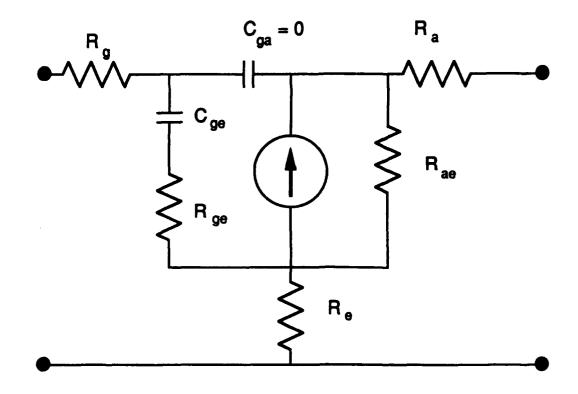

Figure 3-3 Equivalent Circuit Used for Device Performance Calculations

Figure 3-4 Maximum Available Gain versus Frequency and Stability Factor for Three Field Emission Triode Transconductances.

Figure 3-5 Comparison between Edge and Point Field Emitter Triodes for the Current State-of-the Art with the Same Current for a One Micron Edge and a single Point.

Figure 3-6 Agressive Point Emitter Structure Used in Simulations

Figure 3.7 High Power Diode Array Reticle Showing the Test Patterns and High Power Diode Structures.

## Nanometer Thin-Film-Edge Emitter Devices with High Current Density Characteristics

A. I. Akinwande<sup>\*</sup>, P. E. Bauhahn<sup>\*</sup> and H. F. Gray<sup>+</sup> <sup>\*</sup> Honeywell Sensor and System Development Center, 10701 Lyndale Avenue South, Bloomington, MN 55420, U. S. A. Ph : 1- (612) 887-4481; Fax: 1- (612) 887-4517 <sup>+</sup> Naval Research Laboratory, Washington, DC 20375, U. S. A..

## Abstract

Conventional distributed interaction thermionic emission cathode tubes have demonstrated power outputs exceeding 1 megawatt for a wide range of microwave frequencies while solid state field effect transistors continue to break previous records for low noise performance up to 100 GHz. For many applications, these devices are quite appropriate. However, the tube cost, weight and power supply complexity as well as power outputs exceed many budget requirements. Solid state devices, operating at low voltages, may have insufficient power outputs. The field emission triode may offer advantages as a compromise device with more power output than the solid state approach with simpler power supplies and lighter weight than other vacuum tubes.

We report the demonstration of thin-film-edge emitter devices with reproducible high current density characteristics. The demonstrated devices include both diodes and triodes with thin film emitters, anodes and control electrodes on the same wafer. Contrasted with the usual vertical FEA structures, this particular triode design invokes two dimensional vertical symmetry for the extraction electrodes using multi-layer thin-film deposition and patterning techniques. A central nanometer thick edge-emitter film is sandwiched between two extraction electrodes (one above and one below). This design and fabrication methodology has several major advantages compared to the classical vertical FEA design: (1) The radius of curvature of the electron emitter must be less or equal to the thickness of the thin film emitter metallization. The thickness of the thin film can be controlled to nanometer dimensions by a number of known deposition processes. (2) The distance between the control electrodes and the emitter is determined by the thickness of deposited insulator thin films. These thicknesses can also be controlled to nanometer tolerances by deposition processes. (3) The total electron path can be potentially much shorter than vertical designs. This distance, which determines the total transit time, might be important for high frequency operation. (4) No critical dimension is dependent on high resolution lithography. Finite element based simulation of field emitter structures has been used to estimate the electric fields, currents and temperatures of typical devices to enhance our understanding of their operation and suggest techniques to improve their performance.