# FINAL TECHNICAL REPORT

# RAPID PROTOTYPING OF APPLICATION SPECIFIC SIGNAL PROCESSORS PROGRAM

Prepared For:

# DARPA/ESTO ATTN: Mr. Eliot D. Cohen 3701 North Fairfax Drive Arlington, VA 22203-1714

The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the Defense Advanced Research Projects Agency of the U.S. Government.

Distribution Statement A. Approved for public release; distribution is unlimited.

# Prepared By:

Texas Instruments Integrated Circuity and Computers Department 6550 Chase Oaks Blvd., M/S 8435 Plano, Texas 75023

'noci 1097

TEXAS INSTRUMENTS

#### TABLE OF CONTENTS

| Sec | tion <u>Title</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1.  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1      |

|     | 1.1         Study Approach         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | 1<br>1 |

|     | 1.2 Work Summary     1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2      |

|     | 1.4 RASSP Design Approaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2      |

|     | 1.5     RASSP Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3      |

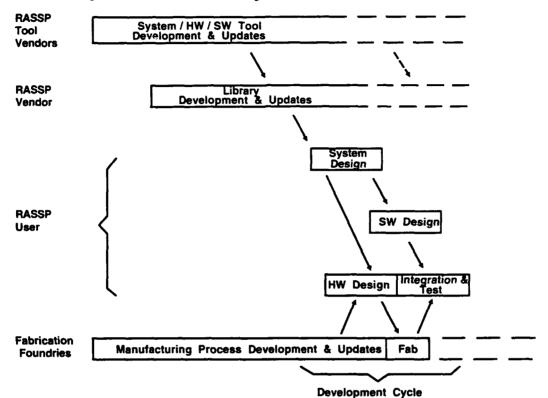

|     | 1.6 RASSP Development Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5      |

|     | 1.7 RASSP Program Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5      |

|     | 1.8 Key Ingredients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6      |

|     | 1.9 Overview of Detailed Technical Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7      |

|     | is overview of becariod reconsider biscublich                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ,      |

| 2.  | DESIGN LIBRARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8      |

|     | 2.1 Target Platform Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8      |

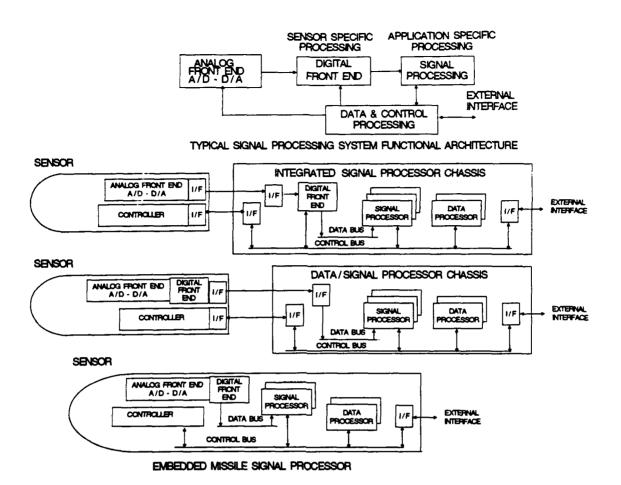

|     | 2.2 Signal Processor System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9      |

|     | 2.2.1 Functional Architecture Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9      |

|     | 2.2.2 Architecture Implementation/Upgrades                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11     |

|     | 2.2.3 Library Based Architecture Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12     |

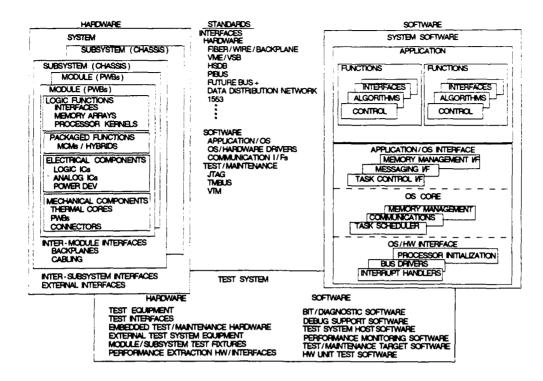

|     | 2.3 Library Element Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13     |

|     | 2.3.1 Standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14     |

|     | 2.3.2 Test System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15     |

|     | 2.3.3 Software Library Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16     |

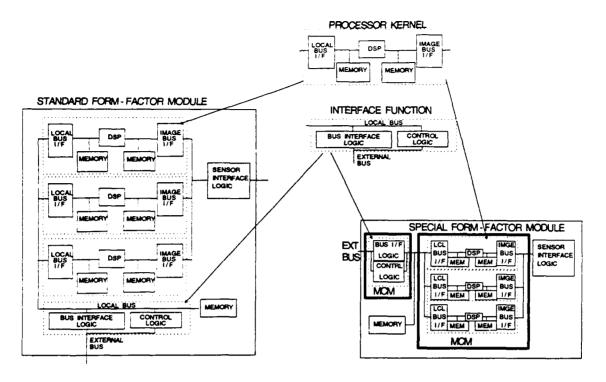

|     | 2.3.4 Hardware Library Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16     |

|     | 2.3.5 RASSP Library Views                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18     |

|     | 2.4 Design Library Based Model Year Upgrades                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20     |

|     | 2.4.1 Functional Element Design Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20     |

|     | 2.4.2 Standard MCM Library Element Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22     |

|     | 2.5 Summary of Issues and Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23     |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23     |

| 3   | DATA BASE AND DATA INTERCHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26     |

| 2.  | 3.1 RASSP System Architecture Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26     |

|     | 3.2 Summary of Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27     |

|     | 3.2.1 Enterprise Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29     |

|     | 3.2.2 Information Management Standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30     |

|     | 3.2.3 Generic Frameworks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31     |

|     | 3.2.4 Domain-Specific Frameworks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32     |

|     | 3.2.5 Data Base Management Standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34     |

|     | 3.2.6 Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38     |

|     | 3.2.7 Generic Interchange Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39     |

|     | 3.3 Issues/Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41     |

|     | 3.3.1 Issue: Object Model Harmonization Needed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41     |

|     | 3.3.2 Issue: Frameworks Harmonization Needed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41     |

|     | 3.3.3 Issue: The need for OODB Interface Standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 43     |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44     |

|     | 3.3.4 Issue: Who Will Win: OODBs or RDBs (Relational DBMSs) .<br>3.3.5 Issue: The Need for Federated, Decentralized, Scalable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44     |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

|     | Intra- and Inter-enterprise-wide Repositories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44     |

|     | (Data Base Systems)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

|     | 3.3.6 Issue: Improvements to PDES/Express are Needed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44     |

|     | 3.3.7 Issue: Which Interchange Formats and Representations to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|     | Standardize?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44     |

|     | 3.3.8 Issue: What to put in the RASSP Library?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45     |

|     | 3.3.9 Issue: How to Bootstrap the RASSP Business?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45     |

|     | 3.4 Summary of Key Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45     |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

| 4.  | APPLICATION DESIGN SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48     |

|     | 4.1 DSSA Software/DSHA Hardware Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49     |

|     | 4.2 ASSP Application Design System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52     |

|     | 4.3 Design Integration and Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53     |

|     | 4.4 Extended DSSA Support Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54     |

# TABLE OF CONTENTS (CONTINUED)

| Sec  | tion       | Title                                                       | Page       |

|------|------------|-------------------------------------------------------------|------------|

|      |            | Extended DSHA Support Environment                           |            |

| 5.   |            |                                                             |            |

|      | 5.2        | Overview                                                    | 62         |

|      | 5.3<br>5.4 |                                                             |            |

| 6. ( | COMP       | UTER AIDED DESIGN                                           | 71<br>71   |

|      |            | CAD Process Flow Overview                                   |            |

|      | 6          | .2.1 System/Concept Level                                   | 77         |

|      | ő          | .2.2 Functional Design Level                                | 77         |

|      |            | .2.3 Detailed Design Level                                  |            |

|      | 6          | .2 4 Design Verification Level                              | 81         |

|      | 6          | .2.5 Manufacturing "Pre Fab" Interface Level                | 81         |

|      | 6.3        | Design Information Modeling                                 | 82         |

|      | 6 4        | RASSP Libraries                                             | 84         |

|      |            | Tool Data Base Federation                                   |            |

|      | 6 6        | Design Model Standards                                      | 86         |

|      | 6 7        | RASSP CAD Recommendations and Summary                       | 89         |

|      | 0.7        |                                                             | 05         |

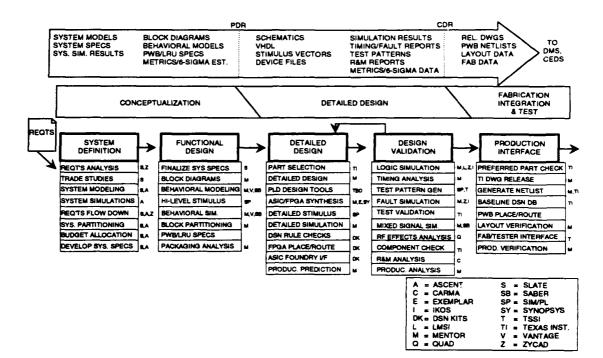

| 7 1  | ΜλΝΠΙ      | FACTURING                                                   | 92         |

|      |            | FACTURING                                                   | 92         |

|      |            |                                                             |            |

|      | 1.2        | Manufacturing Overview                                      | 107        |

|      |            | .2.1 Quality/Reliability Plan                               | 111        |

|      |            | .2.2 Production Test Needs                                  | 111        |

|      | 7          | .2.3 Test Solutions                                         | 111        |

|      |            | .2.4 Hardware Foundries - Test Interface                    |            |

|      |            | .2.5 Test Technology Roadmap                                |            |

|      |            | .2.6 Manufacturing Control                                  |            |

|      | 7          | .2.7 The Future of Computer Integrated Manufacturing        | 115        |

|      | 7          | .2.8 Next Generation Manufacturing System Contacts          | 116        |

|      | 7          | .2.9 Next Generation Manufacturing Issues                   | 116        |

| 8.1  | BUSI       | NESS PLAN AND PROGRAMATICS                                  | 119<br>119 |

|      |            | Program Plan                                                |            |

|      | . –        |                                                             | -          |

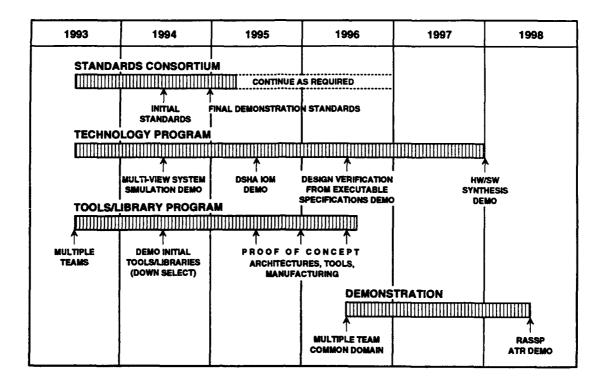

|      |            | .2.1 Standards Consortium                                   |            |

|      | 8          | .2.2 Technology Program                                     | 121        |

|      |            | .2.3 Tools and Library Program                              |            |

|      |            | .2.4 Demonstration                                          |            |

|      | 8.3        | Applications                                                | 122        |

|      | 8          | .3.1 Applications Criteria                                  | 122        |

|      | 8          | .3.2 Application Evaluation                                 | 124        |

| 9    | SUMM       | ARY                                                         | 136        |

|      |            |                                                             | 136        |

|      | 9.1        | Application Domain Selection Effort: "Iskisk: Dow           | 720        |

|      | 9.2        | Data Representation Standards Selection Effort:             | 170        |

|      |            | ~5%Risk: Moderate                                           | 136        |

|      | 9.3        | In-cycle Library Framework and CAx Tool Selection           |            |

|      | _          | Development Effort: 30%Risk: High                           | 136        |

|      | 9.4        |                                                             | _          |

|      |            | ~1%Risk: Low                                                | 137        |

|      | 9.5        | Selection and Integration of the CAD/Case Libraries and Too | ls<br>137  |

|      |            | for Module Development Effort: 15%Risk: Low to Moderate     | 121        |

# TABLE OF CONTENTS (CONTINUED)

| Section  |      | <u>Title</u>                                                                                                     | Page |

|----------|------|------------------------------------------------------------------------------------------------------------------|------|

| 9.6      |      | lect, Design, and Validate the Hardware/Software Modules to<br>Support the Domain Specific Demonstration Effort: | 0    |

|          |      | 15%Risk: Low to Moderate                                                                                         | 137  |

| 9.7      |      | Aate and Demonstrate Seamless Interfaces to<br>Flexible Foundries Effort: 5%Risk: Low to Moderate                | 137  |

| 9.8      |      | stem Demonstration Effort: 20%Risk: Moderate                                                                     | 137  |

| 9.9      | Tech | chnology Transfer Effort: 5%Risk: Low to Moderate                                                                | 138  |

|          |      |                                                                                                                  |      |

| Appendix | κA   | Critical Issues and Recommendations                                                                              | A-1  |

| Appendi  | ĸВ   | Key Standards                                                                                                    | B-1  |

| Appendia | ĸC   | Bibliograpny                                                                                                     | C-1  |

| Appendia | e D  | Distribution                                                                                                     | D-1  |

Ť.

D'

Õ

\_\_\_\_

iv

D C

# LIST OF ILLUSTRATIONS

| Figure | <u>Title</u>                                                | Page        |

|--------|-------------------------------------------------------------|-------------|

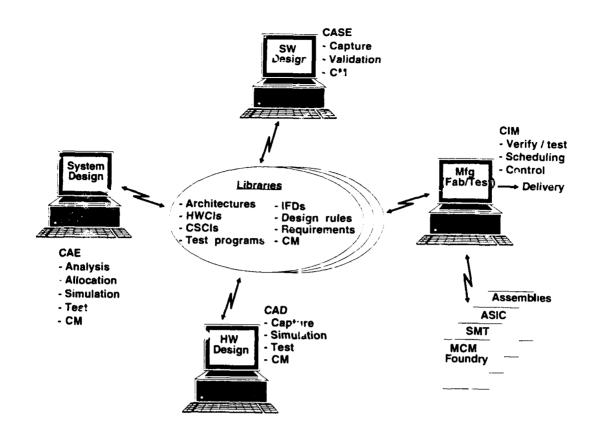

| 1      | PACCE Design System                                         | . 3         |

| 1      | RASSP Design System                                         |             |

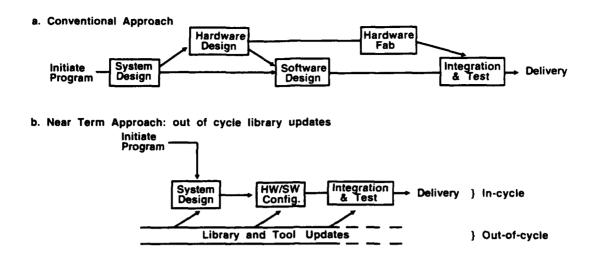

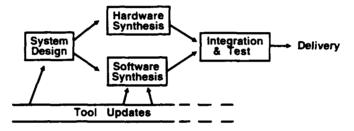

| 2      | Signal Processor Design Approaches                          | . 4         |

| 3      | The RASSP Development Cycle                                 |             |

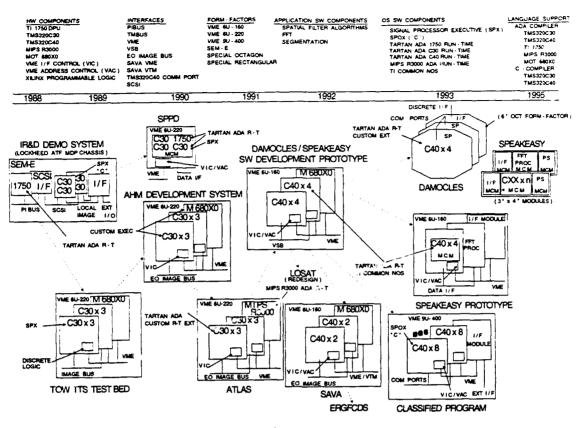

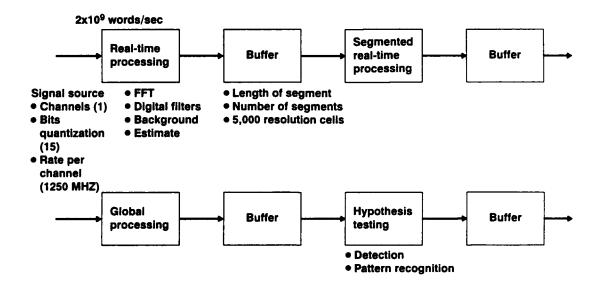

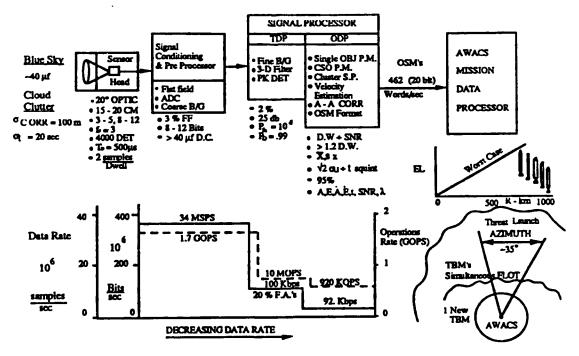

| 4      | Signal Processor Architecture                               | . 10        |

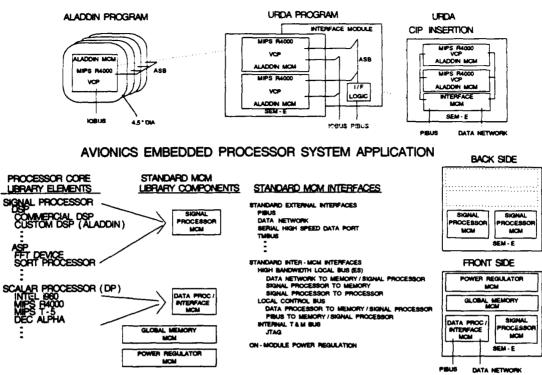

| 5      | Library Elements                                            | . 14        |

| 6      | Library Element Model Examples                              | . 18        |

| 7      | Library Element Model Examples                              |             |

| 8      | Functional Element Design Examples                          |             |

| 9      | Standard MCM Library Element Examples                       | . 23        |

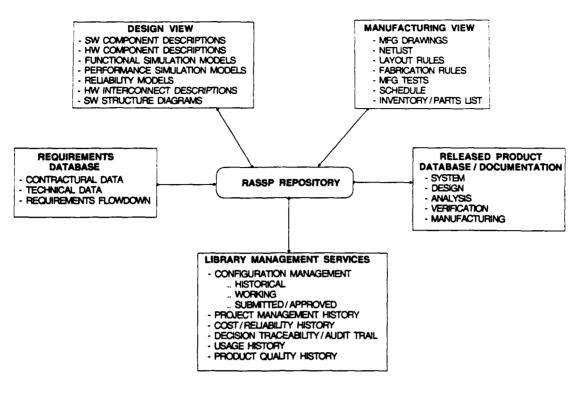

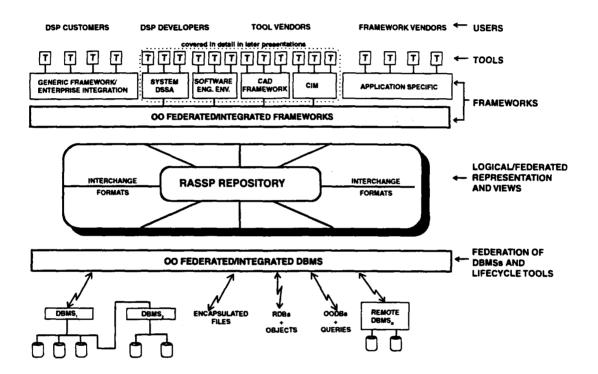

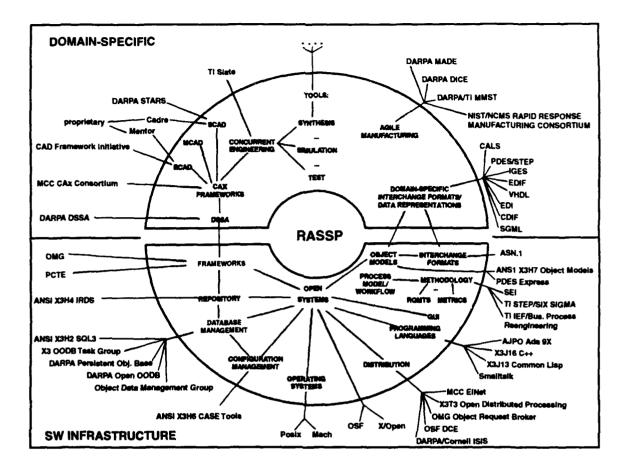

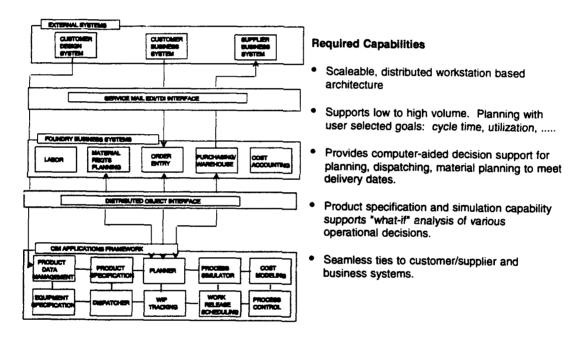

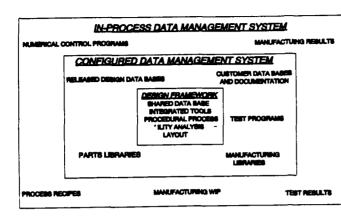

| 10     | RASSP System Architecture                                   | . 26        |

| 11     | Summary of Related Work                                     | . 28        |

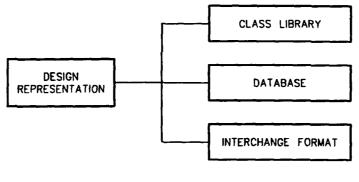

| 12     | Automated Mappings Should Exist Between These               |             |

|        | Three Views of Design Representations                       | . 40        |

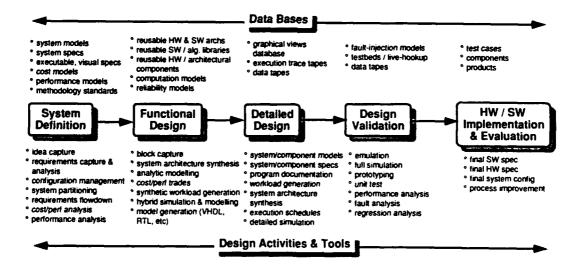

| 13     | Typical Breakdown of Major Activity Stages                  | . 48        |

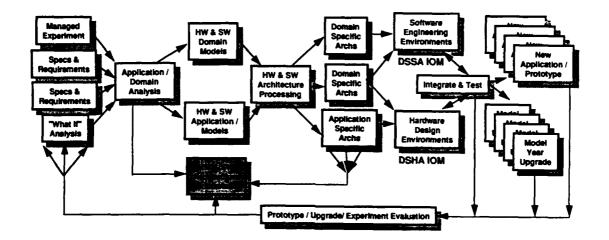

| 14     | Possible Top-level View of Formal System Design Process     |             |

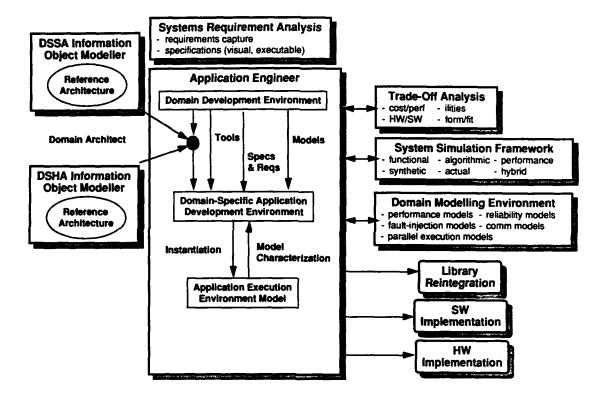

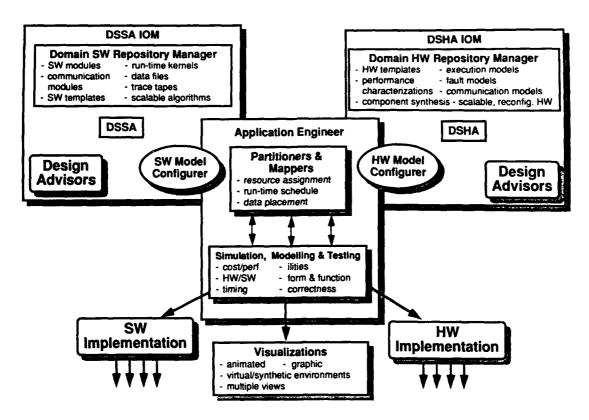

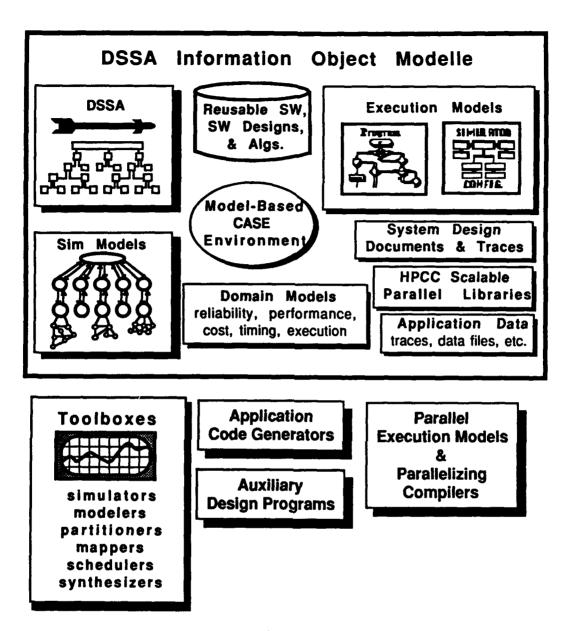

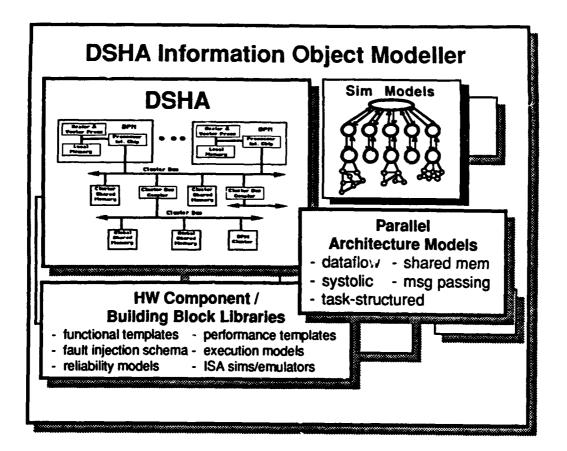

| 15     | Top-level View of Proposed RASSP Design System              | . 52        |

| 16     | Design Integration and Validation                           |             |

| 10     | Fundamental Components and Access Methods                   |             |

|        | Fundamental Components of Access Methods for DSHA Support . |             |

| 18     | Tundamental Components of Access Methods for DSHA Support.  | . 50        |

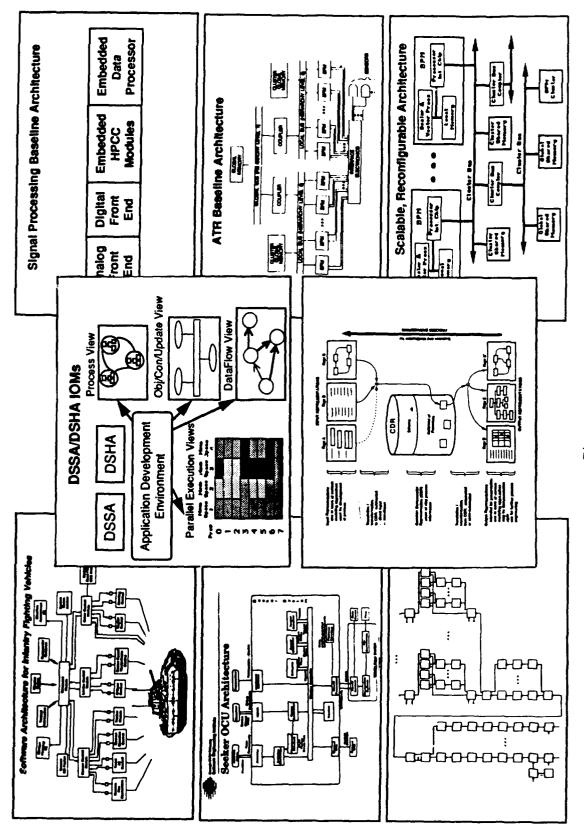

| 19     | Three examples DSSA Architectures                           | . 60        |

| 20     | Software Design Overview                                    |             |

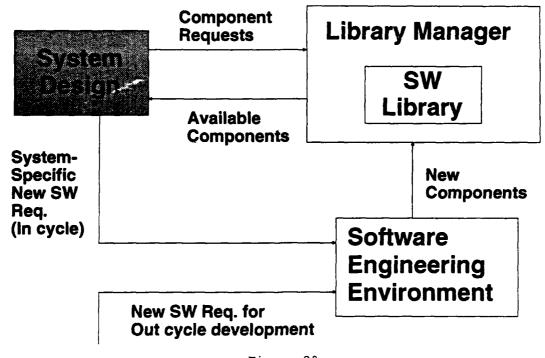

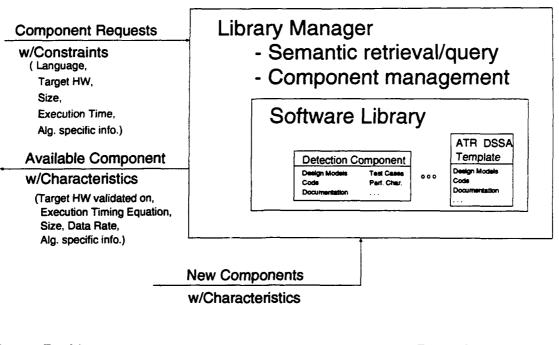

| 21     | Software Library                                            |             |

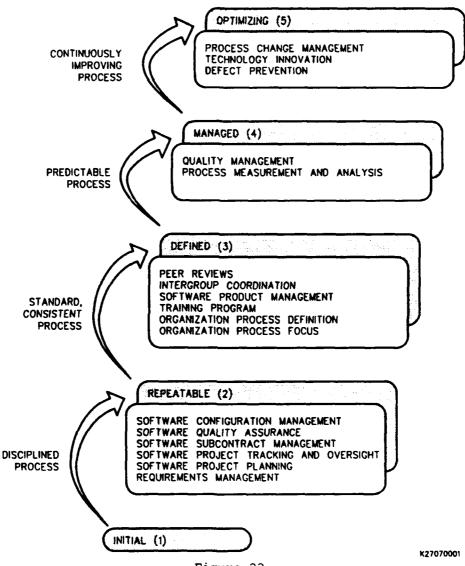

| 22     | Five Levels of Software Process Maturity                    | . 65        |

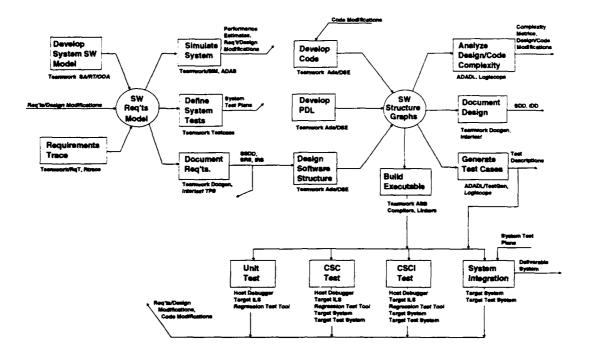

| 23     | Software Development - Today                                | . 67        |

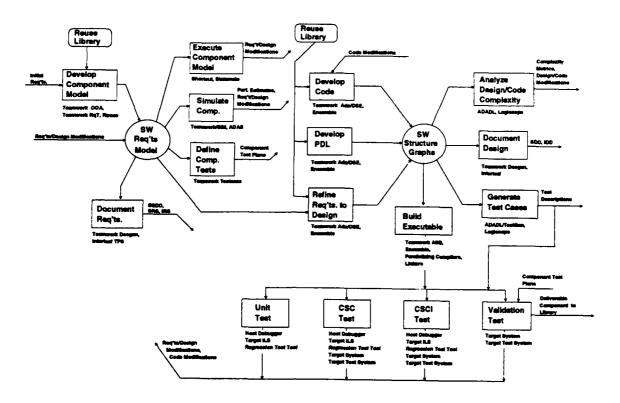

| 24     | Software Development - 1997                                 | . 68        |

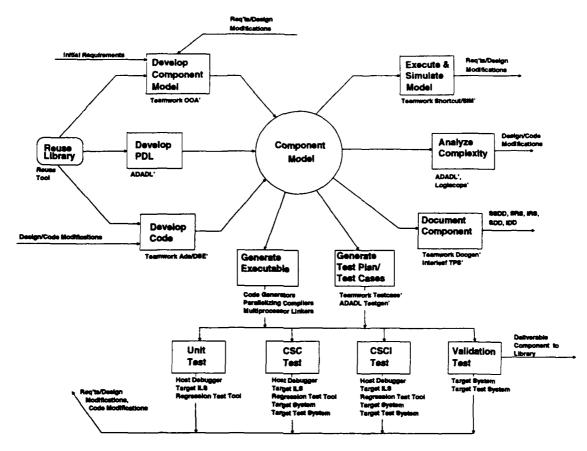

| 25     | Software Development - 2002                                 | . 69        |

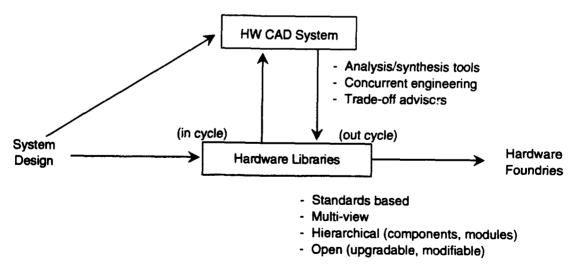

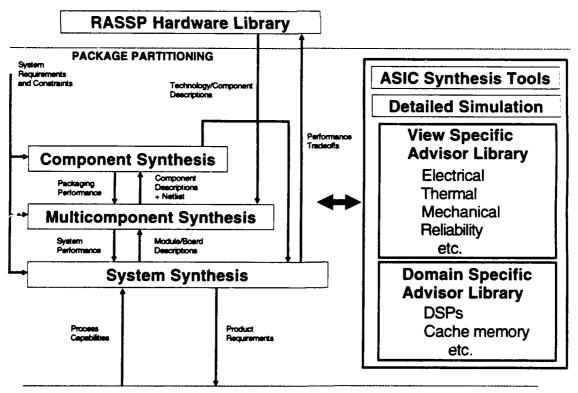

| 26     | Library Based Hardware CAD Concept                          |             |

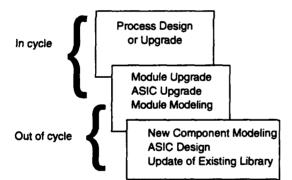

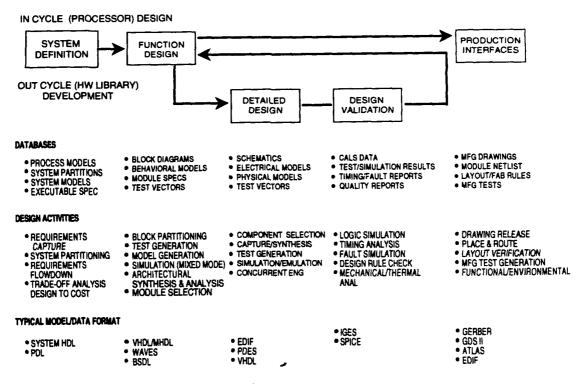

| 27     | In Cycle and Out of Cycle RASSP CAD                         | . 72        |

| 28     | RASSP Design Advisers/Tradeoff Analysis                     | . 75        |

| 29     | Key RASSP Related Testability Trends                        |             |

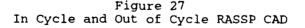

| 30     | TI Design Flow                                              | 78          |

| 31     | RASSP Design Flow                                           | . 79        |

| 32     | System Definition/Concept Design                            | . 79        |

| 33     | Functional Design Level                                     | . 80        |

|        |                                                             | . 82        |

| 34     | Detailed Design Level                                       |             |

| 35     | Design Verification Level                                   | . 83        |

| 36     | Manufacturing "Pre Fab" Interface                           | . 83        |

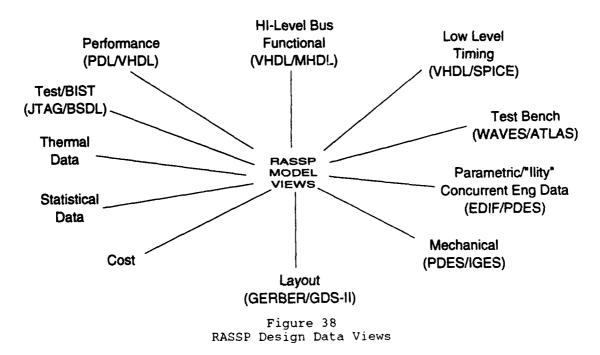

| 37     | RASSP Design Information Modeling                           | . 84        |

| 38     | RASSP Design Data Views                                     | . 85        |

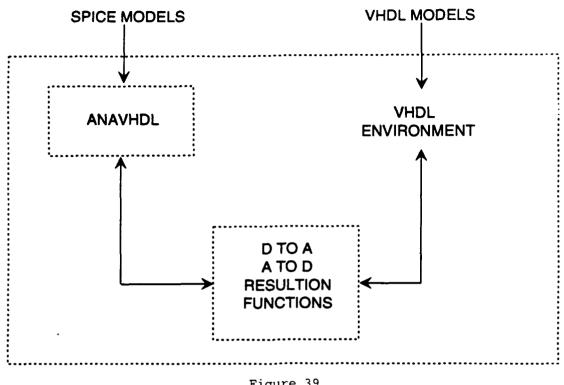

| 39     | AnaVHDL Mixed Mode VHDL Environment                         | . 88        |

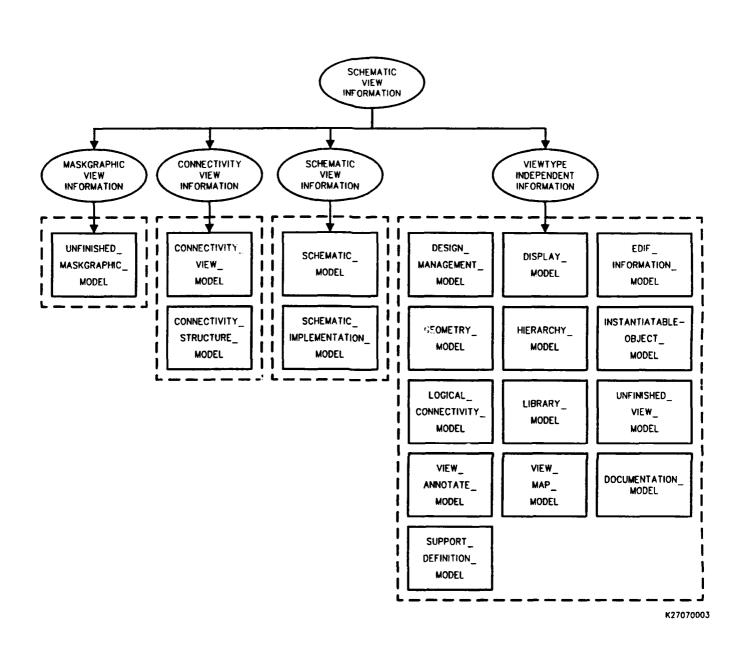

| 40     | EDIF Information Model Views                                |             |

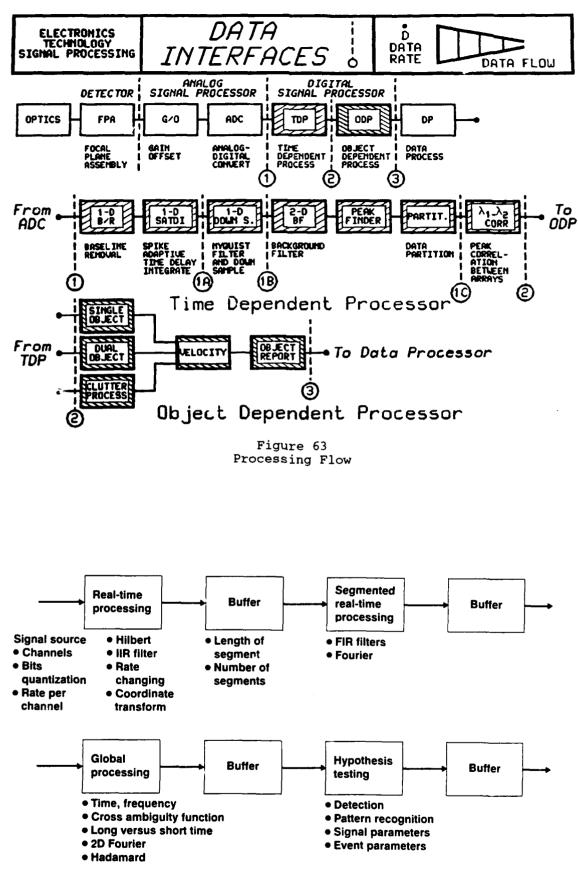

| 41     | Presentation Flow                                           |             |

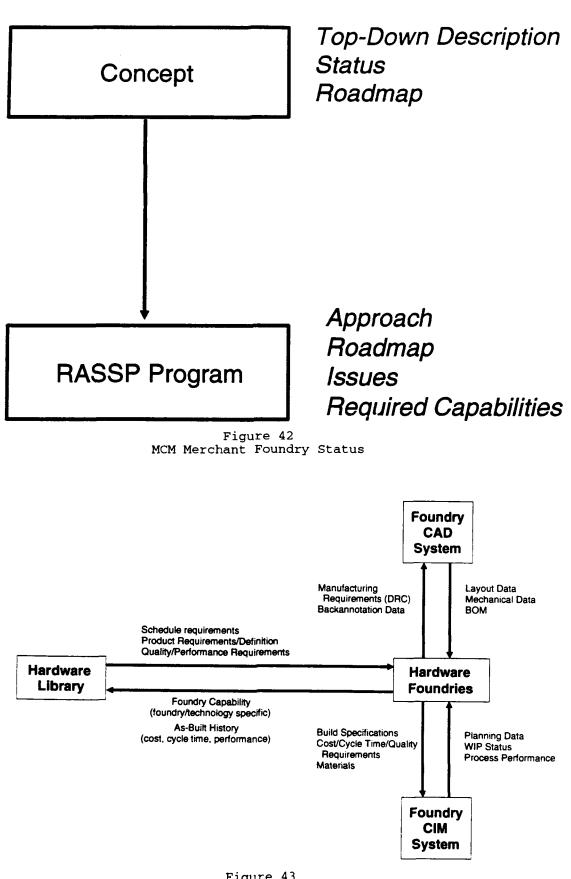

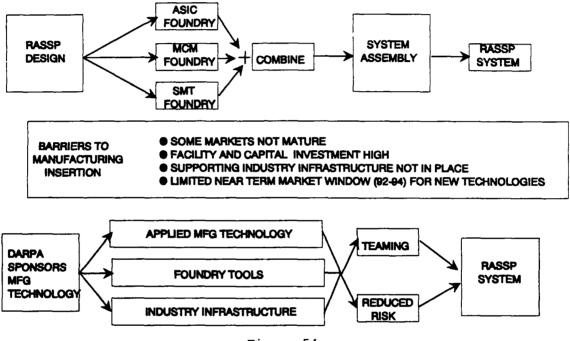

| 42     | MCM Merchant Foundry Status                                 |             |

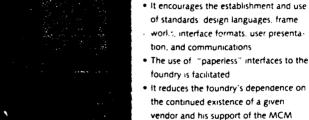

| 43     | Hardware Foundries                                          | . 93        |

| 44     | DSPIV Module                                                | . 95        |

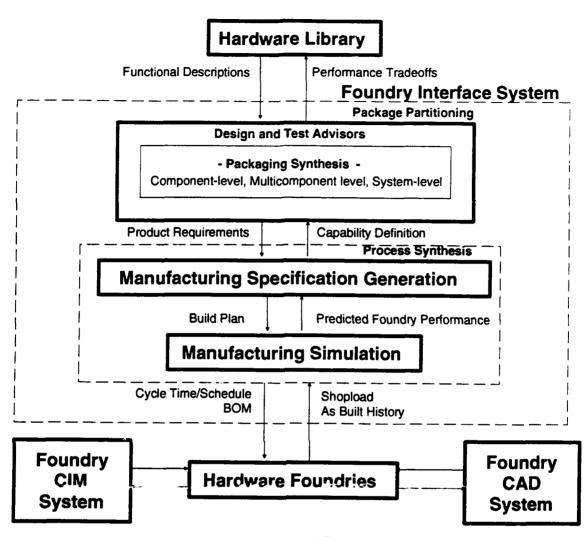

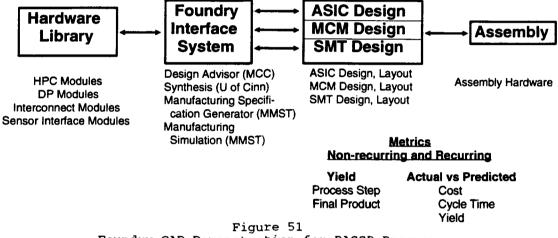

| 45     | Foundry Interface System                                    | . 96        |

| 46     | MCC Summary of Tool Status - Known Tradeoff Analysis Tools  |             |

| 47     | MCC Summary of Tool Status - Test Advisor Tools             |             |

|        | MCC Packaging Synthesis System                              |             |

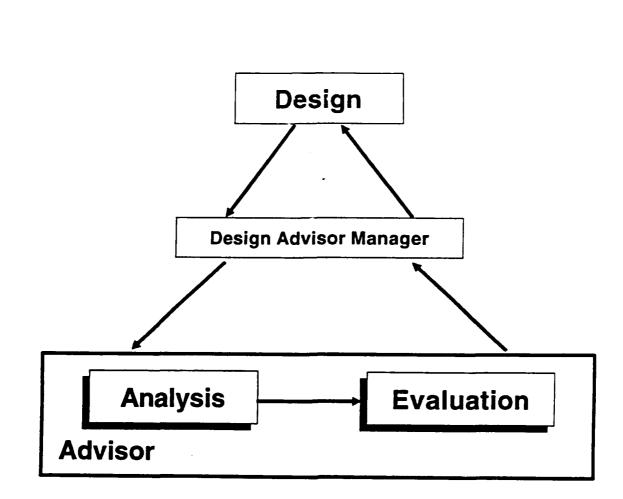

|        | Design Advisor Components                                   | . 100       |

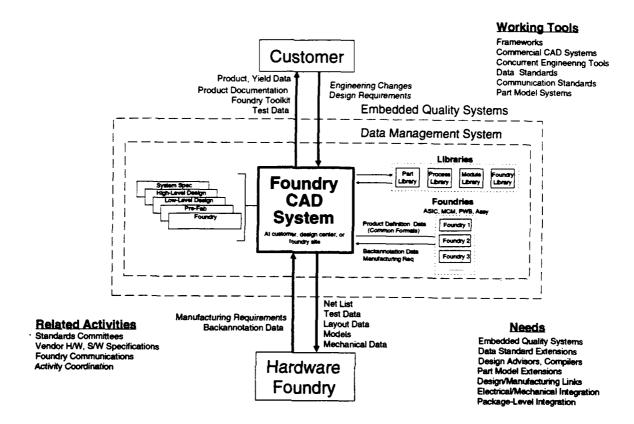

| 49     | Foundry CAD System                                          | . 101       |

| 50     |                                                             |             |

| 51     | Foundry CAD Demonstration for RASSP Program                 | . 105       |

| 52     | Common Elements Associated with RASSP Program               |             |

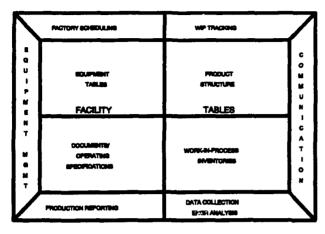

|        | Manufacturing Environment                                   | . 108       |

| 53     | Tool Samples                                                | . 109       |

|        | Network of Foundries                                        | $\cdot$ 11° |

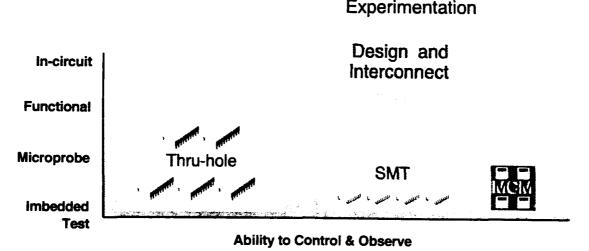

| 55     | Production Test Needs                                       | . 112       |

| 56     | Test Technology Roadmap                                     | . 113       |

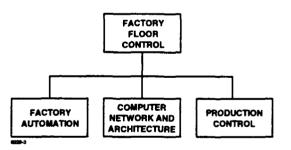

| 57     | Foundry Manufacturing Control                               | . 113       |

# LIST OF ILLUSTRATIONS (CONTINUED)

| Figure | <u>a Title</u>                                   | Page |

|--------|--------------------------------------------------|------|

|        |                                                  |      |

| 58     | Foundry Data Automation System                   |      |