### Kaytheon/BK-21717

### **RAPID PROTOTYPING OF APPLICATION SPECIFIC SIGNAL PROCESSORS (RASSP)**

### FINAL TECHNICAL REPORT

George J. Agule Stephen M. Lorusso

Kelley J. Arsenault Paul N. Bompastore Robert V. Bryant Victor L. Corbin Colleen A. Hartnett

**Raytheon Company**

### Raytheon/BR-21717

### **RAPID PROTOTYPING OF APPLICATION SPECIFIC SIGNAL PROCESSORS (RASSP)**

### FINAL TECHNICAL REPORT

#### Prepared by,

George J. Agule, Consulting Engineer, Digital Systems Laboratory Stephen M. Lorusso, Senior Engineer, Digital Systems Laboratory

Kelley J. Arsenault, Section Manager, CAE System Level Analysis Paul N. Bompastore, Section Manager, CAE Digital & Analog Systems Robert V. Bryant, Section Manager, CAE Manufacturing Support Victor L. Corbin, Department Manager, Electronic Design and Test CAE Colleen A. Hartnett, Senior Engineer, CAE Operations

### **Raytheon** Company

Missile Systems Division Tewksbury, Massachusetts 01876

### October 1992

Prepared for, Defense Advanced Research Projects Agency (DARPA) Electronics Systems Technology Office Rapid Prototyping of Application Specific Signal Processors Program ARPA Order No. <u>9219/3</u> Issued by DARPA/CMO under Contract No. <u>MDA972-92-C-0059</u>

The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the U.S. Government.

| REPORT DO                                                                                                                                                       | CUMENTATION P                                                                                           | AGE                                                                           | Form Approved<br>OMB No 0704-0188                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gathering and maintaining the data needed, and to                                                                                                               | mpleting and reviewing the collection of<br>reducing this purden to Washington He                       | information - Send comments rega<br>adquarters Services, Directorate for      | viewing instructions searching existing data sources,<br>rding this burden estimate of any other aspect of this<br>i information Operations and Reports, 1215 Jefferson<br>ect (0704-0188), Washington, DC 20503 |

| 1. AGENCY USE ONLY (Leave blank)                                                                                                                                | 1. AGENCY USE ONLY (Leave blank) 2. REPORT DATE 3. REPORT TYPE AND DATES<br>9-OCT-92 Final Technical Re |                                                                               |                                                                                                                                                                                                                  |

| 4. TITLE AND SUBTITLE                                                                                                                                           | 9-001-92                                                                                                | Filial leciuli                                                                | 5. FUNDING NUMBERS                                                                                                                                                                                               |

| Rapid Prototyping of App<br>(RASSP) Final Techni                                                                                                                |                                                                                                         | Signal Processors                                                             | Contract<br>MDA972-92-C-0059                                                                                                                                                                                     |

| 6 AUTHOR(S)<br>George J. Agule, Stepher<br>Paul N. Bompastore, Robe<br>Colleen A. Hartnett                                                                      | • •                                                                                                     | -                                                                             |                                                                                                                                                                                                                  |

| 7. PERFORMING ORGANIZATION NAM                                                                                                                                  | IE(S) AND ADDRESS(ES)                                                                                   |                                                                               | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER                                                                                                                                                                      |

| Raytheon Company<br>Missile Systems Division<br>50 Apple Hill Drive<br>P. O. Box 1201<br>Tewksbury, MA 01876                                                    | BR-21717                                                                                                |                                                                               |                                                                                                                                                                                                                  |

| 9. SPONSORING / MONITORING AGEN                                                                                                                                 | CY NAME(S) AND ADDRESS(E                                                                                | 5)                                                                            | 10. SPONSORING / MONITORING                                                                                                                                                                                      |

| Defense Advanced Researd<br>Electronics Systems Tech<br>3701 North Fairfax Drive<br>Arlington, VA 22203-171                                                     | AGENCY REPORT NUMBER                                                                                    |                                                                               |                                                                                                                                                                                                                  |

| 11. SUPPLEMENTARY NOTES                                                                                                                                         |                                                                                                         |                                                                               |                                                                                                                                                                                                                  |

|                                                                                                                                                                 |                                                                                                         |                                                                               |                                                                                                                                                                                                                  |

| 12a. DISTRIBUTION / AVAILABILITY ST                                                                                                                             | ATEMENT                                                                                                 |                                                                               | 12b. DISTRIBUTION CODE                                                                                                                                                                                           |

| Approved for public rele                                                                                                                                        | ease; distribution i                                                                                    | s unlimited.                                                                  |                                                                                                                                                                                                                  |

| 13. ABSTRACT (Maximum 200 words)                                                                                                                                |                                                                                                         |                                                                               |                                                                                                                                                                                                                  |

| The report is organized<br>their efforts to manage<br>program. This document<br>comprehensive reference<br>feasibility of developin<br>YEAR cost, schedule, and | the risks inherent<br>is a compendium of<br>useful for gaining<br>ng application spec:                  | in the Implement<br>study phase repo<br>insight into the<br>ific signal proce | ation Phase of the RASSP<br>rts that together form a<br>complexities and                                                                                                                                         |

| 14. SUBJECT TERMS<br>Design System, Interope<br>Database, Teaming, Targ                                                                                         |                                                                                                         | ring, Testing,                                                                | 15. NUMBER OF PAGES<br>119<br>16. PRICE CODE                                                                                                                                                                     |

| 17. SECURITY CLASSIFICATION 18.<br>OF REPORT                                                                                                                    | SECURITY CLASSIFICATION<br>OF THIS PAGE                                                                 | 19. SECURITY CLASSIFIC                                                        | CATION 20. LIMITATION OF ABSTRACT                                                                                                                                                                                |

|                                                                                                                                                                 | classified                                                                                              | Unclassified                                                                  |                                                                                                                                                                                                                  |

| · · · · <del>·</del> · · · · · · · · · · · · · ·                                                                                                                |                                                                                                         |                                                                               |                                                                                                                                                                                                                  |

Prescribed by ANSCStd. 239-18 298-102

### Table of Contents

l

l

Í

l

J

| 1.0 Introduction                                                   | 1              |

|--------------------------------------------------------------------|----------------|

| 2.0 Executive Summary                                              |                |

| 2.0.1 Study-Task Objectives                                        |                |

| 2.0.2 Technical Problems                                           |                |

| 2.0.3 General Methodology                                          |                |

| 2.0.4 Technical Results                                            |                |

| 2.0.5 Important Findings and Conclusions                           |                |

| 2.0.6 Significant Hardware Development                             |                |

| 2.0.7 Special Comments                                             |                |

| 2.0.8 Implications for Further Research                            |                |

| 3.0 Detailed Study Phase Reports                                   |                |

|                                                                    |                |

| 3.1 Design and Design-System Requirements                          | IJ<br>15       |

| 3.1.1 Study Phase Accomplishments                                  |                |

| 3.1.2 Overview of the Design System Concept                        |                |

| 3.1.2.1 Design System Framework                                    |                |

| 3.1.2.2.1 Assessment Tools                                         |                |

| 3.1.2.2.2 Electronic Design Notebook                               |                |

| 3.1.2.2.3 Electronic Design Databook.                              |                |

| 3.1.2.2.4 Visualization Techniques                                 |                |

| 3.1.2.3 Product Design Concurrent Engineering Environment          |                |

| 3.1.2.3.1 Requirements Design and Analysis Phase                   |                |

| 3.1.2.3.2 Concept (Preliminary) Design and Analysis Phase          |                |

| 3.1.2.3.3 Software Design and Analysis                             |                |

| 3.1.2.3.4 Hardware Design and Analysis                             | 35             |

| 3.1.2.3.5 Physical Design and Analysis                             |                |

| 3.1.3 CALS Interface                                               |                |

| 3.1.4 Design System Issues                                         |                |

| 3.1.5 Raytheon Related Efforts                                     |                |

| 3.2 Interoperability Considerations                                |                |

| 3.2.1 Hardware Interoperability                                    |                |

| 3.2.1.1 Current Approaches To Interoperability                     |                |

| 3.2.1.2 Adopting A Standard For High-Speed Data Transfers          |                |

| 3.2.1.3 Flexible Interfaces For Interoperability                   |                |

| 3.2.1.4 Interoperability Trade Offs                                |                |

| 3.2.1.5 Known Interoperability Problems And Considerations         |                |

| 3.2.2 Software Interoperability                                    |                |

| 3.2.2.1 Parallel Software                                          |                |

| 3.2.2.2 Real-Time Software Specification                           |                |

| 3.3 Design/Manufacturing Interface Considerations                  | 57 🗇           |

| 3.3.1 Production/Procurement Services                              | 57 🛛           |

| 3.3.2 Contract Assembly Services                                   |                |

| 3.3.3 A PWB Design/Manufacturing Interface Example                 | 59             |

| 3.3.4 On-Line Process and Cost Feedback                            | 60             |

| 3.3.5 DICE Manufacturing Optimization                              | 61             |

| 3.3.6 MMIC Process/Cost Database                                   | <b>.63</b> .es |

| 3.3.6 MMIC Process/Cost Database<br>DITC QUILLI'T LIVEPECTED 1 A-1 | Jr             |

| DITC QUALLANT                                                      | epeerdt        |

| WI INCLECTED 1                                                     | ł              |

|                                                                    | 1              |

|                                                                    | i              |

ijj

### Table of Contents, Continued

| 3.4 Manufacturing Considerations                                          | 65   |

|---------------------------------------------------------------------------|------|

| 3.5 Testing Procedures                                                    | 67   |

| 3.5.1 Major Issues                                                        | . 67 |

| 3.5.2 Possible Solutions                                                  | 68   |

| 3.5.2.1 Translation System For TPS Development                            | . 68 |

| 3.5.2.2 Design/Test Interactive Link                                      |      |

| 3.5.2.3 BIT/BITE Insertion                                                | . 70 |

| 3.5.2.4 Integrated Diagnostics Design Tools                               | 71   |

| 3.5.3 Challenges                                                          |      |

| 3.5.4 Feasibility                                                         | 73   |

| 3.6 Equipment Requirements                                                | .75  |

| 3.6.1 Assembly Equipment                                                  | 75   |

| 3.7 Facility Requirements                                                 | .77  |

| 3.7.1 Raytheon SEM-E Capabilities                                         | .77  |

| 3.7.2 Raytheon Lowell Capabilities                                        | .78  |

| 3.7.3 PWB Fabrication and Assembly Services                               | 78   |

| 3.7.4 Cluster Tool Facilities                                             | .79  |

| 3.7.5 RASSP Sources                                                       | 79   |

| 3.8 Database                                                              |      |

| 3.8.1 Objectives                                                          |      |

| 3.8.2 Data Integration Solution                                           | 83   |

| 3.8.2.1 Data Model                                                        |      |

| 3.8.2.2 Standards                                                         |      |

| 3.8.3 Libraries                                                           |      |

| 3.8.4 Risks/Issues/Recommended Research                                   | 88   |

| 3.9 Teaming Arrangements With Other Organizations                         | .89  |

| 3.10 Establishment of Military Sources                                    | .93  |

| 3.11 Target Systems                                                       |      |

| 3.11.1 Candidate Systems And Classes                                      |      |

| 3.11.2 Missile Systems Candidates                                         | 104  |

| 3.11.3 ATR Category                                                       |      |

| 3.11.4 Classes Of Systems Which Benefit Most From The Model Year Approach | .109 |

| 3.11.5 Primary RASSP Insertion Targets                                    |      |

| 3.11.5.1 Equipment Division Candidates                                    |      |

| 3.11.5.2 Submarine Signal Division Candidates                             |      |

| 3.11.5.3 Electromagnetic Systems Division Candidates                      |      |

| 3.11.5.4 Missile Systems Division Candidates                              | 117  |

### Tables and Figures

ſ

Í

Ì

ľ

|                                                                                                                      | ~  |

|----------------------------------------------------------------------------------------------------------------------|----|

| Table 2.0-1, Set Of System Engineering CAE Tools         Figure 3.0-1, Phased Development Of The RASSP Design System |    |

| Figure 3.0-2, Multidimensional Design-System Structure                                                               |    |

| Table 3.1-1, RASSP Design Activities                                                                                 |    |

| Table 3.1-2, Software Design Standards                                                                               |    |

| Table 3.1-2, Software Design Standards         Table 3.1-3, DARPA and DOD Programs of Interest to RASSP              | 17 |

| Figure 3.1-4, RASSP Design System Architecture Concept                                                               |    |

| Figure 3.1-5, Flow of the CACE/PM Tool                                                                               |    |

| Figure 3.1-6, Statemate Functional Perspective                                                                       |    |

| Figure 3.1-7, Statemate Behavioral Perspective                                                                       |    |

| Figure 3.1-8, Statemate Organizational Perspective                                                                   |    |

| Figure 3.1-9, Examples of Estimate Data Elements                                                                     |    |

| Table 3.1-10, Data Hierarchy                                                                                         |    |

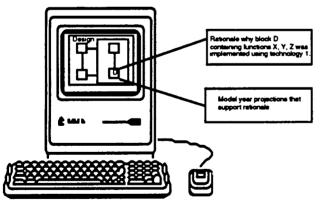

| Figure 3.1-11a, Electronic Design Notebook Concept                                                                   |    |

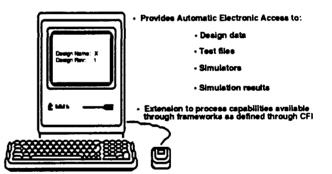

| Figure 3.1-11b, Example of Electronic Databook Concept                                                               |    |

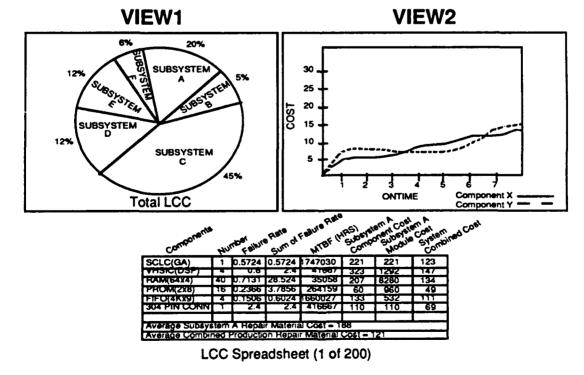

| Figure 3.1-12, Alternate views on a dense LCC spreadsheet                                                            |    |

| Table 3.1-13a, System Engineering CAE Tools Currently Meeting RASSP Design System Criteria                           |    |

| Table 3.1-13b, State-of-the-Art CAE Tools for the System Level Requirements Analysis Phase                           |    |

| Table 3.1-14, Adv. Research CAE Tools and Methods for System Level Requirements Analysis                             |    |

| Table 3.1-15, Detailed Information on the System Level Requirements Analysis Tools Researched                        |    |

| Table 3.1-16, State-of-the-Art CAE Tools for the Concept Design and Analysis Phase                                   |    |

| Table 3.117, Advanced Research CAE Tools and Methods for Concept Design and Analysis                                 |    |

| Table 3.1-18, Detailed Information on the Concept Design and Analysis Tools Researched                               |    |

| Table 3.1-19, State-of-the-Art CASE Tools for the Software Design and Analysis Phase                                 |    |

| Table 3.1-20, Information on a Subset of the Software Design and Analysis Tools Researched                           |    |

| Table 3.1-21, State-of-the-Art CAE Tools for the Hardware Design and Analysis Phase                                  |    |

| Table 3.1-22, Adv. Research CAE Tools and Methods for the Hardware Design and Analysis                               | 35 |

| Table 3.1-23, Detailed Information on the Hardware Design and Analysis Tools Researched                              | 36 |

| Table 3.1-24, State-of-the-Art CAE Tools for the Physical Design and Analysis Phase                                  | 38 |

| Table 3.1-25, Detailed Information on The Physical Design and Analysis Tools Researched                              | 39 |

| Table 3.126, VHDL Standards Study Areas                                                                              | 41 |

| Figure 3.1-27, Prototype System Design Environment                                                                   |    |

| Table 3.1-28, Tools Used and Evaluated for Seamless Digital Design Environment                                       | 44 |

| Figure 3.1-29, System Re-Engineering Methodology                                                                     |    |

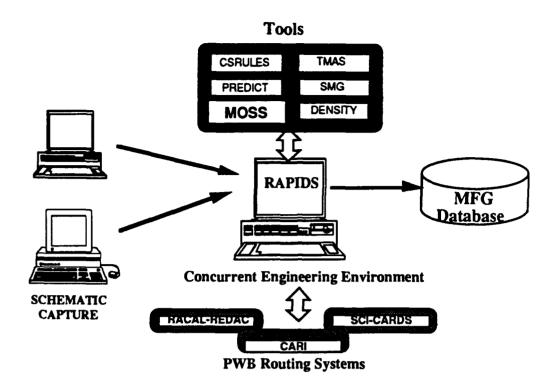

| Figure 3.1-30, RAPIDS Concurrent Engineering for PWBs                                                                |    |

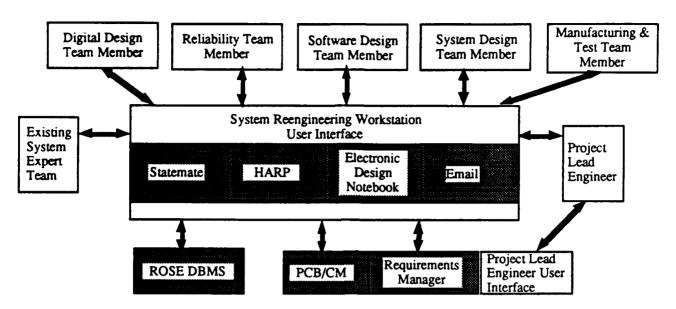

| Figure 3.1-31, System Re-engineering Workstation Environment                                                         |    |

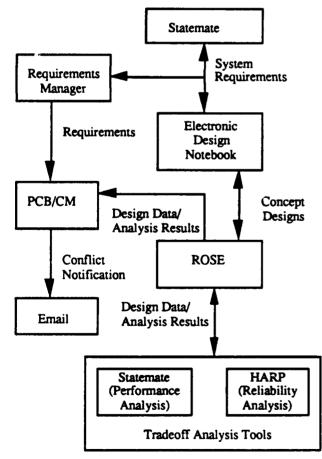

| Figure 3.1-32, System Re-engineering Workstation Information Flow                                                    |    |

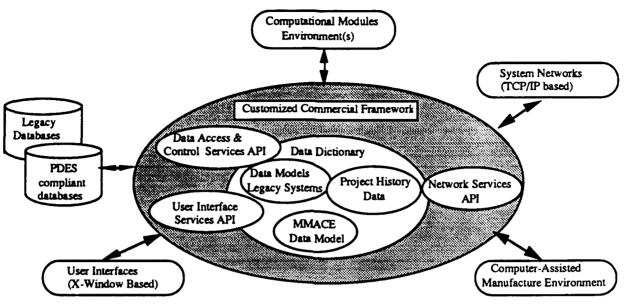

| Figure 3.1-33, High Level Overview of the MMACE System                                                               |    |

| Table 3.1-34, Examples of Raytheon/Vendor/University Working Relationships                                           |    |

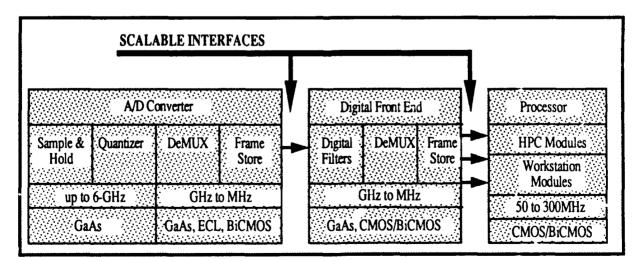

| Figure 3.2-1, Application Specific Signal Processor With Interoperable Sections                                      |    |

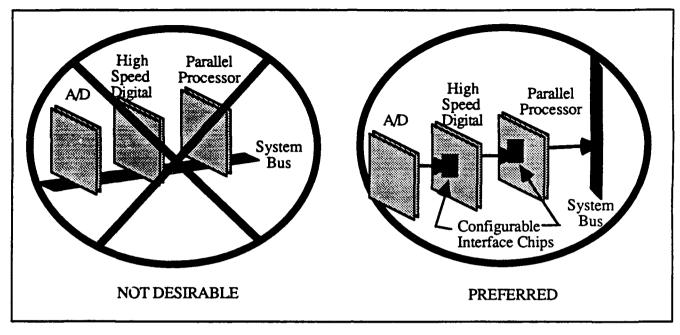

| Figure 3.2-2, System Bus Use For Interoperability                                                                    |    |

| Table 3.2-3, Standards And Products Affecting Interoperability                                                       |    |

| Table 3.2-4, Interface Implications for Subsection Upgrades                                                          |    |

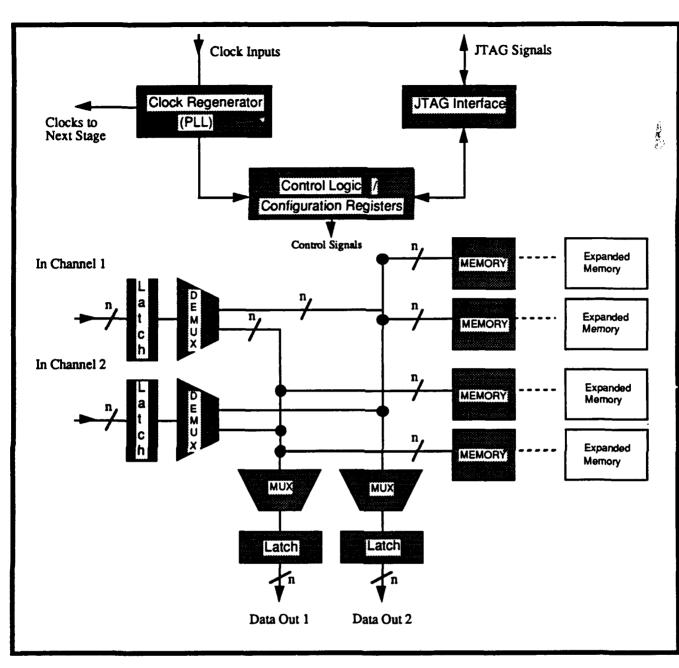

| Figure 3.2-5, Configurable Interface Chip                                                                            |    |

| Table 3.2-6, Libraries for Parallel Architectures                                                                    | 55 |

### Tables and Figures, Continued

| Table 3.2-7, Software Reuse Repositories                         | 56             |

|------------------------------------------------------------------|----------------|

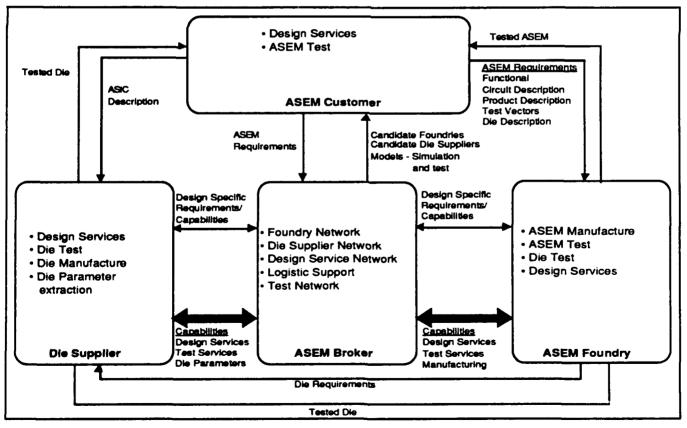

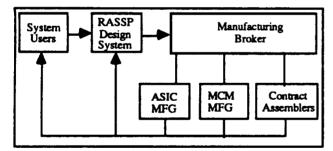

| Figure 3.3-1, ASEM Broker                                        |                |

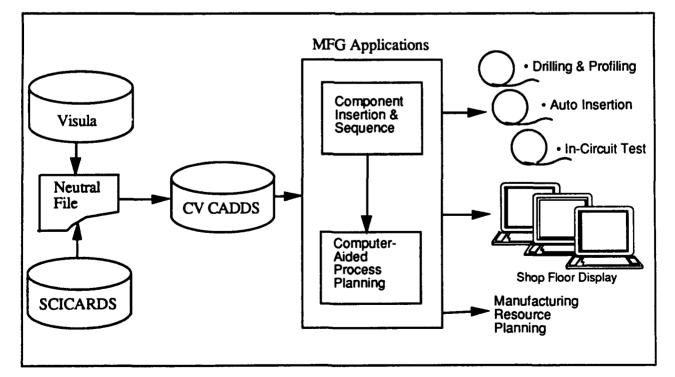

| Figure 3.3-2, PWB Transition Database                            | 59             |

| Table 3.3-3, NRE Applications from Interface                     | 60             |

| Table 3.3-4, Production Equipment                                | 60             |

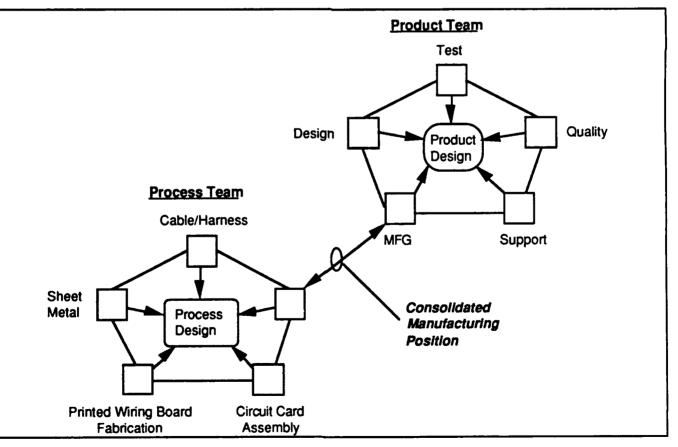

| Figure 3.3-5, Two Tiered Team Concept                            | 61             |

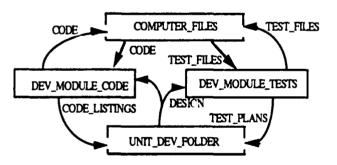

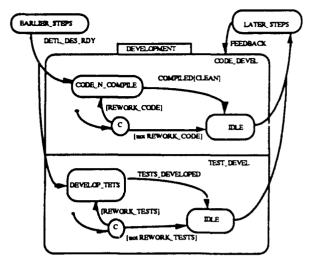

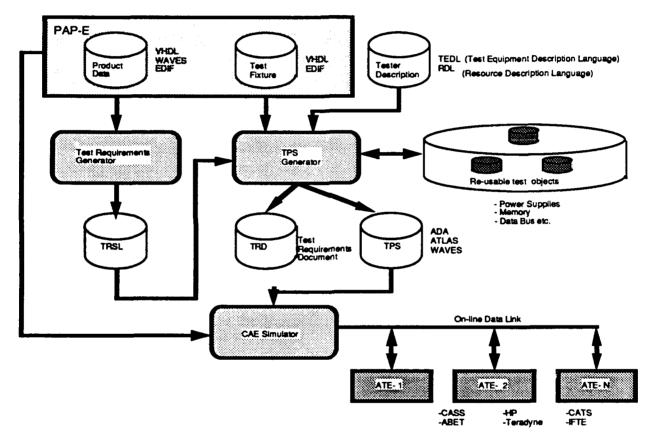

| Figure 3.5-1, TPS Data Flow                                      |                |

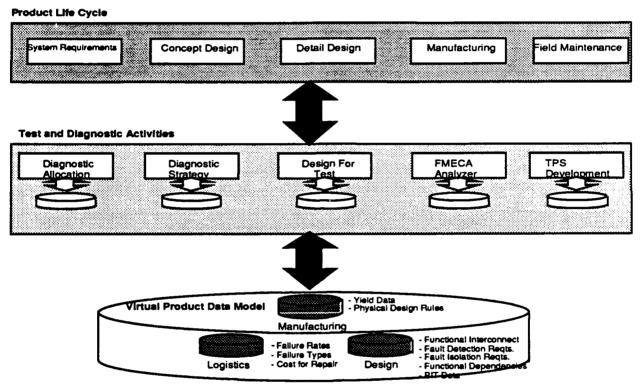

| Figure 3.5-2, Life Cycle Testing                                 | 71             |

| Figure 3.7-1, MCM Suppliers                                      | 80             |

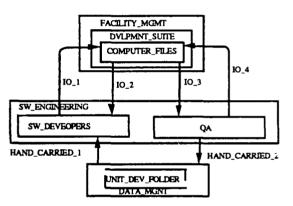

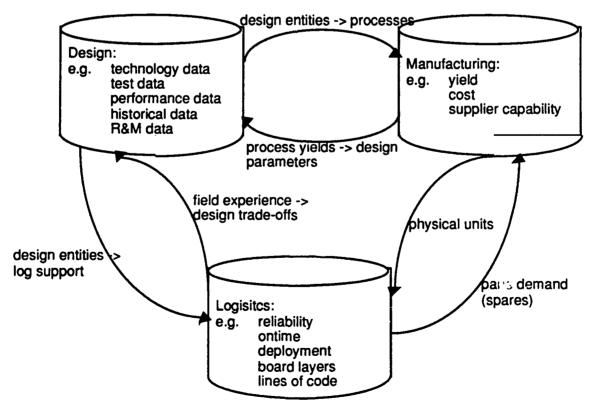

| Figure 3.8-1, Domains to be Integrated                           | 83             |

| Table 3.8-2, Matrix of Domain Relationships                      | 84             |

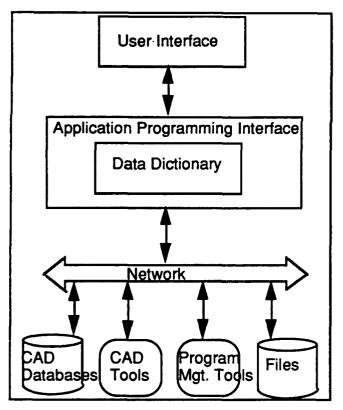

| Figure 3.8-3, Data Access Architecture                           | 85             |

| Figure 3.8-4, Standards Timeline                                 | 87             |

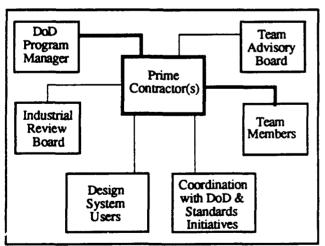

| Figure 3.9-1, Teaming Organization Chart                         | 89             |

| Table 3.9-2, CAx Vendor Candidates                               |                |

| Table 3.9-3, Manufacturer Candidates                             |                |

| Table 3.9-4, University Candidates                               |                |

| Table 3.9-5, Standards Organizations                             | 90             |

| Figure 3.9-6, Generic Team Structure                             |                |

| Figure 3.9-7, ASIC Vendor Acting As Broker                       |                |

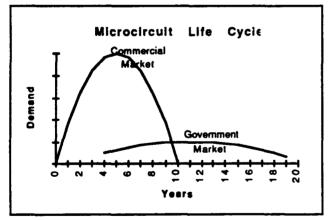

| Figure 3.10-1, Typical Life Cycles For A Family of Microcircuits | 93             |

| Table 3.11-1, Historical Insertion Timeline                      |                |

| Table 3.11-2, RASSP Insertion Time Line                          | <del>9</del> 8 |

| Table 3.11-3, Trade Parameters                                   |                |

| Table 3.11-4, Raytheon's Relevant Signal Processing Programs     | 100            |

| Table 3.11-5, Commercial-based Signal Processor Programs         |                |

| Table 3.11-6, Growth of Product Functionality                    |                |

| Table 3.11-7, Missile Processing Algorithms                      | 105            |

| Table 3.11-8, Missile Processing Architecture                    |                |

| Table 3.11-9, Missile ATR Functions                              |                |

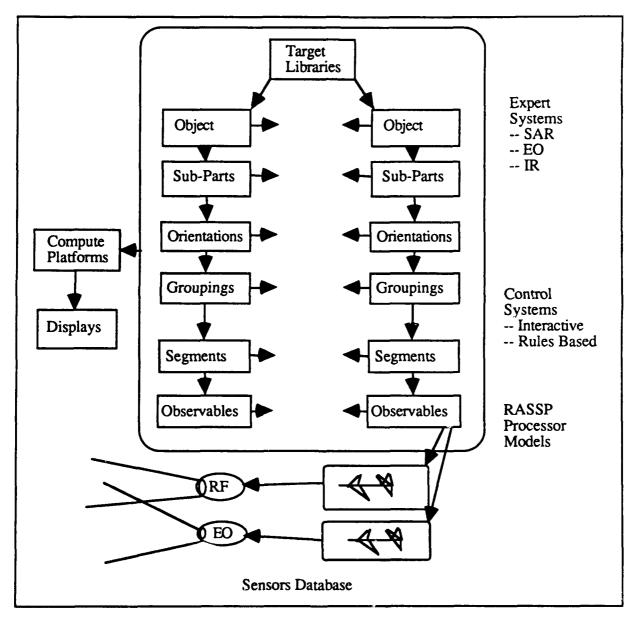

| Figure 3.11-10, Air Target Algorithm Development Test Bed        |                |

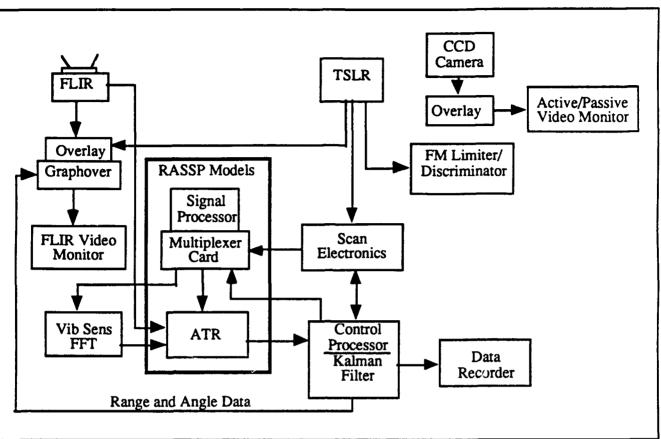

| Figure 3.11-11, ALCTV Phase II Block Diagram                     |                |

| Table 3.11.12, ED's Primary RASSP Insertion Targets              |                |

| Table 3.11-13, SSD's Primary RASSP Insertion Targets             | 113            |

| Table 3.11-14, ESD's Primary RASSP Insertion Targets             |                |

| Table 3.11-15, MSD's Primary RASSP Insertion Targets             |                |

| Table 3.11-16, MSD's Contacts For RASSP Insertion Targets        | 118            |

#### **1.0 Introduction**

This document contains information useful for assessing the applicability, complexity, and feasibility of implementing the RASSP methodology. The Study Phase investigated eleven topics. Each investigation consisted of 1) a feasibility of the proposed RASSP methodology, 2) a compendium of related work, 3) a discussion of any perceived or known problems, and 4) a discussion of possible solutions to problems.

The report is organized to provide information to program managers in support of their efforts to manage the risks inherent in the Implementation Phase of the RASSP program. This report has three major sections. Sections 1 and 2 provide introductory and summary information. Section 3 provides detailed information on eleven separate categories as defined in the Statement of Work in solicitation RFP MDA 972-92-R-0017. These eleven sub-sections make up a compendium of study phase reports that together form a comprehensive reference useful for gaining insight into the complexities and feasibility of developing application specific signal processors that meet MODEL YEAR cost, schedule, and upgrade objectives.

#### 2.0 Executive Summary

#### 2.0.1 Study-Task Objectives

The objective was to study eleven critical areas and document major issues, potential problems, possible solutions, current state-of-the-art, feasibility of RASSP objectives, and related work. The eleven areas are:

- Design and Design-System Requirements

- Interoperability Considerations

- Design/Manufacturing Interface Considerations

- Manufacturing Considerations

- Testing Procedures

- Equipment Requirements

- Facility Requirements

- Database Requirements

- Teaming Arrangements

- Establishment of Military Sources

- Target Systems

#### 2.0.2 Technical Problems

The major technical issues are concerned with the Design System, Standards, industry integration and manufacturing resource links. Action items were accepted at the Final Program Review to expand on these issues. Three action items are addressed here as a summary.

### **ACTION ITEM 1**

# Subjects: CFI, Block Releases, Expediting

The Final Report should contain a discussion of the present CFI plan, a suggested approach for expediting the standards development, a suggested approach for expediting its promulgation by MENTOR, CADENCE, DEC, and COMPASS, and how the improved plan might fit in with the Raytheon concept of block releases.

During the Study Phase, CFI Inc. and various CAD framework vendors were approached

concerning this issue. CFI has provided us with their proposal and funding requirements profile. The industry interaction and nuances are complex and will find many problems to overcome in the course of obtaining full CFI and RASSP goals. Our approach is one of both "push" and "pull." CFI Inc. needs support and perhaps expansion of their projects. The industry needs a means of resolving conflict, but what is more important is ensuring that what evolves is fully marketable. The RASSP funding of CAE vendors to provide the various elements of Block one, Block two, and Block three "RASSP Design System" provides the "pull." It also establishes a mechanism, along with workshops, symposia and newsletter, to sell the capabilities to industry. This is accomplished not only through demonstrations, but through making the design system available to industry evaluators for hands on use.

CFI (CAD Framework Initiative) is an international cooperative effort within the electronics industry. CFI was formed in 1988 as a non-profit organization with the following mission: "Define interface standards that facilitate the integration of design automation tools for the benefit of end users and vendors worldwide."

Today's design engineers are generally not satisfied with the performance and functionality of their hardware and software automation tools. Because no single vendor offers the best solution for all users' design problems, users often piece together their own set of solutions. This results in wasted design time spent painfully integrating tools from different sources. CFI was formed to address this problem. Among its members are design automation vendors, computer and semiconductor suppliers, and CAD tool end users, as well as government, research and academic institutions. CFI believes that effective use of standard frameworks will raise productivity among users by providing interchangeable tools, and will allow vendors to focus on tool functionality rather than reinventing

proprietary interfaces.

CFI believes that a framework should be a layered procedural interface, supported on multiple platforms, that is modular and easily extensible. The CFI mission is synergistic with other industry standards efforts, such as the Open Software Foundation (OSF), the Electronic Data Interchange Format (EDIF) and the government funded Engineering Information System (EIS) program.

Raytheon Company has a subscription membership to the CAD Framework Initiative and has been closely tracking the activities of CFI.

Much of the work of CFI is now documented in the draft specifications, user guides, reference software and regression tests. CFI refers to this collection of items as CFI Pilot Release 1.0. It includes the following draft standards.

- Design Representation Electrical connectivity Information Model and Programming Interface.

- Inter-tool Communication Procedural Interface

- Inter-tool Communication Architecture

- Inter-tool Communication Base Object Model and Interface

- Tool Encapsulation Specification

- Execution Log Format

- Base Networking Services Guideline

- Base System Services Guideline

- CFI Users, Goals and Objectives

#### **RASSP** Applicability

The above standards will partially address many of the areas required for RASSP including Incremental Change/Analysis Tool Invocation and Control and a Standard Extension Language.

CFI's RASSP plan defines four Integration Phases: Phase 0-EDA Systems Integration, Phase 1- Manufacturing Integration, Phase 2-CASE/Codesign Integration, and Phase 3-Enterprise Integration. What CFI brings to the RASSP program is a model for developing framework standards. CFI has been successful in selecting a specific problem, getting large end-user companies experiencing the integration problem to participate, and getting vendors to work together to solve the end user's problem by developing the appropriate standards. CFI's RASSP funding requests, totaling \$4.1 million over 4 years, covers CFI's costs of coordinating the framework standards development effort. It includes the cost of a program manager, general support to the vendors and end-users, development of specifications, technology, and regression tests. It does not include costs incurred by the vendors or end-users involved in the standards development effort. However, CFI has been successful in the past in getting companies to volunteer their own time and effort to develop the standards.

ľ

# CFI'S RASSP Phase 0 And CFI'S Release 2.0:

CFI's release 2.0 should complete CFI's work in the EDA area including specifications for a Multisimulator Backplane and Library Standards. Process Management and Data Management standards are just beginning to be addressed. CFI admits that there is still much work to do in these areas, specifically regarding namespace resolution, and that without additional attention, standards will not be available in the short term. RASSP program influence with CFI and the contributing CAD vendors can shorten this schedule.

#### **CFI'S RASSP Phase 1:**

The RASSP program could have a greater influence in the Manufacturing interfaces. These programs are still in the vision stage and there exists the possibility that they may not get off the ground at all without government input. Raytheon's general belief is that manufacturing interfaces would be developed by CFI regardless of the involvement of the RASSP program but would not be at a pace sufficient to ensure

#### RASSP success.

#### CFI'S Phase 2 And 3:

Standards for CASE/co-design and enterprise integration play a major role for RASSP. This is basically a "cottage industry" with no standardization. The RASSP program would have a large impact in this technology area. Without RASSP involvement, there is a chance these areas will not be addressed at all. Phase 2 and 3 cannot be accomplished within the RASSP program time frame. RASSP design system will provide an implementation that will seed further CFI standard development in these areas.

#### Approach

Raytheon's suggested approach is to have the DARPA fund a number of resources available to all the RASSP contractor teams. These include CFI and NIST. The funding level for CFI should be approximately \$1 million over the four years. CFI will provide general support and consulting. This funding will also help CFI in development of specifications, technology, and regression tests. The contractor team should have, as team members, at least two framework companies and a group of CAD/CAM/CASE vendors. The two framework companies will ensure that the design system is not vendor specific. The CAD/CAM/CASE vendors will provide the needed design functions within the frameworks. The contractor team will ensure that the developed design system will meet RASSP goals and conforms to CFI standards. Within this teaming and support structure, RASSP and framework houses will be coordinating releases of the RASSP design system. The main reason for this approach is to reduce the risk of CAD/CAM/CASE vendors not participating and conforming with standards.

This approach will also expedite the standards development because real application implementation and demonstration will accelerate the development process.

With regard to CFI and the Raytheon concept of

block releases: our block releases will conform to whatever is available at the time.

- At block release one, not all EDA Systems integration standards will be ready. In block one release, the contractor will bring the design system (with its tool sets) to the CFI release 1.

- In block two release, the design system should conform with CFI release 2. There should also be some implementation of manufacturing integration that will be coordinated with CFI.

- In block three release, the design system will consist of upgrade of manufacturing integration to CFI's manufacturing integration standard. Block three release will also start the implementation of CASE/codesign integration. This implementation will contribute to CFI's CASE/co-design integration.

In summary, much of the standards related work required for the RASSP program will occur regardless of the RASSP program's involvement in CFI. However, the delivery dates and the sample implementation will probably not match those required by this program. CFI's track record in the development of standards is good and there is no reason to believe that, with proper funding and participation, the additional standards required for RASSP would not be accomplished in a timely and complete manner. Raytheon's teaming approach will facilitate working with CFI. Raytheon's design system block release will conform with CFI standards available at the time and will also help CFI's framework development process.

#### ACTION ITEM 2

# Subject: RASSP CAE Investment Strategy

Indicate which design system elements are critically important to RASSP and have probable development time lines that are compatible with RASSP's four year plan. Identify which current

industry efforts are going in the right direction.

During the RASSP Study Phase, the Raytheon team researched applicable CAE tools and methods (commercially available, advanced research, and applicable DoD initiatives). These are presented in section 3.1 of the study phase final report. Included with the list of tools is an overview of the functionality and input and output mechanisms. Some of the tools are compatible with the use of standards (for input modeling and use of libraries) within the current

| Tools                                                         | Use of<br>Modeling<br>Standards<br>(input &<br>Output) | Integration<br>with<br>Standard<br>Libraries | Ease of<br>Use | Open<br>Architecture | Link to Other<br>CAE Tools                                                                          |

|---------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------|----------------|----------------------|-----------------------------------------------------------------------------------------------------|

| Scientific and<br>Engineering<br>Software (SES)<br>Workbench  | Yes                                                    | Yes                                          | Yes            |                      | Link to software<br>through pictures                                                                |

| JRS's IDAS                                                    | Yes                                                    |                                              |                |                      | Link to Synopsys'<br>Design Architect                                                               |

| Synopsys' Design<br>Architect                                 | Yes                                                    | Yes                                          | Yes            |                      | Link to several target<br>technology foundries<br>and popular digital<br>schematic capture<br>tools |

| Mentor Graphics'<br>System Design<br>Station                  | Yes                                                    | Yes                                          |                |                      | Link to University of<br>Virginia U/I<br>Performance Models                                         |

| Redwood Design<br>Automation Tools                            | Yes                                                    | Yes                                          |                |                      | Unreleased information                                                                              |

| i-Logix's Statemate,<br>Express-VHDL                          | Yes                                                    |                                              |                |                      | Link to major logic synthesis tools                                                                 |

| University of<br>Virginia's U/I<br>VHDL Performance<br>Models | Yes                                                    | Yes                                          | Yes            |                      | Link from Mentor's<br>Block Diagram<br>cajability                                                   |

| IDE's Software<br>Through Pictures                            | Yes                                                    |                                              | Yes            |                      | Link to SES<br>Workbench                                                                            |

| Cadre's Teamwork                                              | Yes                                                    |                                              | Yes            |                      | Link to Statemate<br>and ADAS                                                                       |

| Mentor's Falcon<br>Framework                                  | Yes                                                    | Yes                                          | Yes            | Yes                  |                                                                                                     |

| Cence's<br>Framework                                          | Yes                                                    | Yes                                          | Yes            | Yes                  |                                                                                                     |

TABLE 2.0-1 SET OF SYSTEM ENGINEERING CAE TOOLS

tools. To realize RASSP goals, the block one RASSP Design System will take advantage of existing tools and concepts that make integration easier. Early proof-of-principle can be completed within the first year of the RASSP program. The following are important criteria that are followed when choosing CAE tools to integrate into this first design system.

- Functionality

- Use of modeling standards (VHDL, Ada, Verilog, etc.) for input and output mechanisms

- Integration of CAE tool with standard libraries for COTS parts

- Ease of Use

- Open architecture

- Link to other CAE tools

A particularly strong effort will be made to incorporate system engineering tools. Table 2.0-1 highlights the criteria and gives a set of system engineering tools that are moving in the direction necessary for RASSP goals. The functionality for each of these tools is available in section 3.1 of the Final Report. Table 2.0-1 does not go into detail for software, hardware, and physical design phases of the system design life cycle. Tools for software, hardware, and physical design phases are well established -- integrated to a large extent -- and take advantage of current modeling standards and libraries.

These tools are currently conforming to one or more of the criteria described above and therefore can be integrated successfully into the block one RASSP Design System within the first year of the program. However, in order to meet longterm RASSP goals, several other design system elements are important. A list of those design system elements follows along with their expectations.

Tools with the following functionality are necessary for RASSP program and should be researched and developed under the RASSP implementation phase.

- Hardware/software co-design tools

- System and subsystem functional partitioning/high-level synthesis tools

- System-level manufacturing advisor

- System-level logistics advisor

- System-level packaging compiler

#### **Database Technology**

The type of database technology required for RASSP model year design system makes demands on data integration rather than traditional database technology. The fact that data is stored in relational, object-oriented or system file is less important than the fact that these data entities, however represented, must be integrated.

Many activities in information integration are aggressively being pursued on an academic and practical level. Research initiatives in this area, sponsored by DoD, have been ongoing since the 1970's with the Air Force Information Integration Support System (I2S2) program, and the recent XEROX Design Research Center's DICE contract for in its explicit support for concurrent engineering, which is a fundamental requirement of the RASSP design system. However, a prototype from the XEROX activity in the meta data management area will not be available until 1993 for review. Until then, it would be recommended that this activity be closely followed. Industry activities are also prominent, such as the CALS Data Dictionary Further, Raytheon's internal Task Force. investigation of integration technologies for its implementation of the Raytheon Integrated Technical Information Service (RITIS) has reviewed several commercial products for implementation of the data dictionary service. These products include integration technologies from HyperDesk, GRC, DEC, Information Builders, Control Data Corp., Etc. The most promising thus far has been the Distributed

Object Management System, from HyperDesk, which is OMG compliant. It would be recommended for further investigation for data model implementation.

For Block one RASSP design system, the current Raytheon RITIS plan would be followed.

### **CFI PROGRAM**

It is anticipated that EDA and Manufacturing Integration will be completed within the RASSP program time frame. The RASSP program should provide direct funding to CFI for any additional integration strategies such as CASE/co-design Ircegration and Enterprise Integration. Additionally, the RASSP implementation team should provide input to the CFI standards efforts through its CAD team members.

#### N. DL, AHDL, VHDL Programs

The RASSP program should provide input to and a strong presence within the standards bodies to ensure success. The definition of AHDL is slower in proceeding but will be defined within the RASSP program time frame. The MHDL program, under Intermetrics, is still in its early stages. RASSP emphasis is on VHDL and its expanded application in supporting CALS, PAP-E, High Level Co-design, etc.

#### Generic System Description Language

There exists the need to develop a standard representation for system models that can be used prior to partitioning system requirements into subsystems requirements and then those subsystems into their digital, analog, microwave, and software requirements. Currently, there are no standards or industry organizations addressing this issue. RASSP can monitor and provide inputs to incipient activities.

#### Library Standardization

Developing standard library representations for performance models, functional models, reliability models, manufacturing process models, etc., are currently not being addressed under a unified standards organization and should be an area of investment under the RASSP program. Any progress made in this direction will add to the success of the RASSP program.

#### AVAILABILITY OF ENGINEERING ESTIMATE MODELS FOR DESIGN, LOGISTICS, AND MANUFACTURING DATA

Ì

The Raytheon RASSP Design System concept relies on the existence of models at various levels of abstraction in order to assess the cost, risk, and benefit of design upgrades and in order to design for model year. Ensuring the methodology for development and maintenance of models is an important RASSP investment area.

### ACTION ITEM 3

# Subject: Target System Application Domain

Select a single application domain that would be recommended for use as the demonstration model during RASSP development. It appears that generalized ATR processor model that has modular options to accommodate requirements of Radar, Sonar, IR, Laser, MMW Sensors would be most suitable. The Target programs would be:

- Advanced Land Combat Vehicle (ALCVT)

- Joint Direct Attack Munitions (JDAM)

- Advanced Kinetic Energy Missile (ADKEM)

- Passive Torpedo

Detection/Classification/Localization System

#### (DCLASP)

- Sonar Mine Detection Set (AN/AQS-20)

- Ground Based Radar (GBR)

- Airborne Shared Aperture Program (ASAP)

A RASSP program option would be to use, as an initial demonstration model the Synthetic Aperture Radar (SAR) processing function for both JDAM and the air to ground portion of ASAP. Much of the algorithm technology has been derived from the same research. A common hierarchical VHDL model sourced from program executable specifications would contain solutions for both systems. The VHDL model contains modular options and parametrically driven design functions that would be assembled into appropriate hardware/software demonstration models. In initial program phases, scaled portions of the system would be used to exercise the brokered flexible manufacturing and test resources. As the RASSP program progresses, the underlying database models can be extended to include capabilities for additional ATR functions and the expanded processor needs of other system programs in this category. This short list also includes two sonar applications, two combat vehicle/tank applications and a major ground radar system.

### 2.0.3 General Methodology

The study process involved three principal elements:

- The personnel, IR&D and contracts currently involved in the study areas within Raytheon's four divisions:

- Submarine Signal Division Portsmouth, RI

- Missiles Systems Division

Tewksbury, MA

- Equipment Division Marlboro, MA

- Electromagnetic Systems Division Goleta, CA

- Raytheon performed a concerted interviewing process of in-house experts and of industry resources. Industry resources were

expanded to include standards groups/consortia, service laboratories, CAD/CAM/CAT vendors and universities.

The data gathered was analyzed and resulted in suggested approaches and feasibility.

Feasibility analysis included both technical and schedule concerns. Detailed recommendations were established.

#### 2.0.4 Technical Results

Raytheon's Study Phase investigations produced results in each of the eleven study areas. These results are listed below.

- Established a promulgation strategy through phased releases and design-system structure

- Conceptually linked test-beds, RASSP design-system and industry resources

- Determined team structure, expertise required, and sources of support

- Defined aspects of design methodology to support MODEL YEAR concept

- Developed S/W and H/W interoperability solution sets to support management of MODEL YEAR upgrades

- Developed RASSP design-system concept --Framework, tools, standards

- Unique design-system features --Visualization, electronic data books, early assessment

- Strategy for test which reduces all costs over product life cycle

- Conceptual integration of RASSP, ASEM, DICE, PAP-E, and commercial industry

- Structured plan for integration of multi discipline data using standards

- Target system selection driven by growth and volatility of threat

# 2.0.5 Important Findings and Conclusions

Significantly, the commercial and military industries are enthusiastically in support of a major RASSP initiative. This philosophical alliance has many forces: product affordability, time to market or rapid response, open architectures, standards, logistics and a growing evidence of the importance of co-developments

or shared resources. The need to start immediately was evident. The initiative would establish the urgency and focus necessary to attain the standards (e.g., VHDL, CALS, CFI, etc.) which will promote increased industry investment in the tools, methodology and equipment necessary to meet the market places need for a RASSP development process.

In many application areas, the requirements for quickly providing state-of-the-art processing throughput at affordable life cycle costs have outgrown the last generation development paradigm. Two areas covered in some detail in this report are: Automatic Target Recognition and EW processors. Desert Storm experience was reviewed in these areas; the demands of fast response and advanced algorithms were much in evidence.

The systems front ends of CAD systems are lacking today and demand well thought out techniques for high level simulation, requirement traceability and early assessment tools supported with advanced visualization techniques. A RASSP program can get this effort started on the right track with a good standard foundation and on integration of the most promising available tools. A longer range development road map in this area is also important. It has become apparent that expertise and resources are available but highly diverse. The management of a successful RASSP program must address this complexity, provide guidance, selective funding and intense coordination. Universities, national laboratories, service laboratories, system houses, major and minor CAD/CAM/CAT/CASE vendors, manufacturing contractors, and standards organizations are all part of this resource base. It is a national effort that must involve all willing participants.

# 2.0.6 Significant Hardware Development

Raytheon did not develop any hardware under the RASSP Study Phase contract. Raytheon's efforts consisted of literature searches, discussions with industry leaders, and development of documentation.

### 2.0.7 Special Comments

Comments pertaining to the eleven study tasks are found within Sections 3.1 to 3.11.

# 2.0.8 Implications for Further Research

Where appropriate, implications for further research were highlighted within Sections 3.1 through 3.11.

#### 3.0 Detailed Study Phase Reports

During the RASSP Study Phase, the Raytheon team researched applicable CAE tools and methods (commercially available, advanced research, and applicable DoD initiatives). These are presented in section 3.1 of this report. Included with the list of tools is an overview of the functionality and input and output mechanisms. Some of the tools are compatible with the use of standards (for input modeling and use of libraries) within the current tools.

One of our major concerns resulting from the investigations was the successful industry integration through promulgation of the design system.

To realize RASSP goals, the block-one RASSP Design System will take advantage of existing tools and methods that make integration easier. Early proof-of-principle can be completed within the first year of the RASSP program. The following are important criteria that should be followed when choosing CAE tools to integrate into this first design system.

- Functionality

- Use of modeling standards (VHDL, Ada, Verilog, etc.) for input and output mechanisms

- Integration of CAE tool with standard libraries for COTS parts

- Ease of Use

- Open architecture

- Link to other CAE tools

A particularly strong effort will be made to incorporate system engineering tools. Functional descriptions of system engineering tools are available in section 3.1 of this report. Tools are well established in areas such as software, hardware, and physical design. These tools are well integrated, and take advantage of current modeling standards and libraries. Currently, these tools conform to one or more of the criteria described above and therefore can be integrated successfully into the block-one RASSP Design System within the first year of the program. However, in order to meet long-term RASSP goals, many other design system elements are important. Each of these elements is explained in Section 3.1.

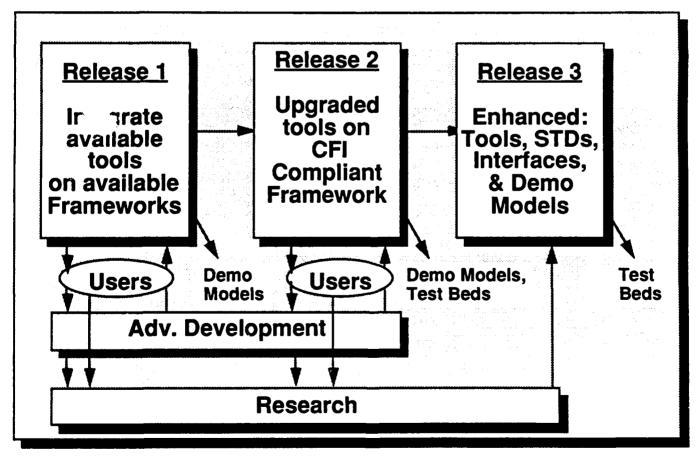

Promulgation of the RASSP design-system and its associated product data models can be attained by providing the user community with access and involvement during the RASSP Implementation Phase. Access and involvement are key program elements in attaining the goal of widespread acceptance and use. Access to an operable system throughout the course of the development allows hands-on evaluation that benefits both the RASSP contractor and the industry user. Most major DoD contractors and commercial system houses invest each year in tool evaluation and in decisions to upgrade their CAE resources. If the program plan incorporates a phased development where sequential block releases of systems (block 1, 2, 3) are made available to industry at no cost, then the opportunities for interest, use and comments from the user community are greatly enhanced.

Block 1, 2, and 3 of the design system must make sense to the RASSP program and to the user community. Block 1 would result from the integration of available tools placed on available frameworks (Mentor, Cadence, Compass). Tools and standards would be strongly based on VHDL in its latest form(s). Block 2 would take advantage of on-going initiatives in commercial CAE, RASSP funded advanced development, DICE, MADE, MANTECH -- that fit the timeline. Full CFI standards would tie the system together. Block 3 would be the RASSP design system and incorporate suitable results of research activity and lessons learned from block 1 and 2. Raytheon anticipates that the user community would be proactive in their evaluation and perhaps propose additional projects for contract consideration. Maturing university research would also be transitioned into the block 3 system. Block 3 is obviously the

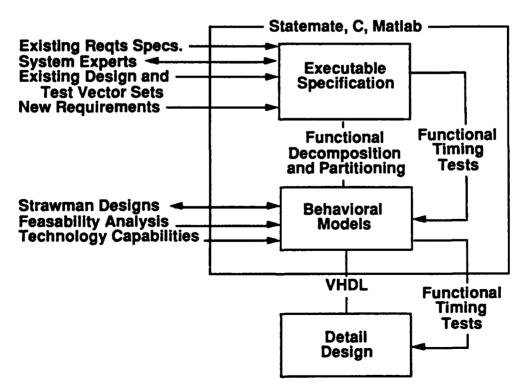

commercialization baseline with the justifying econometrics being provided by increased user activity and system driven demonstrations. Figure 3.0-1 is a pictorial of this phased development. Block 1 provides a baseline. Block 2 resolves many of the issues related to the current technology. Block 3 addresses evolving technology and attempts to avoid the "generation gap" that often exists between mature/highly efficient CAE and the advanced hardware technology it addresses. An example of the last issue might be the CAE necessary to manage the "power and parasitics" of several hundred megacycle component interconnections.

Another example might be the ability to use assessment tools within a framework when "look-ahead" ad hoc CAE design/analysis tools are used for next generation product models (next model year interoperability issues). There are many exciting possibilities that will come from research of design systems, languages, and system test bed interfaces which can be placed within the Block 3 framework and be allowed to mature even beyond the RASSP contract.

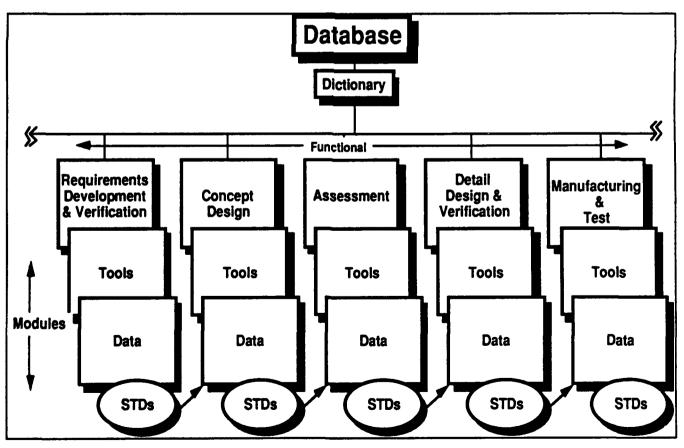

Involvement requires a system of selectable assets for use by the industry. Figure 3.0-2 highlights the idea of a multi-dimensional design system structure. Essentially, the structure can be viewed as partitioned (perhaps virtually) into "functions" represented horizontally. Vertically, each function has a tool set, data types and standards that are not necessarily exclusive to the particular functional domain. The advantages of this structure are several. The military systems house, the commercial systems house, or the commercial CAE vendor can gain access to a particular segment of interest without resorting to a complete resource commitment. For example,

Figure 3.0-1, Phased Development Of The RASSP Design System

a commercial CAE developer may find an increasing market for assessment tools and decide to focus their investment strategy in this area. Many other combinations of business and development situations can be envisioned. The system's structural focus on standards and the way in which functions, tools, libraries, manufacturing resources and test bed interfaces communicate throughout the design process provides an excellent environment for evaluation of upgrades, and additional language constructs and translators. This data is also made available through networked bulletin boards to the user community for comment and to the standards committees for consideration and potential action.

To meet program objectives RASSP products will rely heavily on ASICs and MCMs to realize the upgradability of the model year approach. Design agencies will need to have access to ASIC and MCM suppliers, and will demand flexibility

in how the interface is executed. While the ASIC industry is fairly well established, the MCM industry is in its infancy. Access to Application Specific Electronic Modules (ASEM) foundries will be facilitated by common electronic data exchange and an electronic brokering system. The ASEM brokering service would provide a mechanism for managing the acquisition of ASEMs through multiple suppliers. The broker manages the relationships with IC and MCM This reduces the number of suppliers. relationships to be managed by the design organizations. The broker would be responsible for qualifying suppliers, understanding vendor capabilities and particular areas of expertise, and responding to customer needs.

Figure 3.0-2, Multidimensional Design-System Structure

### 3.1 Design and Design-System Requirements

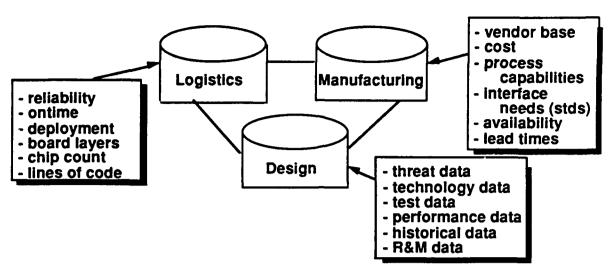

An important element of the RASSP program is the RASSP Design System. The design system provides a support environment in which RASSP designers can assess the cost, risk and benefit of design upgrades early in the design cycle and provides a seamless environment for designing the present model year system. Given the RASSP model year concept, the designer needs to design today with look-ahead knowledge for two to three model years. The assessment criteria takes into account design information (such as the latest or next generation packaging technology or signal processing algorithm, etc.) but also takes into account manufacturing information (such as supplier capabilities current and future, costs, lead time, etc.) and logistics information (such as field test equipment, spares, etc.). All of this data, if presented early enough, provides a good baseline for determining the feasibility of the upgrade prior to doing any detailed design or manufacturing.

This section of the final report is organized as follows:

- Study Phase Accomplishments

- Overview of the RASSP Design System Architecture Concept

- Detailed description for each element of the RASSP Design System Architecture Concept

- RASSP Design System interface to the CALS delivery standards

- Major Issues to be addressed during development of the RASSP Design System

- Relevant Raytheon related efforts

# 3.1.1 Study Phase Accomplishments

As a result of the RASSP study contract, a concept was developed for a system design environment which improves the design

capabilities available to the designer early in the design cycle and allows for the assessment of the impact of implementation architecture and technology on a system.

One of the key concepts is the development of an environment that has access to design. manufacturing and logistics engineering estimate and historical data. Access to historical logistics data allows the designer to assess design tradeoffs based on historical support data and allows the designer to address historical support problems in the updated design. For new designs, historical data may not be available. For these cases, engineering estimates can be derived based on similar systems in the field or through theoretical models. Historical and estimated manufacturing data is also beneficial early in the design cycle. This information allows the designer to address prior manufacturability problems as the design is updated, as well as assessing the manufacturability of the design, available manufacturers, and the projected manufacturing cost.

A major portion of this phase was a study of the current state-of-the-art and advanced research in CAE tools and methodologies. The team assessed the applicability of integrating CAE tools from the current commercial CAE industry. Additionally, applicable advanced research currently underway at universities or through funded DoD initiatives was reviewed to fill in functional holes or incomplete solutions in the design system. Included in this report is a set of detailed matrices that outline various CAE tools available commercially or through advanced research avenues. Table 3.1-1 summarizes the basic design activities surveyed under the RASSP Study. Although there are tools for every activity of the design process listed, the utility of the tools is limited since they are not well integrated. Many have their own specialized data representation, and data entry means. In addition, some tools do not easily lend themselves to use by designers due to the knowledge required to operate them effectively.

The key issues in the development and integration of tools under RASSP is the development and integration of the tools via standards, the development of a consistent means of invoking and interacting with the tools, and the ability to generate standard interchange formats to meet CALS deliverable requirements.

| Design Activities                |

|----------------------------------|

| Requirements Design and Analysis |

| Concept Design and Analysis      |

| Software Design and Analysis     |

| Hardware Design and Analysis     |

| Physical Design and Verification |

| Test Generation                  |

| Documentation                    |

#### TABLE 3.1-1, RASSP DESIGN ACTIVITIES

As part of the investigation of CAD design tools, a number of standards were investigated. The number of standards which impact CAD tools is large. They include the CFI standards for tool integration, the EDIF standards for data exchange, and standard languages for design and simulation (e.g. VHDL). However, additional standards must be considered to allow a consistent user interface, and the development of portable software. These standards are listed in Table 3.1-2. Any RASSP funded software should be consistent with these standards, as well as CFI and IEEE standards, to assure the implementation will not be obsolete in the near term, and that the software will be easily ported to new platforms in the rapidly changing workstation and PC marketplace. Knowledge of the above mentioned standards are key to the development of a seamless design environment that is usable, extensible, supportable and portable.

As previously indicated, standards are an important technology for RASSP. We have evaluated some of the key standards such as VHDL and CFI to understand their implications. A major concern to the RASSP project is the length of time required to issue and update standards. As an example, VHDL is currently undergoing a revision, however, analog issues are not being considered for the 1992 release, which means they will not be available until the year 1997 at the earliest, since IEEE standards are reviewed on a 5 year basis. In other areas such as CFI, the initial standards will be voted on in 1992, however, additional standards as well as updates to the standards will be required to support RASSP. It is not clear that large funding will greatly increase the speed of the standards work, or the development of standards where none exist today. The adoption of standards is voted on by representatives of commercial firms. DoD contractors, universities and the DoD. It is important, therefore, to identify standards work that is of importance to RASSP and to influence voting representatives to push strongly for those standards. One manner of doing this is through RASSP implementation phase teaming arrangements with voting CAD members.

| Standard<br>Organization | Name of<br>Standard | Area of Applicability                                            |

|--------------------------|---------------------|------------------------------------------------------------------|

| IEEE                     | POSIX               | Software standards to assure portability                         |

| ANSI                     | Various             | Computer languages, graphics standards, and networking standards |

| OSF                      | OSF/DCE             | Interoperability standard                                        |

| OSF                      | OSF/Motif           | Graphical user interface standard                                |

| UI                       | UNIX                | Interoperability standards                                       |

| X Consortium             | X Windows           | Protocol for base level graphics                                 |

TABLE 3.1-2, SOFTWARE DESIGN STANDARDS

Additionally, the RASSP Design System will be incrementally upgraded and made available for evaluation three times throughout the implementation phase thereby giving non-team members a view of the product and the direction that CFI should head.

A key consideration in the proposed RASSP contract will be the split of funding between the development and enhancements of tools, versus the integration of tools via standards. A mixture of each activity is required, however, it is important to look at the benefits to be derived from improved synthesis and assessment tools for the system designer versus improve ease of use of currently used tools at the logic and physical design stages. Areas which are ready exploitation include: executable for specifications, requirements flow down, automatic system partitioning into commercially available parts, availability of models for design, manufacturing and logistics information, improved insertion of testability at all levels of the design, and improve manufacturability analysis prior to release to manufacturing. For RASSP to be successful, a careful funding tradeoff must be performed between integration via standards which is occurring today without RASSP funding, and the acceleration of the

development of tools which are non-existent or in the prototype stage today.

Some of the technical challenges for improving the CAD tools above are being addressed in a number of DOD and DARPA initiatives. These initiatives include DICE, MADE, VTEST, etc. These programs should be leveraged by RASSP to eliminate duplicate funding and use RASSP funds to address needs not met. Table 3.1-3 lists a sample of the on-going and proposed efforts which should be monitored for inclusion in the RASSP program.

# **3.1.2** Overview of the Design System Concept

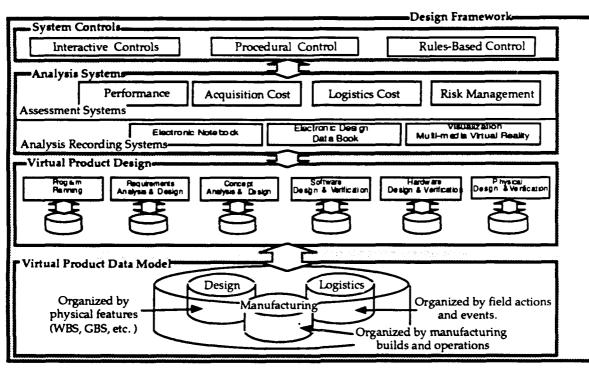

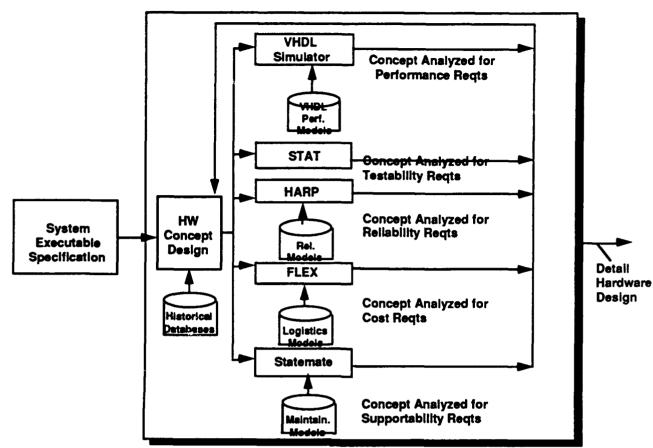

Figure 3.1-4 depicts the RASSP Design System architecture concept developed under the study phase contract. The concurrent engineering system provides a design, analysis, assessment and documentation environment for hardware and software codesign.

The design system will be implemented using commercial framework tools such as Mentor's Falcon framework and Cadence's Framework. It will be developed using the framework standards for tool and data integration and communication as defined by CFI. CAE tools will be encapsulated and integrated into the design

| Program Name                                          | Objective                                                                                                              |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| DICE (DARPA)                                          | Development and demonstration of enabling<br>technologies for concurrent engineering                                   |

| Simulatable Specifications<br>(Wright Laboratories)   | Develop guidelines/ methodologies and CAD tools<br>to support the use and integration of simulatable<br>specifications |

| PAP-E (Wright<br>Laboratories)                        | PDES Application Protocols for electronics                                                                             |

| VTEST (Wright<br>Laboratories)                        | Development of a virtual test environment to<br>support multiple testers                                               |

| QUEST (DARPA)                                         | Advanced CAD algorithms for VHDL-based parallel processing                                                             |

| Multi-Component<br>Synthesis (Wright<br>Laboratories) | Extend high-level partitioning and synthesis algorithms and tools for multi-component devices                          |

TABLE 3.1-3, DARPA AND DOD PROGRAMS OF INTEREST TORASSP

Figure 3.1-4, RASSP Design System Architecture Concept

framework. There are four main elements of the system:

- 1. Design System Framework (discussed in section 3.1.2.1)

- 2. Analysis Recording and Assessment Tools (discussed in sections 3.1.2.2.x)

- 3. Concurrent Engineering Product Design Tools (discussed in section (3.1.2.3)

- Product Data Models that support the design system (discussed in sections 3.1.2.2.x)

Each of the four parts of the design system will be discussed in more detail throughout the remainder of section 3.1.2.

#### 3.1.2.1 Design System Framework