IIII AGARD-AG- 160 Vol.19

ADVISORY GROUP FOR ERCOMACE RESEARCH & DEVELOPMENT 7 RUE ANCELLE 92200 NEUILLY SUR SEINE FRANCE

#### AGARDograph 160 Flight Past Instrumentation Series - Volume 19

## Digital Signal Conditioning for Flight Test

(Le Traitement du Signal Numérique pour les Essais en Vol)

ed attraction of GCAR without A Atmosfied by periods and any Online period

10.00

125

ALA V

NORTH ATLANTIC TREATY ORGANIZATION

Distribution and Availability on Back Cover

$\langle \rangle$

()

The Mission of AGARD

According to its Charter, the mission of AGARD is to bring together the leading personalities of the NATO nations in the fields of science and technology relating to aerospace for the following purposes:

- Recommending effective ways for the member nations to use their research and development capabilities for the common benefit of the NATO community;

- Providing scientific and technical advice and assistance to the Military Committee in the field of aerospace research and development (with particular regard to its military application);

- Continuously stimulating advances in the aerospace sciences relevant to strengthening the common defence posture;

- Improving the co-operation among member nations in aerospace research and development;

- Exchange of scientific and technical information;

- Providing assistance to member nations for the purpose of increasing their scientific and technical potential;

- Rendering scientific and technical assistance, as requested, to other NATO bodies and to member nations in connection with research and development problems in the aerospace field.

The highest authority within AGARD is the National Delegates Board consisting of officially appointed senior representatives from each member nation. The mission of AGARD is carried out through the Panels which are composed of experts appointed by the National Delegates, the Consultant and Exchange Programme and the Aerospace Applications Studies Programme. The results of AGARD work are reported to the member nations and the NATO Authorities through the AGARD series of publications of which this is one.

Participation in AGARD activities is by invitation only and is normally limited to citizens of the NATO nations.

The content of this publication has been reproduced directly from material supplied by AGARD or the authors.

Published June 1991

Copyright © AGARD 1991 All Rights Reserved

ISBN 92-835-0621-9

Printed by Specialised Printing Services Limitea 40 Chigwell Lane, Loughton, Essex IG10 3TZ

### Preface

Since its founding in 1952, the Advisory Group for Aerospace Research and Development has published, through the Flight Mechanics Panel, a number of standard texts in the field of flight testing. The original Flight Test Manual was published in the years 1954 to 1956. The Manual was divided into four volumes:

- 1 Performance

- 2 Stability and Control

- 3 Instrumentation Catalog, and

- 4 Instrumentation Systems.

As a result of developments in the field of flight test instrumentation, the Flight Test Instrumentation Group of the Flight Mechanics Panel was established in 1968 to update Volumes 3 and 4 of the Flight Test Manual by the publication of the Flight Test Instrumentation Series, AGARDograph 160. In its published volumes AGARDograph 160 has covered recent developments in flight test instrumentation.

In 1978, the Flight Mechanics Panel decided that further specialist monographs should be published covering aspects of Volume 1 and 2 of the original Flight Test Manual, including the flight testing of aircraft systems. In March 1981, the Flight Test Techniques Group was established to carry out this task. The monographs of this Series (with the exception of AG 237 which was separately numbered) are being published as individually numbered volumes of AGARDograph 300.

At the end of each volume of both AGARDograph 160 and AGARDograph 300 two general Annexes are printed. Annex 1 provides a list of volumes published in the Flight Test Instrumentation Series and in the Flight Test Techniques Series. Annex 2 contains a list of handbooks that are available on a variety of flight test subjects, not necessarily related to the contents of the volume concerned.

The present Volume (No. 19 of AGARDograph 160) provides flight test instrumentation engineers with an introduction to digital processes on aircraft. Flight test instrumentation systems are rapidly evolving from analog intensive to digital intensive systems, including the use of onboard digital computers. Topics include: measurements that are digital in origin, sampling, encoding, transmitting, and storing of data. Particular emphasis is placed on modern avionic data bus architectures and what to be aware of when extracting data from them. Some example data extraction techniques are given. Tradeoffs between digital logic families, trends in digital development, and design testing techniques are discussed. An introduction to digital filtering is also covered.

## **Préface**

Depuis sa création en 1952, le Panei de la Mécanique du vol, sous l'égide du Groupe Consultatif pour la Recherche et les Réalisations Aérospatiales a publié, un certain nombre de textes qui font autorité dans le domaine des essais en vol. Le Manuel des Essais en Vol a été publié pour la première fois dans les années 1954—1956. Il comportait quatre volumes à savoir:

- 1 Performances

- 2 Stabilité et Contrôle

- 3 Catalogue des appareils de mesure, et

- Systèmes de mesure.

Les novations dans le domaine des appareils de mesure pour les essais en vol, ont conduit à recréer, en 1968, le groupe de travail sur les appareils de mesure pour les essais en vol pour permettre la remise à jour des volumes 3 et 4. Les travaux du groupe ont débouché sur l'édition d'une série de publications sur les appareils de mésure pour les essais en vol, l'AGARDographie 160. Les différents volumes de l'AGARDographie 160 publiés jusqu'à ce jour couvrent les derniers développements dans le domaine.

En 1978, le Panel de la Mécanique du vol a signalé l'intérêt de monographies supplémentaires sur certains aspects des volumes 1 et 2 du Manuel initial et notamment les essais en vol des systèmes avioniques. Ainsi, au mois de mars 1981, le groupe de travail sur les techniques des essais en vol a été recrée pour mener à bien cette tâche. Les monographies dans cette série (à l'exception de la AG 237 qui fait partie d'une série distincte) sont publiées sous forme des volumes individuels de l'AGARDographie 300.

A la fin de chacun des volumes de l'AGARDographie 160 et de l'AGARDographie 300 figurent deux annexes générales. L'annexe 1 fournit la liste des volumes publiés dans la série "Appareils de mesure pour les essais en vol" et dans le série "Techniques des essais en vol". L'annexe 2 donne la liste des manuels disponibles sur les mêmes thèmes dans le domaine des essais en vol, qui ne sont pas forcément en rapport avec le contenu du volume en question.

Ce volume 19 de l'AGARDographie 160 offre aux ingénieurs d'instrumentation des essais en vol une introduction au traitement numérique de bord.

Les systèmes d'instrumentation pour essais en vol, analogues jusqu'ici, sont en train d'évoluer très rapidement vers des systèmes numériques, qui intègrent des ordinateurs numériques de bord. Parmi les sujets examinés on distingue:

- les mesures d'origine numérique

- l'échantillonnage,

- --- le codage,

ويتجربوه ومساويته

- la transmission,

- ie stockage des données.

L'accent est mis en particulier sur les architectures modernes de bus de données avioniques et les consignes à donner à l'utilisateur qui veut en extraire des données. Quelques exemples de techniques d'extraction de données sont fournis. Les compris envisageables entre les différentes familles de logique numérique, les tendances en ce qui concerne les développements numériques et les techniques d'essais de prototypes y sont discutées, avec une introduction au filtrage numérique.

## Acknowledgement to Working Group 11 Members

In the preparation of the present volume the members of the Flight Test Techniques Group listed below took an active part. AGARD has been most fortunate in finding these competent people willing to contribute their knowledge and time in the preparation of this volume.

La liste des membres du groupe de travail sur les techniques des essais en vol ont participé activement à la rédaction de ce volume figure ci-dessous. L'AGARD peut être fier que ces personnes compétentes aient bien voulu accepter de partager leurs connaissances et aient consacré le temps nécessaire à l'élaboration de ce document.

Appleford, J.K. Bogue, R.K. (Editor) Boischot, M. Bothe, H. Campos, L.M.B. Delle Chiaie, S. Langdon, G. Fayze, T. Pool, A. (Consultant) Russell, R.A. van der Velde, R.L. Zundel, Y. A&AEE/UK NASA/US CEV/FR DLR/GE IST/PO DASRS/TT A&AEE/UK MSB/TU NE NATC/US NLR/NE CEV/FR

R.R.HILDEBRAND, AFFTC/US Member, Flight Mechanics Panel Chairman, Flight Test Techniques Group

# (1997) A **Contents** and

**...**. .

•

•

,

:

The The second by the

.

•

1

Page

# and the first of the second second

| Prelace                                                                      | iv         |

|------------------------------------------------------------------------------|------------|

| Prélace                                                                      |            |

| Acknowledgement to Working Group 11 Members                                  | ¥          |

| Summary                                                                      | 0-1        |

| Objective                                                                    | 0-1        |

| Nometiclature                                                                | 0-1        |

|                                                                              | 1-1        |

| 1 Introduction<br>1.1 Definitions                                            | 1-1        |

| 1.2 Sampling in the Analog World                                             | 1-2        |

| 1 2 1 Common Examples                                                        | 1-2        |

| 1.2.2 Effects and Pitfalls (Problem Areas)                                   | 1-3<br>1-3 |

| 1.3 Tradeoff Considerations                                                  | 1-3        |

| 2 Digital Processes in Flight Testing                                        | 2-1        |

| 2.1 Avionics Systems                                                         | 2-1        |

| 2.2 Data Acquisition Systems                                                 | 2-1        |

| 2.3 Signal Processing-Conditioning                                           | 2-1<br>2-1 |

| 2.4 Hardware Considerations                                                  | 2-1        |

| 2.4.1 Technology                                                             | 2-2        |

| 2.4.1.1 Bipolar Logic                                                        | 2-2        |

| 2.4.1.2 Emitter-Coupled Logic                                                | 2-3        |

| 2.4.1.3 CMOS Logic                                                           | 2-3        |

| 2.4.1.4 Logic Families Compared                                              | 2-5        |

| 2.4.1.5 Problem Areas                                                        | 2-5        |

| 2.4.1.6 Programmable Logic Devices                                           | 2-6        |

| 2.4.1.7 Hybrid Circuits<br>2.4.2 Environment Considerations                  | 2-6        |

| 2.4.3 Architecture                                                           | 2-6        |

| 2.4.5 Architecture<br>2.5 Software Considerations                            | 2-7        |

| 2.5.1 Languages                                                              | 2-7        |

| 2.5.2 Software Development                                                   | 2-8        |

| e tuite to Pitatini Interface                                                | 3-1        |

| 3 Analog-to-Digital Interface<br>3.1 Analog-to-Digital Conversion Techniques | 3-1        |

| 3.1.1 Successive Approximation                                               | 3-1        |

| 3.1.2 Integration                                                            | 3-1        |

| 3.1.3 Multiple Comparator (Flash) Converter                                  | 3-2        |

| 3.1.4 Tracking Converter                                                     | 3-3<br>3-4 |

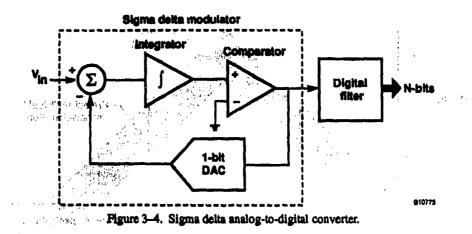

| 3.1.5 Sigma Delta Converter                                                  | 3-4<br>3-5 |

| 3.2 Divital-to-Analog Conversion Techniques                                  | 3-5        |

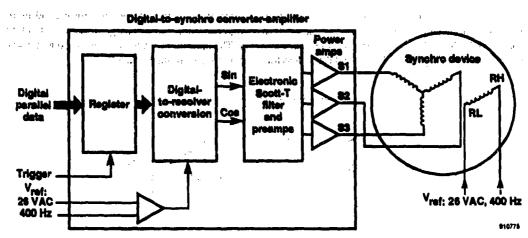

| 3 3 Digital-to-Synchro Conversion Techniques                                 | 3-7        |

| 3.4 Synchro-to-Digital Conversion Techniques                                 | 3-7        |

| 3.5 Conversion Process Considerations                                        | 3-7        |

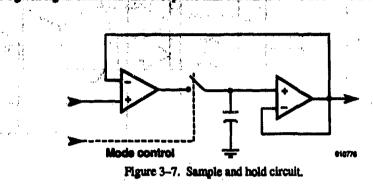

| 3.5.1 Sample and Hold                                                        | 3-8        |

| 3.5.2 Presample Filtering                                                    | 3-8        |

| 3.5.3 Antialiasing Filtering                                                 | 3-10       |

| 3.6 Process Error Sources                                                    |            |

. . . . . . .

vì

• •

|   | -9 · 1                                                                   | Page         |

|---|--------------------------------------------------------------------------|--------------|

| 4 | Digital Transducers                                                      | 4-1          |

|   | 4.1 Transduction Techniques                                              | 4-1          |

|   | 4.1.1 Coded Disks                                                        | 4-1          |

|   | 4.1.2 Variable Frequency                                                 | 4-2          |

|   | 4.1.3 Pulse Techniques                                                   | 4-2<br>4-2   |

|   | 4.2 Coding<br>4.2.1 Progressive Codes                                    | 4-2          |

|   | 4.2.1 Nonprogressive Codes (Gray)                                        | 4-3          |

| 5 | Digital Filtering                                                        | 5-1          |

|   | 5.1 Applications and Guidelines                                          | 5-1          |

|   | 5.2 Time Domain Filters                                                  | 5-1          |

|   | 5.2.1 Nonrecursive Filters                                               | 5-2          |

|   | 5.2.2 Recursive Filters                                                  | 5-2<br>5-2   |

|   | 5.2.3 Switched Capacitor Filters<br>5.3 Statistical Filtering            | 5-4          |

|   | 5.4 Data Compression Filtering                                           | 5-4          |

|   | 5.5 Pitfalls (Problem Areas) of Digital Filtering                        | 5-4          |

| 6 | Digital Communication                                                    | 6-1          |

|   | 6.1 Technology Choices                                                   | 6-1          |

|   | 6.1.1 Copper Wire                                                        | 6-1          |

|   | 6.1.2 Fiber Optics                                                       | 6-1<br>6-2   |

|   | 6.1.3 Telemetry<br>6.2 Transmission Timing Choices                       | 6-2          |

|   | 6.2.1 Synchronous                                                        | 6-2          |

|   | 6.2.2 Asynchronous                                                       | 6-2          |

|   | 6.2.3 Isochronous                                                        | 6-3          |

|   | 6.3 Communication Format Choices                                         | 6-3          |

|   | 6.3.1 Serial Transfer                                                    | 6-3          |

|   | 6.3.2 Parallel Transfer                                                  | 6-3          |

|   | 6.4 Data Formats                                                         | 6-4          |

|   | 6.4.1 Timing and Synchronization<br>6.4.2 Error Detection and Correction | 6-4<br>6-4   |

|   | 6.4.2.1 Parity Bit                                                       | 6-4          |

|   | 6.4.2.2 Error Correction Code                                            | 6-5          |

|   | 6.4.2.3 Cyclic Redundancy Code                                           | 6-6          |

|   | 6.4.3 Data Packet Format                                                 | 6-6          |

|   | 6.5 Standard Avionics Data Buses                                         | 6-6          |

|   | 6.5.1 MIL-STD-1553/1773                                                  | 6-6          |

|   | 6.5.1.1 Terminal Types                                                   | 6-7          |

|   | 6.5.1.2 Data Bus Cable<br>6.5.1.3 Terminal Characteristics               | 6-8<br>6-9   |

|   | 6.5.1.4 Data Bus Operation                                               | 6-9          |

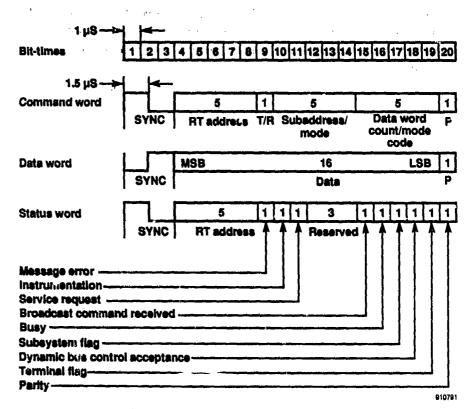

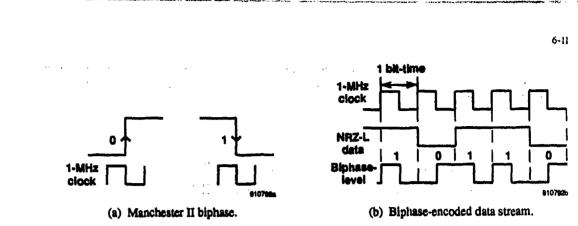

|   | 6.5.1.5 Word Types                                                       | 6-10         |

|   | 6.5.1.6 Word Formats                                                     | 6-10         |

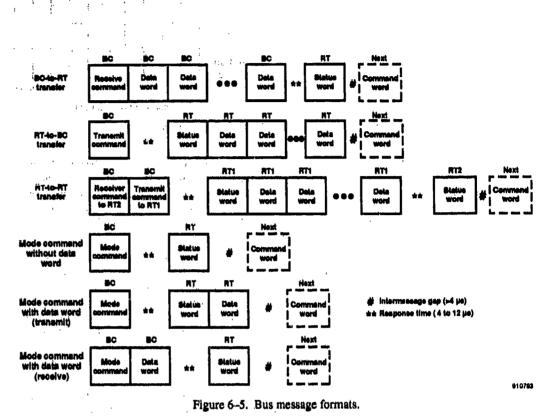

|   | 6.5.1.7 Bus Message Formats                                              | 6-11         |

|   | 6.5.1.8 MIL-STD-1553 Notices                                             | 6-13         |

|   | 6.5.1.9 Design Tips for MIL-STD-1553                                     | 6-13         |

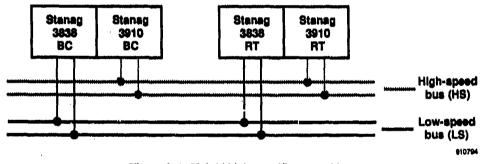

|   | 6.5.1.10 MIL-STD-1773 and STANAG                                         | 6-14         |

|   | 6.5.2 ARINC 419/429/629                                                  | 6-14         |

|   | 6.5.2.1 ARINC 419<br>6.5.2.2 ARINC 429                                   | 6-14<br>6-15 |

|   | 6.5.2.3 <b>ARINC 629</b> (DATAC)                                         | 6-19         |

|   | 6.5.3 H009                                                               | 6-20         |

|   | 6.6 General-Purpose Data Buses                                           | 6-21         |

|   | 6.6.1 RS-232/422/423/449                                                 | 6-21         |

|   | 6.6.2 IEEE 488/HP-IB/IEC 625                                             | 6-24         |

|   | 6.6.2.1 Bus Operation                                                    | 6-24         |

|   | 6.6.2.2 Bus Application and Limitations                                  | 6-25         |

|   | 6.6.3 Ethernet (IEEE 802.3)                                              | 6-25         |

|   |                                                                          |              |

Ì

÷

•

:

;

and the second second

. .

•

•

•

vi

**.....**

|     | Y.                                                        | Page             |

|-----|-----------------------------------------------------------|------------------|

|     | 6.7 Sampling Data Buses for PCM Transmission              | 6-26             |

|     | 6.8 Wave Shaping for Special Situations                   | 6-27             |

|     | 6.8.1 Pulse Trains for Telemetry Transmission             | 6-27             |

|     | 6.8.2 Pulse Trains for Tape Recording                     | 6-27             |

|     | 6.8.2.1 Filtering and Encoding Considerations             | 6-27             |

|     | 6.8.2.2 Enhancement Techniques                            | <del>ű</del> -28 |

| 7   | Digital Data Storage                                      | 7-1              |

|     | 7.1 Tape Recorders                                        | 7-1              |

|     | 7.2 Semiconductor Memory                                  | 7-1              |

|     | 7.2.1 Random Access Memory                                | 7-1              |

|     | 7.2.2 Electrically Erasable Programmable Read Only Memory | 7-2              |

|     | 7.3 Bubble Memory                                         | 7-2              |

|     | 7.4 Disks                                                 | 7-2              |

|     | 7.4.1 Magnetic (Hard and Flexible)                        | 7-2              |

|     | 7.4.2 Optical                                             | 7-3              |

|     | 7.4.3 Interfacing                                         | 7-3              |

| 8   | Testing                                                   | 8-1              |

|     | 8.1 Failure Modes and Mechanisms of Digital Systems       | 8-1              |

|     | 8.2 Hardware Test Methods                                 | 8-1              |

|     | 8.3 Software Test Methods                                 | 8-2              |

| 9   | Reliability and Safety                                    | 9-1              |

| -   | 9.1 Verification and Validation                           | 9-1              |

|     | 9.2 Flight-Critical System Data Extraction                | 9-1              |

| Rcí | ierences                                                  | R-1              |

| Ind | lex .                                                     | I-1              |

| An  | nexes                                                     | A-1              |

1.1.1.1.1.1.1.1

:

$Y \in \mathcal{V}$

تا مان المان المريكة المان المريكة الم المريكة ł

· . . .

#### DIGITAL SIGNAL CONDITIONING FOR FLIGHT TEST

0-1

Glenn A. Bever NASA Ames Research Center Dryden Flight Research Facility P.O. Box 273 Edwards, California 93523-0273 U.S.A.

#### SUMMARY

Flight test instrumentation systems are rapidly evolving from what was an all-analog technology into what will be an almost all-digital art. The development and widespread application of digital processes in data processing and reduction make it imperative that the advantages of the digital approach be exploited wherever appropriate in the flight test process. The areas of signal conditioning and data acquisition offer many opportunities to use digital techniques to achieve improved performance. For some time, digital techniques have seen much use in data acquisition systems. More recently, the use of digital computers in airborne systems has become commonplace, both in data acquisition systems and in the aircraft avionics and control systems. The computer brings an extensive capability for real-time processing to the onboard systems and, to realize its full potential, must be appropriately interfaced to the aircraft environment. Often, aircraft avionic digital systems contain data which are required for conducting the flight test. It becomes necessary to extract the data from the onboard systems for inclusion in the flight test database. For these reasons it is essential that the flight test instrumentation engineer understand digital signal conditioning techniques and be familiar with their applications.

#### **OBJECTIVE**

The objective of this volume is to provide the engineer with a limited theoretical basis, and with the necessary practical design information to permit the exploitation of the advances in the digital systems state of the art as applied to flight testing. Included in this objective is the use of digital techniques in strictly signal conditioning applications as well as interfacing and communication applications between various aircraft systems. Not included in this objective is the coverage of strictly computer-based systems information. This information is covered in computer society literature or in software professional society publications. These topics may be noted for consideration, but the reader is directed to other references for detailed subject coverage.

#### NOMENCLATURE

- AC alternating current or advanced CMOS

- ACT advanced CMOS TTL level

- A-D analog to digital

- ALS advanced low-power Schottky

- AM amplitude modulation

- AND logic "and" function

- ANSI American National Standards Institute

- ARINC Aeronautical Radio, Inc.

- ASCII American Standard Code for Information Interchange

| 0-2            |                                                                                            |

|----------------|--------------------------------------------------------------------------------------------|

| BC             | bus controller                                                                             |

| BCD            | binary-coded decimal                                                                       |

| BI <b>Φ-</b> L | Manchester II biphase-level                                                                |

| BM             | bus monitor                                                                                |

| BNR            | binary                                                                                     |

| CCITT          | The International Telegraph and Telephone Consultative Committee                           |

| CMOS           | complementary metal oxide semiconductor                                                    |

| CRC            | cyclic redundancy code                                                                     |

| D-A            | digital to analog                                                                          |

| DAC            | digital-to-analog converter                                                                |

| DATAC          | digital autonomous terminal access communication                                           |

| DC             | direct current                                                                             |

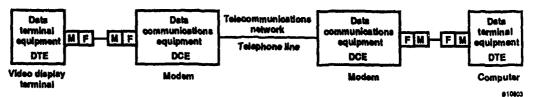

| DCE            | data communication equipment                                                               |

| DCTL           | direct-coupled-transistor logic                                                            |

| DEEC           | digital electronic engine control                                                          |

| DITS           | digital information transfer system                                                        |

| DM-M           | delay modulation-mark (Miller)                                                             |

| DoD            | Department of Defense (U.S.A.)                                                             |

| DTE            | data terminal equipment                                                                    |

| DTL.           | diode-transistor logic                                                                     |

| ECC            | errer correction code                                                                      |

| ECL            | emitter-coupled logic                                                                      |

| EEPROM         | electrically erasable programmable read-only memory<br>(also known as E <sup>2</sup> PROM) |

| EFA            | European fighter aircraft                                                                  |

| EMI            | electromagnetic interference                                                               |

| EPLD           | electrically programmable logic device                                                     |

| ESDI           | enhanced small device interface                                                            |

| ESD            | electrostatic discharge                                                                    |

| EU             | engineering units                                                                          |

| FAST           | Fairchild advanced Schottky TTL                                                            |

| FET            | field effect transistor                                                                    |

| FIFO           | first in, first out                                                                        |

| FIR            | finite impulse response                                                                    |

| FM             | frequency modulation                                                                       |

| FTI            | flight test instrumentation                                                                |

|                |                                                                                            |

.

| GP-IB   | general-purpose interface bus                          |

|---------|--------------------------------------------------------|

| HC      | high-speed CMOS                                        |

| нст     | high-speed CMOS TTL level                              |

| HP-IB   | Hewlett-Packard interface bus                          |

| IC      | integrated circuit (chip)                              |

| IEC     | International Electrotechnical Commission              |

| TREE    | Institute of Electrical and Electronic Engineers       |

| IIR.    | infinite impulse response                              |

| IRIG    | Inter-Range Instrumentation Group (U.S.A.)             |

| IRU     | inertial reference unit                                |

| ISC     | International Standards Organization                   |

| LS      | low-power Schottky                                     |

| LSB     | least significant bit                                  |

| lSD     | least significant digit                                |

| lsi     | large-scale integration                                |

| MIL-STD | military standard                                      |

| MODEM   | modulator-demodulator                                  |

| MOS     | metal oxide semiconductor                              |

| MSB     | most significant bit                                   |

| MSCP    | mass storage control protocol                          |

| MSD     | most significant digit                                 |

| NASA    | National Aeronautics and Space Administration (U.S.A.) |

| NRZ     | nonreturn to zero                                      |

| PAL.    | programmable array logic                               |

| PCM     | pulse-code modulation                                  |

| PLA     | programmable logic array                               |

| PLD     | programmable logic device                              |

| R       | resistance                                             |

| RAM     | random access memory                                   |

| RC      | resistance-capacitance                                 |

| RF      | radio frequency                                        |

| RH      | rotor reference high                                   |

| RL      | rotor reference low                                    |

| RMI     | radio magnetic indicator                               |

| RT      | remote terminal                                        |

| RTL     | resistor-transistor logic                              |

|         |                                                        |

5

· . • . `

0-3

- .

| 0-4   |                                       |

|-------|---------------------------------------|

| RZ    | return to zero                        |

| nns   | root mean square                      |

| rpm   | revolutions per minute                |

| rps   | revolutions per second                |

| SAE   | Society of Automotive Engineers       |

| SCSI  | small computer systems interface      |

| SDI   | source designation indicator          |

| SDLC  | synchronous deta link control         |

| SM    | status matrix                         |

| SSI   | small-scale integration               |

| SSM   | sign-status matrix                    |

| ST506 | Seagate disk interface standard       |

| 1/R   | transmit-receive                      |

| TTL   | transistor-transistor logic (bipolar) |

| UV    | ultraviolet                           |

| V     | volts                                 |

| VAC   | volts alternating current             |

| VDT   | video display terminal                |

| WORM  | write once, read many                 |

#### Symbols

| С           | capacitor                                           |

|-------------|-----------------------------------------------------|

| D           | digital output                                      |

| E           | electromotive force (voltage)                       |

| f           | frequency                                           |

| Ι           | current                                             |

| H           | matrix                                              |

| k, m, n     | variables                                           |

| P           | parity                                              |

|             |                                                     |

| Q           | charge                                              |

| Q<br>R      | charge<br>ratio                                     |

| •           | ÷                                                   |

| R           | ratio                                               |

| R<br>S      | ratio<br>signal                                     |

| R<br>S<br>T | ratio<br>signal<br>time between successive closings |

...

-1

, 1 .

;

۲. بند

٠.

and the second of the second s

| ave       | average                   |

|-----------|---------------------------|

| clk       | clock                     |

| G         | ground                    |

| H         | high                      |

| IH        | input high                |

| IL        | input low                 |

| in        | input                     |

| n         | variable                  |

| 0         | characteristic or nominal |

| ОН        | output high               |

| OL        | output low                |

| out       | output                    |

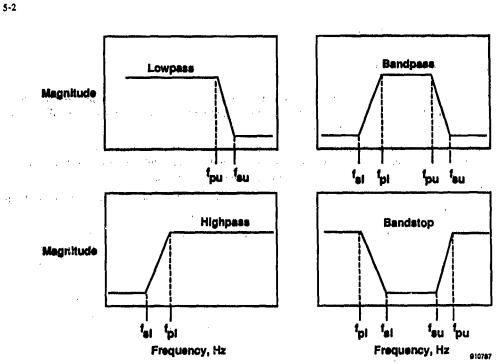

| pl        | passband lower            |

| ри        | passband upper            |

| ref       | reference                 |

| 8         | source                    |

| si        | stopband lower            |

| <b>su</b> | stopband upper            |

|           |                           |

0-5

#### **1 INTRODUCTION**

Traditionally, engineering disciplines surrounding flight test have been broken into several groups. Groups concerned with flight operations, flight control, aerodynamics, propulsion, and instrumentation existed with a great deal of autonomy. More recently, aircraft are being viewed and tested as a complete aircraft SYSTEM. The dividing lines between disciplines have become very indistinct. Information about fuel distribution may be input to control systems that adjust for center of gravity change. Digitally controlled propulsion systems may integrate their calculations with the flight control system. System designers require data from these systems to evaluate their performance or safety. Instrumentation engineers are taking advantage of sensors embedded into avionics packages rather than installing their own unique sensors.

More demanding requirements are driving aircraft systems to be more integrated. Many processes traditionally done on the ground are moving into aircraft systems. Improving digital electronic technology is making aircraft systems possible that were impossible just a few years ago. Optical technologies loom on the horizon. The rapid progress in the state of the art requires individuals charged with designing aircraft measuring systems to become better acquainted with new solutions to their requirements.

This volume is concerned with aircraft measuring systems as related to flight test and flight research. Measurements that are digital in origin or that must be digitized are discussed. Sampling, encoding, transmitting, and storing the data are dealt with. Examples of actual solutions to these problems will be given. This volume will provide an overview and introduction to the various areas of concern in modern aircraft digital measurement. Processes taking place on the aircraft rather than on the ground are emphasized.

There is no one right way to instrument an aircraft. Different organizations have different goals and requirements. An aircraft manufacturer has a different emphasis than an organization concerned with basic aerodynamic research. The manufacturer's primary concern is to validate the aircraft design and to prove its safety. While a military flight testing organization may be more concerned with gaining experience in a particular aircraft to write flight manuals, a flight research organization may be more concerned with measuring the airflow over a wing or doing precise wind calculations. Some organizations can design in the test instrumentation when the aircraft is built. Others are faced with the task of installing equipment in places that the designers never envisioned.

For example, designers of avionics systems in civil transport aircraft proceed from a rigid criteria for avionics box size and function. The designer of flight test instrumentation for fighter or small civil planes is more likely to use criteria "as small as is practicable" with a function uniquely defined by the flight test program.

The organizations' diverse missions, together with the natural tendency to continue with familiar approaches to problems and equipment, create a wide range of solutions to flight measurement problems.

#### **1.1 Definitions**

What parameters are measured in flight that are of concern to digital signal conditioning? Nearly all parameters in modern flight test eventually become digital. Even analog sensors are digitized for inclusion into databases at some point. Avious systems communicate by way of digital data buses. And increasingly, data is being digitally stored in memory, tape, and disk. The following basic terms found in this volume are defined.

A measurand is the physical quantity to be measured, such as temperature, pressure, or strain.

A transducer is a device that converts a measurand into another form of energy. For flight test instrumentation, this energy is typically electrical or optical.

Signal conditioning is necessary to convert a transducer output to a form required for input to a recorder, computer, or telemetry device.

**Digital signal conditioning is** defined as converting a transducer output signal to the digital domain and passing it to a recording, computing, or telemetry device. Conditioning or altering signals between different forms in the analog domain is not discussed in this volume. See reference 1 for a discussion of this topic.

#### 1.2 Sampling in the Analog World

1-2

The adage "to measure is to change" sums up the skill required to measure phenomena. The problem is twofold. First, probing a medium disturbs it. Second, no measuring device is perfect. Correct interpretation of how much the medium has been disturbed and how much error that contributes along with sensor imperfection is the key to correct interpretation of the results.

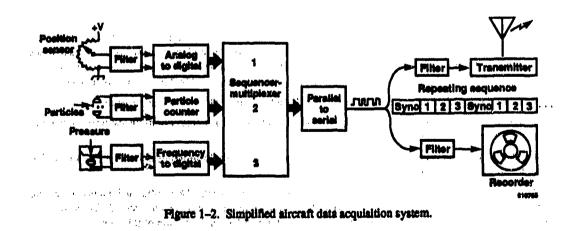

When a conversion is made, whether between human languages or between analog and digital, something is lost in the translation. It is a truism that because it has been changed, it is different. The advantage of handling data in the digital regime is that it is much less sensitive to further degradation than is a signal in the analog domain. Because a digital signal is passed as a two-state value, wide tolerances in the signal levels can be accepted and still retain the information (fig. 1-1(a)). However, most measurands of interest are more appropriately thought of as being in the analog domain (signal amplitude varies with time). Figure 1-1(b) shows a sample analog signal. Most measurands vary in small amounts, not large (digital) jumps. The problem, then, becomes one of translating analog phenomena into a digital signal while keeping introduced error to a known minimum.

#### 1.2.1 Common examples

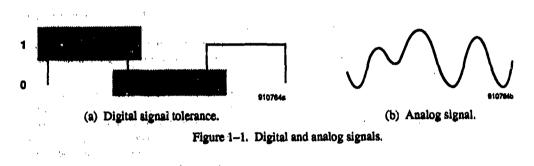

Figure 1-2 shows a typical aircraft data acquisition system. Data flow from the sensors to the recording mechanism. Note that regardless of the sensor type, the data become digitized for recording. There are many ways to send the data through the system. The method shown converts each of the inputs to a parallel digital word. The sequencer then multiplexes these digital words in a repeating sequence and sends each digital word out in serial. Synchronization words are added to assist data reconstruction later. This serial bit stream is finally recorded on tape and transmitted.

#### 1.2.2 Effects and pitfalls (problem areas)

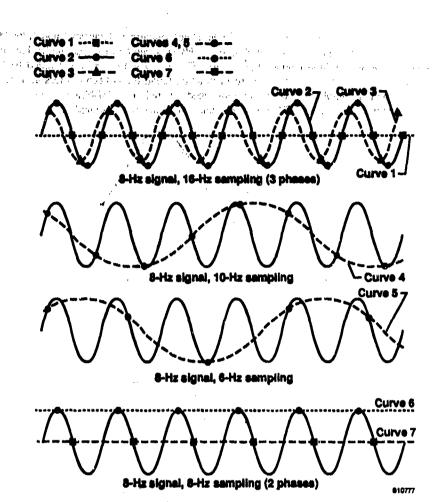

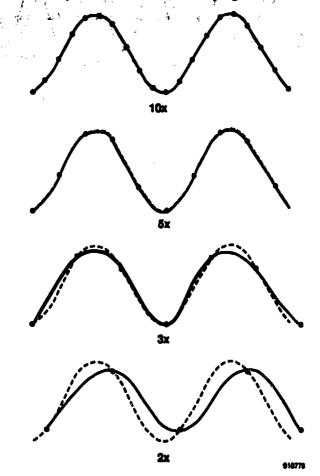

Sampling introduces its own problems. Sampling is looking at a signal at discrete moments in time. The more the signal is looked at, the more the sampling rate increases. In theory, as the sampling rate approaches infinity, the original signal is seen, with no error introduced in sampling. However, in reality the signal must be sampled less than infinitely often. Sampling circuit limitations, as well as limitations in ability to process, transmit, or record high data rates, force decisions about how fast the signal must be sampled. If the sampling rate is too low, important information can be lost. Sampling too high wastes bandwidth resources.

Consider an 8-Hz signal sampled only once. The reconstructed signal will look like a DC level whose amplitude is whatever the signal happened to be when it was sampled that one time. This is an extreme example of a phenomena known as aliasing and is discussed in section 3.5.3.

#### **1.3 Tradeoff Considerations**

While sampled data systems can lose important information if sampled too low, there are other factors that can lead to loss of data. Filtering techniques employed to assure that aliasing does not occur must be applied BE-FORE sampling (sec. 3.5.3). Electronic filtering cannot be used, for example, where scanning pressure transducers are used. The only antialiasing filtering that can be done here is in the mechanics of the pressure lines.

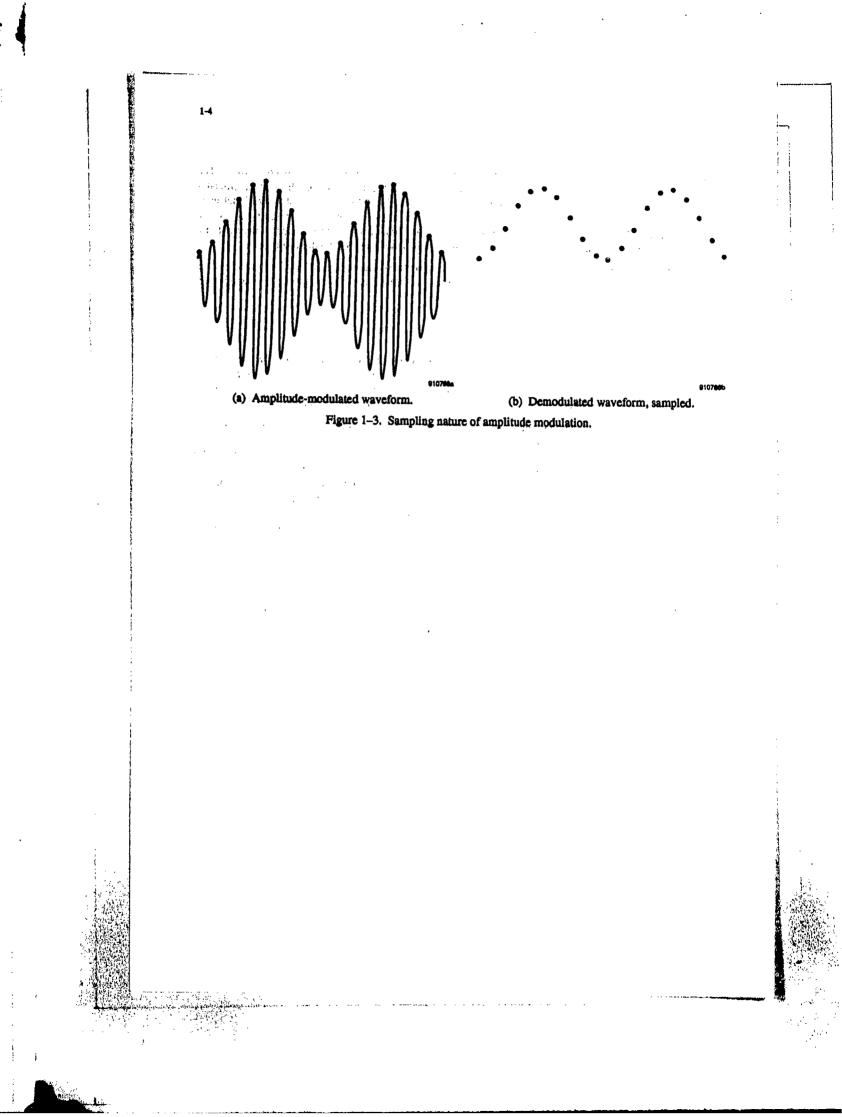

Techniques other than sampled, systems can be subject to the same deficiencies. Systems like FM recording---where an analog voluge modulates a frequency around a carrier center-are thought to be "continuous." However, an FM signal cannot be demodulated at one discrete point in time. It takes at least two points, usually two zero crossings, to determine the frequency AT that time. This implies that arbitrarily large input variations (continuous signals) cannot be supported because of the finite time it takes to demodulate a particular frequency. Instantaneous determination of frequency at infinite resolution is required to actually support a continuous analog input. This is analogous to saying that the system must have an infinite number of samples to be truly a continuous reading, which is impossible. Everything has a bandwidth, although some bandwidths are larger than others. Because the carrier is centered at a particular finite frequency and doesn't have an infinite modulation rate, the ability of the carrier to "carry" information could be exceeded.

Another example is an AM signal. Figure 1-3(a) shows a modulated carrier. To reconstruct the information, there is an interpolation connecting the dots shown broken out (fig. 1-3(b)). This process is identical to the process of reconstructing a sampled signal. If the carrier frequency is too low for the information it carries, there won't be enough dots to connect and still retain the information required and aliasing will take place.

#### 2 DIGITAL PROCESSES IN FLIGHT TESTING

#### 2.1 Avionics Systems

The word "avionics" is a contraction of the words "aviation" and "electronics," and it may include all electronic subsystems on an aircraft. In particular, avionics refers to those electronic subsystems that are directly concerned with flight control, weapon systems, navigation, and cockpit display. In most aircraft, these systems are part of the operational aircraft, and modifications to these systems are not regarded lightly. They are designed to exacting specifications, and packaged to facilitate easy replacement by nonexperts.

Avionics systems, as defined previously, are not the subject of this AGARDograph. See reference 2 for more information on avionics systems. However, because flight testing frequently requires their data, some avionic communication standards are discussed in section 6.

#### 2.2 Data Acquisition Systems

Flight testing requirements usually have different ground rules than avionics systems, as defined earlier. Easy replacement of data acquisition equipment is, of course, desirable. But more important is how flexible the system is, how easy it is to alter (to test other flight conditions), and how small it is. Data acquisition traditionally is open loop; that is, data are acquired and stored or transmitted for analysis, but not fed back into the aircraft to control it. A test display may be available to the pilot, but this is seldom a display certified for safe flight reference.

#### 2.3 Signal Processing-Conditioning

Referring back to figure 1-2, notice that three different types of sensors are shown. The position sensor, which may measure control surface position, is a potentiometer whose voltage output varies proportionally with wiper position. This analog output must be converted to a digital word. The particle sensor must convert individual particle detection to an aggregate total number of particles detected. The pressure sensor output is a frequency that is proportional to the pressure applied. This frequency must also be converted to a digital value for use in the data acquisition system.

Some sensors are regarded as "digital" sensors because the conversion to the digital domain (conditioning) is done at the sensor. For example, if the only output from the "sensor" box is digital, then it is transparent to the engineer using it that the pressure sensor is an element of a tuned circuit (the output of which is frequency).

Once the initial "conditioning" to the digital domain is done, then the data must be finally passed to some recording mechanism. This may mean that the data need to be further conditioned to ease their transfer. For instance, again referring to figure 1-2, the data are multiplexed, converted to serial (changing their condition again), and then perhaps filtered (further conditioned) for telemetry transmission or onboard recording. The data may be used onboard in computations for cockpit displays or data thinning. This type of signal processing is increasingly common. The conversions and filtering are performed on the digital data to ease their transfer and in no way alter the basic digital information content.

#### 2.4 Hardware Considerations

#### 2.4.1 Technology

Improvement of electronic technology has proceeded at an incredible rate. It is difficult to maintain an awareness, much less a proficiency, in every development that enters commercial production. Generally, an electronic designer working against a deadline will design with the familiar. Taking the time to learn the ins and

2-1

outs of a new technology is a luxury that frequently cannot be indulged in. Often new techniques must be used, particularly when requirements dictate lower power, higher speeds, and smaller package size than what can be provided with known techniques.

The design engineer often needs to have experience with new technology and techniques before recommending it. There are too many unknowns to make a firm commitment to schedule. Technique advancement then requires a far-sighted project manager or a risk-taking design engineer willing to spend long hours perfecting the understanding of the technique in question.

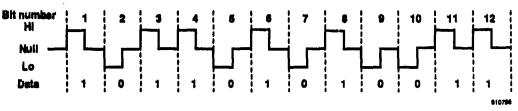

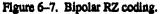

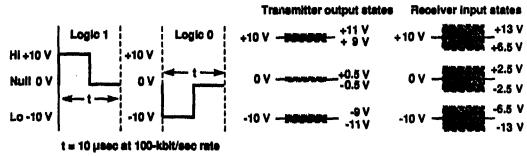

There are currently several technologies to choose from when selecting components to implement digital logic circuits. Details of these devices are found in manufacturers' data books (refs. 3 through 7). Reference 8 discusses technology family tradeoffs. The basic tradeoffs made in selecting a logic family are power consumption, gate speed, noise immunity, circuit density, output drive (far-out), cost, and reliability.

#### 2.4.1.1 Bipolar logic

This line of logic components is the first line of digital integrated circuits to come into commercial usage. The technique uses bipolar transistors. Historically, the order of development and usage was:

Direct-coupled-transistor logic (DCTL) Resistor-transistor logic (RTL) Diode-transistor logic (DTL) Transistor-transistor logic (TTL)

A DCTL device had poor noise immunity and high current consumption. An RTL device was low speed, and had poor noise immunity and low fan-out. A DTL device reduced power requirements, but at the expense of being slower. All of these technologies are obsolete and are not used in new designs.

The TTL devices have been by far the most popular logic family for nearly 20 years. This logic, or variations of it, can still be found in new designs, although its popularity is waning. It boasts higher noise immunity than its predecessors and is faster. Subfamilies of TTL have been introduced to improve various characteristics, like lower power consumption or higher speed. A commercial logic-integrated circuit (IC) is easily recognized by its prefix of 74. A military specification IC prefix is generally 54. The subfamilies follow the prefix with letters indicating the subfamily, as follows:

- AS Advanced Schottky

- ALS Advanced low-power Schottky

- H High speed (up to 50 MHz)

- L Low power (up to 3 MHz)

- LS Low-power Schottky (up to 45 MHz)

- S Schottky (up to 125 MHz)

Bipolar logic families are inherently current devices, because bipolar junction transistors are current driven. Therefore, output drive is limited to some finite number, usually stated in terms of how many logic *inputs* (in the same logic family) can be fed before the current demand moves the output voltage into the transition (indeterminate) region. This unit of drive capability is called the fan-out. Fan-out for TTL devices is usually around 10. Switching speeds are regarded as fast because of the use of transistors rather than passive resistor-capacitor coupling between most stages.

#### 2.4.1.2 Emitter-coupled logic

Emitter-coupled logic (ECL) is characterized by extremely high speeds, into the 1- to 2-GHz range. The tradeoff is that it also has high power consumption and low circuit density. The ECL operates in the active region of the transistor—which enhances its speed. The high power consumption and low circuit density limit its use on alrevant. It is seen primarily in mainframe computers.

2-2

#### 2.4.1.3 CMOS logic

Complementary metal oxide semiconductor (CMOS) logic circuits are voltage driven rather than current driven as bipolar circuits are. They are voltage driven because CMOS uses field effect transistors (FET's), which are voltage-driven devices. This is what allows for the low power consumption of CMOS devices. With a constant voltage and low current leakage, power dissipations in the microwatts can be achieved. Voltage-driven gates also allow for much larger fan-outs than can be achieved with bipolar devices.

CONTRACTOR CONTRACTOR

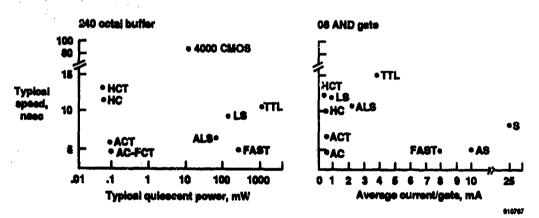

The CMOS device has existed for several years in the form of the 4000 series parts. It boasts high noise immunity and extremely low power consumption, which has made it popular for battery-operated equipment. However, 4000 series CMOS is very slow when compared with the bipolar logic families (fig. 2-1).

As technology has progressed, other CMOS logic families have been developed to be plug replaceable with existing bipolar logic families. For example, the 54HC/74HC family was designed to replace the 54LS/74LS bipolar family. It retains much of the bipolar speed but reduces the power consumption while improving noise immunity characteristic of CMOS. Later, the 54AC/74AC family was designed to replace the 54HC/74HC family while increasing the speed.

#### 2.4.1.4 Logic families compared

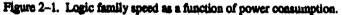

Table 2-1 shows a comparison of several logic families. The function chosen for comparison is a quad 2-input AND (four AND gates). The table is generally ordered from slowest to fastest logic part. Figure 2-2 shows the input and output current and voltage-naming conventions used in table 2-1. Figure 2-1 graphically illustrates the speed-power tradeoffs between logic families. Note that the AC and ACT logic families generally yield the best speed and the lowest quiescent power.

2-4

| Table. | 2-1 | Com | nerison | of lo | nic | familics. |

|--------|-----|-----|---------|-------|-----|-----------|

|        |     |     |         |       |     |           |

| Input      |     |             |           |            |            |            | Output    |              |           |          |               |               |             |                 |

|------------|-----|-------------|-----------|------------|------------|------------|-----------|--------------|-----------|----------|---------------|---------------|-------------|-----------------|

| Chip       | Y   | I.          | MAX       | V<br>MIN   | At         | <br>       |           | V<br>Typical |           | lypicel  | <u> </u>      | I<br>Source   |             | t               |

| 74/54      | (V) | ave<br>(mA) | ما<br>(۷) | 111<br>(V) | لم<br>(mA) | Hi<br>(mA) | ما<br>(۷) | ما<br>(۷)    | ні<br>(V) | Щ<br>(V) | at Lo<br>(mA) | at Hi<br>(mA) | MAX<br>(bS) | Typical<br>(nS) |

| 06         | 5.0 | 3.88        | 0.8       | 2.0        | -1.6       | 0.04       | 0.4       | 0.2          | 2,4       | 3.4      | 16            | -0.8          | 27          | 15              |

| LSO        | 5.0 | 0.85        | 0.8       | 20         | -0.36      | 0.02       | . 0.5     | 0.35         | 2.7       | 3.4      | 8             | -0.4          | 24          | 12              |

| HCTOS      | 4.5 | 0.04        | 0.8       | 2.0        | -0.001     | 0.001      | 0.33      | 0.2          | 3.84      | 4.2      | ~3.6          |               | 35          | 12              |

| HCOS       | 4.5 | 0.04        | 0.9       | 3.15       | 0.001      | 0.001      | 0.33      | 0.2          | 3.84      | 4.2      | ~3.6          |               | 20          | 10              |

| ALSOS      | 45  | 2           | 0.8       | 2.0        | -0.1       | 0.020      | 0.5       | 0.35         | V2        |          | 8             | -0.4          | 18          | ~11             |

| 505        | 5.0 | 25          | 0.8       | 2.0        | -2         | 0.05       | 0.5       |              | 2.5       | 3.4      | 20            | -1            | 7.5         |                 |

| ACTOS      | 45  | 0.04        | 0.8       | 2.0        | 0.001      | 0.001      | 0.40      |              | 3.76      |          | 57            | -50           |             | 6.7             |

| AC06       | 4.5 | 0.04        | 1.35      | 3.15       | -0.001     | 0.001      | 0.1       |              | V-0.1     |          | 24            |               | 12          | 5               |

| <b>P06</b> | 5.0 |             | 0.8       | 2.0        | -0.6       | 0.020      | 0.50      | 0.35         | 2.7       | 3.4      | 20            | -1            | 6.6         | 4.2             |

| AS06       | 4.5 | 10          | 0.8       | 2.0        | -0.5       | 0.020      | 0.5       | 0.35         | V2        |          | 20            | -2            | 6.5         | ~4              |

Figure 2-2. Logic circuit parameter-naming conventions.

Whereas older MOS gates, although less "power hungry," were considerably slower than TTL bipolar parts, newer metal oxide semiconductor (MOS) devices not only use much less quiescent (steady state) power than TTL, but they are also faster and more noise immune. They also retain the circuit densities that have made large-scale integration possible.

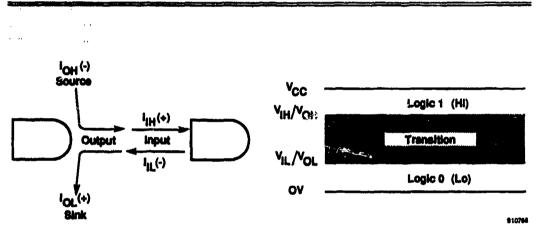

Minor problems arise when mixing logic families. In table 2-1, the differences in the input and output threshold voltages can result in "filogical" logic. For example, the 74AC08 expects logic "1" inputs to be no less than 3.15 V, whereas a 74F08 logic "1" output may be as low as 2.7 V (fig. 2-3). Where a 74F08 output is feeding a 74AC08 input, a pullup resistor is required to pull the 74F08 output higher when it's in the logic "1" state. This has an impact on both component count (adding resistors) as well as gate-transition speed.

Figure 2–3. Logic family interfacing problem.

The HC family can replace LS logic if all the logic were LS. However, there is both an HC and HCT family (as well as AC and ACT) because of this interfacing problem. As long as the entire design uses LS logic, either HC or AC logic can replace it. However, the design may rely on maintaining LS voltage levels for other logic interfacing. Because HC improves noise immunity by wider separation of acceptable input voltages for logic "1" or "0" than does LS logic, problems may arise. Therefore, HCT and ACT logic families were developed. They retain the reduced power consumption of the HC and AC families, but sacrifice the improved noise immunity in favor of mimicking LS tolerance levels.

#### 2.4.1.5 Problem areas

Α.

The improvements made in logic are not a panacea. New problems have arisen that require watching. For instance, CMOS logic outputs have higher output impedance (Z) than bipolar families. Although CMOS has higher noise immunity than bipolar families (because of greater separation of logic output voltages), they are more susceptible to external signal coupling as a result of their higher Z. Care must be taken in circuit layout to minimize crosstalk.

The AC logic is susceptible to a condition known as "ground bounce." This condition occurs when logic tolerances are altered because of high frequency signals.

#### 2.4.1.6 Programmable logic devices

The most interesting logic devices to gain popularity lately are programmable logic devices (PLD's). Different manufacturers refer to this class of device by various names like programmable array logic (PAL) and programmable logic array (PLA). The underlying idea is the same: they are hardware logic gates and flipflops whose interconnections are programmable. Some devices are programmed once only. That is, once programmed, they cannot be altered again. Others are ultraviolet (UV) erasable electrically programmable logic devices (EPLD's) and can be reprogrammed. All of these devices offer the best of both worlds---the speed of hardware logic and the flexibility of programming. In essence, it is a way of programming hardware.

Making logic changes is as easy as reprogramming an IC rather than (necessarily) requiring circuit board modifications. PLD's also allow more customized "hardwired" logic to be packed into a small area. The major drawback is that their speeds never match small-scale integration (SSI) logic like the AND gates described earlier. Also, it may be more difficult to troubleshoot the logic if the signals requiring monitoring are buried inside the PLD with no external leads.

#### 2.4.1.7 Hybrid circuits

When it is necessary to miniaturize systems, hybrid circuits may become necessary. Hybrid circuits are a group of monolithic IC's, resistors, and capacitors that are wired as a circuit. A unique quality of hybrids is that the IC's are the "chips"—without their carrier package, which saves board space. The hybrid technique requires manual fabrication, a disadvantage which drives up the cost. Savings of scale are minimal because of the manual labor involved.

#### 2.4.2 Environmental considerations

Airborne electronics often encounter a wide range of environments. For example, a fighter aircraft may absorb tremendous heat sitting on a ramp in the desert. The aircraft then takes off and flies to high altitudes (low ambient pressure) where ambient temperatures are -50 °C, then returns to the hot desert floor. The same aircraft might be flown from the deck of a damp aircraft carrier. The possibility of high electromagnetic radiation environment operation must be considered as well.

Operational aircraft electronics are designed to withstand all the extremes just listed. This dramatically increases the cost of flight systems as a result of more difficult design and manufacturing constraints plus required testing.

Often in flight test, design criteria can be relaxed considerably because the mission ground rules can be more controlled. In most cases, instrumentation equipment failure results in the termination of data acquisition and does not endanger the safety of the aircraft. Also, mission rules may dictate operating only in clear weather when the ramp temperatures are below 30°C. The test instrumentation could be located in a pressurized area where there is good airflow. These rules would allow the instrumentation to be less expensive and to be designed more quickly.

Another environmental consideration that is gaining importance is electrostatic discharge (ESD). Static electric charges build up on the bodies of personnel. An example of electrostatic discharge is the spark generated when reaching for a doorknob on a dry winter day. The discharge can cause when it ronic components to be damaged or destroyed. Less known is that ESD can damage electronic components even when it hasn't built to the level of discharging a spark. This sensitivity to ESD worsens as IC fabrication technologies shrink IC line widths to fit more logic on a substrate. Precautions must be taken to prevent damage. Personnel working with electronics must be grounded through high-impedance leads. High-impedance leads allow a charge to drain off gradually. If a charge drains instantaneously, high currents would flow or a spark would occur.

#### 2.4.3 Architecture

There are many ways to design a data acquisition system. In most engineering endeavors, compromises must be made depending on design constraints. For example, constraining a system to be under 1000 cm<sup>3</sup> and less than 5 kg probably constraints the power dissipation, but not the cost. Optimizing the cost may minimize the channels available and determine minimum size possible.

As table 2-1 illustrates, modern logic families are becoming faster and dissipate less power than before. The size of IC components is also shrinking, which means that more electronics per unit area is possible. This in turn drives up the dissipation requirements. While the units are shrinking, the computational requirements are increasing. These increased computational requirements can drive an increase in unit size. The usual tradeoff is size as opposed to performance.

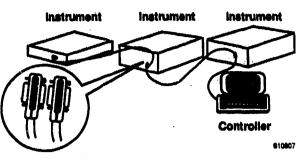

Data acquisition on an aircraft can be categorized into three basic groups: centralized, distributed, and separate. A centralized data acquisition system has one central controller that directly controls the data acquisition of all the sensors. It also determines what the output data stream will be. Refer to figure 1–2 for a simplified example.

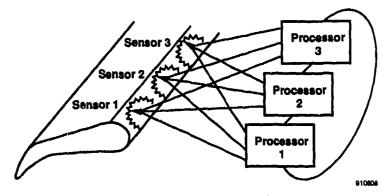

A distributed data acquisition system is more loosely coupled. It may be thought of as several "central" data acquisition systems that share information—usually through digital serial channels. One system directs the sampling of the rest, but the actual sampling, filtering, and conversion into digital form is done at each remote location. Distributed systems are important when long lengths of thick wire bundles must be avoided, such as on large aircraft with widely separated sensors or on small aircraft with no room for wire bundles. "Separate" data acquisition systems coexist on an aircraft but have nothing to do with each other. This is frequently the simplest spproach but has the disadvantage of not allowing all the aircraft data acquisition to be synchronized. Although this approach may work for "gross" observation of data, it is frequently intolerable for research.

#### 2.5 Software Considerations

#### 2.5.1 Languages

There was a time when a clear delineation was made between software and hardware. To a software engineer, hardware was something that software was run on. To a hardware engineer, software was the afterthought of the hardware buildup process.

With aircraft, if software was needed, it was in assembly language. This was the responsibility of the hardware engineers. Aircraft systems had to run fast. Programming was viewed as logic replacement, and software was embedded into the hardware. The fastest way to run code was to program in machine code or its slightly more human readable form called assembly language.

With the advent of highly digital aircraft, the thought of programming and verifying several interconnecting digital systems all programmed in assembly language is horrifying. The difficulty in "thinking like a machine" is increased considerably because of the complexity of several, usually asynchronous, systems. Increased processing speeds and higher density memories have allowed higher level languages to be considered for many onboard systems.

A high-level language allows the programmer to write code in a more abstract manner—the programmer's attention can be spent more on solving the problem than on moving bits around a machine—which is where much of the assembly language programmer's time is spent. The tradeoff is that the programmer has less to do with the machine level and a certain level of control is lost. With a high-level language, overhead is increased (taking more time and memory to execute code). But time to code the solution is usually decreased (more time spent on solving the problem and less time telling the machine how to implement it).

Many high-level languages are in use. Four of the most representative and important languages are FORTRAN, PASCAL, "C," and ADA. The FORTRAN (FORmula TRANslation) language has existed since the 1950's and is still a very well understood and popular language. It excels at just that—translating formulas ("number crunching"). In earlier forms it relied on a "threaded code" concept to pass control around a program. This form is more difficult to follow than the so-called structured program concept used by FORTRAN 77 and the quintessential model of structured programming, PASCAL.

The PASCAL language was developed to teach students good structured programming concepts. To this end, it maintains a "death grip" on programming technique. It also separates the programmer from the hardware—by definition. PASCAL is largely self-documenting. Variables are strong!.. typed (integer, real number, logical variable, and so forth), and the use of pointers and record structures allows queues, linked lists, and data structures to be implemented easily. The main drawback for embedded data system applications like aircraft avionics is that the real world intrudes on this view of a structured universe and hooks into the hardware must be provided. Because PASCAL (in standard implementations) is hard to fool, the usual approach is to call assembly language subroutines to do the hardware access. The programmer will then spend time working around the program to accomplish the task.

The "C" language was developed at Bell Labs, Murray Hill, New Jersey. Its main purpose was to build operating system elements—UNIX in particular. There are two advantages to this. First, the operating system programmer can write the operating system code in a high-level language. Second, the operating system is more portable between computers because the system programming is written at the abstract level and not at a machine dependent, assembly language level. But operating systems must deal with the real world of system input-output (disk read-writes, terminal access, printing, and so forth). The "C" program is less strongly typed than PASCAL and allows much "bit twiddling," or bit manipulations. In fact, "C" fits in a niche between assembly code and PASCAL. It includes data structures, block structuring of code, and high-level parsing of coding, and allows the programmer to bypass much of it. Usually, when high-level language concepts are bypassed, the code is less portable. Also, "C" language is frequently less readable. As "C" is a very cryptic language, considerable attention must be paid to making it readable. It is not a self-documenting language.

The most touted and controversial high-level language to come along in recent years is ADA. Unlike "C" or PASCAL, which came out of development groups and universities and gained acceptance in a "bottom up" fashion, ADA is advocated by the U.S. Department of Defense (DoD) as a standard language for all coding done on its programmable systems. The advantage of this standardization is that overall system maintenance costs are minimized because larger pools of expertise are maintained. The ADA language is designed to be all things to all people. It developed out of committee (top down) and is a very large compiler. It is so large and so slow, in fact, that the writing of compilers for different machines and the verification of them is a long process. By definition no extensions are allowed, so all bases must be covered within the language. The end result is a language that is too large and too slow for many of the microprocessor-embedded applications (including logic replacement functions) on board aircraft. However, because DoD is mandating its use, the flight test community must take ADA seriously.

#### 2.5.2 Software development

Software development, like hardware development, requires a clear definition, a development plan, and a verification process of the problem to be solved. Tools are needed for writing the code and debugging it. The time and tools required to debug software are frequently underestimated. "Data crunching" software requires no interface other than disk drives, a printer, and an operator terminal. Software designed for flight activity interfaces to many other systems. These systems usually have their own ideas as to when to send and receive signals, as they are related to real-time processes.

Usually, the code cannot be fully tested until it has been run on the aircraft and connected to the systems used in flight. Some simulation can be done before this. Software modules can be written to simulate (in a parameter-passing sense) the aircraft systems. Language debuggers can be used to examine trouble spots in code execution. But timing checks are very difficult to do without connecting to the aircraft systems. Sometimes code is written on one type of computer and the execution is targeted for another type of computer. This process is called cross-compilation or cross-assembly, depending on whether a compilation or assembly is done. Cross-compilation or cross-assembly allows common ground-based computers (designed for general-purpose use) to be used as a tool in developing code for a system that is optimized as an embedded system.

#### **3 ANALOG-TO-DIGITAL INTERFACE**

#### 3.1 Analog-to-Digital Conversion Techniques

Analog-to-digital (A-D) conversion is central to most data acquisition systems. If a time-varying voltage is the output of a sensor, and the data will be stored in a digital fashion, it must be converted from the analog domain to the digital domain. There are several ways to perform this conversion. This section will briefly describe the methods and the tradeoffs between them.

#### 3.1.1 Successive approximation

Probably the most common technique employed by A-D converters is successive approximation. As the name implies, the input voltage is compared with a succession of reference voltages. Based on each comparison, a new reference voltage is selected (either higher or lower) until within the resolution of the converter the comparison cannot be improved. This technique is similar to finding the root of an equation by "guessing" a root, plugging it into the equation, and then halving or doubling the guess depending on the result. With each successive guess, the range of excursions to the next guess is itself halved or doubled, until the answer is close enough (sufficient resolution). Table 3-1 shows a successive approximation sequence of a 5-bit A-D converter that settles on the number 6.

Table 3-1. Successive approximation sequence.

| Binary Output | Description                                                        |

|---------------|--------------------------------------------------------------------|

| 11111 >       | Think of the process as removing                                   |

| 01111 >       | calibrated weights from a scale                                    |

| 00111 >       | balance-five weights, each                                         |

| 00011 <       | weighing half of the next higher                                   |

| 00111 >       | weight. When removing a weight                                     |

| 00101 <       | tips the scale (<), then put it back                               |

| 00111 >       | on and remove the next lower                                       |

| 00110 =       | weight, until removing any lower<br>weight causes the scale to tip |

|               | to "<," or the scale balances (=).                                 |

This type of A-D converter is used in applications where sampling at less than 1 MHz is sufficient. It is considered a moderate-to-high-speed converter. Successive approximation takes time, but high resolution can be obtained. Commercially available monolithic IC's up to 16 bits are common. The higher the resolution, the more conversion time is required (more voltage comparisons to do), and longer amplifier settling time is necessary to minimize amplifier dynamic effects.

#### 3.1.2 Integration

Integrating A-D converters count pulses for a period proportional to the analog voltage input level. The longer a pulse train is counted, the higher the integration value (of the pulse train) will be. When the integrated value rises to match the value of the input signal, the pulse train stops. A counter that has been counting the number of pulses now freezes, and this value is the digital output of the A-D converter. Dual slope integration involves integrating the analog voltage input for a predetermined time. A reference input is then switched into the integrato, and integrates "down" to zero (where it started). The time it takes for the second (down) integration process is proportional to the average of the analog input voltage over the period of the first integration. A digital pulse train pulses over the second (down) integration period and a counter keeps track of the number of pulses. The resulting number is the digital output and is proportional to the analog input voltage. The advantage of dual slope over a single slope integrator is that the dual slope increases accuracy and cancels out temperature effects contributed by resistor and capacitor time constants. It does this at the expense of requiring more control logic.

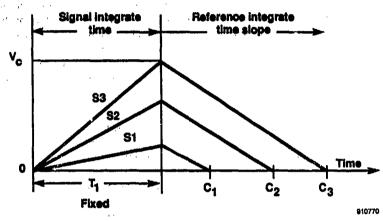

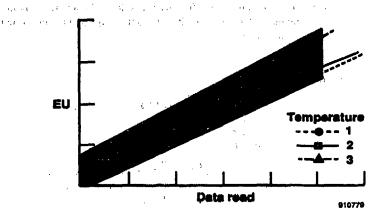

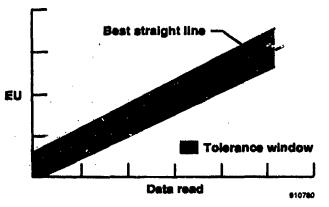

For example, in figure 3-1 three signals are shown:  $S_1$ ,  $S_2$ , and  $S_3$ . The  $S_1$  signal is the smallest, so it integrates up to the smallest level in time,  $T_1$ . When the reference input is switched in at  $T_1$ , the counter is started, and all three signals integrate down at the same rate. The  $S_1$  signal reaches zero first (at point  $C_1$ ), where its counter terminates. Obviously, if the counter terminated at  $C_2$ , its value would be greater—indicating that  $S_2$  is larger than  $S_1$ .

Figure 3-1. Dual slope integration analog-to-digital converter.

Very high resolution data can be obtained at moderate speeds and low cost using this technique. Multiple integration cycles can improve the resolution and accuracy at the expense of speed. The integration process reduces ncise at frequencies whose periods are shorter than the signal integration time (higher frequencies). A sample and hold is not necessary.

#### 3.1.3 Multiple comparator (flash) converter

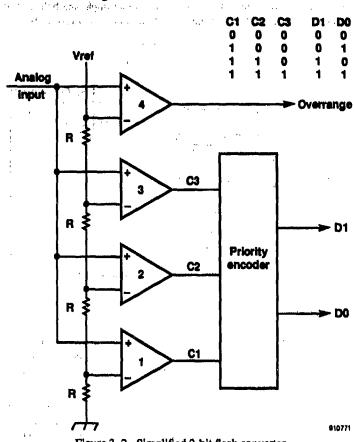

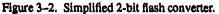

This type of A-D converter is the fastest because the conversion takes place combinationally (unclocked) all at one time. It does this by using many voltage comparators simultaneously. In a true flash converter,  $2^n - 1$ comparators are used, where n equals the number of bits in the A-D output. Each comparator is set for a different level and graded in equal divisions from the minimum to maximum acceptable input voltage. All of the comparators with references below the input voltage will indicate HIGHER and the comparators with reference voltages above the input voltage will indicate LOWER. It is like reading a thermometer, where the mercury is seen at each degree below the indicated temperature and no mercury is seen at each degree above the indicated temperature.

The output of each comparator is fed into a priority encoder that converts the decoded inputs to an encoded binary output. The priority encoder requires  $2^n - 1$  inputs and n outputs. This process requires many accurate voltage comparators and gates for the usual case where  $n \ge 8$ . It is very fast, however, because the conversion happens at once.

3-2

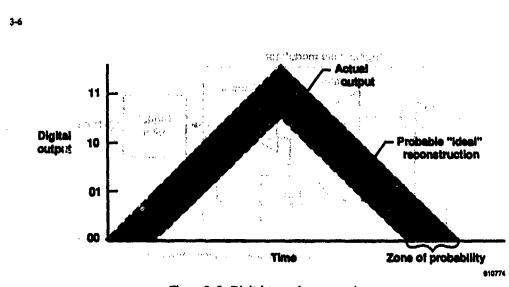

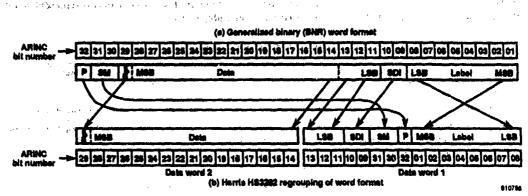

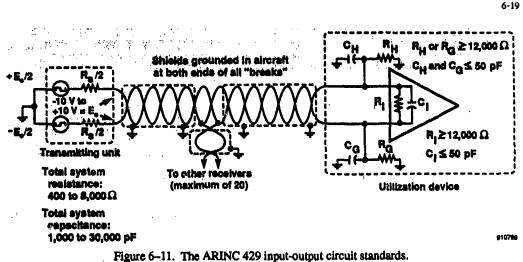

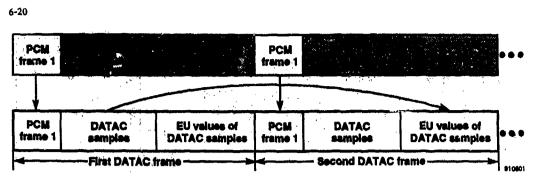

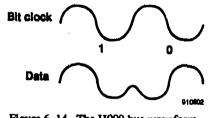

Figure 3-2 shows a simple example. Here, n = 2. So  $2^2 - 1 = 3$  comparator stages are required. An extra comparator is used to indicate overrange.