AFIT/GCS/ENG/91M-03

. -

Optimal Iterative Task Scheduling for Parallel Simulations

THESIS

JoAnn M. Sartor Captain, USAF

AFIT/GCS/ENG/91M-03

Approved for public release; distribution unlimited

91 7 19 140

| REPURI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DOCUMENTATION F                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PAGE                                                                                                                                                                                                                                                                                                                                    | Form Approved<br>OMB No: 0704-0                                                                                                                                                                                                                                                                                                                                                                                              | 88                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Public reporting burden for this follection of<br>gathering in dimarcial ting the data owneed<br>collect on a line interfoll on including suggest                                                                                                                                                                                                                                                                                                                                                                                                                                       | if information is estimated to average timbur p<br>indicompleting and reviewing the clientium of<br>control reducing this Suppon it. Washin types<br>2002 GL2 and to the Office of Management in                                                                                                                                                                                                                                                                                              | er response including this con<br>China primetion i jengi promini<br>China primetion i jengi promini                                                                                                                                                                                                                                    | entre verver a not ust ins verver bing er ut<br>one and notes source on the stellar entry inter<br>and the result of a second                                                                                                                                                                                                                                                                                                | g data so<br>angect -<br>215 Jur                                                        |

| Davis Highway Sules 224 Artington 74 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | a second and the second se                                                                                                                                                                                                                          | AND DATES COVERED                                                                                                                                                                                                                                                                                                                                                                                                            | 3                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | March 1991                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Master's                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                         | 5. FUNDING MUMBERS                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |

| Optimal Iterative Task                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Scheduling for Parallel Simul                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ations                                                                                                                                                                                                                                                                                                                                  | 1997 (1997)<br>1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 -<br>1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 19 |                                                                                         |

| 6. AUTHOP(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | an a                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |

| JoAnn M. Sartor, Cap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | t USAF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                         | yes me e a trade                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| 7. PERFORMING ORCANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | NAME(S) AND ADDRESS(ES)                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ******                                                                                                                                                                                                                                                                                                                                  | 3 PERFORMING ORGANIZ                                                                                                                                                                                                                                                                                                                                                                                                         | ATION                                                                                   |

| Air Force Institute of 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Technology, WPAFB OH 4543                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-6583                                                                                                                                                                                                                                                                                                                                  | REPORT NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                | 10135                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                         | AFIT/GCS/ENG                                                                                                                                                                                                                                                                                                                                                                                                                 | /91M-                                                                                   |

| 9. SPONSORING, MONITORING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GENCY NAME,S' AND ADDRESS,                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.                                                                                                                                                                                                                                                                                                                                      | 1<br>10 SPCNSORING, MCN *C                                                                                                                                                                                                                                                                                                                                                                                                   | RING                                                                                    |

| LTC John C. Toole                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                         | AGENCY REPORT NUM                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

| DARPA/ISTO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                         | ,<br>,                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

| 1400 Wilson Blvd<br>Arlington, VA 22209-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 308                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                         | <b>b</b>                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |

| 11. SUPPLEMENTARY NOTES<br>12a. DISTRICUTION AVAILABILIT<br>Approved for Public R.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                         | 126 DISTRIBUTION CODE                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

| 12a. DISTRISCT ON AVAILABILIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | STATEMENT<br>elease; Distribution Unlimited                                                                                                                                                                                                                                                                                                                                                                                                                                                   | l.                                                                                                                                                                                                                                                                                                                                      | 120 DISTRIBUTION CODE                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

| 12a. DISTRIEUT ON AVAILABILIT<br>Approved for Public R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | elease; Distribution Unlimited                                                                                                                                                                                                                                                                                                                                                                                                                                                                | l.                                                                                                                                                                                                                                                                                                                                      | 120 DISTRIBUTION CODE                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

| <ul> <li>12a. DISTRIELT ON AVAILABILITY<br/>Approved for Public R.</li> <li>12 ABSTRACT Morimum 200 A</li> <li>The ultimate purpose of<br/>In particular, the impart<br/>The classical scheduling<br/>in all but the simplest<br/>nature of computer sim<br/>This investigation dever<br/>for iterative systems wi<br/>particular, it is shown to<br/>iterations of a given tak<br/>To verify the theoretica<br/>tions on the iPSC/2 Hy<br/>optimal assignment, a given tak</li> </ul>                                                                                                  | elease; Distribution Unlimited                                                                                                                                                                                                                                                                                                                                                                                                                                                                | time needed for exe<br>es is determined for<br>ecedence-constraine<br>ing simulation tasks<br>d to execute multip<br>thm (the <i>level strat</i><br>hematical foundatio<br>e systems achieve m<br>used for task assig<br>ng strategies are cor<br>run with mappings<br>at, and an unbalanc                                              | cution of parallel computer si<br>parallel VHDL circuit simul<br>d tasks to m processors is Ni<br>is is further complicated by the<br>le times as the simulation ex-<br>egy) which provides optimal<br>n for iterative task systems is<br>inimal latency, uine between<br>mment.<br>npared using VIDL logic-circo<br>based on the level strategy, t<br>ed assignment. The best resu                                          | ations<br>P-com<br>ne iter<br>ecutes.<br>assign<br>prove<br>succe<br>succe              |

| <ul> <li>12a. DISTRIELT ON AVAILABLE<br/>Approved for Public R.</li> <li>12 ABSTRACT Maximum 200 a<br/>The ultimate purpose of<br/>In particular, the impa<br/>The classical schedulin,<br/>in all but the simplest<br/>nature of computer sim<br/>This investigation deve<br/>for iterative systems wi<br/>particular, it is shown t<br/>iterations of a given tat<br/>To verify the theoretica<br/>tions on the iPSC/2 Hy<br/>optimal assignment, a g<br/>experiments, in terms of</li> <li>14 Automation task schedu<br/>complete problems, pre-<br/>repetitive schedules</li> </ul> | elease; Distribution Unlimited<br>$\frac{1}{2}$<br>of this research is to reduce the<br>ct of task assignment strategie<br>g problem, which assigns <i>n</i> pro-<br>cases. The problem of assigni-<br>nulations: each task is required<br>hops a polynomial-time algorit<br>th specific constraints. A math-<br>hat restricted cases of iterative<br>sk), when the level strategy is<br>l results, various task schedulin-<br>percube computer. Tests are<br>greedy technique for assignment | time needed for exe<br>es is determined for<br>ecedence-constraine<br>ing simulation tasks<br>d to execute multip<br>thm (the <i>level strat</i><br>hematical foundatio<br>e systems achieve m<br>used for task assig<br>ng strategies are cor<br>run with mappings<br>at, and an unbalanc<br>in cases where the<br>tency, optimal sche | ecution of parallel computer si<br>parallel VHDL circuit simul<br>d tasks to m processors is Ni<br>is is further complicated by the<br>le times as the simulation ex-<br>egy) which provides optimal<br>n for iterative task systems is<br>inimal latency, (time between<br>inment.<br>inpared using VIDL logic-circ<br>based on the level strategy, the<br>ed assignment. The best resu-<br>level strategy is used.         | ations<br>P-com<br>ne iter<br>ecutes<br>assign<br>prove<br>succe<br>suit sin<br>he clas |

# **GENERAL INSTRUCTIONS FOR COMPLETING SF 298**

٠

×.

| GENERAL INSTRUCTIONS FOR COMPLETING SF 298                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| The Report Documentation Page (RDP) is used in announcing and cataloging reports. It is important that this information be consistent with the rest of the report, particularly the cover and title page. Instructions for filling in each block of the form follow. It is important to stay within the lines to meet optical scanning requirements. |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Block 1 Agency Lise Only (Leave Blank)                                                                                                                                                                                                                                                                                                               | Plack 12a Distribution (Augilablity Statement                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Block 1. <u>Agency Use Only (Leave Blank)</u><br>Block 2. <u>Report Date.</u> Full publication date<br>including day, month, and year, if available (e.g.<br>1 Jan 88). Must cite at least the year.                                                                                                                                                 | Block 12a. <u>Distribution/Availablity Statement.</u><br>Denote public availability or limitation. Cite<br>any availability to the public. Enter additional<br>limitations or special markings in all capitals<br>(e.g. NOFORN, REL, ITAR)                                                          |  |  |  |  |  |  |

| Block 3. <u>Type of Report and Dates Covered.</u><br>State whether report is interim, final, etc. If<br>applicable, enter inclusive report dates (e.g. 10<br>Jun 87 - 30 Jun 88).                                                                                                                                                                    | DOD - See DoDD 5230.24, "Distribution<br>Statements on Technical<br>Documents."                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Block 4. <u>Title and Subtitle.</u> A title is taken from<br>the part of the report that provides the most<br>meaningful and complete information. When a<br>report is prepared in more than one volume,<br>repeat the primary title, add volume number,                                                                                             | DOE - See authorities<br>NASA - See Handbook NHB 2200.2.<br>NTIS - Leave blank.                                                                                                                                                                                                                     |  |  |  |  |  |  |

| and include subtitle for the specific volume. On<br>classified documents enter the title<br>classification in parentheses.                                                                                                                                                                                                                           | Block 12b. <u>Distribution Code.</u><br>DOD - DOD - Leave blank                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Block 5. <u>Funding Numbers</u> . To include contract<br>and grant numbers; may include program<br>element number(s), project number(s), task<br>number(s), and work unit number(s). Use the<br>following labels:                                                                                                                                    | DOE - DOE - Enter DOE distribution categories<br>from the Standard Distribution for<br>Unclassified Scientific and Technical<br>Reports<br>NASA - NASA - Leave blank<br>NTIS - NTIS - Leave blank.                                                                                                  |  |  |  |  |  |  |

| C- ContractPR- ProjectG- GrantTA- TaskPE- ProgramWU- Work UnitElementAccession No.                                                                                                                                                                                                                                                                   | <b>Block 13. <u>Abstract.</u></b> Include a brief (Maximum 200 words) factual summary of the most significant information contained in the report.                                                                                                                                                  |  |  |  |  |  |  |

| Block 6. <u>Author(s)</u> . Name(s) of person(s)<br>responsible for writing the report, performing<br>the research, or credited with the content of the<br>report. If editor or compiler, this should follow                                                                                                                                         | Block 14. <u>Subject Terms.</u> Keywords or phrases identifying major subjects in the report.                                                                                                                                                                                                       |  |  |  |  |  |  |

| the name(s).<br>Block 7. Performing Organization Name(s) and                                                                                                                                                                                                                                                                                         | Block 15. <u>Number of Pages.</u> Enter the total number of pages.                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Address(es), Self-explanatory.                                                                                                                                                                                                                                                                                                                       | Block 16. Price Code. Enter appropriate price code (NTIS only).                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Block 8. <u>Performing Organization Report</u><br><u>Number</u> . Enter the unique alphanumeric report<br>number(s) assigned by the organization<br>performing the report.                                                                                                                                                                           | Blocks 17 19. <u>Security Classifications.</u><br>Self-explanatory. Enter U.S. Security                                                                                                                                                                                                             |  |  |  |  |  |  |

| Block 9. <u>Sponsoring/Monitoring Agency</u><br><u>Names(s) and Address(es)</u> . Self-explanatory.                                                                                                                                                                                                                                                  | Classification in accordance with U.S. Security<br>Regulations (i.e., UNCLASSIFIED). If form<br>contains classified information, stamp<br>classification on the top and bottom of the page.                                                                                                         |  |  |  |  |  |  |

| Block 10. <u>Sponsoring/Monitoring Agency.</u><br>Report Number. (If known)                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| <b>Block 11.</b> <u>Supplementary Notes.</u> Enter<br>information not included elsewhere such as:<br>Prepared in cooperation with; Trans. of, To<br>be published in When a report is revised,<br>include a statement whether the new report<br>supersedes or supplements the older report.                                                           | Block 20. Limitation of Abstract. This block<br>must be completed to assign a limitation to the<br>abstract. Enter either UL (unlimited) or SAR<br>(same as report). An entry in this block is<br>necessary if the abstract is to be limited. If<br>blank, the abstract is assumed to be unlimited. |  |  |  |  |  |  |

Optimal Iterative Task Scheduling for Parallel Simulations

# THESIS

Presented to the Faculty of the School of Engineering of the Air Force Institute of Technology Air University In Partial Fulfillment of the Requirements for the Degree of Master of Science in Computer Science

> JoAnn M. Sartor, B.S. Captain, USAF

> > 14 March 1991

Approved for public release; distribution unlimited

# Acknowledgments

There are many, many people who deserve mention here! I'd like to take this opportunity to thank some of them:

First of all, my family. Whenever I'd bring home report cards from school, my mother's response was, "I don't care what grade you get, as long as you do your best." (This, of course, doesn't let a student off-the-hook even if she brings home A's!) My dad, with his stubborn outlook on life, taught me to persevere through the tough times. My three siblings, Kathy, Joe, and Mike, (along with their spouses) performed a chameleon act: a cheering section when I did well – and a support group when I needed a shoulder to cry on. And my brother's children, Josh and Jessie, added sparkle to my life when research looked dreary.

The library staff (in particular, Kathy, Barbara, and Jeff) searched databases; located sources; and answered innumerable questions. Rick, the Keeper of the Hypercubes, simplified the VHDL simulation input, answered computer questions – and helped me scrounge an office. Dr. Roth guided me through the maze of  $I\Delta T_E X$ . My classmates (Ann Lee, James Jaques, and especially Betty Topp) listened to my griping and helped me keep my sense of proportion. And AFIT faculty members (Dr Khatri, Dr Howatt, Dr Bailor, Dr Brown, ...) all answered questions and helped me to decipher technical material. Dr Potoczny worked with me to derive the Combinatoric Example in Appendix A, and Jeff Simmers offered a method of simplifying induction proofs.

My committee members, MAJ Robert Hammell, Dr Gary Lamont, and Maj William Hobart all contributed valuable insights to this effort. Dr Hartrum, though not a member of my committee, took an interest in this thesis and provided several of the ideas that led to breakthroughs. In fact, Dr Hartrum was the first one to mention the iterative property of VHI)L simulations!

MAJ Hammell gave me constant encouragement; his confidence-building speeches helped me through several low points: "Writing a thesis is like building a house..." "In graduate school, you'll find that no one has 'THE' answer!" ... MAJ liammell, I am greatly in your debt for all your work...If ever you need a blood donor, call on me! Dr Lamont! You have been my role model, as well as my advisor: Sometimes, I've come back from a discussion with you feeling the way King Arthur's knights might have felt after leaving the Round Table – as if I have the strength to triumph over any obstacle. You have been a profound influence in my life, as well as the driving force behind this research. Thank you!

And most of all, I'd like to acknowledge the patience and support given by my husband Ray. (Often, Ray was more excited about this thesis than I was: "They're going to let you work on the **Hypercube!!!**") Although putting in "80 hours a week" on his PhD research, Ray found the time to cook huge batches of jambalaya; to go for walks around the neighborhood; and to roar laughing at the escapades of Bertie Wooster!<sup>1</sup> Ray, you've been a great blessing throughout this struggle; I wouldn't trade you for

- All the tea in China,

- All the rum in Jamaica,

- Or even the jackpot in last week's Lotto!

JoAnn M. Sartor

<sup>&</sup>lt;sup>1</sup>For those of you who haven't had a good laugh lately, check out any "Bertie and Jeeves" book by P.G. Wodehouse!

# Table of Contents

|                                                  | Page |

|--------------------------------------------------|------|

| List of Figures                                  | viji |

| List of Theorems                                 | xi   |

| Abstract                                         | xii  |

| I. Introduction                                  | 1-1  |

| 1.1 Overview                                     | 1-1  |

| 1.2 Simulation Tasking Background                | 1-2  |

| 1.3 Task Scheduling Problem                      | 1-7  |

| 1.4 Assumptions                                  | 1-8  |

| 1.5 Scope (Context)                              | 1-8  |

| 1.6 Approach                                     | 1-9  |

| 1.7 Structure of Thesis                          | 1-10 |

| II. Background                                   | 2-1  |

| 2.1 General Task Scheduling Problem Description  | 2-1  |

| 2.2.1 Algorithm Considerations                   | 2-5  |

| 2.1.2 Notation and Diagrammatic Representation   | 2-6  |

| 2.2 Classes of Repeating Schedules               | 2-7  |

| 2.3 Latency                                      | 29   |

| 2.4 General approaches to the scheduling problem | 29   |

| 2.5 Iterative nature of the problem              | 2-12 |

| 2.6 Assumptions and Environment                  | 2-14 |

| 2.7 Additional Considerations                    | 2-16 |

| 2.8 Summary                                      | 2-16 |

|      |           |                                             | Page  |

|------|-----------|---------------------------------------------|-------|

| III. | Schedulin | g Algorithm Design                          | 3-1   |

|      | 3.1       | Basis for Level Strategy (One-pass Systems) | 3-1   |

|      |           | 3.1.1 One-Pass Level Algorithm              | 3-1   |

|      | 3.2       | Level Algorithm for Iterative Tasks         | 3-3   |

|      | 3.3       | Search Process                              | 3-3   |

|      |           | 3.3.1 Exhaustive Search                     | 3-4   |

|      |           | 3.3.2 Informed Search                       | 3-4   |

|      | 3.4       | Reducing the Search Space                   | 3-8   |

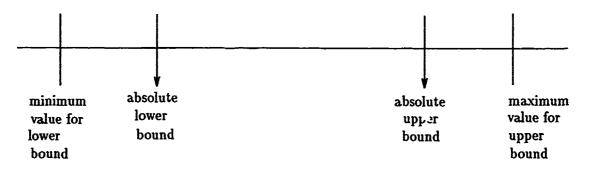

|      |           | 3.4.1 Lower Bound Metrics                   | 3-8   |

|      | 3.5       | Heuristics for Schedule-Building            | 3-14  |

|      | 3.6       | Summary                                     | 3-16  |

| IV.  | Low-level | Analysis                                    | 4-1   |

|      | 4.1       | Theoretical Design of Schedule              | 4-1   |

|      |           | 4.1.1 Justification for Latency Measure     | 4-3   |

|      | 4.2       | Restrictions                                | . 4-5 |

|      | 4.3       | Level Strategy                              | 4-6   |

|      | 4.4       | Scheduling Within a Processor               | 4-9   |

|      |           | 4.4.1 Decision Strategy                     | 4-9   |

|      | 4.5       | Lower Bound on Latency                      | 4-10  |

|      | 4.6       | Upper Bound on Latency                      | 4-12  |

|      |           | 4.6.1 Processor Delay Time                  | 4-1.3 |

|      |           | 4.6.2 Chain of Tasks                        | 4-14  |

|      |           | 4.6.3 Arbitrary Precedence                  | 4-18  |

|      | 4.7       | Equal Execution Time Task Systems           | 4-24  |

|      | 4.8       | Variable Execution Times                    | 4-25  |

|      |           | 4.8.1 Problem Description                   | 4-25  |

|      |           | 4.8.2 Reasons for Level-Strategy Failure    | 4.26  |

|                 |                                                 | Page |

|-----------------|-------------------------------------------------|------|

|                 | 4.8.3 Bounds on Variable-Execution-Time Latency | 4-28 |

|                 | 4.8.4 Minimizing Number of Processors           | 4-32 |

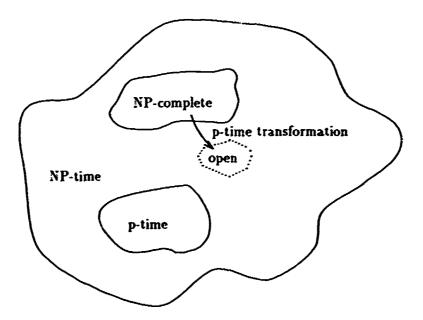

| 4.9 1           | NP-Complete Aspects                             | 4-35 |

|                 | 4.9.1 Background                                | 4-35 |

|                 | 4.9.2 Proving NP-Completeness                   | 4-36 |

|                 | 4.9.3 Variable Execution Time Systems           | 4-37 |

| 4.10 \$         | Summary                                         | 4-42 |

| V. Application  | /Experimental Results                           | 5-1  |

| 5.1             | HDL Application                                 | 5-1  |

|                 | 5.1.1 VHDL Parameters and Results               | 5-1  |

| 5.2 (           | Gaming Simulation Results                       | 5-4  |

| 5.3 \$          | Summary                                         | 5-7  |

| VI. Conclusions | and Recommendations                             | 6-1  |

| 6.1 0           | Conclusions and Contributions                   | 6-1  |

| 6.2 J           | Recommendations for Further Research            | 6-4  |

| Appendix A.     | Combinatoric Complexity Example                 | A-1  |

| A.1 ]           | Detailed Example                                | A-1  |

| Appendix B.     | Level Strategy Example                          | B-1  |

| B.1 1           | Level Strategy                                  | B-3  |

| Appendix C.     | A* Search                                       | C-3  |

| C.1 A           | A* overview                                     | C-1  |

| C.2 S           | Sample A* Search                                | C-1  |

| C.3 1           | Evaluation Function,                            | C-3  |

| Appendix D.     | Iteration-Number Decision Strategy              | D-1  |

्र स्वयंत्रकार्यन्तुः - स्वयंत्रकार्यः

.

| Vita         | •     |

|--------------|-------|

| Index        | IND-1 |

| Bibliography | BIB-1 |

÷

----

-----

# List of Figures

.

| Figure |                                                                | Page |

|--------|----------------------------------------------------------------|------|

| 1.1.   | Unbalanced Processor Loads                                     | 1-3  |

| 1.2.   | Relationships Between Tasks (1) and (2)                        | 1-4  |

| 1.3.   | Branch and Bound Search Tree                                   | 1-6  |

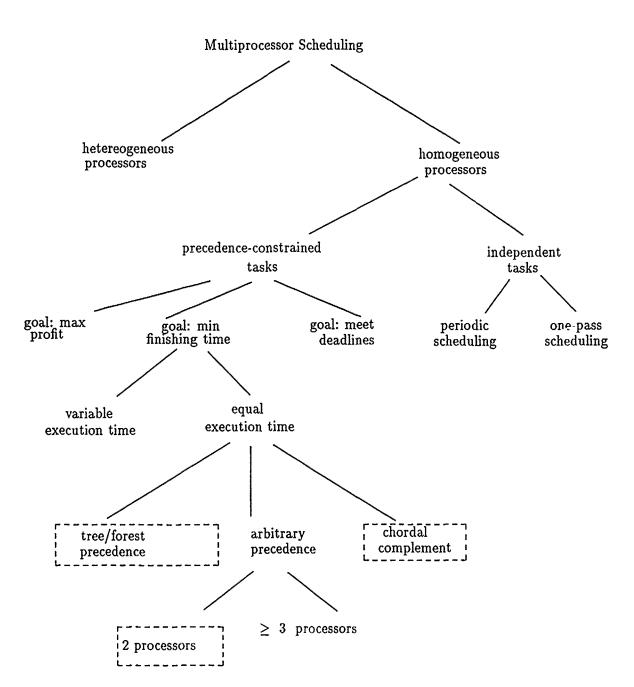

| 2.1.   | Relationship Between Multiprocessor Scheduling Problems        | 2-3  |

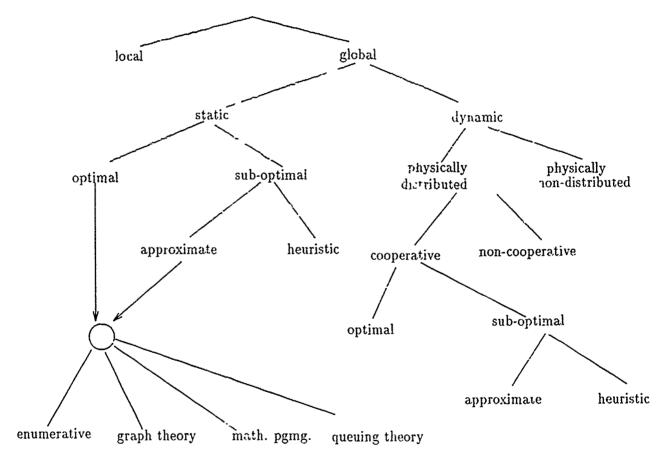

| 2.2.   | Taxonomy of Scheduling Problems                                | 2-5  |

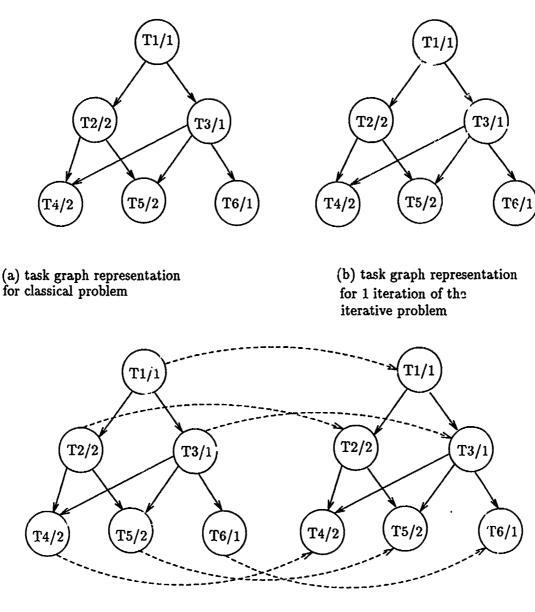

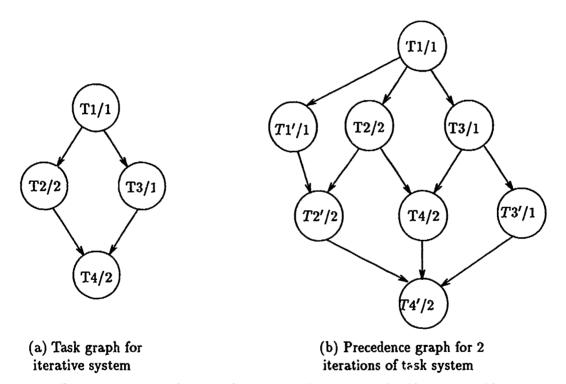

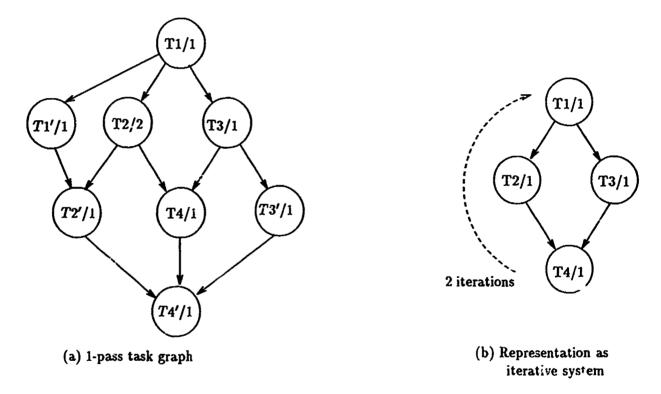

| 2.3.   | Task system                                                    | 2-7  |

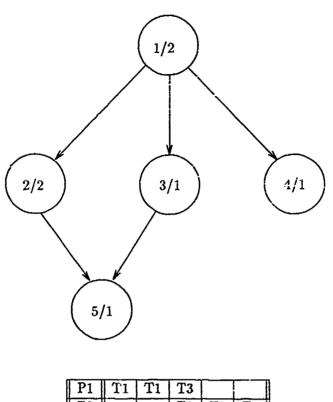

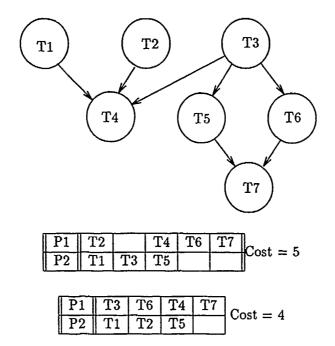

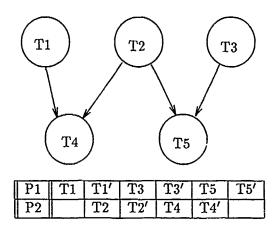

| 2.4.   | Arbitrary Precedence Graph with Optimal Schedule               | 2-10 |

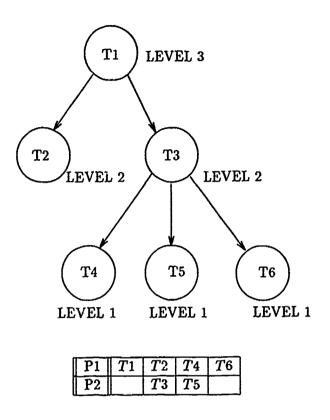

| 2.5.   | Tree-Structured Precedence Graph with Optimal Schedule         | 2-11 |

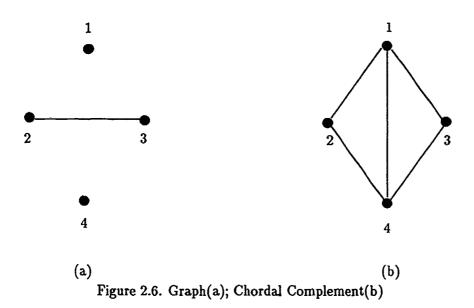

| 2.6.   | Graph(a); Chordal Complement(b)                                | 2-12 |

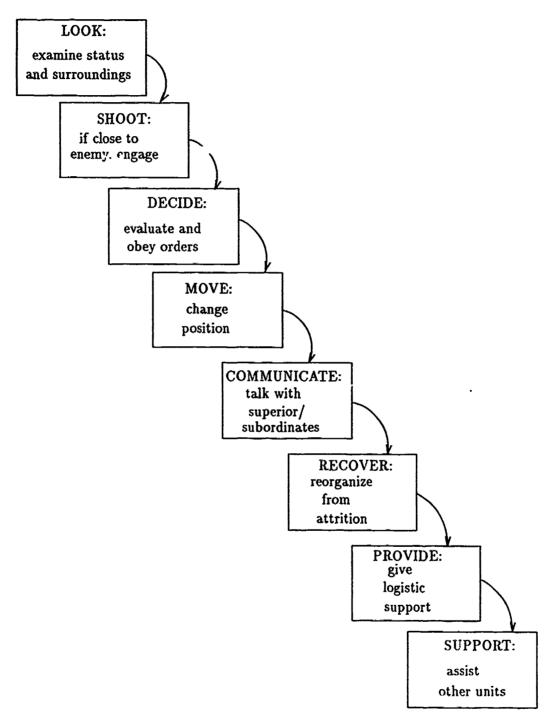

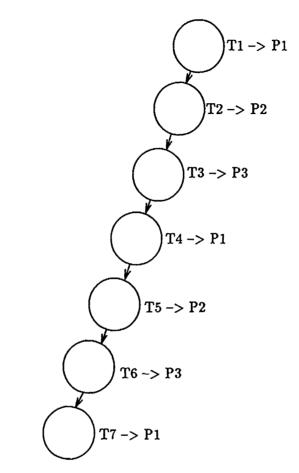

| 2.7.   | CORBAN Tasks                                                   | 2-13 |

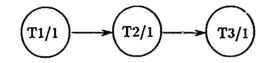

| 2.8.   | Optimal (1-pass) vs Pipelined                                  | 2-14 |

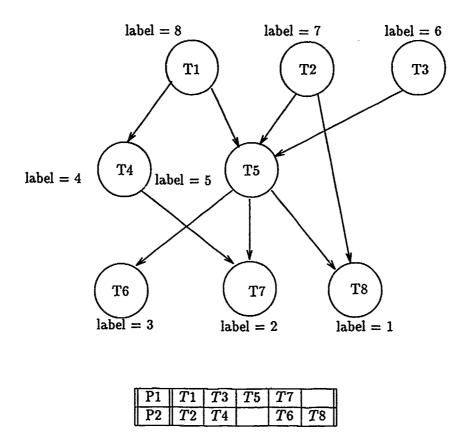

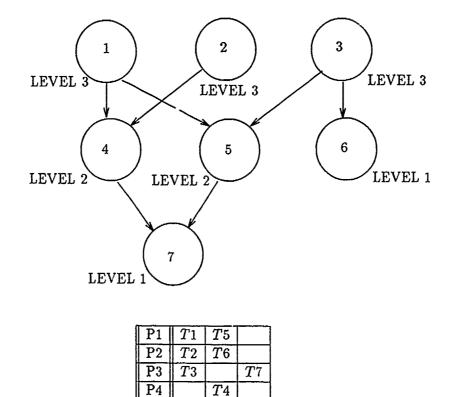

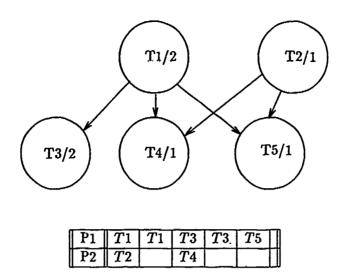

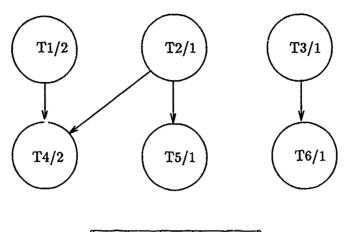

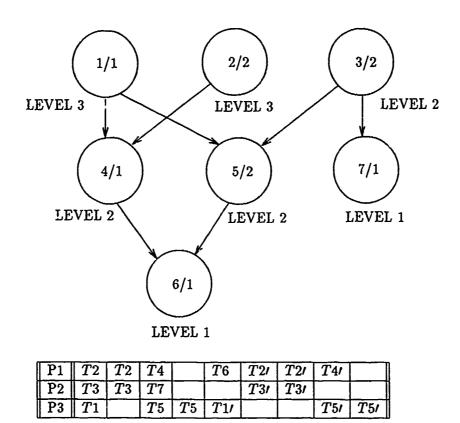

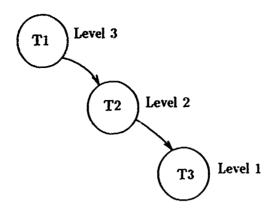

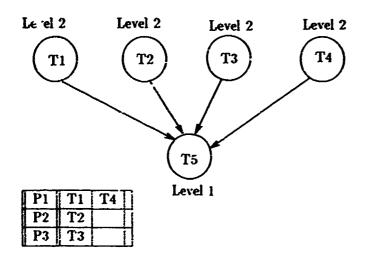

| 3.1.   | Assignment by level strategy                                   | 3-2  |

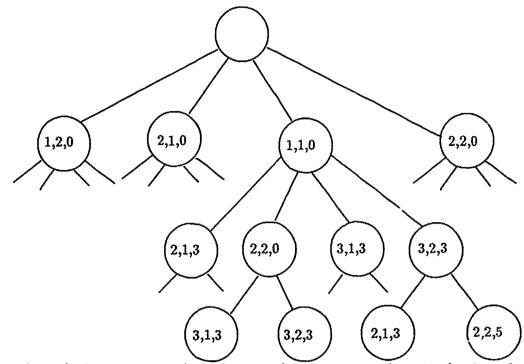

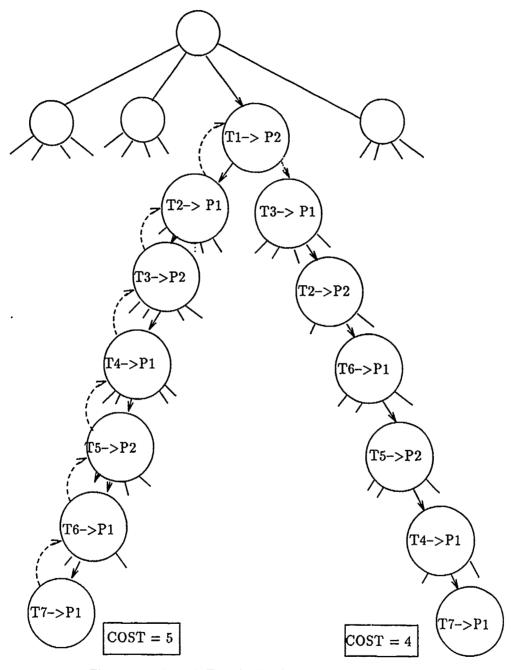

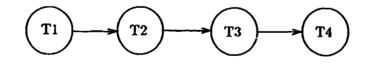

| 3.2.   | Exhaustive Search                                              | 3-5  |

| 3.3.   | Partial Search Tree                                            | 3-6  |

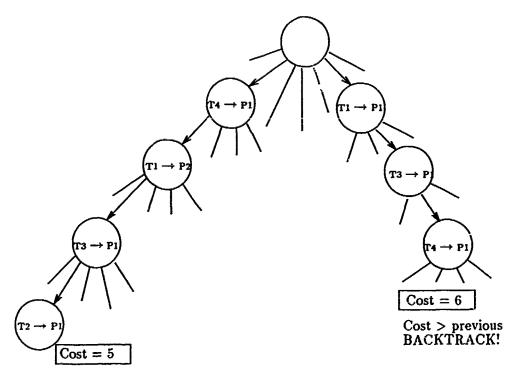

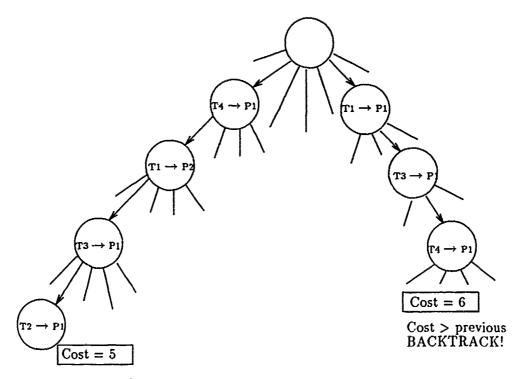

| 3.4.   | Branch and Bound Search Tree                                   | 3-7  |

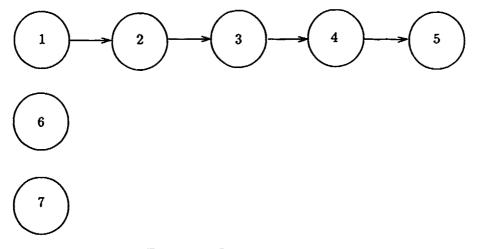

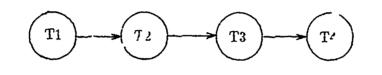

| 3.5.   | Chain of 9 Tasks                                               | 3-9  |

| 3.6.   | Longest Path = 5                                               | 3-10 |

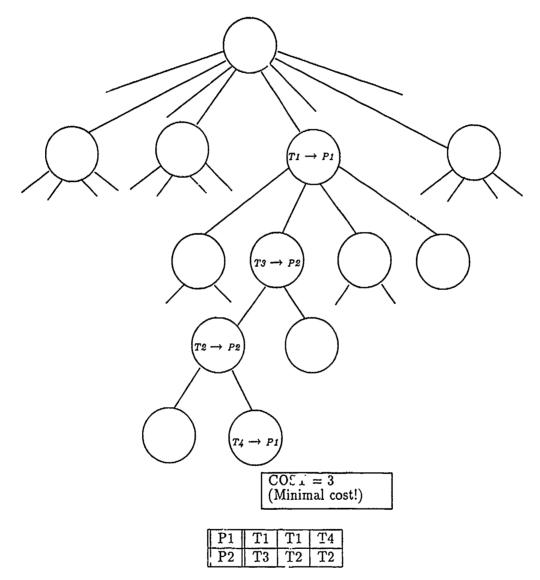

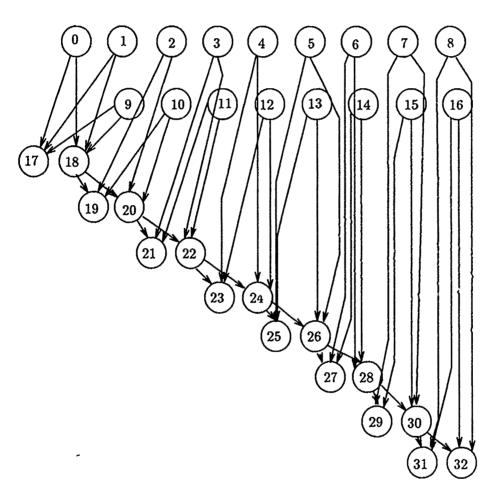

| 3.7.   | Search Graph and Optimal Schedule for Independent Task Example | 3-13 |

| 3.8.   | Scheduling Tasks with Most Successors                          | 3-15 |

| 3.9.   | Search Tree for Tasks with Most Successors                     | 3-17 |

| 4.1.   | Precedence Graph: 8-bit Adder                                  | 4-2  |

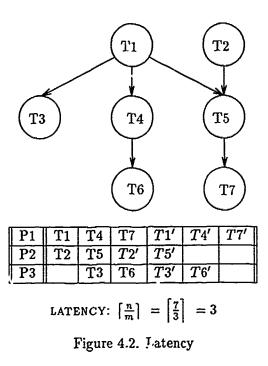

| 4.2.   | Latency                                                        | 4-3  |

| 4.3.   | Search Tree (Level-Strategy Assignment)                        | 4-4  |

| Figure                                                                             | Page |

|------------------------------------------------------------------------------------|------|

| 4.4. Mapping for 10 tasks and 10 processors; $(latency = 1) \dots \dots \dots$     | 4-4  |

| 4.5. Task System with Non-optimal Mapping                                          | 4-7  |

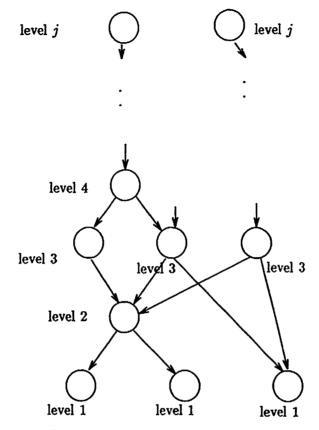

| 4.6. Assigning Levels to Tasks                                                     | 4-8  |

| 4.7. Effects of Decision Strategy                                                  | 4-9  |

| 4.8. 5 independent tasks; 2 iterations                                             | 4-11 |

| 4.9. Maximum Latency for Task System                                               | 4-13 |

| 4.10. Comparison: Assignment Strategies with Schedule 1                            | 4-14 |

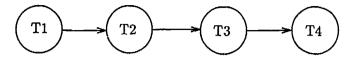

| 4.11. Level Strategy Assignment: chain of $m$ tasks on $m$ processors              | 4-15 |

| 4.12. Level Strategy Assignment: chain of $m + 1$ tasks on $m$ processors $\ldots$ | 4-15 |

| 4.13. Level Strategy Assignment: Serial Precedence (chain)                         | 4-16 |

| 4.14. Last task execution on all processors                                        | 4-17 |

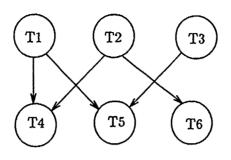

| 4.15. Level Strategy Assignment: arbitrary precedence $vs$ . serial precedence.    | 4-19 |

| 4.16. Idle time due to level change                                                | 4-20 |

| 4.17. Variable execution time task system                                          | 4-27 |

| 4.18. Task System with Variable Execution Time                                     | 4-28 |

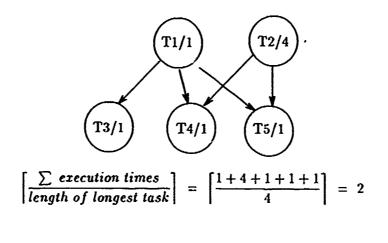

| 4.19. Variable execution time task system                                          | 4-29 |

| 4.20. Relationship between bounds                                                  | 4-33 |

| 4.21. Lower Bound on Processors                                                    | 4-33 |

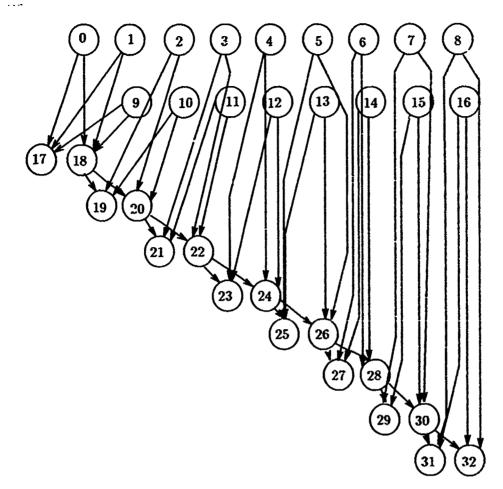

| 4.22. Transformation to Show NP-Completeness                                       | 4-37 |

| 4.23. Nondeterministic Turing Machine Assignment                                   | 4-39 |

| 4.24. Mapping NP-Complete Problem into Open Problem                                | 4-40 |

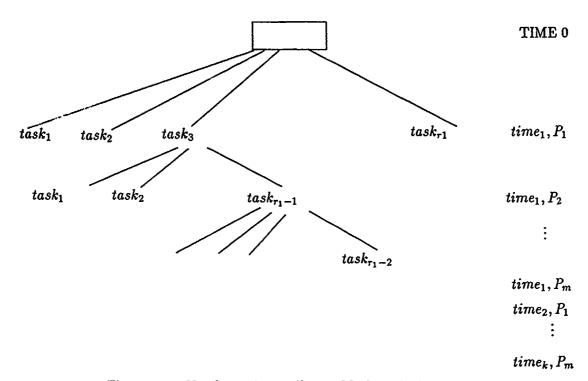

| 4.25. Transforming the Iterative Problem to the Classical Problem                  | 4-41 |

| 4.26. Transforming the Classical Problem to the Iterative Problem                  | 4-43 |

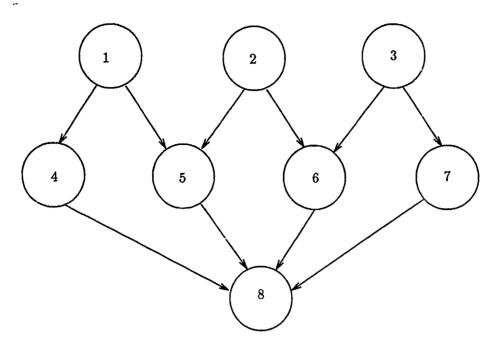

| 5.1. Precedence Graph: VHDL tasks                                                  | 5-2  |

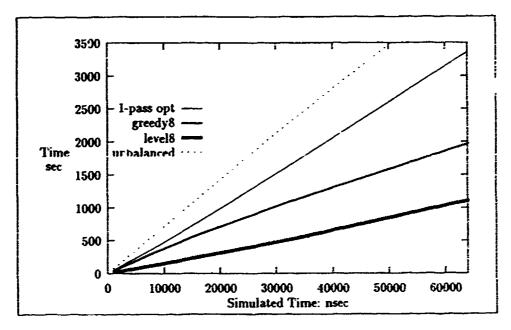

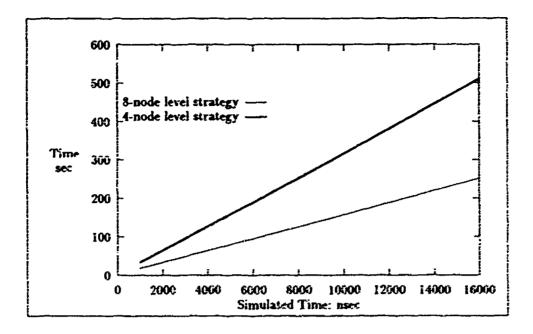

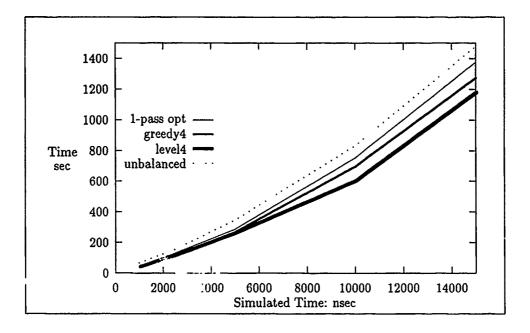

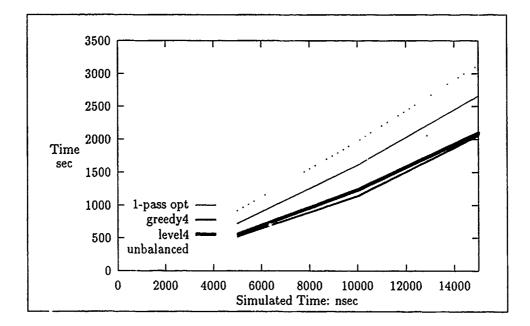

| 5.2. Varied Mapping Strategies                                                     | 5-5  |

| 5.3. Speedup                                                                       | 5-6  |

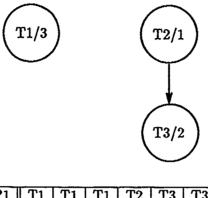

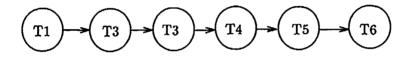

| 5.4. Gaming Simulation Precedence Graph                                            | 5-7  |

|                                                                                    |      |

÷,

10.00

| Figure                                              | Page |

|-----------------------------------------------------|------|

| 5.5. Varied Mapping Strategies (Spin Loops 10,000)  | 5-8  |

| 5.6. Varied Mapping Strategies (Spin Loops 100,000) | 5-8  |

| 6.1. Precedence Graph with Feedback                 | 6-5  |

| B.1. Precedence Graph                               | B-1  |

| B.2. Level Assignment                               | B-2  |

| B.3. More ready tasks than processors               | B-4  |

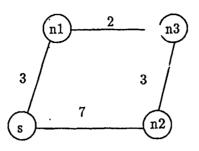

| C.1. Graph for A* Example                           | C-2  |

| D.1. Delay Time Due to rbitrary Decision Strategy   | D-1  |

| D.2. Optimal Schedule                               | D-2  |

•

# List of Theorems

• •

| Theorem                                       | Page |

|-----------------------------------------------|------|

| UET Lower Bound                               | 4-11 |

| Delay Time: chain                             | 4-15 |

| Delay Time: arbitrary precedence              | 4-18 |

| Maximum Delay Time                            | 4-21 |

| UET Upper Bound                               | 4-22 |

| Firm Bound on UET Latency                     | 4-23 |

| Equal Execution Time                          | 4-24 |

| Variable-execution-time Lower Bound           | 4-29 |

| Variable-execution-time Upper Bound           | 4-31 |

| Number of Processors: Variable-execution-time | 4-34 |

| NP-completeness                               | 4-37 |

#### AFIT/GCS/ENG/91M-03

# Abstract

The ultimate purpose of this research is to reduce the time needed for execution of parallel computer simulations. In particular, the impact o<sup>c</sup> task assignment strategies is determined for parallel VHDL circuit simulations.

The classical scheduling problem, which assigns n precedence-constrained tasks to m processors is NP-complete in all but the simplest cases. The problem of assigning simulation tasks is further complicated by the iterative nature of computer simulations: each task is required to execute multiple times as the simulation executes.

This investigation develops a polynomial-time algorithm (the *level strategy*) which provides optimal assignment for iterative systems with specific constraints. A mathematical foundation for iterative task systems is proved. In particular, it is shown that restricted cases of iterative systems achieve minimal latency, (time between successive iterations of a given task), when the level strategy is used for task assignment. In addition, the iterative scheduling problem is proved NP-complete when constraints are relaxed.

To validate the theoretical results, various task scheduling strategies are  $com_{r'}$  ared using VHDL logic-circuit simulations on the iPSC/2 Hypercube computer. Tests are run with mappings based on the level strategy, the classical optimal assignment, a greedy technique for assignment, and an unbalanced assignment. The best results of these experiments, in terms of speedup, occur consistently in cases where the level strategy is used.

xii

# Optimal Iterative Task Scheduling for Parallel Simulations

## I. Introduction

## 1.1 Overview

Although computer technology has evolved dramatically in recent years, some applications are limited by intense computational requirements. Examples of these include aircraft design; weather prediction; and computational fluid dynamics (5, 13).

Some computer applications, such as matrix operations and search problems, may execute faster when *parallel processing* is used. If a designer can decompose the problem into tasks, each processor in a parallel architecture can work on a subset of the original problem. This may be done through *data decomposition*, a technique which partitions a data structure into pieces with different processors working on separate parts of the problem, or by *control/algorithm decompositon*, which allows different processors to perform different functions (31). Dividing the problem in this manner may enable the overall solution to develop faster than on a sequential (one-processor) machine.

After a large problem has been decomposed into tasks, each task must be assigned to a processor so that the computation can be performed. Assigning tasks to processors in an optimal schedule to minimize execution time is, in general,  $z \ge NP$ -complete problem (10). All NP-complete problems have certain characteristics:

- There is no known polynomial-order solution for any NP-complete problem.

- NP-complete problems have combinatoric or exponential search spaces.

- Every NP-complete problem can be mapped (in polynomial time) to every other NP-complete problem. This implies that if a polynomial-time (p-time) solution is found for any NP-complete problem, then a p-time solution can be found for all NP-complete problems.

NP-complete problems can be approached in several ways:

- If an approximate solution is acceptable, heuristics can be developed to produce "good" solutions for specific cases, rather than *optimal* solutions.

- Informed search strategies can be used to reduce the amount of time needed to find an optimal solution in most instances. There are, however, cases where informed search strategies produce no better results than an exhaustive search.

- The problem can be restricted so that it conforms to a problem which has a known polynomial-time solution.

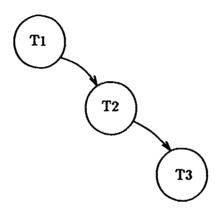

This thesis investigation concentrates on methods for finding an optimal solution to the task scheduling problem, as defined by iterative task systems. In iterative systems, such as those reflected in electronic circuit simulations, each task executes several times during the course of the simulation. This problem is shown to have a polynomial-time solution, for highly-restricted cases, which means that a deterministic Turing machine (DTM) can solve the problem with an algorithm of complexity  $O(n^c)$ , where c is constant (?). Most task scheduling problems, however, require NP-time (10), which means that a nondeterministic Turing machine (NDTM), can solve the problem with an algorithm of complexity  $O(n^c)$ , but that a DTM cannot (?).

# 1.2 Simulation Tasking Background

The development of electronic circuits, such as Very Large Scale Integration (VLSI) circuits, involves numerous steps, from circuit design to physical implementation (30). One attempt to streamline the process of circuit design uses the Very High Speed Integrated Circuit (VHSIC) Hardware Design Language, or VHDL, a design methodology which allows VLSI circuit behavior to be modelled on a computer (2). If VHDL simulations efficiently model circuit behavior, the turnaround time from design to final implementation could be decreased; instead of building intermediate designs and physically measuring the outputs, computer simulations could be used to iteratively refine the circuit before implementation.

Unfortunately, VIIDL simulations for current applications take a disproportionate amount of computer time compared to the size of the circuit which is modeled. For example, one projection estimates that simulating a VHDL design for a circuit with 100,000 transistors would require 700 hours to execute on a VAX 11/780 computer (30).

Previous research (30), attempted to decrease the time needed for VHDL processes by running VHDL test cases on a parallel computer. Although successful VHDL circuit simulations were implemented in parallel, the parallel simulation required approximately the same amount of time as the sequential version. This may have been due to any of several factors which prevent parallel applications from achieving the theoretical speedup:

#### • Communications Overhead:

The simulation must be amenable to parallelization. For example, if each simulation task has a small amount of computation compared to the required amount of communication, then the simulation can spend more time communicating between processors than performing actual work.

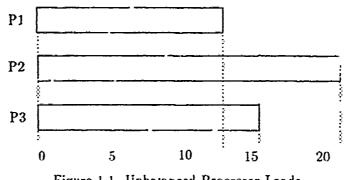

• Inefficient Loading:

The task scheduling process, which assigns sub-problems to different processors, must provide an assignment so that each processor is kept busy. If tasks are assigned to processors so that processors are not fully-1 tilized, execution time is dominated by the processor with the heaviest workload. For example, tasks are assigned to 3 processors in Figure 1.1. Although the average processor finishing time is 17, the finishing time for the entire job is 21.

Figure 1.1. Unbatanced Processor I pads

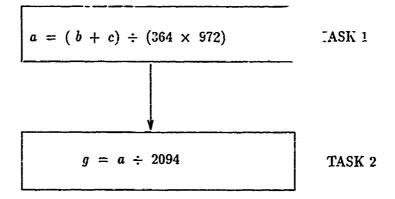

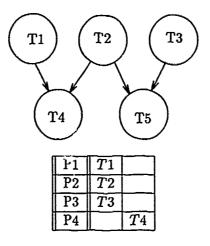

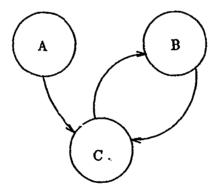

Since dependencies exist between inputs and outputs in VHDL tasks, the process of assigning tasks to processors involves *precedence-constrained* scheduling. In a precedence-constrained system, some tasks must delay until previous tasks are complete. For example, the following task system, shown in Figure 1.2, has a constraint between tasks:

Task 1: Calculate  $a = (b + c)/(364 \times 972)$ Task 2: Calculate g = a/2094

Figure 1.2. Relationships Between Tasks (1) and (2)

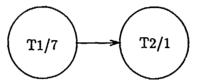

In this task system, Task 2 cannot begin until a value is given for a. Since the value of a is the final result of Task 1, Task 2 cannot begin until Task 1 has completed. Therefore, Task 2 is *constrained* by Task 1.

The problem of mapping precedence-constrained tasks to processors to obtain an optimal schedule falls into the class of NP-complete problems (10, 15). One characteristic of NP-complete problems is that a large search space exists implicitly and is partially generated e plicitly when deriving optimal solutions; another characteristic of these problems is that an optimal solution may require an exceedingly long time to generate using a graph search algorithm (4).

For example, uppose an optimal schedule is desired for 60 independent tasks assigned to 2 processors. If the problem is simplified by assuming that only 30 time slots can be filled on each processor, it is possible to derive the number of possible combinations:

- There are 60 choices for the placement of the first task.

- After the first task is chosen, there are 59 choices for the placement of the second task.

- After the second task is chosen, there are 58 choices for the placement of the third task.

- :

- For the final task, there is one choice for the placement.

- Thus, there are  $60 \times 59 \times 58 \times ... \times 1 = 60!$  unique ways to schedule 60 tasks on 2 processors so that there are 30 tasks on each processor.

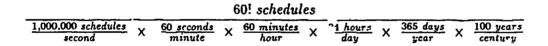

In order to determine an optimal schedule for this problem by exhaustive search, 60! sombinations must be examined. Assuming that schedules are generated by a computer at the rate of 1,000,000 schedules per second, the time required to generate all schedules would exceed hundreds of billions of centurizs!

$$= \frac{8.321 \times 10^{81}}{3.15 \times 10^{15}} = 2.63 \times 10^{66} \ centuries$$

Thus, optimal schedules must be derived using methods other than exhaustive search. (Appendix A contains more complete calculations for this example).