AD-A234 882

RADC-TR-90-404, Vol III (of 18) Final Technical Report December 1990

# THE VERSATILE MAINTENANCE EXPERT SYSTEM (VMES)

Northeast Artificial Intelligence Consortium (NAIC)

Sargur N. Srihari, Stuart C. Shapiro, Shambhu J. Upadhyaya

97 1 15 035

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

This effort was funded partially by the Laboratory Director's fund.

Rome Air Development Center Air Force Systems Command Griffiss Air Force Base, NY 13441-5700

## DISCLAIMER NOTICE

THIS DOCUMENT IS BEST QUALITY AVAILABLE. THE COPY FURNISHED TO DTIC CONTAINED A SIGNIFICANT NUMBER OF PAGES WHICH DO NOT REPRODUCE LEGIBLY.

This report has been reviewed by the RADC Public Affairs Division (PA) and is releasable to the National Technical Information Services (NTIS). At NTIS it will be releasable to the general public, including foreign nations.

RADC-TR-90-404, Volume III (of 13) has been reviewed and is approved for publication.

APPROVED:

Dale M. RICHARDS

Project Engineer

APPROVED:

JOHN J. BART

Technical Director

Directorate of Reliability & Compatibility

FOR THE COMMANDER: Gar G. Monisch

ICOR G. PLONISCH

Directorate of Plans & Programs

If your address has changed or if you wish to be removed from the RADC mailing list, or if the addressee is no longer employed by your organization, please notify RADC (RBES) Griffiss AFB NY 13441-5700. This will assist us in maintaining a current mailing list.

Do not return copies of this report unless contractual obligations or notices on a specific document require that it be returned.

#### Form Approved REPORT DOCUMENTATION PAGE OMB No. 0704-0188 Public reporting burden for this collection of information is eatimized to everage 1 hour per response, including the time for reviewing instructions, searching eating data sources. aded, and completing and reviewing the collection of information. Send comments regarding this outsin estimate or any other expect of this collection of information, including suggestions for reducing this burdern, to Washington Headquesters Services, Directorate for information Collections and Reports, 1215 Jefferson Davis migrievey: Suits 1204, Arfington, VA 22202-4302, and to the Office of Managament and Budgist, Paperwork Reduction Project (0704-0188), Washington, DC 20503. 1. AGENCY USE ONLY (Leave Blank) 2 REPORT DATE 3. REPORT TYPE AND DATES COVERED Sep 84 - Dec 89 December 1990 Final 4. TITLE AND SUBTITLE 5. FUNDING NUMBERS THE VERSATILE MAINTENANCE EXPERT SYSTEM (VMES) C - F30602-85-C-0008 PE - 62702F PR - 5581 6. AUTHOR(S) TA - 27Sargur N. Srihari, Stuart C. Shapiro, WU - 13 Shambhu J. Upadhyaya (See reverse) 8. PERFORMING ORGANIZATION 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) REPORT NUMBER Northeast Artificial Intelligence Consortium (NAIC) Science & Technology Center, Rm 2-296 N/A 111 College Place, Syracuse University Syracuse NY 13244-4100 C. SPONSORING/MONITORING AGENCY NAME(S) AND ADDRESS(ES) 10. SPONSORING/MONITORING AGENCY REPORT NUMBER Rome Air Development Center (COES) Griffiss AFB NY 13441-5700 RADC-TR-90-404, Vol III (of 18) 11. SUPPLEMENTARY NOTES (See reverse) RADC Project Engineer: Dale W. Richards/RBES/(315) 330-3476 This effort was funded partially by the Laboratory Director's fund. 12a. DISTRIBUTION/AVAILABILITY STATEMENT 12b. DISTRIBUTION CODE Approved for public release; distribution unlimited. 13. ABSTRACT (Meanum 200 words) The Northeast Artificial Intelligence Consortium (NAIC) was created by the Air Force Systems Command, Rome Air Development Center, and the Office of Scientific Research. Its purpose was to conduct pertinent research in artificial intelligence and to perform activities ancillary to this research. This report describes progress during the existence of the NAIC on the technical research tasks undertaken at the member universities. The topics covered in general are: versatile expert system for equipment maintenance, distributed AI for communications system control, automatic photointerpretation, time-oriented problem solving, speech understanding systems, knowledge base maintenance, hardware architectures for very large systems, knowledgebased reasoning and planning, and a knowledge acquisition, assistance, and explanation system. The specific topic for this volume is the exploration of methods for developing a versatile expert system for equipment maintenance. 14. SUBJECT TERMS Artificial Intelligence, Export Systems, Fault 15 NUMBER OF PAGES Detection, Graphical Knowledge, User Interfaces, Hypothetical 18 PRICE CODE Reasoning, Semantic Networks 17. SECURITY CLASSIFICATION 18. SECURITY CLASSIFICATION 19. SECURITY CLASSIFICATION | 20. LIMITATION OF ABSTRACT OF REPORT OF THIS PAGE OF ABSTRACT UNCLASSIFIED UNCLASSIFIED UNCLASSIFIED III.

SN 7540-31-280-4500

#### Block 5 (Cont'd)

#### Funding Numbers

| PE - 62702F | PE - 61102F | PE - 61102F | PE - 33126F | PE - 61101F |

|-------------|-------------|-------------|-------------|-------------|

| PR - 5581   | PR - 2304   | PR - 2304   | PR ~ 2155   | PR - LDFP   |

| TA - 27     | TA - J5     | TA - J5     | TA - 02     | TA - 27     |

| WU - 23     | WU - 01     | WU - 15     | WU - 10     | WU - 01     |

#### Block 11 (Cont'd)

This effort was performed as a subcontract by the State University of New York at Buffalo to Syracuse University, Office of Sponsored Programs.

| Access | ion For              |       |

|--------|----------------------|-------|

| NTIS   | GRA&I                |       |

| DTIC 3 | EAB                  |       |

|        | sunced               |       |

| Just 1 | ciuation_            |       |

|        | lbution/<br>lability | Codes |

| Avel   |                      |       |

|        | Aveti en             |       |

| Dist   | Specia               | -     |

| 1.     |                      |       |

| D'     |                      |       |

| 11,    | 1 1                  |       |

## 3 THE VERSATILE MAINTENANCE EXPERT SYSTEM (VMES) RESEARCH PROJECT

#### Report submitted by:

Dr. Sargur N. Srihari, Principal Investigator

Dr. Stuart C. Shapiro, Co-Principal Investigator

Dr. Shambhu J. Upadhyaya, Co-Principal Investigator

Jiah-shing Chen, Graduate Research Assistant

Amruth Kumar, Graduate Research Assistant

Joongmin Choi, Graduate Research Assistant

Sudip Nag, Graduate Research Assistant

Scott S. Campbell, Computer Programmer/Analyst

Department of Computer Science SUNY at Buffalo 226 Bell Hall Buffalo, NY 14260

#### TABLE OF CONTENTS

| 3.1    | TEC   | HNICAL OVERVIEW                                  | 5  |

|--------|-------|--------------------------------------------------|----|

|        | 3.1.1 | Executive Summary (1984–1989)                    | 5  |

|        | 3.1.2 | Device Modeling                                  | 5  |

|        | 3.1.3 | Interfaces                                       | 6  |

|        | 3.1.4 | Model-based Reasoning                            | 6  |

|        | 3.1.5 |                                                  |    |

|        | 3.1.6 | Diagnosis of Printer Buffer Board                |    |

|        | 3.1.7 | Migration of Deep Knowledge to Shallow Knowledge |    |

|        | 3.1.8 | Enhancements of SNePS                            |    |

|        | 3.1.9 | Possible Extensions                              | 9  |

| 3.2    | DEV   | ICE REPRESENTATION                               | 11 |

|        | 3.2.1 | Introduction                                     | 11 |

|        | 3.2.2 | Knowledge of Versatile Diagnosis                 | 11 |

|        | 3.2.3 | Logical and Physical Knowledge in Diagnosis      |    |

|        | 3.2.4 | Structural Representation                        |    |

|        | 3.2.5 | Functional Representation                        | 20 |

| 3.3 IN | INT   | ERFACES                                          | 23 |

|        | 3.3.1 | Natural Language Graphics                        | 23 |

|        |       | Frontend: User Interface to Encode Devices       |    |

| 3.4    | DIA   | GNOSTIC REASONING USING MEASUREMENTS             | 29 |

|        | 3.4.1 | Introduction                                     | 29 |

|        | 3.4.2 | Candidate Ordering, Reordering and Elimination   |    |

|        | 3.4.3 | Termination of Diagnosis                         | 30 |

|        | 3.4.4 | Analysis                                         | 31 |

|        | 3.4.5 | Simulation Results                               | 33 |

|        | 3.4.6 | Discussion                                       | 33 |

| 3.5    | REP   | RESENTATION AND DIAGNOSIS OF SEQUENTIAL CIR-     |    |

|        | CUI   | TS                                               | 37 |

|        | 3.5.1 | Introduction                                     | 37 |

|        | 3.5.2 | Representation of Sequential Circuits            | 37 |

|        | 3.5.3 | Handling Feedback in Sequential Circuits         | 38 |

|        | 3.5.4 |                                                  |    |

|        | 3.5.5 | Diagnosis of Sequential Circuits                 | 41 |

|        | 3.5.6 |                                                  |    |

|        | 357   | Conclusio"                                       | 44 |

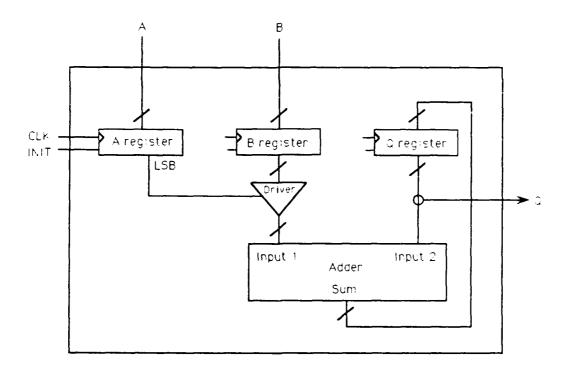

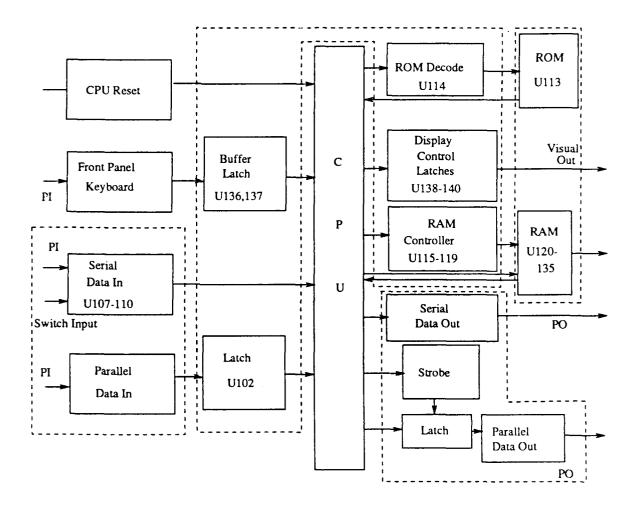

| 3.6  | NEW TEST DEVICE                                                                       | 45         |

|------|---------------------------------------------------------------------------------------|------------|

|      | 3.6.1 Introduction                                                                    | 45         |

|      | 3.6.2 Physical Description                                                            | 45         |

|      | 3.6.3 Operational Description                                                         |            |

|      | 3.6.4 Representation and Diagnosis                                                    |            |

|      | 3.6.5 Conclusion                                                                      |            |

| 3.7  | A SCHEME FOR SHADOWING GENERAL KNOWLEDGE BY ITS INSTANCES                             | 49         |

|      |                                                                                       |            |

|      | 3.7.1 Introduction                                                                    |            |

|      | 3.7.2 Automatic Migration of General to Specific Knowledge                            |            |

|      | 3.7.3 Shadowing General Knowledge by Its Instances                                    |            |

|      | 3.7.4 An Implementation: SNePS                                                        |            |

|      | 3.7.5 An Application                                                                  |            |

|      | 3.7.6 Conclusion                                                                      | 64         |

| 3.8  | CONCLUSION                                                                            | 65         |

| 0.0  | 3.8.1 Accomplishments                                                                 |            |

|      | 3.8.2 Possible Extensions                                                             |            |

|      | 3.0.2 Possible Extensions                                                             | 00         |

| 3.9  | REFERENCES                                                                            | 69         |

| 3.10 | VMES PUBLICATIONS IN 1989                                                             | 73         |

| 3.11 | TRIPS FUNDED BY RADC                                                                  | <b>7</b> 5 |

| 3.12 | STUDENTS DIRECTLY FUNDED BY NAIC, 1985-1989                                           | 77         |

| 3.13 | DEPARTMENT STATISTICS: ARTIFICIAL INTELLIGENCE                                        | 79         |

| 3.14 | PH.D. GRADUATES IN ARTIFICIAL INTELLIGENCE                                            | 81         |

| 3.15 | MASTER'S DEGREES FROM THE DEPARTMENT OF COMPUTER SCIENCE (1984-1989)                  | 83         |

| 3.16 | ARTIFICIAL INTELLIGENCE FACULTY                                                       | 87         |

| 3.17 | ARTIFICIAL INTELLIGENCE ADDITIONS TO THE DEPARTMENT DURING THE PERIOD OF NAIC FUNDING | 89         |

| 3.18 | ONGOING ARTIFICIAL INTELLIGENCE DISSERTATIONS                                         | 91         |

### 3 THE VERSATILE MAINTENANCE EXPERT SYSTEM (VMES) RESEARCH PROJECT

#### 3.1 TECHNICAL OVERVIEW

#### 3.1.1 Executive Summary (1984-1989)

The State University of New York at Buffalo started its participation in the Northeast Artificial Intelligence Consortium in 1984 with the objective of developing a versatile expert system for equipment maintenance. A prototype expert system originally projected to be a rule-based system was designed to advise a maintenance technician on testing. However, during the course of this project, it evolved into a more versatile system by incorporating features such as model-based reasoning and communication capabilities such as natural language and graphics. The new system came to be known as the Versatile Maintenance Expert System (VMES).

VMES research is concerned with the development of a system that could diagnose faults in an electronic circuit and interact with a maintenance technician. Versatility has been the main goal of our research. VMES is designed to be versatile across a range of target devices in the circuit domain, across most of the possible faults, across different maintenance levels and across a variety of user interfaces. To achieve these versatilities, the device model-based approach has been followed. VMES has been implemented in SNePS, the Semantic Network Processing System and has several modules: an expandable component library as its knowledge base, an inference package with diagnostic rules, an active database for diagnosis, a user interface for intermediate users to adapt VMES to new devices by incrementally updating the component library, and a multimedia user interface for end users to interact with VMES for fault diagnosis.

Our accomplishments during the lifetime of the project (1984-1989) can be classified into the following seven categories. (1) Device modeling – structural and functional knowledge and efficient representation, (2) Graphical interface for end users to interact with VMES. (3) Model-based reasoning for diagnosis – initial candidate ordering, reordering and elimination, (4) Sequential circuit representation and a general control structure for diagnosis. (5) Representation and diagnosis of a real device, (6) Migration of deep knowledge to shallow knowledge and (7) Enhancements of SNePS, the system used for the implementation of VMES. In the remainder of this summary, a few more details in each are given.

#### 3.1.2 Device Modeling

VMES uses structural and functional descriptions of devices to avoid difficulties of empirical rule-based diagnosis systems in knowledge acquisition, diagnosis capability and system generalization. Based on the requirements of expressibility, buildability, computer-usability and expandability, a device in the circuit domain has been modeled as a hierarchically arranged set of subparts from both logical and physical perspectives. Wires and points of

contact (POCONs) have been explicitly represented in order to perform the diagnosis of faults in circuit connections.

#### 3.1.3 Interfaces

The usability of VMES would be enhanced greatly if it were to communicate with the maintenance technician graphically as well with text. Toward that end, we developed a general theory of "Graphical Deep Knowledge," defined as declarative knowledge that is projectively adequate (adequate for drawing) as well as deductively adequate (adequate for deducing relevant spatial information). We also made major progress in the field of Natural Language Graphics, the attempt to design a knowledge representation that may be used for graphical deep knowledge and for meaning structures that underly the comprehension and generation of natural language. Using these theories, we designed and implemented graphical interfaces for VMES that can draw the devices being tested, and that can graphically show the reasoning process that VMES is pursuing to diagnose the device.

An interface for encoding devices represented using structural templates and instantiation rules has been implemented to facilitate fault diagnosis. This is user-friendly and robust, providing for as few key-strokes from the user as possible. It fills in most of the invariant template, documents the code and stores it in the appropriate file for the user. It was encoded in Franz Lisp on a VAX to begin with, and was transferred to Common Lisp on a TI Explorer.

#### 3.1.4 Model-based Reasoning

A major step in model-based fault diagnosis has been the generation of candidate sub-modules which might be responsible for the observed symptom of malfunction. After the candidates are determined, each submodule can then be examined in turn. It is useful to be able to choose the most likely candidate to focus on first so that the faulty parts can be located sooner. We have developed a systematic method for candidate ordering that takes into account the structure of the device and the discrepancy in outputs between the observed and expected values. However, because the same good/bad output pattern of a device always gives rise to the same initial ordering, the method has its limitation. For any device and good/bad output pattern, it is easy to come up with an example on which the method does poorly in the sense that the actual faulty part is in the last place of the initial ordering.

To fix this problem, more dynamic methods, candidate reordering and elimination, have been developed. Both methods modify the candidate list as new information becomes available. Reordering moves components connected to the inconsistent inputs of the current candidate to the front of the candidate list and those connected to the consistent inputs to the tail. Elimination removes components which no longer have any non-error-propagating paths to incorrect primary outputs after the current candidate is found not error-propagating. It has been proved that under the single fault assumption, the average

number of components to checked is  $O(\log n)$ , where n is the number of components in the circuit under test. And in general,  $k \log n$  components will be checked when there are k faults in the circuit. As to the implementation, all the above-mentioned theories have been implemented in our VMES system. Also the system has been successfully ported from our UNIX machine using SNePS-79 and Franz Lisp to TI Explorers using SNePS-2 and Common Lisp. The improvement in preformance is enormous. It runs at least ten times faster than before.

#### 3.1.5 Sequential Circuit Diagnosis

In order to incorporate sequential circuit diagnosis into VMES, the following steps have been taken: (1) change in device knowledge representation; (2) change in control structure and inclusion of assumption relaxation; and (3) candidate generation based on electrical behavior. The change in representation was essential for better organization of the device knowledge and the incorporation of sequential components. Devices no more have any physical hierarchy, and logical hierarchy is not related to physical details of the device. This has enabled arbitrary number of logical levels, and has allowed arbitrary grain of focus for diagnosis. Wires were no more represented explicitly. Diagnosis of wires and POCONs was intended to be hard-coded into VMES. Assignable variables were found to be necessary to represent states in sequential components. Since SNePS is built on the philosophy of logical programming, it did not allow for such variables. Hence, the new scheme of representation had been developed in CommonLisp.

The control structure has been streamlined so as to accept various options such as shallow reasoning and diagnosis with multiple symptoms. Explanation is a very necessary part of an expert system and hence, an explanation generation system was also incorporated. The criteria upon which the system should discard single-fault and non-canceling fault assumptions has been worked out and partially implemented. The new system VMES II, with the above modifications, runs considerably faster than the previous system.

Since sequential circuit diagnosis is harder than combinational, the stage of candidate generation had to be exploited to the maximum so as to narrow the focus of diagnosis as much as possible. Therefore, candidate generation based on electrical behavior was researched and implemented. In this method, given the symptom, the system works backward through the subdevices to come up with a probable candidate list. The scheme is based on the assumption that one could shorten the suspect-list by eliminating those of the relevant inputs that can in no way contribute to the observed symptom at output. This knowledge can be conveniently expressed for small devices as fault characteristics and was exploited during diagnosis of large systems.

Sequential circuit diagnosis poses many special problems. A sequential circuit has feed-back loops, and, therefore, it is necessary to specify the start and end of the loops for proper simulation of states. Moreover, during simulation and candidate generation, more than one (as many as the clock cycles) value has to be stored with each device-port. Fault characteristics are not as well behaved for sequential circuits and are to be specified for the

superdevice too. These and many other related problems have/are being solved towards incorporating sequential circuits.

#### 3.1.6 Diagnosis of Printer Buffer Board

Although VMES was intended to be adaptable to a wide range of devices in the domain of digital circuits, selection of a realistic device was essential as a test bed. Upon recommendation by RADC, a Heathkit Printer Buffer Board was selected. This test device, assembled locally, is of reasonable complexity to work with. It consists of an eight-bit microprocessor, two sets of serial and parallel ports, memory and latches. This device has been represented hierarchically at various levels of abstraction to facilitate diagnosis. A device of this kind helped spur new ideas, extensions and refinements to the diagnosis theory.

#### 3.1.7 Migration of Deep Knowledge to Shallow Knowledge

Deductive reasoning systems, including automatic fault diagnosis, usually make use of vast numbers of rules to infer new knowledge from existing knowledge. Different rules may be at different levels of generality. In particular, a method of rule nesting enables a rule to contain a subrule in its consequent. If some instance of the antecedent of the outer rule is satisfied, that instance of the subrule will be asserted in the knowledge base. This subrule has a lower level of generality than its dominating rule. We call this phenomenon the migration of deep to shallow knowledge.

As more specific knowledge emerges from the general knowledge, the speed of inference might become slower if the system tries to use both specific and general rules for similar problems. We need a proper scheme to take advantage of specific knowledge to avoid duplicate inference branches and, in the long run, to realize fast inference. An idea of shadowing general knowledge has been suggested and implemented by exploiting its instance information accumulated in the previous reasoning. A list of instances containing the binding information was maintained for each rule so that this rule can be blocked in the next inference if instances of that rule are already activated with the same binding information. This shadowing strategy is tested for wire-faulty detection rules of the M3A2 circuit, and the result shows a significant improvement in diagnosis speed for the same types of wires.

#### 3.1.8 Enhancements of SNePS

During the course of this project, we have continued the development of the Semantic Network Processing System. This effort resulted in a new major version of the system called SNePS-2.0, and a new minor version, called SNePS-2.1. SNePS-2 represents a major redesign of SNePS, and is implemented in Common Lisp, for maximal portability. SNePS-2.1 incorporates an assumption-based belief revision system (SNeBR) as a standard feature of the system. SNeBR is designed to reason the consistency of rules and hypotheses defined within a particular context or belief space. SNeBR was applied to fault detection

in electronic circuits [Campbell and Shapiro, 1986]. We have ported SNePS to, and have maintained it on over seven different computer systems.

#### 3.1.9 Possible Extensions

The current VMES system can be enhanced in a number of ways. The control structure can be generalized to include various schemes of diagnosis. For instance, a retry method, or direct isolation or intersection isolation can be applied in a sequence to diagnose a circuit. This involves the development of direct and/or intersection isolation techniques and its implementation. Model-based reasoning can be enhanced by incorporating heuristic knowledge in the reasoning process. It is also worthwhile to investigate the effect of multiple tests, test generation techniques, and mixing of procedural and declarative knowledge in diagnosis. The versatility of VMES can be further enhanced by the development and integration of analog circuit component diagnosis. Diagnosis of intermittent faults is another area that needs further investigation.

#### 3.2 DEVICE REPRESENTATION

#### 3.2.1 Introduction

A versatile fault diagnosis system is an expert system that is capable of diagnosing a variety of faults on a wide range of devices in its domain. In this work, issues about knowledge representation for versatile fault diagnosis are investigated with digital circuits as the experimental domain. This domain consists of numerous types of devices with different configurations and functionalities. Automatic diagnosis of faults in digital circuits is highly desirable due to their widespread use and relative short market life cycles as well as the general shortage of qualified maintenance technicians. Our aim is to develop a knowledge representation formalism which is capable of supporting a versatile fault diagnosis system while still retaining the effectiveness of fault diagnosis.

Versatility in diagnosis is multifold: ability to adapt to different devices without extensive knowledge engineering; capability of diagnosing a wide range of common faults; capability of operating at different maintenance levels; and capability of interacting with the user through various media.

Device representation is the task of modeling a device and abstracting it into a representation formalism suitable for a specification-based system. As knowledge engineering is to empirical-rule-based systems, device modeling/representation is the key to the success of a device-model-based fault diagnosis system, since its major power comes from knowledge about the structure and function of a device. While much work has been done in the area of knowledge engineering for empirical-rule-based systems Feigenbaum, 1979, Quinlan, 1982. Waterman, 1979, Williams, 1986, little has been done in device representation for devicemodel-based systems, and most current device representation schemes are either improper or insufficient for fault diagnosis. Computer hardware description languages such as ISP [Siewiorek, 1974a], PMS [Siewiorek, 1974b] and Zeus [German and Lieberherr, 1985] are designed for communication between computer designers, but not for the purpose of fault diagnosis Barbacci and Uehara, 1985, Chu, 1974. Other existing device description schemes for fault diagnosis are either ad hoc or insufficient to support a versatile fault diagnosis system Examples are the predicate logic representation used by Genesereth Genesereth, 1984, and the schematic diagram representation language designed by Davis Davis and Shrobe, 1983...

#### 3.2.2 Knowledge of Versatile Diagnosis

It has been argued that the performance of an expert system depends mostly on the contents and the forms of its knowledge, since it is the major resource of its reasoning [Buchanan and Shortliffe, 1984, Hayes-Roth +t al., 1983, Michie, 1980]. In this section, we first analyze the knowledge for troubleshooting electronic circuits, and identify the core knowledge for versatile fault diagnosis. We discuss how domain experts coordinate different views of a same

device in diagnosing and repairing it, and the difficulties they might have in coordinating the different views.

#### Knowledge Analysis and Characterization

In analyzing the knowledge used in circuit diagnosis, we suggest that the knowledge be categorized as device-specific empirical associations, generic domain knowledge, and a device model.

Device-specific empirical associations relate observed symptoms to possible fault hypotheses for a specific device. Such rules are highly device specific, and cannot apply to other devices in the same domain, since devices in the same domain may have different structures.

Generic domain knowledge is the general knowledge in the designated domain that domain experts use for fault diagnosis. A very primitive piece of generic knowledge for circuit fault diagnosis is that "when an output of a device deviates from the expected value regarding to the known inputs, it implies that the device is malfunctioning". Another one is that "to locate the faulty component(s), one should first identify the signal flow paths from inputs to the bad output, this can be efficiently done by back-tracing the connections from the bad output to the relevant inputs". The domain knowledge is not necessarily very primitive, it may also relate to higher human perception as in the example of "a burnt appearance of a component implies that the component is a potential faulty part".

A model of the target device, which consists of the structural and functional information about the device, is maintained by the technician when troubleshooting electronic circuits. Though the model is device specific, unlike device-specific empirical associations, a model of a device is "public" knowledge which is highly structured and readily available at the time when the device is designed. This model is sometimes referred to as a "mental model" of the device since it is the technician's view of a device when troubleshooting it [Rasmussen and Jensen, 1974]. This model is also referred to as a "design model" of the device, since it usually reflects, though not always necessarily, the design of the device [Genesereth, 1982].

#### Core Knowledge of Versatile Fault Diagnosis

In analyzing the knowledge used by maintenance technicians for troubleshooting electronic equipment, it turns out that human experts use all kinds of knowledge described above, viz., device-specific empirical associations, generic domain knowledge, and a model of the target device, in an intermixed manner.

In attempting to combine all knowledge to facilitate diagnosis, a two-level architecture has been proposed for neurological diagnosis [Xiang and Srihari, 1986], which suggests that the system that the system first works on the empirical-association-based module, and then turns to the device-model-based module if the problem can not be successfully solved by the first module. Two reasons convince us that we will not adopt this idea. First, human experts usually use all sorts of their knowledge in an interleaving or mixed manner for fault diagnosis. A sharp partition of knowledge into two separate working modules seems

unrealistic to us. Second, our research is to develop a device representation scheme to support a versatile fault diagnosis system, and the inclusion of empirical associations at this point may impair the construction of such a versatile system.

As mentioned before, versatility of an automatic fault diagnosis system is extremely important in an electronic circuit domain due to the fast rate at which new products are introduced and their relatively short market lives. In noticing that an experienced technician is able to effectively troubleshoot an electronic device by using the schematic diagrams of the device and his general knowledge about troubleshooting devices in the domain and without having to learn how the device may fail, we define an automatic versatile fault diagnosis system as an expert system which behaves like an experienced technician who is competent in diagnosing devices he has never seen before. A major point here is that a versatile fault diagnosis system should be able to be adapted to new devices easily, just like an experienced technician does.

Device-specific empirical associations are quite different from the knowledge of a device model in both the contents and the representation forms. Device-specific empirical associations are assertive knowledge (or propositions) relating symptoms to possible faults. It is natural to represent them as production rules. Knowledge of a device model is basically descriptive, and can be best represented as semantic networks or as frames. There are two major hurdles in including the device-specific empirical associations in a versatile fault diagnosis system: techniques in acquiring it by interviewing with domain experts through knowledge engineering have to be improved so that this process will not slow down the adaptation of the system to other devices; and the capability of an expert system in selecting and using proper knowledge at proper time from a knowledge-base (or knowledge-bases) containing various types of knowledge in different forms has to be achieved so that the system can have an acceptable performance.

One major consideration in developing a versatile fault diagnosis system is the system's ability in adapting itself to other devices. It is improper to include the device-specific empirical associations in a versatile maintenance system, since this may impair system versatility, and moreover, this kind of knowledge is not available at all for newly designed devices. Therefore, only the generic domain knowledge and the knowledge of a device model should be incorporated into a versatile fault diagnosis system. In mimicking the versatility of experienced maintenance technicians in troubleshooting devices they had never seen before, the generic domain knowledge is transformed into the search algorithms and diagnosis rules of the fault diagnosis system, and the knowledge of a device model, which is the basis of the system's reasoning, becomes the core knowledge of the system.

#### 3.2.3 Logical and Physical Knowledge in Diagnosis

The emphasis of most previous research on the device-model-based approach to fault diagnosis has been on using the logical structure of a target device. Such a representation emphasizes the functional interrelations of components but not the physical interrelationships, e.g., functionally unrelated components may be physically related (adjacent, in the

same area, etc.). However, knowledge about physical device structure often plays an important role in fault diagnosis performed by human technicians. This research explores the representation and use of knowledge about both logical and physical structures of target devices in a versatile maintenance system. In particular, we examine the relationships (cross-links) between logical and physical structures.

The use of physical structure in a diagnostic problem in the medical domain, viz., neurological diagnosis based on a model of neural pathways in the human spinal cord, was explored by Xiang and Srihari Xiang and Srihari, 1985. In their system, two functionally unrelated paths may be examined due to their physical proximity. In the domain of circuit diagnosis there is little in the literature on physical structure representation with the exception of references made by Davis [Davis and Shrobe, 1983, Davis, 1984]. He suggests including a physical description based on the notion that different paths of interaction or adjacency should be represented to diagnose different kinds of faults. A particular application of utilizing the physical structure description of the device is demonstrated as the diagnosis of bridge faults under the assumption that bridges can only occur between two adjacent pins of an IC (integrated circuit) chip. Although the result is effective and impressive, there are two limitations. First, human experts can visually locate a bridge fault easily by exhaustively searching (looking around) the suspected local area without the complicated reasoning i.e. suggested. When computer vision techniques are unavailable, it may be proper to rely on the user to pinpoint the bridge fault without the strict assumption that bridge faults can only occur between two adjacent pins of an IC chip. Based on this argument, a better role of the automatic fault diagnosis system is to locate and direct the user to the suspected area. Moreover, we find that human experts do maintain a model of the physical structure of the device being diagnosed, but they use it in a more general manner, which is not limited to troubleshooting a bridge fault.

Human diagnosticians for electronic devices seem to simultaneously maintain models of the logical and physical structures of the target device. They carry out most of the diagnostic reasoning over the logical structure of the device due to its functional association. While carrying out the reasoning, the logical structure is apparently mapped to the physical structure from time to time. Tests and measurements are first initialized using the logical structure, and then are realized and executed on the physical structure. Repair, which is usually done by replacing a physical unit or by fixing a physical connection, is planned and done on the physical structure. In other words, maintenance technicians use a model of physical structure of the target device, which is a hierarchically arranged set of replaceable physical components at various maintenance levels such as field-level and depot-level. By mapping the logical structure of the device to its physical equivalent, maintenance technicians are able to terminate the diagnostic process at the right moment and to form an adequate repair plan.

Given that the mapping between the logical structure of the device and its physical equivalent happens throughout the diagnostic process at all hierarchical levels, the speed in carrying out the mapping is critical to the time needed to locate faults. This implies that objects on both the logical level structure and the physical structure of the device should

be closely linked to each other so that the mapping is done efficiently. Even experienced technicians may have difficulty in locating a point of a schematic diagram on the real device, where the schematic diagram represents the logical structure of the device, and the form of the real device is the physical structure; which is attributable to a lack of cross-links at all hierarchical levels of the device in human memory. On the other hand, when modeling and representing a device in an automatic fault diagnosis system, the cross-links between its logical structure and physical structure can be modeled and represented to an appropriate level of detail.

#### 3.2.4 Structural Representation

In our system, a device is abstracted as a hierarchically arranged set of objects, and each object is abstracted at two levels. At level-1 abstraction, an object is modeled as a module with ports; and at level-2 abstraction, the structures of the object is envisioned. An object is represented according to these two abstraction levels from both logical and physical perspectives. Abstractions of an object at these two levels are represented by SNePS rules and SNePS assertions. The former are categorized as instantiation rules and the latter as structural template. The representation for cross-links between the logical structure and the physical structure is also discussed.

#### Instantiation Rules as the Level-1 Abstraction

At level-1 abstraction, knowledge about a component type is represented as a SNePS rule. The rule is used later on to instantiate an object of the component type as a module with its own ports and associated functional descriptor. The functional descriptor contains information about the functional description of the component type. The instantiation rule for a physical component type is a little bit simpler in that it contains no functional information of the component type.

#### Logical Structure

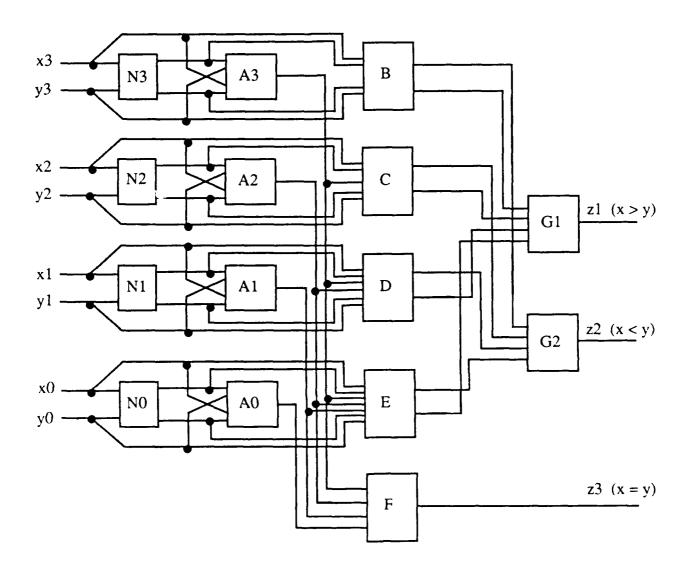

The instantiation rule for objects of the M3A2 type is shown in the SNePSUL (SNePS User Language) command form in Figure 3.2.1. The first three lines of the instantiation rule says that "if x is an M3A2-type object, which is a logical object, and it is to be instantiated at its level-1 abstraction (IRfL1), then do the following". The next five "cq's" will instantiate the ports of the object when this rule is executed. I/O ports of an object are the places where the input/output values of the object are stored. Measured (observed) I/O values depict the real behavior of the object, and calculated I/O values show its expected (normal) behavior. The last two "cq's" create the functional descriptors of the object; functional descriptors are pointers to the representation of the function of the object. The first one says "in order to simulate (calculate) the value of the first output, use the function M3A2out1 which takes three parameters, viz., the inputs of the object x in order". The "tolrnc" denotes the tolerance allowed for a measures value when compared to the calculated value. This is

Figure 3.2.1: Instantiation rule for M3A2 type objects

especially important for analog components, and is usually set to zero for digital devices. Similar functional descriptors can be included for the input ports if the inference of input value from outputs is desired (these are not shown in the figure).

#### Physical Structure

The instantiation rule for objects of the MAC3200 type is shown in Figure 3.2.2 "MAC3200" is the physical equivalent of the logical component type "M3A2". The first three lines of the instantiation rule says the "if x is an MAC3200-type object, which is a physical object, and it is to be instantiates at its level-1 abstraction (IRfL1), then do the following". The next twenty "cq's", which are shown in partial to save space, will instantiate the

Figure 3.2.2: Instantiation rule for MAC3200 type objects

twenty ports of the object when this rule is executed. The instantiation rule for a physical component type is quite similar to that for a logical type component type except that all ports of a physical object are P-PORTs, which are functional (logically) neutral, and thus no functional descriptors are associated with these ports.

#### Structural Templates as the Levei-2 Abstraction

At level-2 abstraction, a structural template, which is implemented as a SNePS assertion, is used to describe the subparts of a logical object at the next hierarchical level, and the wire connections between the object and its subparts, as well as those among the subparts themselves. Since wires are eliminated from the physical abstraction, the structural templates of a physical component type only contain descriptions of its non-wire subparts.

#### Logical Structures

The structural template representation is shown in Figure 3.2.3. The representation can be viewed as consisting of five parts—an identification section, a subparts section, a connections section, a part-links section. The last two sections in a structural template, whose contents are missing in the above SNePSUL command, concern the cross-links between the logical structure and the physical structure of a device, and are discussed later.

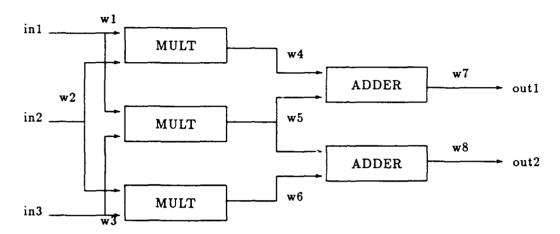

The identification part, which consists of the first three lines of the SNePSUL "build" command if Figure 3.2.3, denotes that the representation is the structural template for the logical component type M3A2 at the level-2 abstraction (STfL2). The subparts section describes the subparts of the component type at the next hierarchical level. A new case-frame, "id/type", is introduced to describe the subparts of a logical component type within its structural template. The "id" is composed of the name of the component type, i.e., M3A2, and a unique id, such as M3, A1, and W6, within the component type. It identifies the subpart in the rest of the structural template; it also serves for name extension of the subpart when it gets instantiated. For instance, if D1 is an M3A2 device, and its first subpart, which is identified as M3A2-M1 in the structural template, is being instantiated, the subpart will be instantiated with a name of "D1-M1". The part "type" of the subpart specifies its component type; this information is needed when the subpart is to be instantiated. The connections section of the structural template specifies the connections. Note that connections by port superimposition and by POCON (point of contact) are treated differently as discussed in [Taie and Srihari, 1987].

A structural template provides the necessary knowledge about the sub-structure of all objects of same component type without representation overhead. Unlike instantiation rules, structural templates are never executed (fired) to produce a representation for any specific object. When reasoning on the sub-structure of an object is required, instead of instantiating the sub-structure (all the subparts and connections) and then reasoning on the resulted representation, we do it directly on the structural template of the object. If suspicious subparts are located, they (but not all subparts) instantiated at their level-labstractions using proper instantiation rules for further examination.

```

(build

type M3A2

abs-lv STfL2

modality logical

sub-parts ((build id M3A2-M1 type MULT)

(build id M3A2-M2 type MULT)

(build id M3A2-M3 type MULT)

(build id M3A2-A1 type ADDER)

(build id M3A2-A2 type ADDER)

(build id M3A2-W1 type WIRE3)

(build id M3A2-W2 type WIRE3)

(build id M3A2-W3 type WIRE3)

(build id M3A2-W4 type WIRE2)

(build id M3A2-W5 type WIRE3)

(build id M3A2-W6 type WIRE2)

(build id M3A2-W7 type WIRE2)

(build id M3A2-W8 type WIRE2))

connections

((build equiv (findorbuild type B-PORT port-of M3A2-W1 id 1

signal (findorbuild type D bit-width 2))

equiv (findorbuild type I-PORT port-of M3A2 id inp1

signal (findorbuild type D bit-width 2)))

(build contact (findorbuild type B-PORT port-of M3A2-W2 id 2

signal (findorbuild type D bit-width 2))

contact (findorbuild type I-PORT port-of M3A2-M1 id inp1

signal (findorbuild type D bit-width 2)))

. . . . . )

part-links (....)

port-links (....))

```

Figure 3.2.3: Structural template for M3A2 type objects

#### (build

Figure 3.2.4: Structural template for MAC3200 type objects

#### Physical Structure

The structural template representation is shown in Figure 3.2.4. Unlike the structural template for a logical type, which consists of five sections, the structural template for a physical component type has only two component sections: the initial section and the subparts section. This is because the wires are eliminated from the physical representation of a device, thus no connection is to be specified, and because the cross-links between the logical structure and the physical structure have been specified at the structural template of the logical component type or elsewhere as will be discussed later.

The identification part, which is the first three lines of the SNePSUL "build command", denotes that the representation is the structural template for the physical component type MAC3200 at its level-2 abstraction (STfL2). The subparts section describes the subparts of the component type at the next hierarchical level. A new semantic network case-frame, "id/type/mntn-lv", is introduced to describe the subparts of a physical component type within its structural template. The meaning and use of part "id" and part "type" are the same as those in a structural template for a logical component type as described in the last section. The "mntn-lv" indicator shows the intended maintenance level of the subpart, in the maintenance level where the subpart, if found faulty, is replaced without further diagnosis. These informations are used for instantiating a physical subpart.

Knowledge about the intended maintenance level is associated with the physical structure of a device because the repairment of a device is performed based on the physical model of the device. It is adequate to store the "mntn-lv" (maintenance level) tag of an object at the subpart section of the structural template of the object's super-part. A more straightforward way is to store the "mntn-lv" tag at the instantiation rule of each component type, but this may cause problems. The reason is that "mntn-lv" values of objects with same component type may be different when they are used in different devices. For instance, as AC00 chip (an adder) may have a different "mntn-lv" value of DEPOT when it is a subpart of Air-Force-Device-1, and have a different value as FIELD when it is a subpart of

Navy-Device-3. This implies that the "mntn-lv" value of an object is not only complexity dependent but also environment-sensitive, and thus it should be stored at the subpart section of structural templates rather than at the instantiation rule. Though currently, only FIELD and DEPOT levels are used in VMES, "mntn-lv's" and the corresponding system parameter VMES-IML, which stores the intended maintenance level of a diagnostic session, can be set to any arbitrary maintenance level by the user if desired.

#### Cross-Links between Logical and Physical Structures

There are two kinds of cross-links between the logical and physical structure of a device. The first kind is the cross-links for components. The second kind is the cross-links for ports. Like representing the level-2 abstraction of a device for its sub-structures, the cross-links between the logical and the physical structures is implemented as structural templates to remove any representation redundancies. The cross-links for components are specified in the part-links section of the structural template of the logical object, and the cross-links for ports are specified in the port-links section as partially shown in Figure 3.2.5.

#### 3.2.5 Functional Representation

The function of an object in the electronic domain can be best abstracted as the relationship between its inputs and outputs. The functional description should be usable to simulate the component behavior, i.e. to calculate the values of output ports if the values of the input ports are given. It should also be usable to infer the the values of the input ports in terms of the values of other I/O ports. This is important if hypothetical reasoning is used for fault diagnosis. Though at this stage, VMES only uses the functional description to calculate values at output ports, our representation scheme can be used both ways.

As depicted by the instantiation rule for M3A2 type, a functional descriptor of a port contains a pointer to its functional description as well as other information concerning the use of the functional description. The functional description itself is implemented as a LISP function which calculates the desired port value in terms of the values of other ports. Every port of a component type has such a function associated with it. The functional descriptions for the output ports of the component type M3A2 are shown in Figure 3.2.6.

Some different ports of different component types might have the same function, some functions can be shared. For instance, the simple function "ECHOback", which simply returns its input, can be shared by several different component types, viz., by the type "super-buffer", the type "wire" and the type "one-to-one transformer". All these component types show the same behavior at out level of component abstraction: they echo the input to the output.

```

(build

type M3A2

abs-lv STfL2

modality logical

sub-parts (....)

connections (....)

part-links ((build object M3A2-M1 inside MAC3200-U3)

(build object M3A2-M2 inside MAC3200-U3)

(build object M3A2-M3 inside MAC3200-U1)

(build object M3A2-A1 inside MAC3200-U4)

(build object M3A2-A2 inside MAC3200-U2))

port-links ((build equiv (findorbuild type I-PORT port-of M3A2-M1 id inp1

signal (findorbuild type D

bit-width 2))

equiv (findorbuild

bit (findorbuild type P-PORT

port-of MAC3200-U3

id 1)

lo-bit (findorbuild

bit (findorbuild

type P-PORT

port-of MAC3200-U3

id 3))))

....))

```

Figure 3.2.5: Cross-links between logical and physical structures

Figure 3.2.6: Output functions for M3A2 type objects

#### 3.3 INTERFACES

#### 3.3.1 Natural Language Graphics1

#### Introduction

Natural Language Graphics (NLG) deals with diagram generation driven by natural language utterances. This investigation applies the methods of declarative knowledge representation to NLG systems. Declarative knowledge that can be used for display purposes as well as reasoning purposes is termed "Graphical Deep Knowledge" and described by supplying syntax and semantics of its constructs. A task domain analysis of Graphical Deep Knowledge is presented covering forms, position, attributes, part, parts, classes, reference frames, inheritability, etc.

Part hierarchies are demonstrated, and criticism of traditional inheritance-based knowledge representation formalisms is derived from this finding. The "Linearity Principle of Knowledge Representation" is introduced and used to constrain some of the presented knowledge structures. The analysis leading to Graphical Deep Knowledge also results in the description of two fundamental conjectures about knowledge representation.

The Gricean maxims of cooperative communication are used as another source of constraints for NLG systems. A new maxim for technical languages is introduced, the "Maxim of Unnecessary Variation". It is argued that common symbolic representations like circuit board diagrams have not yet been described in literature by explicit feature analysis, and that this in necessary to give a system knowledge about the meaning of the diagram it is displaying.

Part of the developed theory has been implemented as a generator program that creates pictures from knowledge structures and as an ATN grammar that creates knowledge structure; from limited natural language input. The function of the picture generation program (TINA) as a user interface for a VMES has been demonstrated. An older version of TINA incorporates a module of "Intelligent Machine Drafting" (IMD), a completely new subfield of AI that has been introduced in this research and that relates to Computer Aided Design (CAD). The IMD program does layout and routing for the members of a simple class of functional circuit diagrams based on a policy of symmetry and equal distribution over the available space. This layout/routing is based on cognitive requirements as opposed to physical requirements used by CAD systems.

<sup>&</sup>lt;sup>1</sup>This section is a condensation of a paper by J. Geller, "Natural Language Graphics for Human Computer Interaction". Submitted to the International Journal of Man-Machine Studies.

#### Representational Constructs of Graphical Deep Knowledge

#### Form Knowledge

A number of different scientific subfields and fields have been interested in the representation of forms. Among these are computer vision, computer graphics, and imagery, but also solid modeling computer aided design (CAD) and character recognition. We argue [Geller, 1988] that no representation in any of these fields satisfies the requirements for graphical deep knowledge. These requirements are:

- The representation should be projectively adequate.

- The representation should be deductively adequate.

- The representation should be based on conceptual primitives that seem natural to the human observer.

- The representation should support relations between primitives which are natural to humans.

- The representation may contain redundant information.

To fulfill these requirements a representation that consists of basic forms (icons) and asserted relations is used. The basic forms are (supposed to be) meaningful to human observers. Every basic form is represented as a procedure that has three properties. (1) The procedure consists of calls to graphics primitives. (2) Executing a procedure of the name < name > results in the drawing of an object that is described by < name >. (3) The procedure < name > is accessible as a concept in the knowledge representation system, i.e., it functions simultaneously as a node in a semantic network. The representation of a basic form is therefore projectively adequate and also a conceptual unit. Relations between icons are represented propositionally.

The SNe<sup>DS</sup> system is used in the following way to accommodate the described form representation. The name of every basic form in the system is a base node in the SNePS semantic network. The SNePS inference machine treats it as a conceptual unit and permits reasoning about it. At the same time every SNePS node is also an uninterned LISP atom. This atom refers<sup>2</sup> to a LISP function made up of calls to graphics primitives from a LISP graphics package. Objects and forms are separate nodes, linked by an asserted proposition. This conceptual separation of forms and objects makes it possible to associate a form with a class of objects, instead of a single object.

#### Part Hierarchies

Part hierarchies have been of fundamental importance in a number of different areas of artificial intelligence. Knowledge representation has dealt with them as well as hardware modeling in maintenance and research in computer vision.

<sup>&</sup>lt;sup>2</sup>The linkage of the function has been handled differently depending on the dialect of LISP used. Our favorite solution has been to use the function cell of an interned atom of the same name as the node.

Our interest in part hierarchies is motivated by the need for a method to decide "what content" to put on the screen of an NLG system and "how to organize it," to be optimally useful to a viewer. In KBUIMS (knowledge based user interface management system) design this complex of problems has been referred to as "presentation planning".

Part hierarchies permit a strategy to decide what to show and how to avoid information overload: don't show all the parts of a requested object. If a simple display is expected, just show an integral object. If a more informative display is expected, then show the integral object with its parts. More generally, control the complexity of a display by selecting the number of levels of the part hierarchy that are shown on the screen.

#### The Class Hierarchy

In our theory a non-tangled class hierarchy is used for standard downward inheritance. However, we also supply a limited upward inheritance facility. We find justification for this in the psychological research on categorization. The cognitive science literature reports three different approaches to categorization the classical approach, the prototype approach and the exemplar approach. The classical approach has been but totally rejected from a cognitive point of view. It requires that every member of a class is described by necessary and sufficient conditions.

The prototype view as developed by E. Rosch [Rosch, 1978] describes a "prototype" as a summary description of all the members of a class. The third theory of categorization is the exemplar view. The exemplar view differs from prototype theory in the following way. The summary description used by prototype theory is not necessarily identical to any existing member of the category. Exemplar theory on the other hand postulates the use of one or more stored real exemplars of the category, in other words no summary description exists.

The exemplar view of categorization permits us to think in terms of upward inheritance from an individual to a class, because if we do not assume a summary description we may not associate attributes with it, and then the only source to derive inherited attributes from are other exemplars. This implies that it must be possible to inherit attributes from one exemplar upwards to a class and then back downwards to another exemplar.

For example, a knowledge base in our system might contain an object with no specified form that belongs to a class hierarchy. Classical downward inheritance would search up in the hierarchy until at some higher level a form is encountered. However, it might happen that no form is found anywhere in the hierarchy. In our interpretation of the exemplar theory it is valid to do a "down" search in the hierarchy for an object that belongs to the same class as the current focus object, and to inherit an existing form with "up-and-down inheritance" for it.

The idea of up-inheritance is not popular in AI. It is either ignored or explicitly prohibited. For instance, knowledge representation of the NETL style [Fahlman, 1979] which is based on marker passing, prohibits the idea of inheritance according to an up-and-down-movement because if one would permit markers to move up and down in the network the whole network would eventually be marked.

One is tempted to interpret up-and-down inheritance by considering the first step (the up-inheritance) as a form of generalization or inductive learning. However, this is not what we have in mind, because the representation of the class itself is "not" changed by a step of up-and-down inheritance. If a class should have many members only one of which has a form, and if this form should be changed after one application of up-and-down inheritance, then the second application of this inheritance rule will supply the new form, not the old form. Were we talking about a step of generalization, then the class would preserve the form after the first use of up-inheritance.

Are we then making a decision for the universal use of exemplar inheritance and against prototype theory? Clearly this is not our intention, because up-and-down inheritance is "only" used when no sufficient information is associated with the classes used for inheritance i.e., when our version of a summary description fails. We do not eliminate the use of a summary description!

For practical purposes we have limited the use of up-and-down inheritance in two ways. Up-search is done only from the lowest level, the level of the individuals, to the level immediately above it, i.e., to the lowest level of classes. If there is no other member in this class, or if the other members do not carry the desired information, then up-and-down inheritance fails. One can argue that this does not make complete use of the class hierarchy, but it seems like a reasonable compromise, because humans use hierarchies that are flat and bushy. Rosenfeld has even argued that it is not necessary to view operations on hierarchies as recursive to an arbitrary depth, because this constitutes an unnecessary effort if one has only a flat hierarchy.

Secondly, up-and-down inheritance is used only for information that is urgently needed, and not as the default case. In a graphics system the one item of information that is obviously needed most is the form of an object, for which no "reasonable defaults" can be supplied. We will now formally define up-and-down inheritance which we also refer to as exemplar inheritance.

Definition: Exemplar Inheritance. If an individual is missing information about an important property, and this property cannot be derived by inheritance from a superclass of the individual, then the property may be inherited from any of the other members of the *immediate* superclass of the individual.

In our domain only "forms" are considered important, and we have therefore decided not to represent the fact that a property is important by an explicit assertion.

It is not yet clear what happens when several members of a class offer different properties for upward inheritance. In such a case a combined strategy of majority and recency may be used.

#### Reasoning

The major reason for introducing the notion of graphical deep knowledge as separate from graphical knowledge has been the interest in doing reasoning about graphical structures. The first step of making a corpus of representations accessible to logic based reasoning is

to transform it into a well formed declarative format with a defined syntax and semantics. It has been the approach of this investigation to limit the procedural representations which at some point are not avoidable in graphics to a small area, namely to iconic primitives. All conceptual relations between these iconic primitives are represented declaratively.

The second step is to formally define reasoning patterns. SNePS provides two different facilities for doing so, a system of rules and a system for defining paths. Although the rules that can be defined are very powerful and permit quantification as well as the use of non-standard connectives we have chosen to concentrate in our implementation on the use of paths which are more efficient.

Path based inference in SNePS assumes that one has a node of a well specified category available (typically an "object") and follows the arcs that are pointing to this node backwards until one hits a node describing unknown and interesting information (for instance a "form" or one coordinate of a position). The well specified case frames of GDK assure that if the required information exists at all in the network, then it will be reachable by a well defined path.

#### Maintenance Interface

The use of the TINA program as a graphics interface of the VMES project is described in this section. The VMES system consists of a maintenance reasoner and a graphics interface. The graphics interface is an application of an older version<sup>3</sup> of the TINA program. The task of the maintenance reasoner is to identify a faulty component in a given device, usually a circuit board. The maintenance reasoner and the display program share a knowledge base realized as a SNePS network.

During the process of identifying a faulty component in a device, the maintenance reasoner repeatedly updates the shared knowledge base. It categorizes components as being in a "default state", being in a state of violated expectation, being recognized faulty or being suspected to be faulty. Information about any of these states is asserted in the network, using the attribute case frame described earlier on. Whenever the maintenance reasoner wants to express changes in its state of knowledge about the analyzed device, it executes a call to TINA. TINA presents the current state of the maintenance process to the user. This is done by mapping attributes into signal colors (red = faulty, blue = default, green = suspect, magenta = violated expectation).

Typically a device will be displayed completely blue in the beginning. After finding a violated expectation, for instance a port that has a wrong voltage value, this port will receive an attribute "violated expectation". The device will now be blue, except for the port in question which will be magenta. Finally, after several steps of reasoning and redisplay, the device will be shown in blue with the faulty component(s) in red.

The procedural interface between maintenance reasoner and display program consists of the TINA function only! All other communication is done through the shared knowledge base that both parts of the program have access to. Our experience with this type of

<sup>&</sup>lt;sup>3</sup>Based on a VAX 11/780 and a GIGI graphics terminal.

programming has been that it is exceedingly easy to combine two independently developed modules. To our own surprise no integratory debugging was necessary!

#### 3.3.2 Frontend: User Interface to Encode Devices

FRONTEND is a user-friendly piece of software designed to help encode circuit devices in the representation, to perform the diagnosis. In it, basically, the user is:

- (1) asked to specify what he wants to encode: physical or logical instantiation-rule, structural-template, or cross-links;

- (2) asked questions to elicit the details of the device being represented. The segments of representation code that do not change from device to device are automatically filled in.

- (3) led through the various segments of device representation, in order. Thus, any possibility of missing out on some segments of the representation, is totally avoided.

- (4) informed to the extent possible, what type of an answer is expected for each question. e.g., D(igital) / A(nalog). Questions are framed as clearly as the topic permits. eg., "What is the physical bit corresponding to the MSB of the remaining 5 bits?".

- (5) offered the ease of answering in as few key-strokes as possible. The emphasis of the package is on cutting to a minimum, the drudgery of the author.

The following are the special features of FRONTEND:

- (1) Files are named, opened and closed automatically. When a device is completely coded, the name of the file where the representation of the device can be found, is displayed for convenience.

- (2) Each file is documented automatically. Documentation includes the last name of the author, the date of encoding and a brief explanation as to the nature of the contents of the file. This information is patched to the beginning of the file created.

- (3) The representation code generated is pretty-printed. This makes reading the code easier. However, this also results in a much larger file than is strictly necessary.

- (4) Most of the questions asked not only specify the nature of the answer expected, but also reject unacceptable answers. For example, if a fixed point number is typed in where a non-negative integer was expected, the question is repeated till an integer is entered.

FRONTEND was originally written in FranzLisp on VAX 11/785 and is about 13K in size. It has been now transported to Common Lisp on the TI Explorer 2. It uses about forty functions, most of which have been named in a self-documenting style. The code can be easily changed to incorporate future extensions in representation.

#### 3.4 DIAGNOSTIC REASONING USING MEASUREMENTS

#### 3.4.1 Introduction

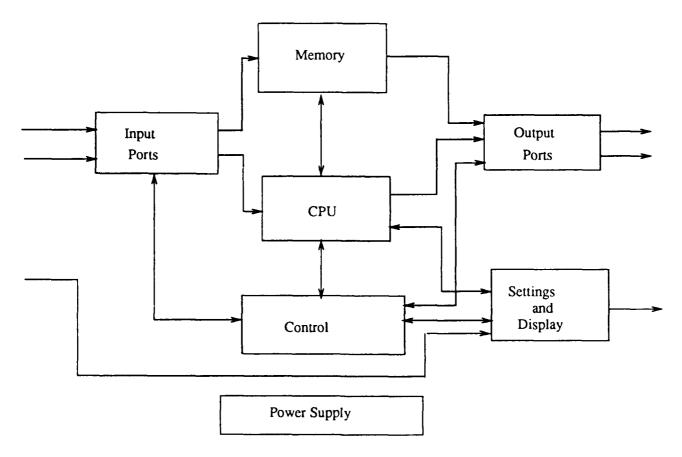

In model-based diagnosis, there are three major steps: discrepancy detection, candidate generation and candidate discrimination/confirmation. Discrepancy detection is the process of identifying the discrepancy between the predicted and observed values at certain places, e.g., at the primary outputs of a circuit. After a discrepancy is detected, the failure symptom is used to generate a set of candidates which can potentially explain the observed symptom when some of them are faulty. Here we use the simplest candidate generation procedure which collects components connecting to any violations. Usually, the candidate generation procedure produces more than one candidate for a particular symptom. This calls for the need to discriminate or confirm candidates as well as the need to select the most likely candidate to test first. The latter motivates the initial ordering of candidates based on structure and symptom information. Simple probes at the inputs and outputs of a candidate are used to determine if it is actually faulty under the current test.

Measurements are used not only to determine the status of a candidate but also to determine the relative fault possibilities of other randidates. A more measurement information becomes available, some candidates recome these likely less likely or in possible of faulty. This infution is the foundation on which want is to represent the likely of indicated as based. New measurements are associated as determined them. I have seen been also that the first making the shade for a use of pulses. A for the contribution of foundations which has a top exhibit as top the contributions of

The properties are quite for the properties of the properties of the form of the properties of the pro

#### 3.12 Candidate Ordering, Reorder's and Eliminates.

This section summarizes the principle of small date releting to a complete account for these topics for the found in Chernalia School 1984. As an appropriately, when more than one candidate is preduced in the candidate general or step, it is desirable for a diagnostic system to be able to focus on the most likely candidate first so that the faulty parts can be located earlier. Intuitively, we have the following two heuristics: It a submodule is more likely to be faulty if it is connected to more lead primary outputs and (2) a submodule is less likely to be faulty if it is connected to more good primary outputs. Initially, candidates are ordered according to their relationships with incorrect and correct primary outputs as described.

While the initial candidate ordering look promising, there is no guarantee that actual

#### 3.4 DIAGNOSTIC REASONING USING MEASUREMENTS

#### 3.4.1 Introduction

In model-based diagnosis, there are three major steps: discrepancy detection, candidate generation and candidate discrimination/confirmation. Discrepancy detection is the process of identifying the discrepancy between the predicted and observed values at certain places, e.g., at the primary outputs of a circuit. After a discrepancy is detected, the failure symptom is used to generate a set of candidates which can potentially explain the observed symptom when some of them are faulty. Here we use the simplest candidate generation procedure which collects components connecting to any violations. Usually, the candidate generation procedure produces more than one candidates for a particular symptom. This calls for the need to discriminate or confirm candidates as well as the need to select the most likely candidate to test first. The latter motivates the initial ordering of candidates based on structure and symptom information. Simple probes at the inputs and outputs of a candidate are used to determine if it is actually faulty under the current test.

Measurements are used not only to determine the status of a candidate but also to determine the relative fault possibilities of other candidates. As more measurement information becomes available, some candidates become more likely, less likely or impossible to be faulty. This intuition is the foundation on which candidate reordering and elimination are based. New measurements are also used to determine when a diagnosis can be terminated without making the single fault assumption. A diagnosis can be terminated when there are no more violations which cannot be explained by the faults found so far.

Some assumptions are made throughout the discussion. We assume the faults are non-intermittent so that measured values are independent of time. Probing at any intermediate points of a circuit is assumed to be always possible. We also assume there is no bridge fault and the directions of inputs and outputs are correct. However, single fault assumption is not required.

#### 3.4.2 Candidate Ordering, Reordering and Elimination

This section summarizes the principles of candidate ordering, reordering and elimination. A complete account for these topics can be found in [Chen and Srihari, 1989]. As mentioned earlier, when more than one candidate is produced in the candidate generation step, it is desirable for a diagnostic system to be able to focus on the most likely candidate first so that the faulty parts can be located earlier. Intuitively, we have the following two heuristics: (1) a submodule is more likely to be faulty if it is connected to more bad primary outputs and (2) a submodule is less likely to be faulty if it is connected to more good primary outputs. Initially, candidates are ordered according to their relationships with incorrect and correct primary outputs as described.

While the initial candidate ordering looks promising, there is no guarantee that actual

```

procedure diagnose (CL: an ordered candidate list)

while CL is not empty do

Instantiate the first candidate at its level-1 abstraction

Measure its inputs and outputs

if it has violated outputs then

if its corresponding physical object is at IML then

Issue repair order for the physical object

else

Instantiate it at its level-2 abstraction

Generate and order suspected components of it using its structural description

Call diagnose on the ordered suspected components

endif

else

Claim that the current candidate is intact

endif

Eliminate candidates

Reorder the remaining candidates

Propagate measurements to update predications, violations and CL

endwhile

Report findings

endprocedure

```

Figure 3.4.1: Control structure of VMES

faulty components are ordered in the front of the candidate list. In fact, for any device and good/bad output pattern, it is not difficult to come up with a counterexample on which our method does poorly in the sense that the actual faulty component is put at the last few places in initial ordering. To fix this problem, we reorder or eliminate candidates whenever some intermediate values are measured.

After the inputs of current candidate are measured, some candidates become more likely to be faulty than others. Obviously, candidates connecting to inconsistent inputs are more likely to be faulty than those to consistent ones. Therefore, candidates connected to its incorrect inputs are shoved to the front of candidate list and candidates connected to correct inputs but not to incorrect inputs are shoved to the tail.

In addition, some candidates may become impossible to be faulty after new measurements are known. As a result, candidates that no longer have a path to any violations can be removed from the candidate list.

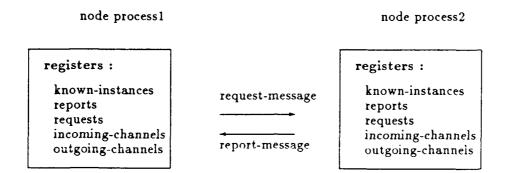

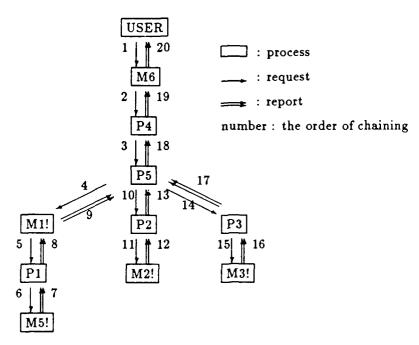

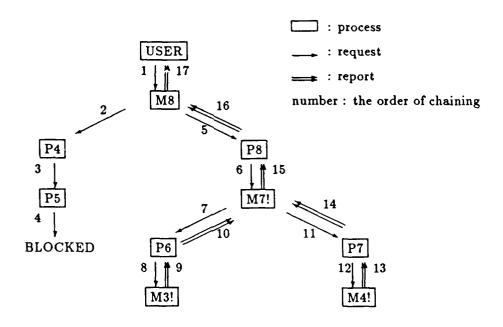

#### 3.4.3 Termination of Diagnosis