# AD-A233 926

|    | <br> | <br> | _ |

|----|------|------|---|

| AD |      |      |   |

| 45 |      |      |   |

|    |      |      |   |

| -  |      |      |   |

|    |      |      |   |

AD-E402 183

**Technical Report ARFSD-TR-91002**

# SELECTABLE LIGHTWEIGHT ATTACK MUNITION OPERATING COMPONENT OF THE GATE ARRAY

Nanette M. Shoenfelt

**April 1991**

# U.S. ARMY ARMAMENT RESEARCH, DEVELOPMENT AND ENGINEERING CENTER

**Fire Support Armaments Center**

Picatinny Arsenal, New Jersey

Approved for public release; distribution is unlimited.

The views, opinions, and/or findings contained in this report are those of the author(s) and should not be construed as an official Department of the Army position, policy, or decision, unless so designated by other documentation.

The citation in this report of the names of commercial firms of commercially available products or systems does not constitute official endorsement by or approval of the U.S. Government.

Destroy this report when no longer needed by any method that will prevent disclosure of contents or reconstruction of the document. Do not return to the originator.

| REPORT DOCUMENTATION PAGE                                                                          |                                                                    |                                                        |                                           |                                           | Form Approved<br>OMB N0. 0704-0188                    |                                                                                                                                                |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| needed land comp<br>to Washington He                                                               | pleting and revealent the citiest                                  | on of information. Send<br>a to: information Operation | comments rugs, thig this burden w         | tim the cit timy other propert            | of the confirmation of information                    | ata sources, gathering and mainturining the data<br>on unrhiding sidgestions from which his horder<br>dito the Office of Management and Sudder |

|                                                                                                    | Y USE ONLY (Leave                                                  |                                                        | REPORT DATE April 1991                    | 3. R                                      | EPORT TYPE AND                                        | DATES COVERED                                                                                                                                  |

| 4. TITLE AND SUBTITLE SELECTABLE LIGHTWEIGHT ATTACK MUNITION OPERATING COMPONENT OF THE GATE ARRAY |                                                                    |                                                        |                                           | 5. FUNDING NUM                            | BERS                                                  |                                                                                                                                                |

| 6. AUTHOI<br>Nanette                                                                               | e M. Shoenfelt                                                     |                                                        |                                           |                                           |                                                       |                                                                                                                                                |

| ARDE<br>Precisi                                                                                    | RMING ORGANIZATI<br>C, FSAC<br>ion Munitions Di<br>iny Arsenal, NJ | vision (SMC                                            | AR-FSP-E)                                 |                                           | 8. PERFORMING<br>REPORT NUM<br>Technical Ro           |                                                                                                                                                |

| ARDEC<br>STINFO<br>ATTN: S<br>Picatinn                                                             | , IMD<br>) Br<br>SMCAR-IMI-I<br>y Arsenal, NJ 0                    |                                                        | IE(S) AND ADDRESS(I                       | ES)                                       | 10. SPONSORING<br>AGENCY REP                          | MONITORING<br>ORT NUMBER                                                                                                                       |

| I1. SUPPL                                                                                          | EMENTARY NOTES                                                     |                                                        |                                           |                                           |                                                       |                                                                                                                                                |

| 12a. DISTF                                                                                         | RIBUTION/AVAILABI                                                  | LITY STATEME                                           | NT                                        |                                           | 12b. DISTRIBUTIO                                      | ON CODE                                                                                                                                        |

| Approved for public release; distribution is unlimited.                                            |                                                                    |                                                        | i.                                        |                                           |                                                       |                                                                                                                                                |

| 13. ABSTF                                                                                          | RACT (Maximum 20                                                   | 0 words)                                               |                                           |                                           | <u> </u>                                              |                                                                                                                                                |

| a mine w<br>is detect<br>SLAM is                                                                   | where it can be p<br>red. It can also to<br>controlled by el       | placed on the<br>be used with<br>ectronics wit         | e ground to detona<br>a tripline or to de | ate when the tonate after a unctions on a | magnetic signa<br>set period of til<br>gate array. Th | It can be used similarly to ture of the desired target me. The operation of the ne functions of the gate                                       |

| 14 SUBJE                                                                                           | ECT TERMS                                                          |                                                        | - W - 7                                   | <del></del>                               |                                                       | 15. NUMBER OF PAGES<br>27                                                                                                                      |

| Mine                                                                                               | Tripwire                                                           | Munition                                               | Gate array                                | Tripline                                  | Logic                                                 | 16. PRICE CODE                                                                                                                                 |

| OF REF                                                                                             |                                                                    | OF THIS                                                | TY CLASSIFICATION PAGE                    | OF ABSTR                                  | CLASSIFICATION<br>ACT<br>ASSIFIED                     | 20. LIMITATION OF ABSTRACT                                                                                                                     |

# CONTENTS

|                                                                                                                                             | Page                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Introduction                                                                                                                                | 1                                         |

| Overview                                                                                                                                    | 1                                         |

| SLAM<br>Gate Array                                                                                                                          | 1<br>2                                    |

| Functional Blocks                                                                                                                           | 3                                         |

| A Timer String B Timer String Time Out Clock Check Self Check Input Processor Antidisturbance Processor Safety Pin Processor Output Control | 3<br>3<br>4<br>4<br>4<br>5<br>6<br>6<br>7 |

| SLAM Gate Array                                                                                                                             | 8                                         |

| Conclusions                                                                                                                                 | 8                                         |

| Bibliograpphy                                                                                                                               | 21                                        |

| Distribution List                                                                                                                           | 23                                        |

# **FIGURES**

|    |                                        | Page |

|----|----------------------------------------|------|

| 1  | A timer string                         | 9    |

| 2  | Timing sequence for the A timer string | 10   |

| 3  | B timer string                         | 11   |

| 4  | Time out                               | 12   |

| 5  | Clock check                            | 13   |

| 6  | Self check                             | 14   |

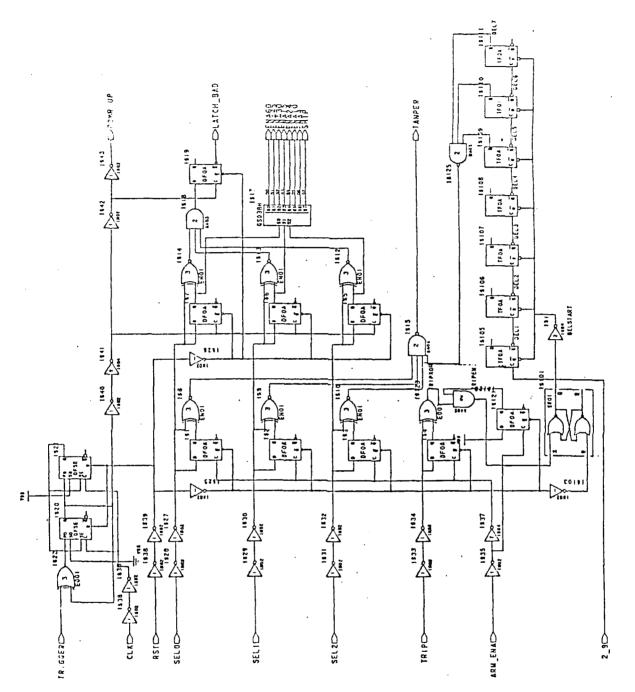

| 7  | Input processor                        | 15   |

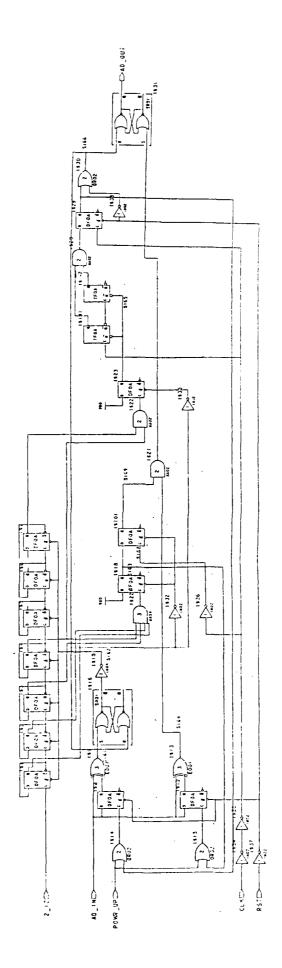

| 8  | Antidisturbance processor              | 16   |

| 9  | Safety pin processor                   | 17   |

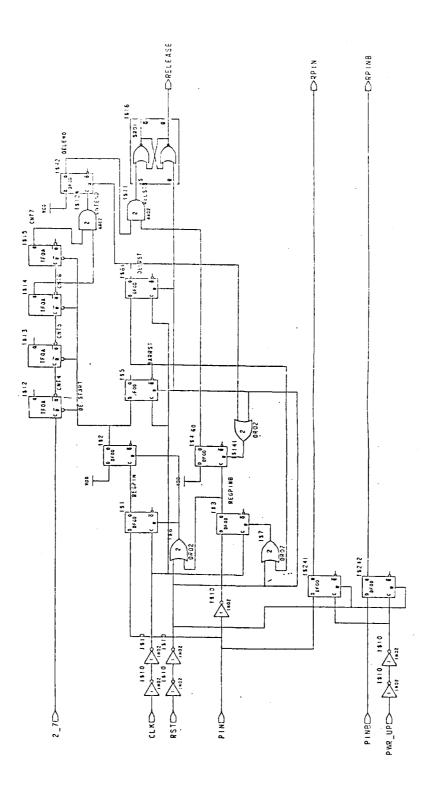

| 10 | Output control                         | 18   |

| 11 | SLAM gate array                        | 19   |

it to become activated. At this point, the system performs a self-test. When the safety pin is removed, the timing for the system begins. Depending on the mode of operation that has been selected, the SLAM electronics is alerted for the appropriate signal in which it is to fire or self-neutralize.

All of the functions of the SLAM except for the use with a blasting cap are controlled by the system electronics. The SLAM uses surface mount technology with most of the functions of the munition on a gate array. This gate array is a highly customized application specific integrated circuit (ASIC).

# **Gate Array**

The gate array logic has been divided into two parts: the operating and testing components. The operating component has been partitioned into functional blocks to facilitate the design and analysis of the system. The functional blocks can be combined to provide the logic for the entire gate array chip. The functional blocks for the operating component of the system are as follows:

| A timer string            | timing string type a                                 |

|---------------------------|------------------------------------------------------|

| B timer string            | timing string type b                                 |

| Time out                  | timing for the safe separation period                |

| Clock check               | logic for checking if the main clock is fast or slow |

| Self check                | logic for performing the system self-check           |

| Input processor           | logic for latching and processing input signals      |

| Antidisturbance processor | logic for processing the antidis-<br>turbance sensor |

| Safety pin processor      | logic for processing the safety pin status           |

logic for performing the electronic

enable

Output control

The description and drawing of each functional block follows. The interconnection of the blocks is also shown.

#### **FUNCTIONAL BLOCKS**

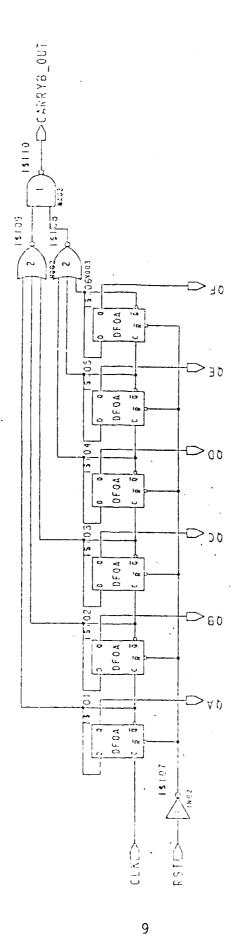

## A Timer String

The gate array contains two types of timing strings. These are the A\_TIMER\_STR and the B\_TIMER\_STR. Each string is made of six stages of ripple counters which are used to provide the timing for the entire chip. A A\_TIMER\_STR is the first block of each string with the remainder of the string made of B\_TIMER\_STR.

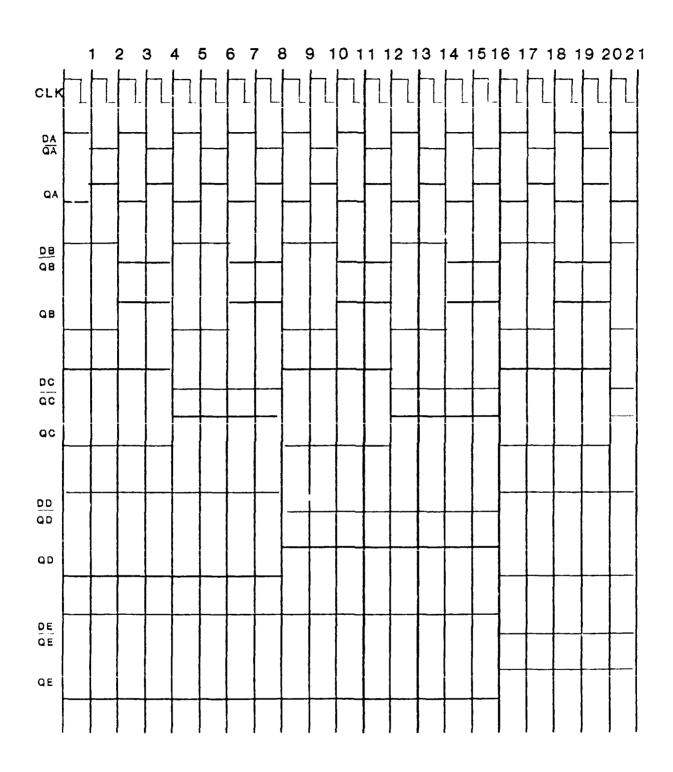

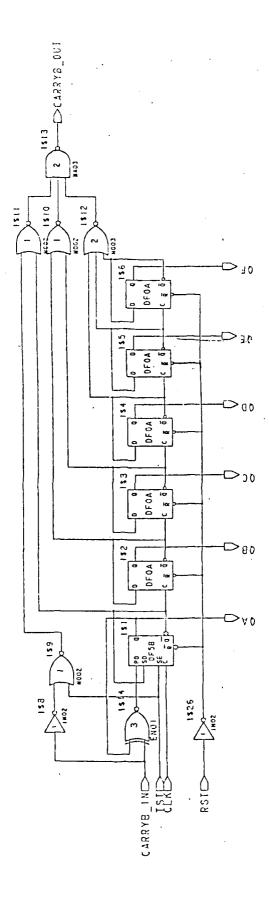

The A\_TIMER\_STR (fig. 1) is composed of six D flip-flops. The output of a D flip-flop is the same as the input; however, it is delayed one clock cycle. When these flip-flops are put into a string with the complement of the output of one used as the input to the next, the delay times increase exponentially. For example, the output of the first flip-flop is delayed one (or  $2^{\circ}$ ) clock pulse from the reset of the system (fig. 2). The output of the second flip-flop is  $2^{\circ}$  clock pulses. Likewise, the output of the third flip-flop is delayed  $2^{\circ}$ . This continues up the string, so that the output to the sixth flip-flop is delayed  $2^{\circ}$  clock cycles. After each of the flip-flops have been toggled, the signal is carried out as the input to the B\_TIMER\_STR.

### **B Timer String**

The B TIMER STR (fig. 3) is very similar to the A TIMER STR in that it is composed of six flip-flops in a string. The outputs are again delayed in the same exponential iashion. The main difference is that the B TIMER STR has a test input. it is very difficult to test a long timing string since the timing gets so large. Therefore, this functional block includes a method for testing the string. The first flip-flop in the string is a selectable flip-flop. It is a D flip-flop, in which there is a choice of the SO or the PO input. If the selectable input SE is high, then SO is used as the input. But if the SE input is low, then the input that the flip-flop sees is PO. When the test signal is high, then the SE input is also high. This forces the system to use SO which makes the system similar to the A\_TIMER\_STR. In this way it can be tested to work just like the previous system, using only 25 clock cycles to get through the string. However, if there is no test input, then the PO input, which is the output of the A TIMER STRING, is used. This causes the string to continue with delays established in the prior block. These B TIMER STR blocks can be strung together to create long strings. In this arrangement, outputs can be taken from each stage of each string which makes it possible to obtain almost any time interval desired

## **Time Out**

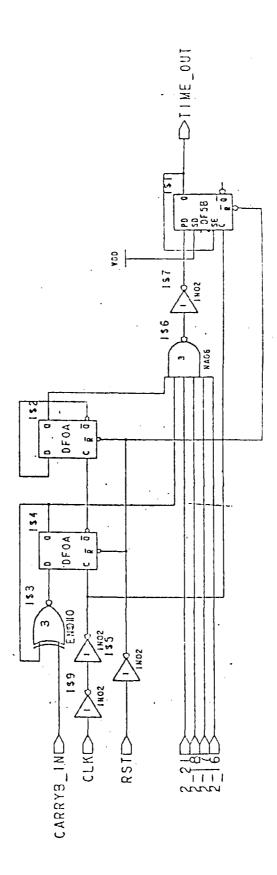

The TIME\_OUT functional block (fig. 4) is used to determine when the safe separation period of the SLAM has expired, thus allowing the munition to become active. The inputs to this block are four timing signals and the CARRYB\_IN which is the CARRYB\_OUT output from the B\_TIMER\_STR. The CARRYB\_IN must toggle two flip-flops before being ANDed with the other timing signals. This signal then toggles the final flip-flop to show that the timing sequence has taken place.

#### Clock Check

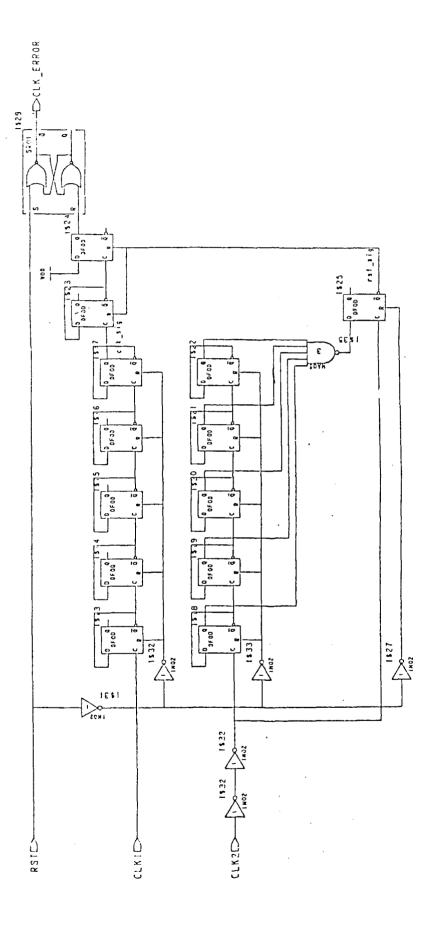

There are two crystal oscillators in the SLAM that check each other. The one that provides the timing for the gate array is the primary time base (PTB); the other timer is the test time base (TTB). The CLK\_CHK functional block is used in two places in the gate array. Time checks are made to see if the PTB is faster than the TTB, and the other tests if it is slower. This depends on which time base is used for which input to the block

The CLK\_CHK block (fig. 5) has the master reset, the CLK1, and the CLK2 as inputs. The CLK1 is the clock input to a four stage timing string. The output of this string is the clock signal to two flip-flops assimilated so that two sequential clock pulses will cause the output of the second flip-flop to go high. The CLK2 is also applied to the clock input of a four stage flip-flop string. The outputs of these flip-flops enter a fifth flip-flop configured so that the output of this flip-flop is a high pulse that is one clock period wide. This pulse is one clock pulse after the fourth flip-flop is toggled. The pulse is used as the reset to the two flip-flops that are run by the CLK1 string. The result of this is that if the clocks are close to the same frequency, then the flip-flops will be reset before the clock signal appears. This will in turn cause the CLK\_ERROR output to remain low. If, however, the CLK2 has a lower frequency than the CLK1, the clock will occur before the flip-flops are reset causing the CLK-ERROR output to go high. This shows that the CLK2 is slow with respect to the CLK1. This check is an ongoing check for the time the chip is operating.

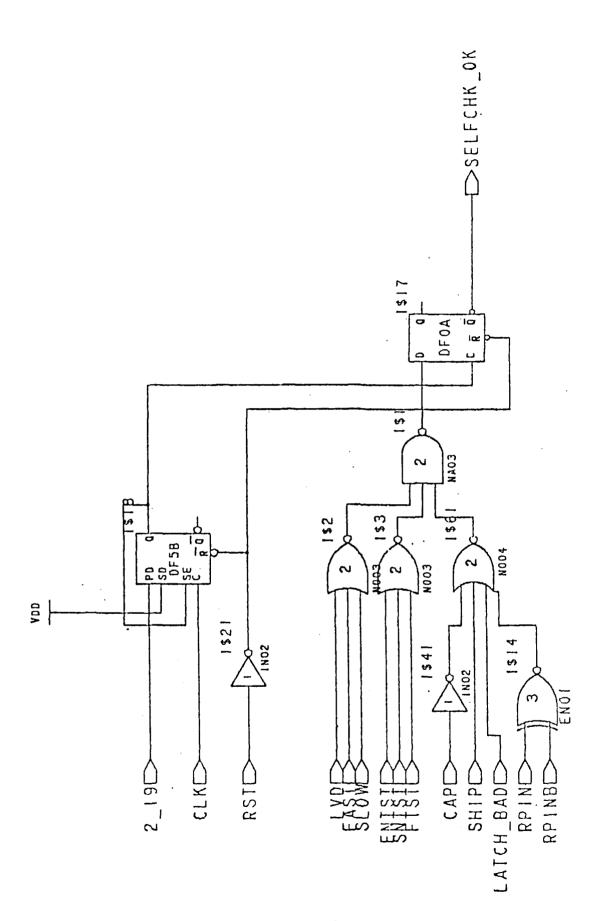

#### Self Check

A number of elements in the SLAM system are checked when the battery is initiated and the gate array chip is activated (fig. 6). The items which are inputted to be checked are the safety pin (RPIN and RPINB), the firing capacitor (CAP), the low voltage detector (LVD), the fast and slow clock checks (FAST and SLOW), the settings on the selector switch (LATCH BAD), the safety switch not in the shipping position (SHIP), and the output of the boundary scans. BS\_IN\_CELL, which are the tests of the enable, self-neutralize, and fire outputs of the gate array (ENIST, SNIST, and FTST). If any part of the self check fails, then the firing output will be disabled.

The RPIN and RPINB inputs should be in opposite states. The CAP should be low. This represents no charge on the timing capacitor. A translator external to the gate array verifies whether there is voltage or not on the capacitor. The LVD should be low. A low voltage detector circuit, off the chip, will give a high signal if the battery voltage drops below a certain amount. The FAST and SLOW inputs should be low. These are the outputs of the two CLK-CHK functional blocks of the gate array. The LATCH BAD signal should be low to pass the self-check. It is the LATCH BAD output of the IN-PUT\_PROC functional block. This shows that the switch position is selected and stored. The SHIP input should be low. If the SLAM's battery is activated when the selector switch is in the slapping position, then the system will fail the self-check and it will fail cate. If all or these tests position the second top flop will toggle to make the SELF CHK OK output go high.

# **Input Processor**

The input block (fig. 7) is used to store the switch positions in memory just after the master reset for the date array is administered. It also is used to detect any changes in the cwitch positions that take place after the system is enabled. The two flip-flops in the upper left-hand corner of the diagram are used to create a signal pulse that is one PTB width in duration and begins one PTB period after the TRIGGER signal. This pulse is used as the POWER UP inputs which initiate the AD PROC and the PIN PROC blocks. It is also used to clock four flip-flops in this functional block. These flip-flops are employed to latch the three selector switch lines (SEL0, SEL1, and SEL2). to give the settings on the selector switch. The outputs of each of these flip-flops go to Exclusive OR gates which are the outputs of each of these gates being ANDed together. This signal goes into another flip-flop, such that if the inputs and outputs of each of the flip-flops agree, then the input to the final latch will be high. The output of this flip-flop will be high if the switch settings did not successfully latch. This is the LATCH BAD output that is tested in the SELF CHK part of the gate array. The three switch selection lines (SEL0, SEL1, and SEL2) go into a three-to-eight decoder, providing the outputs of the block. The SHIP output is the shipping setting; the ENA settings are as follows: time demolition times of 15, 30, 45, and 60 minutes, and selfneutralization time of 4, 10, and 24 hours.

The ARM ENA input comes from the OUTPUT CONTROL block. It is used to relatch the switch states just prior to the system enabling. If the switches are changed after this time, then the TAMPER output will go high. Therefore, the function of the SLAM will be determined by the switch settings when the battery is initiated. The switch can be changed from this time until the time the munition is enabled without any change to the mission. This can be used to hide the actual switch setting. If, however, the switch position is changed after the system is enabled, then the antitamper feature will cause the munition to detonate.

#### **Antidisturbance Processor**

This block (fig. 8) has inputs from the PTB, the 2<sup>12</sup> delay from the timing string, the master reset, the power up pulse created by the INPUT\_PROC block, and the antidisturbance (AD) switch input. To help facilitate the rejection of false AD detection and increase the reliability of the AD switch, this block provides the algorithm. The user desires that the SLAM not detonate with vibrations on the ground. When the AD switch is activated by a movement of the system, the ball inside the switch moves and sends a signal to this functional block. This input is again observed after a certain amount of time is determined by the timing string at the top of the diagram. If there is no change in position at this time, then no disturbance is detected. However, if there has been some additional movement in the munition, then the AD switch is addressed again after the next part of the timing string has taken place. If there is no change in the state of the AD switch at this point, then the munition will remain unchanged. If there is a change in the switch, then the AD\_PROC block will output a high signal on the AD\_OUT to the FIRE\_SAFE block.

### Safety Pin Processor

This component of the gate array is used to determine when the safety pin has been released (fig. 9). To start the timing of the gate array, a safety pin on the SLAM unit must be pulled. This pin is positioned next to a mechanical switch. Normally the safety pin microswitch is not depressed. The PIN input will be low, while the PINB will be high. This causes the RPIN to be low and the RPINB to be high. These are inputs to the SELF\_CHK block which tests to see that they are in opposite states. With a low signal on the PIN input, the timing chain of flip-flops at the upper right corner of the block will not get a reset signal. Therefore, the output of the string will be low. This signal goes into an AND gate with the output remaining low. This low signal propagates to the RELEASE output showing that the safety pin has not been released.

When the safety pin is pulled, the microswitch is depressed. This means that the PIN input is high, while the PINB is low. This is also true for the RPIN and RPINB supputs. With the PIN input high, the flip-flops in the timing string will reset, and the input into the AND gate will be high. However, the low signal on the PIN input continues to the other input on the AND gate. This will still keep the RELEASE output low.

When the safety pin is completely removed, the microswitch is no longer depressed. This makes the PIN input low again. The same thing will occur as before, except that the output from the timer string is now high from the previous step. The high PIN input now gives a high signal on the other input to the AND gate making the RELEASE output high indicating that the safety pin has been removed. This output goes to start the timing sequences in another part of the gate array.

## **Output Control**

This segment of the gate array is very important in that this is the part that determines whether or not the munition will enable the system to self-neutralize or fine (fig. 10). There are a number of timing inputs that are used to determine the ames required for each event. There are also inputs for the PTB, master reset, neit test (SELF CIEK, OK), the seven ENA settings from the selector switch, the result of the low voltage detector that is still operating after the self-test occurs (LVD), the output of the off-the-chip delta-sigma modulator (VEH), and the outputs of the INPUT PROC (TAMPER) AD PROC (AD), CLK (CHK (FAST and SLOW), and TIME OUT (TIME OUT). The timing is also controlled in this part of the circuit to charge the firing capacitor in order to initiate a piston actuator (CHARGE). There is also the PRE ENA output that initiates the piston actuator that unlocks the safe and arm device. FIRE is the signal that initiates the piston actuator to move the rotor in line so that the warhead can be detonated. The SN signal is the signal that fires the rotor when it is out of line so that the rotor will be forced out of the encasement of the munitial on. This gives a visible means of displaying that the system has self-neutralized.

If one of the time demolition modes has been selected a.e., ENA15 ENA30, ENA45, or ENA60 is high) and the appropriate timing has toggled the flip-flop, then the NAND gate will output high. This high signal will continue through to the CHARGE and FIRE outputs providing that the system has passed the self-test and it has not been self-neutralized. There are, however, four other methods for initiating the SLAM to fire. If the selector switch has been changed after the system has been enabled no matter what mode the munition is operating, then the antitamper feature will detonate the system. Another method of causing a high fire signal is if the munition is moved when it is in tripline mode or any other nontime demolition modes. In this case, the AD switch signal will be high which will propagate to the fire line in this block. This will detonate the munition. A third means for causing the SLAM to fire is to detect a vehicle when the mine is not in the tripline mode or any time demolition mode. The final method of firing the system is if there is a clock error or low battery after 15 min of activation, if in time demolition mode.

There are three channels for the SLAM to become self-neutralized. If the selector switch is set to one of the self-neutralization times (ENA4, ENA10, ENA24), and the appropriate time has passed, a high signal will spread to the SN output. In time demolition mode, the system will self-neutralize if a clock error or low battery is encountered with in the first 15 min of activation. It will also transpire if a clock error or low battery voltage occurs anytime in one of the self-neutralization modes.

#### **SLAM GATE ARRAY**

The entire gate array (fig. 11) shows the interconnection of each of the functional blocks in the operating component of the gate array as well as the testing component. There are inputs for the timing from the crystal oscillators, the switch settings, the safety pin position, the antidisturbance switch, the low voltage detector, the firing capacitor, the delta-sigma modulator, and the test access port controller. The outputs are CHARGE, which fires the capacitors; ARM\_ENABLE, which unlocks the rotor on the safe and arm device; FIRE, which detonates the warhead; SN, which self-neutralizes the munition; and TAP MONITOR, which gives serial data as to the output of the testing function.

#### CONCLUSIONS

The operating component of the gate array for the SLAM has been described in detail. The gate array controls the timing for the system by receiving inputs from two crystal oscillators. The two oscillators are used to check each other to make sure that the primary time base oscillator is not too fast or slow. This primary time base is used in the timing strings to get all of the desired time delays. The gate array also locks in the switch settings and determines if they have been tampered with. The algorithm for the antidisturbance switch is also in the gate array. The primary function of the gate array is to determine when the system will fire or self-neutralize. The chip will send a signal to the firing capacitors to charge, to enable the system by unlocking the safe and arm device, to fire the piston actuators to detonate the warhead or self-neutralize the munition.

This munition is still in the full scale development stage, and there may still be minor changes to the unit before the design is finalized.

Figure 1. A timer string

Figure 2. Timing sequence for the A timer string

Figure 3. B timer string

Figure 5. Clock check

Figure 6. Self check

Figure 7. Input processor

Figure 8. Antidisturbance processor

Figure 9. Safety pin processor

Figure 10. Output control

Figure 11. SLAM gate array

# **BIBLIOGRAPHY**

- 1. SLAM IR&D Report, Honeywell Ordnance Division, Edina, MN, 1987.

- 2. SLAM Schematic Drawings, Alliant TechSystems, Edina, MN, 1990.

#### **DISTRIBUTION LIST**

# Commander

Armament Research, Development and Engineering Center U.S. Army Armament, Munitions and Chemical Command

ATTN: SMCAR-IMI-I (5)

SMCAR-FSP-E (10)

Picatinny Arsenal, NJ 07806-5000

#### Commander

U.S. Army Armament, Munitions and Chemical Command

ATTN: AMSMC-GCL (D)

Picatinny Arsenal, NJ 07806-5000

#### Administrator

Defense Technical Information Center

ATTN: Accessions Division (12)

Cameron Station

Alexandria, VA 22304-6145

#### Director

U.S. Army Materiel Systems Analysis Activity

ATTN: AMXSY-MP

Aberdeen Proving Ground, MD 21005-5066

#### Commander

Chemical Research, Development and Engineering Center U.S. Army Armament, Munitions and Chemical Command

ATTN: SMCCR-MSI

Aberdeen Proving Ground, MD 21010-5423

#### Commander

Chemical Research, Development and Engineering Center U.S. Army Armament, Munitions and Chemical Command

ATTN: SMCCR-RSP-A

Aberdeen Proving Ground, MD 21010-5423

#### Director

Ballistic Research Laboratory

ATTN: AMXBR-OD-ST

Aberdeen Proving Ground, MD 21005-5066

# Chief

Benet Weapons Laboratory, CCAC Armament Research, Development and Engineering Center U.S. Army Armament, Munitions and Chemical Command ATTN: SMCAR-CCB-TL Watervliet, NY 12189-5000

#### Commander

U.S. Army Armament, Munitions and Chemical Command ATTN: AMSMC-IMF-L Rock Island, IL 61299-6000

#### Director

U.S. Army TRADOC Systems Analysis Activity ATTN: ATAA-SL White Sands Missile Range, NM 88002