AGARD-CP-456

NORTH ATLANTIC TREATY ORGANIZATION ADVISORY GROUP FOR AEROSPACE RESEARCH AND DEVELOPMENT (ORGANISATION DU TRAITE DE L'ATLANTIQUE NORD)

AGARD Conference Proceedings No.456

# Fault Tolerant Design Concepts for Highly Integrated Flight Critical Guidance and Control Systems

(Systèmes tolérants aux fautes pour les phases critiques du guidage et pilotage)

Papers presented at the Guidance and Control Panel 49th Symposium, held at the Ecole Nationale Supérieure de l'Aéronautique et de l'Espace in Toulouse, France, 10th-13th October 1989.

# THE MISSION OF AGARD

According to its Charter, the mission of AGARD is to bring together the leading personalities of the NATO nations in the fields of science and technology relating to aerospace for the following purposes:

- Recommending effective ways for the member nations to use their research and development capabilities for the common benefit of the NATO community;

- Providing scientific and technical advice and assistance to the Military Committee in the field of aerospace research and development (with particular regard to its military application);

- Continuously stimulating advances in the aerospace sciences relevant to strengthening the common defence posture;

- Improving the co-operation among member nations in aerospace research and development;

- Exchange of scientific and technical information;

- Providing assistance to member nations for the purpose of increasing their scientific and technical potential;

- Rendering scientific and technical assistance, as requested, to other NATO bodies and to member nations in connection with research and development problems in the aerospace field.

The highest authority within AGARD is the National Delegates Board consisting of officially appointed senior representatives from each member nation. The mission of AGARD is carried out through the Panels which are composed of experts appointed by the National Delegates, the Consultant and Exchange Programme and the Aerospace Applications Studies Programme. The results of AGARD work are reported to the member nations and the NATO Authorities through the AGARD series of publications of which this is one.

Participation in AGARD activities is by invitation only and is normally limited to citizens of the NATO nations.

Accession For BTIS GRA&I D DTIC TAB Unannounced Justification By\_\_\_\_\_\_ Distribution/ Availability Codes Avail and/or Dist Special The content of this publication has been reproduced directly from material supplied by AGARD or the authors.

Published April 1990 Copyright © AGARD 1990 All Rights Reserved

ISBN 92-835-0552-2

Printed by Specialised Printing Services Limited 40 Chigwell Lane, Loughton, Essex IG10 3TZ

ä

# THEME

The trend towards highly integrated systems continues to expand at a rapid rate. Recent examples include automated maneuvering attack systems, flight control/fire control coupling, mission sensor management, real-time armament fuzing and propulsion coupling/performance optimization,

The prospect of improved mission effectiveness through integrated systems is a very real and powerful motivation with far reaching implications. Recent advances in microprocessor technology are bringing about fundamental changes in several traditional functional domains. Specifically, systems architecture requirements, partitioning considerations and functional performance parameters take on new meaning in the context of fully integrated flight critical systems. Effective system integration focuses on end-item functional performance using the most efficient mechanization possible. In this regard, system wide consideration of sensing elements, computational elements and command signalling loops are critically important. Crew station design considerations and the pilot's role must also be thoroughly assessed vis-a-vis varying levels of task automation and overall system wide integrity management requirements. Key wards and Systems and Systems Achieving the full potential of integrated systems is highly dependent upon demonstrating adequate reliability, safety

Achieving the full potential of integrated systems is highly dependent upon demonstrating adequate reliability, safety and survivability. Historical evidence indicates that interfacing subsystems can introduce serious compromises in overall system safety and performance. High integrity software is essential. Satisfying stringent flight critical system requirements necessitates innovative fault tolerant design approaches and mechanization schemes. Adding redundancy levels across the full spectrum of system elements is a self-limiting approach based on practical considerations of weight, volume, cost and supportability. Reconfiguration strategies, graceful degradation and aerodynamic redundancy are but a few of the modern concepts currently under development. State estimation techniques in conjunction with artificial intelligence technology also offer potential fault tolerance enhancements. Blending system elements for fully integrated or multi-purpose usage under both nominal and extreme operating conditions, requires an intensive system integration effort to achieve acceptable levels of fault tolerance.

This symposium focused on advanced fault tolerant design concepts and their practical application to integrated flight critical military systems.

(active is the

Le tendance vers les systèmes hautement intégrés se developpe rapidement. Des exemples récents concernent les manoeuvres automatiques dans la phase d'attaque, le couplage des systèmes de pilotage automatique et de contrôle des armements, les dispositifs permettant la supervision de la mission, la mise à jour automatique d'armes et l'optimisation globale des performances par inclusion du contrôle de la propulsion.

La perspective d'une amélioration de l'efficacité d'une mission grâce à l'intégration des systèmes est une motivation réelle et puissante avec des conséquences à long terme. Les récents progrès dans le domaine des microprocesseurs apportent des changements fondamentaux dans certains domaines traditionnels. Plus précisément, les exigences de l'architecture des systèmes, la répartition des fonctions et les performances des paramètres fonctionnels prennent un nouveau sens dans le contexte de systèmes hautement intégrés contrôlant les phases critiques de la mission. L'efficacité des systèmes intégrés recherche les performances en bout de chaîne en utilisant la meilleure automatisation: les éléments capteurs, les calculateurs et les informations sur l'état du système conditionnent le succès. La conception des postes de pilotage et les rôles des pilotes doivent être définis avec soin en face des tâches automatisées ainsi que les spécifications de l'ensemble du système largement intégré.

L'aboutissement du potentiel total des systèmes intégrés dépend largement de la démonstration d'une fiabilité, sécurité et survivabilité adéquates. Dans le passé, il est apparu que l'interconnexion de sous-systèmes peut conduire à de sévères compromis sur les performances et la sécurité globales du système. Des logiciels à haute fiabilité sont nécessaires. La satisfaction des contraintes dues à la phase critique de la mission nécessite des concepts nouveaux dans la tolérance aux fautes et dans les schémas d'architecture et d'automatisation du système. L'adjonction de composants, par redondance et à tous niveaux, est un processus qui a ses propres limites pour des questions de poids, de volume, de coût et de réalisation. Les stratégies de reconfiguration, de dégradation acceptables et de redondance aérodynamique sont quelques uns, parmi la multitude, des concepts couramment utilisés. Les techniques d'estimation de l'état du système liées à celles de la technologie de l'intelligence artificielle offrent également un potentiel de résistance aux fautes. L'interconnexion poussée d'éléments du système pour une intégration totale ou une utilisation polyvalente du système à la fois en conditions nominales et en conditions extrêmes nécessite un effort d'intégration intensif pour atteindre un niveau de tolérance acceptable aux pannes.

Ce symposium s'est intéressé aux concepts avancés de systèmes tolérants aux fautes, à leurs applications aux systèmes intégrés militaires "critiques".

# GUIDANCE AND CONTROL PANEL OFFICERS

Chairman: Ir P.Ph.van den Broek Department of Aerospace Engineering Delft University of Technology Kluyverweg 1 2629 HS Delft The Netherlands Deputy Chairman: Professor E.B.Stear Director, Washington Technology Center University of Washington 376 Loew Hall – FH10 1013 NE 40th Street Seattle, WA 98195 United States

# **TECHNICAL PROGRAMME COMMITTEE**

| Mr J.K.Ramage<br>Dr M.J.Pelegrin<br>Mr U.K.Krogmann<br>Pr J.T.Shepherd | US<br>FR<br>GE<br>UK |

|------------------------------------------------------------------------|----------------------|

| Mr D.E.McIver                                                          | US                   |

| Dr G.T.Schmidt                                                         | US                   |

| Pr E.B.Stear                                                           | US                   |

|                                                                        |                      |

# PANEL EXECUTIVE

Mail from Europe: Commandant M.Mouhamad, FAF Executive, GCP AGARD-OTAN 7 rue Ancelle F-92200 Neuilly sur Seine France Tel. 33 (1) 4738 5780 Telex 610 176F Fax 33 (1) 4738 5799 Mail from USA and Canada: AGARD-NATO Attention: GCP Executive APO New York 09777

# HOST COORDINATOR

Dr Marc J.Pelegrin Haut Conseiller ONERA/CERT BP 4025 2 avenue Edouard Belin F-31055 Toulouse France

# ACKNOWLEDGEMENTS/REMERCIEMENTS

The Panel wishes to express its thanks to the French National Delegates to AGARD for the invitation to hold this meeting in their country and for the facilities and personnel which make the meeting possible.

Le Panel tient à remercier les Délégués Nationaux de la France près l'AGARD de leur invitation à tenir cette réunion dans leur pays et de la mise à disposition de personnel et des installations nécessaires.

iv

| CONTENTS                                                                                                                                                                 |           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                                                                                          | Page      |

| THEME                                                                                                                                                                    | <i></i>   |

| PANEL OFFICERS AND PROGRAMME COMMITTEE                                                                                                                                   | iv        |

| KEYNOTE ADDRESS<br>by Général François Maurin                                                                                                                            | K-E       |

| EXPOSE DE L'ESSENTIEL DU SUJET<br>par Général François Maurin                                                                                                            | K-F       |

| SESSION I — TRENDS IN INTEGRATED FLIGHT CRITICAL SYSTEMS<br>Chairman: Dr M.J.Pelegrin (FR)                                                                               | Reference |

| FLIGHT CRITICAL DESIGN CONCEPTS FOR LOW-LEVEL TACTICAL<br>GUIDANCE AND CONTROL<br>by M.R.Griswold                                                                        | 11        |

| EVOLUTION DANS LES APPLICATIONS CIVILES                                                                                                                                  |           |

| (Civil Applications Trends)<br>par P.Traverse                                                                                                                            | 12        |

| PILOT MONITORING OF DISPLAY ENHANCEMENTS GENERATED FROM<br>A DIGITAL DATA BASE                                                                                           |           |

| by P.J.Bennett and J.J.Cockburn                                                                                                                                          | 13        |

| <u>SESSION II – ADVANCED FAULT TOLERANT DESIGN CONCEPTS</u><br>Chairman: Mr U.K.Krogmann (GE)                                                                            |           |

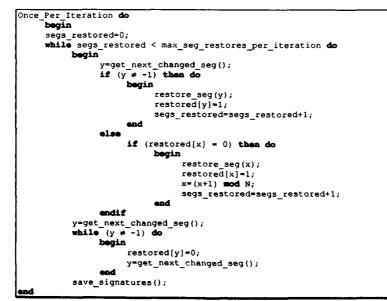

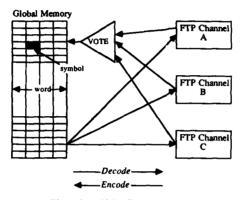

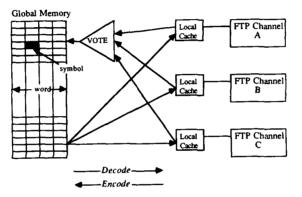

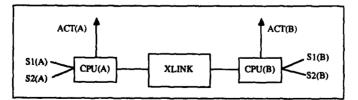

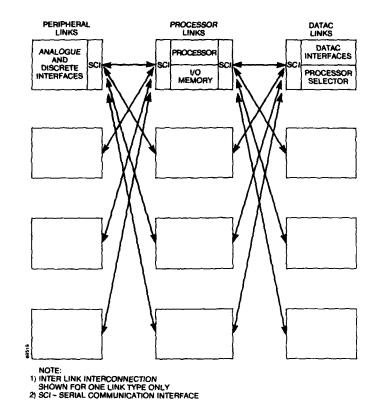

| TECHNIQUES FOR TRANSIENT ERROR RECOVERY AND AVOIDANCE IN REDUNDANT<br>PROCESSING SYSTEMS                                                                                 |           |

| by S.J.Adams and M.J.Dzwonczyk                                                                                                                                           | 21        |

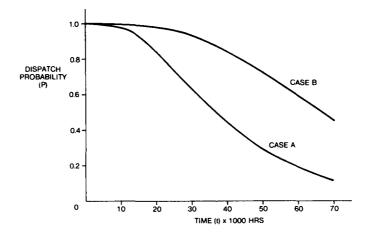

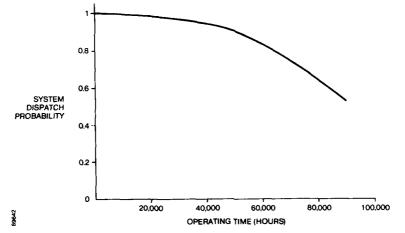

| THE ROLE OF TIME-LIMITED DISPATCH OPERATION IN FAULT-TOLERANT<br>FLIGHT CRITICAL CONTROL SYSTEMS<br>by D.F.Allinger, F.J.Leong, P.S.Babcock IV, G.C.Horan and R.F.LaPrad | 22        |

| A FAULT TOLERANT FLY-BY-WIRE SYSTEM FOR MAINTENANCE                                                                                                                      |           |

| FREE APPLICATIONS<br>by R.W.Dennis and A.D.Hills                                                                                                                         | 23        |

| THE INTEGRATED AIRFRAME/PROPULSION CONTROL SYSTEM<br>ARCHITECTURE PROGRAM (IAPSA)                                                                                        | • /       |

| by D.L.Palumbo, G.C.Cohen and C.W.Meissner                                                                                                                               | 24        |

| DEPENDABLE SYSTEMS USING "VIPER"<br>by J.Kershaw                                                                                                                         | 25        |

| FAULT TOLERANT, FLIGHT CRITICAL CONTROL SYSTEMS<br>by T.Sadeghi and G.Mayville                                                                                           | 26        |

| SESSION III – SYSTEM ARCHITECTURES, MECHANIZATION<br>AND INTEGRATION ISSUES                                                                                              |           |

| Chairman: Professor E.B.Stear (US)                                                                                                                                       |           |

| METHODS TO PRESERVE THE INTEGRITY OF A COMBAT AIRCRAFT FLIGHT<br>CONTROL SYSTEM THROUGH MAJOR UPGRADE PROGRAMMES<br>by M.Rössler and W.Schmidt                           | 31        |

| Paper 32 withdrawn                                                                                                                                                       |           |

| RESEARCH INTO A MISSION MANAGEMENT AID                                                                                                                                   |           |

| by J.R.Catford and I.D.Gray                                                                                                                                              | 33        |

v

α stanget in t

2 8.

-

. . .

|                                                                                                                                 | Reference |

|---------------------------------------------------------------------------------------------------------------------------------|-----------|

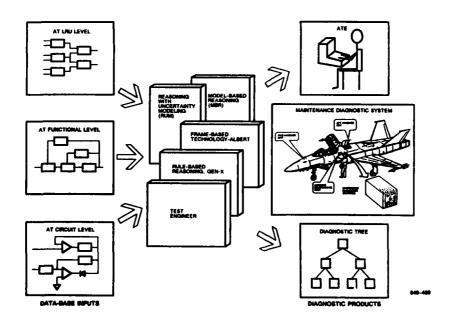

| INTEGRATED DIAGNOSTICS FOR FAULT-TOLERANT SYSTEMS                                                                               |           |

| by H.A.Funk and M.M.Jeppson                                                                                                     | 34        |

| A BYZANTINE RESILIENT PROCESSOR WITH AN ENCODED FAULT<br>Tolerant shared memory                                                 |           |

| by B.Butler and R.Harper                                                                                                        | 35        |

| SESSION IV - HIGH INTEGRITY SOFTWARE DESIGN METHODOLOGIES                                                                       |           |

| AND ALGORITHMS                                                                                                                  |           |

| Chairman: Professor J.T.Shepherd (UK)                                                                                           |           |

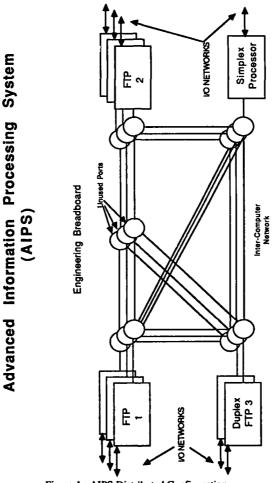

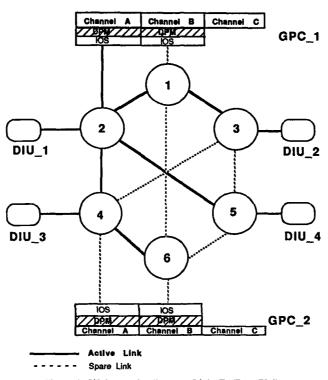

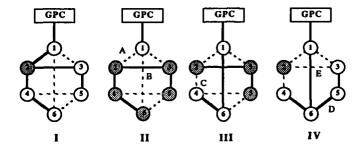

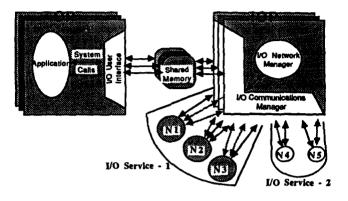

| A HIGHLY RELIABLE, AUTONOMOUS DATA COMMUNICATION SUBSYSTEM FOR<br>AN ADVANCED INFORMATION PROCESSING SYSTEM                     |           |

| by G.Nagle, T.Masotto and L.Alger                                                                                               | 41        |

| FORMALISATION DE DEVELOPPEMENTS: DE LA THEORIE AU PROGRAMME<br>(Formalizing Developments: From Theory to Practice)              |           |

| par M.Lemoine et K.Bechane                                                                                                      | 42        |

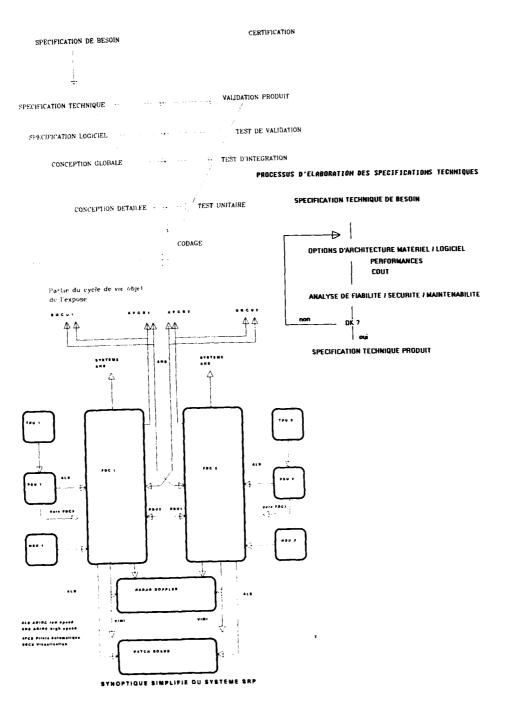

| METHODOLOGIE DE DECOMPOSITION D'APPLICATION DE NAVIGATION<br>CRITIQUE EN ELEMENTS SIMPLES                                       |           |

| (Break-down Methodology for Flight Critical Applications into Elementary Components)<br>par B.Chavana et F.de Sainte Maresville | 43        |

| FAULT TOLERANCE VIA FAULT AVOIDANCE<br>by B.D.Bramson                                                                           | 44        |

| Paper 45 withdrawn                                                                                                              |           |

| SESSION V - SYSTEM VALIDATION, SIMULATION AND                                                                                   |           |

| FLIGHT TEST EXPERIENCE                                                                                                          |           |

| Chairman: Dr G.T.Schmidt (US)                                                                                                   |           |

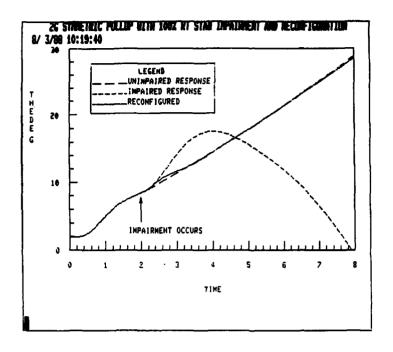

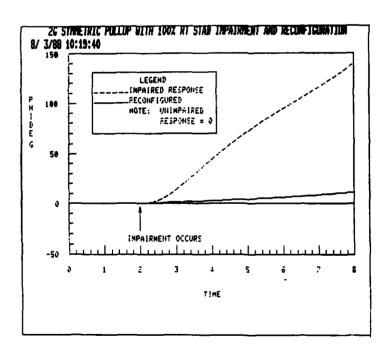

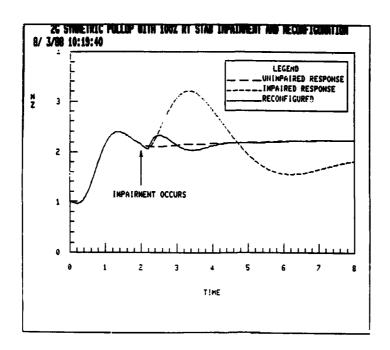

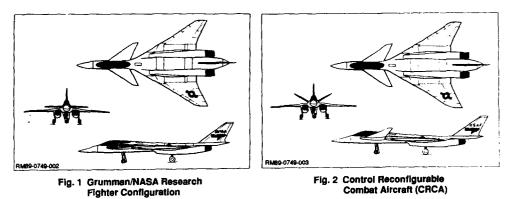

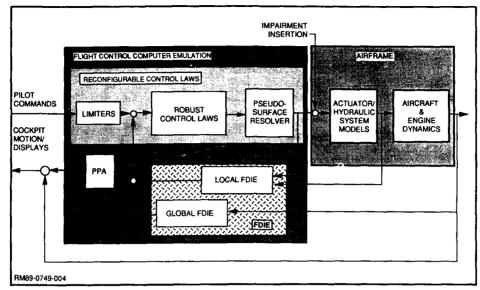

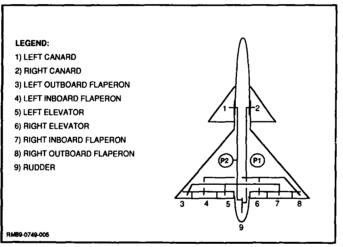

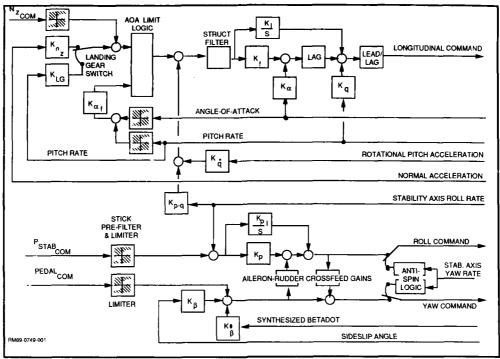

| PILOTED SIMULATION VERIFICATION OF A CONTROL RECONFIGURATION STRATEGY<br>FOR A LIGHTER AIRCRAFT UNDER IMPAIRMENTS               |           |

| by R.Mercadante                                                                                                                 | 51        |

| FLIGHT TEST RESULTS OF FAILURE DETECTION AND ISOLATION ALGORITHMS<br>FOR A REDUNDANT STRAPDOWN INERTIAL MEASUREMENT UNIT        |           |

| by F.R.Morrell, P.R.Motyka and M.L.Bailey                                                                                       | 52        |

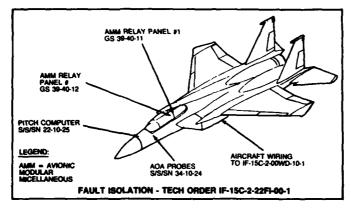

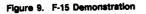

| FLIGHT DEMONSTRATION OF A SELF REPAIRING FLIGHT CONTROL SYSTEM<br>IN A NASA F-15 FIGHTER AIRCRAFT                               |           |

| by J.M.Urnes, J.Stewart and R.Eslinger                                                                                          | 53        |

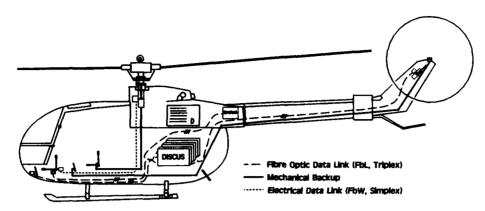

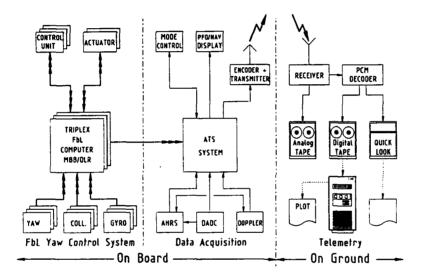

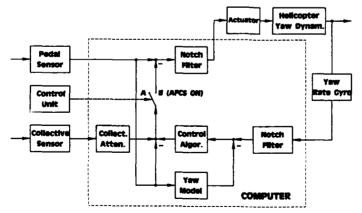

| FLIGHT TESTING OF A REDUNDANT FBW/FBL HELICOPTER CONTROL SYSTEM<br>by H.Becker, K.Bender, K.D.Holle and G.Mansfeld              | 54        |

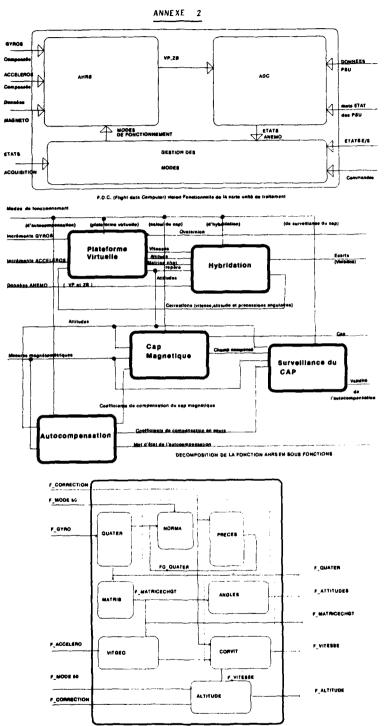

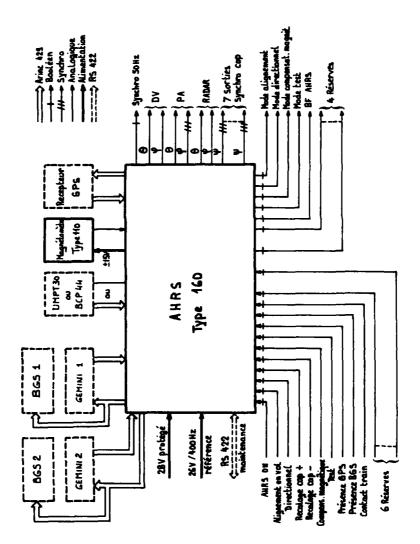

| UN SYSTEME DE REFERENCES PRIMAIRES DE HAUTE INTEGRITE<br>(A High Integrity Flight Data System)                                  |           |

| (A High Integrity Fught Data System)<br>par J.L.Roch et J.Contet                                                                | 55        |

vi

• • •

• • •

K-E-I

### **KEYNOTE ADDRESS**

by

## Général François Maurin

# Member of French Conseil d'Etat and Former Chief of Staff of the French Armed Forces

# I INTRODUCTION

Thank you for inviting me to give the keynote speech to this 49th GCP symposium on "Fault Tolerant Design Concepts for Highly Integrated Flight Critical Guidance and Control Systems". This topic will certainly be one of the major concerns of aeronautics from now until the year 2000.

If NATO air forces are to maintain their superiority over the air vehicles and missiles of our potential adversaries, whose aerodynamic performances and flight envelopes are close to or equal to those of our own aircraft, then the only possible solution is to concentrate our efforts on increasing and improving our flight control and combat aids, and thereby maintain our technology lead in this area.

I am sure you will agree with me when I say that in the coming decades, weapon system reliability will prove vital to the success of missions performed by combat aircrew in an increasingly hostile environment. Numerically inferior, the availability of our air vehicles and the speed of their reconfiguration must be considerably improved.

Our weapon systems will need to be increasingly accurate, safe, reliable, all-weather and computerised, so as to allow the pilot to optimise his threat response and achieve his aims, while at the same time reducing his workload.

In order for this to happen, stress must be placed on the guidance and control functions of the weapon system and on their ability to deal with internal errors and false alarms, not just in computers, but in all components.

Increasing computerisation means that the various system functions are becoming highly critical, and the loss of one of these functions during a crucial flight phase can be catastrophic, resulting in mission failure.

System architecture should ensure not only increased performance, but also greater reliability and simple, rapid maintenance.

In this context, the internal organisation of the architecture management of a sophisticated and highly integrated weapon system and its error tolerance is much more complex than for a normal computer, as in addition to its links with on-board computers, system reliability is closely bound up with the design and management of the following:

- the sensors and their interfaces

- operation of the various subassemblies

- data transmission along the network which interlinks them

- reliability of the software and the capabilities of the language chosen,

### II THE TECHNICAL CONSTRAINTS

Having had the honour of commanding the French Air Force Experimental Centre at Mont de Marsan, and having been ChiefofStaffofthe French Armed Forces in the 1970s, I can measure the progress achieved in your field by developments in French weapon systems, or in systems produced in conjunction with our European partners, in both the civil and military domains.

Sufficient as examples, are the developments and technological advances which have taken us from the first generation of Mirage III's to the Rafale, by way of the Jaguar, and the equally spectacular progress which separates the Transal from the family of Airbus aircraft.

This notwithstanding, there remain a number of permanent features of the question, on which it would be advisable to concentrate our attention, in order to make our weapon systems more efficient by reducing procurement and deployment costs.

From the user's point of view, these features can be summarised as follows:

- a reduction in weight and volume

- reliability and survivability

- a reduction in the amount of connections between subassemblies, which are a frequent source of faults and corrosion

- system versatility, interchangeability and modularity

- redundancy for data transmission systems

- software reliability and adaptability

- tolerance of internal errors and downgraded and rapid reconfiguration mode capability

- ECM and partial destruction withstand capability

- rapid and simple maintenance procedures.

I am sure that you are as familiar as I am with all these different constraints, but I think it is useful to restate them here. You see, experience has taught me just what feats of ingenuity researchers and specialists such as yourselves are capable of producing in order to meet military specifications laid down by users who are not always too bothered about the cost aspect, but are rather more concerned with the success of the mission.

What happens in these cases is that once a solution is found, insurmountable financial problems arise and the project never sees the light of day because of the lack of credits.

# **III THE HUMAN CONSTRAINTS**

Having dealt briefly with the technical constraints, I now propose to consider the human aspects of the problem. As far as the project and the pre-project are concerned, there must be a continuous dialogue between designers, users, and the multidisciplinary team responsible for coordination.

This well known management rule becomes even more vital when designing a highly integrated guidance and control weapon system. In addition to the processing and management of mission data, it imposes and will continue to impose a series of technological decisions on the equipment manufacturers who design the various sensors and flight controls (and even engine designers), and this, some five years before production of the prototype. They must therefore be informed of the specifications to be met in order to produce data in the form of signals which are easy to process in a highly integrated system, in order to avoid costly and fault provoking interfaces.

The PAVE PILLAR and PAVE PACE programmes have opened up the way to solutions of this type and your work should lead to a consensus of opinion among the various nations of the Atlantic alliance.

I would stress this point, as in the coming decades we shall need to ensure that a continuous dialogue takes place between the designers of highly integrated guidance and control systems and flight control and sensor designers, otherwise our efforts will be frittered away and we shall continue to produce highly complex and costly systems.

For some of you, who are familiar with this problem, the choice of the best possible trade-off at least cost, is not and will never be an easy one. This choice becomes even more complex once a highly integrated system project brings together computer designers, software manufacturers, equipment manufacturers and the designers of future sensors, all around the same table, in contrast to recent practice, in which the various parties involved always acted independently, being content to let the overall weapon system designers deal with the details of the interfaces.

We must create multidisciplinary teams right from the outset of any such project, prepared to see it through right to the end. Quite apart from the current technological advances which are being made, I am convinced that one of the main sources of enhancement for future guidance and control systems lies in this common approach, right from the initial design stage of the project. Thanks to this continuous concerted effort, in the future it will be possible to limit the complexity and sophistication of highly integrated and computerized systems, so that they better reflect their ultimate purpose, which is the success of the mission.

The fact is that we often still produce subassemblies whose sophistication is not justified by the overall system specification. We must avoid "art for art's sake".

#### IV FUTURE PROSPECTS

In the near future, advances and innovations in the field of guidance and control will offer a growing number of users a wide range of possibilities, enabling them to accomplish any given mission in different ways, with equal chances of success.

Competition between unmanned vehicles, manned vehicles and completely autonomous missiles will be increasingly open.

I shall consider only manned vehicles, in order to allow for the role of the human operator in the data management loop and for the actions he is required to take, in the shortest possible time, in response to the information relayed to him.

At the present time, fighter pilots or aircrew, are confronted by a multiplicity of information sources, whose variety and dissimilarity tend to divert their attention rather than to concentrate it, and which increase their workload during the most critical phases of the mission. Pilots must constantly create a balance between synthetic data and their visual perception of their operational environment.

It is therefore of prime importance for the design of future guidance and control systems to remember that one of the ultimate aims of the system is to present the pilot with clear and precise, limited and sequential data, which match the requirements of the moment.

One of the tasks which will be required of the design rs of highly integrated systems in the near future, and it is a considerable one, will be to design a data display on the instruments panel which may well involve a complete reconfiguration of the cockpit in next generation weapon carriers.

#### K-E-2

The promise held out by expert systems, artificial intelligence and the three dimensional display of synthetic data should go a long way to solving this problem.

Clearly, all this innovation cannot but add to the sophistication and complexity of the guidance and control systems in future generation weapon systems; but it may also result in appreciable simplification if we are talking about a completely new system and not the adaptation of new technology to an old concept.

With this in mind, it would seem to me to be an opportune moment in my address to summarize the different technologies employed in the subassemblies making up a guidance and control system, in order to point the way to the architecture of a global concept of "mission data management".

This is certainly a major task, and a tricky one. It will require much time and effort, but I think it is within the reach of your Panel, as our programme of work covers most of the points I have just mentioned.

A study of this type should produce recommendations and guidelines enabling the designers of each part of the "puzzle" which a highly integrated guidance and control system represents, to base the design of their projects on a master plan, in all probability using a common language for data transmission. This should, in time, lead to the adoption of a certain standardisation, with a reduction in the complexity and sophistication of the overall system, accompanied by a reduction in cost. This system approach should be developed in our Universities. I know that the Sup Aéro Institute was one of the first, if not the first, to introduce this aspect into its curriculum.

This study of the subassemblies: "fire-control/missile", "navigation" and "control" should enable us to distinguish the share of guidance and control equipment to be retained on the weapon carrier and the share to be incorporated into the missile in order to enable the target to be attained with the greatest possible autonomy.

It is implicit in this approach that only those guidance and control sub-systems necessary for the different phases of the mission (take-off, flight control, target acquisition and landing) would be retained on board the weapon carrier; the rest of the system being incorporated in the missiles. Obviously this type of analysis would need to take into account the assistance provided by next generation navigation systems of the type GPS-NAVSTAR or aircraft such as AWACS or JTIS etc., so as to reduce, or, where possible, simplify the number of on-board sensors carried.

As I pointed out previously, such studies can be successful only if a continuous dialogue is maintained between all parties involved in the global project.

The line is so fine between the concept of "guidance and control" and that of "avionics", that the question of who should be prime contractor for the global system remains unanswered. Perhaps your inter-Panel GCP/AVP symposia could come up with a recommendation.

One of the weak points of the NATO forces, when faced with a potential threat from the Warsaw Pact, being numerical inferiority, it would seem to me of great interest to know to what extent such concepts would allow us to increase the numbers of our "weapon platforms" while reducing their cost, and at the same time maintaining our technological superiority.

#### V THE FINANCIAL CONSTRAINTS

Last, but by no means least, come the financial constraints, which increasingly affect the military budgets of all the nations of the Alliance. They are particularly sensitive in the field which interests us. A global cost estimate of the sensors and detectors which combine to make up the high performance guidance and control systems carried by today's manned air vehicles shows that they represent nearly 40% of the total cost of the air vehicle.

In the face of such financial constraints and of the sheer volume of studies which need to be carried out, it is increasingly apparent that the resources required exceed the possibilities of a single country; the need to combine our efforts within the Alliance on promising new technologies is now urgent.

The current negotiations regarding the reduction of conventional weapons and short range strategic missiles, which will eventually lead to numerical parity between East/West weapon systems outside their countries of origin (USA-USSR), will make this kind of cooperation even more necessary.

We shall not only have to cooperate on individual weapon system projects, but also turn our attention to the broad range of weapon systems to be deployed in order to maintain our effectiveness.

We must replace the idea of standing firm in the face of a numerically superior enemy by the idea of adaptation of our forces to the neutralisation of targets both on the battlefield and in depth. This will probably lead us to review our conventional air weapons and, as a result, the guidance and control concepts of future generation weapon systems.

However utopian it may be to think that international industrial competition in this high-tech sector will disappear in the short term, I think it is realistic, in view of what is at stake, which is nothing less than the preservation of the freedom of the western world, that we should combine our research and design efforts so as to produce a number of common core programmes, methods and a certain interchangeability between the various weapon systems, while at the same time allowing each nation the freedom to develop its weapons industry and the choice as to whether or not to cooperate on common aerospace projects.

It is all too often regrettable to see several different nations of the Alliance exhausting their individual financial resources on R&D work on the same technological problem, only to find that the answer to the problem is discovered by each country practically at the same time, with a few rare exceptions, and that the final products have more or less the same performance and use the same innovations.

In many cases, given clearly defined and approved aims, better cooperation between the nations of the Alliance from the outset of the project would have produced the same result at less cost, and certainly a lot faster, without compromising industrial expansion in our respective countries.

Whereas in the past, the nations of the Alliance may have been able to afford this kind of luxury, the major technological challenges in Aerospace in the coming decades, such as SDI, the supersonic transport plane, are of a nature which prohibits such action.

If we were to continue in this egotistical way, then many of these designs would remain at the "drawing board" stage.

Our potential adversaries, who are more pragmatic, would derive benefit from our difficulties, and in addition to their numerical superiority from the onset of any engagement, would be able to match us from the technology point of view.

Any shortfall in programme credits or extension of the time frame for weapon carrier manufacture would mean that NATO would lose the credibility it still has on the conventional weapons side, and which I would qualify as "conventional tactical and battle skills deterrence", which would be detrimental to the overall strategy of the countries of the Alliance.

#### VI CONCLUSIONS

AGARD is without doubt the most suitable body to carry out such a study, and at the same time convince your respective authorities of the benefits of concerted cooperation, and within AGARD, GCP is incontestably the most suitable Panel.

You are, in fact, practically the only forum, if not the only group of high level experts, free of governmental constraints, who can devote themselves entirely to innovative research, the formulation of pertinent recommendations and the maintenance of a continuous dialogue between all the experts in the various scientific disciplines which combine to form the basis of the future guidance and control systems to be fitted to our future weapon systems.

.

## K-E-4

# EXPOSE DE L'ESSENTIEL DU SUJET

# par

#### Général François Maurin

#### Membre de Conseil d'Etat français et ancien chef d'Etat-major des armées

#### **II INTRODUCTION**

Merci de m'avoir invité pour prononcer le discours d'ouverture de votre 49ème Symposium de la Commission Guidage et Pilotage dont le thème "Les concepts en matière de tolérance aux pannes pour des systèmes critiques hautement intégrés de Guidage de Pilotage" est certainement un des points majeurs que l'aéronautique de l'horizon 2000 devra surmonter.

Pour maintenir aux Forces Aériennes de l'OTAN leur supériorité face aux vecteurs aériens et aux missiles de nos adversaires potentiels dont les performances aérodynamiques et les domaines de vol se rapprochent ou égalent celles de vos propres vecteurs, la seule issue possible est de concentrer nos efforts sur l'accroissement des aídes au pilotage et au combat de nos propres forces et de maintenir dans ce domaine notre avance technologique.

Pour permettre aux équipages et en particulier aux pilotes des avions de combat d'accomplir leurs missions dans un environnement de plus en plus hostile, il est clair et vous en conviendrez avec moi, que la fiabilité des systèmes d'arme est un enjeu capital pour les prochaines décennies. Inférieur en nombre, la disponibilité de nos vecteurs et la rapidité de leur remise en oeuvre doivent être considérablement accrues.

Nos systèmes d'arme doivent et devront être de plus en plus précis, sûrs, fiables, tout temps et automatisés afin de permettre au pilote d'adapter la meilleure réponse à la menace et d'atteindre son objectif tout en diminuant sa charge de travail.

Pour atteindre cet objectif, l'accent doit être mis sur les fonctions de pilotage et de contrôle du système d'arme et sur leur capacité à surmonter les erreurs internes et les fausses alarmes non seulement dans le ordinateurs mais aussi dans tous les composants.

Les diverses fonctions du système devenant très critiques au fur et à mesure que l'automatisation est plus poussée, la perte de l'une de ces fonctions peut être catastrophique dans une phase cruciale du vol et conduire à l'échec de la mission.

L'architecture du système doit non seulement permettre un accroissement des performances mais aussi sa fiabilité et une maintenance simple et rapide.

A ce titre, l'organisation interne de la gestion de l'architecture d'un système d'arme évolué et hautement intégré ainsi que sa tolérance aux erreurs est beaucoup plus complexe que pour un ordinateur proprement dit, car en plus des ordinateurs embarqués, la fiabilité du système dépend aussi étroitement de la conception et de la gestion:

- des capteurs et de leurs interfaces,

- de la mise en oeuvre des divers sous-ensembles,

- de la transmission des données dans le maillage qui les relie entre eux,

- de la fiabilité des logiciels et de la capacité du langage adopté.

# II LES CONTRAINTES TECHNIQUES

Ayant eu l'honneur de commander le Centre d'Expérimentation de l'Armée de l'Air à Mont de Marsan et d'avoir été Chef d'Etat-major des Armées dans les années 70, je peux mesurer les progrès accomplis dans le domaine qui vous préoccupe au travers de l'évolution des systèmes d'arme français ou réalisés en coopération avec nos partenaires européens et ceci aussi bien dans l'aéronautique militaire que civile.

Je ne citerai comme exemple que l'évolution et les réalisations technologiques qui nous ont conduit de la première génération des Mirages III au Rafale en passant par le Jaguar et les progrès tout aussi spectaculaires réalisés entre le Transal et la famille des Airbus.

Il n'en demeure pas moins qu'un certain nombre de constantes demeurent sur lesquelles nous devons concentrer nos efforts afin d'obtenir une meilleure rentabilité des systèmes d'arme pour diminuer les coûts d'achat et de mise en œuvre.

En me plaçant du point de vue de l'utilisateur, ces constantes peuvent se résumer ainsi:

- allègement des poids et diminution des volumes,

- fiabilité et survivabilité,

- diminution des connections entre sous-ensembles qui sont la source de nombreuses pannes et de corrosion,

- versatilité, interopérabilité et modularité des systèmes,

- redondance des systèmes de transmission des données,

K-F-1

- fiabilité et adaptabilité des logiciels,

- tolérance aux erreurs internes et possibilité de travailler en mode dégradé et reconfiguration rapide,

- résistance aux contre-mesures électroniques et à des destructions partielles,

- maintenance rapide et peu onéreuse.

Ces diverses contraintes, vous les connaissez aussi bien que moi mais il m'a semblé opportun de les rappeler car, par expérience, je connais les efforts d'ingéniosité faits par les chercheurs et les spécialistes que vous êtes pour atteindre les spécifications opérationnelles militaires qui vous sont fixées, dans un premier temps, par les utilisateurs qui, bien souvent, les proposent sans trop se soucier des coûts, préoccupés qu'ils sont par la réussite de la mission.

La solution, une fois trouvée, se trouve alors confrontée à des problèmes financiers insurmontables et ne peut voir le jour par manque de crédits.

# III LES CONTRAINTES HUMAINES

Après avoir résumé brièvement les contraintes techniques, je suis amené tout naturellement à vous présenter d'autres contraintes: les contraintes humaines qui doivent être prises en considération. Au niveau de l'avant-projet et du projet: la nécessité d'un dialogue permanent entre les concepteurs, les utilisateurs et l'équipe pluridisciplinaire chargée de coopérer pour sa réalisation.

Cette règle de management bien connue de tous est encore plus impérative lors de la conception d'un système d'armes hautement intégré de Guidage et de Pilotage et de Contrôle.

En plus du traitement et de la gestion des informations nécessaires à la réussite de la mission, elle impose et imposera aux équipementiers qui conçoivent les divers senseurs, les commandes de vol (jusqu'aux motoristes y compris) des choix technologiques et ceci au moins cinq ans avant la réalisation du prototype. Ils doivent donc être informés des spécifications à satisfaire pour produire des informations sous forme de signaux faciles à traiter dans un système hautement intégré afin d'éviter des interfaces coûteux et sources de pannes.

Les programmes "PAVE PILLAR" et "PAVE PACE" ouvrent la voie à cette recherche de solutions et vos travaux devraient pouvoir conduire à un concensus au sein des divers pays de l'Alliance Atlantique.

Je me permets d'insister sur ce point car pour les prochaines decennies il nous faudra veiller à nouer en permanence ce dialogue entre les concepteurs de systèmes hautement intégrés de guidage et de pilotage et les concepteurs de senseurs et de commandes de vol sinon nous disperserons nos efforts et continuerons à produire des systèmes très complexes et coûteux.

Pour certains d'entre vous qui connaissez ce problème, le choix du meilleur compromis possible, à moindre coût, n'est pas et ne sera toujours pas une chose simple à réaliser. Ce choix sera encore plus complexe à faire des lors que la réalisation d'un projet de système hautement intègré associera autour d'une même table, les concepteurs d'ordinateurs, les producteurs de logiciels, les équipementiers et les constructeurs des senseurs futurs qui, jusque là, faisaient cavaliers seuls et laissaient aux autres concepteurs du système d'arme global le soin de concevoir les interfaces.

Il conviendra en conséquence, dès la genèse du projet de créer des équipes pluridisciplinaires chargées de mener à terme le programme global du vecteur. Indépendamment des progrès technologiques en cours je reste persuadé qu'une des améliorations principales des futurs systèmes de guidage et de pilotage résidera dans cette reflexion er commun dès la phase initiale de la conception du projet. Grâce à cette concertation permanente, il sera possible de limiter de la complexité et la sophistication des systèmes hautement intégrés et automatisés en fonction sa finalité globale qui est: la réussite de la mission.

En effet, bien souvent encore nous assistons à des réalisations de sous ensembles dont la sophistication n'est pas justifiée le système étant pris dans son ensemble. En la matière il faut éviter de faire de "l'art pour l'art".

#### IV LES PERPECTIVES D'AVENIR

Dans un proche avenir, les progrès, les novations prévisibles dans le domaine du guidage du pilotage et du contrôle offriront de plus en plus aux utilisateurs un large éventail de moyens pour accomplir une mission donnée avec les mêmes chances de succès.

La compétition entre les vecteurs non pilotés, les vecteurs pilotés et les missiles entièrement autonomes sera de plus en plus ouverte.

Je ne retiendrai, dans mon propos, que les vecteurs pilotés pour tenir compte de la présence d'un être humain à bord et du rôle qu'il doit jouer dans la boucle de la gestion des données et des actions qu'il doit effectuer, dans un minimum de temps, en fonction des informations qui lui sont présentées.

#### K-F-2

A l'heure actuelle le pilote de combat ou l'équipage est confronté à de multiples sources d'informations dont la variété et la non homogénéité ont tendance à disperser son attention et à accroître sa charge de travail dans les phases les plus critiques de la mission. Il doit en permanence faire une synthèse entre les informations synthétiques et la perception visuelle de l'environnement dans lequel il évolue.

Il importe donc, dès la conception des systèmes futurs de guidage de pilotage et de contrôle, de garder en mémoire qu'une des finalités du système est de présenter au pilote les informations claires et précises limitées et séquentielles qui correspondent aux nécessités de l'instant.

Un des efforts, et non des moindres, pour le proche avenir que les concepteurs de systèmes hautement intégrés auront à fournir sera de concevoir une présentation des données sur les tableaux de bord qui pourrait aller jusqu'à la reconfiguration du cockpit dans son ensemble des vecteurs de combat des futures générations.

Les perspectives prometteuses des systèmes experts, de l'intelligence artificielle et de la visualisation en trois dimensions des données synthétiques devraient aider à résoudre ce problème.

Il est certain que cette novation peut encore ajouter à la sophistication et à la complexité des systèmes de guidage de pilotage et de contrôle des futures générations des systèmes d'armes; mais elle peut aussi aboutir à des simplifications très appréciables s'il s'agit d'un système entièrement nouveau et non de l'adaptation de technologies nouvelles sur un concept ancien.

A ce titre, le moment me semble venu de faire une synthèse des différentes technologies que les sous ensembles devront constituter un système de guidage de pilotage et de contrôle afin d'amorcer l'ébauche de l'architecture d'un concept global "Management des données nécessaires à la mission".

Cette tâche est certainement très lourde et délicate à conduire et demandera beaucoup d'effort et de temps mais elle me semble à la portée de votre commission car notre programme de travail porte sur la majorité des points que je viens d'évoquer.

Une étude de ce type devrait dégager des recommandations et ues directives qui permettraient à chacun des concepteurs d'une partie du "puzzle" que constitue un système de guidage de pilotage et de contrôle hautement intégré (d'un vecteur aérien, piloté ou non), de concevoir son projet suivant un schéma directeur et probablement d'adopter un langage commun pour la transmission des données. Ceci devrait conduire à terme à l'adoption d'une certaine normalisation et réduire la complexité et la sophistication du système global et par voie de conséquence de son coût, approche de système qui doit être développée dès l'Ecole. Je sais que Sup Aéro doit être la première, sinon une des écoles, à introduire cette réflexion dans les cours.

Cette étude au niveau des sous-ensembles: conduite de tir-missile, navigation, pilotage devrait permettre de déterminer la part du guidage et du pilotage à maintenir à bord du "vecteur plateforme" et la part à embarquer dans le "missile" pour atteindre son objectif avec la plus grande autonomie possible.

Cette réflexion sous entend que seuls les sous systèmes du système de guidage de pilotage et de contrôle nécessaires aux différentes phases de la mission (conduite et manoeuvre de l'avion du décollage, à l'accrochage de l'objectif et indispensables au retour et à l'atternssage) seraient maintenu à bord du vecteur plate forme, l'autre partie du système étant intégrée à bord du ou des missiles. A l'évidence une telle analyse devrait également prendre en considération l'assistance fournie par des systèmes de navigation des futures générations du type GPS-NAVSTAR ou d'avions du type AWACS, GTIS, etc... afin de réduire ou de simplifier, si possible, le nombre des senseurs embarqués.

Comme je l'ai déjà souligné précédemment, de telles études ne peuvent aboutir que si un dialogue permanent est maintenu entre toutes les parties prenantes du Système global.

La frontière est tellement étroite entre le concept de Guidage de Contrôle et de pilotage et le concept "Avionique" du vecteur que la réponse à la question de savoir qui doit être maître d'oeuvre du système global reste posée.

Vos symposia inter Panel GCP---AVP pourront peut-être répondre à cette délicate question.

Un des points faibles des forces de l'OTAN face à une menace potentielle des forces du Pacte de Varsovie restant l'infériorité en nombre, il m'apparait très intéressant de voir dans quelle mesure de tels concepts permettraient d'accroître le nombre de nos vecteurs aériens "plateforme" en diminuant leur coût tout en maintenant notre supériorité technologique.

### V LES CONTRAINTES FINANCIERES

Enfin, il existe une dernière contrainte et non la moindre: *la contrainte financière*. Vous n'êtes pas sans savoir que celles-ci pèsent de plus en plus lourdement sur tous les budgets militaires des pays de l'Alliance. Elle est en particulier très sensible dans le domaine qui nous intéresse. Une évaluation globale du coût de l'ensemble des senseurs et des capteurs embarqués à bord d'un vecteur piloté qui concourent, plus ou moins étroitement, à la réalisation d'un système performant de guidage de pilotage et de contrôle montre que celui-ci représente pratiquement 40% du coût total du vecteur.

# K-F-3

Face à ces contraintes financières et à l'ampleur des études à mener à terme, il apparaît à l'évidence que l'atteinte de tels objectifs dépasse bien souvent les possibilités d'un seul pays et que le besoin de conjuguer nos efforts au sein de l'Alliance, dès que de nouvelles technologies apparaissent prometteuses, devient de plus en plus pressant.

Les négociations en cours sur la réduction des armements conventionnels et les armements stratégiques à courte portée qui conduiront à terme à la parité numérique des systèmes d'armes Est—Ouest hors des frontières du pays d'origine (USA-URSS) rendront cette nécessité de coopération encore plus nécessaire.

Il faudra non seulement coopérer pour la réalisation de tel ou tel système d'arme, mais encore reporter les efforts sur le large éventail de la panoplie des systèmes d'arme à mettre en œuvre pour maintenir notre efficacité.

A la notion de durée face à un ennemi supérieur en nombre nous devons substituer la notion d'adaptation de nos forces à la neutralisation d'objectifs tant sur le théatre des combats qu'en profondeur ce qui conduira probablement à revoir nos armements aériens conventionnels et par voie de conséquence les concepts de guidage et de pilotage des armements des futures générations.

S'il est utopique de penser à court terme de voir disparaitre la compétition internationale industrielle dans ce secteur de pointe, il me semble réaliste, en raison de l'enjeu que représente le maintien de la liberté du monde occidental, de regrouper nos efforts de recherche et de concept afin de dégager un certain nombre de troncs communs, de mode d'action et d'interopérabilité entre les divers systèmes d'armes, tout en laissant à chacune des Nations leur Génie industriel et le libre choix de coopérer sur des réalisations aérospatiales communes.

Il est bien souvent regrettable de voir plusieurs nations de l'Alliance épuiser individuellement leurs ressources financières en recherches et réalisations sur un même problème technologique pour finir par constater que, la solution au problème posé est trouvée par chacun de ces pays, pratiquement au même moment, à de très rares exceptions près, et que le produit réalisé a sensiblement les mêmes performances et fait appel aux mêmes novations.

Dans bien des cas, sur des objectifs clairement définis et approuvés, une meilleure coopération au sein des pays de l'Alliance, dès la genèse du projet, aurait permis d'atteindre les objectifs à moindre coût et certainement plus rapidement sans compromettre l'essort industriel de nos pays respectifs.

Si dans le passé, on pouvait encore admettre que malgré les coûts élevés, tel ou tel pays de l'Alliance pouvait s'offrir ce luxe, les grands enjeux technologiques aérospatiaux des prochaines décennies (SDI – Avion de Transport Supersonique) ne le permettront plus.

Si nous poursuivions dans cette voie égoiste, il est à craindre que beaucoup de ces études resteraient des "études papier...."

Nos adversaires potentiels, plus pragmatiques, tireraient bénéfice de nos problèmes et en plus de leur supériorité numérique dès les premiers jours du conflit nous rejoindraient sur le plan technologique.

Par manque de crédits de programme ou par un étalement dans le temps de l'industrialisation des vecteurs, l'OTAN perdrait ainsi sur le plan des armes conventionnelles la crédibilité qui est encore la sienne et que je qualifierai de "Dissuasion Conventionnelle tactique et manoeuvrière" ce qui serait néfaste à la stratégie globale des pays de l'Alliance.

#### VI CONCLUSIONS

L'AGARD est certainement l'organisme le mieux adapté et par le sujet qui concerne, au sein de celle-ci, votre commission pour mener à terme de telles études et convaincre vos autorités respectives de l'intérêt d'une coopération concertée.

En effet, vous êtes pratiquement le seul forum, sinon le seul groupe d'experts de haut niveau où, en dehors de toute contrainte étatique vous pouvez vous consacrer entièrement à des recherches novatrices, formuler des recommandations pertinentes et maintenir le dialogue permanent entre tous les experts des diverses disciplines scientifiques qui concourent à la réalisation des futurs systèmes de guidage et de pilotage dont vos futurs systèmes d'armes devront être dotés.

K-F-4

62.

#### FLIGHT CRITICAL DESIGN CONCEPTS FOR LOW-LEVEL TACTICAL GUIDANCE AND CONTROL

Michael R. Griswold General Dynamics Fort Worth Division Fort Worth, Texas, 76101 United States of America

#### SUMMARY

Service and the service of the servi

Low-level combat operations (< 100 meters), such as might be typified by next generation Close Air Support (CAS) aircraft, present new demands on the guidance and control system. The design must address not only the traditional flight-critical definitions related to system management, ground collision avoidance, and operational flight restrictions, but also the possibility of increased exposure to defensive countermeasures due to system failure. It is also clear that traditional guidance and control methods must be re-examined in light of total mission goals. For instance, employing an active sensor to aid in terrain avoidance may decrease overall combat survivability due to increased detectability by threats.

This paper presents several of the elements of flight critical concepts for low-level tactical operation. This includes classical elements as well as mission-specific considerations such as threat exposure and threat evasion. In both cases, system failure may compromise safety. The mission scenario for the discussions presented in this paper is the CAS mission using a fast moving, technologically advanced aircraft.

The guidance and control strategies for the proposed application are discussed with emphasis on system integrity considerations and performance-versus-safety-issues. The previous generation of low-level guidance and control algorithms (such as the ADLAT terrain following algorithm) has been outmoded by the advent of onboard digital terrain databases. By utilizing these databases, it is possible to devise algorithms with far better performance characteristics. At the same time, reliance on the stored terrain data expands the flight critical umbrella to include the navigation system and the process for correlating the terrain database with the actual terrain. Functional partitioning must be re-examined to meet data latency requirements and minimize the distribution of the digital terrain data.

Terrain verification is a critical process for low-level operation when the digital terrain database is utilized for fundamental guidance and control information. While the use of onboard data offers many possibilities for improving the guidance and control system, it brings the need to weigh the risks of database use. The requirements for an active terrain sensor are examined. These requirements are driven by the characteristics of the terrain (and obstacles) to be measured, and by the performance and maneuvering envelope of the aircraft and the constraints on aircraft emissions.

Fault detection and management schemes are also examined. The application of previously developed system-wide integrity management design philosophies are considered for subsystem integrity monitoring and communications. These techniques are reviewed with an eye toward analytical and inductive redundancy techniques to achieve acceptable levels of detection without resorting to physical redundancy. In addition, by integrating the operation and information exchanged between several subsystems, it is possible to achieve practical fault detection strategies through estimation filters and to improve system performance during nominal operation.

#### THE CLOSE AIR SUPPORT MISSION

The Close Air Support (CAS) mission has been selected as the baseline tactical environment for these discussions. The CAS mission is extremely stressful for both the pilot and the aircraft avionic systems since by nature it requires low-altitude operation in a high threat environment with demanding targeting and weapon-delivery requirements. This mission and the desirable aircraft configuration are under considerable scrutiny by the U.S. Air Force, thus making a discussion of technology applications timely.

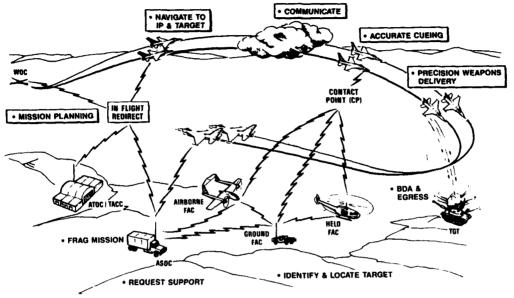

A CAS mission is typically distinguished from other types of tact.cal battlefield operations by: (1) striking hostile targets that are in very close proximity to friendly ground forces, and (2) requiring close coordination and integration with these ground forces. Figure 1 depicts the main steps in a CAS mission and the principal coordinating elements. CAS aircraft operate from the Forward Edge of Battle Area (FEBA) to about 8 kilometers within enemy territory. These aircraft can play a key role in the battlefield due to their combination of speed, range, and firepower.

To achieve the level of coordination and timing required for success, a considerable part the CAS mission is dedicated to communicating mission requirements and goals and to planning the mission. This starts with the determination of initial need for support (from the Army battalion commander), tasking by the Air Support Operations Center (ASOC) and Tactical Air Control Center (TACC), enroute control, and final control and briefing

from the Forward Air Controller (FAC). Communications to and from the aircraft involve critical processes that are undergoing technological upgrades to improve reliability and reduce pilot workload.

Figure 1 CAS Mission

The pilot's tasks in the CAS mission, after receiving his initial tasking, are to navigate his aircraft to the appropriate contact points, to receive his final briefing from the FAC, to acquire the target, to perform an accurate weapon delivery, and to egress. Accurate navigation is essential to reach the contact points accurately and within the given time windows. It is also a prime factor in the pilot's ability to locate the target once he has received location cues from the FAC. Weapon delivery must be precise in order to be effective against armored or hardened targets and to avoid damage to friendly forces. Situation awareness and low-altitude flight is required in order to minimize the risk from enemy threats. Operation at night further compounds the pilot's workload.

While the configuration of the next generation CAS aircraft is still a subject of considerable debate, one of the primary candidates is an F-16 derivative. Proponents of the F-16 foresee the pilot relying on high-speed, low-altitude ingress to avoid enemy threats. To be able to ingress fast and low and still to acquire the targets, the CAS F-16 would use a specially tailored sensor suite, coupled with an accurate navigation. Finally, CAS-specific weapons would complete the vehicle configuration.

The AFTI/F-16 CAS Program is currently investigating technology applications for improving autonomous navigation and target acquisition for the F-16 or similar aircraft. (Reference 1) To date, little has been done in demonstrating automated guidance and control applications for fast moving, low-flying CAS aircraft. The upcoming AFTI/F-16 CAS flight test demonstrations may address these issues. The concepts presented here would be applicable to this effort.

#### GUIDANCE AND CONTROL ISSUES

In developing a guidance and control strategy for an F-16 class CAS aircraft, several major issues must be considered. Perhaps the first question concerns the proper level of automation that should be provided. Automation is typically used in a fighter for two purposes: (1) to help alleviate pilot workload during critical mission phases, and (2) to perform tasks which might be outside the pilot's control bandwidth. Of course these two aspects are related to some extent since high workload may reduce the pilot's effectiveness in performing some "high-gain" tasks. For the CAS mission, clearly the pilot's work-

load is high. Communications, coordination with other friendlies, target acquisition, and threat avoidance will quickly work to saturate the pilot's attention. If low-level, high-speed tactics are employed, the pilot's control bandwidth may also become saturated if significant terrain is encountered. This may cause the pilot to fly higher, raising the level of threat exposure. Given these considerations, some level of guidance and control automation is reasonable. If we consider a fully automated guidance and control system for CAS, several of its fundamental characteristics can be readily deduced.

Since CAS operations, by their very nature, involve delivering weapons on enemy targets that are in close proximity to friendly troops, the weapon-delivery system must be precise. Weapon lethality is a function of target type, weapon effectiveness and delivery accuracy. Since target types are specified, improved weapons and delivery accuracy are the primary considerations for improvements. The key for survivability is to minimize the number of passes that must be made by making every pass count.

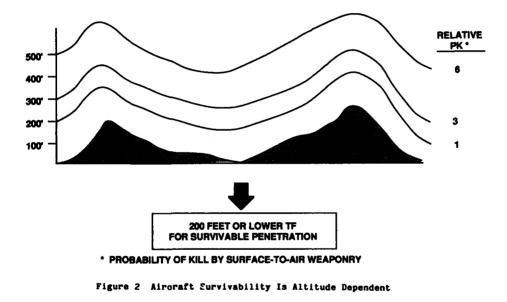

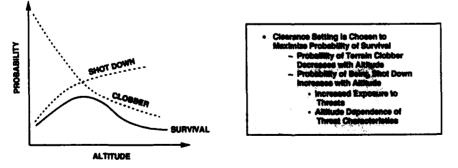

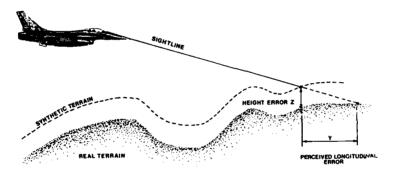

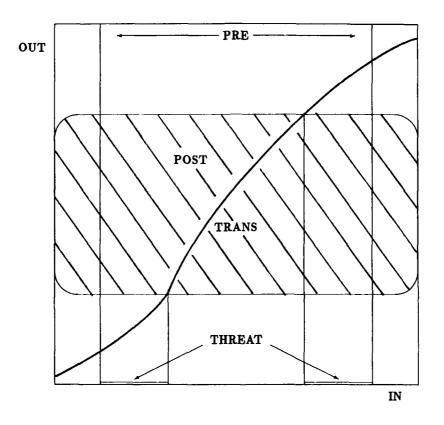

Both passive and active threat avoidance are also important in defining the guidance and control strategy. Passive avoidance is achieved by maintaining the least exposure to potential threat's (known or otherwise) by flying low to reduce the threats effective horizon, and by flying as fast as possible to deny the threat enough time to react to ownship detection if it occurs (Figure 2). To achieve these goals implies a terrain following capability that not only has good terrain hugging characteristics but does not of itself limit the aircraft penetration speed. Despite the advantages of low flight, there remains a practical limit on how low the aircraft may reasonably operate (Figure 3). The nature of the ground collision curve is very much a function of the guidance and control scheme employed.

Figure 3 Terrain Clearance Constraints

Active threat avoidance implies actually determining a route through an array of known or suspected threats, and accounting for threat sensor characteristics and lethal-ity. This typically involves using modeled threat data, terrain profiles, course con-straints (checkpoints, contact points, etc.), target location, and possibly schedule con-straints (time over target, free fire zone windows). While systems have been demonstrat-ed with these capabilities, ground-based in particular, systems suitable for tactical fighters are only now beginning to emerge. The practical constraint on these systems is to provide sufficient processing power onboard to allow the near-real-time replanning re-quired to effectively handle unexpected threats. In particular, if the route planning system is part of an automated guidance and control system, it clearly must not be al-lowed to steer the aircraft into known threats, either by virtue of slow response or sys-tem failure. A complement to the route planning guidance scheme for threat avoidance is an automated evasive maneuver taken in response to a threat detection (or even launch in-dication). dication).

In summary the guidance and control system for this conceptual CAS aircraft provides automated systems for terrain following, optimal route planning for threat avoidance, and weapon delivery. The terrain following algorithm should provide robust terrain hugging capability to generally limit threat exposure.

The system should not limit the pilot's ability to maneuver aggressively while still assuring ground clearance. The route planning algorithms must be responsive and accurate in minimizing threat exposure. Weapon delivery, the ultimate goal of the mission, must be accurate to achieve the desired damage to the enemy while avoiding friendly forces. These functions are flight critical since failure or poor performance can cause the air-craft to hit the ground, be shot down, or drop weapons on friendly forces.

Recent General Dynamics' experience with low-level automated guidance and control was the AFTI/F-16 Program (Reference 2). While this system clearly showed the potential for the AFTI/F-16 Program (Reference 2). While this system clearly showed the potential for this type of operation, the system was constrained to operation over relatively flat ter-rain (less than 2% grade). This allowed the development of a reliable ground collision avoidance system with a straight-forward combination of radar altimeter and inertial mea-surements. Clearly, this is insufficient for CAS operations, which will likely be required in rugged terrain.

#### TERRAIN DATA MANAGEMENT

The key to extending the previous AFTI/F-16 development is the application of onboard digital terrain data. The database provides an independent source of elevation data that can be used and correlated with other (real-time) measurements to give an unprecedented picture of the surrounding terrain. In general, the database can be considered a sensor; its limitations, such as accuracy and failure modes, must be fully accounted for. The database also provides a convenient logical representation of terrain data for the correlation and blending of data from other sources.

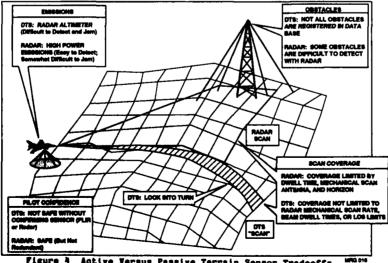

The decision to rely on the digital terrain database as a primary source of terrain information (as opposed to a radar) is not without problems (see Figure 4). The principal issues cited are the accuracy and completeness of the database. While these problems should be reduced with time (due to improved mapping techniques), their impacts must be carefully weighed against the probability of loss of the aircraft, particularly during peacetime.

Figure 4 Active Versus Passive Terrain Sensor Tradeoffs

4

ð

-----

Terrain data management encompasses three related processes, terrain data correlation, terrain data verification, and terrain data blending. Reliance on a stored terrain database requires the proper correlation of the actual aircraft position within the database. This registration can be accomplished by either a self-contained terrain correlation algorithm, by an external position fixing system such as the Global Positioning System (GPS), or a combination of both. Reference 3 describes several representative algorithmic approaches. While the original motivation for these algorithms was increased navigational accuracy, they now form the basis for referencing the actual aircraft position with the stored terrain database. Since data are being extracted from the database for guidance and control purposes (i.e., terrain following), the correlation process is clearly flight-critical. Unfortunately, the current implementations of these algorithms are not fail-safe. Architectural considerations aside, the correlation algorithm's own estimate of its performance is not an adequate failure monitor.

Even a highly registered terrain database may not accurately represent the surrounding terrain. Several General Dynamics' sponsored flight test experiments have pointed up various classes of database anomalies such as rounded or truncated peaks, shifted terrain features, and actual missing features. In addition, significant man-made obstructions (towers, power lines, etc.) are not reliably represented. Even if the pilot is manually flying the aircraft, it cannot be assumed that he will perceive a potential collision in time to react. Some form of real-time data-base verification is required to overcome these problems. (Of necessity, a course of action must be planned in the event discrepancies are noted.)

The probability of collision for a low-flying aircraft is dependent on: (1) the probability of actually encountering an obstacle, (2) the probability of not detecting the obstacle once it is encountered, and (3) the probability of colliding with the obstacle if it is not detected (or not detected in a timely manner). Critical obstacles can typically be categorized as terrain, towers (and possibly its related support wires), and cables spanning towers. Various studies have attempted to quantify the encounter rate for different types of obstacles (Reference 4).

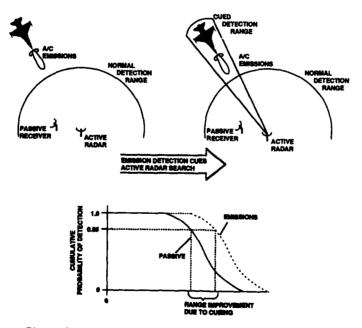

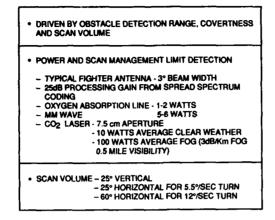

Establishing the obstacle encounter rate for various types of obstacles is a critical design point since it strongly influences the type of sensor required for obstacle detection. In particular, the percentage of obstacles that Ku- and X-band radars cannot reliably detect becomes significant within 100 meters of the ground. The probability of obstacle determined from the sum of the maneuver time (for obstacle avoidance) and the measurement and processing times. These detection ranges typically vary from 1 to 3 kilometers depending on the obstacle type. Obviously the use of an active sensor to reduce terrain database risk itself increases the risk of detection by potential threats (Figure 5). For this reason, techniques are evolving for so-called covert sensors which rely on low-power levels, modified wave forms and different operating frequencies to avoid detection. Table I gives typical sensor parameters.

Figure 5 Active Sensor Emissions Decrease Survivability

ł

#### Table I Guidance and Control Functions

To provide a more robust system, the stored terrain data and the sensed terrain data should be combined to provide a composite database from which to drive the various guidance and control algorithms. In the process of combining the terrain data, differences in the measured elevation from the different sources can be compared against established thresholds to determine if an exceptional condition (such as sensor failure) has occurred. The simplest approach is to use the highest of either the sensed or the stored terrain elevation at a given point. This is the most conservative approach, but it runs the risk of driving the aircraft higher than needed for terrain clearance and may increase threat exposure. A maximum-likelihood blending algorithm would reduce the conservatism by combining the elevation data on the basis of their respective measurement variance.

### GUIDANCE AND CONTROL ALGORITHMS

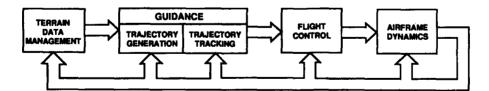

A conceptual representation of the guidance loop is shown in Figure 6. In this model, the terrain data management and the guidance command generation functions represent any flight-critical elements. By using the terrain database format as the underlying representation of terrain data, the guidance and control algorithm development can be largely decoupled from the sensor development. (This is not to say that the choice of sensors is unimportant to the algorithm designer, indeed the available sensor suite may drive the fundamental guidance and control strategy.) Typically, three basic guidance and control algorithm that provides lateral steering. The third is a ground-collision-avoidance algorithm that provides a preemptive response to impending ground impact. Other candidate algorithms might include an automated weapon-delivery system and a missile evasion system. The performance criteria of these algorithms must be established in light of the CAS mission. Criteria that apply for strategic missions or interdiction missions may not be appropriate.

Figure 6 Terrain-Based Guidance Loop

d.

For CAS, the terrain following system must be dynamic enough to allow extensive pilot maneuvering. Currently fielded terrain-following implementations typically limit the aircraft turn rate on the order of 5 degrees per second. This constraint, while largely driven by the terrain sensor characteristics, is not incompatible with their design mission. Since emerging agile beam radars and scanning laser ranging systems, coupled with the digital terrain database, can remove these limitations, the algorithmic design can be readdressed. The particular need is to provide a wide maneuvering envelope consistent with the CAS mission requirements.

The need for an independent ground collision avoidance system (even in the presence of a terrain-following system) is two-fold. First, an independent algorithm can provide coverage for certain classes of failures in the terrain-following system (depending on the overall system architecture). More importantly, if the pilot is manually flying the aircraft through a maneuver which is outside the normal terrain-following envelope (such as missile evasion), the ground collision avoidance system should operate to provide a preemptive safeguard against ground collision. In essence, the two algorithms, terrainfollowing and ground-collision-avoidance, have subtly different goals. The terrain- following algorithm attempts to maintain a set clearance along a certain flight path. The ground-collision-avoidance algorithm attempts to prevent ground collision for any state the aircraft attains.

#### INTEGRITY MANAGEMENT

NAME AND A CONTRACTOR OF A

11-14 1-14

....

2

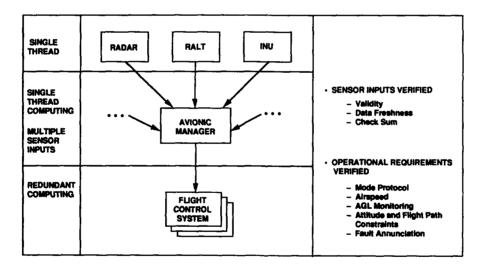

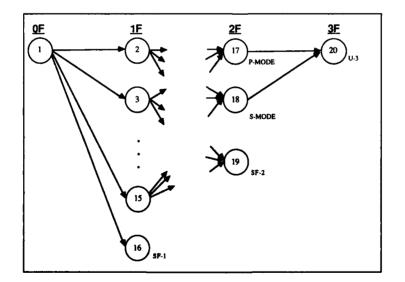

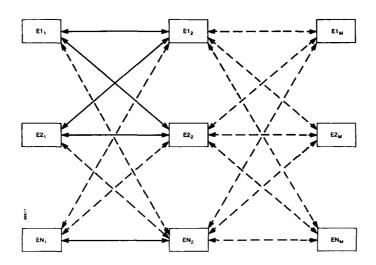

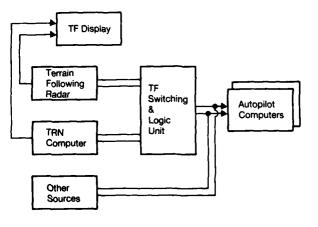

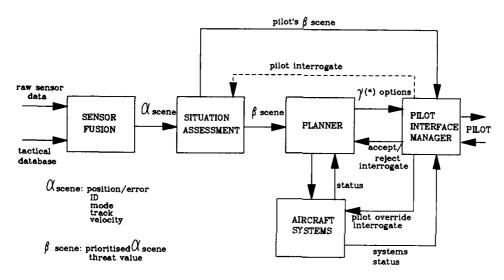

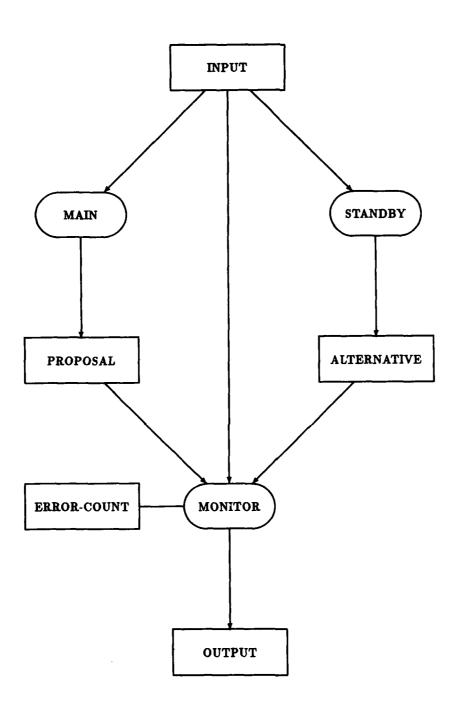

For integrity management purposes, the architecture of the guidance and control system is shown in Figure 7. Typically, single-thread sensors and systems are supplying data to a system manager. The manager, while single thread computationally, has access to enough multiple-sensor measurements to judge the validity of its data sources. Finally, a physically redundant system judges the health of the entire system. Previous General Dynamics' experience in the design of fault detection algorithms for the AFTI/F-16 AMAS low-level operations (Reference 5) was successful in developing a robust and reliable system by using this architecture.

Even a poorly conceived system may be reliable during normal operation. A thoroughly reliable system could be designed using a stored terrain database, terrain-following system driving the flight control system for automated operation. Without a proper understanding of the potential failure modes and, just as importantly, of their effects, the system cannot be considered safe.

.

High-speed maneuvering in rugged terrain or in close proximity to the ground will demand a rapid assessment of systemic hazards resulting from malfunction or miscalculation. Fotential hazards can result from (1) failure or inappropriate operation of physical elements (such as hydraulics, processors, media used for storage and communication, and sensors), and (2) algorithmic and implementation flaws, as well as inadvertent pilot actions. After detecting a hazardous situation, the integrity management system must provide for the safe recovery from the situation and for an orderly resumption of manual pilot control. In order to provide for the detection of suspected subsystems and for the proper identification and annunciation of faults, the integrity management system must various redundancy techniques.

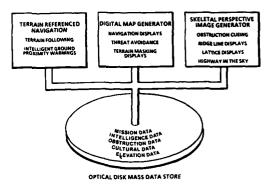

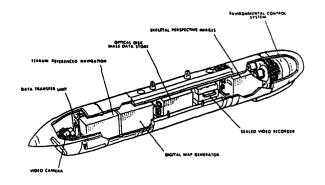

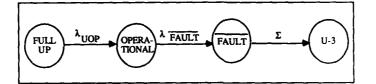

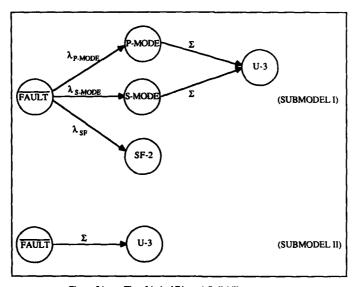

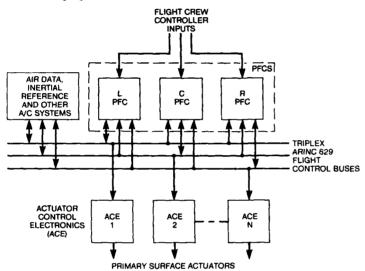

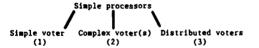

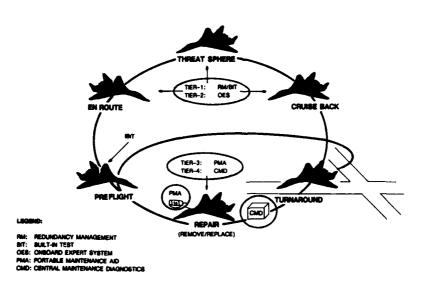

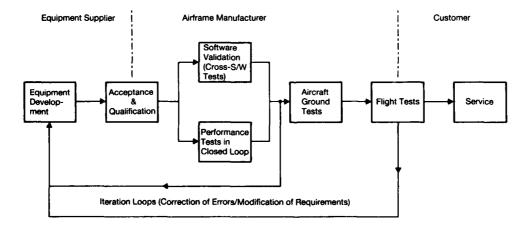

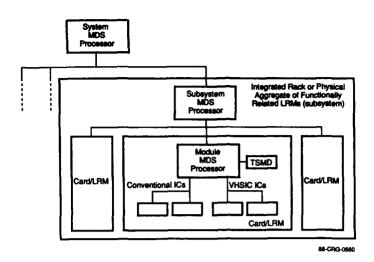

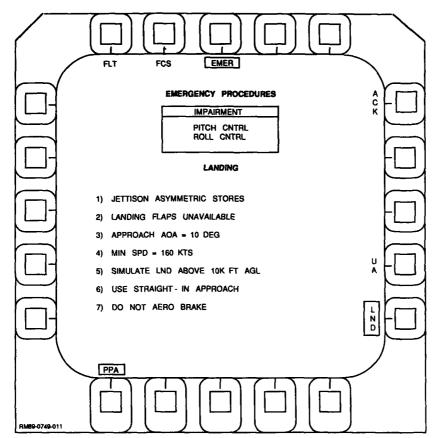

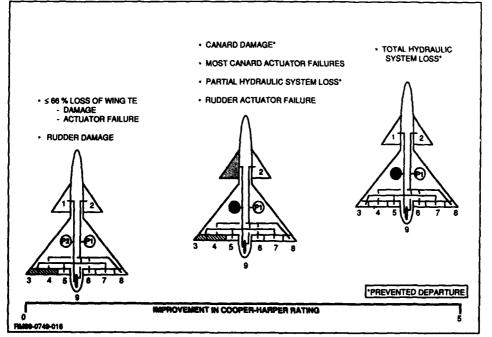

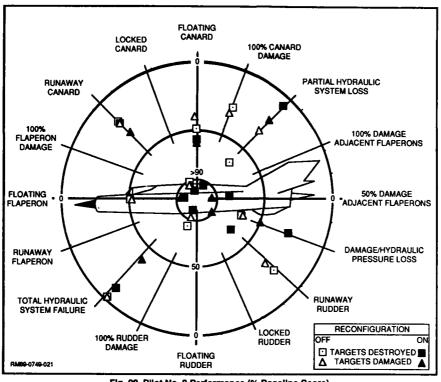

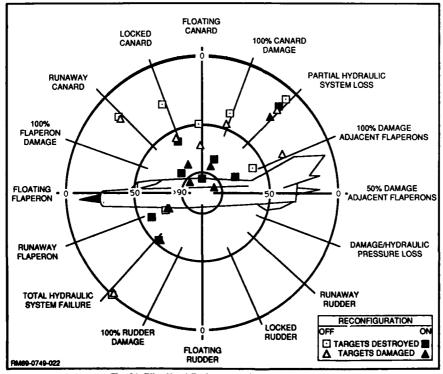

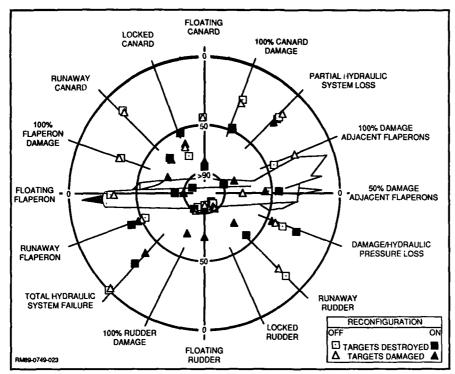

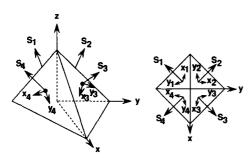

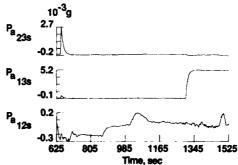

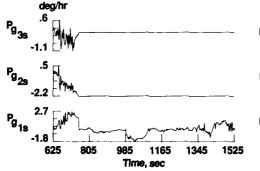

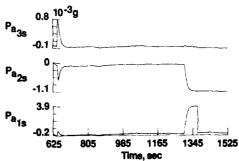

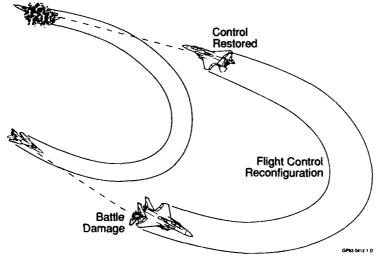

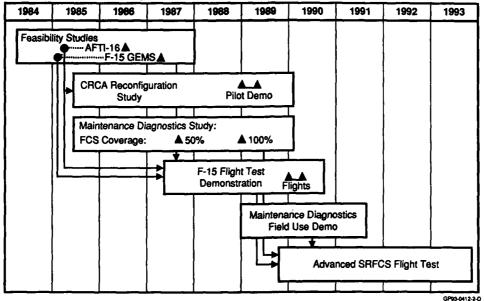

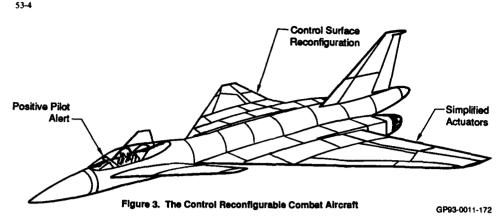

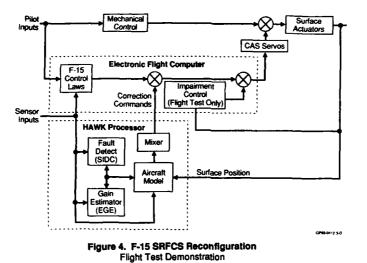

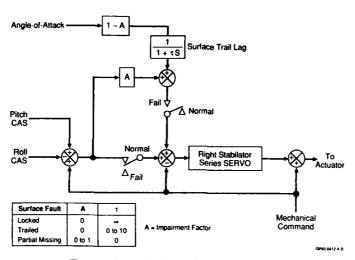

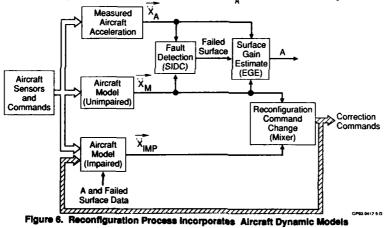

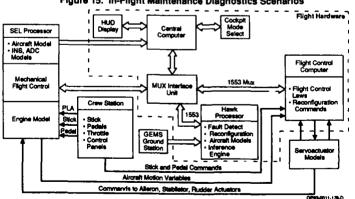

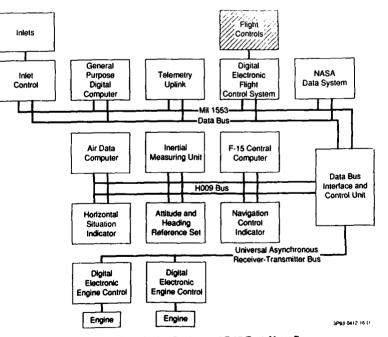

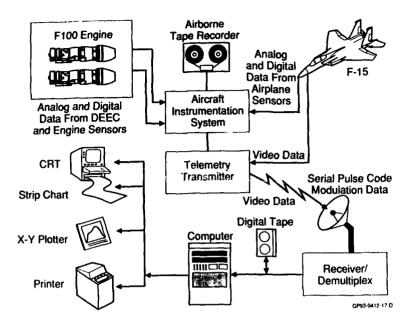

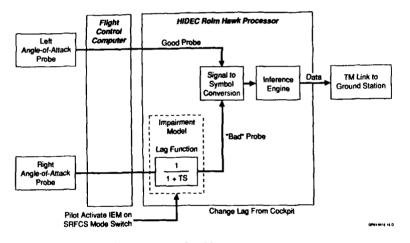

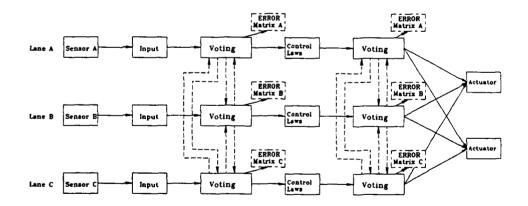

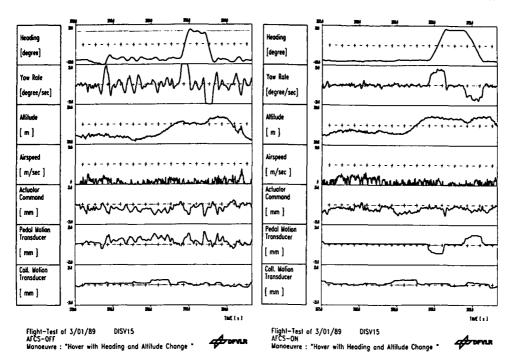

----