MILRORDER RESOLUTEN TEST CHART

TTIC EILE CORY

AD-A215 762

Hypercube Expert System Shell -Applying Production Parallelism

THESIS

William Arthur Harding Captain, USAF

AFIT/GCS/ENG/89D-6

4

5

DEPARTMENT OF THE AIR FORCE

AIR UNIVERSITY

# AIR FORCE INSTITUTE OF TECHNOLOGY

89 12 26 147

Wright-Patterson Air Force Base, Ohio

Annoved for public releases Distribution Unlimited

## AFIT/GCS/ENG/89D-6

Hypercube Expert System Shell - Applying Production Parallelism

## THESIS

Presented to the Faculty of the School of Engineering of the Air Force Institute of Technology Air University In Partial Fulfillment of the Requirements for the Degree of Master of Science in Computer Engineering

> William Arthur Harding, B.A. Captain, USAF

Approved for public release; distribution unlimited

## Preface

This study was prompted by the need for expert system software to produce required results in real-time for systems like the Robotic Air Vehicle. The expert system processing speedups realized on serial machines due to state-saving match algorithms like Rete are impressive, but they still fall short of real-time processing. This research investigation focuses on parallel processing of such state-saving algorithms with the goal of achieving real-time expert system processing.

William Arthur Harding

| Acces | sion For    |       |

|-------|-------------|-------|

| NTIS  | GRALI       | B     |

| DTIC  | TAB         |       |

|       | ounced      |       |

| Justi | fication_   |       |

|       |             |       |

| By    |             |       |

| Distr | ibution/    |       |

| Avai  | lability    | Codes |

|       | Avail an    | d/or  |

| Diat  | Specie      | l,    |

|       | 1           |       |

| 0.1   |             |       |

| IN .  |             |       |

|       | سال سیسی از |       |

## Acknowledgments

This work would not have been possible without the support of my wife, Carol. I thank my thesis advisor, Dr. Gary Lamont, for his insight and direction. I am grateful to Captain Donald Shakley and Lieutenant Jesse Fanning for providing the background information from which I could proceed with my research. I am also endebted to my many AFIT classmates, especially Captain R. Andrew Beard, Captain Mark Huson, Captain William Koch, and Captain Michael Proicou, for their guidance and support at key points during this research investigation.

I lovingly dedicate this effort to my daughter, Erin Marie.

J

William Arthur Harding

## Table of Contents

Ĵ

ļ

Í

×.

|                                     | Page  |  |  |  |

|-------------------------------------|-------|--|--|--|

| Preface                             | ii    |  |  |  |

| Acknowledgments                     |       |  |  |  |

| Table of Contents                   |       |  |  |  |

| List of Figures                     |       |  |  |  |

| Abstract                            | ix    |  |  |  |

| I. Introduction                     | 1-1   |  |  |  |

| 1.1 System Requirement              | 1 - 1 |  |  |  |

| 1.2 Related Work                    | 1-2   |  |  |  |

| 1.3 Problem Statement               | 1-2   |  |  |  |

| 1.4 Research Objectives             | 1-3   |  |  |  |

| 1.5 Scope                           | 1-3   |  |  |  |

| 1.6 Constraints                     | 1-4   |  |  |  |

| 1.7 Summary                         | 1-4   |  |  |  |

| II. Background                      | 2-1   |  |  |  |

| 2.1 Production System               | 2-1   |  |  |  |

| 2.2 Expert System                   | 2-4   |  |  |  |

| 2.3 Speedup and Parallel Processing | 2-5   |  |  |  |

| 2.4 Communication Overhead          | 2-6   |  |  |  |

| 2.5 Load Imbalance                  | 2-8   |  |  |  |

| <b>2.6</b> Summary                  | 2-8   |  |  |  |

|      |            |                                           | Page |

|------|------------|-------------------------------------------|------|

| III. | Productio  | n System Performance Improvement Concepts | 3-1  |

|      | 3.1        | Potential Production System Parallelism   | 3-1  |

|      | 3.2        | Rete Match Algorithm                      | 3-2  |

|      | 3.3        | Parallelizing Rete                        | 3-8  |

|      | 3.4        | Summary                                   | 3-10 |

| IV.  | Research   | Methodology                               | 4-1  |

|      | 4.1        | Justification of Method Sclected          | 4-1  |

|      | 4.2        | Performance Spectrum                      | 4-2  |

|      | 4.3        | Research Investigation Steps              | 4-5  |

|      | 4.4        | Statistical Procedures                    | 4-6  |

|      | 4.5        | Summary                                   | 4-6  |

| V.   | Step 1: Lo | ower Bound Performance                    | 5-1  |

|      | 5.1        | System Design                             | 5-1  |

|      | 5.2        | Detailed Design                           | 5-2  |

|      | 5.3        | Implementation                            | 5-2  |

|      | 5.4        | Summary                                   | 5-4  |

| VI.  | Step 2: U  | pper Bound Performance                    | 6-1  |

|      | 6.1        | System Design                             | 6-1  |

|      | 6.2        | Detailed Design                           | 6-1  |

|      | 6.3        | Implementation                            | 6-2  |

|      | 6.4        | Summary                                   | 6-4  |

| VII. | Step 3: C  | urrent Best Performance                   | 7-1  |

|      | 7.1        | System Design                             | 7-1  |

|      | 7.2        | Detailed Design                           | 7-1  |

|      | 7.3        | Implementation                            | 7-4  |

ļ

)

|       |                  |                                      | Page |

|-------|------------------|--------------------------------------|------|

| VIII. | Step 4: Pa       | arallel Rete Performance             | 8-1  |

|       | 8.1              | System Design                        | 8-1  |

|       | 8.2              | Detailed Design                      | 8-1  |

|       | . 8.3            | Implementation                       | 8-4  |

|       | 8.4              | Summary                              | 8-7  |

| IX.   | Step 5: Pe       | erformance Comparison Findings       | 9-1  |

| Х.    | Conclusion       | ns and Recommendations               | 10-1 |

|       | 10.1             | Research Conclusions                 | 10-1 |

|       | 10.2             | Research Recommendations             | 10-1 |

|       | 10.3             | Summary                              | 10-2 |

| Appen | idix $\Lambda$ . | Robotic Air Vehicle Background       | A-1  |

| Apper | ndix B.          | Parallel Processing Architectures    | B-1  |

| Apper | ndix C.          | Timing Analysis of RAV Expert System | C-1  |

| Apper | ndix D.          | Parallel RAV Expert System Program   | D-1  |

| Apper | ndix E.          | HyperCLIPS Programmer's Manual       | E-1  |

|       | E.1              | General Overview                     | E-1  |

|       | E.2              | HyperCLIPS Initialization            | E-1  |

|       | E.3              | HyperCLIPS Basic Cycle of Execution  | E-1  |

|       | E.4              | Detailed Design                      | E-2  |

|       | E.5              | Embedding HyperCLIPS                 | E-3  |

| Apper | ndix F.          | HyperCLIPS Users' Manual             | F-1  |

|       | F.1              | HyperCLIPS Overview                  | F-1  |

|       | $\mathbf{F.2}$   | Requirements for Running HyperCLIPS  | F-1  |

-

|                             | Page   |

|-----------------------------|--------|

| F.3 Interface to HyperCLIPS | F-2    |

| F.4 HyperCLIPS Limitations  | F-5    |

| Vita                        | VITA-1 |

| Bibliography                | BIB-1  |

)

## List of Figures

| Figure                                      | Page                                  |

|---------------------------------------------|---------------------------------------|

| 2.1. Production System Algorithm            |                                       |

| 2.2. Expert System Components               |                                       |

| 2.3. Example Parallel Speedup Chart         |                                       |

| 3.1. Match-Select-Act Flow Graph            |                                       |

| 3.2. Sample Rete Graph                      | 3-3                                   |

| 3.3. Production Parallelism                 |                                       |

| 4.1. Example Performance Spectrum Chart     |                                       |

| 5.1. RAV Serial Rete Design                 | 5-3                                   |

| 7.1. RAV iPSC/1 Hypercube Design            |                                       |

| 7.2. iPSC/1 RAV Performance Results         |                                       |

| 8.1. RAV Hypercube Rete Design              | · · · · · · · · · · · · · · · · · · · |

| 9.1. RAV Expert System Performance Spectrum |                                       |

| A.I. RAV System Architecture                | A-2                                   |

| A.2. RAV System Configuration               | A-3                                   |

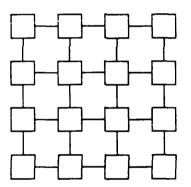

| B.1. 2-D Mesh Network                       | B-2                                   |

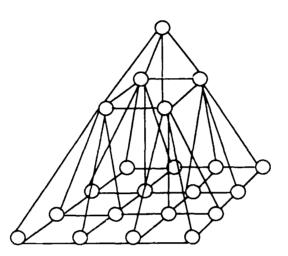

| B.2. Size 16 Pyramid Network                | B-3                                   |

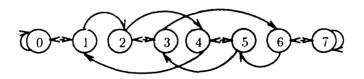

| B.3. 8-Node Shuffle-Exchange Network        | B-3                                   |

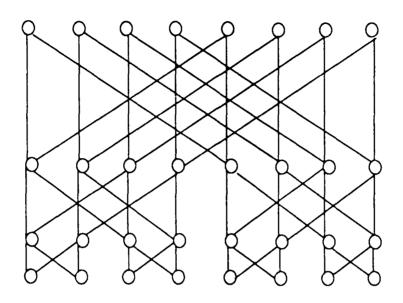

| B.4. 32-Node Butterfly Network              | B-4                                   |

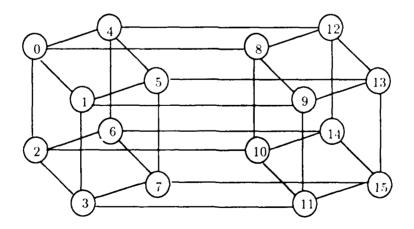

| B.5. 4-D Hypercube Network                  | B-4                                   |

| B.6. Summary of Architectures               | B-6                                   |

#### AFIT/GCS/ENG/89D-6

#### Abstract

This research investigation proposes a hypercube design (hardware and software) which supports efficient symbolic computing to permit real-time control of an air vehicle by an expert system. Real-time processing requirements motivate the researcher to alleviate common expert system bottlenecks. Examples of these bottlenecks include the inefficiency of symbolic programming languages like Lisp and the disproportionate amount of computation time commonly spent in the match phase of the expert system match select-act cycle.

In the design presented in this research investigation, faster processing of the Defense Advanced Research Projects Agency's (DARPA) Robotic Air Vehicle (RAV) expert system software is approached through 1) fast production matching using an expert system shell which employs Rete, a state-saving match algorithm, 2) more efficient expert system shell program execution due to implementation using the C-Programming Language and 3) parallel processing of the RAV expert system production cycle using multiple copies of the serial expert system shell. For this design, the serial C-Language Integrated Production System (CLIPS) shell, which uses the Rete match algorithm, is modified to execute in parallel on the iPSC/2 Hypercube. Although the RAV expert system is the application of interest in this investigation, the parallel expert system shell is capable of processing any CLIPS-syntax software.

Speedups achieved using this architecture are quantified through theoretical timing analysis, and comparison with serial architecture performance results, with earlier parallel architectures' performance results, with best case theoretical analysis performance results, and with the "real-time" goal performance. This performance quantification approach introduces the concept of a performance spectrum which exposes the level of maturity of RAV expert system processing in particular and the level of maturity of parallel expert system shell processing on a multicomputer in general. Hypercube Expert System Shell - Applying Production Parallelism

## I. Introduction

The feasibility of improving the performance of production system software (particularly, expert system software) running on a parallel architecture is an area of current interest in artificial intelligence research. One sponsor of research in this area, the Air Force Wright Aeronautical Laboratories (AFWAL), requires a fast multiprocessor architecture to process an expert system capable of piloting a robotic air vehicle (RAV) (28:1326). The Strategic Defense Initiative Organization (SDIO) is another sponsor of faster expert system processing research. This research investigation is performed in support of the RAV expert system project and is a follow-on to the investigation by Captain Donald Shakley (37). Some of the areas recommended for future research in Shakley's thesis are pursued.

#### 1.1 System Requirement

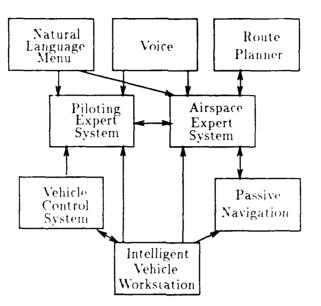

The concept of the RAV project is to create an unmanned air vehicle capable of autonomous operation (see Appendix A). To develop this robotic capability, AFWAL contracted Texas Instruments, Inc. to produce RAV software which, when executed, could perform all of the basic piloting skills as well as various navigation and obstacle avoidance functions (28:1326). AFWAL and TI jointly chose an expert system as the preferred RAV software implementation method for several reasons.

First and foremost, AFWAL uncovered through literature reviews that efforts to apply traditional software implementation methods to intelligent vehicle control had failed due in part to unmanageability of code (37:77). Second, researchers increasingly are discovering that applications that humans currently do better than machines (like the task of piloting an aircraft) lend themselves to solution using an artificial intelligence approach. Because expert system technology is currently one of the most successful branches of artificial intelligence, AFWAL and TI chose the expert system approach to the RAV software construction (18:4). Unfortunately, the RAV expert system has proven to be too compute-intensive to yield results in real-time on any serial or parallel computer architecture (hardware and software) developed to date. Real-time means "the time needed to make a calculation has to be less than the time from when the need for the calculation is recognized until the time when the response is needed to take action" (31:10). The RAV concept is not feasible until a computer architecture that produces real-time results processing the RAV expert system can be developed.

#### 1.2 Related Work

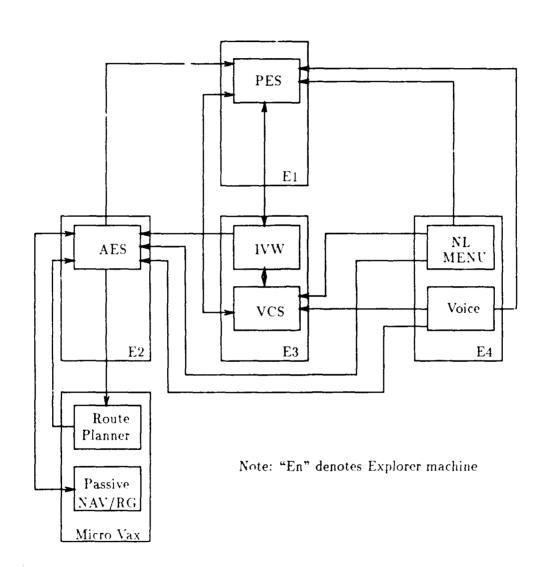

The only parallel architectures applied to the RAV expert system were developed by Shakley (37). These include parallel processing designs implemented on a network of Texas Instruments (TI) Explorer Lisp machines and on a first generation Intel Personal Supercomputer (iPSC). Although this study showed that the increased parallelism of the iPSC design could in fact produce processing speedup compared to the TI Explorer design, the amount of speedup tealized was hampered by the effects of interprocessor communication overhead and load imbalance. These effects were caused mainly by the simple data decomposition employed on the iPSC design (37:72). Furthermore, comparing the iPSC design to the TI Explorer design may have allowed factors unique to each of these products to skew the analysis. That is, the difference in the observed processing speeds of the two systems may have resulted from factors other than just the difference in the number of parallel processors applied.

#### 1.3 Problem Statement

The goal of this research investigation is the design, implementation, and analysis of a parallel processing architecture implemented on a second generation Intel Personal Supercomputer (iPSC/2) and the quantification of the processing speedup realized by this design as applied to the RAV expert system.

## 1.4 Research Objectives

The following are the objectives of this research:

- implement an efficient and effective parallel RAV expert system architecture on the iPSC/2 configured to use varying numbers of processors to gather data on the speedups realizable through parallelization

- quantify the performance results for this parallel RAV design through theoretical order-of timing analysis and through comparisons with past research results, with serial architecture results, with best-case theoretical analysis results, and with the real-time goal performance

## 1.5 Scope

The Intel Personal Supercomputer (iPSC/2) is the multicomputer employed in this research investigation (see Appendix B). This supercomputer, which can be configured with up to 128 available processors, is chosen due to availability as well as to research interest in the performance of artificial intelligence application software executing on a multicomputer. Limiting the analysis to designs implemented on this one supercomputer eliminates the possibility of machine-unique factors skewing the results, thus yielding more quantifiable comparisons of the performance differences between designs.

Software coding is done in the C Programming Language. C was chosen over the major AI programming languages, Lisp and PROLOG, to facilitate better efficiency and portability (27:190). C is also the only one of these languages available for use on the AFIT iPSC/2 at the time of this research investigation. Shakley's parallel RAV design, however, was implemented not in C but in Lisp on the iPSC. Shakley's design is not reimplemented in C as part of this research investigation, because the potential execution speedups attainable through reimplementation in C on the iPSC/2 are derived much more easily using theoretical analysis.

Because the RAV expert system is the application of interest, it is the only application to which research designs are applied for performance comparison purposes. Pertinent

RAV computation data is acquired from and assumed validated by AFWAL RAV project managers.

#### 1.6 Constraints

The decision to use the iPSC/2 to implement an RAV parallel expert system drives many program design decisions. Certain features of iPSC/2 hardware configuration, such as a local memory for each processor node, exclude many program design options. For example, algorithms that perform relatively few operations between synchronizations (i.e., have a small grain size) usually exhibit poor efficiency on multicomputers that employ multiple local memories as does the iPSC/2 (34:53). Consequently, small grain algorithms are excluded from consideration in this study. In fact, the iPSC/2's multicomputer design prevents this research investigation from taking advantage of extensive production system research performed to date using shared-memory multiprocessors (14:63).

The RAV expert system is the application of interest to this research investigation. Although the research methodology and design factors are applicable to any parallel architecture research, the performance results realized are unique to the RAV expert system. That is to say, even though the form of the RAV expert system is not unlike that of any other expert system program, the application of the architecture implemented in this investigation to other expert systems will not necessarily produce the same performance effects. This fact is significant when analyzing the expert system shell execution speeds observed for an application and when using these execution speed analysis metrics to quantify the merit of the expert system shell.

#### 1.7 Summary

This research investigation addresses improving the performance of production system software by executing this software on a parallel architecture. Such an architecture is applied to the Robotic Air Vehicle (RAV) expert system. The parallel expert system architecture is implemented on the iPSC/2 supercomputer using the C programming language. Realization and quantification of performance speedups using this parallel architecture are the objectives of this investigation. Chapter II provides background information on the key topics underlying this research effort, including expert systems and parallel processing. Chapter III describes the Rete match algorithm and issues regarding parallelization of Rete. Chapter IV details the fundamental approach to this research and introduces performance quantification using a performance spectrum. In Chapters V and VI, the lower and upper performance bounds of processing the RAV software are derived. Capt Shakley's parallel RAV design and its performance are related in Chapter VII. The parallel Rete expert system shell design and its application to the RAV expert system are presented in Chapter VIII. The many performance metrics produced in Chapters V through VIII are compared using the performance spectrum method in Chapter IX. Finally, the research conclusions and some recommendations stemming from research findings are offered in Chapter X. Appendices are available for those seeking deeper insight into the RAV project itself (Appendix A), parallel architectures (Appendix B), the theoretical and actual realizations of the parallel Rete expert system shell (Appendix C and Appendix D, respectively), and programmers' and users' manuals for the expert system shell (Appendix E and Appendix F, respectively).

#### II. Background

This chapter summarizes some of the underlying concepts, uncovered through literature search, that form the basis of this research, including production systems, expert systems, parallel processing, communication overhead, and load imbalance.

#### 2.1 Production System

A production system is a pattern recognition formalism based on string replacement rules. An order is imposed on these rules to decide which applicable rule to apply next. Production system computation proceeds as a string-resolution-based search. A control strategy is used with string-modifying production rules to model certain types of human problem-solving behavior (30:48).

The major elements of a production system are a global database of *facts*, a set of *production rules*, and a *control system*.

A fact is an assertion which represents a specific item of knowledge. A fact is generally of the following abstract form (14:8):

Written in this form, a fact is a parenthesized list consisting of a constant symbol, commonly called the *object*, and zero or more *attribute-value* pairs. An object represents an entity within a problem's domain that is of significance to the solution of that problem. An attribute represents a specific characteristic of its associated object. A value is the parameter instantiated for a given attribute (36:75).

The global database of facts, also called *working memory* (WM), is the central data structure used by a production system. Because facts are held in working memory, the facts are often referred to as working memory elements (WME). At the start of production system computation, WM contains a set of initial facts about the problem domain. As production system computation proceeds, facts are added and/or deleted from WM.

A production rule is expressed as strings that represent general knowledge about a particular subject area. A production rule generally appears in the form of an "IF condition THEN action" implication. By convention, the condition part of a rule is called the Left Hand Side (LHS) and the action part of a rule is called the Right Hand Side (RHS). The LHS is consists of one or more *condition elements* (CEs) that are compared to the actual state of referenced facts in WM at a given point in computation. The RHS consists of an unconditional sequence of *actions* which can add facts to and/or delete facts from WM. The following is a sample production rule (14:12):

(rule sample):

if ((object2 attribute1 15 attribute2 y) (object4 attribute1 y) ) then (add object3 attribute1 12))

This production rule, named "sample", consists of two condition elements in its LHS and one action, an add to WM, in its RHS. Note that this production rule form can be generalized in the following first-order predicate calculus form:

$$if = ((P_1(x_1, x_2)) + (P_2(x_3, x_4)))$$

)

then

$(P_3(x_1,x_3))$

In this example, both predicate  $P_1$  and predicate  $P_2$  must be *true* for predicate  $P_3$  to be *true*.

The production rules, known as the *production memory* (PM), are matched against the global database of facts. All rules in PM can match against and alter any facts in WM. The LHS of each rule in PM is either satisfied or is not satisfied by one or more facts in the global database in WM at any given discrete step in production system computation. If a rule's LHS is satisfied, that rule may be applied. Application, or *firing*, of a rule adds facts to and/or deletes facts from WM as dictated by that rule's RHS. For example, the production rule "sample" shown above is satisfied when there exists one or more facts in WM that meet all of the following conditions: i) the fact's object matches *object2*, ii) the fact's current value y for *attribute1* is "15" and iii) the fact's current value y for *attribute2* is the same as the current value y saved for *attribute1* in some other fact whose object matches *object4*. If all three of the above conditions exist in WM, the "sample" rule is then eligible to fire, adding a new fact with object *object3* and value "12" for *attribute1* to WM.

It is possible during production system computation that more than one rule's LHS is satisfied by the state of the facts in WM. The list of satisfied production rules in PM is commonly called the *conflict set*. The *control system* chooses which among all of the satisfied rules is to be applied. The choice of which rule to fire may be based on some firing priority assigned to each rule, on some characteristic of the rule string itself, or on some arbitrary ordering. The control system may employ an *irrevocable* control strategy or a *tentative* control strategy. In an irrevocable strategy, a satisfied rule is selected and applied without provision for reconsideration later. In a tentative strategy, a satisfied rule is selected and applied, but with provision made to return later to that point in the computation to apply some other satisfied rule instead. The control system halts computation when a predefined termination condition, or *goal* condition, exists in the current contents of WM (30:18).

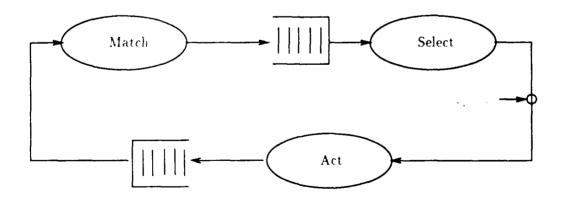

The basic production system algorithm is illustrated in Figure 2.1. This algorithm is executed as a Match-Select-Act cycle, usually in the following order (11:36):

- 1. Match evaluate the LHSs of the production rules to determine which are satisfied given the current contents of WM

- 2. Select choose one production rule with a satisfied LHS from the conflict set; if no production rules have satisfied LHSs, return control to the user

- 3. Act perform the actions specified in the RHS of the selected production rule

- 4. If a termination condition is detected, then return control to the user; otherwise go to Step 1 (Match)

#### Procedure PRODUCTION

1. DATA - initial fact database

2. until DATA satisnes the termination condition, do;

begin

select some rule R in the set of rules that can be applied to DATA

DATA  $\leftarrow$  result of applying R to DATA

3. end

Figure 2.1. Production System Algorithm (30:21)

#### 2.2 Expert System

One class of production systems is that of expert systems. Expert systems are formal computing systems, or programs, that use the production system paradigm to offer advice or solve problems by reasoning with bodies of knowledge highly specific to a particular domain (4:105). The bodies of knowledge are generally extracted from human experts in the domain. Using this knowledge base, the expert system attempts to emulate the experts' methodology and performance toward solving a problem (27:291).

Knowledge engineering is the interdisciplinary AI field concerned with the extraction of knowledge from domain experts and the transfer of this knowledge into hardware and software representation. After the knowledge engineer has developed the basic expert system, the acquired expertise is refined through a process of giving the system example problems to solve. Domain experts criticize the system's behavior and make any required changes or modifications to its knowledge. This process is repeated until the system has achieved the desired level of performance (27:16). Because the knowledge engineering task is difficult and expensive, expert systems typically emulate problem solving over a very limited domain.

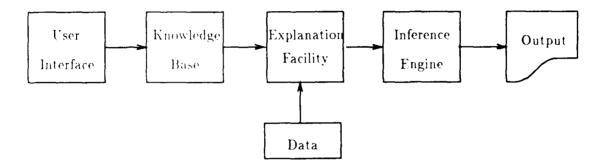

The principal components of a rule-based expert system are a knowledge base, an in-

ference engine, and a man-machine interface (see Figure 2.2). The knowledge base contains the global database of facts and the production rules that embody an expert's expertise. The inference engine is the control system that serves as a reasoning mechanism and search controller. It is the inference engine that performs the match-select-act cycle. These two expert system components represent the major elements present in any production system. The man-machine interface simply produces dialog (string, graphics, etc.) between the computer and the user (18:8-13).

Figure 2.2. Expert System Components (18)

## 2.3 Speedup and Parallel Processing

Compute-intensive applications, such as the RAV expert system (28), require processing beyond the performance ability of conventional, single-processor machines. Ishida and Stolfo suggest that although speed improvements in single-processor machines have occurred, "further speed improvements are required for very large [expert] systems with severe time constraints." (23:568) *Parallel processing*, which means applying several processors to run the solution algorithm for a single problem, is one approach to achieving such speed improvements.

The degree to which parallel processing improves processing speed depends upon the efficient use of available processors. Two main obstacles to achieving peak performance using parallel processing are *communication overhead* and *load imbalance* (37:72). One key

to overcoming both obstacles is the proper choice of a problem decomposition approach. A decomposition algorithm divides the overall expert system into independent subunits, or *tasks*, each of which is assigned to one of the available processors for execution.

### 2.4 Communication Overhead

Communication, or the passing of required information between processors, seriously degrades expert system performance because the overhead can become so intense that "the [processors] spend more of their time communicating than computing." (6:72) Obviously, chosing the most current technology parallel processor that performs interprocessor communication as fast as possible is one way of reducing communication time. An algorithmic approach to reducing the detrimental effects of communication overhead is to decompose and distribute the expert system tasks in such a way that the interprocessor communication time incurred by parallelizing the expert system is less than the computation time saved through parallelization of the expert system. The benefits of a "good" expert system decomposition are realized regardless of the particular parallel processor's communication speed. But an extremely fast interprocessor communication capability cannot be expected to always overcome the effects of a poor decomposition.

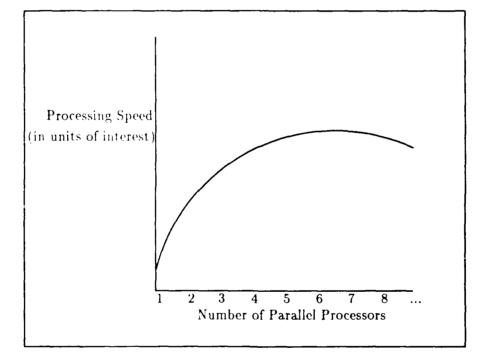

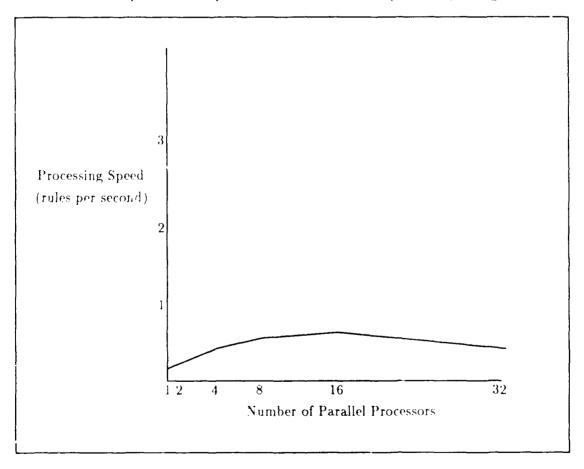

The number of processors over which an expert system's tasks are decomposed also affects communication overhead. A phenomenon called the *Amdahl effect* dictates that any parallel algorithm shows constrained speedup if there is not enough work to be done by the number of processors available (34:60). The Amdahl effect suggests there exists an optimal number of processors upon which a parallel program can be run. Applying more than this optimal number of processors adds communication overhead that overcomes some of the computation time savings of parallelizing the system. Figure 2.3 shows how processing can slow down when more than the optimal number of processors are applied to a problem. Proponents of parallel processing hasten to point out that Amdahl's effect occurs under the assumption that some number of necessarily sequential operations exist to interrupt the parallel execution of an algorithm. Hence, Amdahl's argument serves as a way of determining whether an algorithm is a good candidate for parallelization, rather than as a provable limit to speedup for all algorithms (34:19).

Figure 2.3. Example Parallel Speedup Chart

#### 2.5 Load Imbalance

An imbalance of the task load among the processors also severely degrades performance. The goal is to ensure that "the tasks being executed [are] uniformly distributed amongst the various processing nodes in a manner which maximizes resource utilization to enhance the total throughput of the system." (2:189) Achieving load balance, like achieving low communication overhead, also depends on choosing a good problem decomposition. A good decomposition algorithm maps the expert system tasks to the available processors in such a way as to keep as many of the processors busy doing useful work as possible.

There are two general task allocation policies: *static* decomposition and *dynamic* decomposition. Static decomposition assumes that tasks and their precedence relations are known before execution. Dynamic decomposition assumes that tasks are generated during program execution. The advantage of static decomposition is that it allows the preallocation of tasks to processors, thus reducing the amount of interprocessor communication. The advantage of dynamic decomposition is that it makes it easier to keep all the processors busy because tasks requiring processing are assigned to the first available processor (34:62). But dynamic decomposition adds communication overhead to distribute tasks to available processors.

#### 2.6 Summary

A production system consists of a global database of facts and a set of production rules (constituting the knowledge base), and a control system (inference engine). The basic production system execution algorithm is the Match-Select-Act cycle. The rule LHSs are matched against the current facts in the knowledge database, one of the satisfied rules is selected for firing, and the RHS actions of the selected rule are performed to update the fact database. An expert system applies the production system paradigm to problem solving using knowledge that is specific to a particular domain. Parallel processing, which means applying several processors to the solution of a single problem, is employed to speed up processing of a wide range of applications, including expert systems. Two main obstacles to realizing speedup through parallelization are communication overhead and load imbalance.

#### III. Production System Performance Improvement Concepts

This chapter offers some production system parallelism concepts and introduces the serial Rete match algorithm. The parallelization of the Rete algorithm lays the groundwork for a new distributed processor parallel RAV expert system design.

#### 3.1 Potential Production System Parallelism

As discussed in Chapter II, the three steps that are repeatedly performed to execute a production system algorithm are *match*, *select*, and *act*. Figure 3.1 illustrates the information flow among these three steps. Note that a synchronization point exists after the select step and before the subsequent act step. This synchronization point has a serializing effect on the match-select-act cycle. The select step must finish completely before the next production rule to fire can be determined and its RHS evaluated. Without this synchronization, a potential race condition exists in which the WM change inputs to a match-select-act cycle may be corrupted by outputs of that same cycle. No other mandatory synchronization points exist in the cycle.

Figure 3.1. Match-Select-Act Flow Graph (14:46)

This feature of production systems suggests areas of potential parallelism. For example, it is possible to use parallelism within the match step, within the select step, and within the act step. It is further possible to overlap the processing performed within the match step and the select step of the same cycle and the processing performed within the act step of one cycle and the match step of the next cycle (14:45). These potential interstep overlaps are represented by the queue symbols in Figure 3.1. But as noted above, it is not possible to overlap the processing within the select step of one cycle and the subsequent act step.

#### 3.2 Rete Match Algorithm

All of the information presented in this section is taken from (15) except items noted from other sources.

The most time consuming step in the execution of production systems is the *match*. Matching is a pattern recognition activity which involves matching the left hand sides (LHSs) of all productions against all facts in working memory (WM). Even with specialized algorithms, the match step constitutes around 90% of the interpretation time (13:4). Consequently, speeding up the match step in production systems is an area of intense research.

The Rete (pronounced "reet") algorithm is among the most efficient algorithms for match yet developed. To achieve this efficiency, Rete exploits two features common to most production systems: first, only a small fraction of working memory typically changes every match-select-act cycle: and, second, similar condition elements often appear repeatedly among the productions in production systems. Rete exploits the first feature by storing results of match from previous cycles and using them in subsequent cycles. Rete exploits the second feature by recognizing condition elements referenced in multiple productions and performing common tests only once (13:4).

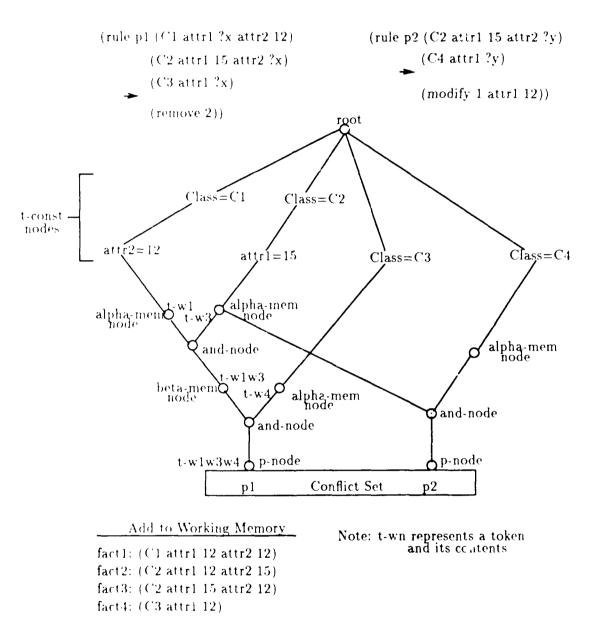

The Rete algorithm uses an augmented discrimination network compiled from the LHSs of the productions to perform the match. In fact, the name "Rete" comes from the latin word for "network." (29) Figure 3.2 shows such a network for productions p1 and p2 which appear in the top part of the figure. In this figure, lines have been drawn between nodes to indicate the paths along which information flows. Information flows from the top node down along these paths.

Figure 3.2. Sample Rete Graph (14:12)

To generate the network for a particular expert system application, the production rules are parsed and "translated" by a *network compiler*. Note that the Rete network compiler is not a compiler in the conventional sense of computing. The Rete compiler builds a network which serves as the data structure acted upon by the inference engine during execution of the expert system.

The network compiler proceeds first with the individual condition elements in the rules' LHSs. For each condition element, the compiler chains together test nodes that check the following:

- if the attributes in the condition element that have a constant as their value are satisfied

- if the attributes in the condition element that are related to a constant by a predicate are satisfied

- if two occurrences of the same variable within the condition element are consistently bound (i.e. working memory elements with the same value for the specified attribute exist)

Each node in the chain performs one such test. These three tests are called *intra*condition tests because they correspond to individual condition elements. In Figure 3.2, the nodes with a single predecessor (near the top of the network) are the ones that are concerned with individual condition elements.

Once the network compiler has finished with the individual condition elements, it adds nodes that check for consistency of variable bindings across the multiple condition elements in the LHS. These tests are called *inter-condition* tests because they refer to multiple condition elements. The nodes with two predecessors are the ones that check for consistency of variable bindings between condition elements.

Finally, the compiler adds a special terminal node to represent the successful matching of the production to which this part of the network corresponds. The terminal nodes are at the bottom of the figure. Note that when two LHSs require identical nodes, the compiler builds a shared set of nodes in the network rather than duplicate nodes. This feature of Rete ensures that the same test is not performed repeatedly for multiple rules within a single match step.

To avoid performing all of the same tests completed during the previous match step, the Rete algorithm stores the result of a match with working memory as *state* within the network. Only changes made to the working memory by the most recent production firing have to be processed every match-select-act cycle. That is, the input to the Rete network consists of the most recent changes to the working memory. These changes filter through the network and, where relevant, the state stored in the network is updated. Due to the Rete algorithm's state-saving feature, the amount of effort expended by the matcher depends primarily on the rate of change of working memory rather than the absolute size of working memory (11:37). The output of the network consists of a specification of changes to the list of rules eligible to be fired. This list of rules is called the *conflict sct* because only one of these rules may be allowed to fire under the production system paradigm. Consequently, the rules can be said to be in conflict over the right to be fired in the current cycle.

The objects that are passed between nodes in the network are called *tokens*, which consist of a tag and a list of working memory elements. The tag can be either a +, indicating that an element has been *added* to the working memory, or a -, indicating that an element has been *deleted* from working memory. No special tag for working memory element modification is needed because a *modify* is treated as a delete followed by an add. The list of working memory elements associated with a token corresponds to the permutation of those elements that the system is trying to match or has already matched against a subsequence of condition elements in the LHS.

The discrimination network produced by the Rete network compiler consists of a number of the following types of nodes:

Root Node: This node forms the root of the discrimination net. It broadcasts tokens corresponding to any change in the working memory to all its successor nodes. In Figure 3.2, the root node is shown at the top.

3-5

- Constant Test (t-const) Nodes: These nodes are used in the network to perform intra-condition tests, for example, to check if condition attributes that have constant symbols or numbers as their values are satisfied. Each t-const node checks for one feature. Whenever the token arriving at the input of a t-const node satisfies the associated test, it is passed on to the successors of the t-const node. If the token does not satisfy the test, it is not passed on to the successors. In Figure 3.2, the nodes towards the top of the network are t-const nodes. Because the second condition element of production p1 is similar to the first condition element of production p2, t-const nodes "Class=C2" and "attr1=15" are shared in the network for rules p1 and p2.

- Alpha Memory (alpha-mem) Nodes: If a working memory element satisfies all intracondition tests for a condition element, the working memory element is said to partially match the condition element. Note that it may not, as yet, satisfy all the inter-condition tests. Tokens corresponding to working memory elements that partially match a condition element are stored in the alpha-mem node for that condition element. When a token arrives at an alpha-mem node with a + tag, the token is stored in the alpha-mem node and a copy of the token is passed to the node's successors. If the tag is -, a corresponding token with a + tag must already exist in the alpha-mem. The corresponding + token is deleted from the alpha-mem node and the incoming token is passed down to the successors of the alpha-mem node. If two condition elements in the same or different productions have exactly the same tests for a successful partial match, the network compiler generates a shared alpha-mem node for the two. This sharing of an alpha-mem node can be seen in Figure 3.2.

- Beta Memory (beta-mem) Nodes: Just as alpha-mem nodes store tokens that partially match individual condition elements, so beta-mem nodes store tokens that partially match two or more condition elements in the LHS of a production. The list of working memory elements in beta-mem tokens has length two or more. The response of beta-mem nodes to the arrival of tokens at their inputs is exactly the same as that of alpha-mem nodes. The beta-mem nodes form the left input of and-nodes and not-nodes.

- And-Nodes: The and-nodes are the first of the two-input node types. The primary function of an and-node is to check for consistency of variable bindings between the partially matched tokens it receives on its left and right inputs. The right input of an and-node always comes from an alpha-mem node, while its left input can come from an alpha-mem or a beta-mem node. Whenever a token arrives at the left input of an and-node, the and-node compares the incoming token to each token stored in the mem-node connected to its right input to check if they are consistent. For every right-token which is consistent with the left-token, a new token is constructed and sent down to the successor nodes. The new token has the same tag as that of the left-token, and the list of working memory elements is the concatenation of the working memory element lists for the left and right tokens. The case when a token arrives at the right input of an and-node is processed exactly as above, with left and right interchanged.

- Not-Nodes. The not-nodes are the second of the two-input node types. They also have a left and a right input. The not-nodes are used by the network to implement negated condition elements. Their functionality differs from that of and-nodes only in minor ways. One difference is that not-nodes keep reference counts with tokens in left memory to find when there are no tokens in the right memory that are consistent with them.

- Production Nodes (p-nodes): These are the terminal nodes in the network. There is one such node associated with each production. Whenever a token with a + tag flows into a p-node, it adds an instantiation (corresponding to the token) of the associated production into the confict set. The arrival of a token with a - tag leads to the deletion of the corresponding production instantiation from the conflict set.

- Other Nodes: Other than the node types mentioned above, the network uses two more node types. These are the Two-Nodes and the Any-Nodes. The two-node is used as a place filler in some circumstances, and the any-node is used when the value of an attribute is to be one of a number of alternatives.

The match step in a Rete network interpreter can itself be divided into two parts: the

selection phase, which consists of evaluating the t-const nodes; and the state-update phase, which consists of evaluating the alpha-mem nodes, beta-mem nodes, and-nodes, not-nodes, and p-nodes. Comparing these two phases, about 75% to 95% of the total processing time is spent performing the state-update phase (14:47).

#### 3.3 Parallelizing Rete

The Rete match algorithm is suitable for parallel implementations. The data-flow like organization of the Rete network makes it possible to evaluate the activations of different nodes in the network in parallel. It is also possible to evaluate multiple activations of the same node in parallel and to process multiple changes to working memory in parallel (14:20). Of the many sources of production system parallelism, the following three are particularly important in the parallelization of Rete and, specifically, of the state-update phase of the Rete match step: production parallelism, node parallelism, and action parallelism.

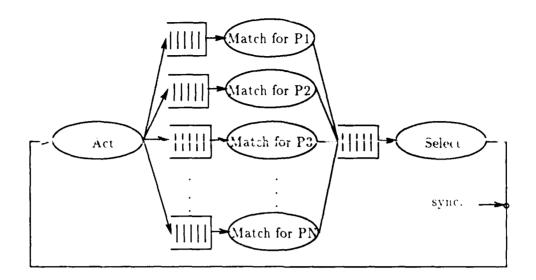

Production parallelism is accomplished by dividing the productions in a program into several partitions and performing the match for each of the partitions in parallel. Figure 3.3 illustrates the partitioning of productions of an expert system. Production partitioning is a static task decomposition approach. Consequently, the main advantage of using production parallelism is that no communication is required between the processes performing match for different productions or different partitions. That is, it is largegrain parallelism. Disadvantages of production parallelism are that it is limited by 1) the typically small number of productions affected per change to working memory, 2) the large variance in the amount of processing required by the affected productions, and 3) the loss of sharing in the overall Rete network as a result of production partitioning (14:48-49).

Node parallelism, which is unique to the Rete algorithm, means that activations of different two-input nodes in the Rete network are evaluated in parallel. An advantage of node parallelism is that both activations of two-input nodes belonging to different productions (corresponding to production parallism) and activations of two-input nodes belonging to the same production (resulting in extra parallelism) are processed in parallel. Node parallelism is implemented at a finer granularity than production parallelism to 1) reduce the effect of large variance in the amount of affected productions processing, and 2) to recover

Figure 3.3. Production Parallelism (17:48)

some of the sharing lost in the overall Rete network when using production parallelism. This fine granularity, however, leads to increased communication requirements between processes evaluating the nodes in parallel (14:51).

Action parallelism refers to the concurrent processing of changes made to working memory when a production fires. Action parallelism enhances the speedup obtainable using production, node, and other forms of parallelism (14:54).

A significant amount of research has been performed toward implementing parallel Rete on multiprocessors (14, 25). Fine-grain node parallelism, enhanced with action parallelism wherever possible, is the preferred implementation method when using a multiprocessor architecture. This method is attractive because multiprocessors have the advantage of shared memories (see Appendix B), which offsets much of the cost of increased communication associated with node parallelism (14:58).

In a typical multiprocessor design, a single copy of the Rete network is held in shared memory. The match is broken into fairly small units of work called *tasks*, where a task is an independently schedulable unit of work that may be executed in parallel with other tasks (17:103). Each task is represented by a token. This token is essentially the same as that described for the sequential Rete matcher, except that it has two extra items of information: the *address* of the node to which the token is to be sent; and, if that node is a two-input node, an indication of whether to send it to the *left* or *right* input. The list of tokens that are awaiting processing is held in a central data structure called a *task* queue. When a processor in the multiprocessor becomes available, it removes a token from the task queue. If, during processing of a token, new tokens are to be sent out, these are entered into the task queue for subsequent processing. See (17) for details of a highly successful parallel production system implementation employing Rete on a shared-memory multiprocessor.

Unlike the parallel Rete research performed on multiprocessors, implementation of a parallel Rete matcher on a multicomputer architecture remains relatively unexplored for two basic reasons. First, the most natural approach to implementing production systems on a multicomputer is production parallelism, enhanced with action parallelism. But preliminary simulation analysis of parallel processing using only production parallelism and action parallelism indicates that the speedups attainable are very low (32:92). Second, the node parallelism approach was shown theoretically and through simulation to be superior to production parallelism. But the fine granularity of node parallelism adds communications costs that may restrict the class of suitable architectures to shared-memory multiprocessors (14:58).

Limited theoretical analysis of a parallel architecture which implements Rete in an object-oriented manner on a multicomputer has been performed (16). This research draws heavily from work performed on multiprocessor designs. At the time of this research investigation, the only parallel multicomputer implementation of a production system interpreter that employs Rete is II CLIPS, developed for the FLEX/32 (MIMD) multicomputer (35).

#### 3.4 Summary

Production systems lend themselves to parallel execution. The only mandatory synchronization point in the match-select-act cycle exists after the select step and before the subsequent act step. Speeding up processing of the match step is critical, as it typically constitutes around 90% of the production cycle time. The Rete match algorithm speeds match time in two ways: first, Rete saves WM search time by saving state between cycles, a feature that takes advantage of the small fraction of WM typically changed per cycle; second, Rete recognizes condition element references common to multiple rules and executes common tests only once. The data-flow like organization of the Rete network makes it suitable for parallel implementations to take particular advantage of production parallelism, node parallelism, and act parallelism during execution. Parallel multicomputer implementation of a production system interpreter that employs Rete is an area of research still in its infancy.

# IV. Research Methodology

This chapter presents and justifies the research methodology applied to parallelization of the RAV expert system during this research investigation. The following are the restated and expanded goals of this research:

- Present the fastest processing of the RAV expert system achieved to-date using the current state-of-the-art parallel design and determine this design's expected performance if implemented on the iPSC/2.

- Design and implement a new parallel design on the iPSC/2 using a more efficient and effective match-select-act algorithm (Rete) to achieve speedup over the current state-of-the-art design.

- Ensure valid performance comparisons between these parallel designs by considering implementations of the designs that use the same tools (e.g. hardware, language) and the same input data wherever possible.

- Determine the relative usefulness of these parallel designs by showing their relation to the expected lower and upper bounds of parallel processing performance and to the desired "real-time" performance of the RAV expert system.

### 4.1 Justification of Method Selected

It is common practice in parallel computer architecture research to compare the performance of one's *new design* with that of the current *state-of-the-art* design applied to the same problem. Speed and correctness of processing are the key performance criteria analyzed. The comparison of designs is necessary to show the advancement of knowledge in the field of application. But this approach by itself offers only a very limited analysis of the merit of the new design for two main reasons.

First, the new parallel design is often configured to run on a different machine than that used by the previous parallel design. Consequently, the performance speedups attributable to the different hardware are not distinguishable from the speedups attributable solely to the new program design. It is imperative that architectures being compared use identical, or at least very similar, hardware to isolate the performance differences attributable to program design.

Second, the true merit of the current state-of-the-art parallel design is often a mystery. This is especially true when current research into a particular area of application is relatively immature. In this case, it is not enough that a new parallel design outperforms the previous "best" design, because both designs' performances may still fall far short of the theoretical performance potential for such an application.

## 4.2 Performance Spectrum

To determine the true merit of a parallel design for a particular application, one must determine where on a *performance spectrum* this parallel design lies in terms of processing speed. The processing speed is defined in terms that are significant to the particular application (e.g., for expert systems, the performance metric of interest is typically the average number of rules fired per second). Two logical and essential metrics on the performance spectrum are a good serial design's processing speed and the required, or goal, processing speed.

Performance data on a serial, or single-processor, design for an application is often available to the researcher. In fact, it is sometimes the failure of a serial approach to solve a problem in what the user defines as "real-time" that leads to attempts at parallel solutions. Although the "goodness" of a particular serial design is difficult to quantify, still the performance of some serial design is useful to quantify the performance payback realized by parallelizing a solution in the new design. The serial design's performance serves as the *lower bound* on the performance spectrum.

The other key metric on the performance spectrum is the *goal* processing speed. The maturity level of computer architecture research with respect to a particular application can only be determined by comparing the performance of a new design with the goal performance. For example, the "real-time" performance requirement is the goal driving most research in parallel processing of expert systems. The real-time metric defines the speed at which computational results must be produced for the particular application to

be successful.

An additional metric on the performance spectrum is needed to show if it is reasonable for the researcher to expect to meet the performance goal within the limitations of research assumptions. For example, although processing speed comparisons among a serial design, a state-of-the-art design, and a new design may all show progress toward the goal processing speed, the hardware of choice may not be physically capable of ever actually achieving the goal performance. Consequently, there exists a research need for an *upper bound* performance metric under given application and architecture constraints. Of course, because the upper bound is not readily attainable like the other performance spectrum metrics, theoretical and/or simulation methods must be applied.

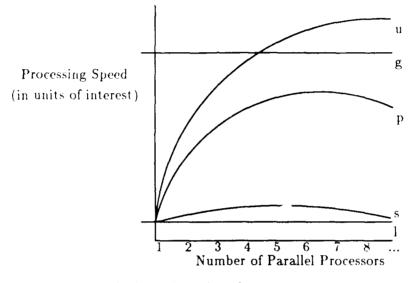

Figure 4.1 is an example performance spectrum chart illustrating the above metrics and their interaction for a fictional application. Note that interpretation of this figure suggests the following:

- The performance of the serial design applied to this problem falls far short of the goal performance. This poor serial design performance leads the researcher to consider the possibility of attempting a parallel solution.

- 2. The upper bound performance metric suggests that the architectural approach being taken, under ideal parallel conditions, has the potential to achieve the goal performance. The upper bound performance findings encourage continued research on the current architecture.

- 3. The state-of-the-art design realizes only limited performance improvement over the serial design. This limited performance improvement suggests to the researcher that perhaps a whole new design approach, rather than enhancements to the previous design, should be pursued.

- 4. The new design performance produces significant speedup over the serial design and approaches the goal performance, lending merit to the research contribution of this new design.

)

Legend: 1 - lower bound performance metric

- s current state-of-the-art parallel performance

- p proposed parallel architecture performance

- g goal performance

- u upper bound on proposed architecture performance

Figure 4.1. Example Performance Spectrum Chart

#### 4.3 Research Investigation Steps

**Based on** the methodology detailed above, this research is comprised of the following steps:

- Step 1: Determine the *lower bound* performance expected in processing the RAV expert system. To do this, a "good" serial design is implemented on the iPSC/2 configured to use only one of its processors. The performance metric observed during the processing of the RAV expert system on a single processor is recorded as the lower bound (worst case) performance metric. This metric is needed to determine the speedup achieved by any of the parallel designs (e.g. Speedup = Time for Parallel Processors to Compute Result / Time for Single Processor to Compute Result).

- Step 2: Determine the upper bound performance expected in parallel processing of the RAV expert system. The upper bound is needed to estimate the maximum speedup achievable under a given parallel design. The theoretical maximum speedup of N (where N is the number of parallel processors) requires the very unlikely pairing of perfect load balance and no communication among processors. A more realistic estimate of the minimal communication and optimal load balance achievable is developed theoretically. Lamanna's hypercube model is adjusted to describe the performance of the RAV expert system over several iPSC/2 configurations of differing numbers of parallel processors (26:4).

- Step 3: Analyze theoretically the expected performance of the current state-of-the-art parallel architecture as implemented on the iPSC/2. This analysis entails considering the likely effects on the Shakley design's performance due to any upgrades added to date to the iPSC/2 as compared to the iPSC/1. Analysis results for the Shakley design over several configurations of differing numbers of parallel processors are recorded.

- Step 4: Design, implement, and analyze the performance speedup (if any) of a *new parallel architecture* on the iPSC/2 using a better match-select-act algorithm and an appropriate decomposition algorithm. This design is exercised over several iPSC/2

configurations employing different numbers of parallel processors and the performance metrics are recorded.

## 4.4 Statistical Procedures

All RAV expert system designs operate on the same data sets. The designs are validated by direct inspection of the results and of performance metrics compiled during expert system processing.

The expert system performance metric of particular interest is processing speed attained, defined in terms of the average number of rules fired per second. Timing data are also collected on the average time spent in each of the match, select, and act steps during processing.

#### 4.5 Summary

The research methodology applied in this investigation stresses not only the development of a new parallel architecture for the RAV expert system but also the quantification of this design's contribution to RAV expert system research. The following is a summary of the RAV expert system research investigation steps:

- Step 1: Determine the lower bound performance metric realized by a good serial RAV expert system design.

- Step 2: Determine theoretically the upper bound performance metrics achievable by a parallel design implemented on the chosen architecture.

- Step 3: Determine theoretically the current state-of-the-art parallel design's performance metrics realized when running on the chosen architecture.

- Step 4: Determine the actual performance metrics realized by a new parallel design implemented on the chosen architecture.

- Step 5: Compare these performance metrics to the real-time performance requirement.

)

## V. Step 1: Lower Bound Performance

### 5.1 System Design

To define the processing speedup attributable to parallel processing of a program, one must first establish the processing speed of a "good" serial design as a base of comparison (e.g. Speedup = Parallel Processing Time / Serial Processing Time). For this research, the processing speed of a "good" serial design is needed to delineate a *lower bound* of performance expected in processing the RAV expert system. Furthermore, the serial design must be implemented on hardware similar to the hardware upon which subsequent parallel designs are implemented if comparison of their processing speeds is to be valid.

The proposed serial design employs an existing serial expert system interpreter, or *shell*, which uses the Rete algorithm when performing the match-select-act cycle on any input set of rules and initial facts. The design decision to use an existing shell to support the RAV expert system allows this research investigation to take full advantage of the Rete algorithm optimization efforts afforded during the implementation of the expert system shell. Expert system shells considered as alternatives for this implementation include Inference Corporation's Automated Reasoning Tool (ART) (1). Carnegie-Mellon University's OPS5 and paraOPS5 (9), and NASA's C-Language Integrated Production System (CLIPS) (5).

The original RAV expert system was developed using ART (see Appendix A), making this expert system shell a good candidate from an RAV knowledge-base portability perspective. But ART is not an attractive alternative for this design effort for several reasons. ART is currently available only in Lisp-based and Bliss-based versions. A Cbased interpreter is desired for this investigation, rather than a shell based in a symbolic language, for both program efficiency and program portability reasons (26:190). Also, the cost of acquiring new versions of ART for the purpose of this research proved prohibitive.

Carnegie-Mellon's OPS5 expert system shell series was developed and optimized by the originators of the Rete algorithm (10). But, again, the early versions of OPS5 are Lisp-based. A later parallel version, called paraOPS5, can execute in serial mode and is C-based at a macro-level. But paraOPS5 is only partially C-coded, with the Rete network embedded directly in the National Semiconductor NS32032 machine code for realization of more speedup (17:96). Neither of these existing designs lend themselves to convenient rehosting into a serial, fully C-based OPS5 to execute on the iPSC/2's Intel 80386 chip.

NASA's C-Language Integrated Production System (CLIPS) interpreter is chosen as the expert system shell for this research investigation (33:743). As the shell's name suggests, the serial CLIPS is written in C specifically for the purposes of efficiency and portability (3:71). Of course, to exercise the RAV expert system using the CLIPS interpreter, the RAV knowledge base (rules and facts) is transliterated from its original Automated Reasoning Tool (ART) syntax to CLIPS syntax with no loss of functionality.

### 5.2 Detailed Design

A full CLIPS interpreter executes on the host processor of the iPSC/2. The source code of the CLIPS program, written in the C-Programming Language, is compiled without modification using the Greenhill C compiler under the UNIX/System V operating system. At system initialization, the processor is loaded with all of the production rules in the RAV knowledge base from which to build a Rete network. Then the initial facts are asserted in working memory, after which the RAV expert system is ready to execute. When production system execution is complete, performance data are collected and displayed by CLIPS (e.g. rules fired, execution time). The high-level algorithm employed by the serial design is illustrated in Figure 5.1.

Note that this algorithm is the same as the match-select-act cycle algorithm described in Chapter II. Of course, no interprocessor communication is required because the iPSC/2 is configured as an SISD computer (see Appendix B).

#### 5.3 Implementation

Because the expert system portions of the RAV constitute the scope of this study, only the Piloting Expert System (PES) and Vehicle Control Expert System (VCES) are executed under CLIPS (see Appendix A). That is, the conventionally programmed subsystems of the prototype RAV design, such as the Route Planner and the Intelligent Vehicle Procedure RETE:

1. do while (termination state not detected);

2. match - update the Rete network with WME

change applied during the last cycle

3. select - select a production from conflict set

4. act - apply WME change specified by selected production's RHS

5. end do;

### Figure 5.1. RAV Serial Rete Design

Workstation, are not present to provide inputs to the PES and VCES. Consequently, the RHSs of key rules are altered to artificially introduce the values normally produced by one or more of the missing conventional subsystems. In this way, the RAV rules are kept firing to simulate progression through a reasonable air mission. The benchmark air mission consists of the execution of the entire RAV takeoff sequence of rules, the initiation of all possible RAV air maneuver rule sequences in the knowledge base, and completion of the entire RAV landing sequence of rules.

The initial facts are asserted into working memory by the firing of a startup rule. The startup rule has no conditions in its LHS, meaning it satisfied regardless of the state of WM. The RHS of the startup rule consists of a set of fact assertions that, when the rule is fired, load all of the facts required to activate the desired set of initial RAV rules. The subsequent RAV rule firings simulate the guidance of an aircraft through the entire takeoff sequence, a series of air maneuvers, and the entire landing sequence. It is for these subsequent rule firings that timing data are collected. For this study's benchmark RAV execution, a total of 73 RAV rules are fired in approximately 3.5 seconds by the CLIPS interpreter for an average of 20.9 rules per second. The entire RAV rule set consists of 273 rules. Therefore, the 73 rule firings observed, representing nearly 27% of the RAV rule base, is considered a valid number to show performance difference among designs.

# 5.4 Summary

NASA's serial C-Language Integrated Production System (CLIPS) shell is used to execute the RAV expert system. The original ART-syntax RAV knowledge base is transliterated into CLIPS-syntax and is adapted to run without external input to allow execution of the RAV using CLIPS. A full CLIPS interpretter executes on the host processor of the iPSC/2 under the UNIX/System V operating system. Using this serial design, an average RAV processing rate of 20.9 rules fired per second is observed. This processing rate serves as the lower bound performance for execution of the RAV expert system.

### VI. Step 2: Upper Bound Performance

# 6.1 System Design

A critical metric in any parallel architecture design is the estimate of the maximum speedup achievable. The theoretical maximum speedup of N (where N is the number of parallel processors) assumes the unlikely pairing of perfect load balance and no communication overhead. A more realistic estimate of the minimal communication overhead and near optimal load balance achievable within a given design must be developed theoretically and/or through simulation.

As Lamanna points out in her Performance Study of the Hypercube Architecture, evaluating the performance of an architecture cannot be divorced from the algorithm used (25:10). Consequently, the theoretical upper bound performance metric in this research investigation represents the maximum potential RAV expert system processing speedup realizable using the parallel expert system algorithm proposed under ideal communication and load balance conditions. The units of speedup of interest regarding the RAV expert system are the number of rules fired per second.

### 6.2 Detailed Design

The upper bound performance analysis presented here follows closely the timing analysis detailed in Appendix C.

Certain assumptions are made at the onset of this analysis to present an ideal computing environment for the RAV expert system executing on the proposed parallel expert system shell which employs mainly production parallelism. First, the optimal load balance is defined as an even distribution of the workload experienced by the serial algorithm amongst the parallel processors available to the parallel program. No computational overhead is introduced through parallelization. Second, the only activity other than computation on a processor that produces a time cost is interprocessor communication. No system interface overhead, such as input or output (I/O), is allowed to degrade optimal performance. From Appendix C, the time required to complete one match-select-act cycle under the proposed parallel design is defined as follows:

(Equation 6.0)

$O([max_{PE}([sum^{PE'sCEs} (match filter time)] + local select time)] +$ select compare/exchange time + act broadcast time + local act time )

This equation states that the cycle time consists of 1) the maximum time spent by one of the processors updating its local Rete network and selecting a candidate rule to fire from its local conflict set, plus 2) the time for the processors to determine, through a gray-code compare/exchange, which processor has the best candidate rule to fire , plus 3) the time to broadcast the actions specified in the RHS of the rule to fire. Under the ideal condition assumptions described above, the time spent by each processor to update its Rete network, select from its conflict set, and fire the best rule's RHS actions is uniform across all processors (e.g. perfect load balance). Furthermore, the sum of the times spent processing these uniform task loads equals the total time spent processing the entire workload serially. Thus Equation 6.0 simplifies to the following, with N being the number of available processors:

(Equation 6.1)

O(( total serial processing time / N ) + select compare/exchange time + act broadcast time )

#### 6.3 Implementation

The task of determining the upper bound performance for the parallel design proposed in this investigation now becomes that of acquiring actual and/or expected times for the total RAV expert system serial processing time, the average select compare/exchange time, and the typical act broadcast time experienced on the iPSC/2 hardware. Substituting these time values into the equation presented in the previous section yields the upper bound of expected performance in terms of the total processing time required to complete one match-select-act cycle.

The total serial processing time, determined empirically using the serial CLIPS design described in Chapter V, is 3.5 seconds to fire 73 rules. The select compare/exchange time and act broadcast time each depend on the data rate of the interprocessor communication lines on the iPSC/2 and on the size of the data structure sent as a message. Because the minimum message data structures for both types of messages were known prior to actual parallel design implementation, the processing times for these activities are also determined empirically on the iPSC/2 hardware.

The data structure passed during a gray-code compare/exchange consists, as a minimum, of the integer ID of the processor passing the message and an integer value representing the firing priority, or *salience*, of its candidate rule. A total of d communications of such a structure (where d is the dimension of the hypercube) is required to ensure the structure representing the best rule-to-fire candidate is at the base processor, say node 0. The last communication required in the select step is the broadcast of the best rule-to-fire structure from the base node 0 to the other processors. The further assumption is made that a broadcast requires the same amount of time as does a node-to-node communication. A total of d+1 communications during the select step add cost to the total program execution time.

The data structure broadcasted during the act represents the RHS actions of the rule selected for firing. These RHS actions can consist of any number of fact assertions, fact retractions, and interface actions (such as I/O). Again, to produce ideal computing conditions for optimal processing speed, only fact assertions and fact retractions are considered in this analysis. Another simplification is that all of a selected rule's RHS actions are passed in a single data structure large enough to contain the average number of assertions and retractions specified by a typical rule in the RAV rule set. The assertions are assumed sent in the form of a typical RAV fact string and the retractions are assumed sent in the form of a typical RAV to be retracted.

Inspection of the RAV knowledge base suggests that the average rule's RHS specifies approximately two fact assertions (1.46 average observed) and about two fact retractions (1.18 average observed). The typical length of a fact string to be asserted is approximately 231 characters, which represents a message size of 231 bytes for each asserted string. Integer IDs of facts to be retracted add 8 bytes each to the message size. Under the above assumptions, the typical single message broadcasted during the act step is about 470 bytes long.

The communication times required for passing of select step and act step messages on the iPSC/2 are determined empirically using a simple ring communication program that sends messages of the specified size around the nodes of the hypercube, configured as a ring. Timing data are collected as message passing proceeds. Each select message communication can be completed in 0.00424 seconds. The single act message can be broadcasted in 0.00776 seconds.

Summing the times derived above, the upper limit on the time required for the proposed parallel design to process the 73 rules fired in the RAV benchmark follows Equation 6.1: