# Aircraft Reply and Interference Environment Simulator (ARIES) Hardware Principles of Operation: Volume I

Edward Mancus

092

AD-A214

$\sim$

October 1989

DOT/FAA/CT-TN88/4-I

Document is on file at the Technical Center Library, Atlantic City International Airport, N.J. 08405

DISTRIBUTION STATEMENT A Approved for public released Distribution Unit in rad

U.S. Department of Transportation Federal Aviation Administration

Technical Center Atlantic City International Airport, N.J. 08405

89 11 01 037

# NOTICE

This document is disseminated under the sponsorship of the U.S. Department of Transportation in the interest of information exchange. The United States Government assumes no liability for the contents or use thereof.

The United States Government does not endorse products or manufacturers. Trade or manufacturers' names appear herein solely because they are considered essential to the objective of this report.

Technical Report Documentation Page

| DOT/FAA/CT-TN88/4-I                                                                                                                                                        | 2. Government Accession No.                                                                                           |                                                                                                                               | Recipient's Catalog I                                                                               | 19.                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------|

| DOTIENRIOT THOOLA T                                                                                                                                                        |                                                                                                                       |                                                                                                                               |                                                                                                     |                                            |

| 4. Title and Subtitle                                                                                                                                                      |                                                                                                                       | 5.                                                                                                                            | Report Date                                                                                         |                                            |

|                                                                                                                                                                            |                                                                                                                       |                                                                                                                               | October 1989                                                                                        |                                            |

| AIRCRAFT REPLY AND INTERFERENCE ENVIRONMENT SIMULATOR<br>(ARIES) HARDWARE PRINCIPLES OF OPERATION: VOLUME I                                                                |                                                                                                                       | 0.                                                                                                                            | Performing Organizati                                                                               | on Code                                    |

|                                                                                                                                                                            |                                                                                                                       |                                                                                                                               | Performing Organizati                                                                               | an Report No.                              |

| 7. Author's)                                                                                                                                                               |                                                                                                                       | 1                                                                                                                             |                                                                                                     |                                            |

|                                                                                                                                                                            | Mancus                                                                                                                |                                                                                                                               | DOT/FAA/CT-TM                                                                                       |                                            |

| 9. Performing Organization Name and Addr                                                                                                                                   | •11                                                                                                                   | 10                                                                                                                            | . Work Unit No. (TRAI                                                                               | S)                                         |

| Federal Aviation Administ                                                                                                                                                  | ration                                                                                                                |                                                                                                                               | Centrect or Grant Ne                                                                                |                                            |

| Technical Center<br>Atlantic City Internation                                                                                                                              | al Airport, New Jers                                                                                                  | sey 08405                                                                                                                     |                                                                                                     |                                            |

| 12 (                                                                                                                                                                       |                                                                                                                       |                                                                                                                               | . Type of Report and f                                                                              | Period Covered                             |

| 12. Sponsoring Agency Name and Address                                                                                                                                     | artation                                                                                                              | Í                                                                                                                             |                                                                                                     |                                            |

| U.S. Department of Transp<br>Federal Aviation Administ                                                                                                                     |                                                                                                                       |                                                                                                                               | Technica                                                                                            | l Note                                     |

| Technical Center                                                                                                                                                           | .14(10)                                                                                                               |                                                                                                                               | Spensoring Agency C                                                                                 | ode                                        |

| Atlantic City Internation                                                                                                                                                  | al Airport. New Jers                                                                                                  |                                                                                                                               |                                                                                                     |                                            |

| files for traffic model a<br>replies and fruit, feedin<br>Support documentation for<br>ARIES Hardware Maintenanc<br>Appendixes of the Hardwar<br>ARIES Hardware Principles | g them to the sensor<br>ARIES consists of:<br>e Manual: Volume I (<br>e Maintenance Manual                            | at radio f<br>DOT/FAA/CT-<br>: Volume II                                                                                      | requency.<br>TN88/3)                                                                                | t                                          |

| ARIES Hardware Frinciples<br>Appendixes of the Hardwar<br>ARIES Software Principles<br>ARIES Software User's Man                                                           | e Principles of Oper<br>of Operation (DOT/F                                                                           | ation: Volu<br>AA/CT-TN87/                                                                                                    | me II                                                                                               |                                            |

|                                                                                                                                                                            | YF 1                                                                                                                  |                                                                                                                               |                                                                                                     |                                            |

| This document, the ARIES<br>the theory of operation o<br>fabricated at the Federal<br>hardware device is discus<br>diagrams, and state timin                               | f the ARIES special<br>Aviation Administra<br>sed. Functional blo<br>g diagrams are inclu                             | purpose har<br>tion Techni<br>ck diagrams<br>ded where a                                                                      | dware designed<br>cal Center. E<br>, signal timin<br>ppropriate.                                    | and<br>ach<br>g                            |

| the theory of operation o<br>fabricated at the Federal<br>hardware device is discus<br>diagrams, and state timin                                                           | f the ARIES special<br>Aviation Administra<br>sed. Functional blo<br>g diagrams are inclu                             | purpose har<br>tion Techni<br>ck diagrams<br>ded where a                                                                      | dware designed<br>cal Center. E<br>, signal timin<br>ppropriate.                                    | and<br>ach<br>g                            |

| the theory of operation o<br>fabricated at the Federal<br>hardware device is discus<br>diagrams, and state timin<br>Figure 1                                               | f the ARIES special<br>Aviation Administra<br>sed. Functional blo<br>g diagrams are inclu<br>Beacon System<br>Replies | purpose har<br>tion Techni<br>ck diagrams<br>ded where a<br>swibution Statement<br>cument is on<br>iter Library               | dware designed<br>cal Center. E<br>, signal timin<br>ppropriate.                                    | and<br>ach<br>g<br>KR)<br>echnical 15<br>y |

| the theory of operation o<br>fabricated at the Federal<br>hardware device is discus<br>diagrams, and state timin                                                           | f the ARIES special<br>Aviation Administra<br>sed. Functional blo<br>g diagrams are inclu<br>Beacon System<br>Replies | purpose har<br>tion Techni<br>ck diagrams<br>ded where a<br>wibutten Statement<br>cument is on<br>iter Library<br>cernational | dware designed<br>cal Center. E<br>, signal timin<br>ppropriate.<br>file at the I<br>, Atlantic Cit | and<br>ach<br>g<br>KR)<br>echnical 15<br>y |

.

### TABLE OF CONTENTS

|     |                                                                              | Page           |

|-----|------------------------------------------------------------------------------|----------------|

| EXE | ECUTIVE SUMMARY                                                              | xiii           |

| 1.  | INTRODUCTION                                                                 | 1              |

| 2.  | BACKGROUND                                                                   | 1              |

| 3.  | RELATED DOCUMENTS                                                            | 2              |

| 4.  | ARIES SYSTEM CAPABILITIES                                                    | 3              |

|     | 4.1 Modeled Reply Generation                                                 | 5              |

|     | 4.1.1 Simulated ATCRBS<br>4.1.2 Simulated Mode S                             |                |

|     | 4.2 Fruit Reply Generation                                                   | 7              |

|     | 4.2.1 ATCRBS Fruit Repl<br>4.2.2 Mode S Fruit Repl                           |                |

|     | 4.3 Radar Report Generation<br>4.4 Self-Test Capabilities                    | 10<br>10       |

| 5.  | ARIES EQUIPMENT                                                              | 11             |

| 6.  | HARDWARE DESCRIPTION                                                         | 19             |

|     | 6.1 ARIES System Clock<br>6.2 Uplink Receiver                                | 30<br>30       |

|     | 6.2.1 Analog Circuitry<br>6.2.2 Digital Circuitry                            | 32<br>32       |

|     | 6.3 Azimuth Decoder/Simulato                                                 | <b>r</b> 57    |

|     | 6.3.1 Sensor Mode<br>6.3.2 ARIES Mode<br>6.3.3 Azimuth Error Det             | 57<br>59<br>62 |

|     | 6.4 Reply Generators                                                         | 64             |

|     | 6.4.1 Modeled Reply Ger<br>6.4.2 Fruit Reply Gener<br>6.4.3 Analog Circuitry |                |

|     | 6.5 Universal Interval Timer                                                 | 176            |

|     | 6.5.1 UIT Control Circu                                                      | itry 179       |

# TABLE OF CONTENTS (Continued)

|      |                                                                                                                                                                                                                   | Page                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 6.6  | Missing Interrogation Timer                                                                                                                                                                                       | 179                                           |

|      | 6.6.1 MIT Control Circuitry                                                                                                                                                                                       | 184                                           |

|      | Random Number Generator<br>Radar Report Generator                                                                                                                                                                 | 184<br>184                                    |

|      | <ul><li>6.8.1 Radar Report Controller</li><li>6.8.2 ADCCP Data Converter</li><li>6.8.3 RRG Buffer Interface</li></ul>                                                                                             | 184<br>188<br>212                             |

| 6.9  | Time-of-Year Receiver                                                                                                                                                                                             | 218                                           |

|      | <ul> <li>6.9.1 Input Logic</li> <li>6.9.2 Read Ring Counter</li> <li>6.9.3 Diagnostic Logic</li> <li>6.9.4 Load Ring Counter</li> <li>6.9.5 Digital Millisecond Timer</li> <li>6.9.6 TOY Control Logic</li> </ul> | 218<br>218<br>220<br>220<br>220<br>220<br>223 |

| 6.10 | Self Test Unit                                                                                                                                                                                                    | 223                                           |

|      | 6.10.1 Uplink Transmitter<br>6.10.2 Downlink Receiver                                                                                                                                                             | 223<br>241                                    |

| Acces | sion For       |

|-------|----------------|

| NTIS  | GRA&I          |

| DIIC  | TAB 🚺          |

|       | ounced 🗌       |

| Justi | fication       |

|       |                |

| By    |                |

| Distr | ibution/       |

| Avat  | lability Codes |

|       | Aveil and/or   |

| Dist  | Special        |

|       |                |

|       |                |

| A     |                |

| w     |                |

# LIST OF ILLUSTRATIONS

| Figure    |                                                | Page |

|-----------|------------------------------------------------|------|

| 4-1       | ARILS Hardware Block Diagram                   | 4    |

| 5-1       | ARIES Equipment Overview                       | 12   |

| 5-2       | Cabinet Layout                                 | 14   |

| 5-3       | ARIES Analog Chassis Layout                    | 17   |

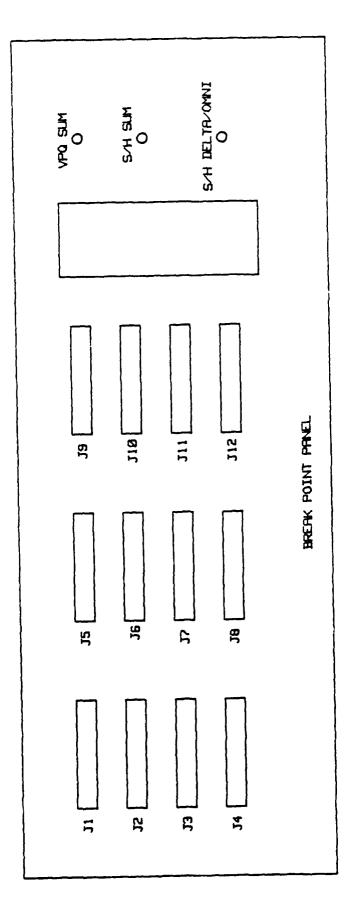

| 5-4       | Break Point Panel Layout                       | 18   |

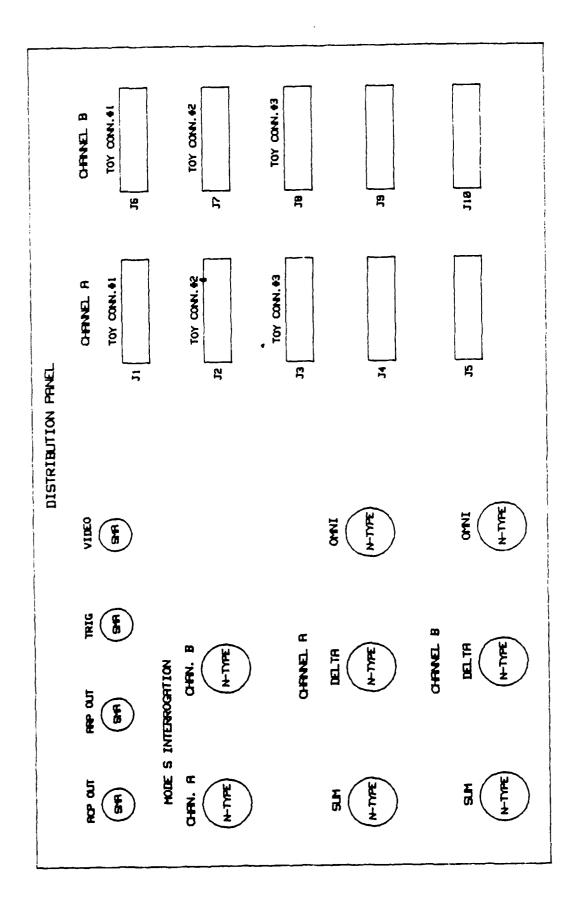

| 5-5       | Distribution Panel Layout                      | 20   |

| 6-1       | ARIES Functional Block Diagram                 | 22   |

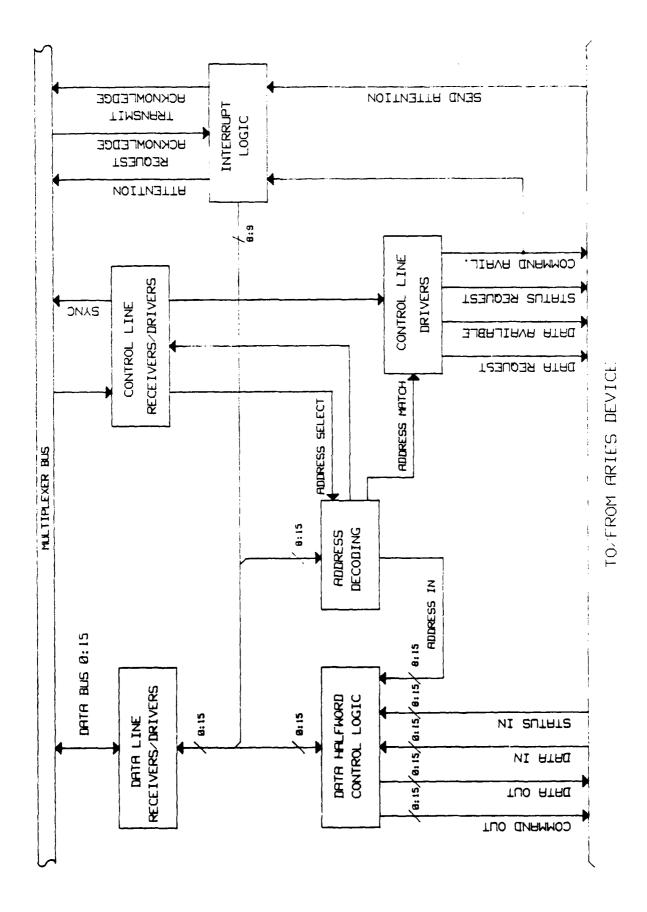

| 6-2       | Concurrent Standard I/O Bus Structure          | 25   |

| 6-3       | General Purpose Interface Block Diagram        | 26   |

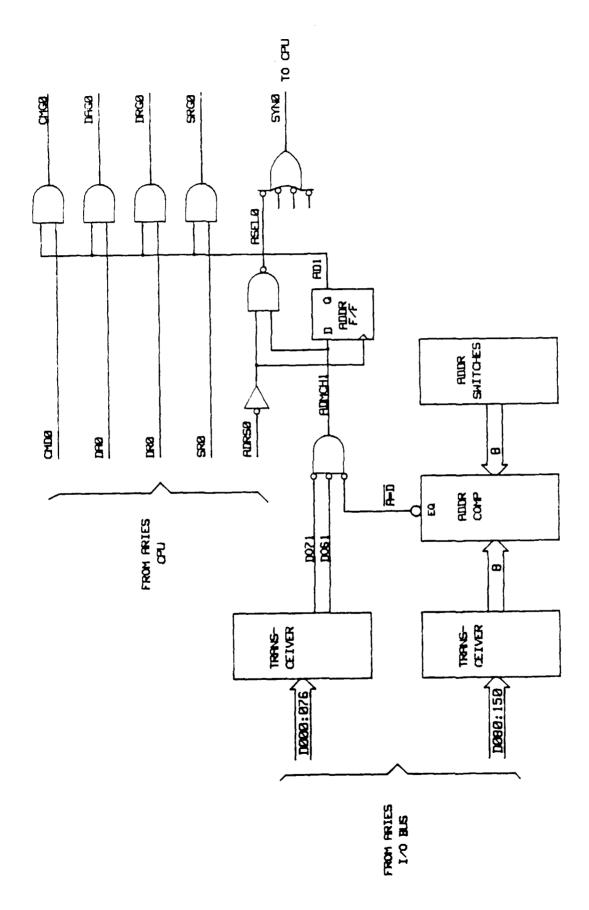

| 6-4       | Address Decoler Logic                          | 27   |

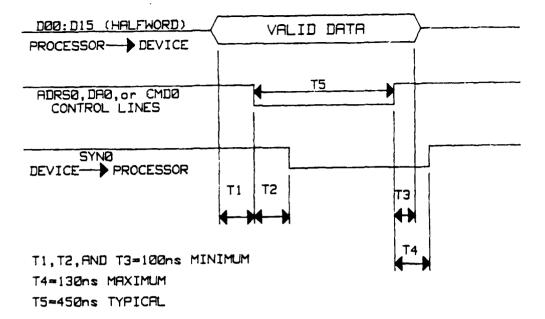

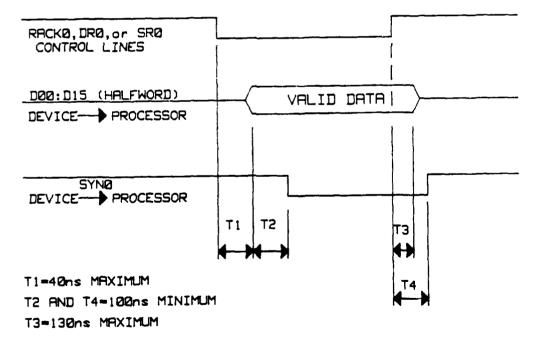

| 6-5       | Multiplexer Channel Timing                     | 29   |

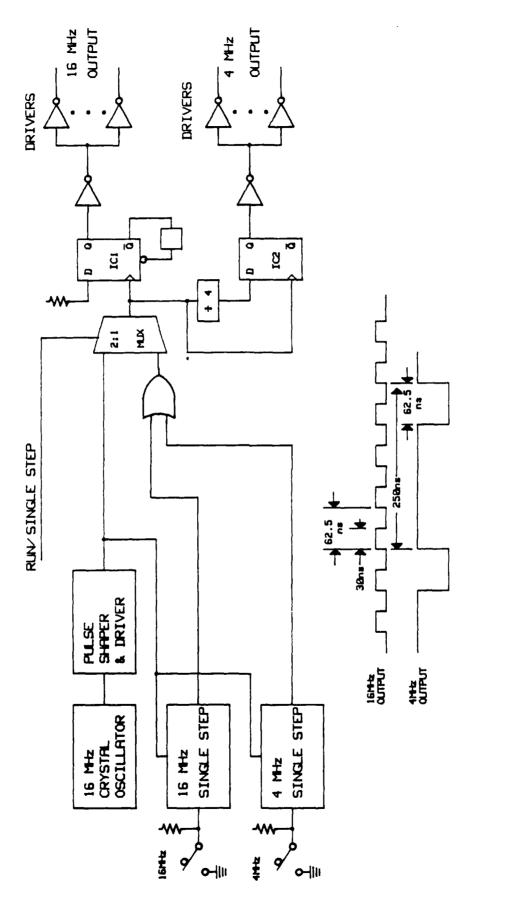

| 6.1-1     | ARIES System Clock Block Diagram and Waveforms | 31   |

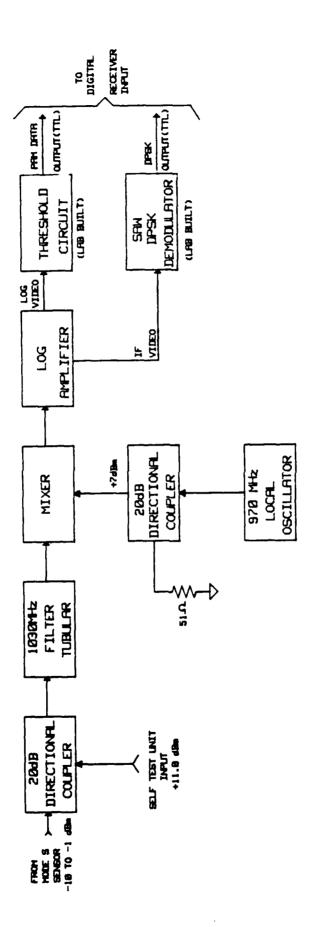

| 6.2.1-1   | Uplink Receiver Analog Block Diagram           | 33   |

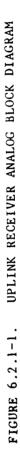

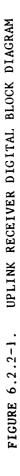

| 6.2.2-1   | Uplink Receiver Digital Block Diagram          | 34   |

| 6.2.2.1-1 | Channel Select Logic                           | 35   |

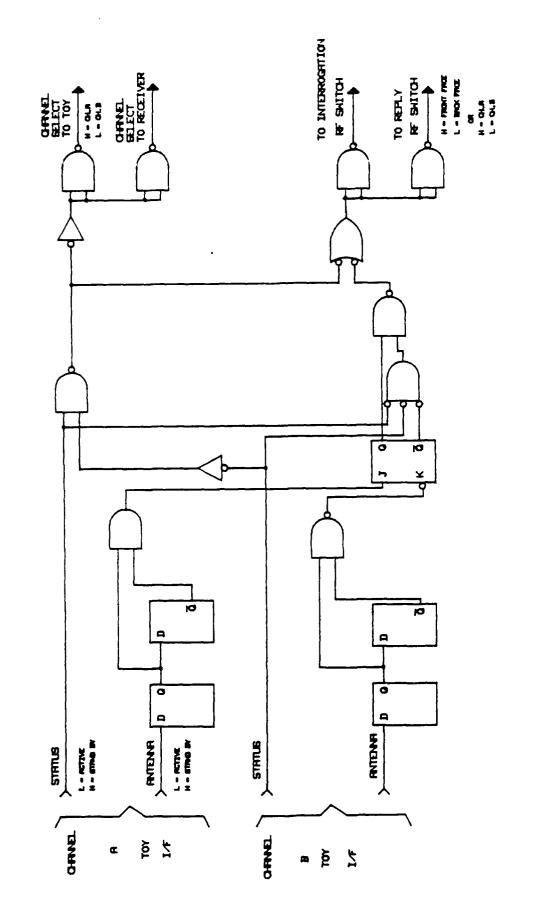

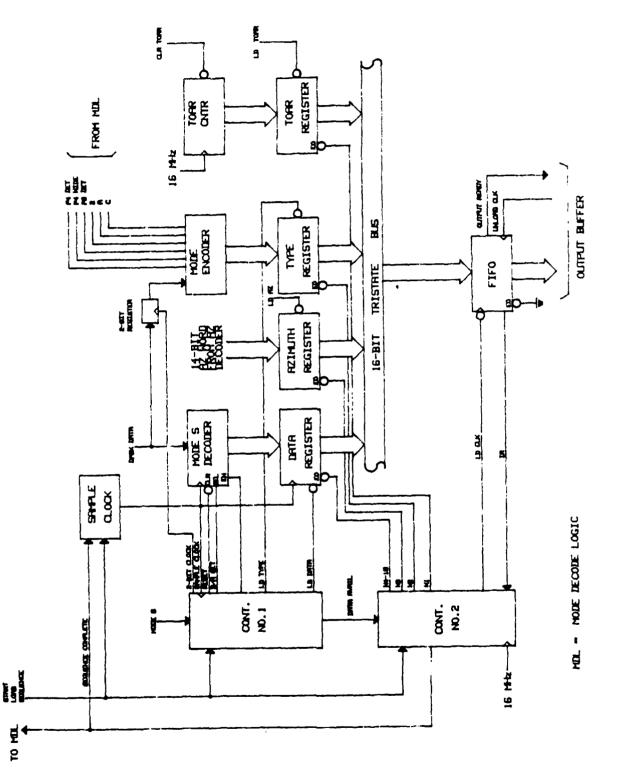

| 6.2.2.2-1 | Mode Decoder Block Diagram                     | 37   |

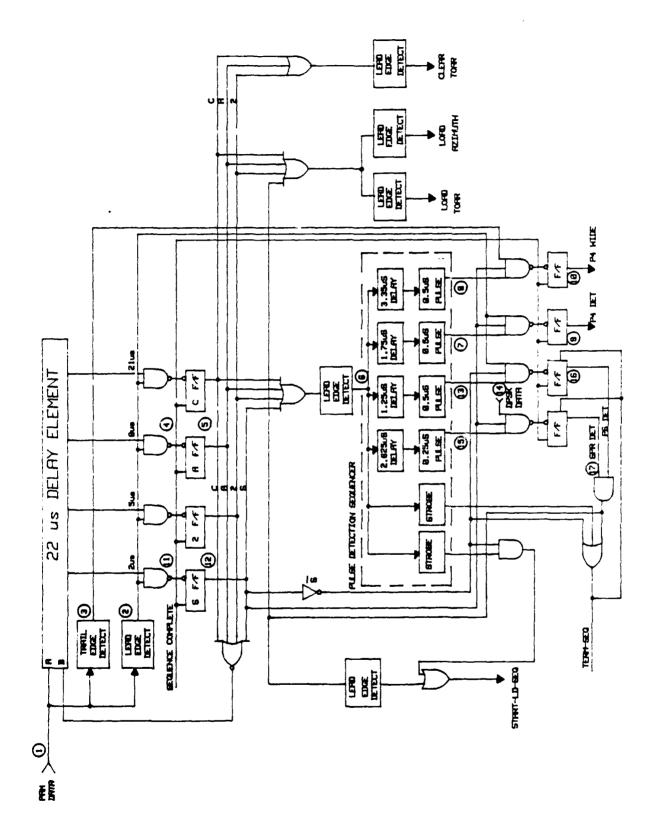

| 6.2.2.2-2 | Mode Decoder Waveform                          | 38   |

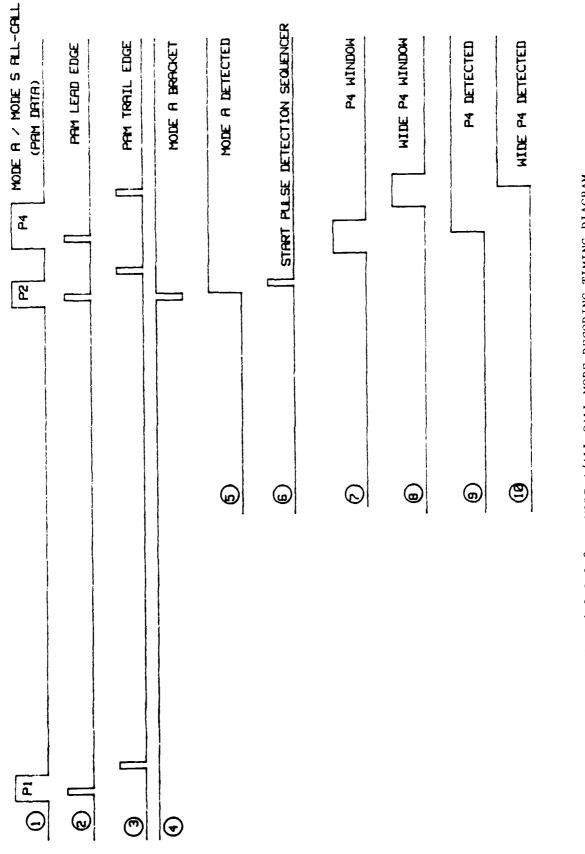

| 6.2.2.2-3 | Mode A/All-Call Mode Decoding Timing Diagram   | 39   |

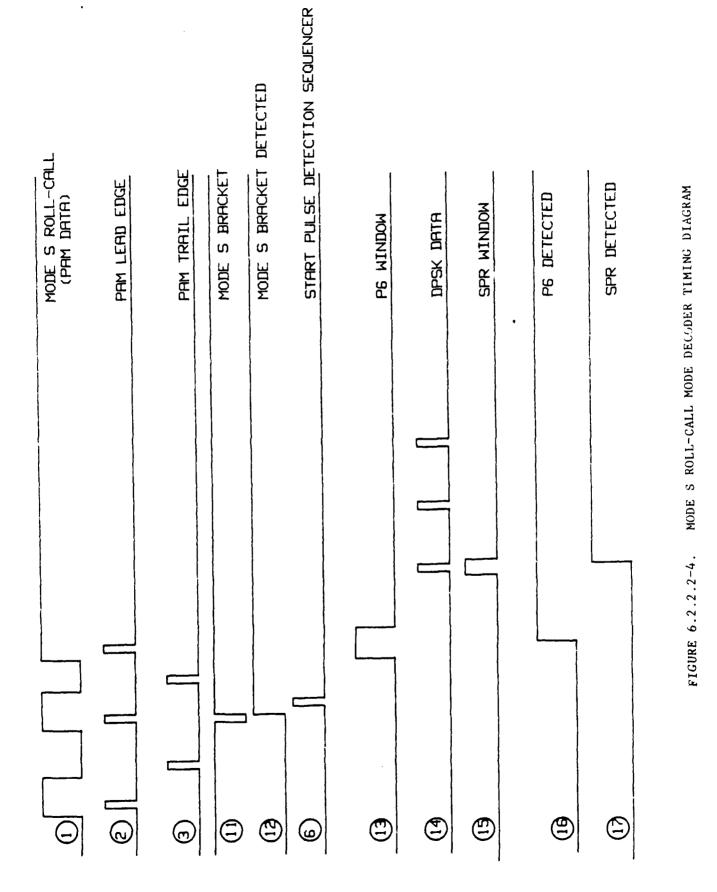

| 6.2.2.2-4 | Mode S Roll-Call Mode Decoder Timing Diagram   | 41   |

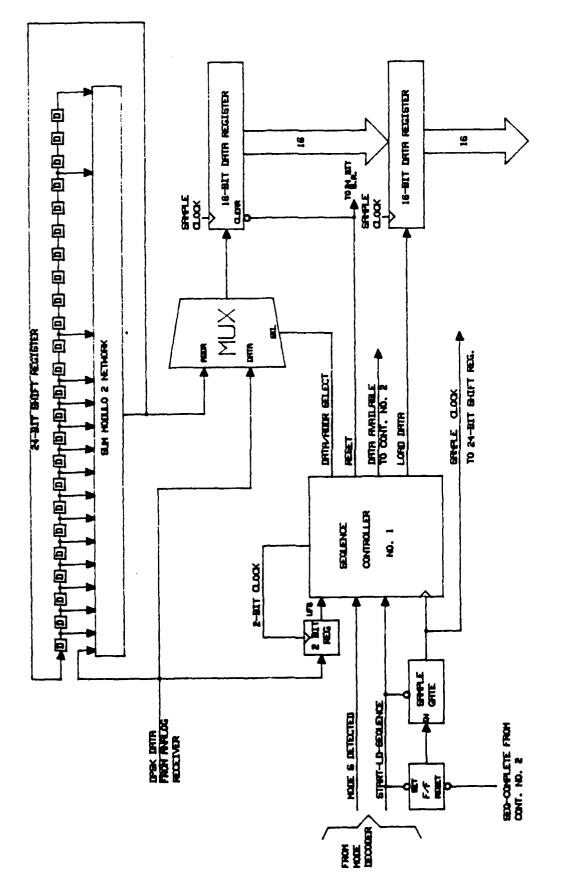

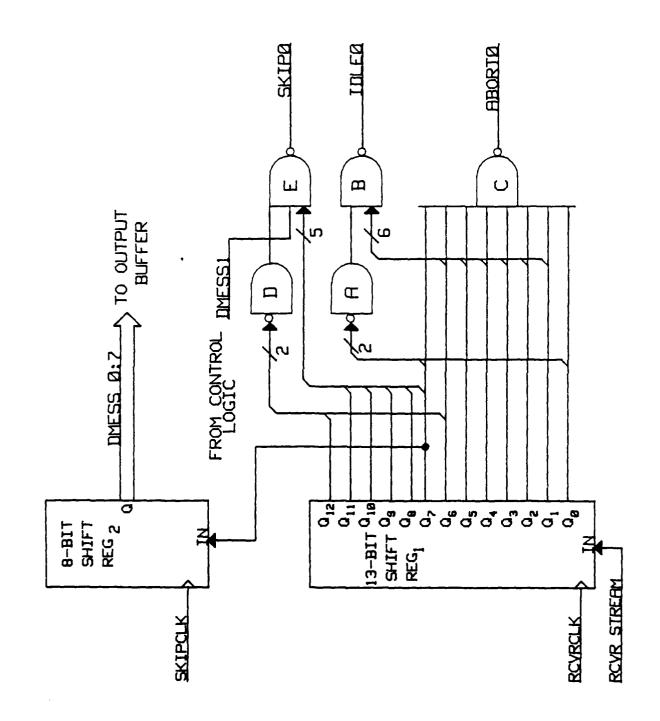

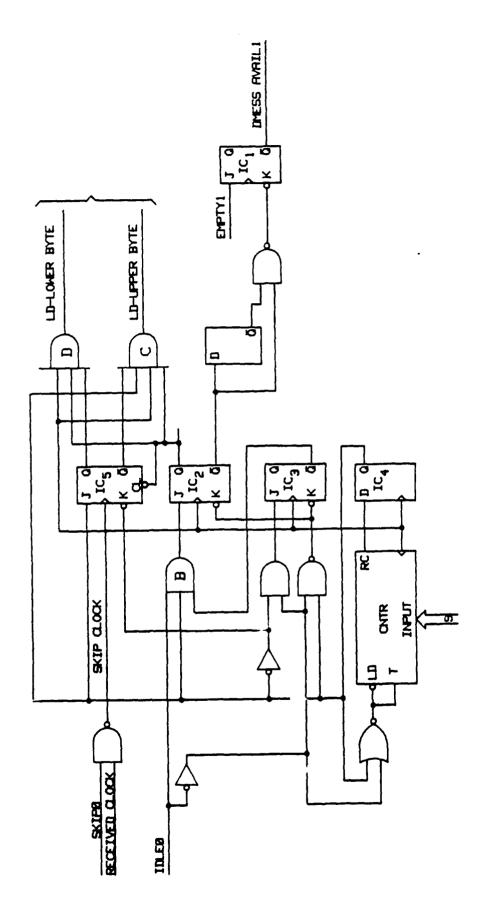

| 6.2.2.3-1 | Data Assembly Block Diagram                    | 42   |

| 6.2.2.3-2 | Mode S Parity Decoding Block Diagram           | 45   |

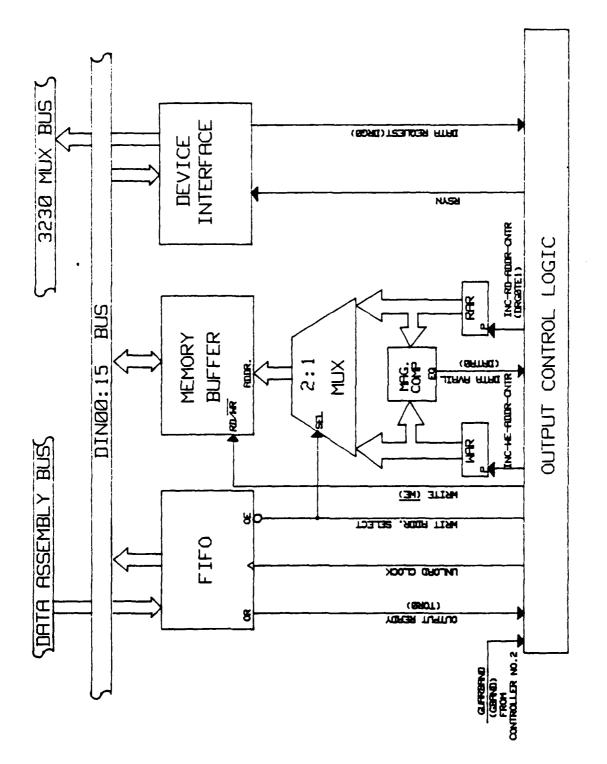

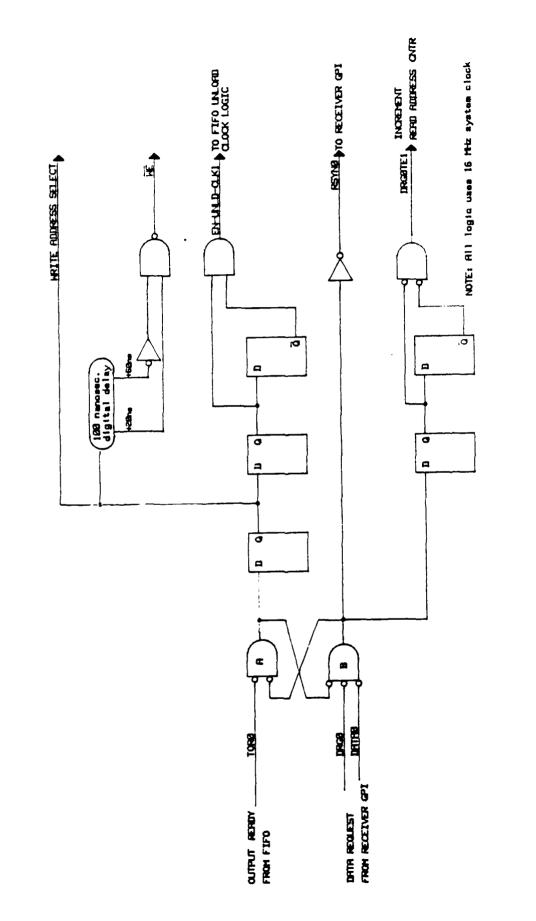

| 6.2.2.4-1 | Output Transfer Sequence Block Diagram         | 46   |

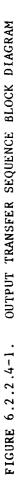

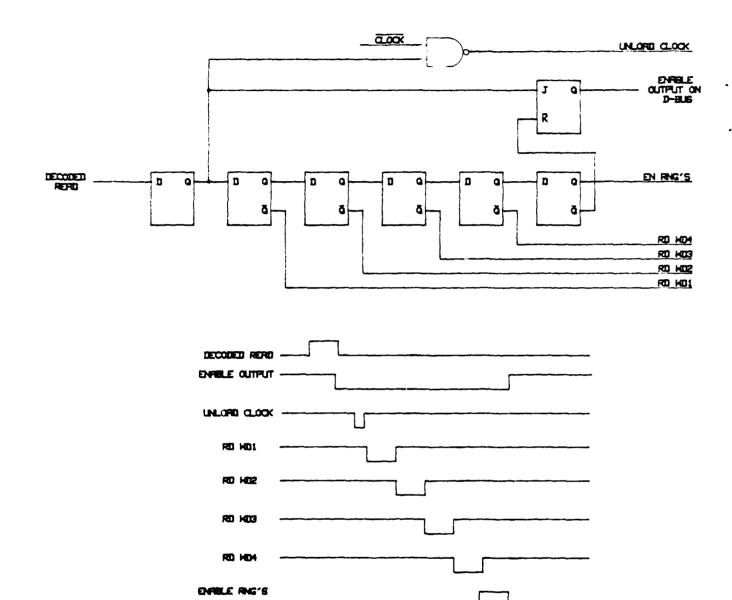

| 6.2.2.4-2 | FIFO Unload Clock Logic                        | 48   |

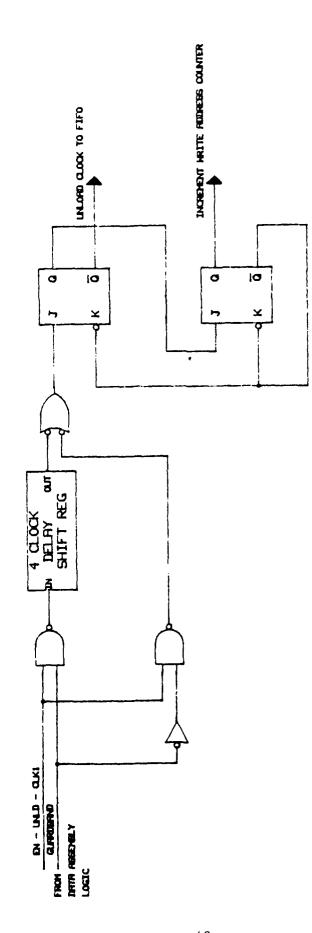

| 6.2.2.4-3 | Uplink Receiver Timing Waveform Diagram        | 49   |

v

| Figure        |                                                 | Page |

|---------------|-------------------------------------------------|------|

| 6.2.2.4-4     | Bus Contention Control Logic                    | 50   |

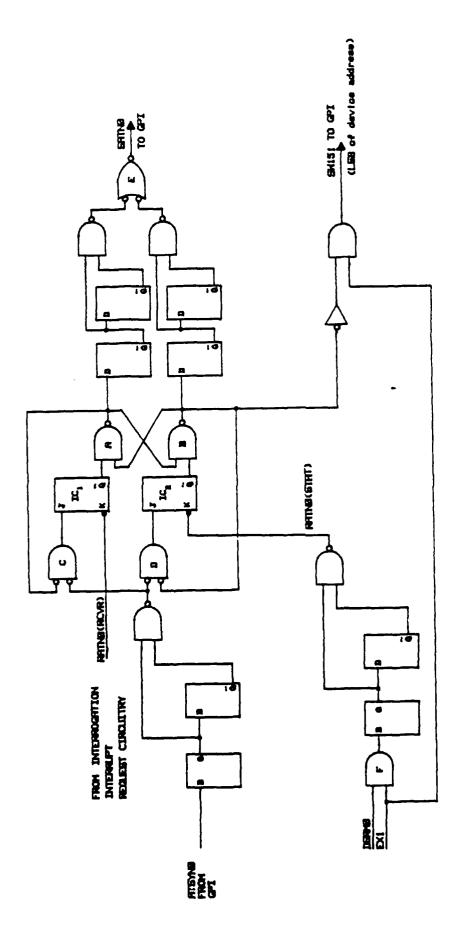

| 6.2.2.5-1     | Interrogation Interrupt Request Circuitry       | 52   |

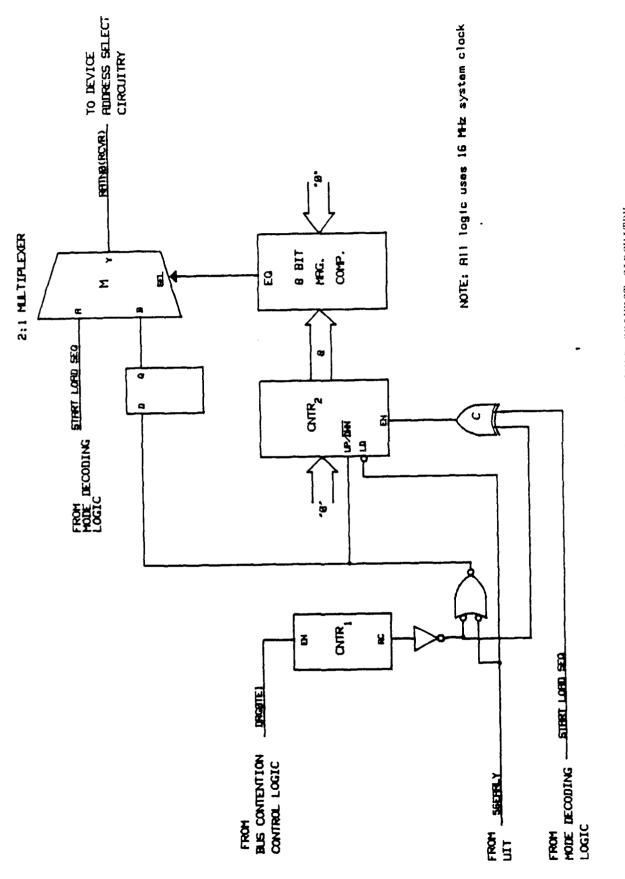

| 6.2.2.6-1     | Modified Device Address Select Circuitry        | 54   |

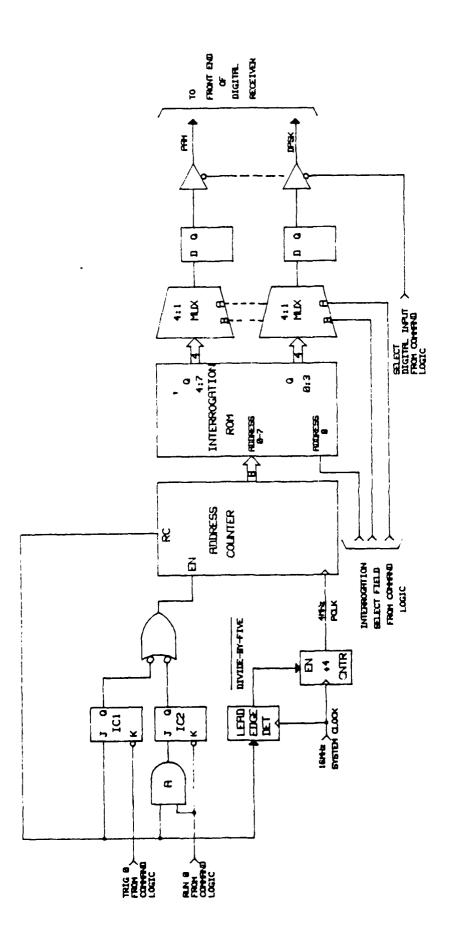

| 6.2.2.7-1     | Interrogation Simulation Circuitry              | 56   |

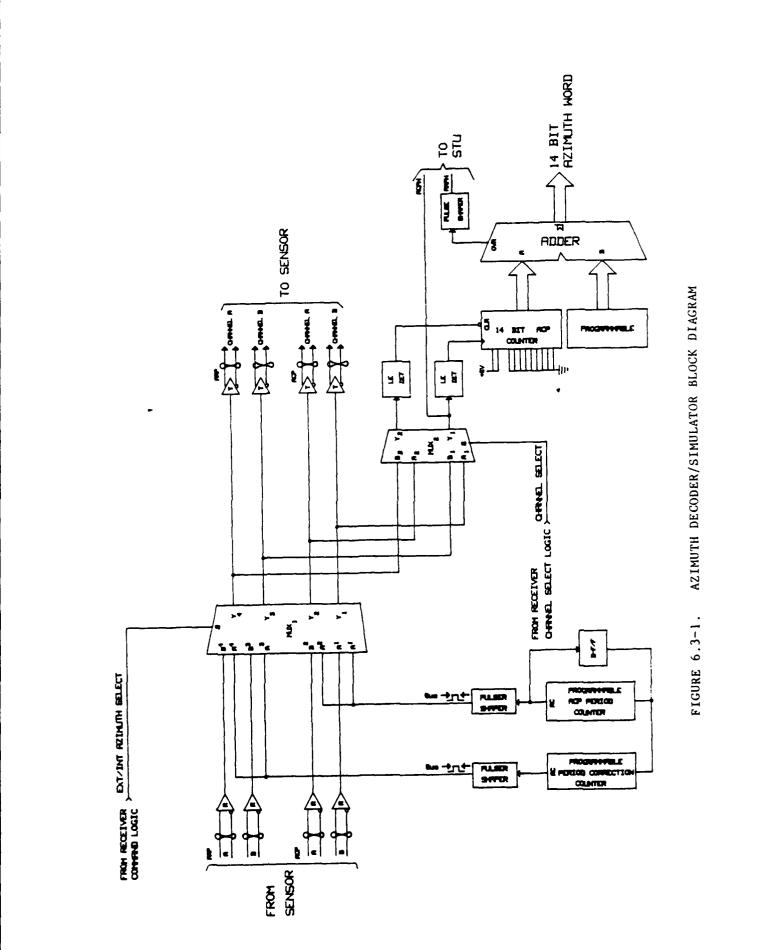

| 6.3-1         | Azimuth Decoder/Simulator Block Diagram         | 58   |

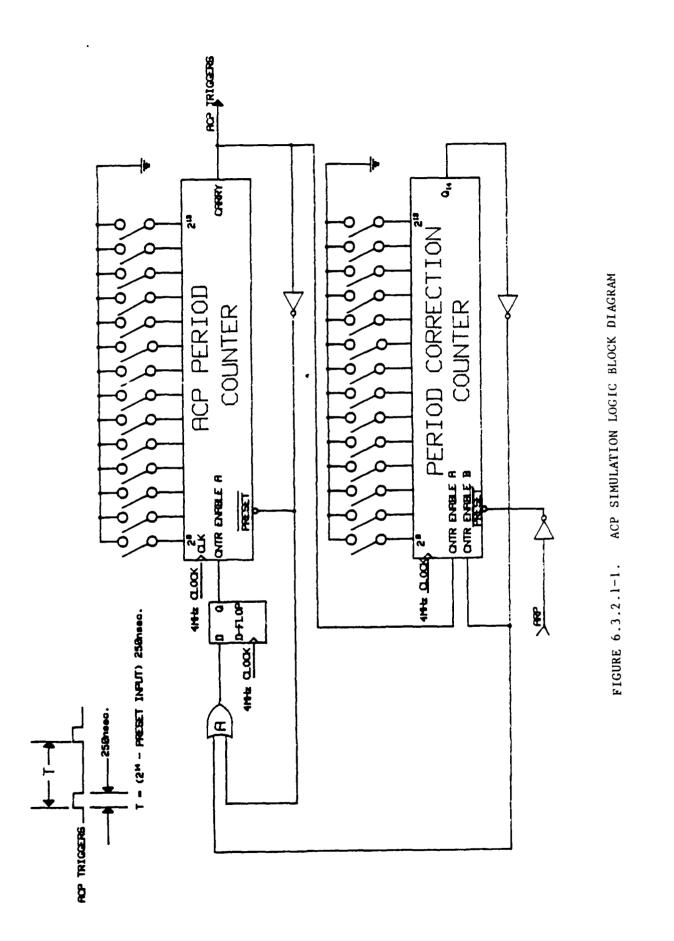

| 6.3.2.1-1     | ACP Simulation Logic Block Diagram              | 60   |

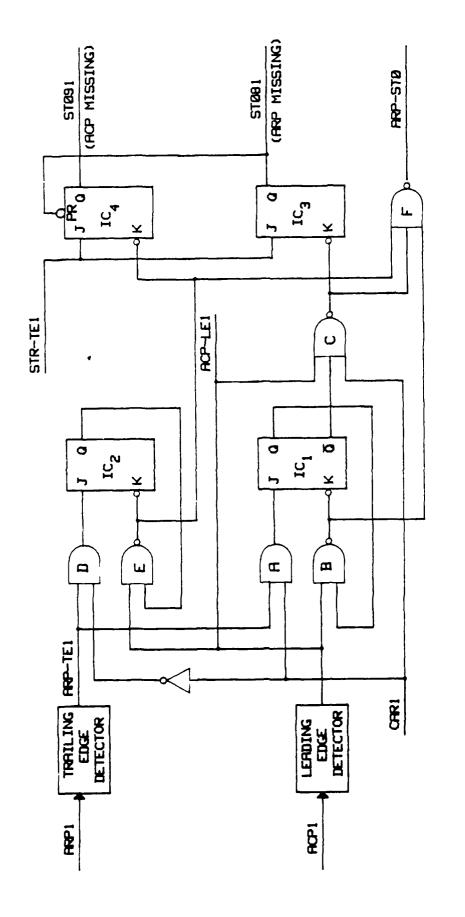

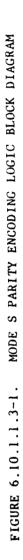

| 6.3.3-1       | Azimuth Error Detection Logic Diagram           | 63   |

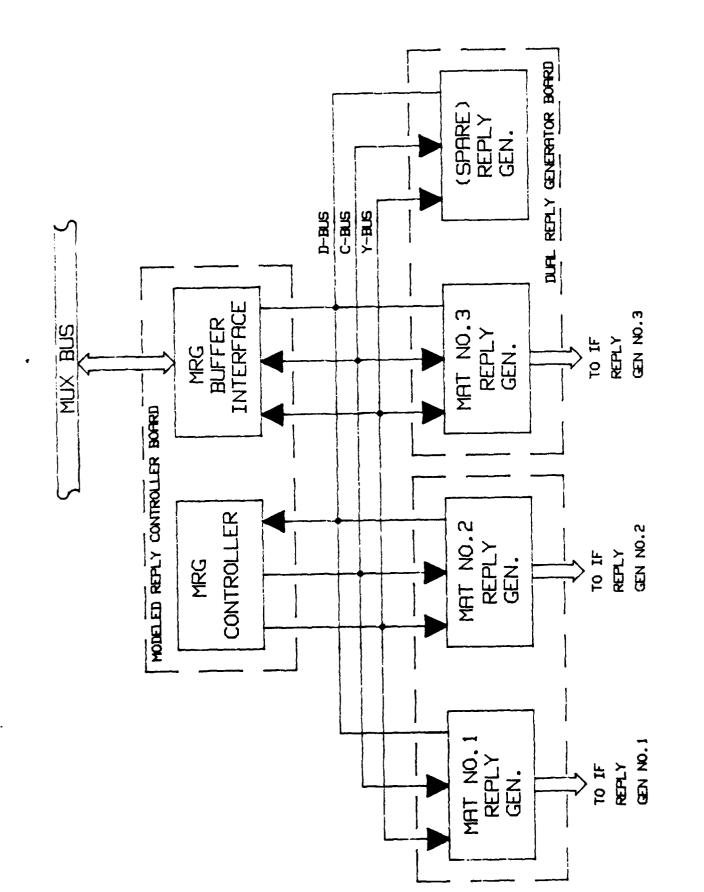

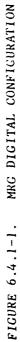

| 6.4.1-1       | MRG Digital Configuration                       | 65   |

| 6.4.1.1-1     | MRC Block Diagram                               | 67   |

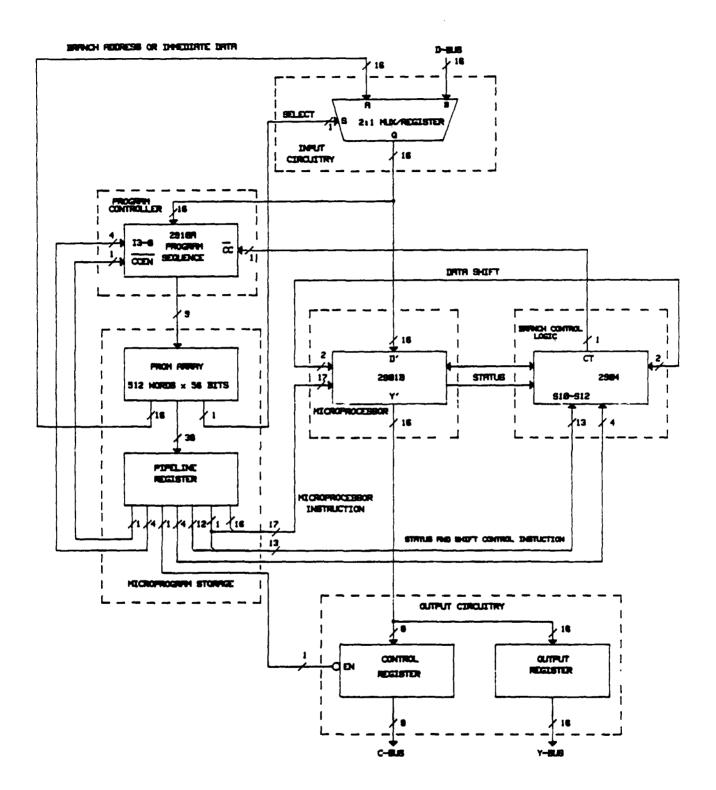

| 6.4.1.1.2-1   | Microprocessor Slice Block Diagram              | 68   |

| 6.4.1.1.2-2   | 16-Bit Microprocessor Block Diagram             | 70   |

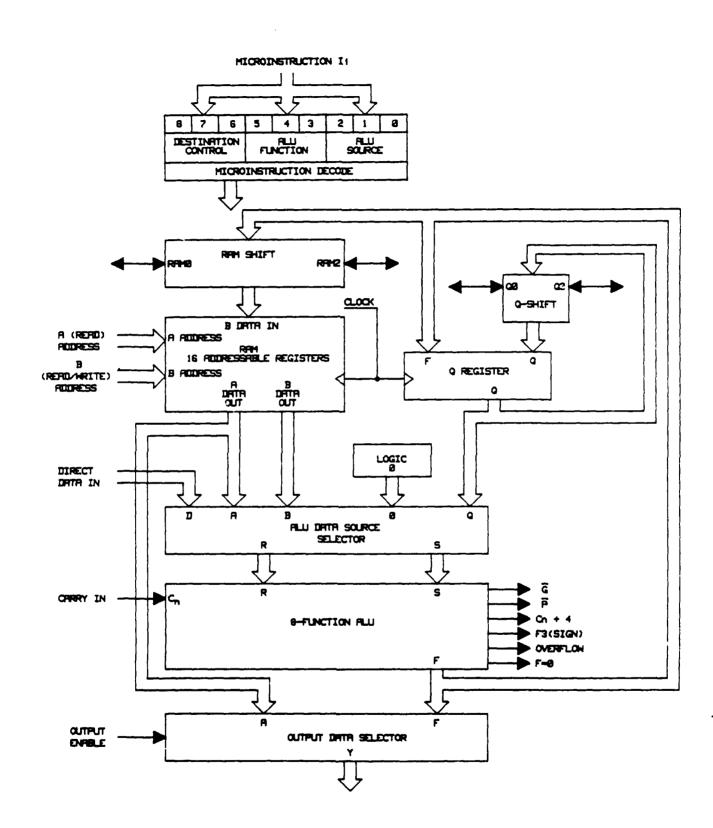

| 6.4.1.1.2-3   | Shift Linkage Multiplexer Instruction Code      | 72   |

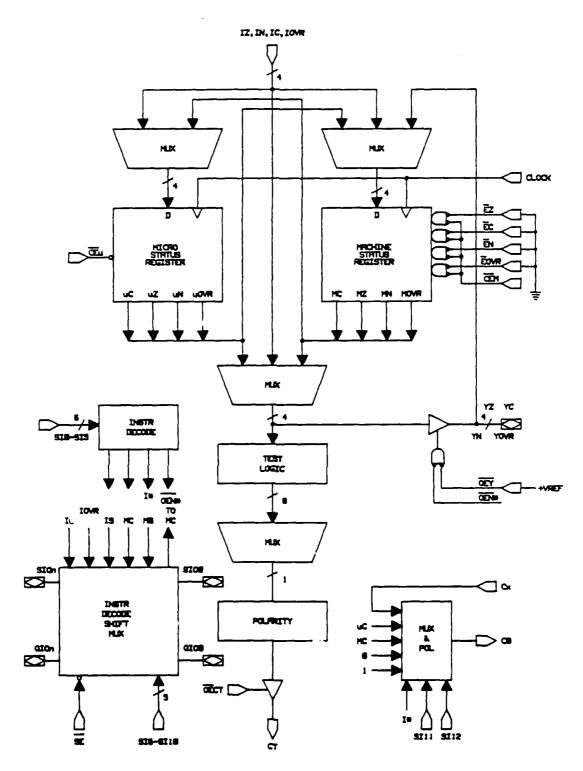

| 6.4.1.1.3-1   | Status and Shift Control Unit Block Diagram     | 74   |

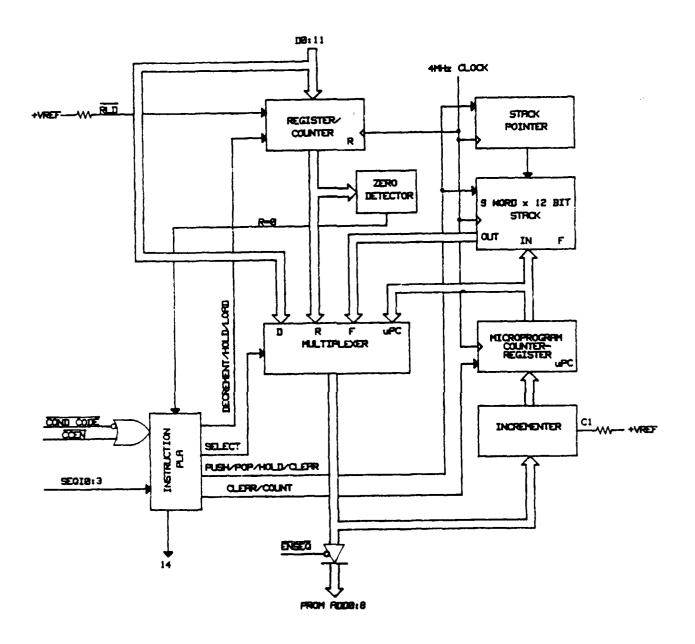

| 6.4.1.1.4-1   | Program Controller Block Diagram                | 77   |

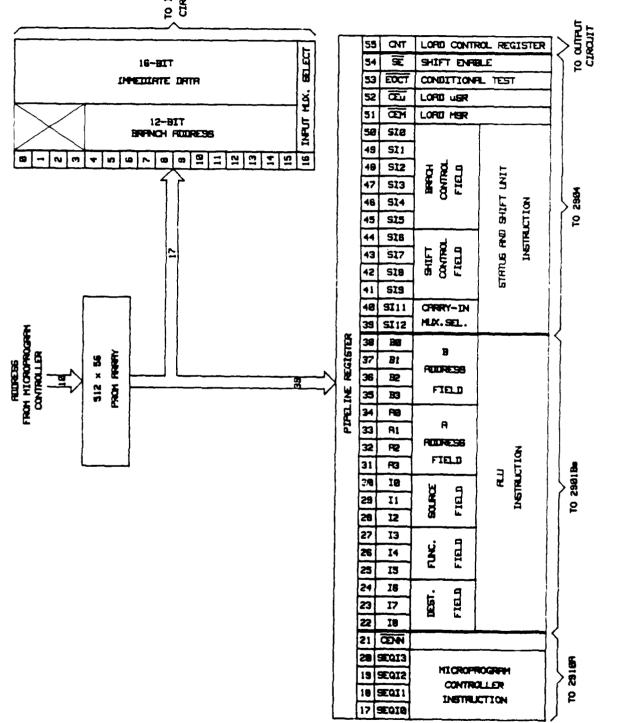

| 6.4.1.1.5-1   | Microprogram Storage and Pipeline Register      | 79   |

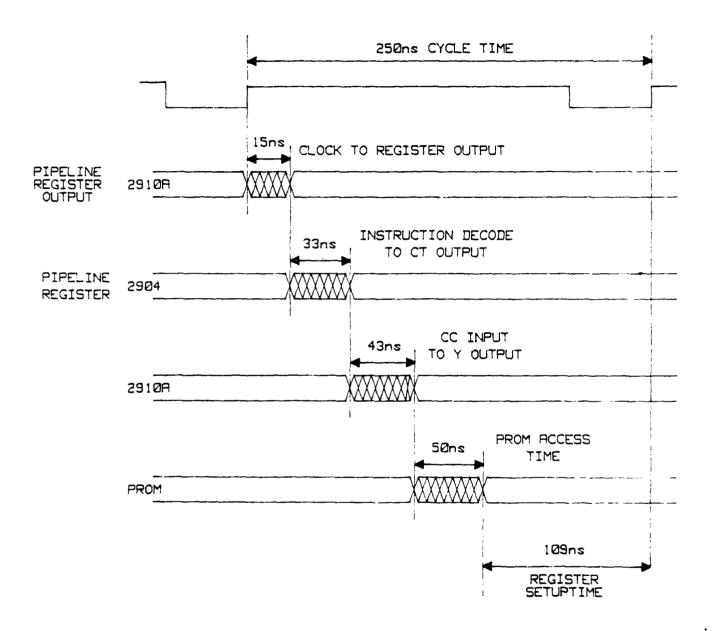

| 6.4.1.1.5-2   | Typical Cycle Timing Waveform                   | 80   |

| 6.4.1.1.6-1   | Controller Input Circuits                       | 81   |

| 6.4.1.1.7-1   | Controller Output Circuits                      | 82   |

| 6.4.1.2.1-1   | Device Address and Op Code for Reply Generators | 85   |

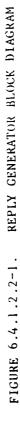

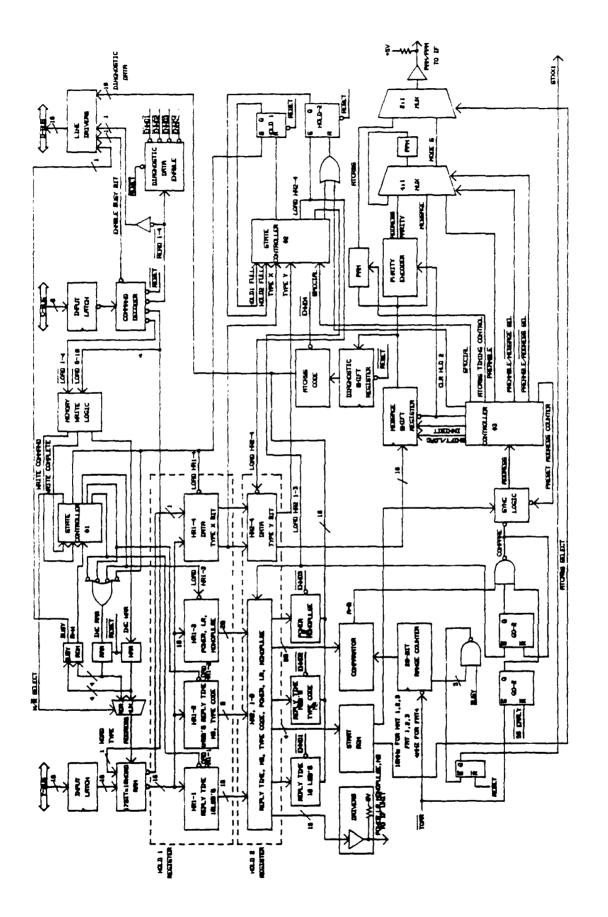

| 6.4.1.2.2-1   | Reply Generator Block Diagram                   | 87   |

| 6.4.1.2.2.1-1 | Reply Generator Detailed Block Diagram          | 89   |

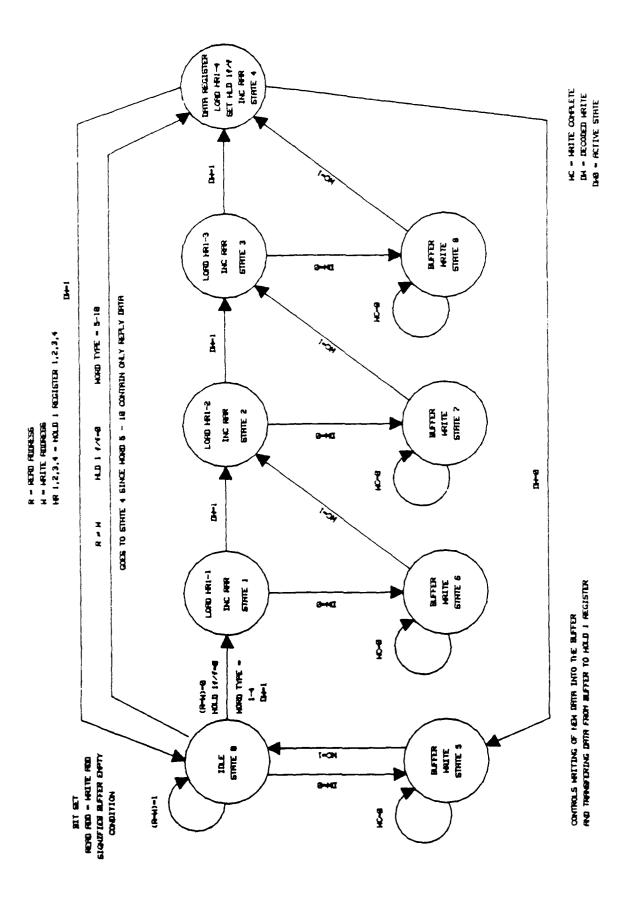

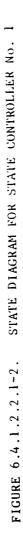

| 6.4.1.2.2.1-2 | State Diagram for State Controller No. 1        | 90   |

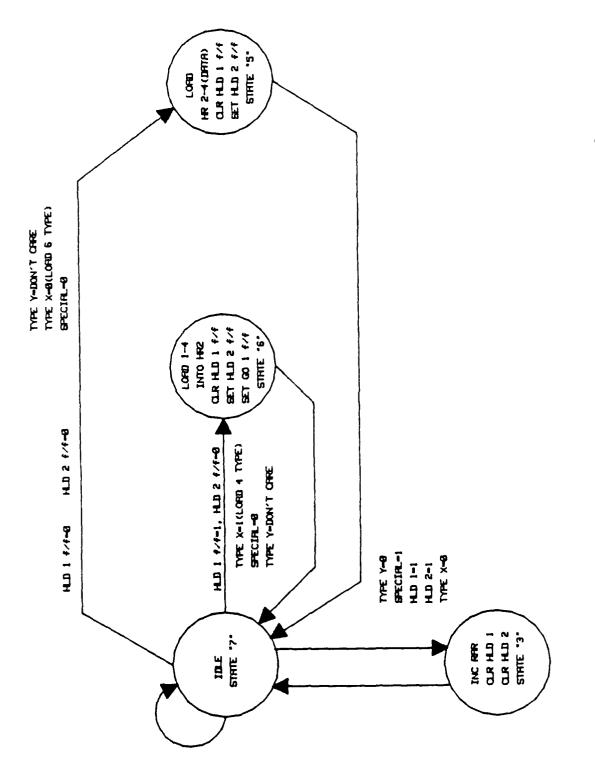

| 6.4.1.2.2.1-3 | State Diagram for State Controller No. 2        | 91   |

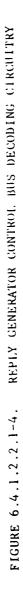

| 6.4.1.2.2.1-4 | Reply Generator Control Bus Decoding Circuitry  | 92   |

| Figure        |                                                                 | Page |

|---------------|-----------------------------------------------------------------|------|

| 6.4.1.2.2.1-5 | Buffer Write Logic                                              | 94   |

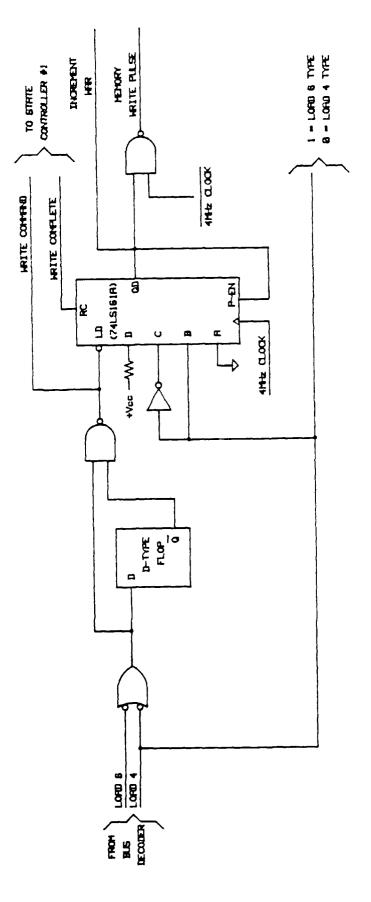

| 6.4.1.2.2.1-6 | Buffer Write Timing Waveforms                                   | 95   |

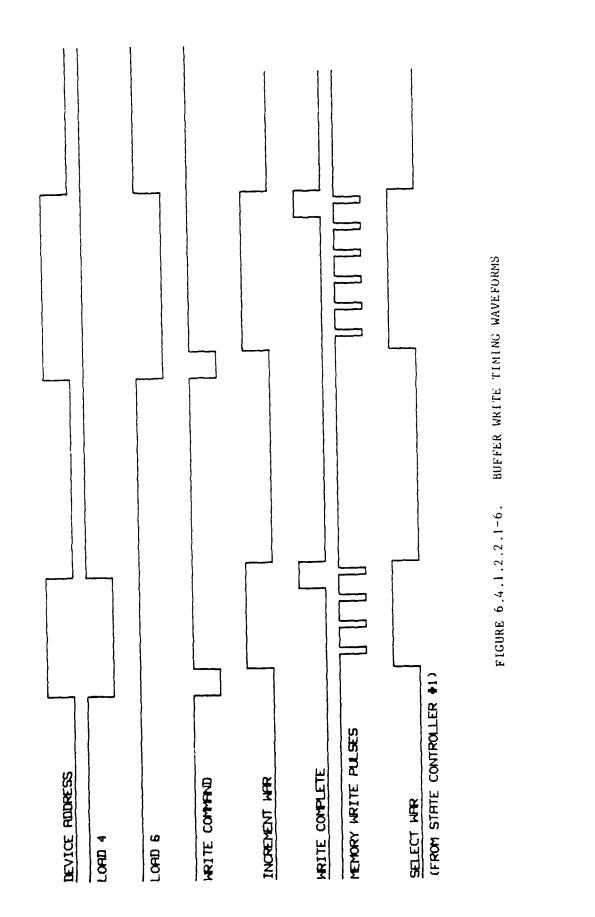

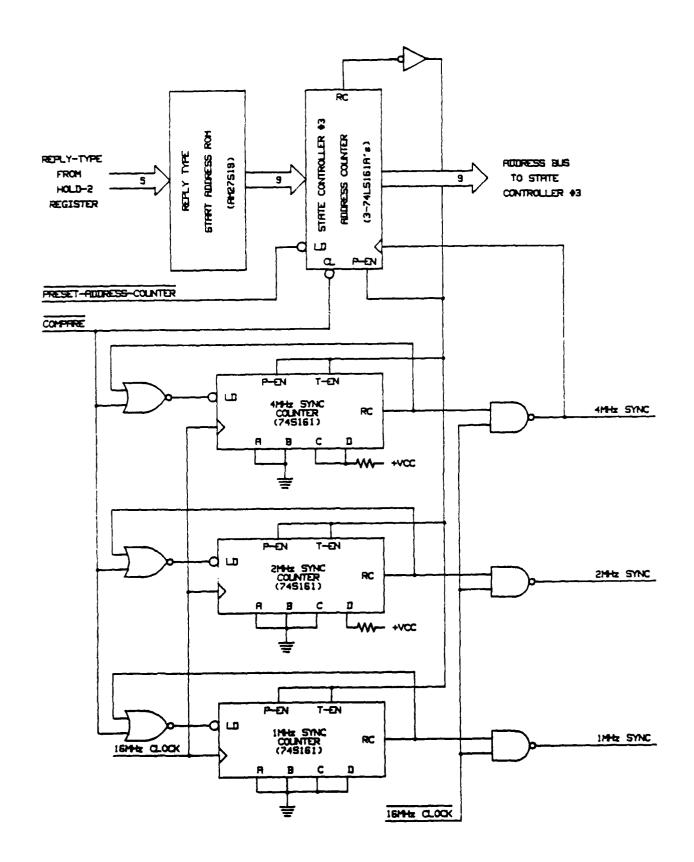

| 6.4.1.2.2.3-1 | State Controller No. 3                                          | 99   |

| 6.4.1.2.2.3-2 | Sync Logic Circuitry                                            | 100  |

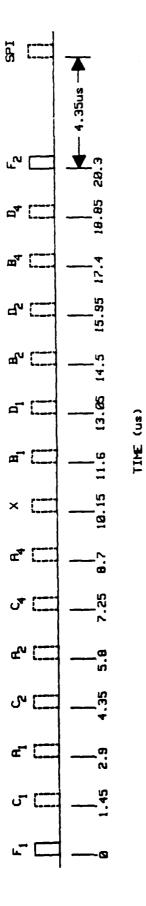

| 6.4.1.2.3-2   | Mode S Reply (short) Control Signal Waveform                    | 102  |

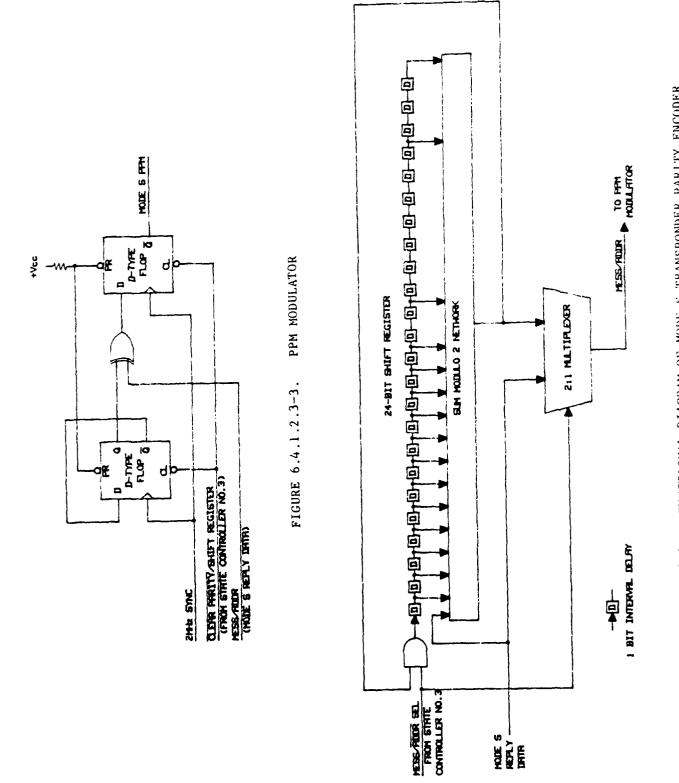

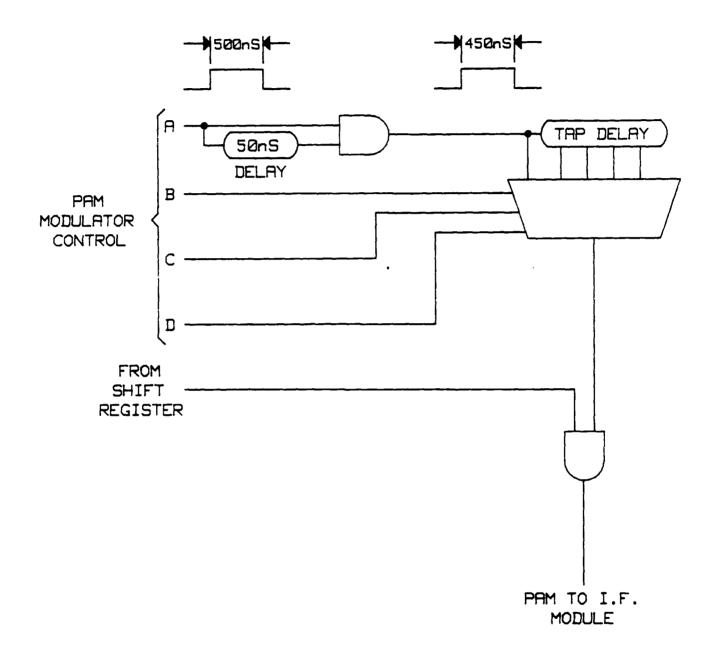

| 6.4.1.2.3-3   | PPM Modulator                                                   | 103  |

| 6.4.1.2.3-4   | Functional Diagram of Mode S Transponder<br>Parity Encoder      | 103  |

| 6.4.1.2.3-5   | ATCRBS Reply Waveform                                           | 104  |

| 6.4.1.2.3-6   | PAM Modulator                                                   | 107  |

| 6.4.1.3-1     | MRG Buffer Interface Block Diagram                              | 108  |

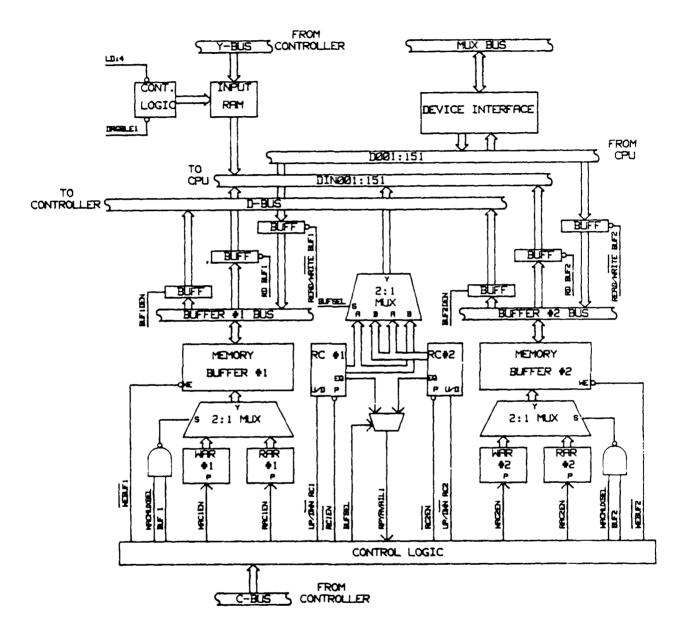

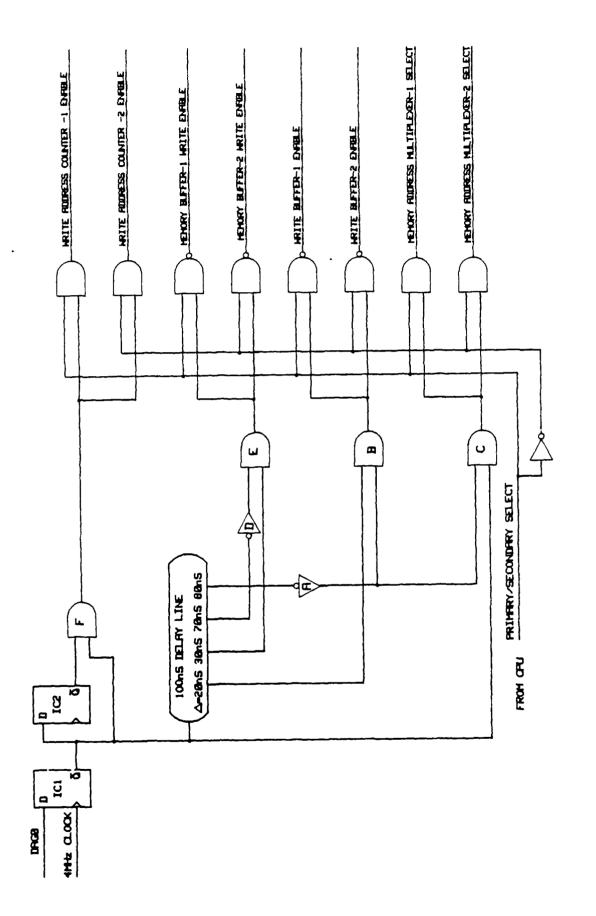

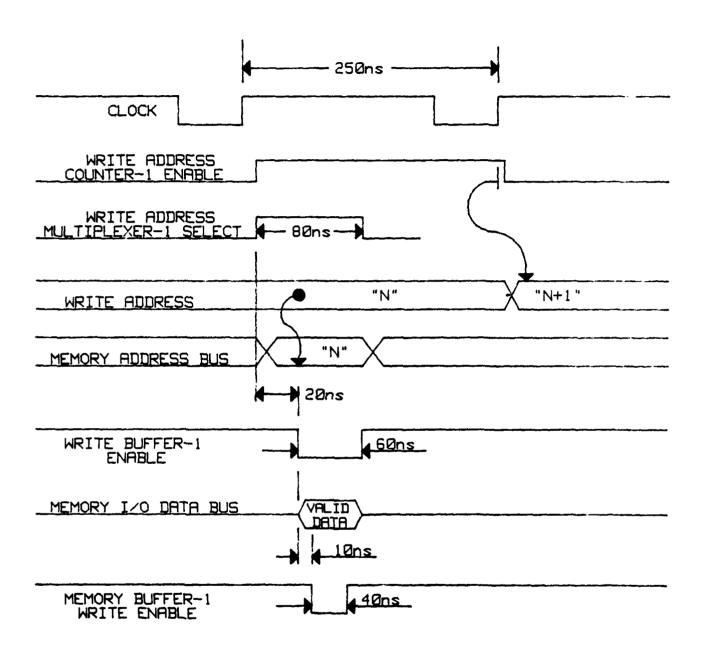

| 6.4.1.3.2-1   | Memory Write Control Logic                                      | 110  |

| 6.4.1.3.2-2   | Memory Write Cycle Waveform                                     | 111  |

| 6.4.1.3.3-1   | Memory Read Control Logic                                       | 113  |

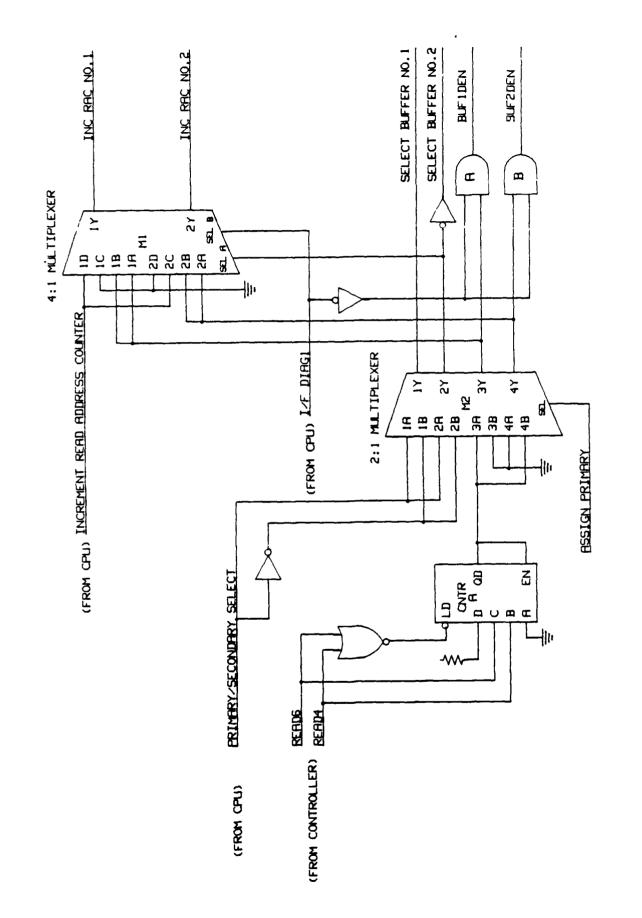

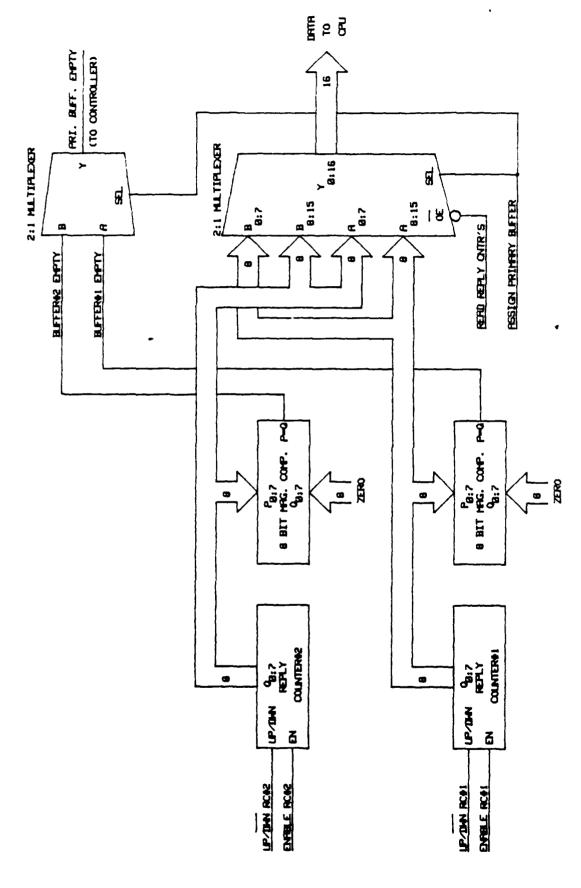

| 6.4.1.3.4-1   | Reply Counters and Supporting Logic Diagram                     | 115  |

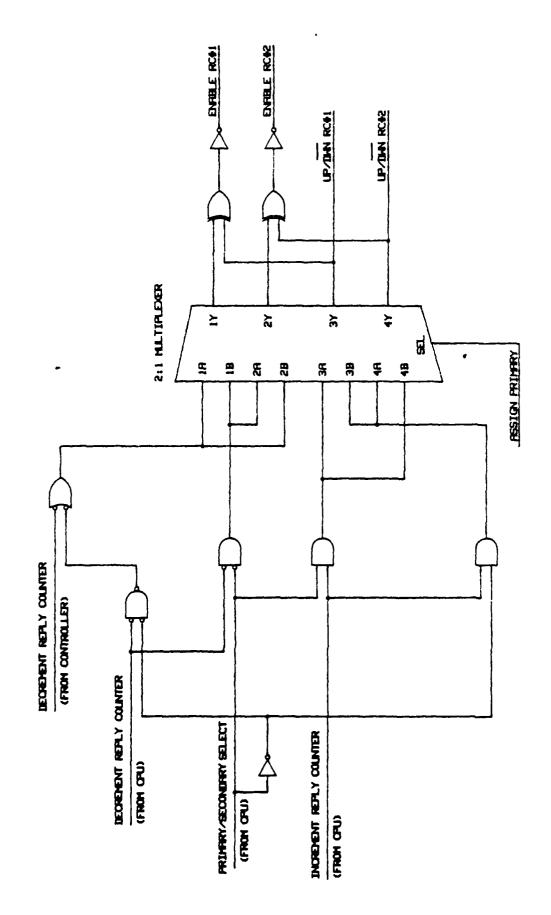

| 6.4.1.3.4-2   | Reply Counter Control Logic                                     | 116  |

| 6.4.1.3.5-1   | MRG Command Decode Logic                                        | 118  |

| 6.4.1.3.5-2   | Self Resetting Pulse Generator Timing Waveform                  | 119  |

| 6.4.1.3.5.3-1 | Input Data Circuitry and Timing Waveforms                       | 121  |

| 6.4.1.3.5.4-1 | Input Data Circuitry Read Control Logic<br>and Timing Waveforms | 124  |

| 6.4.2-1       | FRG Digital Configuration                                       | 125  |

| 6.4.2.2-1     | Daisy-Chain of the ATCRBS Fruit ARIES<br>Target Generators      | 127  |

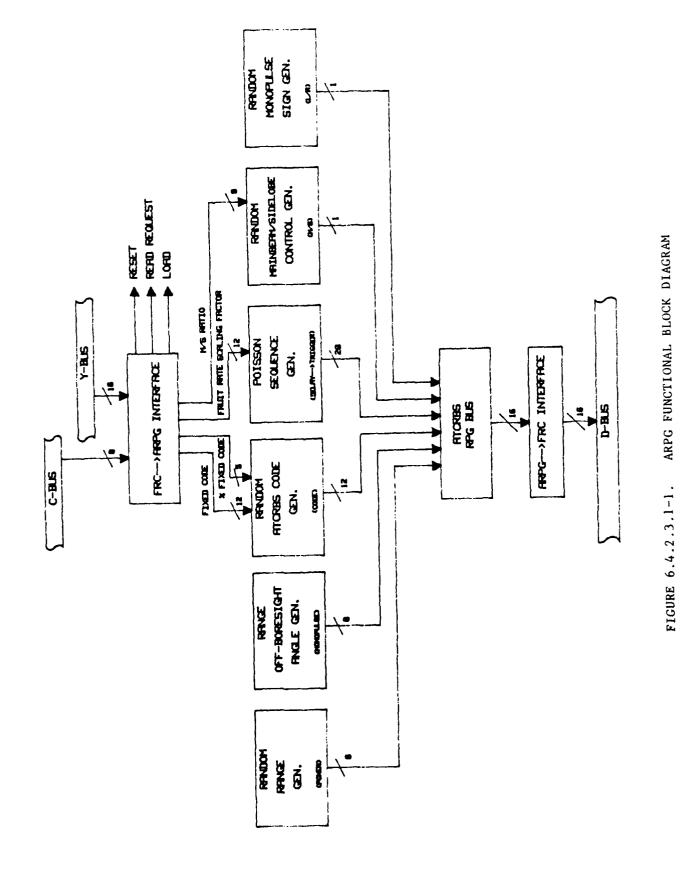

| 6.4.2.3.1-1   | ARPG Functional Block Diagram                                   | 129  |

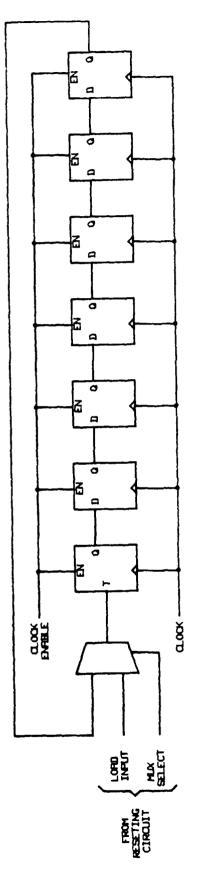

| 6.4.2.3.1.1-1 | 7-Bit Pseudo Random Number Generator (RNG2)                     | 130  |

| Figure        |                                                               | Page |

|---------------|---------------------------------------------------------------|------|

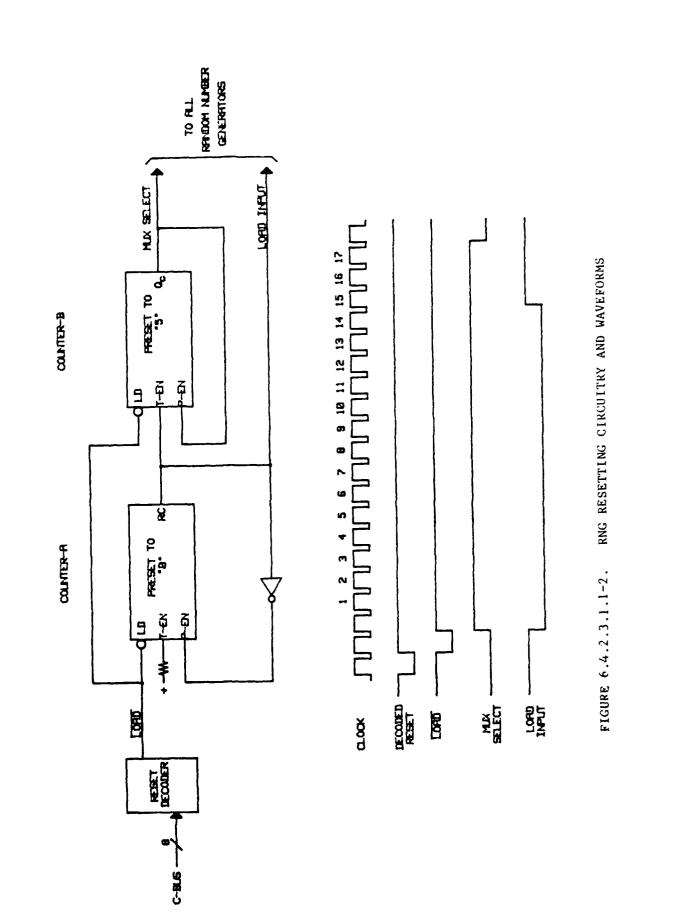

| 6.4.2.3.1.1-2 | RNG Resetting Circuitry and Waveforms                         | 131  |

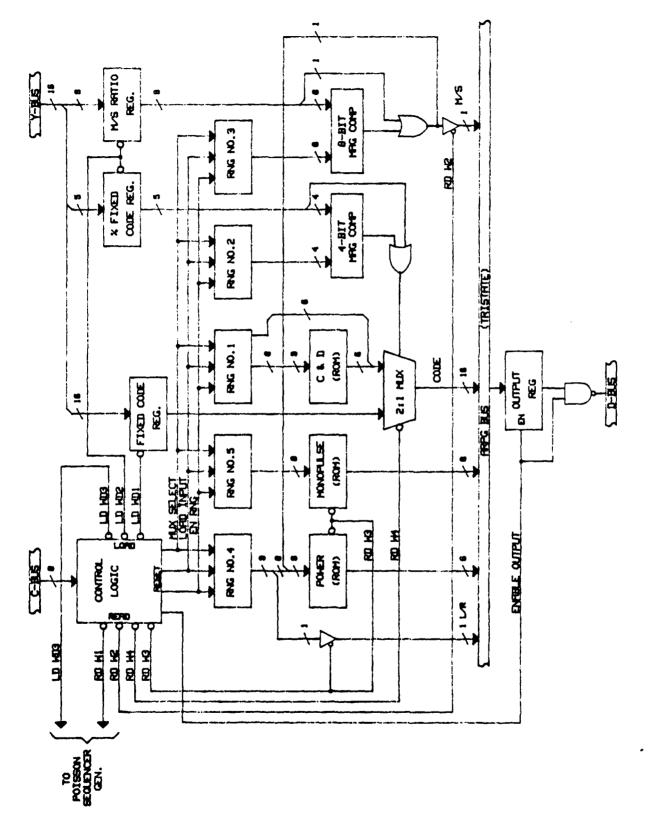

| 6.4.2.3.1.2-1 | ATCRBS Code, Range, Monopulse, L/R<br>and M/S Generators      | 133  |

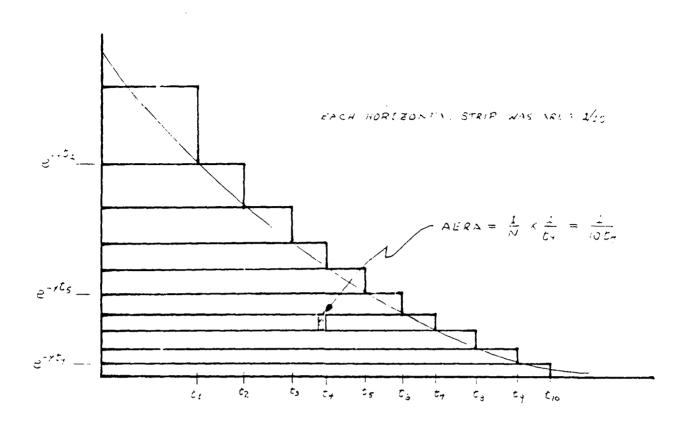

| 6.4.2.3.1.6-1 | Step Function Approximation to Exponential Curve              | 137  |

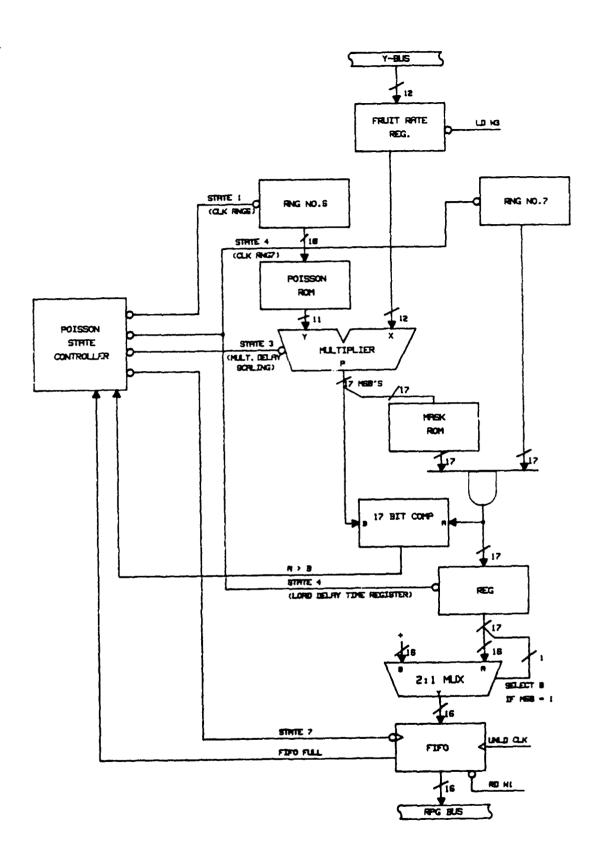

| 6.4.2.3.1.6-2 | ATCRBS Poisson Sequence Generator Block Diagram               | 139  |

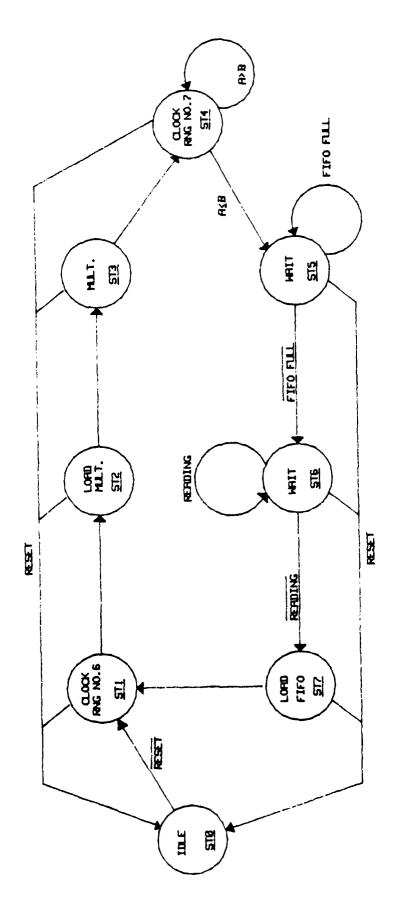

| 6.4.2.3.1.6-3 | ATCRBS Poisson Sequence Controller State Diagram              | 141  |

| 6.4.2.3.1.7-1 | Read Control Logic and Timing Waveforms                       | 142  |

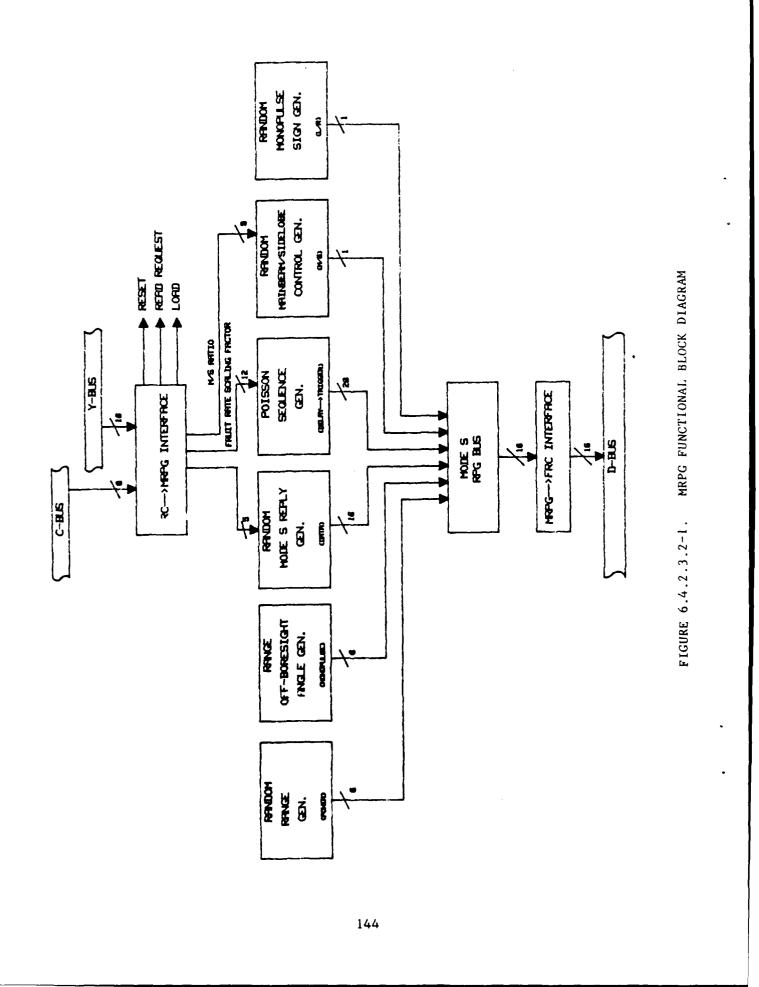

| 6.4.2.3.2-1   | MRPG Functional Block Diagram                                 | 144  |

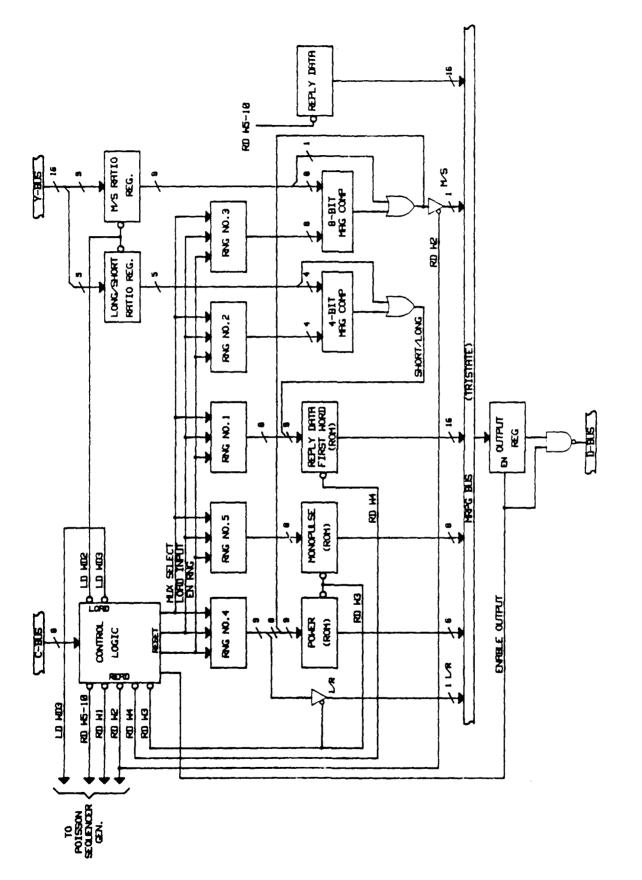

| 6.4.2.3.2.5-1 | Mode S Reply, Range, Monopulse, L/R<br>and M/S Generators     | 146  |

| 6.4.2.3.2.5-2 | Mode S Reply Information Fields and<br>Possible Data Patterns | 148  |

| 6.4.2.3.2.5-3 | Data Distribution for the First Word<br>of a Mode S Reply     | 149  |

| 6.4.2.3.2.5-4 | Mode S Data Generator Block Diagram                           | 150  |

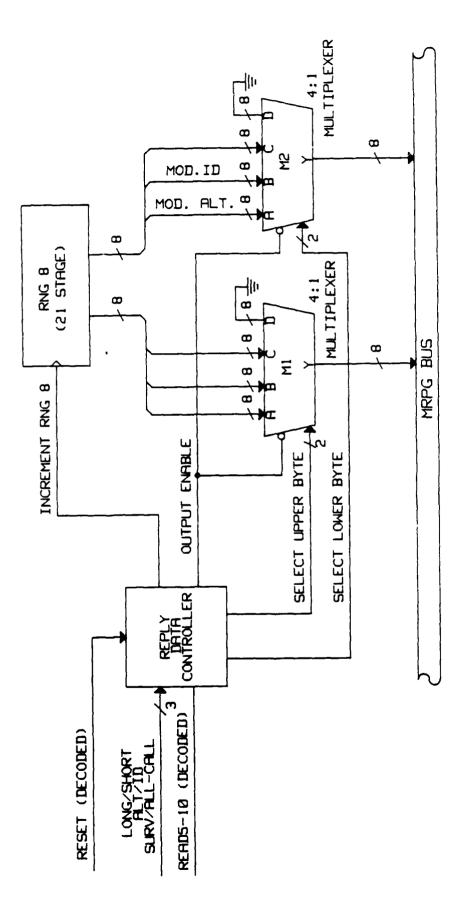

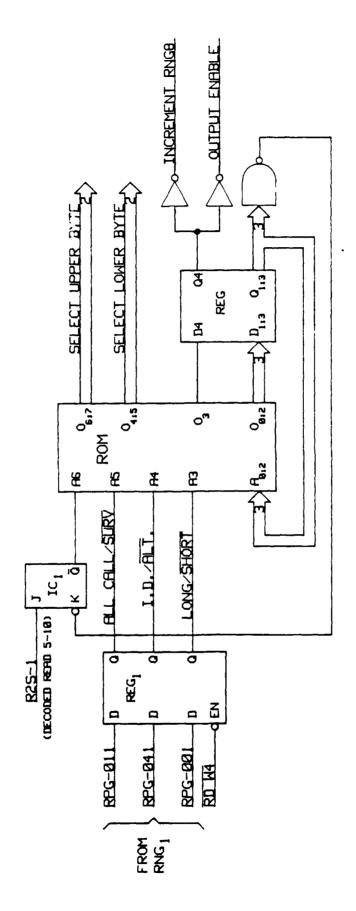

| 5.4.2.3.2.5-5 | Reply Date Controller Logic Diagram                           | 152  |

| 6.4.2.3.2.6-1 | Mode S Poisson Sequence Generator Block Diagram               | 153  |

| 6.4.2.4-1     | FRG Interface Block Diagram                                   | 155  |

| 6.4.2.4-2     | Parameter Input Channel Circuitry                             | 156  |

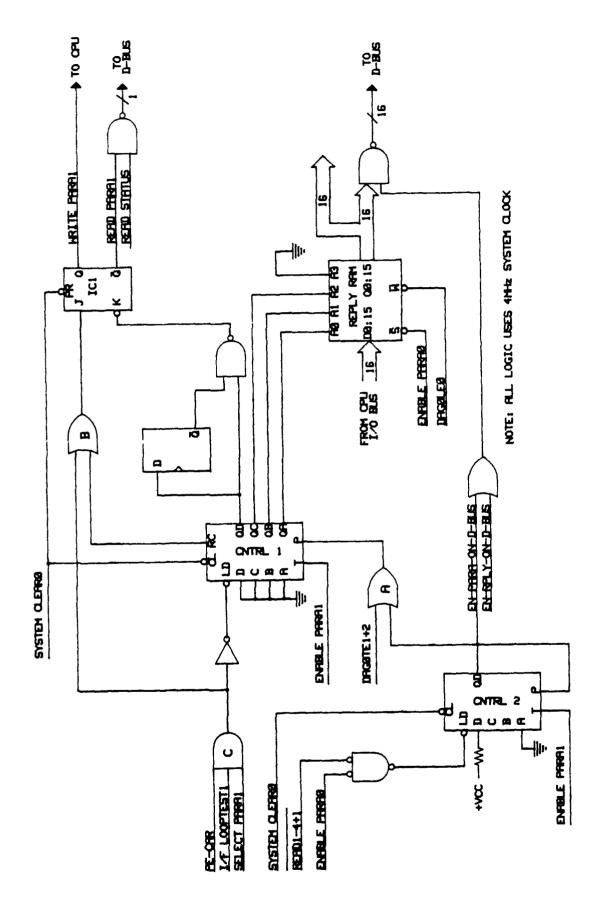

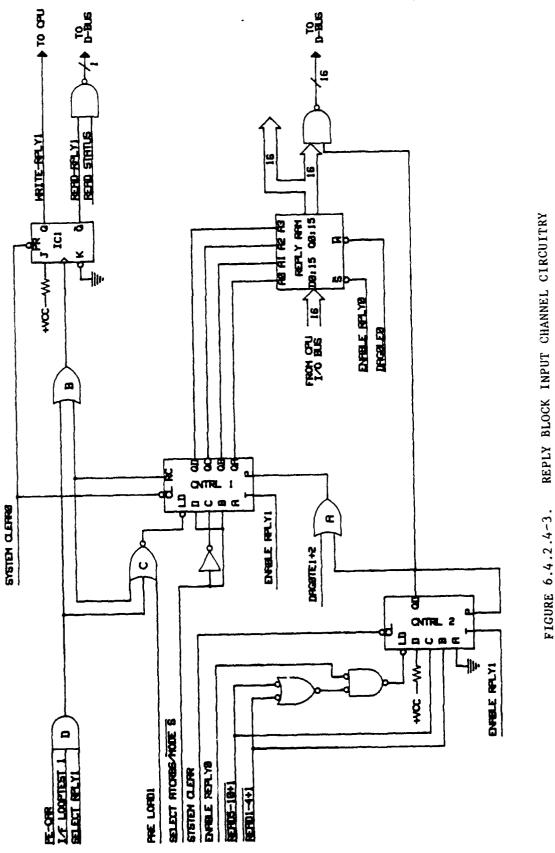

| 6.4.2.4-3     | Reply Block Input Channel Circuitry                           | 158  |

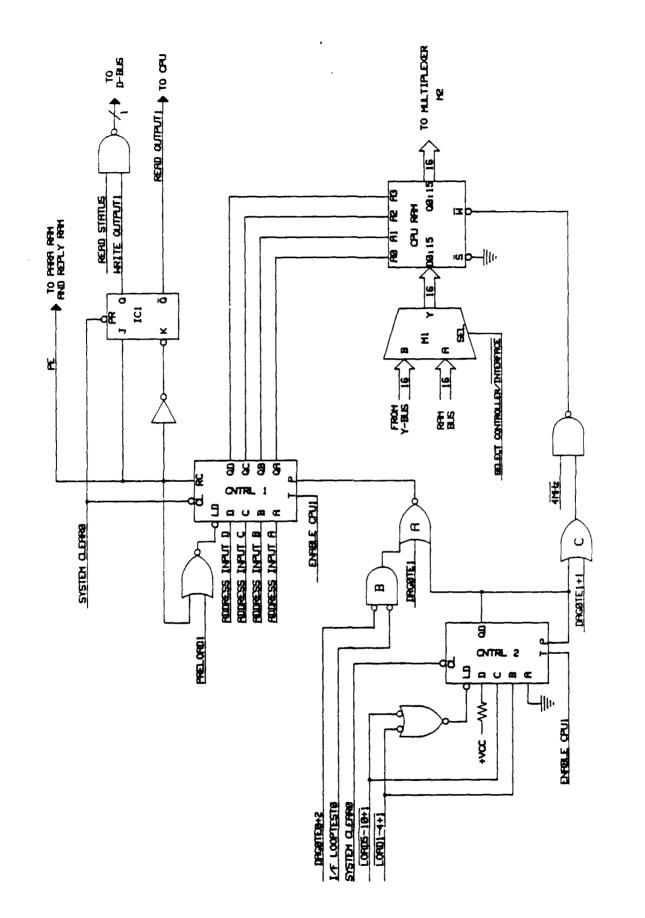

| 6.4.2.4-4     | Output Channel Circuitry                                      | 160  |

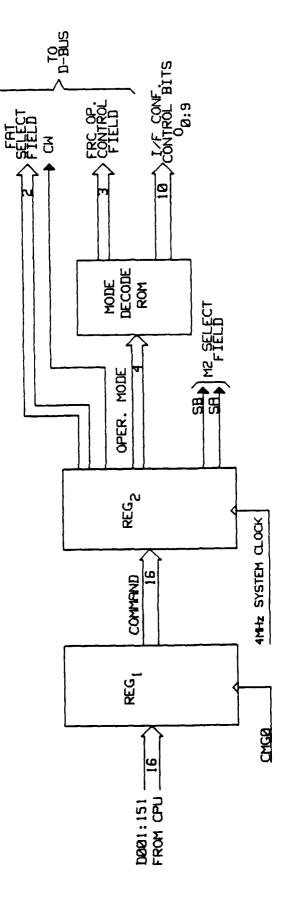

| 6.4.2.4.1-1   | Interface Mode Decoding Logic                                 | 162  |

| 6.4.2.4.2-1   | Interface Control Bus Decoding Logic                          | 166  |

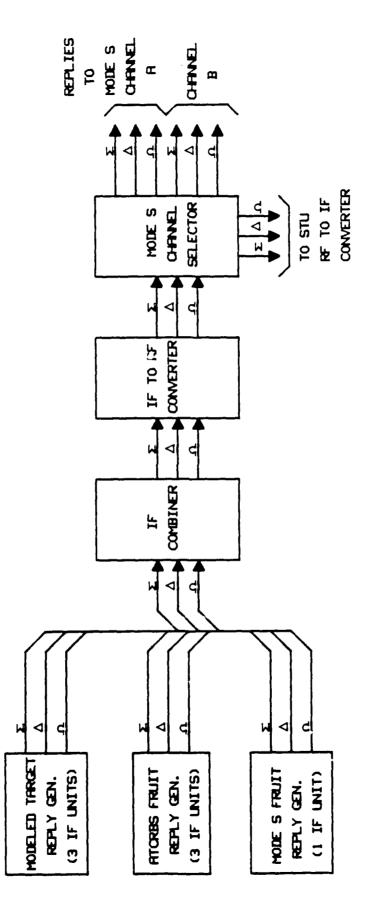

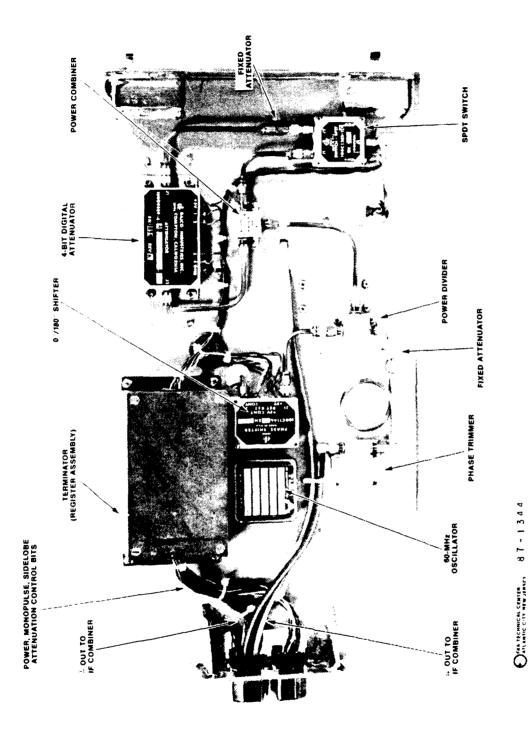

| 6.4.3-1       | Reply Generator Analog Block Diagram                          | 168  |

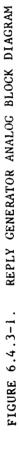

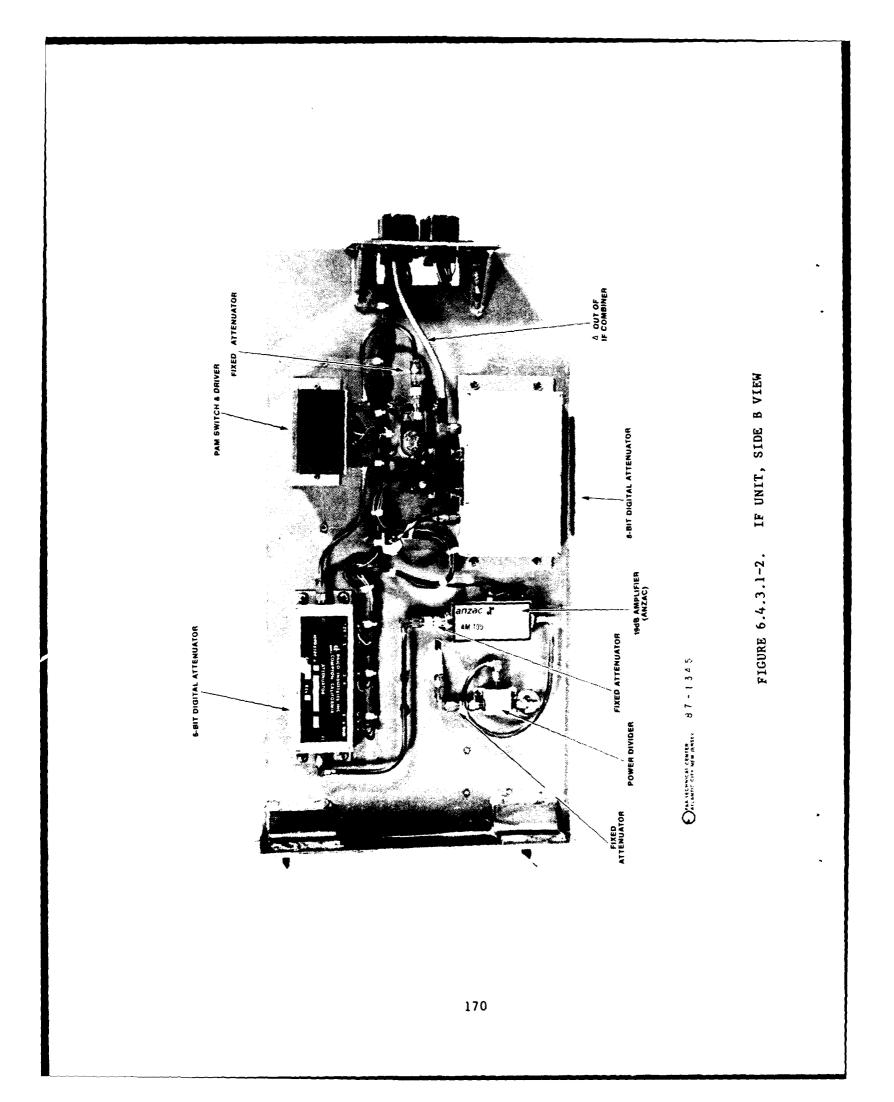

| 6.4.3.1-1     | IF Unit, Side A View                                          | 169  |

| 6.4.3.1-2     | IF Unit, Side B View                                          | 170  |

.

| Figure      |                                                                         | Page |

|-------------|-------------------------------------------------------------------------|------|

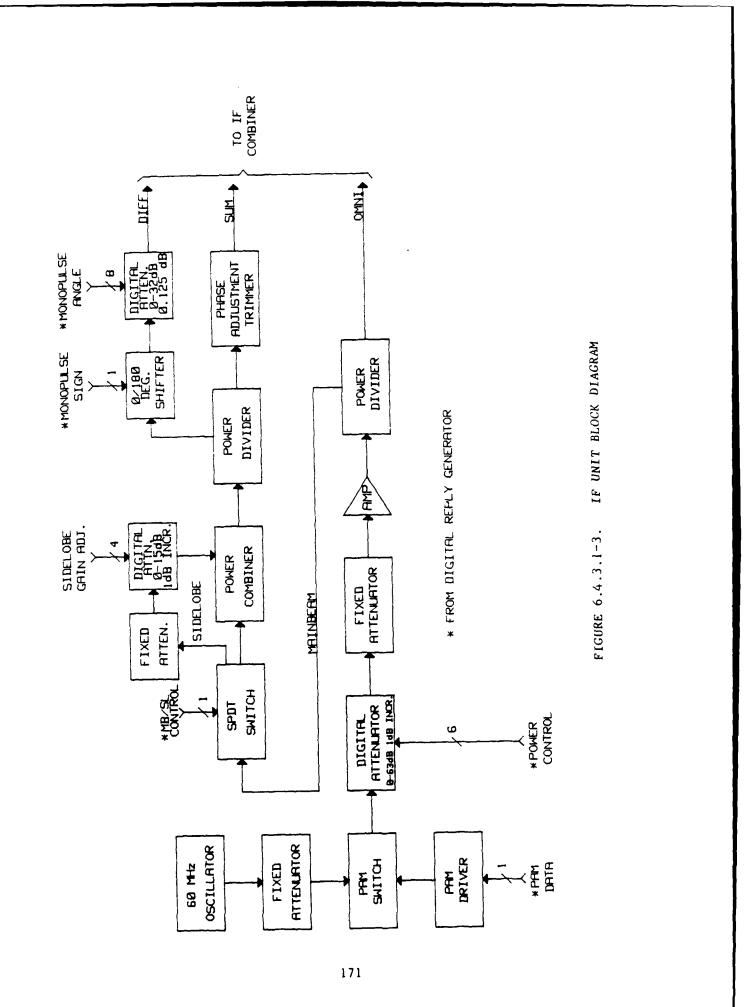

| 6.4.3.1-3   | IF Unit Block Daigram                                                   | 171  |

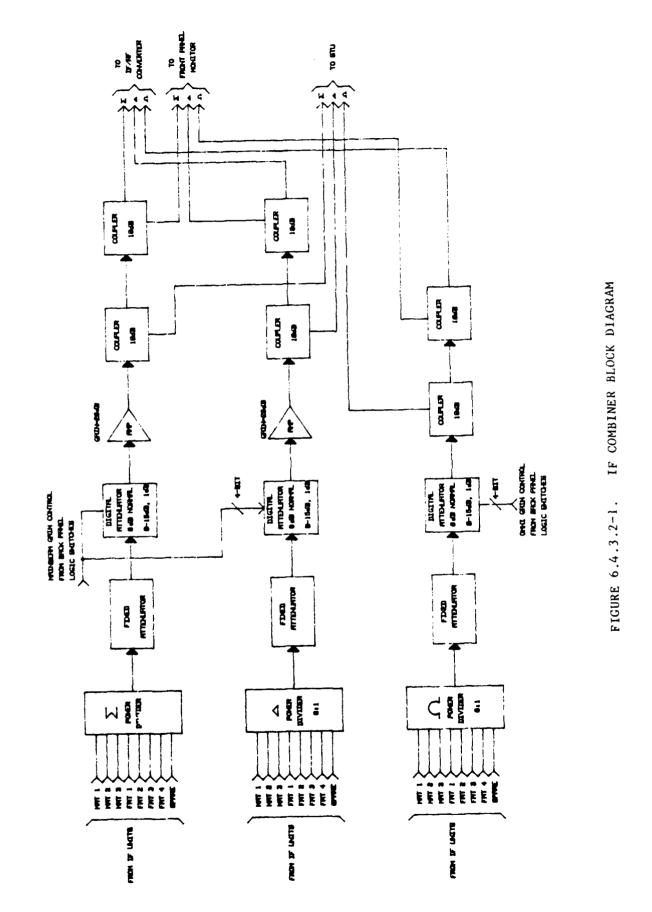

| 6.4.3.2-1   | IF Combiner Block Diagram                                               | 173  |

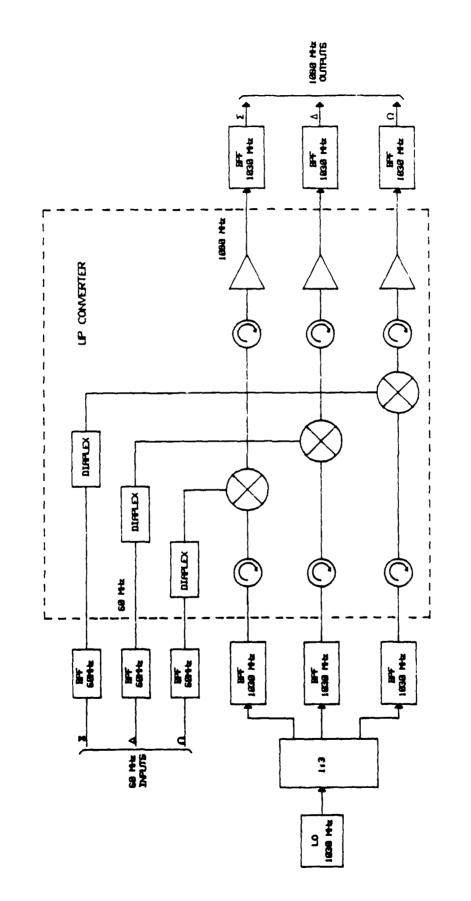

| 6.4.3.3-1   | IF to RF Converter Block Diagram                                        | 174  |

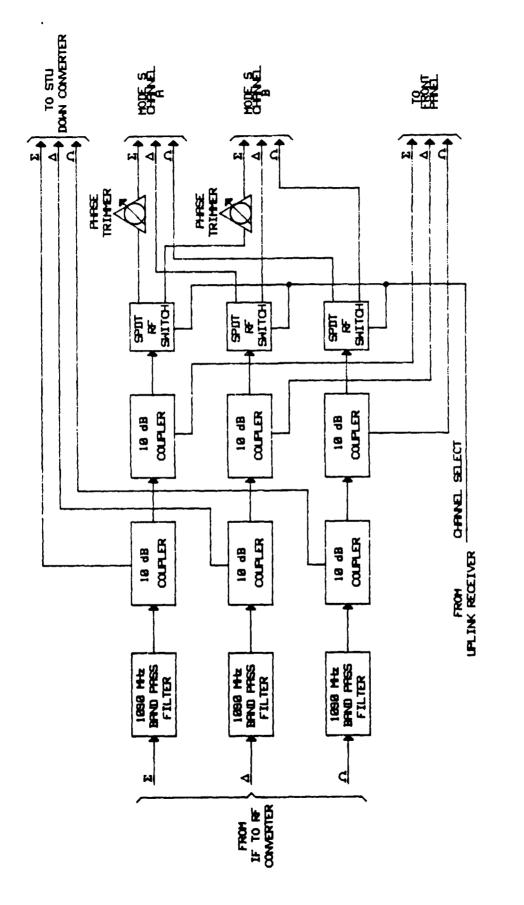

| 6.4.3.4-1   | Downlink Channel Seclector Block Diagram                                | 175  |

| 6.5-1       | UIT Block Diagram                                                       | 177  |

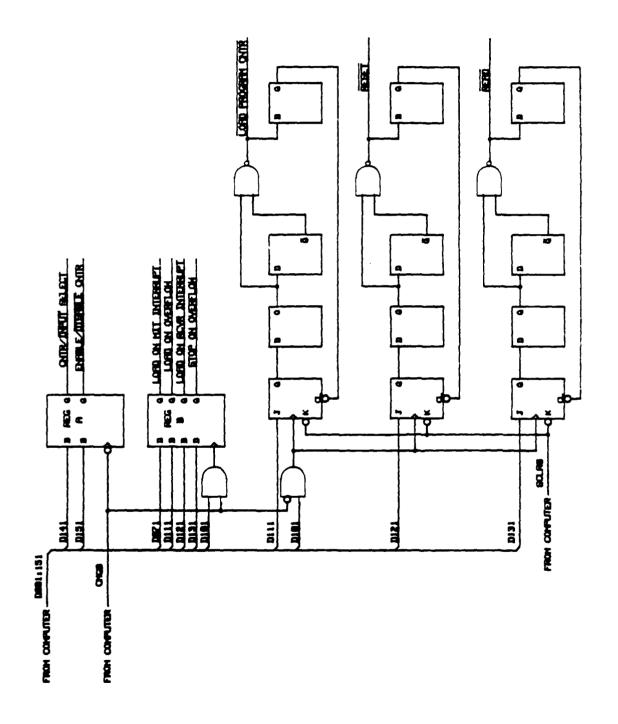

| 6.5.1-1     | UIT Command Decode Logic                                                | 180  |

| 6.6-1       | Interactive Timing Waveforms between<br>RCVR, UIT and MIT               | 182  |

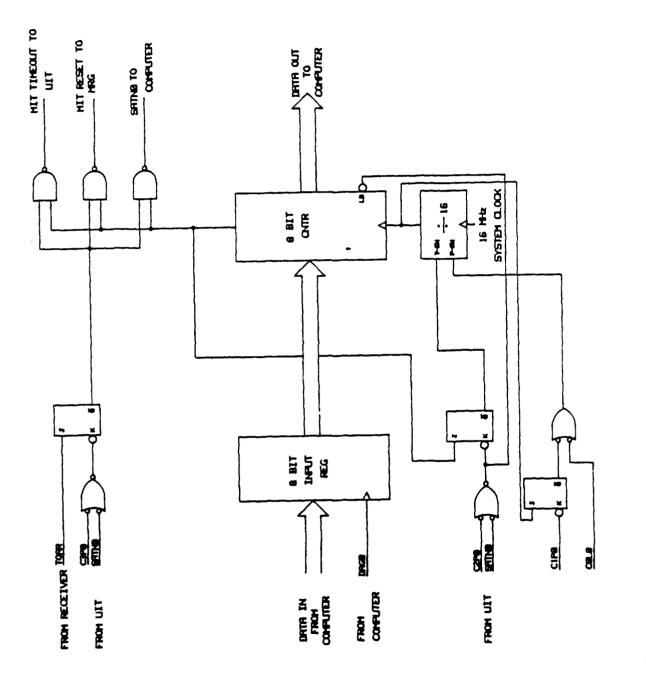

| 6.6-2       | MIT Block Diagram                                                       | 183  |

| 6.6.1-1     | MIT Command Decode Logic                                                | 185  |

| 6.7-1       | RNG Block Diagram                                                       | 185  |

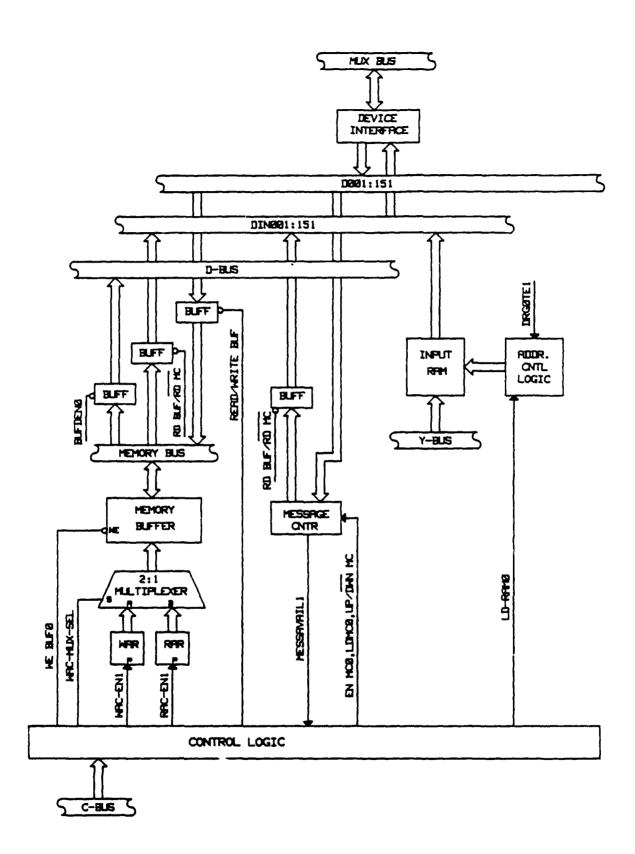

| 6.8-1       | RRG Digital Configuration                                               | 186  |

| 6.8.1-1     | RRC Output Circuitry                                                    | 187  |

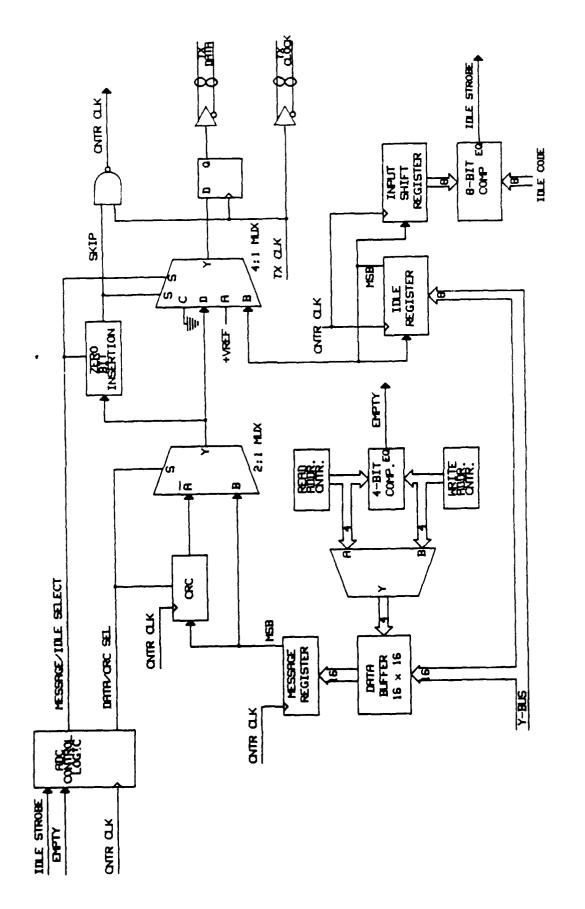

| 6.8.2.1-1   | ADC Block Diagram                                                       | 189  |

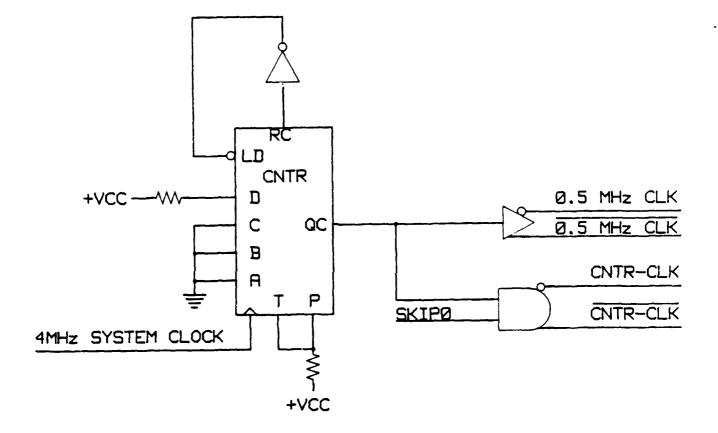

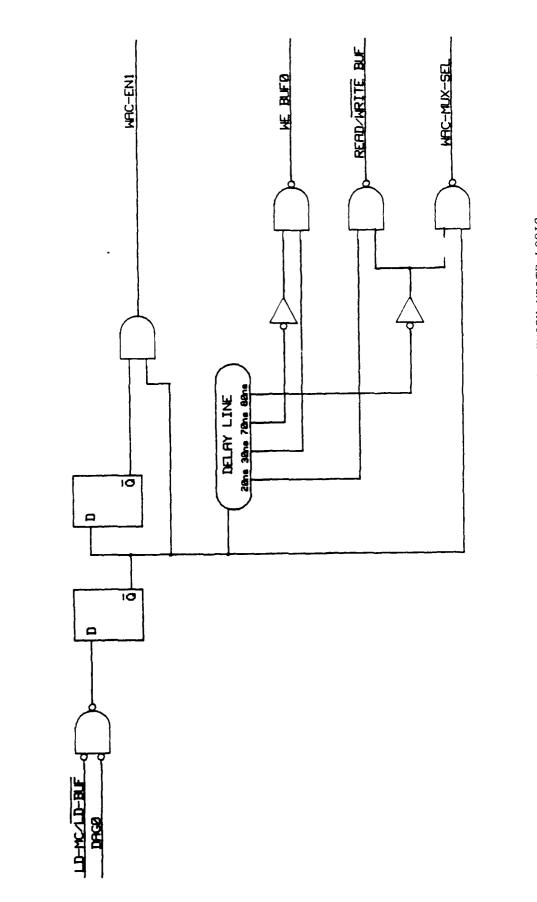

| 6.8.2.1.1-1 | Transmission Clock Logic                                                | 190  |

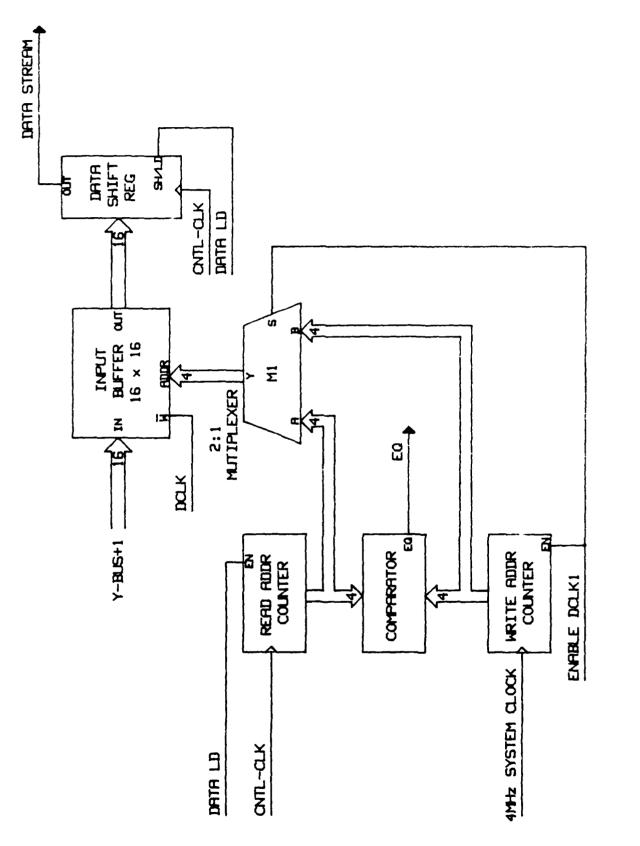

| 6.8.2.1.2-1 | Input Buffer Block Diagram                                              | 191  |

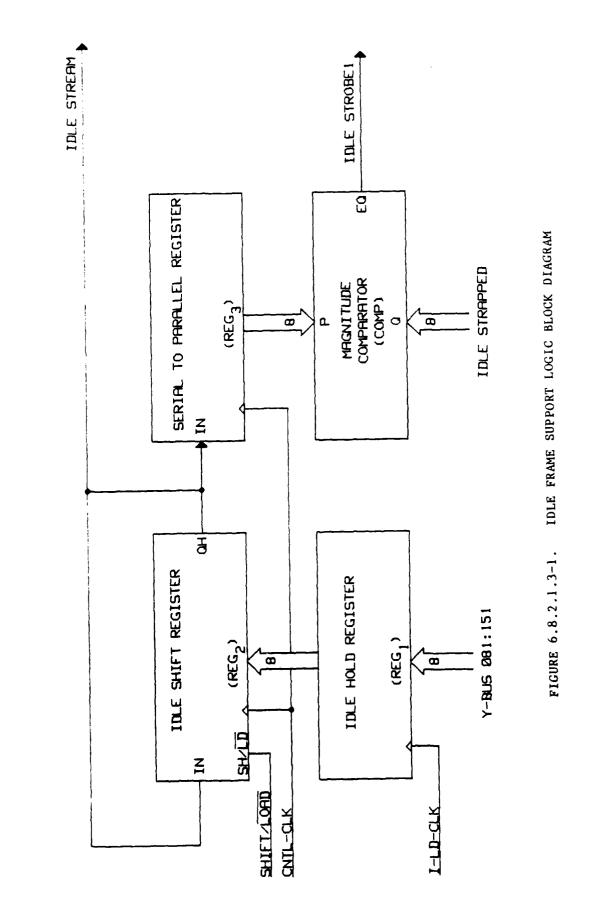

| 6.8.2.1.3-1 | Idle Frame Support Logic Block Diagram                                  | 193  |

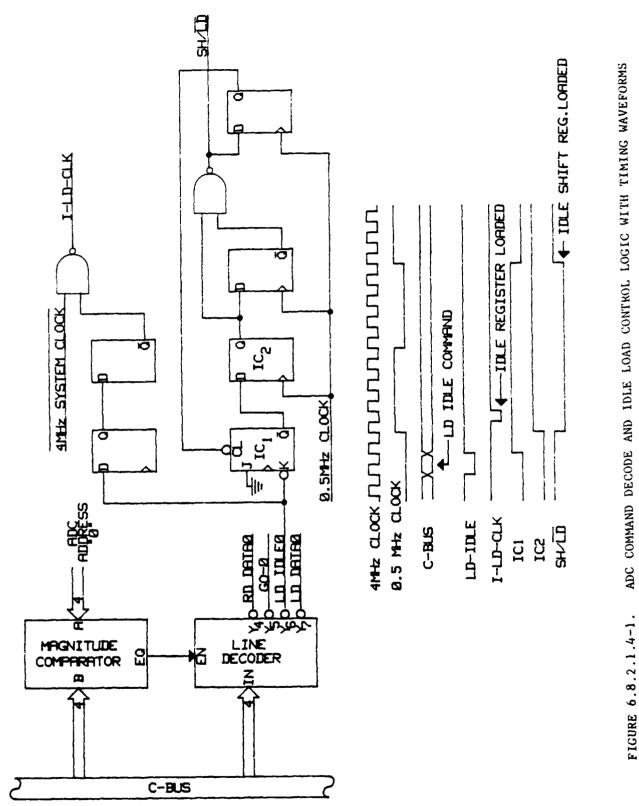

| 6.8.2.1.4-1 | ADC Command Decode and Idle Load Control<br>Logic with Timing Waveforms | 195  |

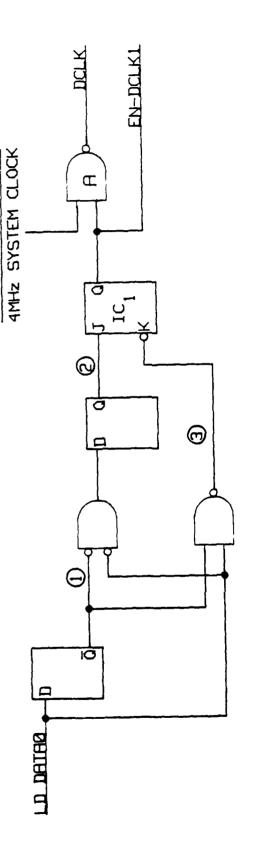

| 6.8.2.1.4-2 | Data Load Control Logic with Timing Waveforms                           | 196  |

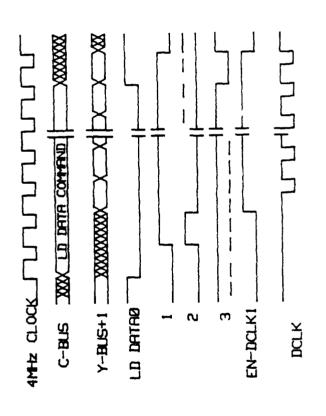

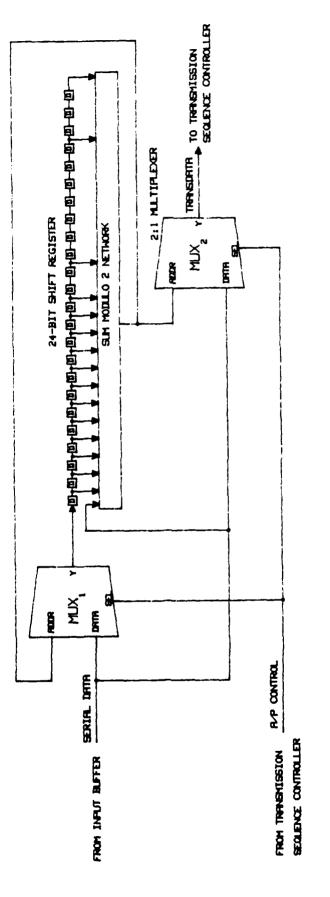

| 6.8.2.1.5-1 | FCS Generator/Checker Block Diagram                                     | 198  |

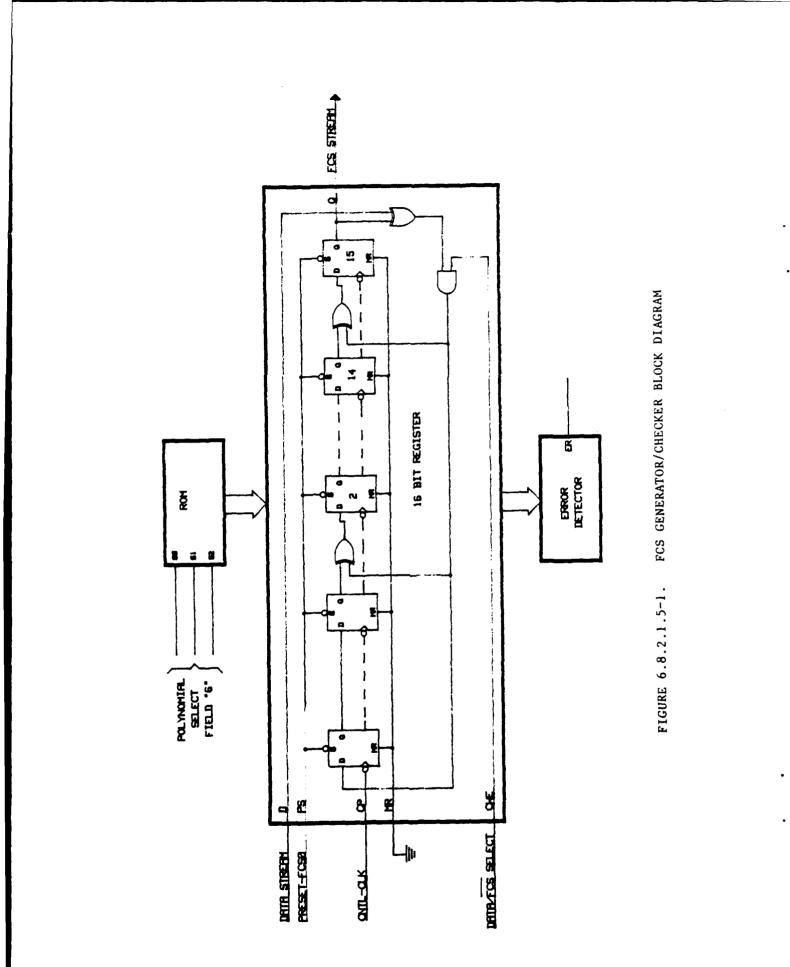

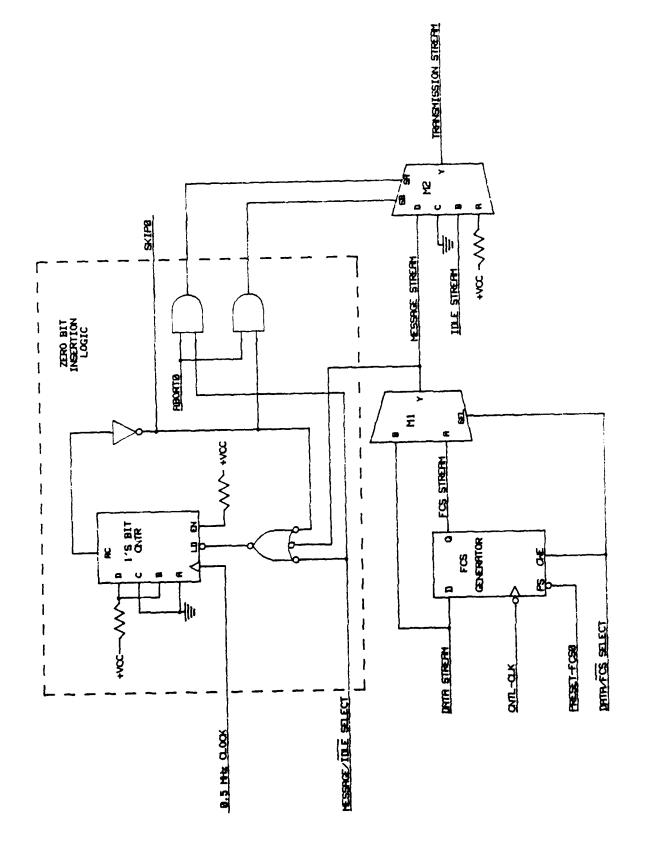

| 6.8.2.1.5-2 | FCS Generation and Zero-Bit Insertion Logic                             | 199  |

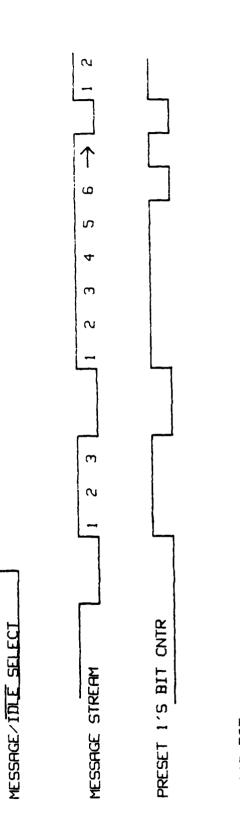

| 6.8.2.1.6-1 | Zero-Bit Insertion Timing Waveforms                                     | 200  |

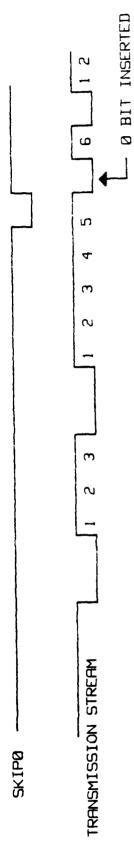

| 6.8.2.1.7-1 | ADC State Controller Block Diagram                                      | 202  |

ix

| Figure       |                                                           | Page |

|--------------|-----------------------------------------------------------|------|

| 6.8.2.1.7-2  | ADC State Controller Condition Logic                      | 203  |

| 6.8.2.1.7-3  | ADC State Controller State Diagram                        | 204  |

| 6.8.2.1.7-4  | ADC Message Transmission Timing Waveforms                 | 206  |

| 6.8.2.2-1    | ADC Diagnostic Ciruitry Block Diagram                     | 208  |

| 6.8.2.2.1-1  | ADC Diagnostic Circuitry Receiving Logic                  | 209  |

| 6.8.2.2.3-1  | ADC Diagnostic Circuitry Message Block<br>Assembly Logic  | 211  |

| 6.8.3-1      | RRG Buffer Interface Block Diagram                        | 213  |

| 6.8.3.2-1    | RRG Buffer Interface Memory Write Logic                   | 214  |

| 6.8.3.4-1    | RRG Buffer Interface Message Counter<br>and Support Logic | 215  |

| 6.8.3.6-1    | RRG Buffer Interface Operating Mode Decode Logic          | 217  |

| 6.9-1        | TOY Receiver Function Block Diagram                       | 219  |

| 6.9.2-1      | Read Ring Counter                                         | 221  |

| 6.9.4-1      | Load Ring Counter                                         | 221  |

| 6.9.5-1      | Digital Millisecond Timer Logic                           | 222  |

| 6.9.6-1      | TOY Control Logic                                         | 224  |

| 6.10-1       | STU/ARIES Configuration Block Diagram                     | 225  |

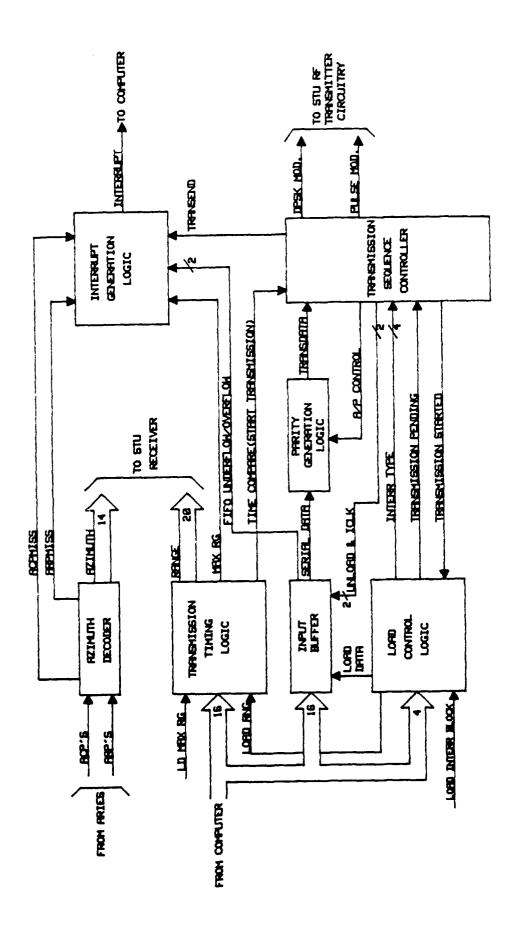

| 6.10.1.1-1   | STU Digital Transmitter Functional Block Diagram          | 227  |

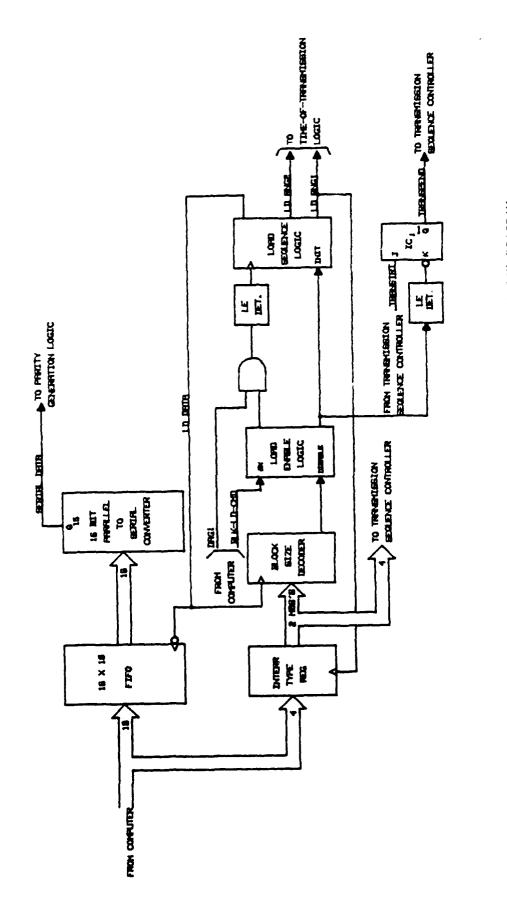

| o.10.1.1.1-1 | Input Buffer and Load Control Logic Block Diagram         | 228  |

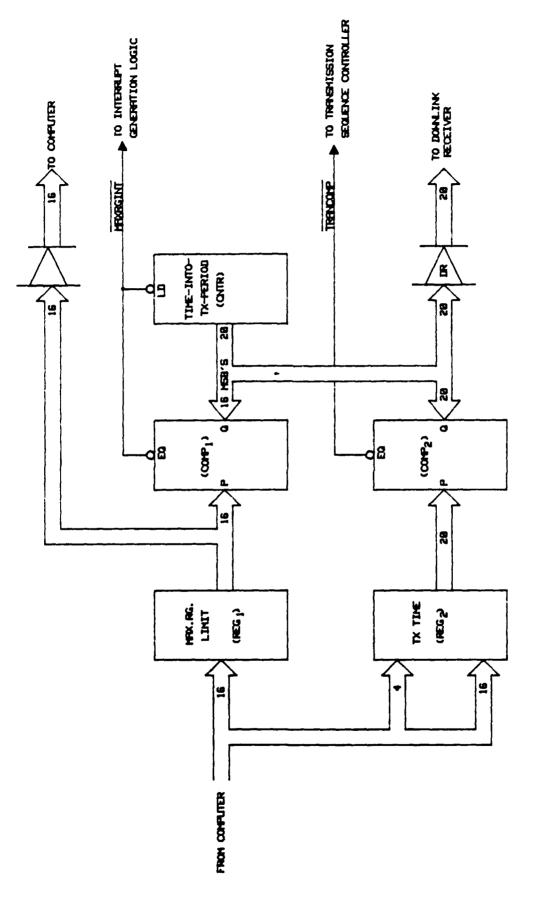

| 6.10.1.1.2-1 | Transmission Timing Logic Block Diagram                   | 230  |

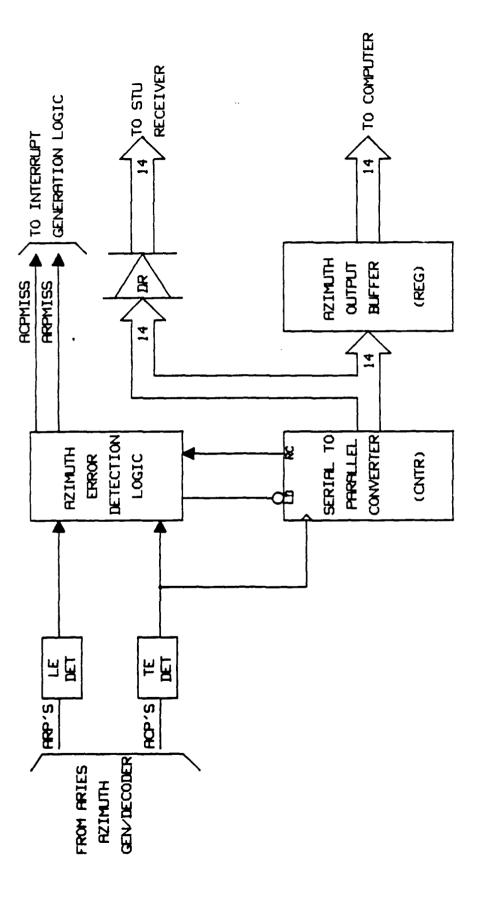

| 6.10.1.1.3-1 | Mode S Parity Encoding Logic Block Diagram                | 231  |

| 6.10.1.1.4-1 | Azimuth Decoder Logic Block Diagram                       | 233  |

| 6.10.1.1.5-1 | Transmission Sequence Controller Logic Block Diagram      | 234  |

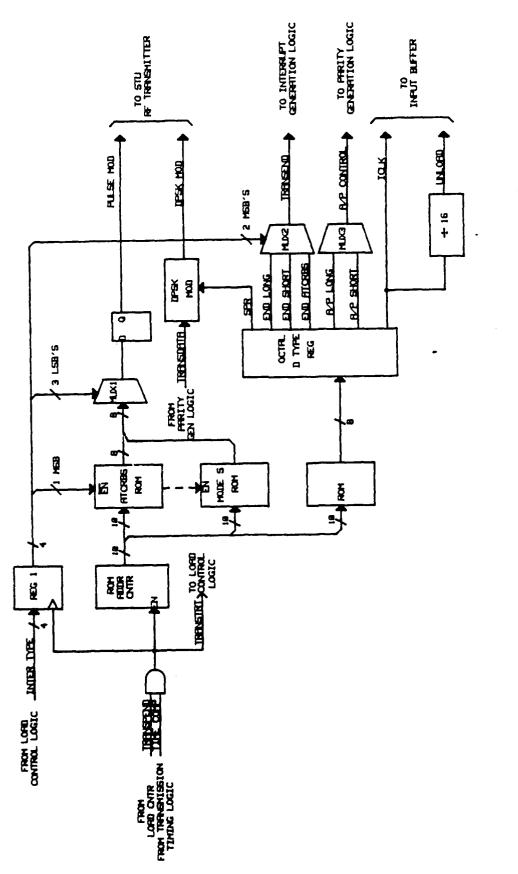

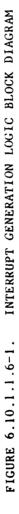

| 6.10.1.1.6-1 | Interrupt Generation Logic Block Diagram                  | 236  |

| Figure       |                                                                    | Page |

|--------------|--------------------------------------------------------------------|------|

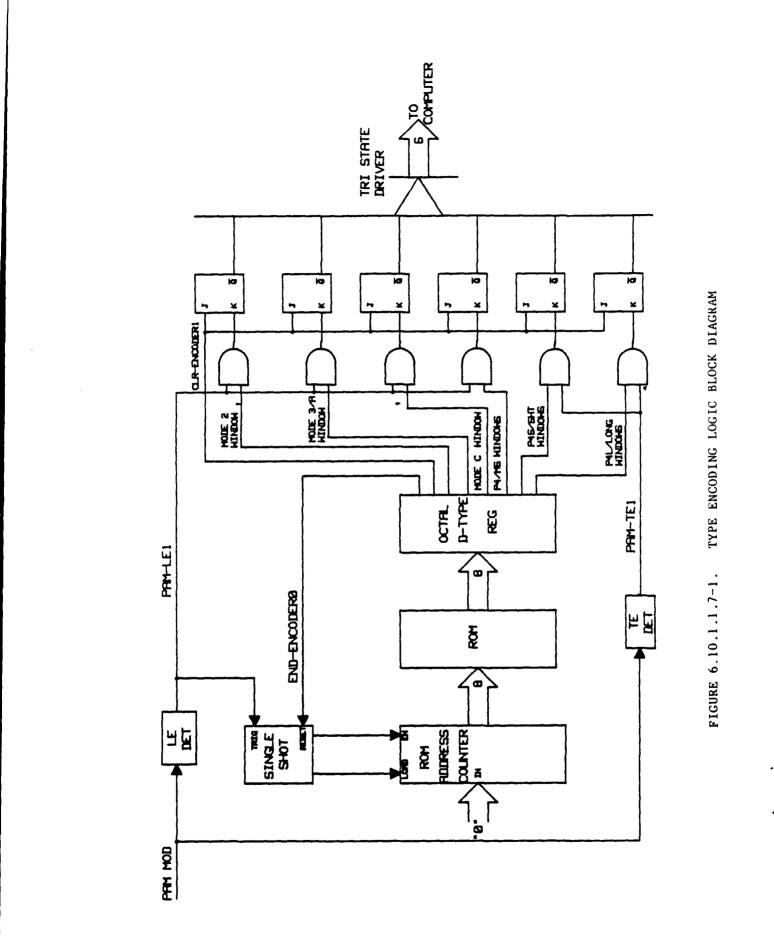

| 6.10.1.1.7-1 | Type Encoding Logic Block Diagram                                  | 238  |

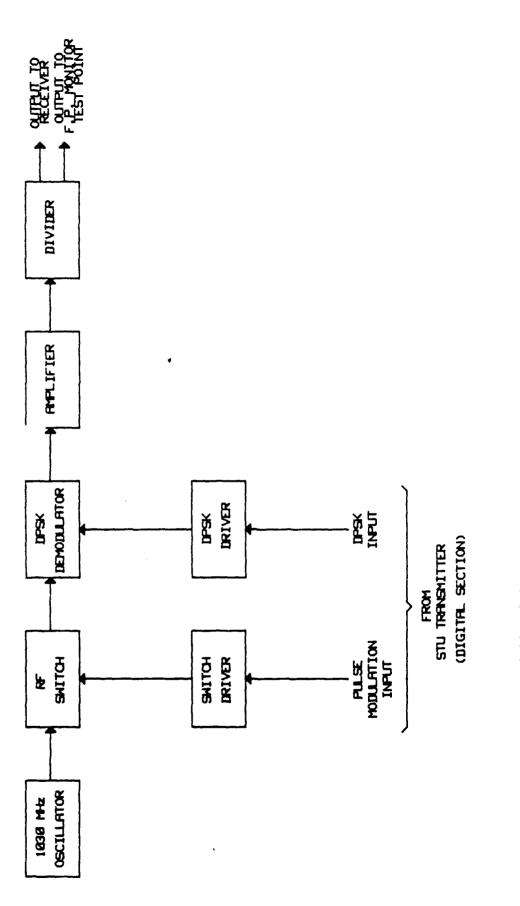

| 6.10.1.2-1   | Analog Uplink Transmitter Block Diagram                            | 240  |

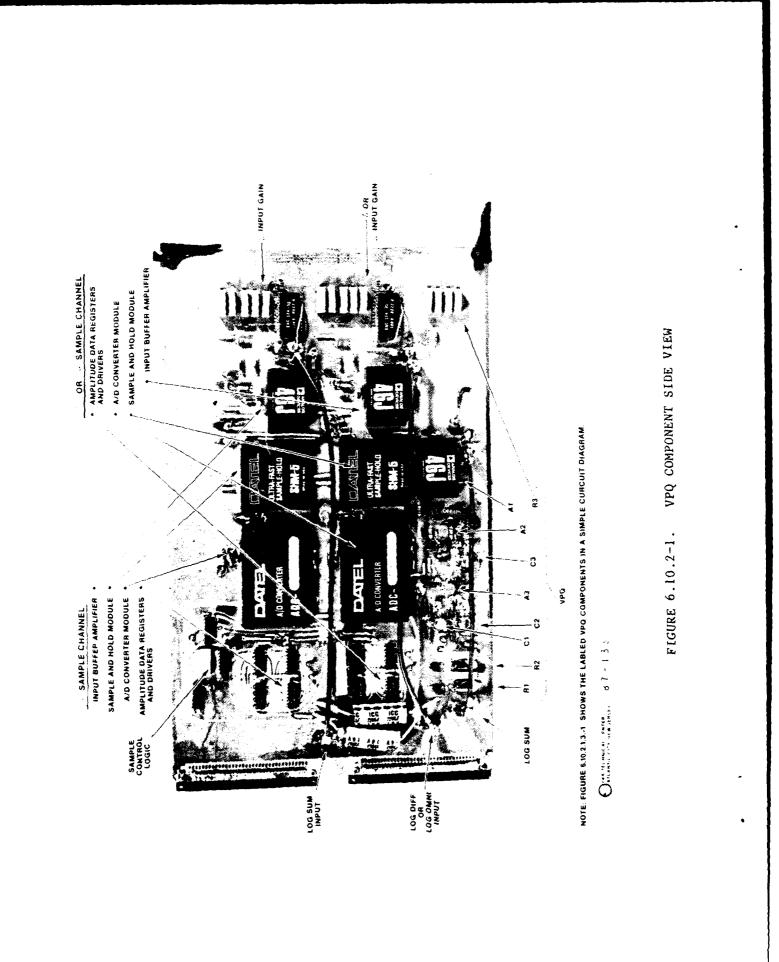

| 6.10.2-1     | VPQ Component Side View                                            | 242  |

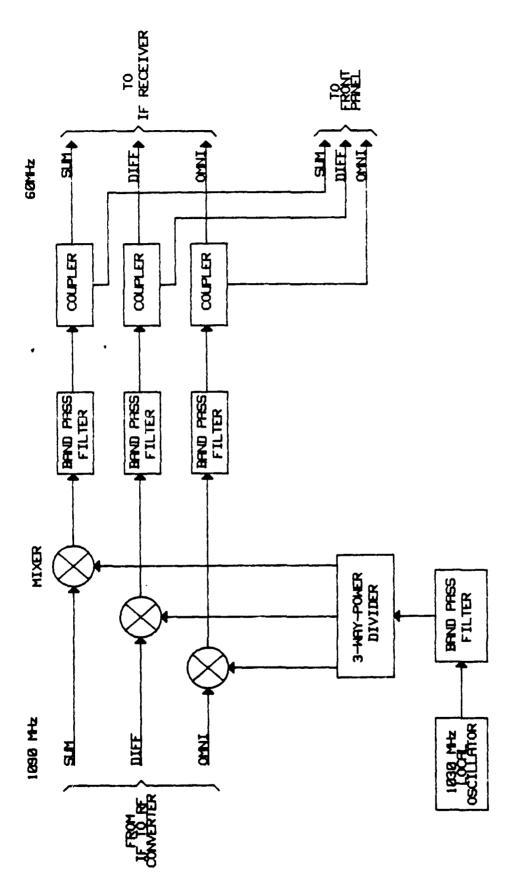

| 6.10.2.1.1-1 | RF to IF Converter Block Diagram                                   | 243  |

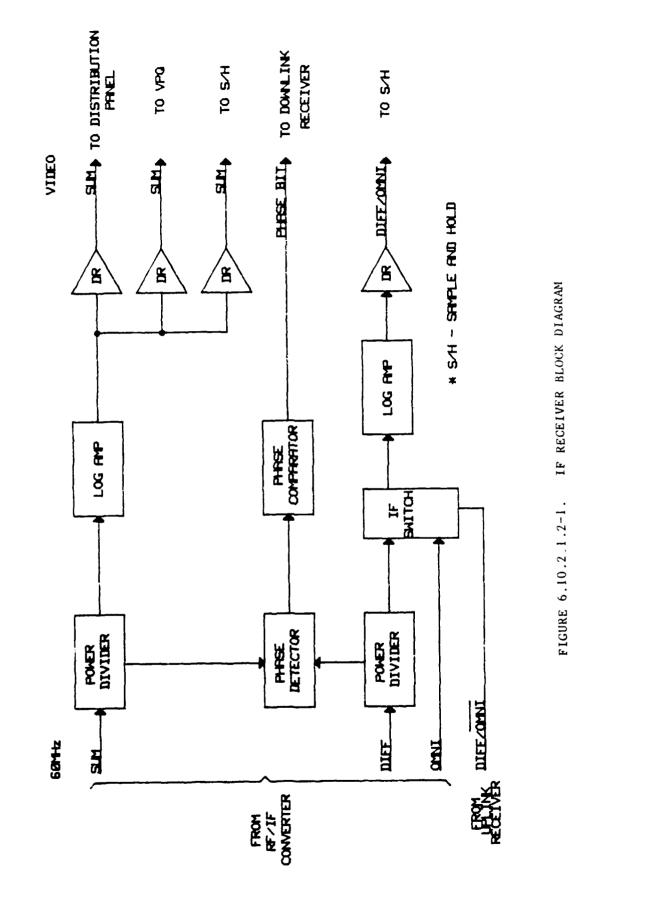

| 6.10.2.1.2-1 | IF Receiver Block Diagram                                          | 245  |

| 6.10.2.1.3-1 | Simplified Diagram of VPQ Circuitry                                | 246  |

| 6.10.2.1.3-2 | VPQ Waveforms                                                      | 247  |

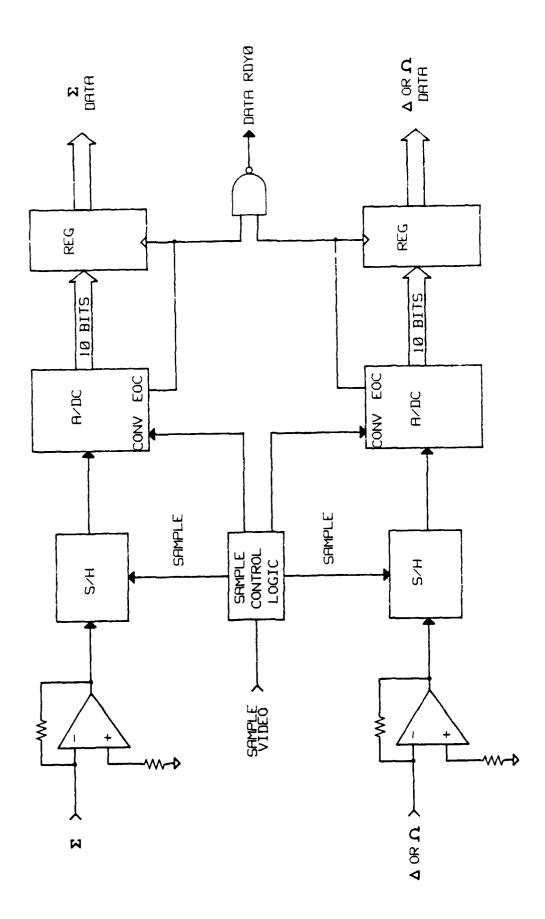

| 6.10.2.1.4-1 | Simplified Diagram of the Dual Channel Video<br>Sampling Circuitry | 249  |

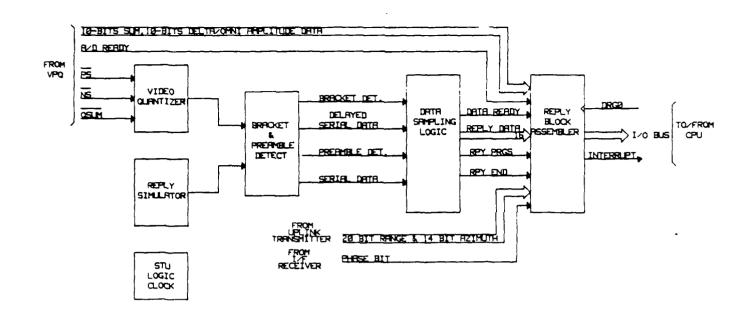

| 6.10.2.2-1   | Digital Downlink Receiver Block Diagram                            | 251  |

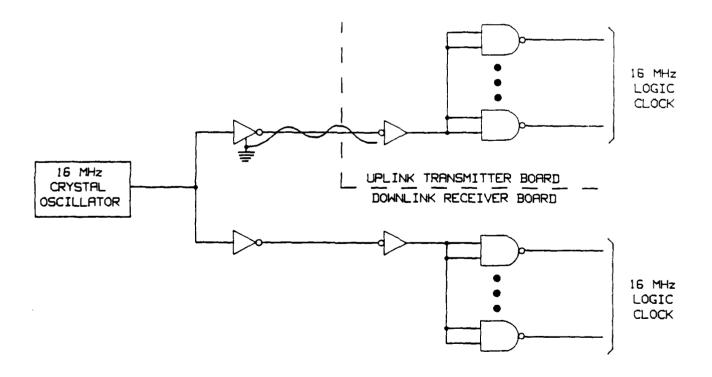

| 6.10.2.2.1-1 | STU Clock Logic                                                    | 251  |

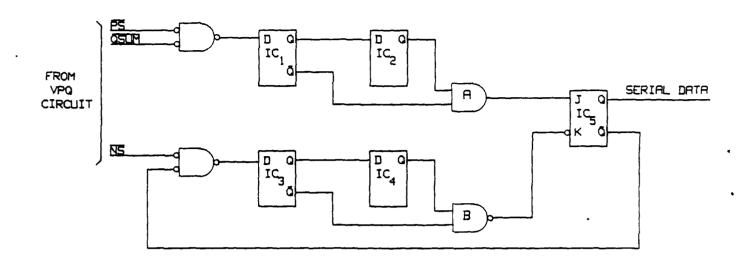

| 6.10.2.2.2-1 | Video Digitizer                                                    | 252  |

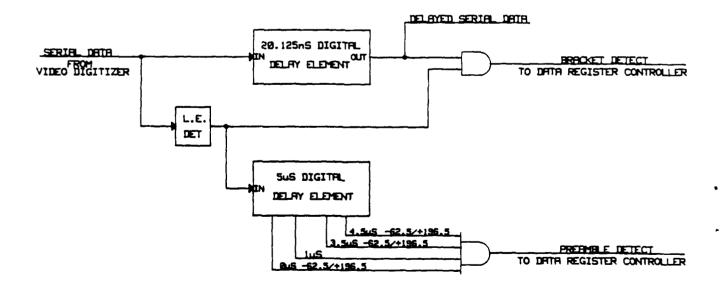

| 6.10.2.2.3-1 | Bracket and Preamble Detection Logic                               | 252  |

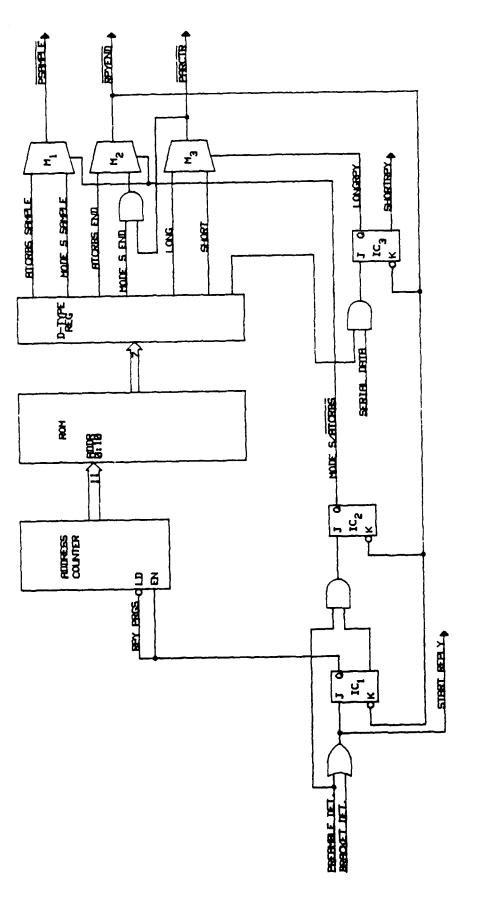

| 6.10.2.2.4-1 | Data Sampling Controller                                           | 254  |

| 6.10.2.2.4-2 | Data Sampling Logic                                                | 255  |

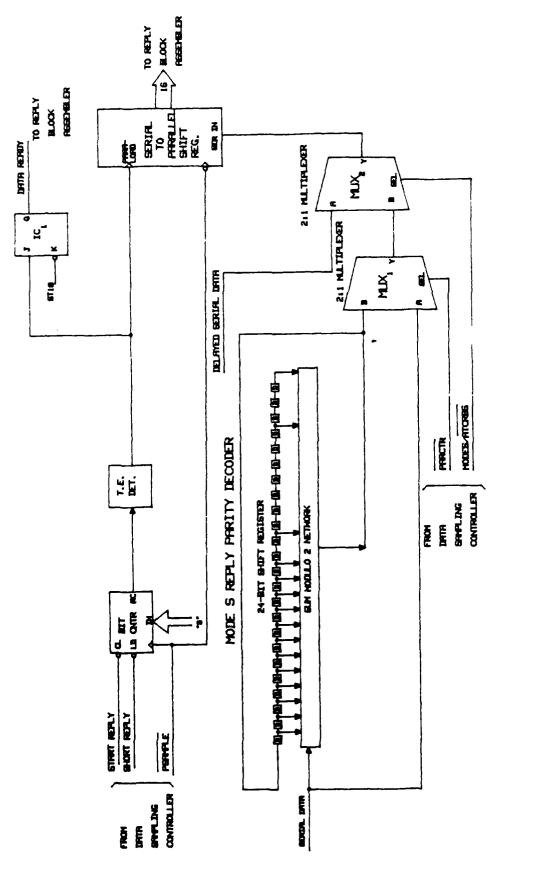

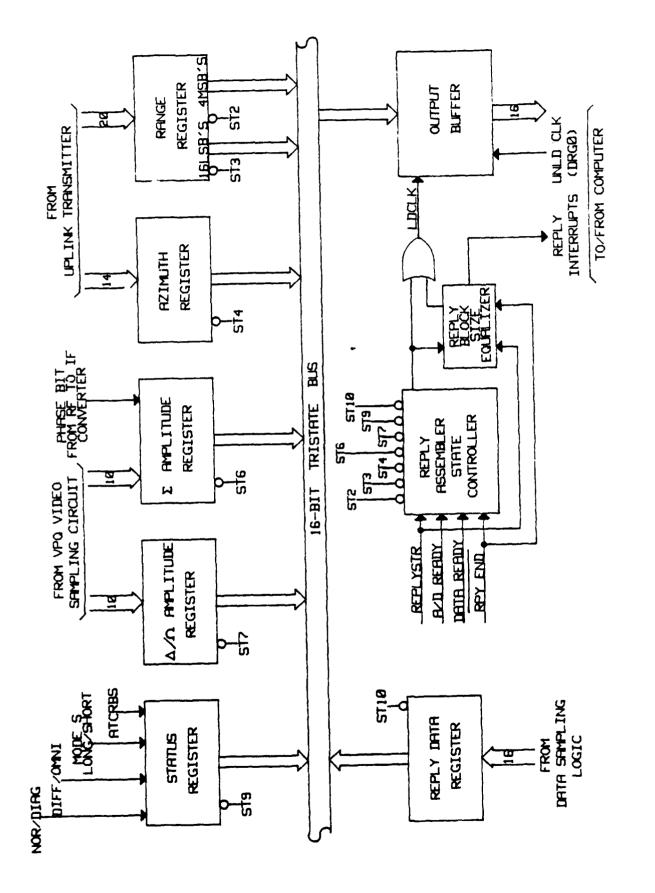

| 6.10.2.2.5-1 | Reply Assembly Block Diagram                                       | 256  |

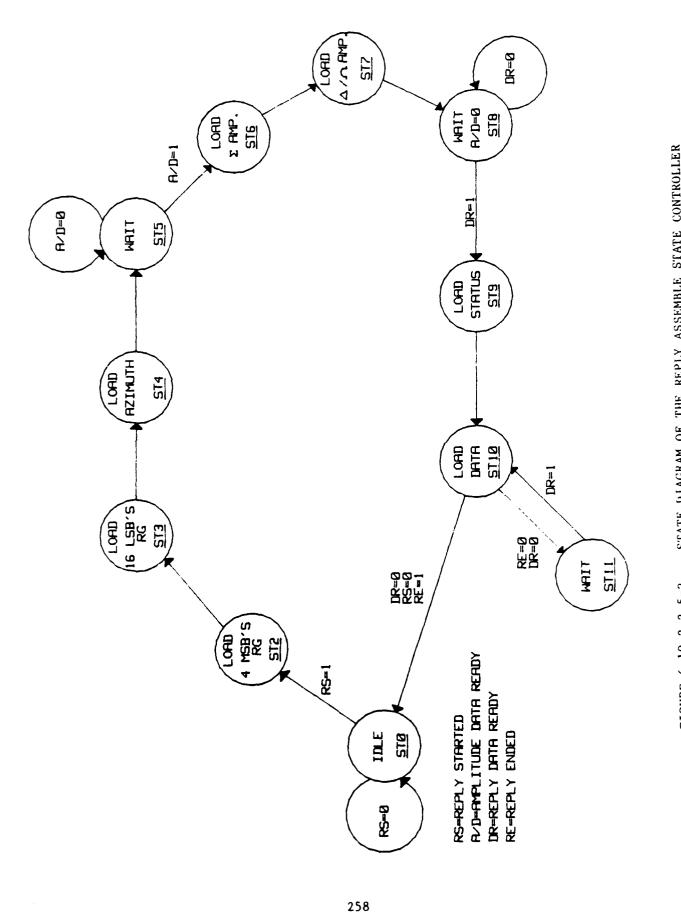

| 6.10.2.2.5-2 | State Diagram of the Reply Assemble<br>State Controller            | 258  |

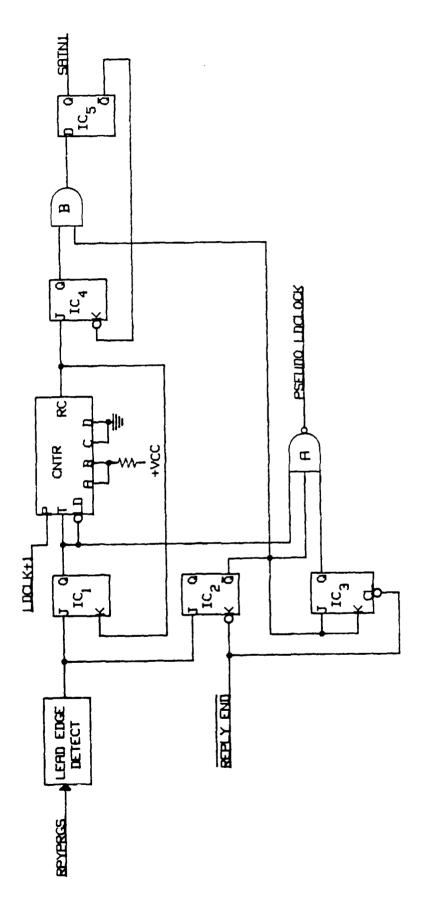

| 6.10.2.2.5-3 | Reply Block Size Equalizer Logic                                   | 260  |

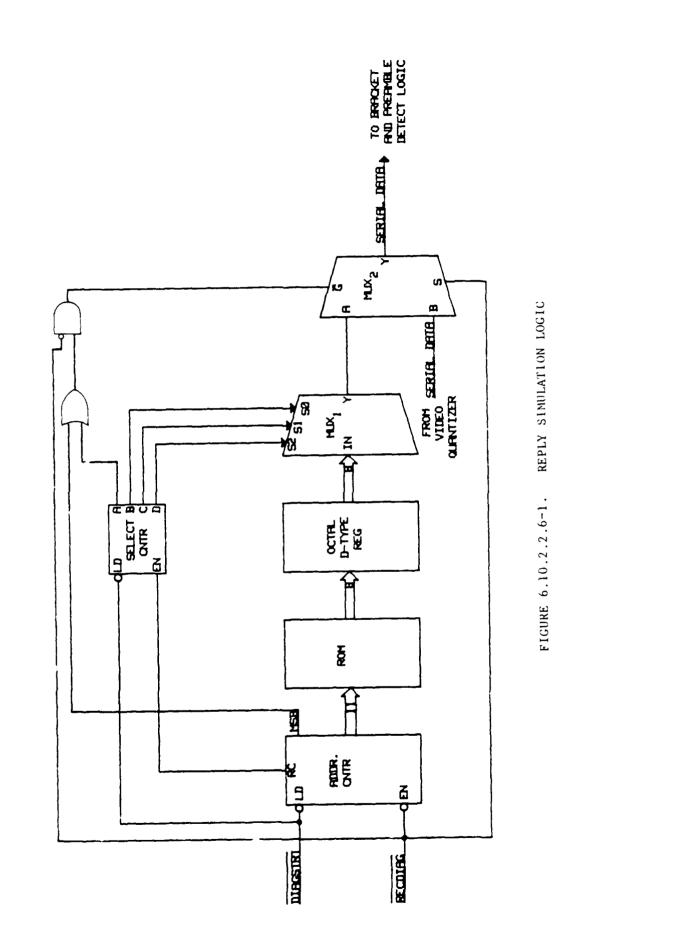

| 6.10.2.2.6-1 | Reply Simulation Logic                                             | 261  |

xi

# LIST OF TABLES

| Table         |                                                      | Page |

|---------------|------------------------------------------------------|------|

| 5-1           | Salient Characteristics of Peripherals Used in ARIES | 13   |

| 5-2           | ARIES Digital Chassis Board Slot Assignments         | 16   |

| 5-3           | Break-Point Panel Connectors                         | 19   |

| 5-4           | Distribution Panel Connectors                        | 21   |

| 6-1           | Interrupt Command Structure                          | 28   |

| 6.2.2.1-1     | Terminal (Single Antenna) Configuration              | 36   |

| 6.2.2.1-2     | En Route (Dual Antenna) Configuration                | 36   |

| 6.2.2.3-1     | Interrogation Mode Encoder ROM                       | 43   |

| 6.4.1.1.2-1   | ALU Source Control                                   | 69   |

| 6.4.1.1.2-2   | ALU Operation Control                                | 71   |

| 6.4.1.1.2-3   | ALU Destination Control                              | 73   |

| 6.4.1.1.3-1   | Branch Control Functions                             | 76   |

| 6.4.1.1.4-1   | Microcontroller Instruction Set                      | 78   |

| 6.4.1.1.7-1   | MRC Microcode Commands                               | 83   |

| 6.4.1.2.2.3-1 | State Controller No. 3 Start Address Table           | 98   |

| 6.4.1.2.3-2   | Timing for an ATCRBS Reply                           | 105  |

| 6.4.1.3.5-1   | MRG Mode-of-Operation Control Field                  | 120  |

| 6.4.1.3.5.4-1 | MAT Selection Control Field                          | 123  |

| 6.4.2.4.1-1   | Mode Decode Configurator ROM                         | 161  |

| 6.4.2.4.2-1   | Device Address and OP Code for the FRG Interface     | 167  |

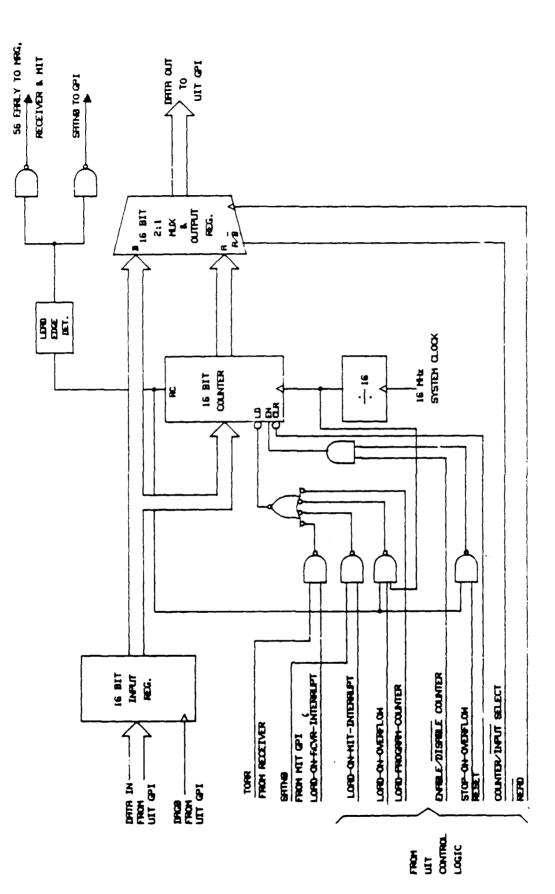

| 6.5-1         | UIT Command Bit Operations                           | 178  |

| 6.8.2.1.4-1   | Device Address and OP Code for the ADC               | 194  |

| 6.8.3.6-1     | RRG Mode-of-Operation Control Field                  | 216  |

| 6.10.1.1.6-1  | Interrupts Generated by the Uplink Transmitter       | 235  |

| 6.10.1.1.7-1  | Encoded Type Interrogation Table                     | 239  |

| 6.10.2.2.6-1  | Onboard Simulated Replies                            | 262  |

#### EXECUTIVE SUMMARY

The Aircraft Reply and Interference Environment Simulator (ARIES) is a stand-alone target simulation system designed and fabricated at the Federal Aviation Administration (FAA) Technical Center to analyze the performance characteristics of the Mode Select (Mode S) Beacon System sensor operating within capacity and high density beacon environments. A total of four ARIES systems have been fabricated to support the development of the Mode S sensor during its production phases. In addition, the ARIES will be used to support acceptance testing to be conducted by the FAA.

Volume I of the Hardware Principles of Operation Manual introduces the user to the special purpose hardware developed for the ARIES. This manual gives the user an overview of its functions and capabilities. ARIES hardware operations are described in sufficient detail, with the assistance of block diagrams, logic diagrams, and flow charts, for a user familiar with analog and digital hardware to maintain the system with the use of the ARIES diagnostic package.

#### 1. INTRODUCTION.

This manual is a general user guide describing the principles of operation of the Aircraft Reply and Interference Environment Simulator (ARIES) special purpose hardware. This hardware was designed and fabricated by Federal Aviation Administration (FAA) Technical Center personnel. The hardware description of off-the-shelf equipment employed in ARIES, such as computer systems, printers, disk drives, etc., is covered by the appropriate manufacturer's hardware manuals and will be addressed only at the level necessary to provide an overall understanding of the ARIES as a system.

A general background for the purpose of ARIES is given in section 2. Reference documents and other related manuals are listed in section 3. Capabilities of the ARIES system are summarized in section 4. The physical and functional layout of the ARIES system is described in section 5, and the principles of operation of each of the special purpose hardware devices used in ARIES are explained in section 6. These sections, along with the appendixes of this manual, provide enough background information for a person experienced in digital and analog hardware design to use hardware drawings to perform repair and/or calibration on the ARIES special purpose hardware 'when necessary.

# 2. BACKGROUND.

The FAA is currently improving the National Airspace System (NAS) to keep pace with the projected traffic growth through the year 2000. One major element in this improvement effort is the deployment of a new secondary radar system referred to as the Mode Select (Mode S) Beacon System. The Mode S sensor works in conjunction with airborne transponders to obtain information on aircraft identity and altitude, and serves as the basis for digital communications between the ground system and the aircraft.

In 1986, the FAA awarded a contract for the procurement of 137 Mode S sensors to be installed in the more busier air traffic locations. These sensors will provide increased target capacity handling, better azimuth measurement precision, and reduced interference between sensors due to reduced interrogation rates as compared to the current Air Traffic Control Radar Beacon System (ATCRBS).

Due to the large target capacity of the new technological ground-based surveillance system, the FAA recognized that it was not possible to find a current beacon environment that is dense enough to fully test the Mode S sensor under heavy load conditions. Furthermore, a Mode S transponder environment does not exist currently, and so it is not possible to provide any significant loading of the Mode S specific functions. For this reason, and also for the desire to be able to repeat the identical test several times, an environment simulator was necessary to appear to the Mode S sensor under test as a dense beacon environment plus a dense interfering environment typical of what might be encountered in the future. These were the primary reasons for the development and fabrication of the ARIES system.

1

The ARIES is designed to simulate a radar beacon environment of up to 700 aircraft equipped with transponders plus high rates of interfering beacon replies "fruit." So using this system, the Mode S sensor can be fully tested under heavy target loads.

Four ARIES systems will be provided as government furnished equipment to the Mode S sensor production contractors, Westinghouse, and Unisys. The systems will be used to simulate, at the radio frequency (RF) level, capacity and high density aircraft and interference loading environments to the Mode S sensor during tests required by the following paragraphs of FAA-E-2716:

a. 4.3.2 Contractor preliminary tests

b. 4.3.3 Design Qualification tests

c. 4.3.4 Type tests

d. 4.4.2.3 Hardware/Software Integration tests

This makes the ARIES an important link in the successful implementation of the Mode S System.

3. RELATED DOCUMENTS.

a. Goon, M. and Spencer, D. A., <u>Aircraft Reply and Interference</u> <u>Environment Simulator (ARIES)</u>, FAA-RD-78-96, March 22, 1979.

b. <u>Mode Select Beacon System (Mode S) Sensor Specifications</u>, FAA-E-2716, March 24, 1983.

c. <u>U.S. National Standard for the IFF Mark X (SIF) Air Traffic Control</u> <u>Radar Beacon System (ATCRBS)</u>, FAA Order 1010.51A, March 8, 1971.

d. <u>U.S. National Standard for the Mode Select Beacon System</u>, FAA Order 6365.1A, January 3, 1983.

e. <u>The Aircraft Reply and Interference Environment Simulator (ARIES)</u> <u>Hardware Maintenance Manual</u>, DOT/FAA/CT-TN88/3 Volume I and II, May 1988.

f. <u>The Aircraft Reply and Interference Environment Simulator (ARIES)</u> <u>Software Principles of Operation</u>, DOT/FAA/CT-TN88/15, April 1988.

g. <u>Mode S to Common Digitizer (Model 2) Interface Control Document</u>, TM-PA-0018/074/02A, March 23, 1987.

h. <u>ASR-9 External Interface Control Document for the ASR-9 C&I Processor</u> to Mode S Sensor Interface and the Mode S to ASR-9 SP Interface, DTFA01-83-C-20027, September 24, 1984.

#### 4. ARIES SYSTEM CAPABILITIES.

The ARIES is capable of simulating a high density radar beacon environment of up to 700 aircraft. Any mix of Mode S and ATCRBS targets is possible. The target environment can be patterned to simulate any capacity and high density aircraft environment necessary to establish Mode S sensor performance with respect to specified requirements. ARIES can simulate these target environments in either single or dual (back-to-back) antenna modes. In addition to simulating the maximum number of targets handled by the Mode S sensor, ARIES is capable of handling the target bunching and data link peaking requirements specified for the Mode S sensor, which is capable of handling:

a. 250 targets within a  $90^{\circ}$  quadrant.

b. 50 targets within an  $11.25^{\circ}$  sector, for not more than four consecutive sectors.

c. 32 targets within a  $2.4^{\circ}$  wedge.

Along with the modeled target environment, ARIES is capable of generating a simulated fruit environment consisting of both ATCRBS and Mode S interfering beacon replies. The arrival times of fruit replies are not based on the traffic model. To do this would require modeling the nearby interrogators that cause these interfering replies to be generated. Instead, fruit is modeled as a random process with Poisson statistics.

For both the modeled transponder and fruit replies, ARIES provides the necessary signals to accurately simulate the monopulse offboresight angle. Also, an omnidirectional signal is provided so that sidelobe replies can be simulated. These signals are connected to the Mode S sensor via an RF interface to ARIES. Inside the sensor they are summed with similar signals from the sensor's own antenna. This allows a simulated environment to be superimposed on a live environment if desired.

In addition to the beacon data, ARIES provides simulated digitized radar data in the output format of an Airport Surveillance Radar model 9 (ASR-9) or a Common Digitizer model 2 (CD-2). The radar targets correspond to the simulated beacon targets. The reported coordinates are those that would be seen by a primary radar whose antenna rotates with the beacon antenna about the same axis.

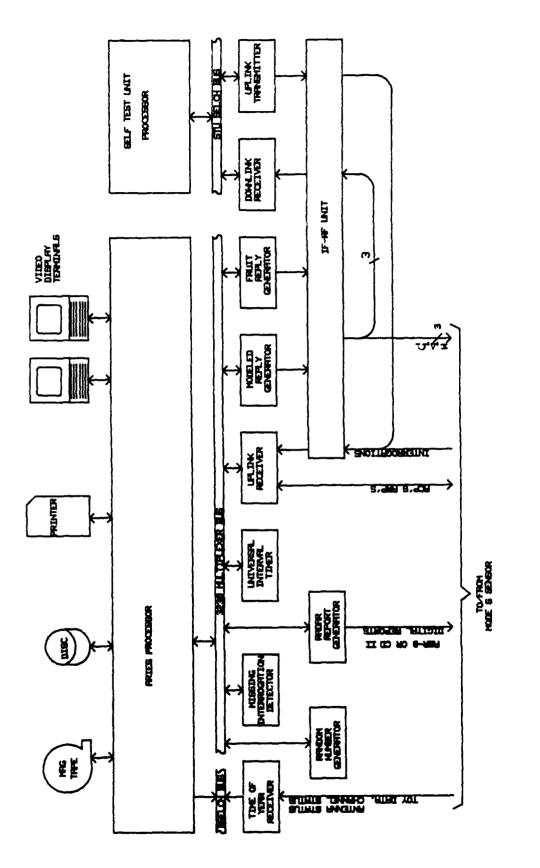

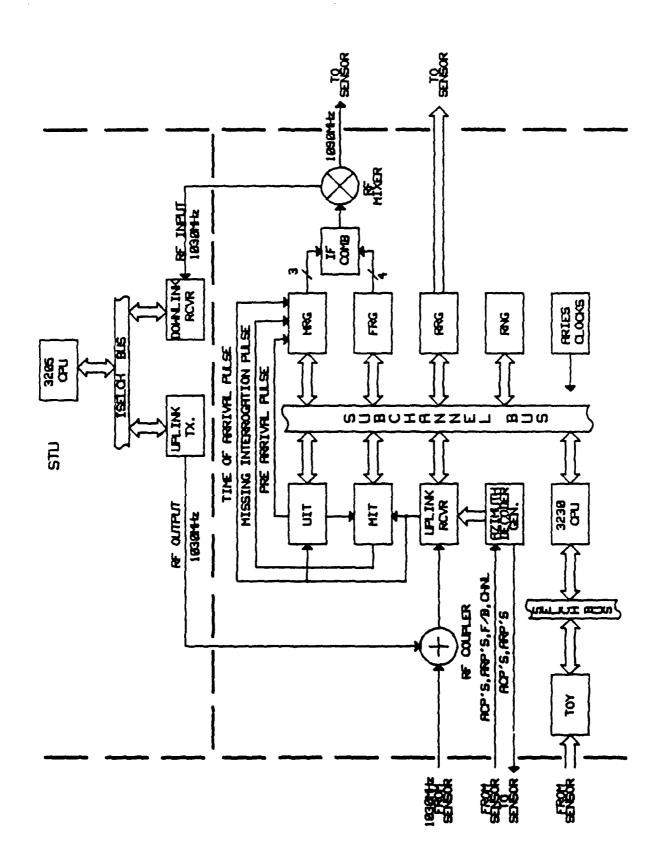

Each of the above mentioned features of ARIES is described in more detail in the following sections. Figure 4-1, an overall view of the ARIES hardware, will be useful in understanding those paragraphs describing the implementation of these features.

FIGURE 4-1. ARIES HARDWARE BLOCK DIAGRAM

.

.

٠

•

#### 4.1 MODELED REPLY GENERATION.

ARIES is capable of simulating both ATCRBS transponder-equipped aircraft and Mode S transponder-equipped aircraft whose characteristics are defined within a traffic model file stored on the system disk. Each logical record specifies the position and velocity of one aircraft at a particular time, as well as such items as its altitude, its identity code, and those items of state information to be mentioned in sections 4.1.1 and 4.1.2. These records are stored in increasing time order. The ARIES computer reads these records from the disk and when the current system time matches the time tag of the model record, that record is used to update the track file entry for that target or to start a new entry if this is the first appearance of the target. Typically, targets are updated periodically by the traffic model file at 4-second intervals. More frequent updates from the traffic model can create more precise flight paths. For more detail on the contents of the traffic model file and how to generate new models, refer to the ARIES Software Principles of Operations Manual.

ARIES receives interrogations from the Mode S sensor at 1030 megahertz (MHz) and processes them by the receiver circuitry. The receiver transfers a data block to the computer giving the type of interrogation, the time-of-arrival, the boresight azimuth of the antenna, whether the interrogation was received by the front antenna or the back antenna, and any data content. The azimuth data is provided by the azimuth decoder/simulator which can operate in either of two modes. In the decoder mode, azimuth change pulses (ACPs) and azimuth reference pulses (ARPs) are received from the sensor's antenna system, and used to increment and reset an azimuth register, respectively. The ACPs and ARPs are also retransmitted, as received, allowing the option of inserting the ARIES into these lines between the antenna and the sensor. In the simulator mode, ACPs and ARPs are produced by ARIES and sent to the sensor. ACPs and ARPs from the antenna, if the antenna is connected, are ignored. Thus, the ARIES can be run with a sensor that is not connected to an antenna system. The decoder mode must be used in the case where live data from the sensor's own antenna and the simulated data from ARIES are to be superimposed.

In the computer, the response depends on the type of interrogation. If it is an ATCRBS/All-Call interrogation, all ATCRBS transponders and unlocked Mode S transponders that are in the antenna beam are located in the track file resident in computer memory. If it is a Roll-Call interrogation, the appropriate track record is located by means of its Mode S address. Reply data blocks are generated for each such target. These specify the time of reply, the reply type, the reply power level, the simulated offboresight angle, and the data content. This data is transferred to the modeled reply generator circuitry. This generates the appropriate reply waveforms at 1090 MHz for acceptance by the Mode S sensor. The parity check encoding for Mode S replies are performed by the digital reply generators. Since there are three independent reply generators, up to three overlapping replies can be simulated. The signals of all these are summed together in the intermediate frequency (IF) combiner, then stepped up to the RF level and output to the sensor.

# 4.1.1 Simulated ATCRBS Transponder Behavior.

Simulated ATCRBS transponders are capable of responding to the following interrogation types:

a. Mode A ATCRBS/Mode S All-Call

b. Mode A ATCRBS-Only All-Call

c. Mode C ATCRBS/Mode S All-Call

d. Mode C ATCRBS-Only All-Call

e. Mode A

f. Mode C

g. Mode 2

The simulated ATCRBS transponders are capable of generating mode A, mode C and, if designated as equipped, mode 2 replies with any data pattern including the special position indicator (SPI) pulse, as defined in the ATCRBS National Standard. The simulated transponder will reply to the above mentioned interrogation types with the appropriate reply type, i.e., a mode A reply for a mode A interrogation unless one or more of the following conditions exist:

a. When the transponder azimuth lies outside of the antenna beam. For this purpose, the antenna beam edges are defined by the points where absolute value of the DIFF divided by the SUM is equal to 2.

b. When a fourth reply generator is required.

c. When the specified reply probability of a transponder is less than one, and the transponder randomly fails to reply in accordance with that reply probability.

d. When the slant range of the transponder is less than 1 nautical mile (nmi).

e. When the interrogation mode is mode 2 and the transponder is not designated as being mode 2 equipped.

#### 4.1.2 Simulated Mode S Transponder Behavior.

Simulated Mode S transponders are capable of responding to the following interrogation types:

Mode A ATCRBS/Mode S All-Call Mode C ATCRBS/Mode S All-Call Mode S short interrogation (56 bits) Mode S long interrogation (112 bits)

The Uplink Format (UF) field for the Mode S interrogation must have a code of 4 (surveillance, altitude), 5 (surveillance, identity), 20 (Comm-A, altitude), 21 (Comm-A, identity), or 24 (Comm-C). Mode S-only All-Calls (UF code 11) is ignored by ARIES.

The simulated Mode S transponders are capable of generating Mode S short (56 bits) and long (112 bits) replies with any data pattern as defined in the Mode S National Standard. The simulated transponder will respond with the appropriate reply (Downlink Format (DF) field of 4 (surveillance, altitude), 5 (surveillance, identity), 11 (Mode S-only All-Call), 20 (Comm-B, altitude), 21 (Comm-B, identity), or 24 (Comm-D) unless one or more of the same conditions mentioned for ATCRBS to reply holds. The contents of the control and protocol fields (first 32 bits) of each reply is determined by ARIES based on both information contained in the interrogation and the traffic model. A summary of these function are listed below:

a. Lockout of simulated transponders is supported for nonselective All-Call lockout protocol and multisite All-Call lockout protocol.

b. The flight status (FS) field of a Mode S reply is defined by the traffic model. The field may take on any value.

c. The capability (CA) field of a Mode S All-Call reply is defined by the traffic model. Also, the extended capability report is defined by the traffic model.

d. Reporting of transponder altitude or identity code.

e. Both air-initiated and ground-initiated Comm-B standard and multisite protocol is simulated. The contents of the Comm-B message (MB) field is defined by the traffic model. The MB field of all other Comm-B replies contain a constant determined by the traffic model.

f. Both the uplink and downlink extended length message standard and multisite protocol is supported. The Comm-C message (MC) field is ignored except as required to support the protocols. The Comm-D message (MD) fields contain a constant determined by the traffic model except as required to support the protocols. Downlink requests are initiated under control of the traffic model and any number of downlink segments up to 16 can be specified.

A final characteristic of the simulated transponders (ATCRBS and Mode S) that can be controlled via the traffic model is the reply probability. Each simulated transponder has its own reply probability value, and this can be used to simulate various round-reliability conditions. The hardware random number generator shown in figure 6.7-1 is used to determine whether or not a target will reply.

#### 4.2 FRUIT REPLY GENERATION.

ARIES is capable of generating both ATCRBS and Mode S fruit replies. These replies, combined with modeled target replies, are coupled at the RF level and output to the Mode S sensor.

### 4.2.1 ATCRBS Fruit Replies.

ATCRBS fruit replies are generated at an average rate between 1,000 to 50,000 replies per second. The fruit rate can be independently specified within each sector of a scan, a sector being a 11.25° wedge. In addition, the fruit rate can be updated every 10 seconds.

The capability of ARIES to generate high fruit rates is required to test the performance of the Mode S sensor reply processing circuitry at the interference level at which it is specified to operate. Because of the high rates required, the entire reply generation process is performed in hardware.

7

The computer updates the fruit environment based on a defined fruit definition file. This file contains the ATCRBS fruit parameters, as well as the Mode S fruit parameters to be discussed in the next section, stored in a time ordered sequence. The specific ATCRBS fruit parameters are (1) the average fruit rate desired, (2) the fraction of the replies that are to appear in the mainbeam of the antenna as opposed to the sidelobes, (3) the fraction of replies that are to have a fixed code, and (4) the specified fixed ATCRBS reply code. The later two items allow a particular code to be emphasized in the otherwise randomly generated stream of reply codes. The likely candidate for emphasis might be, for example, the nondiscrete code 1200.

The fruit inter-arrival times match those expected from a Poisson process, i.e., the probability that any given inter-arrival interval lies between t and t-dt is given by;

$$P(t) = Ae^{-At} dt$$

where A is the average arrival rate as specified by the computer. The allowable range for A is from 1,000 to 50,000 fruit per second. However, there are only three reply generators, so no more than three overlapping replies can be simulated even though this is a high probability event at a fruit rate of 50,000 fruit per second. The number of ATCRBS fruit reply generators provided was chosen to match the Mode S sensor's ability to decode a legitimate reply in the presence of up to three overlapping fruit replies.

Reply parameters, such as offboresight angle, power, and code bits are determined by pseudo-random generators. The term pseudo-random is used to indicate that the sequence of replies can be repeated exactly by initializing the fruit generator (i.e., the sequence is deterministic) although the reply statistics are designed to match those of certain random distributions.

The monopulse angle of the fruit replies is uniformly distributed across the entire range of offboresight angles that are generated by the AkIES.

The fraction of mainbeam fruit, as opposed to sidelobe fruit, is specified by the computer according to a parameter stored in the fruit definition file as mentioned earlier. The range of mainbeam/sidelobe fruit can be specified from 0 to 1 in increments of 1/255. For mainbeam fruit, the SUM channel signal level as measured at the sensor's RF port is randomly chosen according to the distribution;

$$P_{m1} = (-20 - 20 \times \log r_{m1}) dBm$$

where  $r_{ml}$  is a random integer uniformly distributed between 1 and 100 nmi. For sidelobe fruit, the equivalent distribution is;

$P_{s1} = (-55 - 20 \times \log r_{s1}) dBm$

where  $r_{s1}$  is a random integer uniformly distributed between 1 and 32 nmi. The sidelobe replies are simulated by attenuating the SUM and DIFF signals below the OMNI signal. The sidelobe attenuation is set between 20 decibel (dB) and 36 dB, adjustable in steps of 1 dB. The resolution for both power levels is 1 dB.

The reply codes, other than the specified fraction that is generated with a fixed code, are generated according to a distribution that roughly adjusts the probability of each of the ATCRBS data bits according to the likelihood of their being set in real fruit replies. Thus, not all reply codes are equally likely. For example, certain bit patterns are illegal in mode C replies, and these are therefore less likely to occur, although they are legal mode A patterns. Similarly, patterns corresponding to the mode C replies of very high flying aircraft are less likely than others. The X bit and the SPI bit are fixed at 0.

#### 4.2.2 Mode S Fruit Replies.

Mode S fruit replies are generated at an average rate between 10 to 640 replies per second. The fruit rate can be independently specified within each sector and updated every 10 seconds, same as the ATCRBS fruit rate.

The computer updates the fruit environment based on parameters stored in a defined fruit definition file. The specific Mode S fruit parameters are (1) the average fruit rate desired, (2) the fraction of the replies that are to appear in the mainbeam of the antenna as opposed to the sidelobes, and (3) the fraction of replies that are surveillance replies as opposed to Comm B or Comm D replies. In the later item, the allowable range is 0 to 1 in steps of 1/16.

The reply generation process is performed entirely in hardware similar to that used to generate ATCRBS fruit replies. The inter-arrival times for Mode S fruit is exponentially distributed to match those expected from a Poisson process similar to the ATCRBS inter-arrival time given by;

$$P(t) = Be^{-Bt} dt$$

where B is the average arrival rate as specified by the computer. The allowable range for B is 10 to 640 fruit per second.

In the generation of the offboresight angle, the fraction of replies in the mainbeam as opposed to the sidelobes and the SUM power distributions are performed in the same way as defined for the ATCRBS fruit.

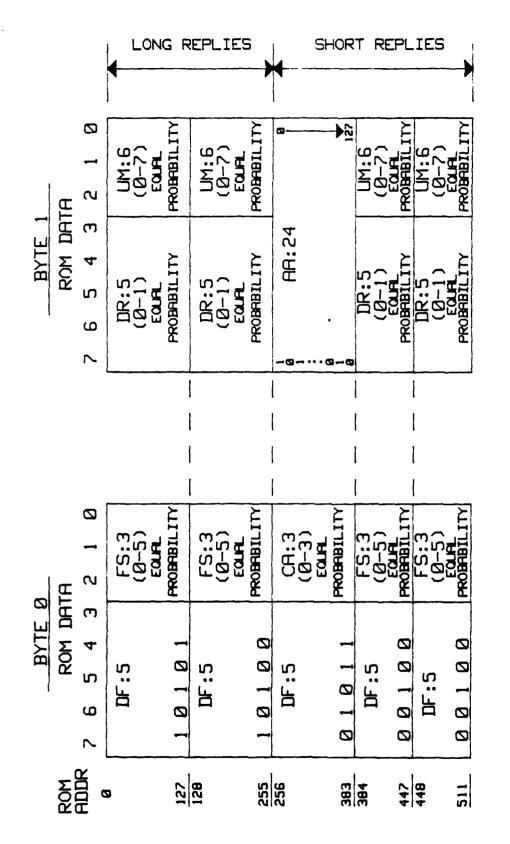

The reply data contents are generated according to a distribution of likely values. The values generated for the following fields: Downlink Format (DF:5), Flight Status (FS:3), Downlink Request (DR:5), Capability (CA:3), Altitude Code (AC:13), and Identity (ID:13) are restricted to defined or legal values and given equal probability. For example, the contents of the Downlink Format field will contain a legal value, that is, if a short reply is generated, its DF field will specify that the reply is a defined short reply. The contents of the remaining data fields are generated by a pseudo-random number generator.

#### 4.3 RADAR REPORT GENERATION.

The ARIES is capable of generating simulated primary radar data from two different primary radars; the ASR-9 and the CD-2. Only one type of primary radar data is simulated during any simulation run. A primary radar report is generated on each scan for each active target specified in the traffic model and is subject to a radar blip/scan ratio specified by the ARIES operator. The blip/scan ratio can have a value of 0 to 1 with a resolution of 1/31. The intermediate values result in the specified system average blip/scan ratio which is used in conjunction with a hardware random number generator to determine on a pseudo-random basis whether a given target will have a radar report on a given scan.

Radar reports are transmitted to the Hode S sensor just after the target has left the antenna beam but within the specified time limit of 3/64 of a scan from the time of the reported azimuth for sensor radar processing. The range and azimuth coordinates used are exactly those obtained from the traffic model as extrapolated to the time of boresight crossing, but converted to the appropriate units. This data is transferred to the radar report generator which outputs the data to the sensor using the bit-oriented Advanced Data Communication Control Procedure (ADCCP) specified in the following documents: (1) "Mode S to Common Digitizer (model 2) Interface Control Document," and (2) "ASR-9 External Interface Control Document for the ASR-9 C&I Processor to Mode S Sensor Interface and the Mode S to ASR-9 SP Interface."

In addition, a Search Real Time Quality Control (RTQC) report is transmitted at the  $180^{\circ}$  azimuth mark and one status report is transmitted at the  $0^{\circ}$  azimuth mark each scan.

The interface is capable of transferring the numbers of reports normally anticipated from the ASR-9 or CD-2 at the rate of 500,000 bits per second.

#### 4.4 SELF-TEST CAPABILITIES.

ARIES is a relatively complex system and is being used to test an even more complex system. It is essential, therefore, that there be some reliable way of confirming that the ARIES hardware is functioning correctly prior to and following simulation runs. This verification must be independent of the Mode S sensor.

The certification of standard off-the-shelf equipment, such as processors, tape drives, disk units, etc., is accomplished using the diagnostics provided by the manufacturer or supplier. These diagnostics are available to be run by the ARIES operator. The certification of the special purpose hardware designed for ARIES is accomplished using the ARIES hardware maintenance software package developed by the FAA Technical Center. This package is described in detail in the "ARIES Hardware Maintenance Manual."

Diagnostic circuitry is incorporated with each of the special digital devices to support several modes. These modes by and large fall into the category of writing data to the device and then reading it back. In some cases, the device command bits affect which data is read back and so their functioning can be tested as well. Also, each digital device containing a bit-sliced microprocessor has stored in their microcode (firmware) a set of diagnostic support routines that allow the testing of hardware not directly accessible to the computer. These routines, along with the description of the microcode set used, are described in appendix B (Volume II - Hardware Principles of Operation). It is not possible to test all the digital logic and none of the RF or IF circuitry in the above mentioned fashion. This is the purpose of the Self Test Unit (STU) included in the ARIES. The STU provides for the complete testing of the interrogation detection/processing and the reply generation/transmission circuitry of the ARIES. It is also useful for system checkout purposes. The STU can be programmed to generate any interrogation pattern and with the azimuth simulation capability of the ARIES, allow the ARIES (both hardware and software) to run in its normal simulation mode without connecting to a Mode S sensor.

The STU consists of its own dedicated computer and two special digital devices, the Uplink Transmitter and the Downlink Receiver. The Uplink Transmitter is capable of generating at 1030 MHz all of the interrogation modes and data patterns that are processed by the ARIES interrogation receiver. The interrogations are coupled into the normal receiver path with the interrogations received from the Mode S sensor. The interrogation type and its time of transmission are under computer control. The Downlink Receiver is capable of demodulating and detecting all of the reply types and sampling all of the reply data bits that are transmitted by the ARIES reply generators. When a reply bracket or a preamble is detected by the STU, an amplitude sample of the SUM and DIFF or OMNI channels is taken and the data bits sampled. The choice between sampling the DIFF or OMNI channels is determined by the computer. Decoding of the Mode S parity check is performed in hardware and the time of the reply is sampled with a same resolution specified for the reply generators. All of the information gathered on the reply is then fetched by the STU's computer for comparison with anticipated results. Both the modeled reply generators and he fruit reply generators can be tested by this method. The fruit reply generators require the use of a special diagnostic mode whereby the ARIES's computer specifies the reply parameters and data, rather than having these randomly generated.

#### 5. ARIES EQUIPMENT.

Before describing in detail the operations of the ARIES special purpose hardware, a brief depription of the overall ARIES equipment will be presented. The discussion will cover the equipment making up the ARIES and its physical layout.

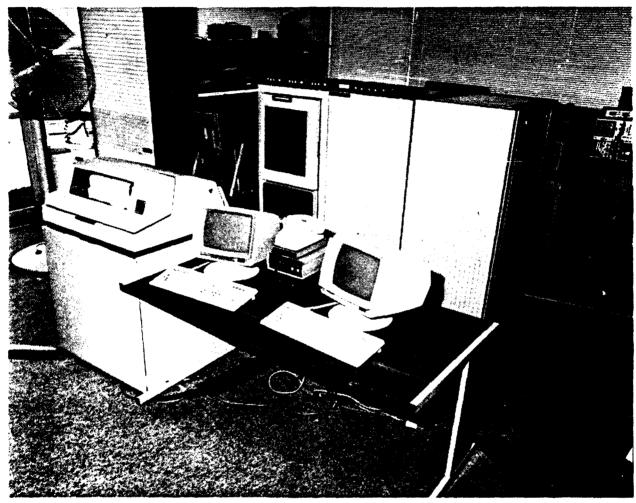

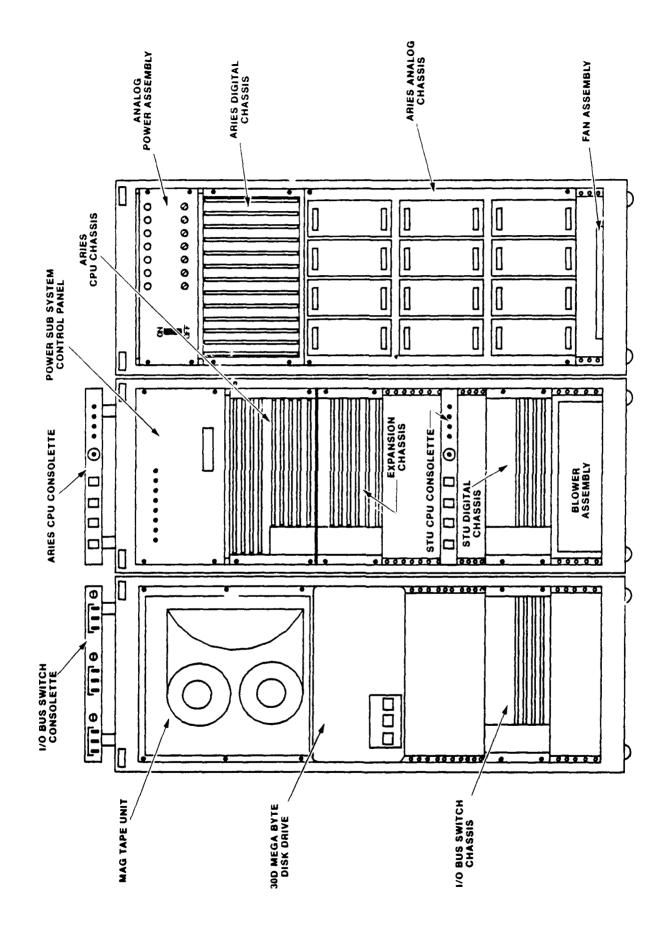

The ARIES equipment consists of interrogation receiving circuitry, reply generation circuitry, self test circuitry, two computers, and associated peripherals to control the system. This equipment is housed in three standard cabinets as shown in figure 5-1. A hardware overview of these equipment, along with their salient characteristics, will be presented in the rest of this section.

The peripherals used by the ARIES system consists of a disk drive, a dual density magnetic tape unit, two video display terminals, and a printer. The salient characteristics of these peripherals are listed in table 5-1. The disk drive and the magnetic tape unit are housed in one cabinet, referred to as the peripheral cabinet as shown in figure 5-2. The remaining peripherals are stand-alone units.

Oran TECHNICAL CENTER 87 - 1321

# FIGURE 5-1. ARIES EQUIPMENT OVERVIEW

TABLE 5-1. SALIENT CHARACTERISTICS OF PERIPHERALS USED IN ARIES

| PERIPHERAL         | SALIENT CHARACTERISTICS                                                                                                                                             |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Magnetic Tape Unit | Quantity one per system<br>75 ips, 9 track<br>Dual (800/1600 cpi) recording density<br>1/2 inch, 2400 foot (10.5 inch) reel<br>120,000 cps transfer rate - 1600 cpi |

| Disk Storage Unit  | Quantity one per system<br>300 Megabyte storage<br>1.2 Megabyte data transfer rate                                                                                  |

| Video Display Unit | Quantity two per system<br>80 characters per line<br>24 lines per screen<br>128 ASCII character set<br>RS232C standard current mode interface                       |

| Line Printer       | Quantity one per system<br>300 lines per minute, 132 columns/line<br>USASCII 96 character set                                                                       |

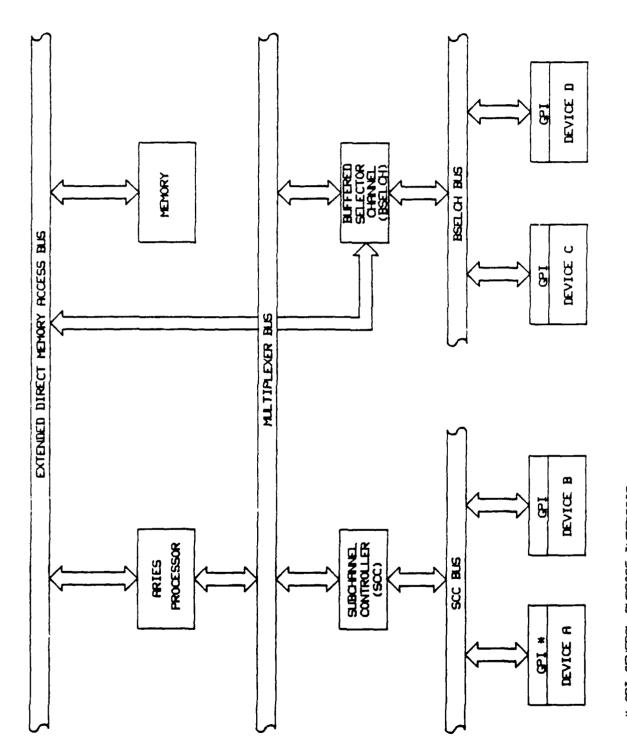

The input/output (I/O) bus chassis and its associated power supply is housed in the peripheral cabinet as well. This chassis contains the intelligent disk controller board, the magnetic tape controller board, a buffer selector board for direct memory address operations, and two I/O bus switch B-boards (The I/O bus switch A-boards that works in conjunction with these boards are discussed later.) The I/O bus switch consolette which selects which computer has access to the magnetic tape unit and the disk drive is located on top of the cabinet.

Two computer systems are housed in a second cabinet, referred to as the processor cabinet (see figure 5-2). The first computer system (Concurrent Computer Corporation 3230 32-bit computer), with 3 megabytes of random access memory (RAM), 4 kilobytes high-speed writable control store (WCS) memory, and with high-speed interface capability, interfaces with and controls the ARIES components. The second computer system (Concurrent Computer Corporation 3205 32-bit minicomputer), with 1 megabyte of RAM, interfaces with and controls the STU components. Each system is housed in their own chassis but share a common +5-volt power supply. Each computer is independent of the other with only one RS-232C communication link setup between them for the purpose of supporting maintenance functions (refer to appendix E of the ARIES Hardware Maintenance Manual for further information).

Two nonstandard boards are housed in the STU computer chassis. Each is a special purpose device used by the STU to support verification testing of ARIES hardware and software functions. These boards are the Uplink Transmitter and the Downlink Receiver boards. They are the only FAA Technical Center fabricated boards not located in the third cabinet to be discussed later.

Three +5-volt 150 Ampere switching power supply units are located at the top of the processor cabinet. One of these units is dedicated to the 3-megabyte memory of the ARIES computer. The remaining two power units, wired together to produce a 300 Ampere supply, provide power to the ARIES computer chassis, the STU computer chassis, and the ARIES digital chassis located in the third cabinet. Not shown in figure 5-2 is a battery backup unit for the main memory of the ARIES computer if power should be lost.

Each computer chassis contains a I/O bus switch A-board. Each A-board works in conjunction with an associated B-board located in the I/O bus chassis housed in the peripheral cabinet. When an A-board and its associated B-board are selected via the I/O bus switch consolette, the desired computer has access to the disk drive and magnetic tape unit.

The third cabinet houses all of the special hardware developed by the FAA Technical Center to support required functions of the ARIES system with the exception of previously mentioned digital boards located in the STU computer chassis. This cabinet is referred to as the hardware expansion cabinet (see figure 5-2). This special purpose hardware is covered in detail in section 6.

Two chassis are housed in the hardware expansion cabinet; one digital and one analog. The digital chassis contains all of the ARIES special purpose devices mounted on 12 digital boards and 1 printed circuit board. The digital chassis is located directly beneath the analog power assembly. The board slot assignment of this chassis is given in table 5-2. Each digital board has the chip capacity of 322 16-pin standard integrated circuit (IC) chips. The analog chassis contains all of the analog circuitry for the ARIES and the STU mounted on 12 removable panels for easy maintenance when required. The analog chassis is located beneath the digital chassis. The layout of this chassis is shown in figure 5-3.

The analog power assembly contains all of the power voltage levels required by the analog circuitry and the video pulse quantizer (VPQ) board located in slot No. 1 of the digital chassis. The analog power assembly is located at the top of the cabinet to minimize the heat flow through the cabinet since the air flow is forced from the bottom to the top of the cabinet by a fan assembly located at the bottom.

A break point panel is located inside of the cabinet behind and between the digital chassis and the analog chassis. This connector panel serves as the demarcation point for all interface cables between the two chassis and the STU chassis. All of the digital connectors used on this panel are 37-pin D-type connectors. A layout of this panel is shown in figure 5-4 and the name of the connectors is identified in table 5-3.

# TABLE 5-2. ARIES DIGITAL CHASSIS BOARD SLOT ASSIGNMENTS

| SLOT | BOARD NAME                                | DEVICE                                                                                                                              |  |

|------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

|      | <u></u>                                   |                                                                                                                                     |  |

| 1    | Video Pulse Quantizer<br>(VPQ)            | Video Pulse Quantizer (VPQ)<br>Dual Channel Video Sampler                                                                           |  |

| 3    | Time-of-Year Receiver<br>(TOY)            | Time-of-Year Receiver<br>(TOY)                                                                                                      |  |

| 5    | Reply Generator No. 3<br>(RGEN)           | Modeled Reply Generator<br>(MRG)                                                                                                    |  |

| 7    | Reply Generator No. 1<br>and No. 2 (RGEN) | n e                                                                                                                                 |  |

| 9    | Modeled Reply Controller<br>(MRC)         | n                                                                                                                                   |  |

| 11   | Uplink Receiver (RVCR)                    | Uplink Receiver<br>Azimuth Decoder/Simulator<br>(AZGEN)                                                                             |  |

| 13   | Multiple Device (MULT)                    | ARIES System Clock<br>Universal Interval Timer<br>(UIT)<br>Random Number Generator<br>(RNG)<br>Missing Interrogation Timer<br>(MIT) |  |

| 15   | Radar Report Generator<br>(RRG)           | Radar Report Generator<br>(RRG)                                                                                                     |  |

| 17   | Fruit Reply Controller<br>(FRC)           | Fruit Reply Generator<br>(FRG)                                                                                                      |  |

| 19   | ATCRBS Random Process<br>Generator (ARPG) | n                                                                                                                                   |  |

| 21   | Mode S Random Process<br>Generator (MRPG) | 'n                                                                                                                                  |  |

| 23   | Reply Generator No. 1<br>and No. 2 (RGEN) | 11                                                                                                                                  |  |

| 25   | Reply Generator No. 3<br>and No. 4 (RGEN) | n                                                                                                                                   |  |

|      |                                           |                                                                                                                                     |  |

| <b> </b>                                                                  | 14                                                   | ••                                                          | •                           |     |

|---------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------|-----------------------------|-----|

| REPLY GEN. 1<br>58.5 MHz.                                                 | REPLY GEN. 2<br>59.0 MHz.                            | REPLY GEN. 3<br>61.0 MHz.                                   | REF*LY GEN. 4<br>61.5 MHz.  |     |

| I<br>IF COMBINER                                                          | 2<br>REPLY GEN. 7                                    | 1                                                           |                             |     |

| 68 144 TEST DAUT<br>-3486 NORDAL<br>0 0 0                                 | 60.5 MHz.                                            | 6 <b>0.0</b> MHz.                                           | 59.5 MHz.                   | 30° |

| 0 0 0                                                                     | _                                                    |                                                             | _                           |     |

| 8<br>INTERROGATION<br>RECEIVER<br>&<br>STU<br>INTERROGATION<br>GENERATIOR | 7<br>DOWNLINK<br>MODE S<br>CHFINNEL<br>SELECTOR      | 6<br>NF TO IF<br>DOHNCONVERT<br>&<br>STU IF<br>FNFLOG RECVR | 5<br>IF TO RF<br>UP-CONVERT |     |

| NDCEIVER STU<br>S78 HMR. DATEMO-<br>L.O. GATIONE<br>O O<br>S              | INNE HHE.<br>OLITHUT<br>REPLY<br>SELTH<br>OHNE<br>18 |                                                             | 12                          |     |

.

FIGURE 5-3. ARIES ANALOG CHASSIS LAYOUT

•

| CONNECTOR | TABLE                          |

|-----------|--------------------------------|

| J1        | Fruit Reply Generator No. 1    |

| J2        | Fruit Reply Generator No. 2    |

| J3        | Fruit Reply Generator No. 3    |

| J4        | Fruit Reply Generator No. 4    |

| J5        | Modeled Reply Generator No. 3  |

| J6        | Modeled Reply Generator No. 2  |

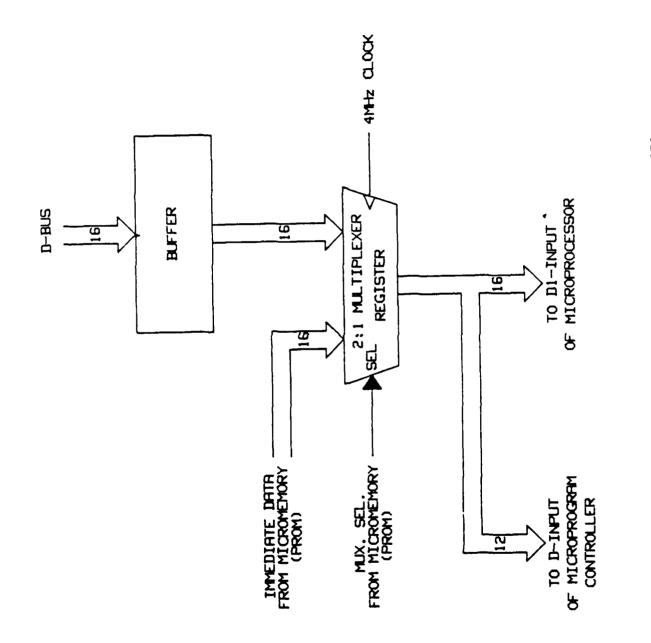

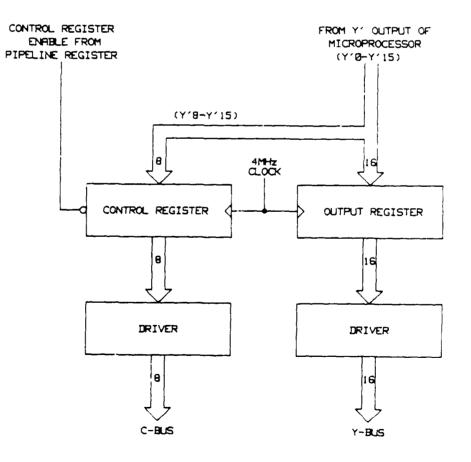

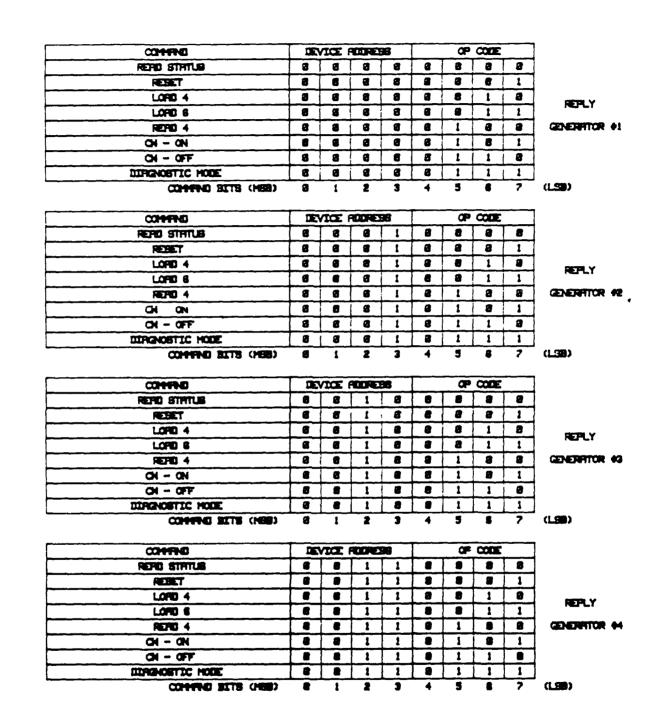

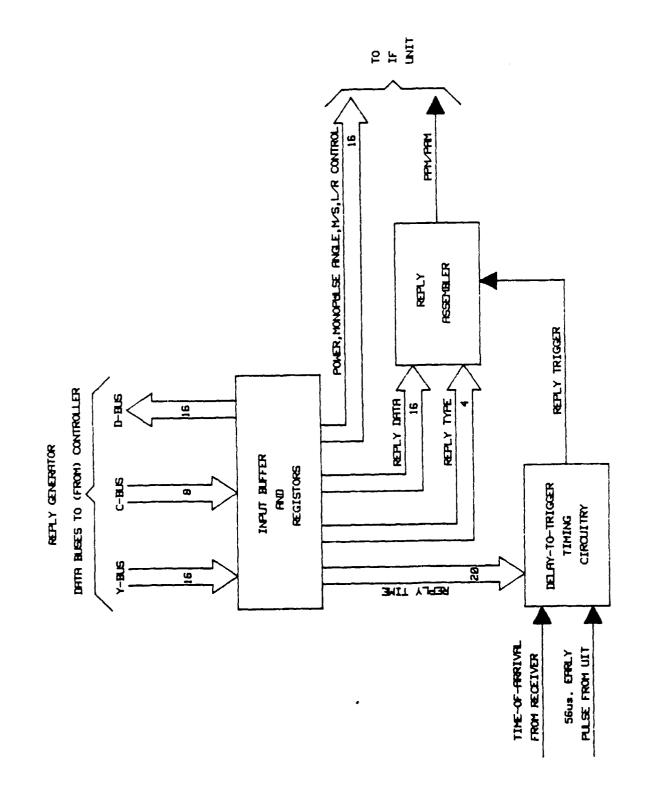

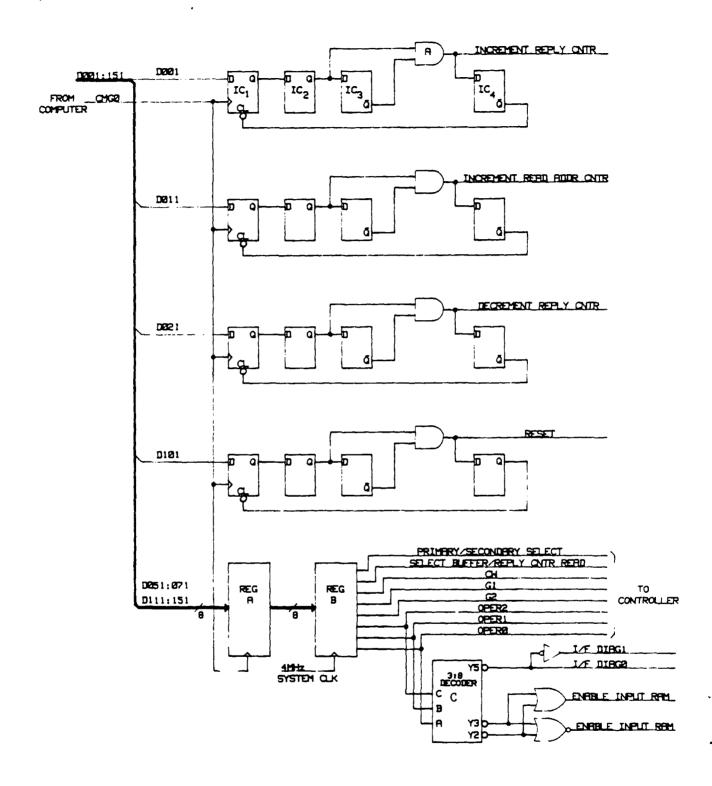

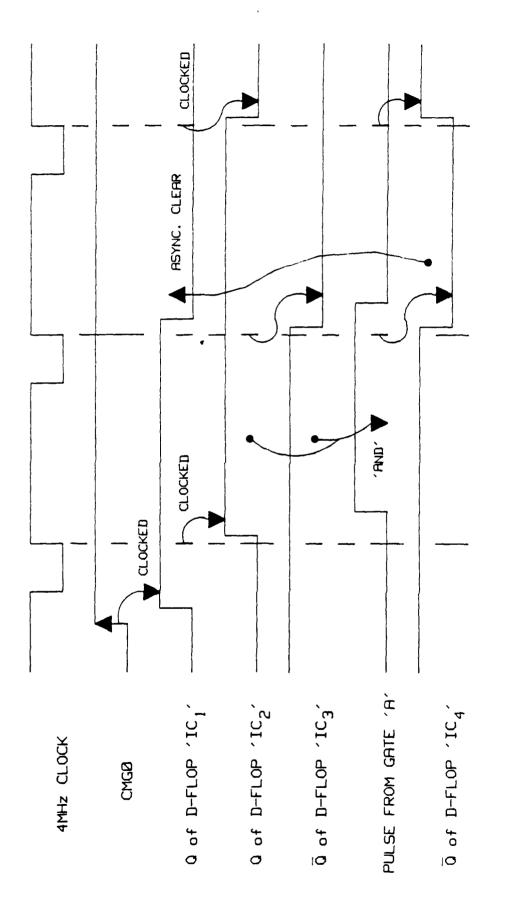

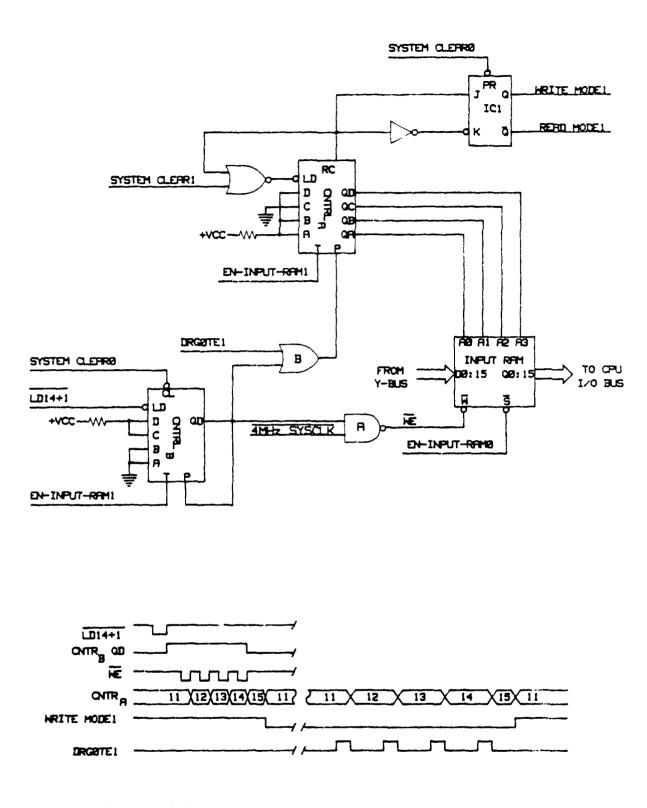

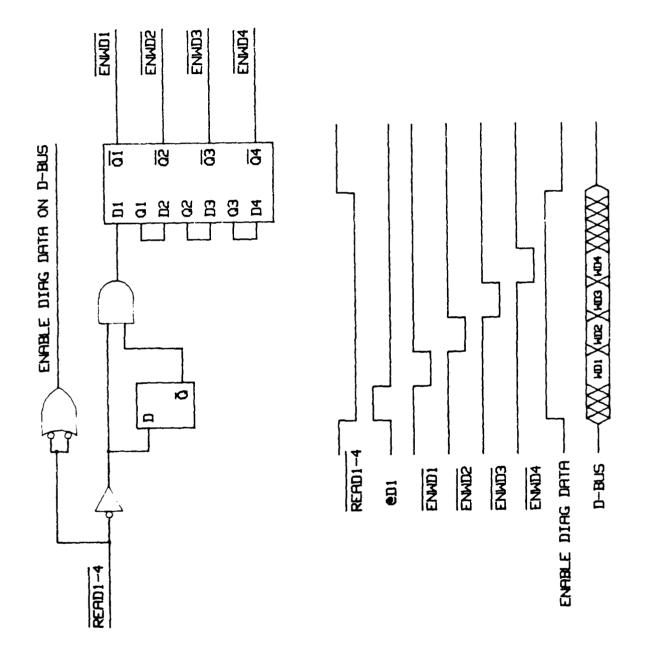

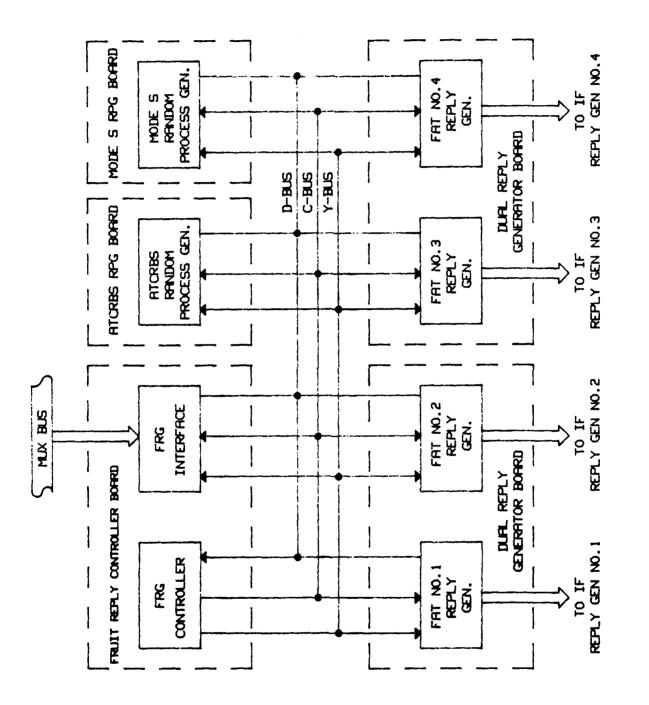

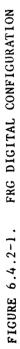

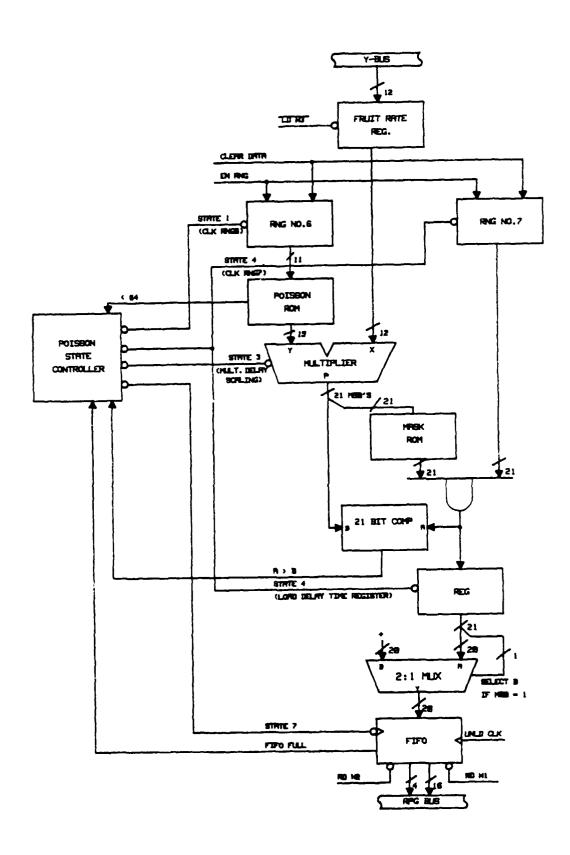

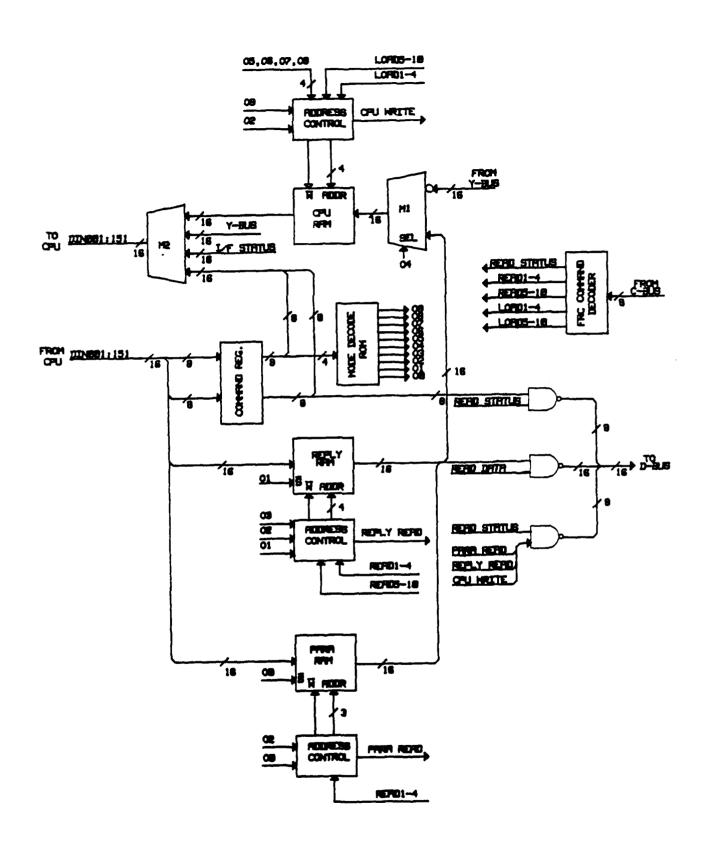

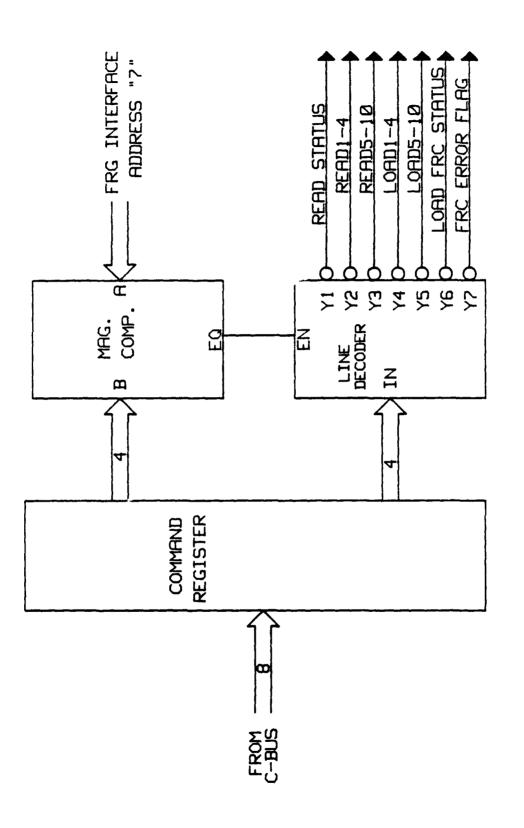

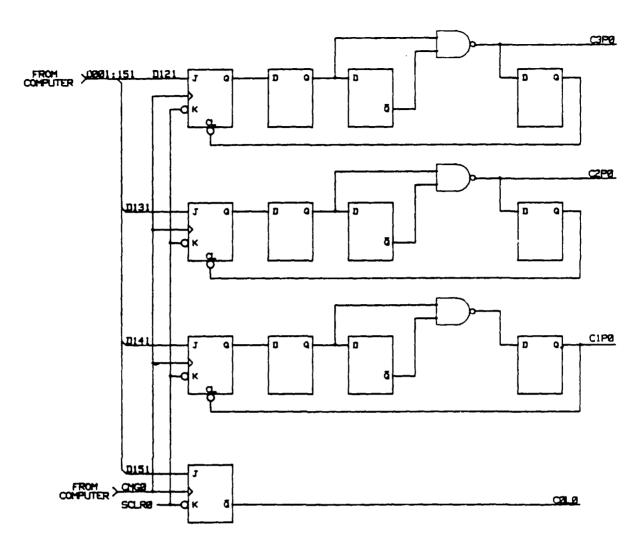

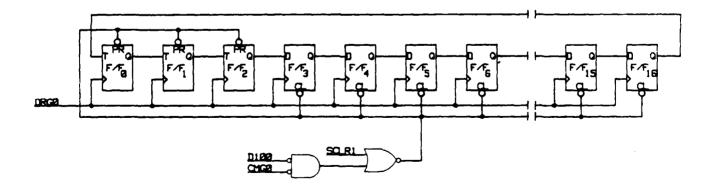

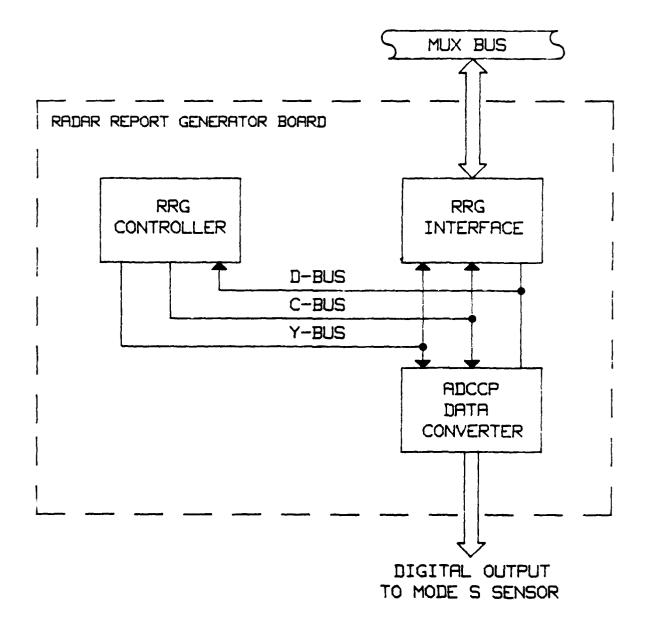

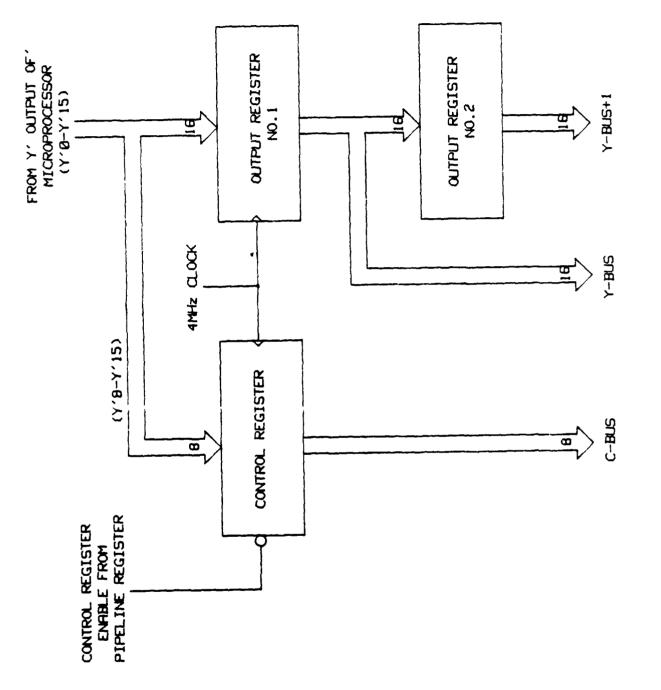

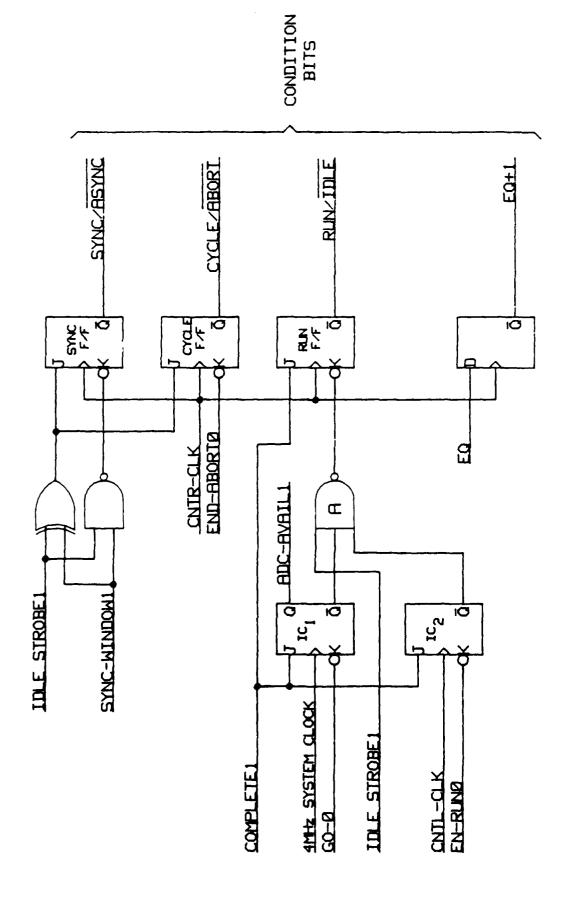

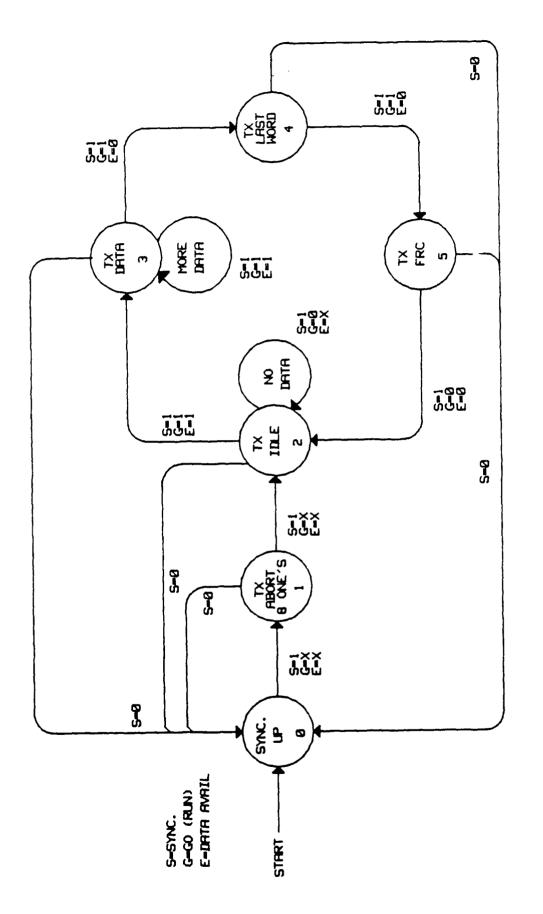

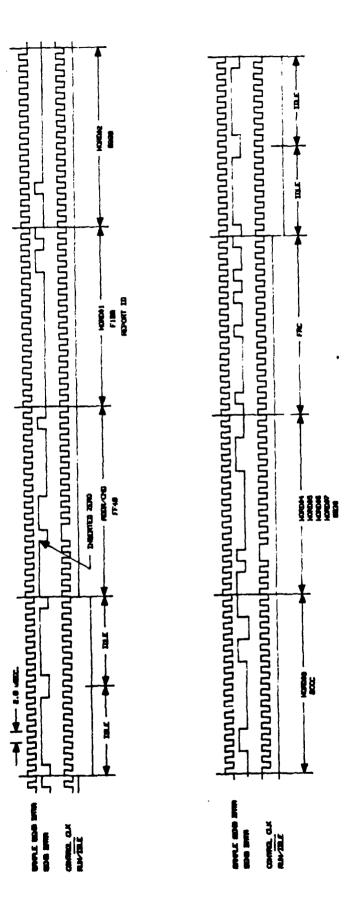

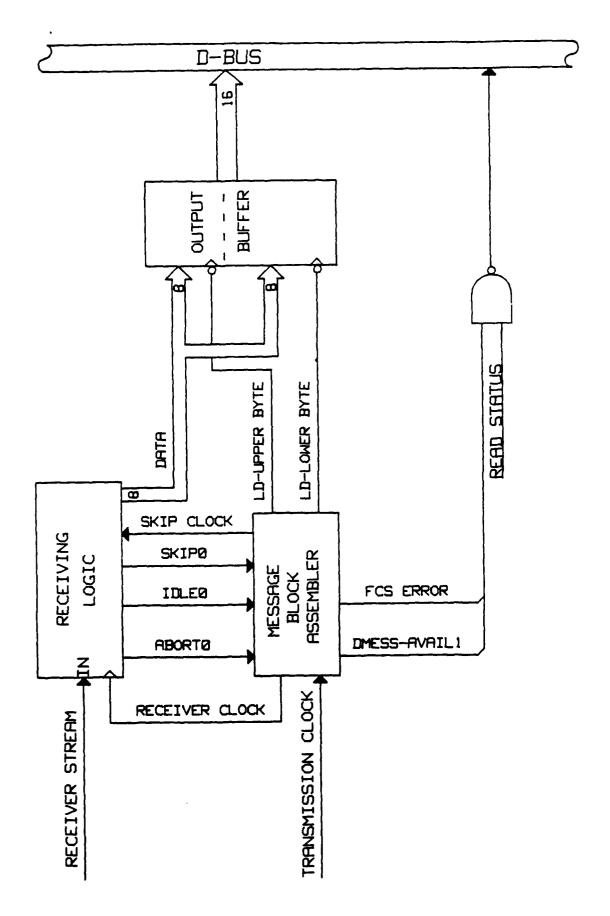

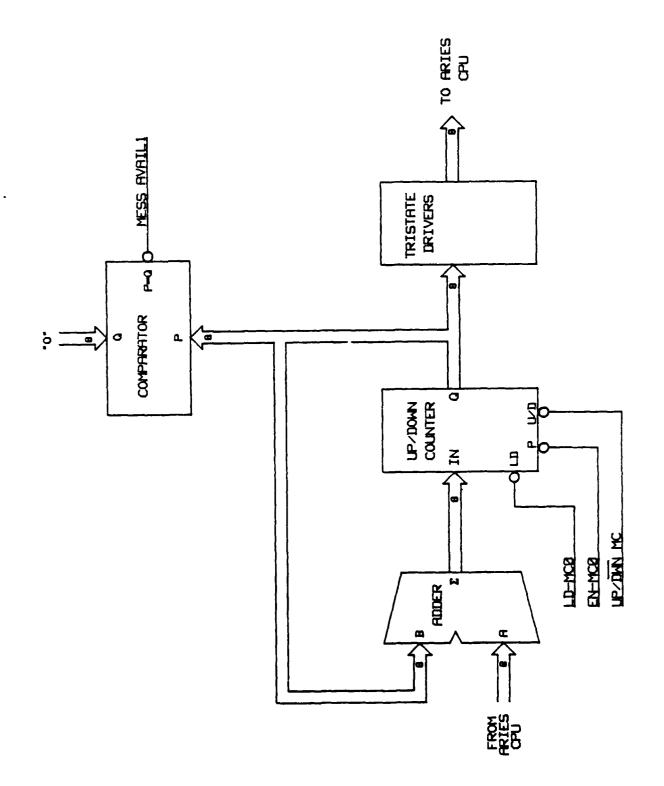

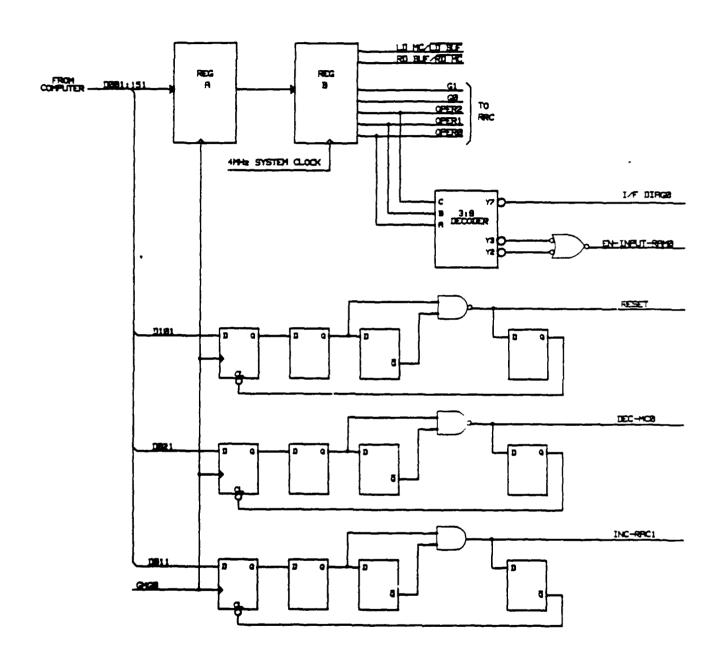

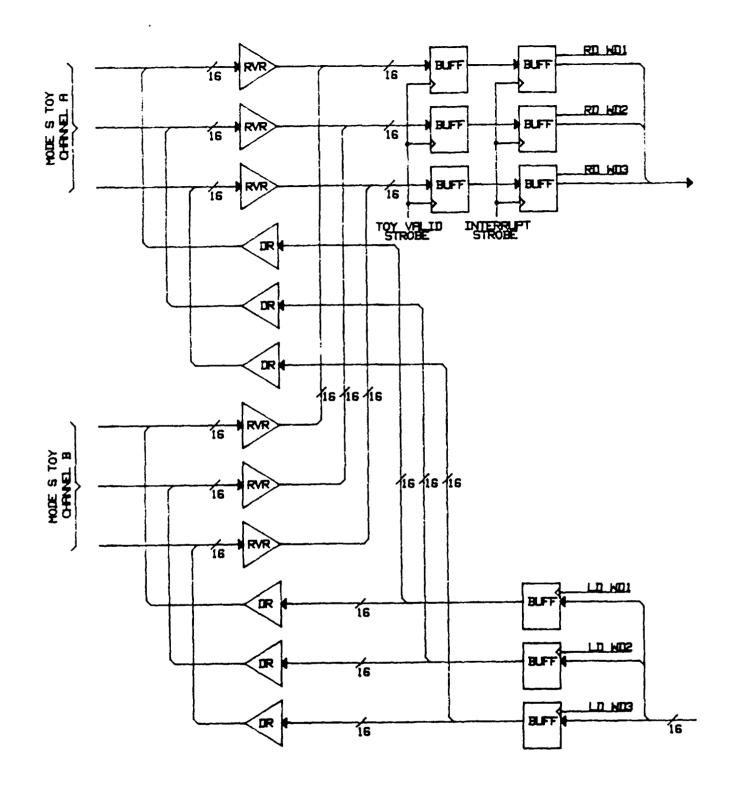

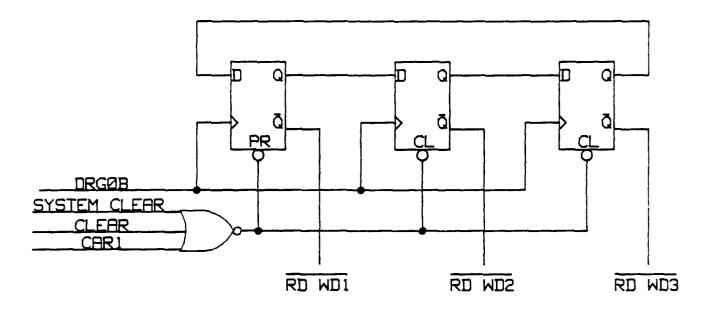

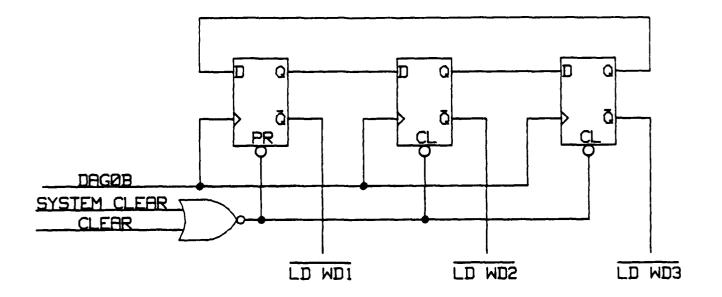

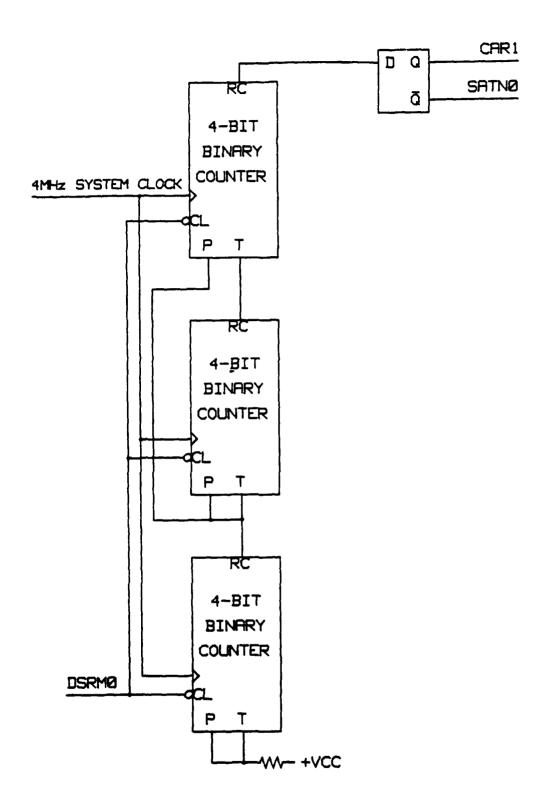

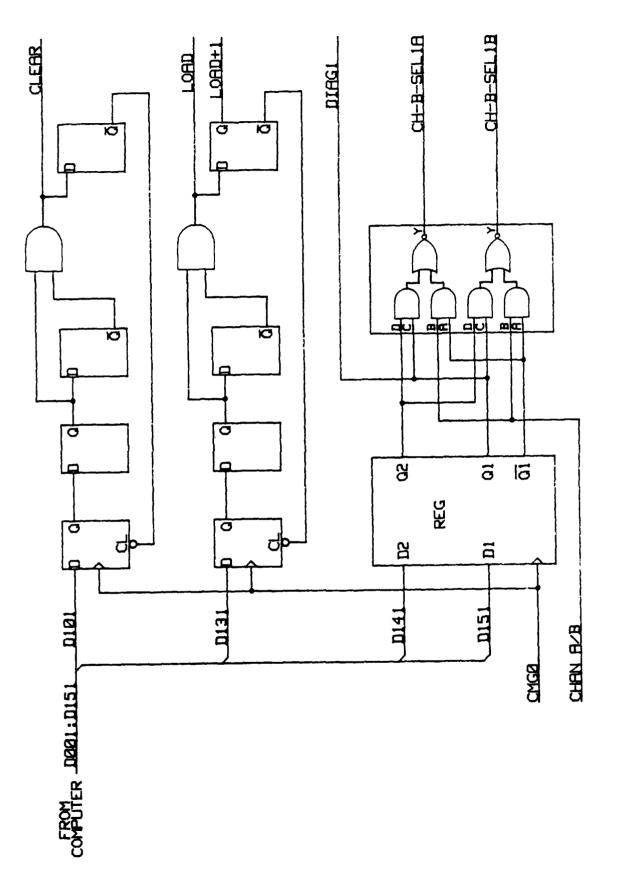

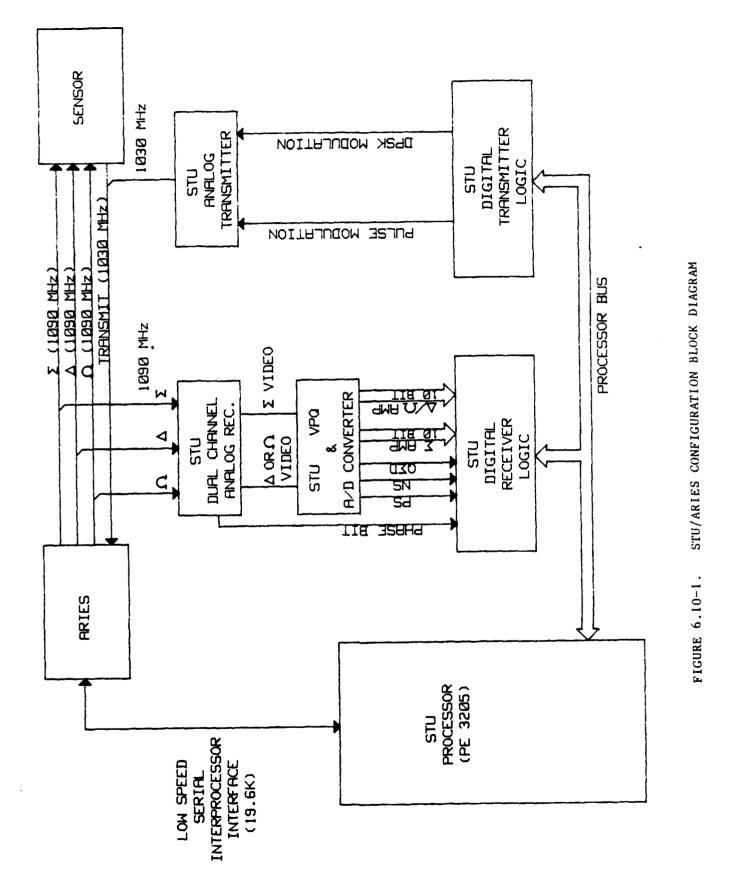

| J7        | Modeled Reply Generator No. 1  |