# DEPARTMENT OF OCEAN ENGINEERING

MASSACHUSETTS INSTITUTE OF TECHNOLOGY CAMBRIDGE, MASSACHUSETTS 02139

COMPUTER SIMULATION OF SHIPBOARD ELECTRICAL DISTRIBUTION SYSTEMS

χα

Norbert H. Doerry

June 1939

Course XIII-A: Naval Engineer

Course VI: SMEECS

#### COMPUTER SIMULATION OF SHIPBOARD **ELECTRICAL DISTRIBUTION SYSTEMS**

bу

N00228-89-6-058

#### NORBERT HENRY DOERRY

B.S., Electrical Engineering United States Naval Academy (1983)

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREES OF **NAVAL ENGINEER**

and MASTER OF SCIENCE

in ELECTRICAL ENGINEERING AND COMPUTER SCIENCE at the MASSACHUSETTS INSTITUTE OF TECHNOLOGY May, 1989

© Norbert H. Doerry, 1989 Signature of Author Departments of Ocean Engineering and Electrical Engineering and Computer Science 12 May 1989 Certified by James L. Kirtley, Thesis Supervisor Associate Professor of Electrical Engineering Certified by Paul E. Sullivan, Thesis Reader Associate Professor of Naval Architecture Accepted by \_\_ A. Douglas Carmichael, Chairman Ocean Engineering Departmental Ofaduate Committee Accepted by Arthur C. Smith, Chairman Electrical Engineering and Computer Science Department Committee to ruble in

il ecular trus

Restriction to an areal

#

THIS DOCUMENT IS BEST QUALITY AVAILABLE. THE COPY FURNISHED TO DTIC CONTAINED A SIGNIFICANT NUMBER OF PAGES WHICH DO NOT REPRODUCE LEGIBLY.

REPRODUCED FROM BEST AVAILABLE COPY

# COMPUTER SIMULATION OF SHIPBOARD ELECTRICAL DISTRIBUTION SYSTEMS

by

#### NORBERT H. DOERRY

Submitted on May 12, 1989 in partial fulfillment of the requirements for the degrees of Naval Engineer and Master of Science in Electrical Engineering and Computer Science.

#### **ABSTRACT**

Shipboard electrical distribution systems are changing significantly with the introduction of solid state frequency converters, introduction of electric propulsion and integrated electric drive, and the possibility in the future of large combat systems pulsed loads. Existing computer tools for analyzing power systems have difficulty simulating these changing conditions. To assist in the evaluation and analysis of future shipboard electrical distribution systems, the Shipboard Electrical Plant Simulation Program (SEPSIP) was developed.

The key feature of SEPSIP is its use of implicitly defined input variables and implicit variables which allow for every element of the simulation to be mathematically isolated from every other element. When the constitutive laws of an element are satisfied by an appropriate set of input variables, all of the implicit variables have zero value. The network description generates the input variables based on the network topology and the results of a Newton-Raphson iterative scheme. The key advantage to this method is that the network description of a node closely models an actual electrical node.

To demonstrate the abilities of SEPSIP, several simulations involving synchronous generators, induction motors, and voltage regulator dynamics were conducted. In all simulations, SEPSIP provided results that matched data generated by other simulation methods.

Thesis Supervisor: James L. Kirtley

Title: Associate Professor of Electrical Engineering

The author hereby grants to the United States Government and the Massachusetts Institute of Technology permission to reproduce and to distribute copies of this thesis document in whole or in part.

Norbert Henry Doerry

#### **ACKNOWLEDGEMENTS**

I am grateful to the Unites States Navy which has afforded me this opportunity to pursue a post graduate education and complete this thesis.

I am also grateful to my thesis advisor, Professor James Kirtley, for his patience, encouragement, and timely guidance

I express my thanks to the numerous individuals at the David Taylor Research Center and Naval Sea Systems Command who provided me with much insight with regards to the issues involved with shipboard electrical distribution systems.

I would also like to thank the men and women of MIT's Project ATHENA who often took time from their busy schedules to answer my questions concerning the UNIX operating system and the C programming language.

# **Table of Contents**

| CHAPTER 1 INTRODUCTION                                           |     |

|------------------------------------------------------------------|-----|

| 1.1 Thesis Objectives                                            | 11  |

| 1.2 Modelling Shipboard Electrical Power Systems                 | 12  |

| 1.2.1 Elements: Constitutive Equations                           | 12  |

| 1.2.2 Networks: Nodal Equations                                  | 13  |

| 1.3 Power System Analysis Computer Tools                         | 14  |

| 1.3.1 Desired Features                                           | 1.7 |

| 1.3.2 Simulation Programs for Land Based Power Utilities         | 14  |

| 1.5.2 Simulation Programs for Land Based Power Utilities         | 14  |

| 1.3.2.1 EMTP                                                     |     |

| 1.3.2.2 POSSIM                                                   |     |

| 1.3.2.3 MANSTAB                                                  |     |

| 1.3.2.4 MANTRAP                                                  | 16  |

| 1.3.2.5 LOTDYS                                                   | 16  |

| 1.3.3 Software Packages for Systems of Nonlinear Equations       | 16  |

| 1.3.3.1 CSMP                                                     | 17  |

| 1.3.3.2 SIMNON                                                   | 18  |

| 1.3.3.3 ACSL                                                     |     |

| 1.3.4 SEPSIP (Shipboard Electrical Plant Simulation Program)     | 10  |

| 1.4 Significance of Thesis                                       | 10  |

|                                                                  |     |

| 1.5 Outline of Thesis                                            | 19  |

|                                                                  |     |

| CHAPTER 2 THEORY OF THE COMPUTATIONAL METHOD                     |     |

| 2.1 General Strategy                                             | 21  |

| 2.2 Device Definitions                                           |     |

| 2.2.1 Input Variables: Interacting with the Network              | 24  |

| 2.2.1.1 Voltage Subnodes                                         | 25  |

| 2.2.1.2 Reference Voltage Subnodes                               | 25  |

| 2.2.1.3 Current Subnodes                                         | 25  |

| 2.2.1.4 Reference Current Subnodes                               |     |

| 2.2.2 Parameters                                                 |     |

| 2.2.3 Implicit Definition of Input Variables                     |     |

| 2.2.4 Implicit Variable Selection: Rotating and Translating Axes | 26  |

| 2.2.4 implicit variable Selection: Rotating and Translating Axes | 20  |

| 2.2.5 Data Storage: State Variables                              |     |

| 2.2.6 External Inputs                                            |     |

| 2.2.7 External Outputs                                           |     |

| 2.2.8 Integration Techniques                                     |     |

| 2.2.9 Modelling Transfer Functions                               |     |

| 2.2.10 Jacobian Construction                                     |     |

| 2.3 ELEMENT DESCRIPTIONS                                         | 32  |

| 2.4 NETWORK Description                                          | 33  |

| 2.4.1 Voltage Subnodes                                           |     |

| 2.4.2 Current Subnodes                                           |     |

| 2.5 Reference Subnodes                                           |     |

| 2.6 Conducting the Simulation                                    |     |

|                                                                  |     |

| 2.6.1 Setup                                                      |     |

| 2.6.2 Initialization                                             |     |

| 2.6.3 Updating External Inputs                                   |     |

| 2.6.4 Balancing the System                                       | 38  |

| 2.6.4.1 Calculating Implicit Variables                           |     |

| 2.6.4.2 Manufacturing System Jacobian Matrix                     | 38  |

| 2.6.4.3 Calculating Variable Corrections via Newton-Raphson      | 41  |

| 2.6.5 Printing Results                                           |     |

| 2.6.6 Updating State Variables and Time Counter        | 41 |

|--------------------------------------------------------|----|

| 2.6.7 Potential Problems                               | 42 |

| 2.6.7.1 Numerical Instability                          | 42 |

| 2.6.7.2 Singular Jacobian Matrix                       |    |

| 2.6.7.3 Non-Unique Solutions                           | 42 |

|                                                        |    |

| CHAPTER 3 SEPSIP SHIPBOARD ELECTRICAL PLANT SIMULATION |    |

| PROGRAM                                                |    |

| 3.1 Introduction                                       |    |

| 3.2 Data Entry Conventions                             | 44 |

| 3.2.1 Acceptable Characters                            |    |

| 3.2.2 Reserved Names                                   | 45 |

| 3.2.3 Specifying Variables and Subnodes                | 45 |

| 3.2.4 Numerical Entries                                |    |

| 3.2.5 White Characters                                 |    |

| 3.2.6 Continuation Lines                               |    |

| 3.2.7 Case Sensitivity                                 |    |

| 3.2.8 Comment Lines                                    | 46 |

| 3.3 Input File Generation                              | 47 |

| 3.3.1 Organization Using INCLUDE Files                 | 48 |

| 3.3.2 ELEMENT Description                              | 48 |

| 3.3.3 NETWORK Description                              |    |

| 3.3.4 INITIALIZATION Description                       |    |

| 3.3.4.1 INITIALIZE                                     | 52 |

| 3.3.4.2 EXTERNAL [INPUTS INITIALIZATION]               |    |

| 3.3.4.3 NODE VOLTAGE [INITIALIZATION]                  |    |

| 3.3.5 SIMULATION Description                           | 53 |

| 3.3.5.1 CONVERGE                                       | 53 |

| 3.3.5.2 DELTA                                          |    |

| 3.3.5.3 DELTA MIN                                      |    |

| 3.3.5.4 DISPLAY                                        |    |

| 3.3.5.5 EXTERNAL INPUTS                                |    |

| 3.3.5.6 MAX_ITERATION                                  |    |

| 3.3.5.7 PRINT_STEP                                     |    |

| 3.3.5.8 REFERENCE                                      |    |

| 3.3.5.9 TIME_STEP                                      |    |

| 3.3.5.10 TMIN                                          |    |

|                                                        |    |

| 3.3.5.11 TMAX                                          |    |

| 3.4 Running the Simulation                             |    |

| 3.4.1 Starting SEPSIP                                  | 57 |

| 3.4.2 Command Entry Conventions                        |    |

| 3.4.2.1 SEPSIP Menus                                   | 3/ |

| 3.4.2.2 Concatenating Commands                         | 28 |

| 3.4.2.3 Input Filename Specification.                  |    |

| 3.4.2.4 Output Filename Specification                  |    |

| 3.4.3 Command Summary                                  |    |

| 3.4.4 Main Menu                                        | 59 |

|                                                        |    |

| 3.4.4.2 d Display Data                                 | 60 |

| 3.4.4.2.1 d c Change Working Directory                 | 6l |

| 3.4.4.2.2 d d Display Device Summary                   | 61 |

| 3.4.4.2.3 d D Display Device Data                      |    |

| 3.4.4.2.4 de Display Element Summary                   |    |

| 3.4.4.2.5 d E Display Element Data                     |    |

| 3 4 4 2 6 d n. Disniav Network Summary                 | 63 |

| 2.4.4.0.7.1                                          | -   |

|------------------------------------------------------|-----|

| 3.4.4.2.7 d q Quit                                   | 03  |

| 3.4.4.2.8 d w Write Device Data File                 | 64  |

| 3.4.4.3 e Edit Simulation Parameters                 | 64  |

| 3.4.4.3.1 e d Edit Display Variables                 | 65  |

| 3.4.4.3.1.1 a Add Display Variable                   | 65  |

| 3.4.4.3.1.2 d Delete Display Variable                | 66  |

|                                                      |     |

| 3.4.4.3.1.3 q Quit                                   | 60  |

| 3.4.4.3.2 e j Edit Jacobian Parameters               | 0/  |

| 3.4.4.3.3 e q Quit                                   | 67  |

| 3.4.4.3.4 e r Edit Reference Voltage Subnode         |     |

| 3.4.4.3.5 e t Edit Time Parameters                   | 68  |

| 3.4.4.4 f File Options                               | 69  |

| 3.4.4.4.1 f d Dump Simulation State                  | 69  |

| 3.4.4.4.2 f i Save INITIALIZATION Section            | 70  |

| 3.4.4.4.3 f I Load INITIALIZATION Section            |     |

| 3.4.4.4.4 f s Save SIMULATION Section                | 71  |

|                                                      |     |

| 3.4.4.4.5 f S Load SIMULATION Section                |     |

| 3.4.4.5 q Quit                                       | 71  |

| 3.4.4.6 s Conduct Simulation                         | 72  |

| 3.4.4.7 u Utilities                                  | 72  |

| 3.4.4.7.1 u e Editor -> emacs                        |     |

| 3.4.4.7.2 u p Plotting -> Norplot                    |     |

| 3.4.4.7.3 u? List Directory                          | 73  |

| 2.4.4.7.4 u. Electrical Comments                     | 73  |

| 3.4.4.7.4 u % Execute System Command                 |     |

| 3.4.4.7.5 u + Screendump to default printer          |     |

| 3.5 Special Considerations                           | 75  |

| 3.5.1 Designing the Network                          | 75  |

| 3.5.2 Selection of Time Increments                   | 75  |

| 3.5.3 Using the SIMULATION File                      |     |

| 3.5.4 Using the INITIAL File                         | 77  |

| 3.6 Adding DEVICE Descriptions                       | 77  |

| 5.0 Adding DEVICE Descriptions                       | //  |

| CHAPTER 4 DEVELOPMENT OF SHIPBOARD ELECTRICAL        |     |

|                                                      |     |

| COMPONENT MODELS                                     | 78  |

| 4.1 Transmission Line Model                          | 79  |

| 4.2 Resistive - Reactive Load Model                  | 82  |

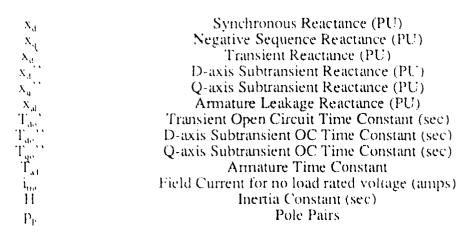

| 4.3 Synchronous Machine Model                        | 85  |

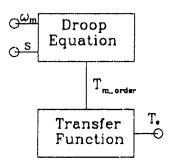

| 4.4 Speed Governor                                   | 91  |

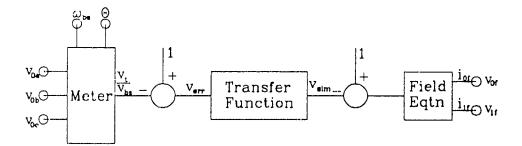

| 4.5 Voltage Regulator Model                          | Ó3  |

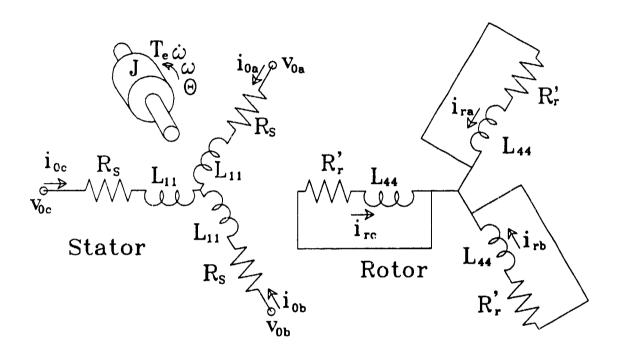

| 4.6 Induction Motor Model                            | 07  |

| 4.0 Induction Motor Model                            | 3/  |

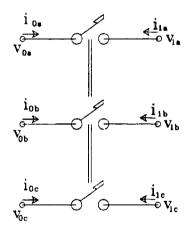

| 4.7 Three Phase Switch Model                         |     |

| 4.8 Circuit Breaker Model                            | 105 |

|                                                      |     |

| CHAPTER 5 SIMULATION RESULTS                         |     |

| 5.1 50 HP Induction Motor Start Up                   |     |

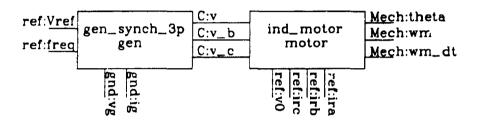

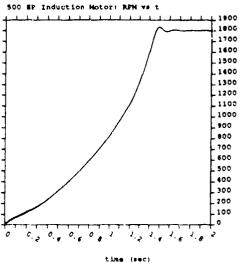

| 5.2 500 HP Induction Motor Start Up                  | 114 |

| 5.3 Synchronous Generator: Switched Load             |     |

| 5.4 Synchronous Generator: Two Phase Fault           | 124 |

| 5.5 Synchronous Generator: Three Phase Fault         | 120 |

|                                                      |     |

| 5.6 Paralleled Synchronous Generators: Switched Load |     |

| 5.7 Paralleled Synchronous Generators: Switched Load | 140 |

|                                                      |     |

| CHAPTER 6 CONCLUSIONS                                | 144 |

| 6.1 Assessment of SEPSIP                             | 144 |

| 6.2 Future Improvements                              | 145 |

|------------------------------------------------------|-----|

| 6.2.1 Variable Time Step                             | 145 |

| 6.2.2 Replace Gaussian Elimination                   | 145 |

| 6.2.3 Reuse of Jacobian Matrix                       | 146 |

| 0.2.5 Reuse of Jacobian Marix                        | 146 |

| 6.2.4 Output Variables and Output Subnodes           | 140 |

| 6.2.5 Action Files                                   | 140 |

| 6.2.6 Integrated Graphics                            | 148 |

| 6.2.7 Implement external variable 'types'            | 148 |

| 6.2.8 Optimization for speed                         | 149 |

| 6.2.9 Check for Recursive INCLUDE Files              | 149 |

| 6.2.10 Break Key                                     | 149 |

|                                                      |     |

| References                                           | 151 |

| **CICIONCOS                                          | 101 |

| APPENDIX A GLOSSARY                                  | 153 |

| APPENDIA A GLOSSARI                                  | 133 |

| ADDENING DESIGNATIONS FOR ADDING DESIGNS             | 157 |

| APPENDIX B INSTRUCTIONS FOR ADDING DEVICES           | 157 |

| B.1 Write Device Driver Routines                     | 15/ |

| B.1.1 Arguments                                      | 157 |

| B.1.2 Select number and types of variables           | 159 |

| B.1.3 Calculate Implicit variables                   | 159 |

| B.1.4 Calculate State Variables                      | 159 |

| B.1.5 Calculate External Output Variables (optional) | 160 |

| B.1.6 Calculate Jacobian Matrix (optional)           | 160 |

| D. 1.0 Calculate Jacobian Matrix (optional)          | 160 |

| B.2 Modify Device Input File (three_phase input)     | 100 |

| B.3 Modify penner.h                                  | 101 |

| B.4 Modify Makefile                                  | 162 |

| B.5 Recompile SEPSIP                                 | 163 |

|                                                      |     |

| APPENDIX C DEVICE DRIVER CODE                        | 164 |

| C.1 f_t_line_3p.c                                    | 165 |

| C.2 f_rl_wye.c                                       | 170 |

| C.3 f_synch_mach.c                                   | 175 |

| C.4 f_speed_reg.c                                    | 183 |

| C.4 I_specu_leg.c                                    | 107 |

| C.5 f_volt_reg.c                                     | 10/ |

| C.6 f_ind_motor.c                                    | 191 |

| C.7 f_switch_3p.c                                    | 196 |

| C.8 f_breaker_3p.c                                   | 201 |

| C.9 f_spst_switch.c                                  | 208 |

| C.10 f_gen_synch_3p.c                                | 211 |

| C.11 penner.h                                        | 216 |

| C.12 three_phase.input                               | 220 |

| C.12 tillee_pilase.iiiput                            | 220 |

| C.13 one_phase.input                                 | 230 |

| ADDENING TO MENTLINDINGS CONT.                       | 225 |

| APPENDIX D MENU DRIVER CODE                          |     |

| D.1 menu.c                                           | 235 |

| D.2 sepsip_util.menu                                 | 241 |

|                                                      |     |

| APPENDIX E PORTABILITY CONSIDERATIONS                | 242 |

|                                                      |     |

| ADDENIOLY E CEDCID COLIDCE CODE                      | 243 |

# Table of Figures

| 44.5                                                |     |

|-----------------------------------------------------|-----|

| 2.1-1 Resistor                                      |     |

| 2.2-1 SEPSIP Variables                              |     |

| 2.2.4-1 Diode                                       | 26  |

| 2.6.4.2-1 Manufacturing System Jacobian             |     |

| 3.3-1 Sample SEPSIP Input File                      |     |

| 3.3.1-1 Using the INCLUDE Keyword                   | 48  |

| 3.3.2-1 ELEMENT Description                         | 48  |

| 3.3.3-1 NETWORK Description                         | 49  |

| 3.3.3-2 NETWORK Description Example                 | 51  |

| 3.3.4.2-1 EXTERNAL INPUTS INITIALIZATION Subsection |     |

| 3.3.4.3-1 NODE VOLTAGE INITIALIZATION Subsection    |     |

| 4.1-1 Transmission Line                             | 79  |

| 4.2-1 Resistive - Reactive Load Model               |     |

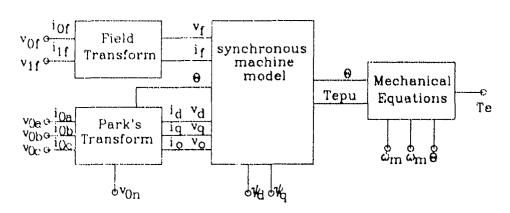

| 4.3-1 Synchronous Machine Model                     |     |

| 4.4-1 Speed Governor                                |     |

| 4.5-1 Voltage Regulator                             |     |

| 4.6-1 Induction Motor Model                         | 97  |

| 4.7-1 Three Phase Switch                            | 102 |

| 4.8-1 Circuit Breaker                               | 105 |

| 4.8-2 Circuit Breaker States                        | 105 |

| 4.8-3 Breaker Transform Table 1                     | 107 |

| 4.8-4 Breaker Transform Table 2                     | 107 |

| 4.8-5 Breaker Transform Table 3                     | 108 |

| 5.1-2 t50.elm : Element Description File            |     |

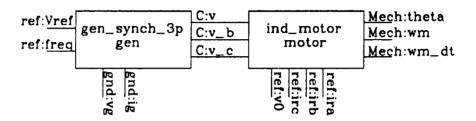

| 5.1-1 50 HP Induction Motor                         | 111 |

| 5.1-3 t50.net: Network Description File             | 111 |

| 5.1-4 t50.init : Initialization File                |     |

| 5.1-5 t50.sim: Simulation File                      |     |

| 5.1-5 t50.all: Input File                           |     |

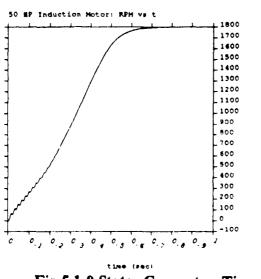

| 5.1-7 RPM vs Time                                   |     |

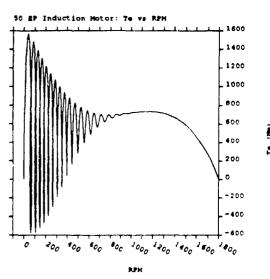

| 5.1-8 Te vs RPM                                     |     |

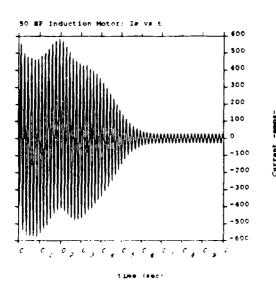

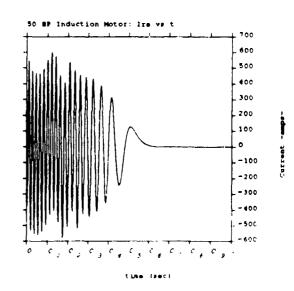

| 5.1-9 Stator Current vs Time                        |     |

| 5.1-10 Rotor Current vs Time                        |     |

| 5.2-1 500 HP Induction Motor                        |     |

| 5.2-2 t500.elm : Element Description File           |     |

| 5.2-3 t500.net : Network Description File           |     |

| 5.2-4 t500.init: Initialization File                |     |

| 5.2-5 t500.sim : Simulation File                    |     |

| 5.2-6 RPM vs Time                                   |     |

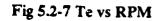

| 5.2-7 Te vs RPM                                     |     |

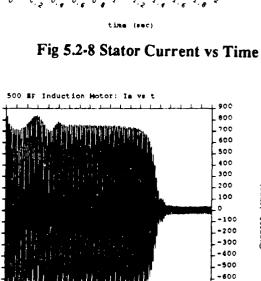

| 5.2-8 Stator Current vs Time                        |     |

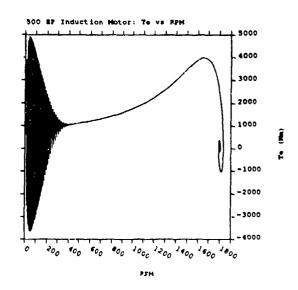

| 5.2-9 Rotor Current vs Time                         |     |

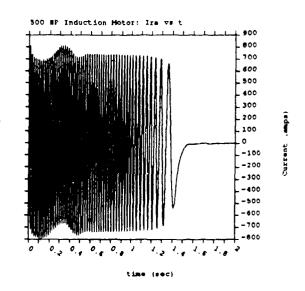

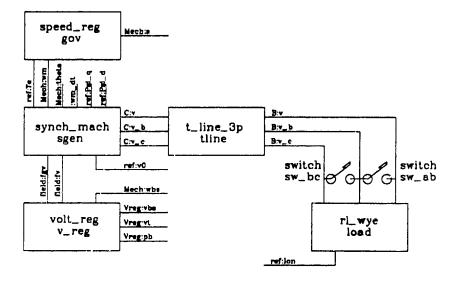

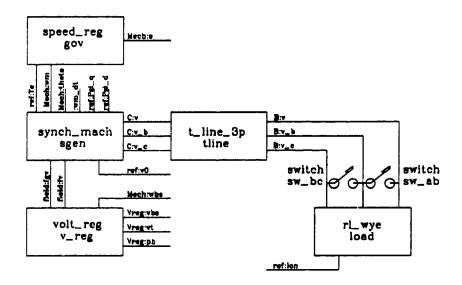

| 5.3-1 Synchronous Generator: Switched Load          | 110 |

| 5.3-2 v.elm : Element Description File              | 110 |

| 5.3-3 v.net : Network Description File              | 110 |

| 5.3-4 v.init: Initialization File                   | 117 |

| 5.3-5 v.sim : Simulation File                       | 120 |

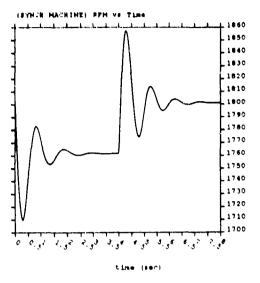

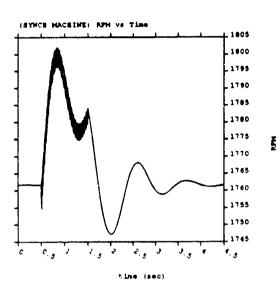

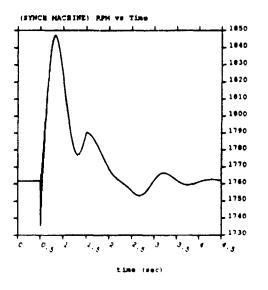

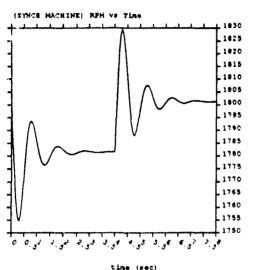

| 5.3-6 RPM vs Time                                   |     |

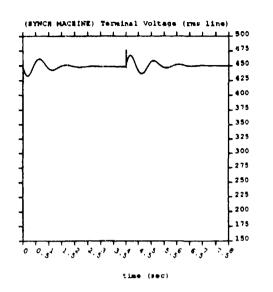

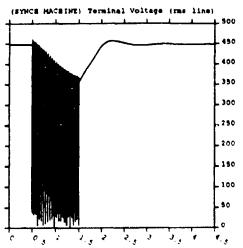

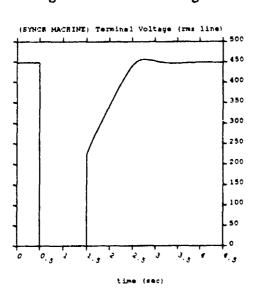

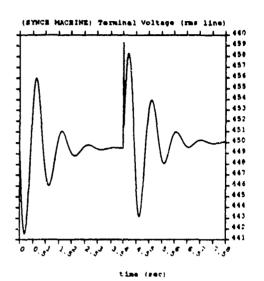

| 5.3-7 Terminal Voltage vs Time                      |     |

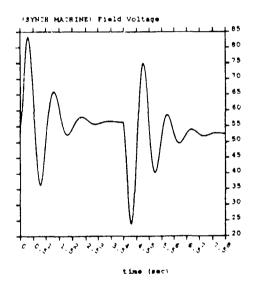

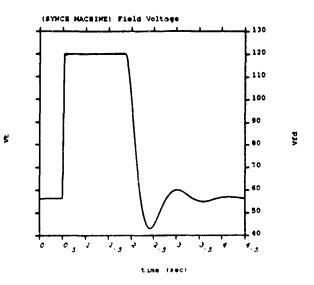

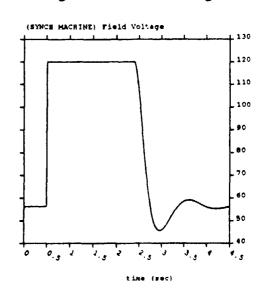

| 5.3-8 Field Voltage vs Time                         | 122 |

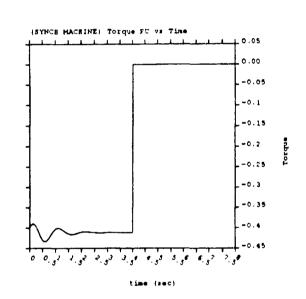

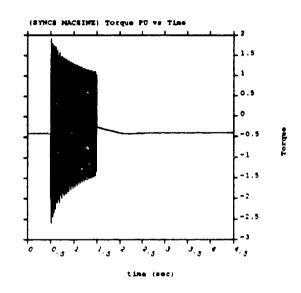

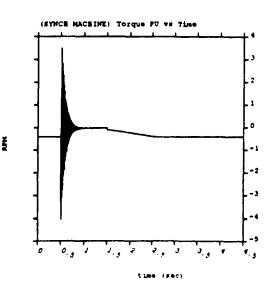

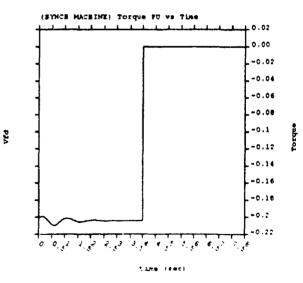

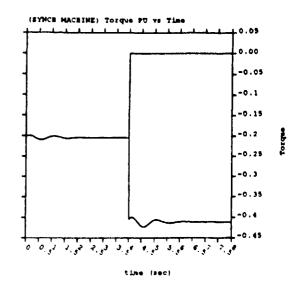

| 5.3-9 Tepu vs Time                                  | 122 |

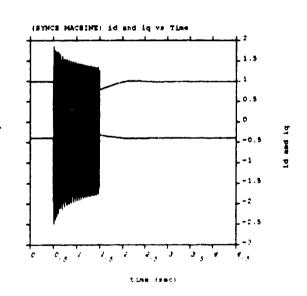

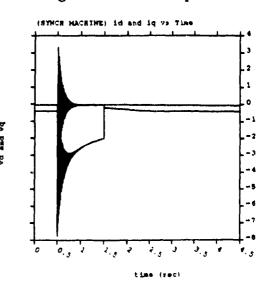

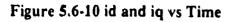

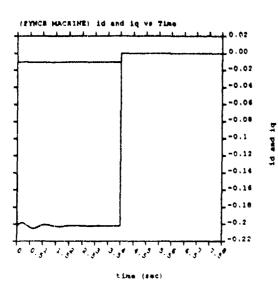

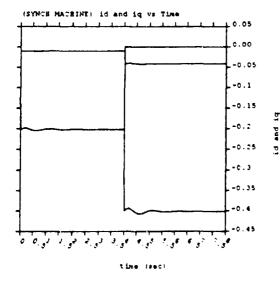

| 5.3-10 id and iq vs Time                            |     |

| J.J-10 10 and 19 vs fille                           | 123 |

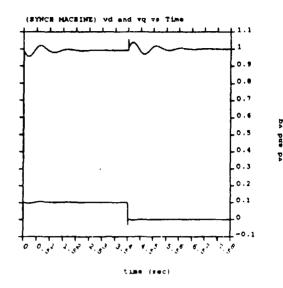

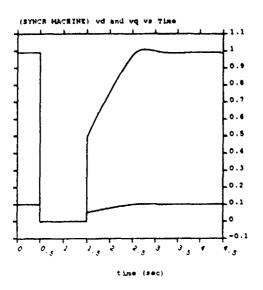

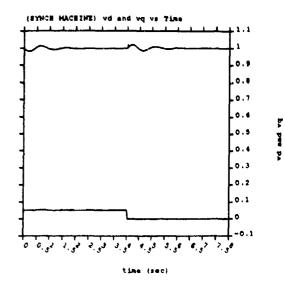

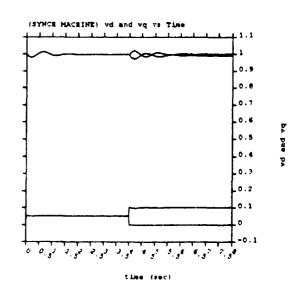

| 5.3-11 vd and vq vs Time                       | 123 |

|------------------------------------------------|-----|

| 5.4-1 Synchronous Generator: Two Phase Fault   | 124 |

| 5.4-2 w.elm: Element Description File          | 124 |

| 5.4-3 w.net: Network Description File          | 125 |

| 5.4-4 w.init: Initialization File              |     |

| 5.4-5 w2.sim; Simulation File                  | 127 |

| 5.4-6 RPM vs Time                              |     |

| 5.4-7 Torque PU vs Time                        | 128 |

| 5.4-8 vd and vq vs Time                        |     |

| 5.4-9 id and iq vs time                        | 123 |

| 5.4-10 Line Voltage                            |     |

| 5.4-11 Field Voltage                           |     |

| 5.5-1 Synchronous Generator: Three Phase Fault | 130 |

| 5.5-2 w3.sim: Simulation File                  | 130 |

| 5.5-3 RPM vs Time                              |     |

| 5.5-4 Torque PU vs Time                        | 131 |

| 5.5-5 vd and vq vs Time                        |     |

| 5.5-6 id and iq vs time                        |     |

| 5.5-7 Line Voltage                             |     |

| 5.5-8 Field Voltage                            |     |

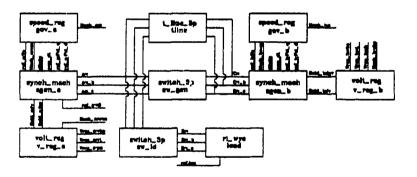

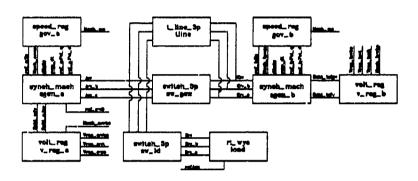

| 5.6-1 Paralleled Synchronous Generators        |     |

| 5.6-2 x.elm: Element Description File          |     |

| 5.6-3 x.net: Network Description File          |     |

| 5.6-4 x init: Initialization File              | 136 |

| 5.6-5 x2.sim : Simulation File                 | 127 |

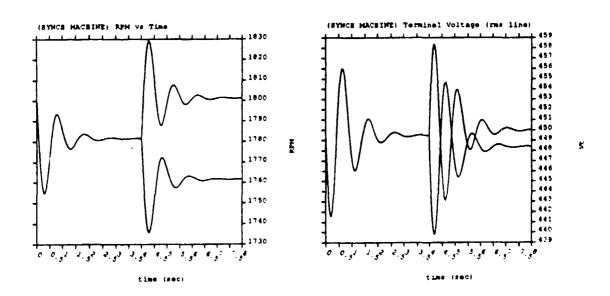

| 5.6-6 RPM vs Time                              | 120 |

| 5.6-7 Terminal Voltage vs Time                 | 130 |

| 5.6.9 Field Valance of Time                    | 120 |

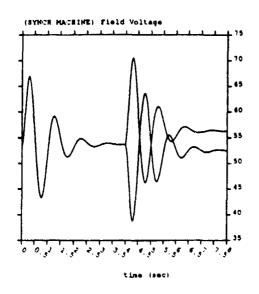

| 5.6-8 Field Voltage vs Time                    | 120 |

| 5.6-10 id and ig vs Time                       | 120 |

|                                                |     |

| 5.6-11 vd and vq vs Time                       | 139 |

| 5.7-1 Paralleled Synchronous Generators        | 140 |

| 5.7-2 x3.sim : Simulation File                 | 140 |

| 5.7-3 RPM vs Time                              | 141 |

| 5.7-4 Terminal Voltage vs Time                 |     |

| 5.7-5 Field Voltage vs Time                    | 142 |

| 5.7-6 Tepu vs Time                             |     |

| 5.7-7 id and iq vs Time                        |     |

| 5.7-8 vd and vq vs Time                        | 142 |

| B.1-1 Device Driver Routine                    | 157 |

| B.1-2 ELEMENT and CONNECT Structures           |     |

| B.2-1 Device Input File Entry                  |     |

| B.4-1 UNIX Makefile Example                    | 163 |

#### **CHAPTER 1**

#### INTRODUCTION

## 1.1 Thesis Objectives

Shipboard electrical power systems in the U.S. Navy are experiencing a number of significant changes. These changes include:

- Solid state frequency converters replacing motor generator sets

- The use of switched DC power supplies by many loads

- Centralized and automated power system control

- More frequent use of electronic motor controllers

- Sensitive electronic equipment requiring high quality 60 Hz. power.

- Electric propulsion

- Large combat systems pulse loads.

Considering the tremendous expense involved with constructing a modern warship, it is necessary to ensure that the incorporation of these changes into the design of the shipboard electrical generation and distribution system can be successfully accomplished with no degradation in the combat capability of the ship. Unfortunately, these changes, along with the small size of the shipboard generation system make the use of many classical methods of analyzing power systems inappropriate. A good analysis requires the recognition of the following properties of the shipboard system:

- The small number of generators (typically only one or two) with the associated small amount of rotational inertia invalidates any assumption of an 'infinite bus' operating at a constant frequency.

- The dynamics of the generator voltage regulators and speed governors have time constants of an order that are important in the study of most disturbances.

- The dynamics of paralleled generators are coupled through the communication of load

sharing and bus voltage information.

- Solid state frequency converters and switched power supplies have non-sinusoidal current characteristics.

- Solid state controllers often greatly modify or even substitute their own dynamics for the dynamics of the motor they are controlling. The controllers may also have non-sinusoidal current characteristics.

- High power pulsed loads for advanced combat systems may become a reality in the near future and deserve study.

- Integrated Electric Drive where propulsion motors and ship's service power are taken from the same distribution system can result in large transients from speed changes in the propulsion system propagating to all of the other loads on the ship.

The purpose of this thesis is to present the theory and design methodology used in the development of a computer simulation tool (SEPSIP: Shipboard Electrical Plant SImulation Program) for analyzing both the steady-state and transient behavior of shipboard electrical power distribution systems.

# 1.2 Modelling Shipboard Electrical Power Systems

Electrical Power systems are not unlike any other electrical network in that they are composed of electrical elements and the topological network connecting the elements. Each of the elements is defined by a number of constitutive equations that relate the voltages and currents of its own terminals. The network on the other hand, is defined by relating the voltages and terminals of different elements through Kirchhoff's voltage and current laws.

# 1.2.1 Elements : Constitutive Equations

The constitutive equations describing an element can be very complicated. In ship board electrical power systems, the equations can take on the form of nonlinear differential equations or even discontinuous functions. Additionally, elements such as generators and motors require the mechanical subsystem be described in detail. Other elements, such as

switches and circuit breakers, are defined by equations depending on the current state of the element. All of these factors contribute to make shipboard electrical power systems difficult to simulate numerically.

# 1.2.2 Networks : Nodal Equations

The nodal equations are the mathematical expression of Kirchhoff's voltage and current laws that define the network topology. Kirchhoff's current law states that the sum of the currents entering a node must equal the sum of the currents leaving a node. Kirchhoff's voltage law states that the voltage at any node is identical for every element attached to it. In themselves, the mathematical representation of Kirchhoff's laws are very simple. However, the resulting system of nonlinear equations is often stiff which implies that the eigenvalues of a linearization of the set of nonlinear equations fall in a range spanning several orders of magnitude.

Stiff systems can be solved numerically, but they require special care. The choice of time increments, integration methods, and simulation time are all affected by how stiff a system is. If a particular differential equation is known to have a very fast time constant, one can ignore the dynamics and always use the *final* value for the variable. If used properly, the Euler Backward method for integrating differential equations approaches the same solution. Fast modes can also be eliminated by a host of other model reduction techniques.

[9] [10] [19] [28] [31] In any case, a tool designed to analyze shipboard systems must incorporate a method for dealing with stiff systems.

<sup>1</sup> An expression of Kirchhoff's Voltage Law that may be more familiar is: The sum of the voltage drops across the elements of a closed loop is equal to zero. The two definitions are not exactly identical but are consistent with one another when one accepts the concept of a voltage being a potential value.

# 1.3 Power System Analysis Computer Tools

#### 1.3.1 Desired Features

In light of the characteristics and potential problems associated with modelling shipboard electrical systems, a computer analysis tool should have the following capabilities:

- \* Ability to solve systems of nonlinear differential equations.

- \* Ability to handle changing network topologies due to the actions of switches and circuit breakers.

- \* Ability to handle discontinuous functions.

- \* Ability to organize the input data into a form that is recognizable as an electrical network.

- \* Ability to easily add or subtract elements from the network description.

- \* Ability to model mechanical subsystems.

- \* Ability to solve stiff systems.

The requirements on a simulation program that these features impose are not trivial. In fact, the author is unaware of any commercially available software package that incorporate all of the listed capabilities. The software that is available can be split into two categories: Programs used for analyzing commercial power utilities, and software packages for solving systems of nonlinear equations.

# 1.3.2 Simulation Programs for Land Based Power Utilities

There are a number of computer programs which can solve different aspects of the power system analysis problem. However none of these programs are optimized for analyzing shipboard systems. Here is a brief summary of several existing programs:

#### 1.3.2.1 EMTP

The Electromagnetic Transients Program (EMTP) [22] is a large-scale network simulation program originally developed by the Bonneville Power Association in the 1960's. It is capable of modeling traveling waves on transmission lines, lumped linear

elements, the saturation of transformers and reactors, the dynamics of synchronous machines as well as other elements of a power network. EMTP handles stiff systems by using the Euler Backward method for integration. In general, the program is optimized for studying the interaction between the dynamics of a number of generators and the dynamics of the interconnecting transmission lines. The dynamics of the loads are not considered important. Unfortunately, the dynamics of loads are important in shipboard systems. Furthermore, EMTP was written in FORTRAN for batch processing and is not very easy to use interactively.

#### 1.3.2.2 POSSIM

The POwer System SIMulator (POSSIM) [19] is a fifty machine transient stability program developed by the General Electric Company. POSSIM uses the results of a network load flow program (LOFYR: LOad Flow and Y-matrix Reduction) as a starting point for a multi-machine simulation. The program allows for dynamics only in the generators and their associated governors and prime movers. While generators and prime movers can be modeled in detail, the transmission line and load equations are purely algebraic. POSSIM also assumes frequency deviations are small. Since load dynamics are important in shipboard electrical systems and frequency deviations can become large, POSSIM's applicability is limited.

#### 1.3.2.3 MANSTAB

The MAchine and Network STABility (MANSTAB) [19] program is an extension of POSSIM which also includes transmission line dynamics. It still does not allow for dynamics in any of its loads. Generally, MANSTAB is suitable for studying high speed dynamics and does not include governor or prime mover models. For this reason, MANSTAB is not suitable for simulating shipboard systems.

#### **1.3.2.4 MANTRAP**

The MAchine and Network TRAnsient Program (MANTRAP) [4] is a General Electric Company modification of the Bonneville Power Administration's Network Transients Program. It is designed to solve problems concerning the interaction between a synchronous generator, its excitation system, torsional system, and the power transmission system. MANTRAP has a major drawback in shipboard studies in that its assumption of an infinite bus does not hold.

#### 1.3.2.5 LOTDYS

The LOng Term DYnamic Simulator (LOTDYS) [21] is designed to study long term transients of power systems lasting up to 5, 10, or 20 minutes. LOTDYS assumes all the generators operate at the same speed and the generator transient time constants and reactances can be ignored. LOTDYS also ignores excitation system dynamics and load dynamics. Prime mover dynamics, load shedding, and power plant auxiliaries are all modeled in detail. The constraints on LOTDYS severely limits its usefulness in studying shipboard systems.

# 1.3.3 Software Packages for Systems of Nonlinear Equations

Since the models of most electric machines are described as systems of linear or nonlinear equations, it seems reasonable that a general simulation program could be used to simulate the shipboard system. On closer examination however, the presently available software packages are limited in their ability to organize and interconnect several different machine models into a large network. Writing a shipboard electrical system as one totally integrated model invites the introduction of numerous programming errors as the input definition file becomes so large as to be unmanageable. Furthermore, the task of trying to add or subtract elements from the network becomes formidable. The ability to define elements in separate blocks is very important in understanding what a simulation is doing, in debugging an input file, and in making error free changes to the configuration.

Many of the nonlinear equation solving packages are unable to solve implicit equations which is a handicap when trying to interconnect different models. In electrical system simulations, the variables representing the voltages and currents at the terminals of an element must be shared with the other elements that connect to the terminals. If implicit equations are not allowed, one of two methods is normally used to effect this sharing. The first method calls for one device explicitly defining the variable while all the remaining variables implicitly define it. This method is very difficult to implement because it forces one to define variables to be either inputs (implicitly defined) or as outputs (explicitly defined). Problems arise when one tries to connect two outputs or two inputs together (i.e. connecting two generators in parallel). Since in real electrical systems there is no such thing as an input or an output (voltages and currents depend on the properties of all the elements attached to a node), this method imposes an artificial constraint on the network definition.

The other method for interconnecting element models is to define the voltages of every device to be inputs and the currents to be outputs. The voltage at a node is defined as a separate variable whose derivative is equated to function of the sum of the currents entering the node. This function should result in the node voltage having a very fast time constant. Adding the fast time constant however, makes the system stiff and difficult to solve numerically. It also adds dynamics that are purely fictional and in general, defeats the purpose of model reduction.

#### 1.3.3.1 CSMP

IBM's Continuous System Modeling Program (CSMP III) [24] is a general purpose program for solving algebraic and differential equations. The program is not capable of solving implicit equations and is limited in the size of the systems it can model. For these reasons CSMP should not be used to simulate shipboard systems.

#### 1.3.3.2 **SIMNON**

SIMNON is a program for **SIMulating NONlinear** systems of equations which was developed by the Lund Institute in Sweden. It is similar in many respects to CSMP and likewise suffers from its inability to solve implicit equations.

#### 1.3.3.3 ACSL

The Advanced Continuous Simulation Language (ACSL) [1] is another general purpose simulation program like CSMP and SIMNON. While ACSL does have the ability to include implicit equations, its execution time slows tremendously when they are included. ACSL also requires a single input file which can become very large and unmanageable for even moderately sized power systems.

# 1.3.4 SEPSIP (Shipboard Electrical Plant Simulation Program)

Since none of the commercially available software was suitable for studying shipboard electrical distribution systems, the author undertook the task of developing the Shipboard Electrical Plant Simulation Program (SEPSIP) which incorporates all of the desired features listed in section 1.3.1. SEPSIP solves the problem of interconnecting device models by forcing all of the device electrical variables to be input variables. This approach mathematically isolates all of the elements of the network from one another. A separate network description specifies how the different input variables relate to one another. The network description provides values for all of the input variables for every element. The elements in turn, provide feedback in the form of implicit variables to the network description as to how well these input variables solve the constitutive equations defining the element. The manner in which this is accomplished is discussed in chapter 2.

The equations defining an electrical device are subroutines of SEPSIP written in the C programming Language. This allows for very detailed and complex models to be incorporated in simulations. It also requires a detailed knowledge of programming in C. Once a device description has been written however, its inclusion into network descriptions

is easy. The concept of using SEPSIP is that initially a number of device descriptions are written to describe the various elements of a shipboard system. Once this library of devices has been created, simulations can be conducted by constructing networks interconnecting the devices models selected from the established library.

## 1.4 Significance of Thesis

The discussions presented in the previous sections demonstrate the need for a computer analysis tool for simulating shipboard electrical distribution systems. SEPSIP, the program written as a part of this thesis, is capable of conducting the desired simulations if time is not a constraint. The organization and user interface of SEPSIP has been optimized to simulate electrical distribution systems such as those found onboard warships. SEPSIP still requires optimization to improve the speed in which it completes simulations. In this regard, potential improvements to SEPSIP are included in chapter 6.

The general nature in which SEPSIP organizes and solves systems of nonlinear equations has applications outside of electrical power engineering. Any physical system composed of a topological network interconnecting nonlinear dynamic elements can be modelled with SEPSIP. The author in fact, has successfully used SEPSIP to conduct a nonlinear dynamic simulation of the motions of a submarine in response to control surface deflections. For this simulation devices were created which related the motions of the bare hull and various appendages to the forces and torques on the center of the submarine. The results of this simulation correctly predicted dynamic responses that can not be derived from conventional linear theory.

#### 1.5 Outline of Thesis

The following chapters are organized to correspond to the four design elements used to create SEPSIP. The second chapter describes the theory and strategy that define the requirements and properties of SEPSIP. The third chapter is a "user's manual" that describes how the requirements of chapter 2 were implemented. Chapter four presents eight device

descriptions created for SEPSIP to demonstrate its usefulness. Chapter five uses the devices of chapter four to conduct actual simulations and where possible, to verify the results from SEPSIP with known responses.

Chapter six provides an assessment of SEPSIP and lists a number of possible improvements for the program. The appendices provide listings of source code and instructions for adding new device descriptions to SEPSIP.

#### CHAPTER 2

#### THEORY OF THE COMPUTATIONAL METHOD

# 2.1 General Strategy

The principle underlying the organization of SEPSIP is that the constitutive relations of the elements of a power system should be separated from the nodal equations describing the network interconnecting the elements. In electrical systems, a node is the electrical connection between two or more elements. The current entering or leaving a node must conform to Kirchhoff's Current Law which states that the sum of the currents entering a node is equal to the sum of the currents leaving the node. Additionally, the voltage at a node is the same for every element attached to it. The role of the constitutive relations is to relate the voltages of the nodes an element is connected to, to the currents resulting from the element that enter and leave those same nodes. These principles are fulfilled in SEPSIP by implicitly defining all of the network voltages, currents, and other variables within the constitutive equations defining the individual elements. During each interval of the time domain siraulation, the network variables are systematically varied so that Kirchhoff's current law is always satisfied and until all the implicitly defined constitutive equations are satisfied.

The advantage to this method is that each element can be treated separately from all the other elements. The element models need not be concerned with the other elements they are connected to. It is the responsibility of the network equations to provide input variables that satisfy the element's constitutive relations, and still satisfy the nodal equations. The purpose of defining the constitutive relations implicitly is to provide feedback to the network equations that indicate how far off the input variables provided by the network are from satisfying the constitutive relations. This feedback is used to make corrections to the input variables until all of the constitutive relations are satisfied.

To implicitly define the constitutive equations for the element, they are put into the form:

$$\overline{F}(\overline{x}) = 0 \tag{1}$$

where

$\bar{x}$  = Network Variable Vector

$\overline{F}() = A$  vector operator (potentially nonlinear) that describes the constitutive equations. If an  $\overline{x}$  is chosen so that the constitutive equations are not fulfilled, then [1] will not be true. Instead, an implicit vector can be defined:

$$\overline{I} = \overline{F}(\overline{x}) \tag{2}$$

Each element then, will have its own  $\overline{x}$  and corresponding implicit vector. The role of the network is to choose appropriate  $\overline{x}$  vectors that satisfy the network nodal equations and result in the  $\overline{I}$  vectors having zero length.

#### **EXAMPLE:**

A resistor is a simple example for illustrating this principle of defining constitutive equations implicitly. A resistor is a device that connects two nodes and satisfies Ohm's Law. If we define the voltages at the two nodes to be  $v_0$  and  $v_1$  and the current entering the resistor from the two nodes to be  $i_0$  and  $i_1$ , then the constitutive relations for the resistor are:

$$v_0 - v_1 = i_0 R$$

$$i_0 + i_1 = 0$$

where

R = Resistance

Figure 2.1-1 Resistor

Since a resistor is a linear device, the constitutive relation can be expressed as a matrix equation of the form:

$$\bar{I} = \begin{pmatrix} 1 & -1 & -R & 0 \\ 0 & 0 & 1 & 1 \end{pmatrix} \begin{pmatrix} v_0 \\ v_1 \\ i_0 \\ i_1 \end{pmatrix}$$

Since a resistor is a linear element, the matrix in the above equation is also the Jacobian matrix for the device.

#### 2.2 Device Definitions

In the language of SEPSIP, a device is a mathematical model of a piece of electrical equipment. Examples of devices are models of synchronous generators, transmission lines, breakers, induction motors, and resistive loads. A device is differentiated from an element in that an element is a particular example of a device. For example, element GTG1 may represent the 2000 KW gas turbine generator located in the forward engine room of a destroyer. Part of GTG1's description would be that it is a device of type KY103 which indicates which equations should be used to model GTG1. There could also be a GTG2 of type KY103. A device is characterized by the equations which relate the variables that represent the interaction of the device with everything else external to itself. Examples of device variables include voltages, currents, speeds, forces, torques, position of switches, temperature, and pressure. These variables can be organized into a number of categories according to the nature of their interaction between the device and the world external to the device.

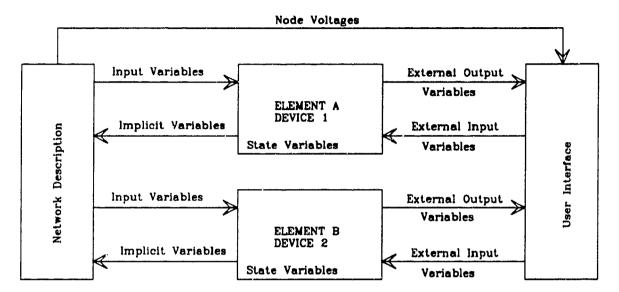

Figure 2.2-1 SEPSIP Variables

SEPSIP Variable Interactions

# 2.2.1 Input Variables: Interacting with the Network

Input variables are those variables which interact with other devices through the network description. The network description consists of a number of nodes each having one or more subnodes. The node itself has no mathematical significance, it merely organizes subnodes into easily understood groups. The subnodes on the other hand, specify which network law should be applied to the input variables attached to it. Every input variable is assigned to one and only one subnode of a node. Each subnode however, can have an unlimited number of input variables assigned to it. There are four types of subnodes to which a variable can be connected to: voltage subnodes, reference voltage subnodes, current subnodes and reference current subnodes.

As an example, a node connecting a three phase motor to a transmission line would contain six subnodes: 3 voltage subnodes to relate each of the voltage phases and 3 current subnodes to relate each of the current phases.

# 2.2.1.1 Voltage Subnodes

All of the input variables attached to a voltage subnode are assigned the same value at all times. This voltage subnode value becomes one of the system variables that must be solved for. Although primarily used for communicating voltages, a voltage subnode can also be used to communicate other information between two devices. Examples include load sharing information and load shedding information.

## 2.2.1.2 Reference Voltage Subnodes

A reference voltage subnode is identical to a voltage subnode with the exception that the subnode voltage is specified as a fixed value and therefore is not a system variable. A reference voltage subnode must be used to set the ground potential, and may be used to set fixed operating points for certain elements.

#### 2.2.1.3 Current Subnodes

A current subnode relates the variables attached to it by a conservation law which in electrical terms is known as Kirchhoff's Current Law. This law states that the sum of the variables attached to a current subnode is identically zero. In SEPSIP, this is accomplished by assigning the first variable attached to a current subnode the negative sum of the other attached variables. All of the input variables after the first one connected to the current subnode become system variables that must be solved for. The convention for current direction is that the current always enters the device and leaves a subnode.

#### 2.2.1.4 Reference Current Subnodes

A reference current subnode does not satisfy Kirchhoff's Current Law. All of the input variables attached to it become system variables. In most simulations, Kirchhoff's Current Law at one subnode is a linear combination of all the Kirchhoff's Current Law equations from the other current subnodes. To specify the law again would result in either a system with too many implicit variables, or one which has a singular system Jacobian matrix.

#### 2.2.2 Parameters

Parameters are variables that do not change through out a simulation. They are used when defining an element to customize a device model to fit the properties of a particular electrical component. Examples of parameters are resistances, inductances, capacitances, time constants, bias voltages, and saturation points.

# 2.2.3 Implicit Definition of Input Variables

An important requirement for the equations describing a device is that the input variables must be implicitly defined. The network balancing algorithms determine the values the input variables take on. The device description provides information (feedback) as to how closely the implicit equations are satisfied through implicit variables. Implicit variables have a value of zero when their corresponding implicit equations are satisfied. One way to look at this process is to view a device as a transfer function between the input variables and the implicit variables. The Network then uses the implicit variables to iteratively generate the input variables until the implicit variables are driven to zero.

# 2.2.4 Implicit Variable Selection: Rotating and Translating Axes

One has a lot of latitude in defining the implicit variables. The easiest method is to write the constitutive equations, move everything over to one side, then define this quantity to be the implicit variable. This is the technique used in the last example which modelled the resistor. Unfortunately, this method can result in numerical instability when dealing with nonlinear devices.

Figure 2.2.4-1 Diode

$$\begin{array}{c|c} \underline{v_0} & \underline{v_i} \\ \underline{i_0} & \underline{i_1} \end{array}$$

Take a diode for example. A simple model for a diode is a switch that allows positive current to flow when the voltage across it 0.6 volts. Once current is flowing through the diode, the voltage drop across it is maintained at 0.6 volts. As with the resistor, the input variables are defined:  $v_0$  and  $v_1$  for the voltages, and  $i_0$  and  $i_1$  for the currents. The constitutive relations are:

$$i_0 = 0$$

:  $v_0 - v_1 < 0.6$

$v_0 - v_1 = 0.6$  :  $i_0 > 0$

$i_0 + i_1 = 0$

The easy method of defining the constitutive equations would be to define  $I_0$  and  $I_1$  to be:

$$I_0 = \begin{cases} i_0 & : \quad v_0 - v_1 < 0.6 \\ v_0 - v_1 - 0.6 & : \quad v_0 - v_1 > 0.6 \end{cases}$$

$$I_1 = i_0 + i_1$$

This definition unfortunately, works badly in many circumstances. To begin with, the definition allows for negative current to flow when the diode is forward biased. Another problem is that the implicit variable  $I_0$  is discontinuous at the boundary where  $\mathbf{v}_0 \cdot \mathbf{v}_1 = 0.6$ . This type of discontinuity will usually cause much difficulty when trying to iteratively solve equations with most standard techniques (Such as the Newton Raphson method used in SEPSIP). In general, keeping the highest possible order derivative continuous across a boundary will help tremendously in achieving a numerically stable solution.

The definition of  $I_0$  can be greatly improved by defining a new set of axes centered on the boundary point ( $v = v_0 - v_1 = 0.6$  and  $i_0 = 0$ ) and rotated 45 degrees. The transformation matrix to the new x and y variables is given by:

$$\begin{pmatrix} x \\ y \end{pmatrix} = \frac{\sqrt{2}}{2} \begin{pmatrix} 1 & 1 \\ -1 & 1 \end{pmatrix} \begin{pmatrix} v_0 - v_1 - 0.6 \\ i_{i_1} \end{pmatrix}$$

The constitutive equation for  $I_0$  becomes:

$$y = |x|$$

I<sub>0</sub> can then be defined to be:

$$I_0 = y - |x|$$

This definition for  $I_0$  is continuous. The discontinuity has been moved to the first derivative. For simple simulations where the voltage across the diode is not changing very rapidly compared to the simulation time increment, this definition for  $I_0$  will normally work. Normally, one would like to have even higher order derivatives continuous to ensure numerical stability. This can only truly be done in this case by changing the constitutive equation to reflect more characteristics of a physical diode.

Even if the constitutive law of the diode is changed to make the slope continuous, the method outlined above for rotating axes should still be used. This is because most numerical methods rely on the partial derivatives of the implicit variables with respect to the input variables in the form of a Jacobian Matrix to update the last guess for the input variable. A very steep slope results in a Jacobian element being very large and the potential of having a floating point overflow when the Jacobian matrix is created or inverted. An overflow can also occur when the corrections to the input variables cause the recalculated implicit variable to overflow. In general, when the slope of the v/i characteristic has a section with a very steep slope, the axes should be rotated so that the maximum slope is minimized.

Another consideration when defining implicit variables is choosing the magnitude correctly. Since an exact solution which results in all the implicit variables being identically zero may not be possible due to time constraints or round off error, every iterative scheme relies on a method for determining when the implicit variables are close enough to zero. One way is to compare the root mean square of the implicit variables with a preset number. If this method is used, the order of magnitude of all the implicit variables should be the same for the same order of magnitude inputs. Otherwise, certain variables would be allowed to

vary more than other variables. For example, one voltage may be known to within a 1% error while another may be known to within a 0.1% error. Of course, if this effect is desired, one can easily weight an implicit variable by an arbitrary constant.

# 2.2.5 Data Storage: State Variables

A number of device models require the condition of the device during the last time increment be known. This information is conveyed to the model through state variables. Examples of states include the voltage and current of a capacitor or inductor, position of switches, position of breakers, time since a specific event occurred, and peak values of specific variables. One could conceivably use the state variables to store the time history of a variable to determine averages or other statistical or spectral properties.

# 2.2.6 External Inputs

External Inputs allow the user to interact with device models. The user can create a queue which contains the values an external input takes on at specified times. Uses for external inputs include position of switches, control waveforms, reference voltages, input waveforms from another program, controlling the configuration of an element.

# 2.2.7 External Outputs

External Outputs (along with External Inputs and Voltage Subnode voltages) are variables the user is allowed to monitor during the simulation. Therefore, any quantity that a user may be interested in should be defined as an external output variable. The user still has the choice as to which external outputs to see, so there is no problem with defining a number of output variables. External Output variables can also be stored in files for plotting at a later time.

# 2.2.8 Integration Techniques

Constitutive equations for devices often require the integration of a time derivative.

Any textbook on numerical methods will provide a large selection of integration algorithms along with methods of determining their accuracy and stability. For most simulations

however, there are three methods that work well. The first is the Euler Forward method which is considered an explicit technique since it requires knowldege only of the values of the variables during the past time step.

$$\frac{dx}{dt} = y$$

$$x = x_{old} + y_{old}dt$$

The Euler Forward method is particularly suited for occasions when the differential equation has a strong mode that is much slower than the simulation time step. For systems with many modes, the Euler Forward method can eliminate the need to add additional implicit variables and associated input variables. The drawback of the Euler Forward method is that it requires small time steps for fast modes.

The Euler Backward method is similar to the Euler Forward method with the exception that the variables are evaluated at their present values instead of their old values. The Euler Backward Method is thus an implicit scheme since it uses present values to specify another present value. Since most devices will have several implicit variables to offset input variables, there is usually no extra computational burden in using an implicit scheme.

$$x = x_{old} + dt y$$

The Euler Backward method should normally be used where the possibility exists that the time increment will be longer than the time constant associated with any of the differential equations.

The implicitly defined Trapezoidal Method combines the Euler Forward and Backward methods:

$$x = x_{old} + \left(\frac{dt}{2}\right)(y + y_{old})$$

Whenever possible, one should use the trapezoidal rule due to its greater accuracy. However, when its use requires the addition of input variables to compensate for additional implicit variables, the Euler forward method should be considered.

There also exists a modified Trapezoidal method where the weights for y and  $y_{old}$  differ from 0.5. Weighting y slightly more helps prevent instabilities when the time step approaches the characteristic time constant of the equation.

# 2.2.9 Modelling Transfer Functions

Many devices have components that are modelled as transfer functions using Laplace Transforms. A common example has the form:

$$Y = \frac{As + B}{Cs + D}X$$

Since  $\frac{dX}{dt} = Xs$ , the Trapezoidal Method can be modified to provide an Implicit Variable

$$I_1 = A(x - x_{old}) + \left(\frac{dt}{2}\right)B(x + x_{old}) - C(y - y_{old}) - \left(\frac{dt}{2}\right)D(y + y_{old})$$

This equation can be incorporated in the definition of a more complicated device or can be defined seperately as its own device.

# 2.2.10 Jacobian Construction

SEPSIP uses a Jacobian Matrix to determine the corrections to the input variables in order to drive the implicit variables to zero. The elements of the Jacobian Matrix are the partial derivatives of the implicit variables with respect to all of the input variables. In other words, the Jacobian Matrix gives the slopes of the implicit surface in the directions of each of the input variables.

$$J = \begin{pmatrix} \frac{\partial I_1}{\partial x_1} & \frac{\partial I_1}{\partial x_2} & \frac{\partial I_1}{\partial x_3} & \cdots \\ \frac{\partial I_2}{\partial x_1} & \frac{\partial I_2}{\partial x_2} & \frac{\partial I_2}{\partial x_3} & \cdots \\ \frac{\partial I_3}{\partial x_1} & \frac{\partial I_3}{\partial x_2} & \frac{\partial I_3}{\partial x_3} & \cdots \\ \cdots & & & & & & \\ \end{pmatrix}$$

SEPSIP allows for the Jacobian to be calculated in two different methods. The device description can generate the Jacobian, or the network will approximate it. Normally the device description should create the Jacobian in the interest of speed and control over how it is created. It usually isn't too difficult to come up with analytic expressions describing the partials of the implicit variables. If desired, the network approximates the Jacobian by varying the input variables a small amount in either direction, and noting how much the implicit variables change. The change in the implicit variable divided by the change in an input variable is usually a fair approximation for the partial derivative.

Another advantage to having the device description generate the Jacobian is that the device description doesn't have to generate the real Jacobian matrix. If a value larger in magnitude than the partial derivative is substituted for an element of the Jacobian Matrix, the corrections to the input variables will result in the implicit variable being driven to zero more slowly. This can be advantageous near discontinuities of the constitutive equations and discontinuities in their first derivatives where one may want to retard the transition from one side of a discontinuity to the other.

Replacing an element of a Jacobian Matrix with a value smaller in magnitude than the partial derivative will usually result in a numerically unstable simulation. The corrections to the input variables will be larger than needed to drive the implicit variable to zero. The implicit variable will usually oscillate around zero and grow in magnitude with time.

#### 2.3 ELEMENT DESCRIPTIONS

As described earlier, an element is a particular example of a device. A resistor for example, could be a device, while R11 which is a specific circuit element of type resistor having a resistance of 47 ohms would be an element. Elements are differentiated from each other by their names, device type, and parameter specification. The first section of the input file for SEPSIP contains all of the element definitions and parameter assignments.

# 2.4 NETWORK Description

The network is described by assigning all of the input variables from all of the elements to one and only one subnode. The subnodes in turn, are organized into groups called nodes. The purpose of the subnode is to relate the input variables of one element to the input variables of another variable. The nature of the relationship is determined by specifying the subnode to be either a voltage subnode or a current subnode. The relationship is further modified if the subnode is classified as a reference subnode.

Once the network is specified, system variables can be defined. System variables are members of the smallest subset of the input variables from which all of the other input variables can be derived from by using the relational properties of the subnodes. For a well defined simulation, the number of system variables will equal the total number of implicit variables. If the two numbers are not equal, there will either be many solutions to the simulation, or none at all. SEPSIP will not conduct a simulation unless the number of system variable does indeed equal the total number of implicit variables.

# 2.4.1 Voltage Subnodes

The input variables at a voltage subnode are all set equal to the subnode voltage which is a system variable (unless designated a reference subnode). As its name implies, a voltage subnode's purpose is to specify potential values. The potential value need not only be voltages however. Temperature, pressure, position, deflection, and Boolean states can also be communicated through voltage subnodes.

#### 2.4.2 Current Subnodes

Input variables assigned to a current subnode satisfy Kirchhoff's Current Law (unless designated a reference subnode). The first input variable attached to the current subnode is set equal to the negative sum of all the remaining input variables attached to the subnode. All of the remaining input variables are system variables. The current subnode can therefore

be used where input variables must satisfy a conservation law through the network. Forces, torques, fluid flow rates and power flow can also be handled in addition to electrical current by the current subnode.

#### 2.5 Reference Subnodes

To match the number of implicit variables with the number of system variables or to ensure there is a unique solution, it may be necessary to designate one or more subnodes a reference subnode. If a voltage subnode is specified to be a reference subnode, its value is always set to a user selected preset value. The normal usage would be to declare the ground voltage subnode to be a reference with zero value. Reference voltage subnodes can also be used to simulate power supply voltage busses.

Reference current subnodes do not satisfy Kirchhoff's current law. All of the input variables attached to them are designated system variables. In a closed system (i.e. one where the conservation law applies at every current subnode and in every element through out the system), Kirchhoff's current law at one of the current subnodes will be a linear combination of all the other Kirchhoff's current law equations at the other current subnodes. Therefore, the sum of the currents entering the reference subnode will automatically be zero.

Reference current subnodes also provide a way to leave input variables unterminated. This property can be used by device descriptions to increase the number of implicit variables used to represent the relations defining the device. Normally, when modelling electrical devices, one implicit equation should be provided for each terminal (which corresponds to two input variables: one voltage, and one current). This can be seen if we define:

m = number of terminals (voltage-current pairs) in the system

n = number of subnodes in the system

$r_i$  = number of reference current subnodes

$r_v =$  number of reference voltage subnodes

$N_v$  = number of system variables due to voltage subnodes

$N_i$  = number of system variables due to current subnodes

$N_e$  = number of implicit equations

then

$$N_{v} = n - r_{v}$$

$$N_{i} = in - n + r_{i}$$

$$N_{e} = N_{i} + N_{v} = m - r_{v} + r_{i}$$

Since electrical devices deal with potential differences, rather than with the absolute magnitude of the potential, a reference potential is required to fix one of the nodes. As explained above, a reference current subnode is also required to prevent a singular system. The total number of implicit variables must therefore equal the number of terminals.

If a device description requires more implicit variables than it has terminals, extra input variables must be provided for the excess implicit variables. These variables should be attached to a reference current subnode or to separate voltage subnodes.

### 2.6 Conducting the Simulation

The simulation of the system described by the network description is carried out by solving a system of nonlinear equations at each time increment. Each nonlinear equation corresponds to the definition of an implicit variable which has a value of zero when the system is balanced. To balance the system, an initial guess is first made for all the system variables. For the first time step, the user may specify the guess, otherwise the system variables are all set to zero. For the remaining time steps, the results of the previous time step are used. The total number of independent system variables is considerably smaller than the total number of input variables since a number of the input variables are related through the network definition. For example, all the input variables attached to a voltage subnode are always given the same value. From the system variables, all of the input variables to each of the elements is derived from a description of the network topology. Using these values of the input variables, the implicit variables are calculated for each of the elements. If the mean square value of all the implicit variables are below a specified threshold, then the system is considered balanced. If the mean square value is larger than the threshold, then the system Jacobian matrix is constructed. The system Jacobian matrix consists of the partial derivatives

of the implicit variables with respect to each of the independent system variables. It is fabricated by piecing together the Jacobian matrices of all the elements. Inverting and multiplying the system Jacobian matrix by the vector containing the implicit variables provides a correction to the independent system variables. Once the corrections are subtracted from the independent system variables, the implicit variables are recalculated and the balancing process continues until the system is balanced. Once balanced, results are printed, state variables and external input variables are updated, and the time counter is incremented. In this manner, the simulation is stepped through time.

### 2.6.1 Setup

During the setup stage, two arrays of data structures are created to describe the network topology in a compact form. The first array describes all of the independent system variables and how they relate to the input variables of the individual elements. The second array keeps track of which implicit variable belongs to which element.

Each data structure for the system variable array consists of three subarrays. The number of entries in all three subarrays is equal to the number of input variables associated with the system variable. For a non-reference voltage subnode, all of the input variables attached to it will be associated with one system variable and will therefore each have entries in the three subarrays. A reference voltage subnode has a specified value and therefore is not associated with any of the system variables. For a reference current subnode, all of the input variables attached to it are separate system variables whose corresponding subarrays will contain only one entry. A non-reference current subnode's first input variable is set equal to the negative sum of the remaining input variables. Each of the remaining input variables is associated with one system variable whose subarrays have two elements: The first corresponding to the first input variable; and the second corresponding to the remaining input variable.

The first subarray for each system variable data structure contains integer offsets to the array of elements. The second subarray contains integer offsets to the input variable list within the element description. The third subarray contains a multiplier that is used in constructing the system Jacobian matrix. Normally this multiplier has a value of 1.0, but for the special case of a system variable corresponding to an input variable attached to a non-reference current subnode, the first entry has a value of -1.0 to account for the fact that the first variable associated with a current subnode is the negative sum of the remaining variables.

The data structures for the implicit variable structure array contain only two integer offsets. The first is an offset for the array of elements and the second is the offset in the array of implicit variables for the element. In this manner, all of the implicit variables can easily be referenced.

The setup section also creates an implicit variable cross-reference array in the description of each element that specifies which entry in the implicit variable structure array to which each of the implicit variables of the element corresponds.

#### 2.6.2 Initialization

Before the simulation starts, all of the input variables, state variables, and external input variables are initialized. The initial values for the state variables are actually applied to the time increment immediately before the start of the simulation (old state variables). The input variables are initialized in a two step process. First, an array of system input variables is initialized. Then from the network description, the input variables for all of the elements are derived. If a variable is not explicitly initialized by the user, it is set to zero.

### 2.6.3 Updating External Inputs

The external input variables are updated at each time increment by scanning the external input queue for variable changes that occur before the present system time. All of the external input variables scheduled for a change in value are then updated.

### 2.6.4 Balancing the System

The process of finding a set of input variables that simultaneously satisfies all the network equations and all the implicit equations of the elements is known as balancing the system. The procedure involves calculating the implicit variables, constructing a system Jacobian matrix, calculating corrections to the input variables, and repeating the process until the implicit variables are within tolerable limits of zero.

### 2.6.4.1 Calculating Implicit Variables

The first step in balancing the system is calculating the implicit variables. The functions describing each of the elements are called one at a time and provided with the appropriate input variables. These functions use the input variables along with the external input variables and the state variables calculated in the previous time step to generate the implicit variables.

Once all of the implicit variables have been calculated, they are assembled into an implicit variable array in the order specified in the implicit variable structure array constructed in the setup phase. The mean square value of all the implicit variables is also calculated and if its magnitude is smaller than a predefined amount, the sytem is considered balanced and the program jumps to printing the results out.

### 2.6.4.2 Manufacturing System Jacobian Matrix

The system Jacobian matrix is generated by piecing together the Jacobian matrices for each of the elements. The elemental Jacobian matrix can be generated by the function which also produces the implicit variables, or it can be approximated numerically. The function that returns the implicit variables also returns a flag indicating whether or not the Jacobian matrix was calculated. If the matrix was not constructed, it is manufactured by varying each of the input variables slightly and approximating the partial derivatives by

dividing the differences between the resulting implicit variables by the differences of the input variables. The percentage change and the minimum change in the input variables can be specified by the operator.

The system Jacobian Matrix is constructed one column at a time. Each column has its associated structure in the input variable structure array that specifies which elements and input variables contribute to that column. Knowing the element and the input variable is enough knowledge to extract the appropriate column from the element Jacobian matrix. Which row in the system Jacobian matrix to insert each of the entries of the element Jacobian column is provided by the implicit variable cross reference array. By stepping through each of the structures of the input variable structure array, the entire system Jacobian matrix can be constructed.