DARPA Status Report -- November 1988

Strupul. ?

Sun Young Hwang

Stup (A 94300

### **1. Introduction**

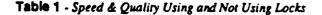

<sup>\*</sup> Simulation now requires vast amounts of cpu time. This severly limits the size of a design that can be tested thoroughly. Incremental simulation is a possible solution to these limit.

Culind pression

Specific synthesis and analysis tools are also proposed. The primary purpose of this project is to allow the designer to make his changes and optimizations at as high a level as possible, but allowing him to observe the ramifications of his changes at a lower level and to help guide the synthesis routines in the selection of a good design. This user guidance is necessary because of the huge design search space faced by synthesis programs.

2. Progess

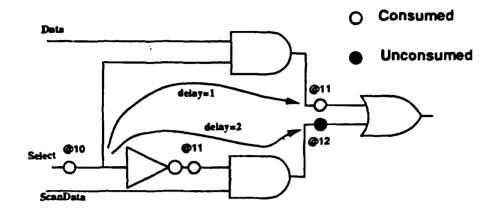

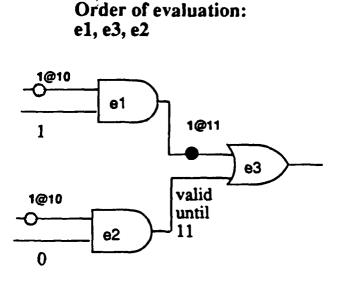

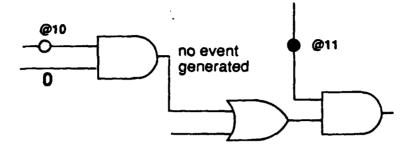

### 2.1. Incremental Simulation

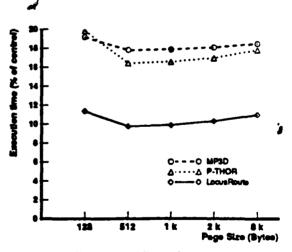

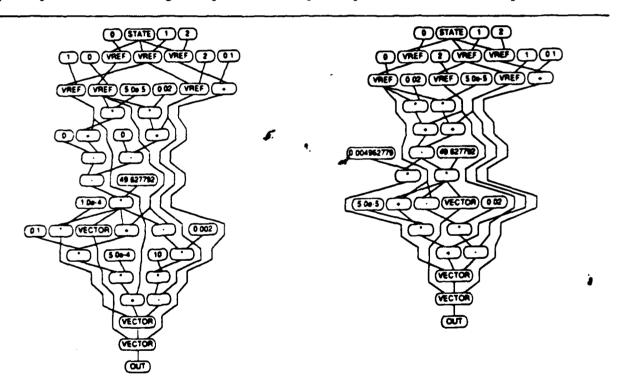

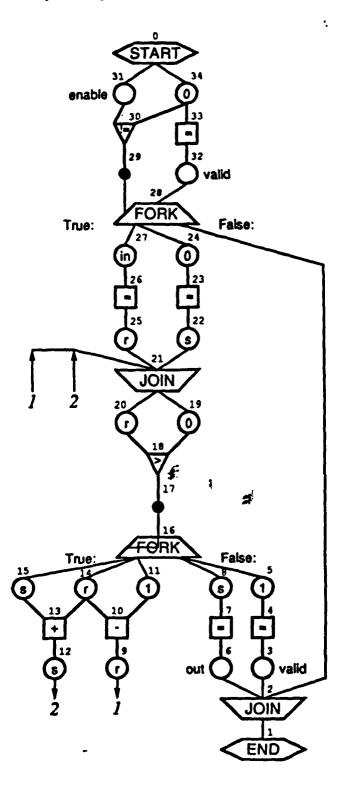

We proposed two incremental simulation algorithms, the incremental-in-space and incremental-in-time algorithms, and implemented them in our THOR simulation system. These two algorithms are comparable to each other: one shows better performance for some circuits over the other, depending on the circuit structure and topology of the circuit under simulation.

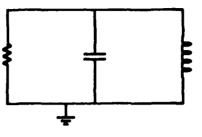

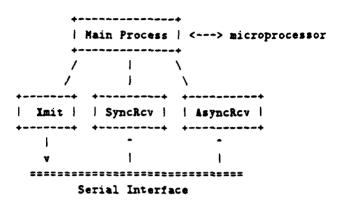

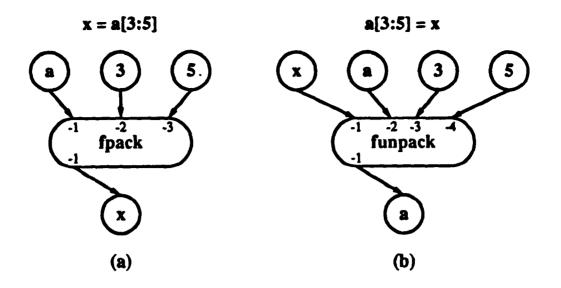

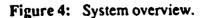

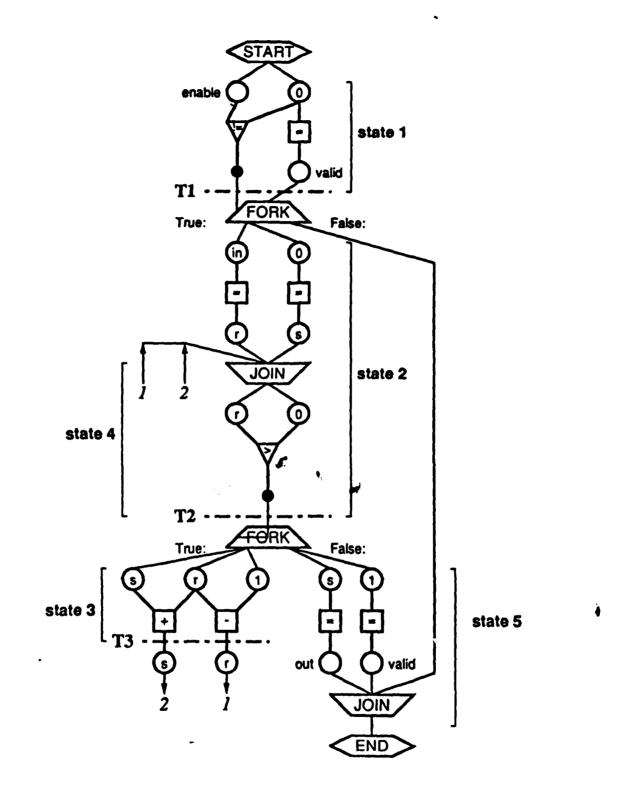

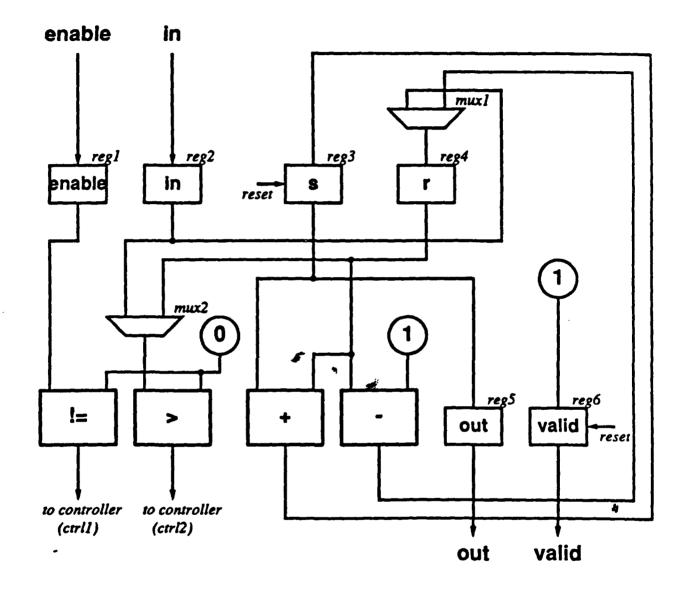

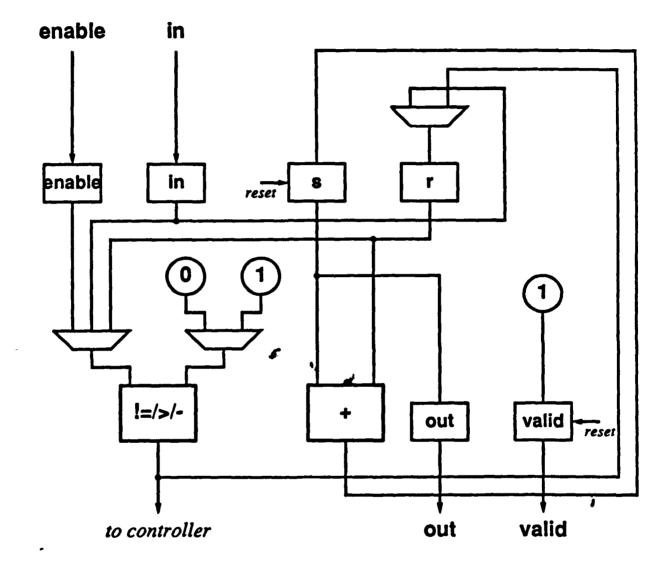

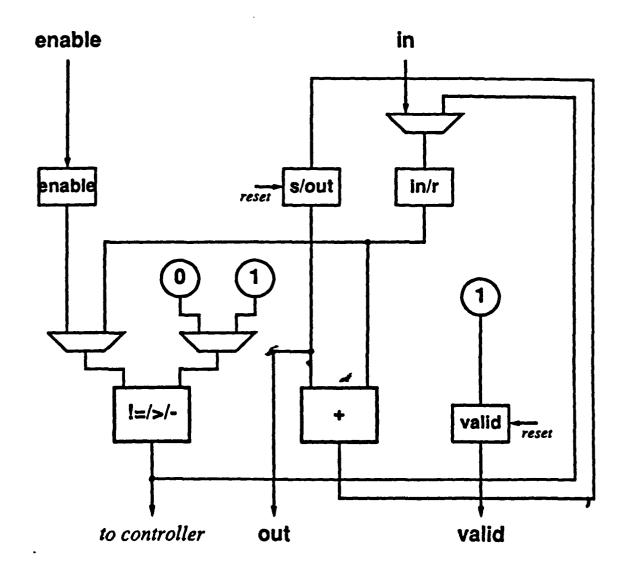

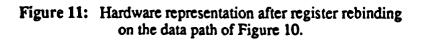

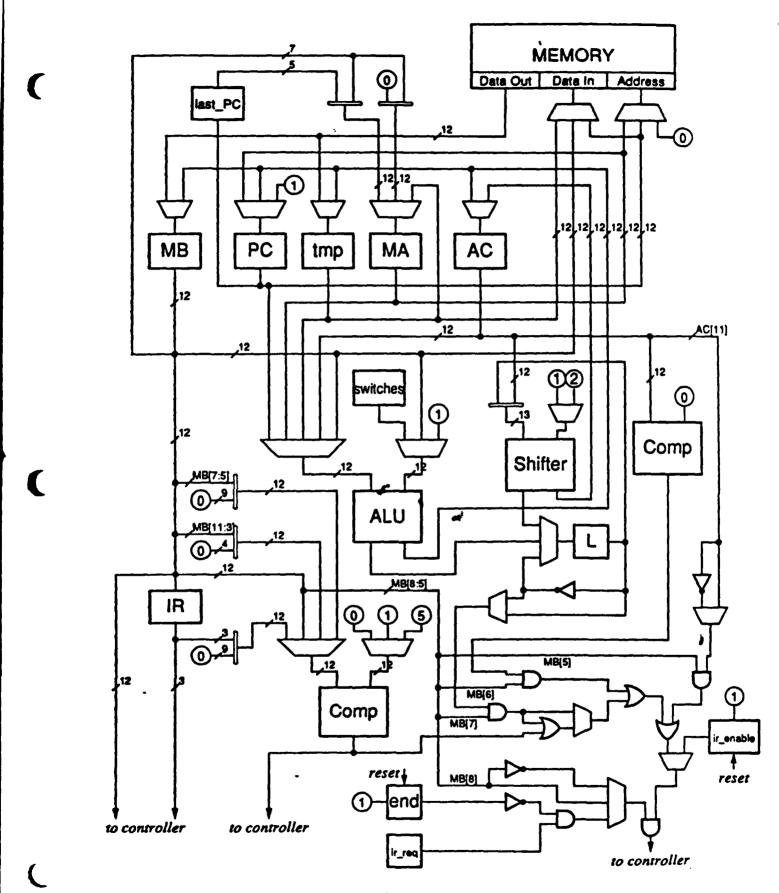

### 2.2. Behavioral Synthesis: Hermod System

The primary purpose of this project is to allow the designer to make changes and optimizations at as high a level as possible, while allowing him to observe the ramifications qf his changes at a lower level and to help guide the synthesis routines in the selection of a good design. This user guidance is necessary because of the huge design search space faced by synthesis programs. The synthesis system displays the data/control flow graph extracted from a functional model on the window screen. And register-transfer representation of a behavioral level description is displayed on the screen after optimization effort by the system.

### 3. Future Work

1. Simulation: More experiment on a hybrid version of the incremental simulator, and install incremental THOR simulator at ~cad directory.

2. behavioral synthesis: Partitioning in behavioral synthesis will be investigated. In the VLSI design, it is important to partition the hardware at the early stage of design to generate good quality designs. Partitioning of algorithmic/behavioral descriptions should provide the synthesizer with the capability to explore design space effectively. Algorithmic partitioning can be achieved by splitting a procedure into multiple processes that can be executed concurrently or be pipelined. Algorithmic partitioner will be designed for the behavioral descriptions written HardwareC, the high level language for Hercules synthesis system.

### 4. Publications

One paper is published and another one is accepted for possible publication around the end of 1988. They are listed below:

[1] S.Y. Hwang, T. Blank, and k. Choi, "Fast Functional Simulation: An Incremental Approach", IEEE Trans. on Computer-Aided Design of Integrated Systems and Circuits, CAD-7 (7), July 1988, pp. 765-774.

[2] M. Odani, S.Y. Hwang, T. Blank, and T. Rokicki, "The Hermod Behavioral Synthesis System", Journal of Systems and Software, to appear in 1989.

Eeb: 18 papers

f

51

COPT

## Suitability of Message Passing Computers for Implementing Production Systems

Anoop Gupta Dept. of Computer Science Stanford University Stanford, CA 94305

### Abstract

Two important parallel architecture types are the shared-memory architectures and the message-passing architectures. In the past researchers working on the parallel implementations of production systems have focussed either on shared-memory multiprocessors or on special purpose architectures. Message-passing computers have not been studied. The main reasons have been the large messagepassing latency (as large as a few milliseconds) and high message reception overheads (several hundred microseconds) exhibited by the first generation message-passing computers. These overheads are too large for the parallel implementation of production systems, where it is necessary to exploit parallelism at a very fine granularity to obtain significant speed-up (subtasks execute about 100 machine instructions). However, recent advances in interconnection network technology and processing node design have cut the network latency and message reception overhead by 2-3 orders of magnitude, making these computers much more interesting. In this paper we present techniques for mapping production systems onto message-passing computers. We show that using a concurrent distributed hash table data structure, it is possible to exploit parallelism at a very fine r granularity and to obtain significant speed-ups from parallelism<sup>1</sup>.

#### **1. Introduction**

Production systems (or rule-based systems) occupy a prominent place in the field of AL They have been used extensively in the attempts to understand the nature of intelligence as well as to develop expert systems spanning a wide variety of applications. Production system programs, however, are computation intensive and run alowly. This slows down research and limits the utility of these systems. In this paper, we examine the suitability of message-passing computers (MPCs) for exploiting parallelism to speed-up the execution of production systems.

To obtain significant speed-up from parallelism in production systems it is necessary to exploit parallelism at a very fine granularity. For example, the average number of instructions executed by subtasks in the parallel implementation suggested in [10] is only about 100. In the past, researchers have explored the use of special-purpose architectures and shared memory multiprocessors to capture this fine-grained parallelism [10, 16, 17, 18, 11, 21]. However, the performance of MPCs for production systems has not

In Procedures of AAAI-88

Milind Tambe Dept. of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

been analyzed. Considering MPCs is important, because MPCs represent a major architectural and programming model in current use. Previously, the communication delays in the MPCs made them impossible to be used for the purpose of exploiting fine grained parallelism. However, recent developments in the implementations of MPCs [3], have reduced the communication delays and the message processing overheads by 2-3 orders of magnitude. The presence of these new generation MPCs such as the AMETEK-2010 [19] makes it interesting to consider MPCs for implementing production systems.

This paper is organized as follows. Section 2 describes the OPS5 production system and the Rete matching algorithm used in implementing it. Section 3 describes recent developments in the MPCs and presents the assumptions about their execution times which we will use in our analysis. Section 4 presents our scheme for implementing OPS5 on the MPCs. We then evaluate its performance and compare it with other parallel implementations of production systems.

# 2: Background

#### 2.1. OPS5

An OPS5 [2] production system is composed of a set of *if-then* rules called productions that make up the *production memory*, and a database of temporary assertions, called the *working memory*. The individual assertions are called working memory elements (WMEs), which are lists of attribute-value pairs. Each production consists of a conjunction of condition elements (CEs) corresponding to the *if* part of the rule (the left-hand side or LHS), and a set of actions corresponding to the *then* part of the rule (the right-hand side or RHS).

The CEs in a production consist of attribute-value tests, where some attributes may contain variables as values. The attribute-value tests of a CE must all be matched by a WME for the CE to match; the variables in the condition element may match any value, but if the variable occurs in more than one CE of a production, then all occurrences of the variable must match identical values. When all the CEs of a production are matched, the production is satisfied, and an instantiation of the production (a list of WMEs that matched it), is created and entered into the *conflict set*. The production system uses a selection procedure called *conflict-resolution* to choose a production fires, the RHS actions associated with that production are executed. The RHS actions can add, remove or modify WMEs, or perform I/O.

The production system is executed by an interpreter that repeatedly cycles through three steps: match, conflict-resolution, and act. The matching procedure determines the set of satisfied

<sup>&</sup>lt;sup>1</sup>This research was sponsored by Encore Computer Corporation, Digital Equipment Corporation and by the Defense Advanced Research Projects Agency (DOD), ARPA Order No. 4976 under contract F33615-87-C-1499 and monitored by the Air Force Avionics Laborstory. Ansop Gupta is supported by DARPA contract N00014-87-K-0828 and an award from the Digital Equipment Corporation. The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of Encore Computer Corporation, Digital Equipment Corporation and the Defense Advanced Research Projects Agency or the US Government.

productions, the conflict-resolution procedure selects the highest priority invantiation, and the act procedure executes its RHS.

#### 2.2. Rete

Rete [7] is a highly efficient match algorithm that is also suitable for parallel implementations [9]. Rete gains its efficiency from two optimizations. First, it exploits the fact that only a small fraction of working memory changes each cycle by storing results of match from previous cycles and using them in subsequent cycles. Second, it exploits the commonality between CEs of productions, to reduce the number of tests performed.

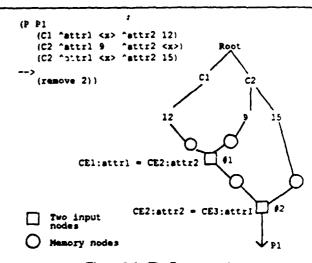

Rete uses a special kind of a data-flow network compiled from the LHSs of productions to perform match. The network is generated at compile time, before the production system is actually run. The entities that flow in this network are called *tokens*, which consist of a *tag*, a *list of WME time-tags*, and a *list of variable bindings*. The tag is either a + or a - indicating the addition or deletion of a WME. The list of WME time-tags identifies the data elements matching a subsequence of CEs in the production. The list of variable bindings associated with a token corresponds to the bindings created for variables in those CEs that the system is trying to match or has already matched.

There are primarily three types of *nodes* in the network which use the tokens described above to perform match:

- Constant-test nodes: These are used to test the constantvalue attributes of the CEs and always appear in the top part of the network. They take less than 10% of the time spent in Match.

- 2. Memory nodes: These store the results of the match phase from previous cycles as state. This state consists of a list of the tokens that match a part of the LHS of the associated production. This way only changes made to the working memory by the most recent production firing have to be processed every cycle.

- 3. Two-input nodes: These test for joint satisfaction of CEs in the LHS of a production. Both inputs of a two-input node come from memory nodes. When a token arrives from the left memory, i.e., on the left input of a two-input node, it is compared to each token stored in the right memory. All token pairs that have consistent variable bindings are sent to the successors of the two-input node. Similar action occurs when a token arrives from the right memory. We refer to such an action as a node-activation.

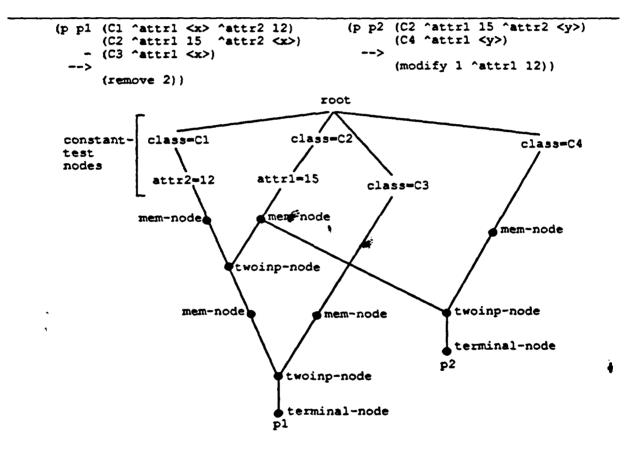

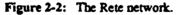

Figure 2-1 shows the Rete net for a production named P1.

### 3. Message-Passing Computers and Assumptions

MPCs are MIMD computers based on the programming model of concurrent processes communicating by message passing. There is no global shared memory and hence communication between the concurrent processes is explicit as in Hoare's CSP [12], though not necessarily synchronous. The early MPCs such as the Cosmic Cube [20] had a high network latency of about -2 millisecond (ms) and a high overhead of message handling of about -300 microseconds ( $\mu$ s). As a result, it was impossible to exploit parallelism at the fine granularity of 50-100  $\mu$ s as is necessary in production systems.

Recent developments in MPCs such as worm-hole routing [4] have reduced the network latencies to 2-3 µs and the use of special processors such as the MDP (Message Driven Processor) [5] can

Figure 2-1: The Rete network.

potentially reduce the message reception overhead by an order of magnitude. With today's VLSI technology, it is possible to construct MPCs with thousands of processing nodes and hundreds of megabytes of memory [3]. Thus very fine grain parallelism can now be exploited easily with the MPCs.

This raises the issue of whether production systems can be implemented efficiently on the MPCs to give good speedups, which we analyze in detail in this paper. For the purpose of this analysis, we assume a 32-ary 2-cube architecture (1024 nodes), with a 4 MIPS processor at each node similar to the MDP. The various times that required for our analysis are as follows. The latency of wormhole routing is given by

$$\mathbf{I}_{\mathbf{A}} = \mathbf{T}_{\mathbf{C}} (\mathbf{D} + \mathbf{L} / \mathbf{W})$$

Where ----

£

| τ <sub>c</sub> | Channel Delay, assumed to be 50 nanoseconds (ns), as in [3].                                                                                                                                           |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| w              | Channel Width, assumed to be 16 bits.                                                                                                                                                                  |

| L              | Length of the message in bits.                                                                                                                                                                         |

| D              | Distance or number of hops traveled by the message. If two processing nodes are selected at random in a k-ary n-cube, then number of hops is $n^{\circ}(k^2 - 1)/3k \approx 22$ for our 32-ary 2-cube. |

We assume that the MDP is driven by a 100 ns clock and that the time to execute a send (broadcast) command is

#### T\_= (5 + M\*Q) alock cycles.

where a message of Q words is to be sent to N sites [5]. The overhead of receiving messages is assumed insignificant [5]. Thus there are two delays associated with a message:  $T_{a}$  in transmission,  $T_{ab}$  in its communication.

#### 4. Mapping Rete on the MPC

In this section we describe our mapping of Rete on the MPCs. We draw heavily from our previous work with the *PSM* implementations of production systems on shared-memory multiprocessors [9, 10, 21].

One possible scheme for implementing OPS5 on the MPCs arises

from viewing Rete in an object-oriented manner, where the nodes of Rete are objects and tokens are messages. This scheme maps a single object (node) of Rete onto a single processor of the MPC. However, there are two serious problems: (1) The mapping requires one processor per node of the Rete net, and the processor utilization of such a scheme is expected to be very low; (2) Often, the processing of a WME change results in multiple activations of the same Rete node, which in the above mapping would be processed sequentially on the same PE, thus causing that PE to be a bottleneck.

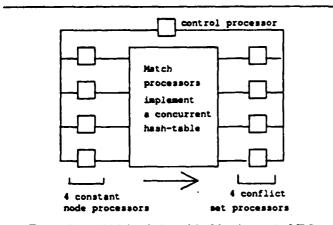

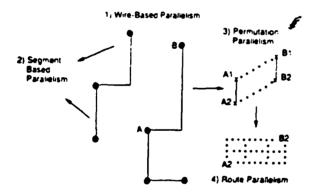

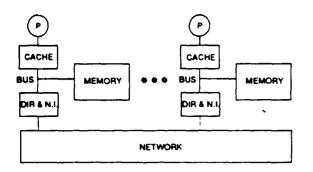

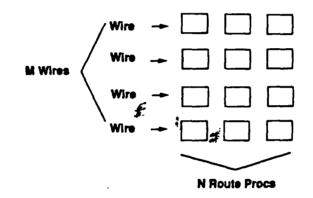

Figure 4-1: A high level view of the Mapping on the MPCs.

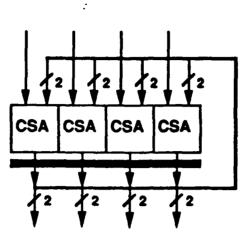

To overcome the limitations of above mapping, we propose an alternative mapping, a high-level picture of which is shown in Figure 4-1. At the heart of this mapping is a concurrent distributed hash-table [6] data structure that enables fine-grain exploitation of concurrency. The details are described later in this section. As shown in the figure 4-1, the parallel mapping consists of 1 control. processor, 4 constant-node processors, 4 conflict set processors, and the rest are match processors. The constant-test nodes of the Rete net are divided into 4 parts and assigned to the constant-node processors. The match processors perform the function of the rest of the Rete net. The conflict-set processors perform conflict-resolution on the instantiations sent to them. Subsequently, they send the best instantiation to the control processor. The control processor is responsible for performing conflict-resolution among the best instantiations, evaluating the RHS and performing other functions of the interpreter.

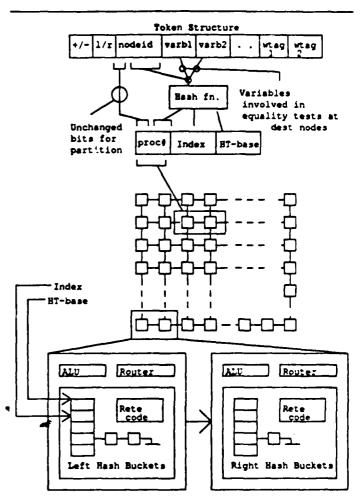

As mentioned in Section 2.2, most of the time in match is spent processing two-input node activations. Hashing the contents of the associated memory nodes, instead of storing them in linear lists, reduces the number of comparisons performed during a nodeactivation and thus improves the performance of Rete. One hash table is used for all left memory nodes in the network and the other for all right memory nodes. The hash function that is applied to the tokens takes into account (1) the variable bindings tested for equality at the two-input node, and (2) the unique node-identifier of the destination two-input node. This permits quick detection of the tokens that are likely to pass the equal variable tests.

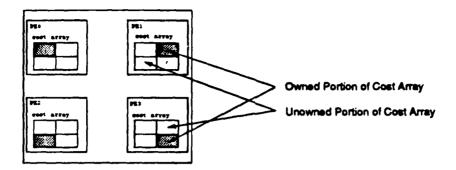

In our mapping, to allow the parallel processing of (1) tokens destined for the same two-input node and (2) tokens destined for different two-input nodes, the hash tables buckets storing the tokens are distributed among the PEs of the processor array. In particular, a small number of corresponding buckets from the left and right hash tables are assigned to each processor pair in the array -- the leftbuckets to the left processor and the right buckets to the right processor. (Note that when processing a node activation, the left and right buckets at only one index need to be accessed.) This mapping is pictorially depicted in Figure 4-2. There is one restriction on the communication with the processor-pair — it can only be done through the *left-processor*. Allowing communication with both left and right processors can result in creation of duplicate tokens leading to incorrect behavior, and it does not gain as much in concurrency.

A processor-pair together performs the activity of a single node activation. Consider the case when a token corresponding to the left-activation of a two-input node arrives at a processor-pair. The left processor immediately transmits the token to the right processor. The left processor then copies the token into a data-structure and adds it to the appropriate hash-table bucket. Meanwhile, the right processor compares the token with contents of the appropriate right bucket to generate tokens required for successor node activations. The right-processor then calculates the hash value for the newly created tokens, and sends each token to the processor pair which owns the buckets that it hashes to. The activities performed by the individual processors of the processor pairs are performed in parallel.

The performance of this scheme depends on the discriminability of hashing. Two observations can be made in this respect:

1. Hashing is based on equality tests in CEs and 90% of the tests at two input nodes are equality tests [9].

2. The locks on the hash tables in the PSM implementations have not been seen to be bottlenecks [10, 21].

Thus hashing is not expected to be a problem in general. However, in certain production systems, a large number of two-input nodes do not have any tests. For such nodes, various schemes as proposed in [1], can be used to introduce discriminability into the tokens generated. Furthermore, when the compiler does come across nodes which cannot be hashed, it can assign a larger number of processors for that pair of buckets, (since all the tokens would end up in a single pair of buckets) thus breaking up the processing.

The code for the Rete net is to be encoded in the OPS83 [8] software technology. With this encoding, large OPS5 programs (with - 1000 productions) require about 1-2 Mbytes of memory — a problem, since each MPC processor has only 10-20 kbytes of local memory. We therefore use two strategies to save space:

- 1. Partition the nodes of Rete such that each processor evaluates nodes from only one partition. This partitioning is easily achieved if the hash function preserves some bits from the node-id. To avoid contention, nodes belong to a single production are put into different partitions.

- 2. One cause of the large memory requirement is the in-line expansion of procedures. We can instead encode the twoinput nodes into structures of 14 bytes, indexed by the node-id. A small performance penalty of loading the required information into registers is then paid in the beginning of the computation.

The system's overall operation is as follows:

- 1. The control processor evaluates a WME change and transmits it to the constant node processors.

- 2. The constant node processors match the WME with the constants in the CEs. The result of this match is tokens that have bindings for the variables in matched CEs. These tokens represent individual node activations and are sent to appropriate processor pairs.

- 3. The following steps are then repeated by the processorpairs until completion of match:

- Split the node-activation into micro-tasks and perform them in parallel.

- Count the number of successor tokens generated due to this token; if no successors are generated, then send an acknowledgement (ack) message to this processor pair's activator.

- Accept ack messages from the successors. If accounted for all successors of a token, send an ack message to the activator.

Detecting termination in a distributed system is a complex problem in itself [15]. The ack messages provide an easy and reasonably efficient method of informing the conflict-set processors about the completion of the match. Thus after the processing of the last activation in the current match cycle, a single stream of ack messages flows back, finally to the control processor, which then informs the conflict set processors that the match is completed.

### 5. Performance Analysis

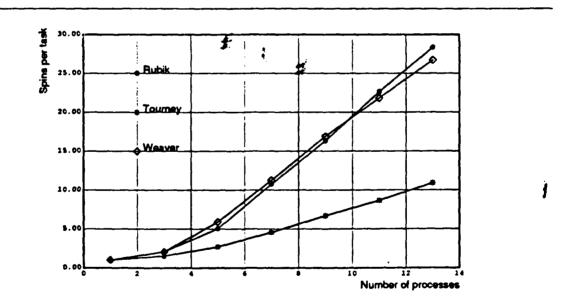

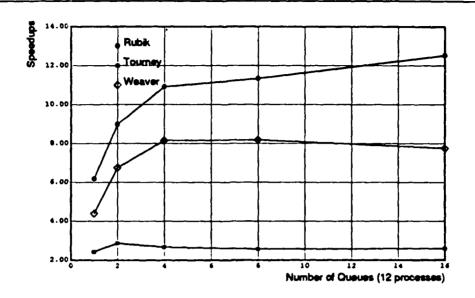

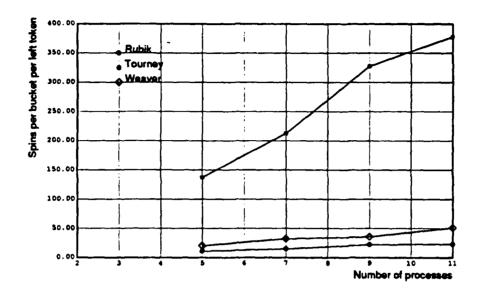

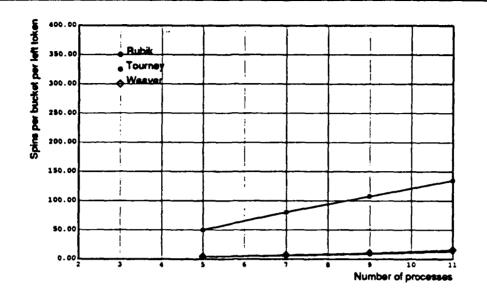

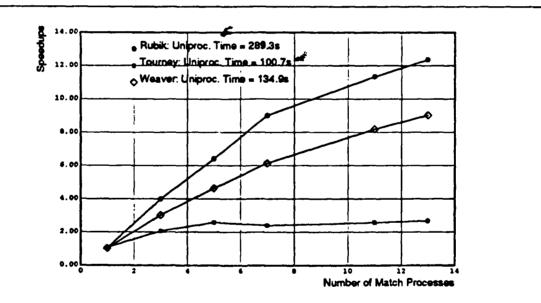

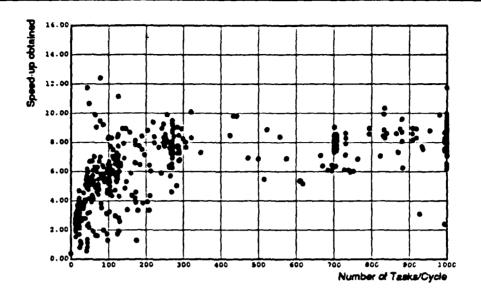

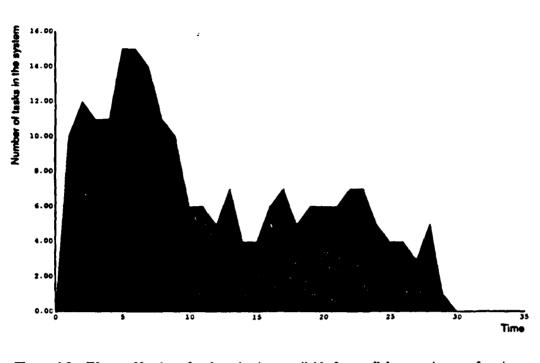

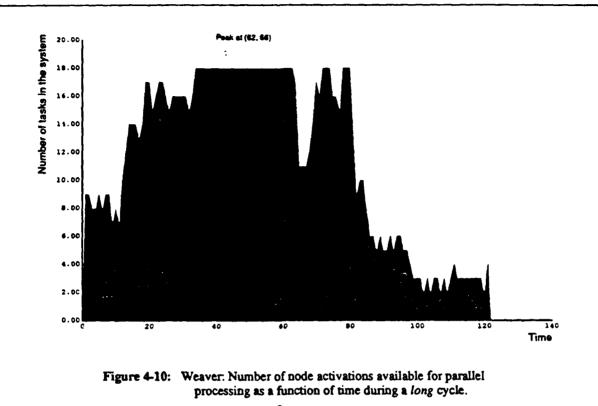

We now evaluate the MPC implementation using the measurements on the Rete net from [9].<sup>2</sup> The point of the analysis is to establish that the MPCs will provide good speedups compared to other previously proposed parallel implementations, rather than to estimate the exact performance that will be obtained on a real machine.

One of the important numbers for this analysis is the time spent in the processing of one node activation. Using that, we can estimate the time for a micro-task. A node activation is identical to a *task* on the PSM, which takes 200  $\mu$ s on a 1 MIPS processor [10]. Measurements of the number of instructions executed indicate that about 50% of that time is spent in updating the hash bucket and 50% in performing tests with tokens in opposite memory. We therefore assume that on our 4 MIPS processor, performing a micro-task will take about 25  $\mu$ s, which is 200  $\mu$ s \* 1/4 (due to processor speed) \* 0.5 (due to partitioning of the node-activation into micro-tasks).

Since the processor-pairs communicate via tokens, we also need to calculate the overhead of a token message. The length of a tokenmessage is dependent on the number of variable bindings and the number of WME timetags carried by the token. There are on average four variable bindings per production [9]. The number of WME timetags is dependent on the number of CEs in a production. Assuming the number of CEs to be (M = 5) for the moment, we use the token-structure in Figure 4-2 to estimate 42 bytes of information per token. The overhead of sending the token message will therefore be equal to  $T_a = (5 + Q * N)$  clock cycles, with Q = 42/4 words and N = 1 processor (see section 3). Substituting, we get  $T_s = 1.6 \ \mu s$ . The communication delay  $T_{wh}$  is given by  $T_C(D + L/W)$ . This communication will be between a random pairs of processors. Therefore, D = 22. We have assumed  $T_C$  to be 50ns and W to be 16. Our L is 42 \* 8 = 336 bits. Substituting, we get  $T_{wb} = 2.2 \ \mu s$ . The total delay will be therefore  $1.6 + 2.2 = 3.8 \ \mu s$  per token message between processor-pairs.

-

We can now estimate the cost of one match cycle. The steps below correspond to the algorithm in the previous section.

Step 1: The WME changes are transmitted to the 4 constant-node processors. The cost of addition of a WME is as follows: The average WME consists of 24 attribute value pairs, which can be encoded in 24 bytes for attributes + 24 words for the values = 30 words. Broadcasting this WME takes  $T_a = (5 + 30 \text{ words} \cdot 4 \text{ processors})$  clock cycles i.e., 12.5 µs.

For the communication delay,  $T_{wh}$ , D = 1 since the constant node processors are one hop away from the control processor. The value of L is 30 words \* 32 bits/word = 960 bits; W = 16 and the value of  $T_c$  is fixed at 50. Substituting, we get  $T_{wh} = 3.1 \ \mu s$ . Thus the total time spent in communication during WME-addition is 15.6  $\mu s$ .

For deleting a WME, only the timetag of the WME to be deleted is passed on to the constant-node processors. Calculating  $T_s$  and  $T_{wh}$  in a similar fashion, we get the total time spent in delete to be 1.1  $\mu$ s. There is an average of 2.5 WME changes per cycle. Assuming equal proportions of adds and deletes, the cost of the first step is  $1.25(1.1 + 15.6) = 21 \ \mu$ s.

<sup>&</sup>lt;sup>2</sup>We do not analyze the conflict-resolution and action parts of the match since these take less than 10% of the time in a scrial implementation. Since we have divided up the conflict set and pipelined the action part with the match, these should take even less time than that. In case they do become bottlenocks, various achemes discussed in [9] can be used to reduce their overheads.

Step 2: The constant tests are now evaluated. Assuming that the constant tests are implemented via hashing, there are 20 constantnode activations per WME change [9]. On average, each partition will have 5 activations per WME change. Thus about  $(5 \circ 2 / 4 \text{ MIPS}) = 2.5 \,\mu\text{s}$  are spent in matching the constant nodes. A token structure is then generated and bindings are created for the variable(s) of the CEs which passed the tests. Measurements [9] show that there will be about 5-7 such tokens generated per WME change, which we assume to take 20  $\mu$ s. This whole operation of processing a WME-change by a constant-node processor is therefore estimated to take about 22.5  $\mu$ s. For the 2.5 WME-changes, (22.5  $\circ$  2.5)  $\approx$  56  $\mu$ s will be spent in processing the constant nodes and generating the initial tokens in a cycle. The generation of these tokens is pipelined with sending the tokens to the match processors.

Step 3: The processor-pairs perform the rest of the match. The node-activation typically go to different processor-pairs, and are processed in parallel. Therefore, the total time to finish the match is determined by the longest chain of dependent node-activations, since the micro-tasks in the chain have to be processed sequentially. On an average, the chain will be generated after 50% of the initial tokens in a cycle have been generated. A constant-node processor takes 56  $\mu$ s to generate all the initial tokens; therefore, we assume that the initial token generating the long chain will be created after 28  $\mu$ s. Including the constant-node processors, let the longest chain be of length M = 5.

When a token arrives at the left processor, it is immediately transmitted to the right processor. For this transmission,  $T_{\rm s}$  is still 1.6 µs. But,  $T_{\rm wh} = 50(1 \text{ channel} + 42 * 8/16) = 1.1 \mu \text{s}$ . Thus, after a token arrives at the left processor, it will take  $1.6 + 1.1 = 2.7 \mu \text{s}$  to reach the right processor. The right processor will take 25 µs to finish the micro-task. It will then take 3.8 µs for the successor token to reach its destination. Thus, the time to complete a micro-task is  $25 + 2.7 + 3.8 = 31.5 \mu \text{s}$ . A chain of length 5 will therefore take  $31.5 * 4 + 28 \mu \text{s}$  (due to the constant nodes) =  $154 \mu \text{s}$ . (Similar analysis could be done if the successors are generated by the left processor).

The ack messages are propagated back through the node activation chain, after the last activation is processed. It is 1 word of information and so we estimate  $T_{wh} = 1.2 \ \mu s$  and  $T_s = 0.6 \ \mu s$ . Assuming that the ack is processed in 1  $\mu s$ , the time spent in the chain of ack messages is  $(M = 5) * (1 + 1.2 + 0.6) = 14.0 \ \mu s$ . Adding all the numbers together, we get the time for MPC to match to be approximately  $154 + 14 + 21 = 189 \ \mu s$ .

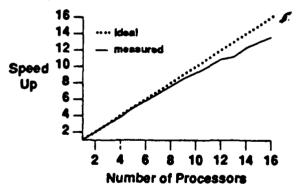

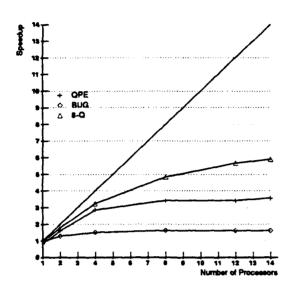

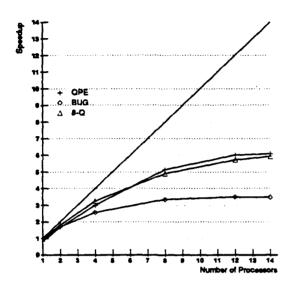

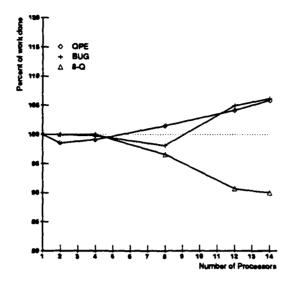

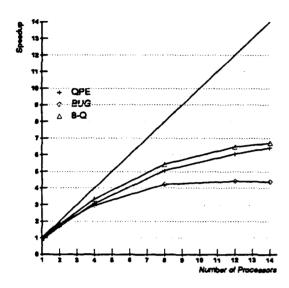

A production system generates 200 micro-tasks on an average/cycle, and therefore a uniprocessor will take 200 \* 25 = 5000  $\mu$ s per cycle. Using this we get about 26 fold speedup for the above system with the longest chain of M = 5. This is ~60% of the maximum parallelism exploitable on an ideal multi-processor at this granularity. Our calculations show that the speedups is ~14 fold if M = 10 and ~9 fold if M = 15. Again, this is ~60% of the maximum available parallelism. This is comparable with the estimate of 60% exploitable parallelism in shared memory multiprocessors at the node-activation level [9]. This coarser grain node-activation level parallelism can be exploited on the MPCs by allocating both the left and right buckets to one processor. Our calculations show that the micro-task based scheme is capable of exploiting 1.5 time more speedup than a scheme to exploit the node-activation level parallelism.

#### 6. Discussion

Comparing the MPC, implementation to a shared memory multiprocessor implementation, we see that the principle advantage of the MPC implementation is the absence of a centralized taak-scheduler, which can be a potential bottleneck. As shown in [9], in sharedmemory implementations, a slow scheduler forces saturation speedup with relatively small number of processors, irrespective of the inherent parallelism in the system. However, the MPC implementation suffers from a static partitioning of the hash tables. It is possible that distinct tokens, which could potentially be processed in parallel, are processed sequentially because they hash to the same processor pair. Such a possibility does not arise in the sharedmemory implementation, since the size of the hash table is independent of the number of processors.

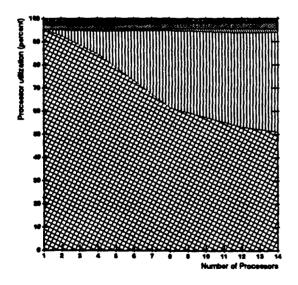

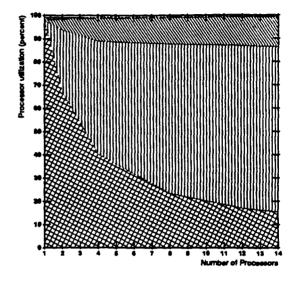

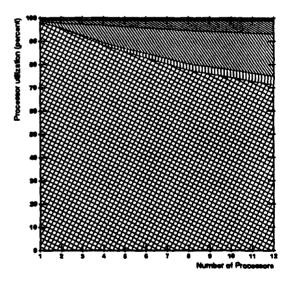

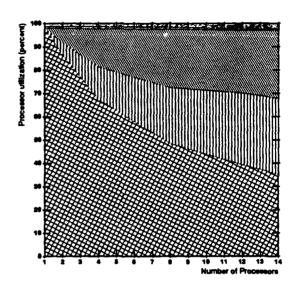

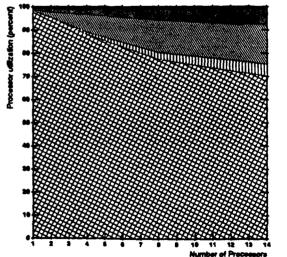

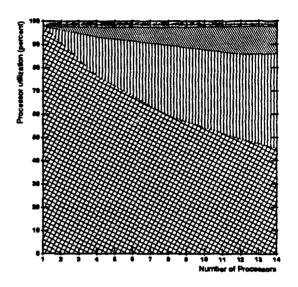

Another tradeoff to be considered is between processor utilization and the number of processors. With a higher number of processors, the processor utilization will be low, but the message contention in the network will be reduced. As the number of processors is reduced, processor utilization will be improved; but again, this will also increase the hash table contention. Thus there are some interesting tradeoffs involved in moving towards the MPCs.

A mapping similar to one proposed in this paper has been used to implement production systems on the simulator for *Nectar*, a network computer architecture with low message passing latencies [13]. These simulations show that good speedups can be obtained by implementing production systems on MPCs with low latencies [22]. The simulations also indicate that the constant node processors can quickly become bottlenecks if the initial tokens are not generated and sent fast enough. In our current implementation, we have hashed the constant nodes to take care of such a possibility. If the constant node processors continue to be bottlenecks inspite of this, then schemes proposed in [22] can be used to remove them.

Finally, we would like to reiterate the importance of mapping production systems on MPCs. Current production systems offer limited (10-20 fold) parallelism [9]. We have shown that the MPCs are capable of exploiting this limited parallelism. However, production systems with more inherent parallelism are getting designed [14]. In such production systems, the parallelism is expected to be much higher [21]. For such production systems, it becomes necessary to analyze easily scalable architectures such as the MPCs for their implementations.

#### 7. Summary

Recent advances in interconnection network technology and processing node design have reduced the latency and message handling overheads in MPCs to a few microseconds. In this paper we addressed the issue of efficiently implementing production systems on these new-generation MPCs. We conclude that it is indeed quite possible to implement production systems efficiently on MPCs. At a high level, our mapping corresponds to an object oriented system, with Rete network nodes passing tokens to each other using messages. At a lower level, however, instead of mapping each Rete node onto a single processor, the state and the code associated with a node are distributed among the multiple processors. The main data structure that we exploit in our mapping is a concurrent distributed hash-table that not only allows activations of distinct Rete nodes to be processed in parallel, but also allows multiple activations of the same node to be processed in parallel. A single node activation is further split into two micro-tasks that are processed in parallel, resulting in very high expected performance.

### Acknowledgements

We would like to thank H. T. Kung for questioning our assumptions about shared memory architectures. We would like to thank Charles Forgy, Brian Milnes, Allen Newell and Peter Steenkiste for many useful comments on earlier drafts of this paper. We would also like to thank Kathy Swedlow for technical editing.

2

### References

- Acharya, A., Kalp, D., Tambe, M. Cross Products and Long Chains.

Technical Report, Carnegie Mellon University Computer Science Department, In preparation.

- [2] Brownston, L., Farrell, R., Kant, E., Martin, N. Programming Expert Systems in OPSS: An Introduction to Rule-based Programming. Addison-Wesley, 1985.

- [3] Dally, W. J.

Directions in Concurrent Computing. In Proceedings of ICCD-86. October, 1986.

- [4] Dally, W. J.

Wire Efficient VLSI Multiprocessor Communication Networks.

In Stanford Conference on Advanced Research in VLSI. 1987.

- [5] Dally, W. J., Chao, L., Chien, A., Hassoun, S., Horwat, W., Kaplan, J., Song, P., Totty, B., Wills, S.

Architecture of a Message-Driven Processor. In International Symposium on Computer Architecture. 1987.

- [6] Dally, W. J.

A VLSI Architecure for Concurrent Data Structures.

PhD thesis, California Institute of Technology, 1987.

- Forgy, C. L.

Rete: A fast algorithm for many pattern/many object pattern match problem.

Artificial Intelligence 19:17-37, 1982.

- [8] Forgy, C. L. The OPS83 Report. Technical Report 84-133, Carnegie Mellon University Computer Science Department, May, 1984.

- [9] Gupta, A.

Parallelism in Production Systems.

PhD thesis, Camegie Mellon University, March, 1986.

- Gupta, A., Forgy, C. L., Kalp, D., Newell, A., Tambe, M. S. Parallel OPS5 on the Encore Multimax.

In Proceedings of the International Conference on Parallel Processing. August, 1988.

- Hillyer, B. K. and Shaw, D. E. Execution of OPS5 production systems on a Massively Parallel Machine.

Journal of Parallel and Distributed Processing 3:236-268, 1986.

- [12] Hoare, C. A. R. Communicating sequential processes. Communications of ACM 21(8):666-677, 1978.

- [13] Kung, H. T., Steenkiste, P., Bitz, F. The Nectar computer architecture. Personal Communication.

- [14] Laird, J. E., Newell, A., & Rosenbloom, P. S. Soar: An architecture for general intelligence. Artificial Intelligence 33:1-64, 1987.

- [15] Mattern, F. Algorithms for distributed termination detection. Journal of Distributed Computing 2:161-175, 1987.

- [16] Miranker, D. P. TREAT: A New and Efficient Algorithm for AI Production Systems. PhD thesis, Columbia University, 1987.

- Oflazer, K.

Partitioning in Parallel Processing of Production Systems.

PhD thesis, Carnegie-Mellon University, March, 1987.

- [18] Schreiner, F., Zimmerman, G. Pesa-1 — A Parallel Architecture for Production Systems. In International Conference on Parallel Processing. 1987.

- [19] Seitz, C., Athas, W., Flaig, C., Martin, A., Seizovic, J., Steele, C., Su, W.

The Architecture and Programming of the AMETEK 2010 Multicomputer.

In Hypercube concurrent computer and applications. 1988.

- [20] Sietz, C. L.

The Cosmic Cube.

Communications of ACM C-33(12), 1984.

- [21] Tambe, M. S., Kalp, D., Gupta, A., Forgy, C. L., Milnes, B., Newell, A. Soar-PSM/E: Investigating match parallelism in a learning production system. In Proceedings of the PPEALS-88. 1988.

- [22] Tambe, M., Bitz, F., Steenkiste, P. Production Systems on the Nectar: Simulation Results and Analysis.

- Alechnical Report, Carnegie Mellon University Computer Science Department, In preparation.

### **Temperature Measurement of Simulated Anriealing Placements**

Jonathan Rose Computer Systems Laboratory, Stanford University, Stanford CA

Wolfgang Klebsch and Juergen Wolf Siemens AG, Munich, Federal Republic of Germany

### Abstract

One way to reduce the computational requirements of Simulated Annealing placement algorithms is to use a faster heuristic to replace the early phase of Simulated Annealing. Such systems need to know a starting temperature for the annealing phase that makes the best use of the existing structure, yet does an appropriate amount of improvement. This paper presents a method for measuring the temperature of an existing placement based on analysis of the probability distribution of the change in cost function. Using this view a new definition of equilibrium is given and the equilibrium temperature of a placement is defined. Temperatures of placements produced both by a Simulated Annealing and a Min-Cut placement algorithm are measured.

### **1** Introduction

The success of the Simulated Annealing algorithm for automatic placement [Sech85] has been hindered by its excessive computational requirements. Recent work on standard cell placement algorithms [Rose86, Grov87, Rose88] has suggested alleviating this by using a two-stage approach: begin with a good heuristic such as the Min-Cut algorithm [Dun185] and follow it with a Simulated Annealing-based approach for more fine optimization. This allows a tradeoff between execution time and quality. A critical issue in this approach is to decide the starting temperature of the Simulated Annealing phase. If it is too high, then some of the structure created by the first phase will be destroyed and unnecessary extra work will have to be done in the Simulated Annealing phase. If the temperature is too low then solution quality is lost, similar to the case of a quenching cooling schedule [Whit84].

This paper presents a technique for measuring the temperature of a placement for use in such two-stage systems. To do so, we present a new view of Simulated Annealing state different from those articulated in [Rome84, Whit84, Aart85]. The principal difference is that we look at probability distributions of the change in cost function of a Simulated Annealing state, rather than the absolute cost function. Using this view we give a definition of equilibrium from which follows the notion of the equilibrium temperature of a placement.

From this we develop a measure that quantifies the neamess of a Simulated Annealing placement to equilibrium and give experimental evidence of its ability to detect equilibrium. This leads to a method for measuring the equilibrium temperature of a placement, and we show that it works both for placements produced by a Simulated Annealing and a Min-Cut placement algorithm. The determination of starting temperature for Simulated Annealing in two-stage systems has not been seriously addressed before. Both [Rose86,Rose88] and [Grov87] introduce the question but avoid answering it by choosing a starting temperature based simply on prior experience.

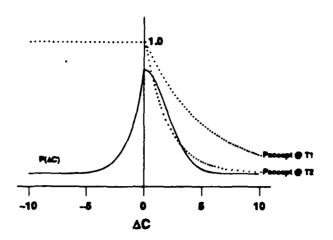

### 2 Definition of Equilibrium and Temperature

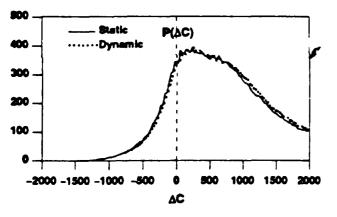

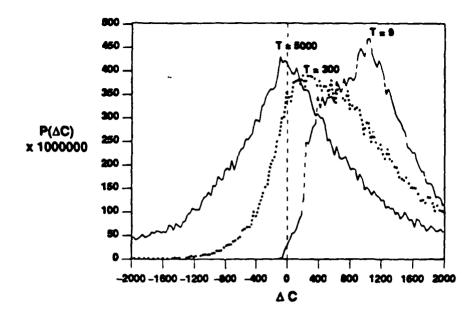

In previous discussions of cooling schedules and convergence [Rome84, Whit84, Aart85], the Simulated Annealing state has been represented either as the probability distribution of the absolute cost P(C), or the set of transition probabilities from every state *i* to every other state *j*,  $T_{ij}$ . We suggest a different view that gives more information about equilibrium dynamics: the probability distribution of the change in cost function from the current state.  $P(\Delta C)$  is the probability that a given state under a Simulated Annealing process with a particular generation function [Rome84] will generate a move with a change in cost function of  $\Delta C \cdot P(\Delta C)$  varies with temperature (T) and as moves are made.

We can use this view to give a different perspective on the equilibrium of a Simulated Annealing process. Since at equilibrium the absolute cost function no longer changes, this implies that the expected value of the *change* in cost function is zero:

$$\boldsymbol{E}(\Delta \boldsymbol{C}) = \boldsymbol{0} \tag{1}$$

An expression for  $E(\Delta C)$  can be formed assuming that  $P(\Delta C)$  is known:

$$E(\Delta C) = \int \Delta C P(\Delta C) P_{Accept}(\Delta C) d\Delta C \qquad (2)$$

$P_{Accept}(\Delta C)$  is the probability that the acceptance function will accept a move with cost  $\Delta C$  [Rome84]. It commonly has the value 1 for  $\Delta C \leq 0$  and  $e^{\frac{-\Delta C}{T}}$  for  $\Delta C > 0$  [Sech85]. We note here that  $P(\Delta C)$  in equation (2) must be the distribution measured on a running Simulated Annealing process at the equilibrium temperature. This distribution is difficult to measure, and will be discussed further in Section 3.1.

Using this  $P_{Accept}(\Delta C)$  we can split equation (2) into two parts and, at equilibrium from equation (1) we can equate it to zero:

$$\int \Delta C P(\Delta C) d\Delta C + \int \Delta C P(\Delta C) e^{\frac{-\Delta C}{T}} d\Delta C = 0 \quad (3)$$

Thus equilibrium can now be defined as the state where, at a given  $T = T_{eq}$ , the distribution  $P(\Delta C)$  satisfies equation (3).

This work was supported by an NSERC Post-Doctoral Fellowship and DARPA Contract #N00014-87-K-0828.

Conversely, the equilibrium temperature of a placement with a distribution  $P(\Delta C)$  is the temperature,  $T_{eq}$ , for which equation (3) is satisfied.

### 2.1 An Equilibrium-Nearness Measure

Using equation (3) we can invent a measure of the nearness of a given Simulated Annealing state to equilibrium. Define  $E_{\perp}$ to be the absolute value of the first term in the equation, that is

$$E_{-} = \prod_{i=1}^{n} \Delta C P(\Delta C) d\Delta C I$$

Similarly let  $E_+$  be the second term of equation (3):

$$E_{+} = \int_{0}^{\infty} \Delta C P(\Delta C) e^{\frac{-\Delta C}{T_{o}}} d\Delta C$$

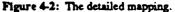

Where  $T_m$  is the temperature of the Simulated Annealing process. We can now define the Cost Force Ratio, (CFR) as:

$$CFR = \frac{E_-}{E_+ + E_-} \times 100 \tag{4}$$

The closer CFR is to 50% (the expected value of the good moves being equal to the expected values of the bad moves,  $E_{-} = E_{+}$ ) the closer the system is to equilibrium.

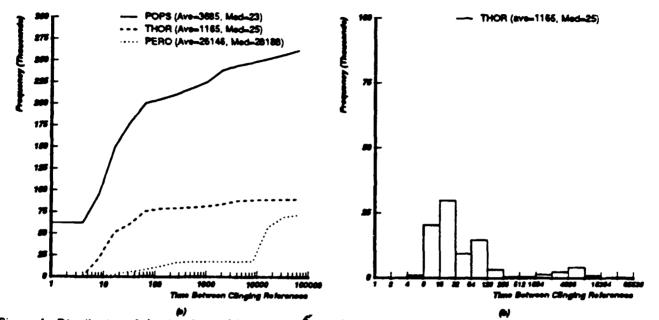

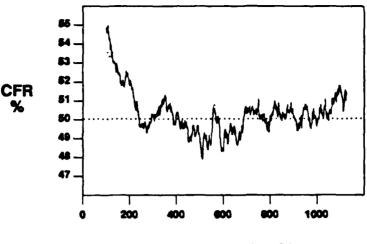

Figure 1 - CFR vs Move as Process Achieves Equilibrium

All experiments in this paper use a placement of the 833 standard cell Primary1 circuit from the Preas-Roberts standard cell benchmark suite [Prea87]. The placement was produced by the SALTOR Simulated Annealing placement program [Rose86, Rose88], which is based on the ideas of the Timberwolf standard cell placement program [Sech85]. Figure 1 is a plot of CFR versus generated move number for a Simulated Annealing process running on circuit Primaryl, as it goes from nonequilibrium to equilibrium at temperature 400 changing to 300. CFR is determined by keeping a window of  $\Delta C$  values multiplied by the  $P_{Accept}$  function and using this to calculate  $E_+$ and  $E_{-}$  In this figure the CFR comes down from an initial value of 55% and hovers around 50%. This shows that the CFR indicates when equilibrium has been achieved. It varies about the 50% point due to the stochastic nature of the algorithm and the approximation of measuring the CFR in a finite window.

#### **3 Measuring Temperature**

:

As defined in Section 2, the temperature of a placement is the temperature at which the Simulated Annealing process running on the placement is in equilibrium. In this section we present a method for measuring the temperature of an arbitrary placement.

The method is called the CFR Binary Search and has the following outline:

- 1. Measure  $P(\Delta C)$  for the given circuit under the Simulated Annealing process. This is discussed in detail in Section 3.1.

- 2. Set the starting search temperature,  $T_m$ , arbitrarily.

- 3. Based on the current  $T_m$ , calculate  $P_{Accept}(\Delta C) = e^{\frac{-\Delta C}{T_a}}$ for  $\Delta C > 0$  and = 1 for  $\Delta C \le 0$ .

- 4. Calculate the Cost Force Ratio, CFR, using  $P_{Accept}(\Delta C)$  and equation (4).

- If CFR < 50, reduce T<sub>m</sub> according to a binary search and go to step 3;

If CFR > 50, increase T<sub>m</sub> according to a binary search and go to step 3.

- 6. When CFR = 50,  $T_{\rm eff}$  is the equilibrium temperature,  $T_{\rm eff}$ . Finish.

- <sup>4</sup> Each iteration of the CFR Binary Search requires only the recalibilation of the positive portion of the acceptance function probability,  $P_{Accept}(\Delta C)$ , and subsequently  $E_{+}$  and CFR since  $E_{-}$  does not change with  $T_{m}$ . Note also that  $P(\Delta C)$  need only be generated once. This is important since it takes many moves  $(10^{4} \text{ to } 10^{5})$  to get an accurate picture of the probability distribution.

#### 3.1 Measurement of the Probability Distribution

A key and difficult step in the CFR Binary bearch temperature measurement procedure is the measurement of the distribution  $P(\Delta C)$ . There are two possible methods:

- 1. Static Measurement.  $P(\Delta C)$  is measured by generating (but not accepting) moves in the Simulated Annealing process on the placement, and recording the frequency with which each cost occurs. These virtual moves do not change the placemen.

- 2. Dynamic Measurement.  $P(\Delta C)$  is measured by generating and accepting moves on the placement. Here the placement does change as the measurement is made.

For the general case of any Simulated Annealing application a static measurement will not give the correct distribution. This is because a static measurement of  $P(\Delta C)$  could be taken when the system was at a local (but not global) optimum. In this case there would be no good (negative) moves generated and since

$E_{-}$  would thus be 0 the temperature would appear to be 0, which is incorrect in the case of a local optimum. Similar problems can occur when the state is at or near discontinuities in the energy landscape.

The dynamic measurement approach must run the Simulated Annealing process at its equilibrium temperature. Using a different temperature would cause the placement's temperature to change. Unfortunately the equilibrium temperature is the quantity we are seeking, and is not known. This is a dilemma not unlike the Heisenberg uncertainty principle: the act of measuring the temperature this way can cause the temperature to change.

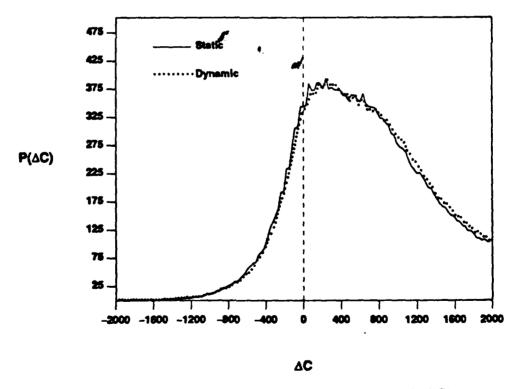

An alternative is to measure  $P(\Delta C)$  using the static method, and to determine how accurate this is as an approximation. The accuracy is entirely problem dependent - is depends on the energy landscape of the underlying Simulated Annealing formulation. We have experimented to determine the accuracy for the standard cell placement problem and have found that the static measurement of  $P(\Delta C)$  is almost exactly the same as the dynamic measurement. Figure 2 shows a plot of a static distribution and a dynamic distribution measured on circuit Primary1 at temperature 300. Measurements and numerical comparisons on this and several other circuits at various temperatures have shown very small differences between the static and dynamic measurements. Thus we will use the static measurement of  $P(\Delta C)$  in the temperature measurement algorithm.

Figure 2 - Comparison of Static and Dynamic Measurement

#### 3.2 Measurement of Annealing Placements

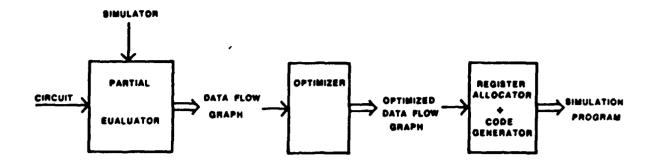

The CFR Binary Search was used to measure the temperature of a set of Primaryl placements produced by the SALTOR Simulated Annealing placement program [Rose86,Rose88]. Each placement was measured statically using N = 100,000 virtual moves to experimentally determine  $P(\Delta C)$ . Table 1 gives the temperature at which each placement's Simulated Annealing process was tempinated (while in equilibrium), and the measured temperature using the CFR Binary Search.

The measured temperature is quite accurate at the higher temperature, usually less than 7% error. The lower temperature measurements are proportionately less accurate. The error is due to two effects: First, there is a slight difference, as discussed above, between the static and the (more correct) dynamic measurement of  $P(\Delta C)$ . Second, at lower temperatures, there are fewer negative moves, and so the accuracy of  $E_{\perp}$  decreases, decreasing the accuracy of CFR and hence the temperature measurement.

ź

| SA Produced<br>Temperature | CFR Binary Search<br>Measured Temp | Difference |

|----------------------------|------------------------------------|------------|

| 500                        | 496                                | 4          |

| 405                        | 420                                | +15        |

| 294                        | 285                                | -11        |

| 213                        | 215                                | +2         |

| 153                        | 164                                | +11        |

| 99                         | 97                                 | -2         |

| 57                         | 60                                 | +3         |

| 28                         | 28                                 | 0          |

| 9                          | 15                                 | +6         |

| 2                          | 4                                  | +2         |

**Table 1** - Temperature Measurement of Annealing Placements

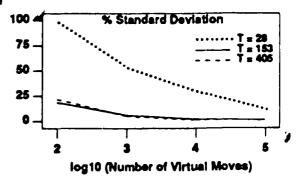

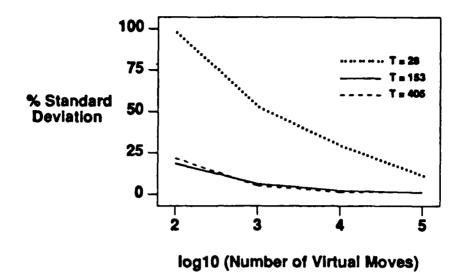

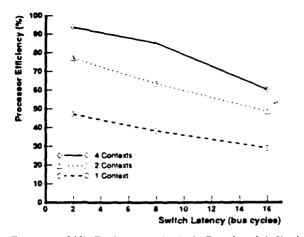

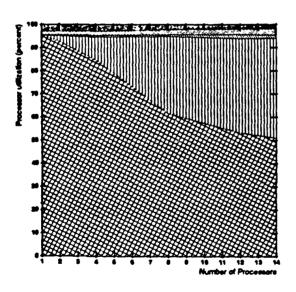

This last point can be seen experimentally: figure 3 is a plot of the percentage standard deviation of the measured temperature as a function of the number of virtual moves, N, for temperatures 28, 153 and 405. The standard deviation was calculated from five runs at each number of virtual moves.

Figure 3 - Variation of Temperature vs. Number of Moves

The variation is a decreasing function of N, as would be expected. The figure illustrates the increase in percentage variation at lower temperature.

#### 4 Measurement of Min-Cut Placements

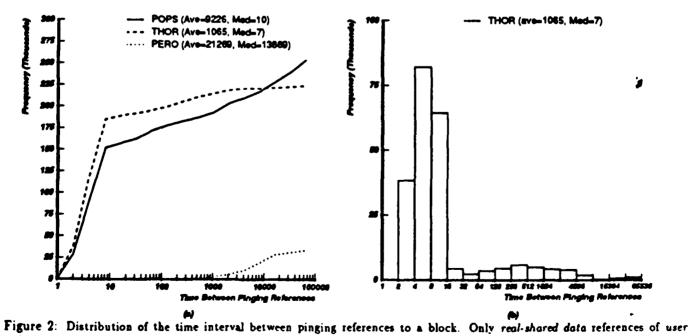

Our goal is to determine the starting temperature when switching from a non-annealing placement algorithm to an annealing-based one. In this section we test the ideas presented above on the Min-Cut placement algorithm [Dun]85].

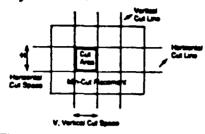

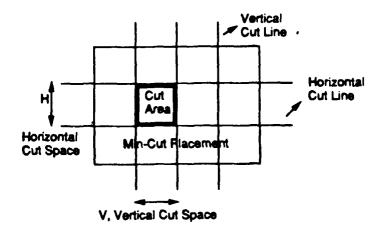

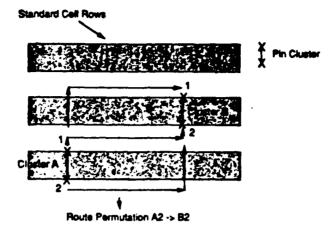

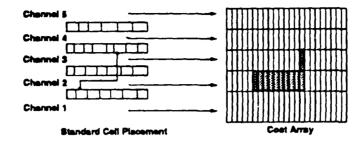

Several terms first need to be defined for Min-Cut placements, as shown in Figure 4. A Min-Cut placement algorithm is characterized by, among other things, the order and spacing of the cut lines applied. In Figure 4, the rectagle represents the entire placement, over which is laid a set of vertical and horizontal cut lines. If the spacing of the vertical cut lines is V and of the horizontal cut lines is H, then the cut area, A, is given by  $A = V \times H$ .

Figure 4 - Definition of Cut-Area

One difficulty with measuring the temperature of \*:mannealing produced placements is that the definition of temperature presented in Section 2 depends on the associated Simulated Annealing process being in equilibrium. It is clear, however, that a placement produced by a non-annealing algorithm is not in equilibrium. Thus we must make an approximation and assume that a min-cut placement can be thought of as being in equilibrium at some temperature. The effect of this approximation is measured in the next section where we compare the CFR Binary Search method with a more direct method.

#### 4.1 Measurements

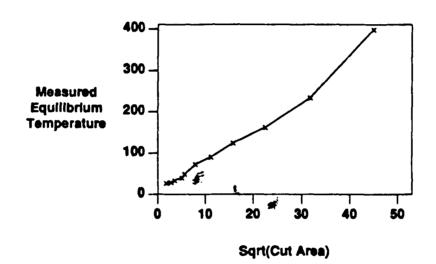

Using the CFR Binary Search method we measured the temperature of several Min-Cut placements with different cut areas. These placements were produced by the ALTOR standard-cell placement program [Rose85]. Table 2 gives the measured temperature for each placement and its cut area.

| Cut Area<br>jum <sup>2</sup> x10 <sup>4</sup> | Temperatur<br>Binary Search |     | Difference |

|-----------------------------------------------|-----------------------------|-----|------------|

| 2021                                          | 398                         | 374 | +24        |

| 1011                                          | 234                         | 200 | +34        |

| 505.3                                         | 162                         | 132 | +30        |

| 252.6                                         | 124                         | 96  | +28        |

| 126.3                                         | 91                          | 67  | +24        |

| 63.22                                         | 73                          | 50  | +23        |

| 31.58                                         | 49                          | 40  | +9         |

| 25.24                                         | 40                          | 32  | +8         |

| 12.60                                         | 34                          | 30  | +4         |

| 7.697                                         | 29                          | 27  | +2         |

| 3.139                                         | 28                          | 26  | +2         |

**Table 2** - Temperature Measurement of Min-Cut Placements

To check the CFR Binary Search measurements, the placements were measured using a different approach, called the Delta Method. It finds the temperature of a placement by running a dynamic annealing process on the placement over a range of temperatures. The percentage difference in absolute cost function after (100 moves per cell are made) is measured. When a temperature is found for which this difference is less than 2%, that is taken as the temperature of the placement. This is a direct way of experimentally finding the temperature at which  $\xi \Rightarrow$  change in cost function is near 0. Table 2 gives the temperatures determined by the Delta Method, and the difference between the CFR Binary Search and the Delta Method. The CFR Binary Search measurement for Min-Cut placements is not as accurate as those for Annealing-produced placements, yet it does track the temperature reasonably well.

The CFR Binary Search method consistently overestimates the equilibrium temperature due to the fact that a min-cut placement is not in equilibrium, as discussed above.

#### **5** Conclusions

We have presented a method for determining the temperature, in the Simulated Annealing sense, of an arbitrary placement. It uses a new view of Simulated Annealing state that is based on the probability distribution of the change in cost function. The temperature of several Simulated Annealing placements have been measured with good accuracy. The temperature of a set of Min-Cut placements has also been measured. This method is useful for determining the starting temperature when switching from a non-annealing based placement strategy to an annealing-based one.

# 6 References

Anna5

s.

B.H.L. Aara, P.J.M. van Laarhovan, "A New Polynomial-Time Cooling Schedule," Proc. ICCAD 85, November 1985, pp. 206-208.

Dun385

A. Dunlop, B. Kornighan, "A Procedure for Placements of Standard-Cell VLSI Circuita," IBEE Trans on CAD, Vol. CAD-4, No. 1, Jan 1985, pp 92-98. GravE7

L.R. Grover, "Standard Call Placement Using Simulated Sintering," Proc. 24th DAC, June 1987, pp. 56 - 59.

Pres#7

B.T. Press, "Benchmarks for Cell-Based Layout Systems," Proc. 24rd[Derign Automation Conference, June 1987, pp. 319-320.

Round4

F. Romee, A. Sangiovanni-Vincentelli, "Probabilistic Hill Climbing Algorithms: Properties and Applications," Memorandum No. UCB/ERL MB4/34, March 1984, University of California, Berksley.

Romis

J.S. Rose, W. Soelgrove, Z. Vranamic, "ALTOR. An Automatic Standard Cell Layout Program," Proc. Canadian Conf on VLSI, Nov 1985, pp. 168-173. Romatic

J.S. Rose, D. Blyths, W. Saslgrove, Z. Vranssie, "Fast, High Quality VLSI Placement on an MDMD Malteprocessor," IOCAD 56, Nov. 56, pp. 42-45.

Rocali

J.S. Rose, W.M. Snelgrove, Z.G. Vranssie, "Parallel Standard Cell Placement Algorithms with Quality Equivalent to Simulated Annealing," IEEE Transactions on CAD, Vol. 7, No.3, March 1983, pp. 357-396. Sarbiti

C. Soches, A. Sangiovanni-Vincentelli, "The Turberwold Placement and Routing Package," IEEE ISSC, Vol. SC-20, No. 2, April 1985, pp 510-522. Whit64

S. White, "Concepts of Scale in Simulated Acrossling," Proc. Int. Conf. on Computer Design, October 1984, pp. 646-651.

# The Effect of Logic Block Complexity on Area of Programmable Gate Arrays

Jonathan Rose

Computer Systems Laboratory, Stanford University, Stanford, CA 94305

Robert J. Francis, Paul Chow, David Lewis Dept. of Electrical Engineering, University of Toronto, Toronto, Ont. Canada

### 2 Experimental Procedure

### **1** Introduction

The Programmable Gate Array (PGA) is an exciting new idea in semi-custom integrated circuits that reduces the IC manufacturing time from months to minutes and prototype cost from tens of kilodollars to under \$100. The PGA was introduced in [Cart86] and newer versions have been presented in [Hsie87,Hsie88,EIGa88a,EIAy88]. It is similar to a gate array in structure, but can be field-programmed to specify the function of the basic logic blocks and their interconnection. This paper studies the effect of logic block complexity on total circuit area for PGAs.

The architecture of a PGA consists of its logic block function, interconnection scheme, I/O block design and the global structure. There are many tradeoffs between architecture, area, and speed, each of which depends heavily on the programming technology. Programming technology is the underlying method by which the logic function is set and the connections are implemented at program time. For example, the programming technology used in [Hsie88] is based on static RAM and pass transistors, while that of [ElGa88a] uses an antifuse. In this paper we focus on the effect of logic block complexity on PGA area, ignoring speed considerations. While circuit speed is very important, this work represents an initial exploration into plausible architectures from an area perspective.

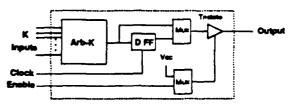

We address two questions: First, should the basic logic block contain a significant amount of fixed hardware, such as a D flip-flop? Our experimental results indicate that a D flip-flop is desirable for large programming technologies (like SRAM [Hsie88]) but that it is inefficient for smaller technologies such as the anti-fuse. Second, for logic blocks containing arbitrary combinational logic functions, (i.e. any K to 1 logic function) what is the best number (K) of inputs to use? Surprisingly, the best number of inputs remains nearly constant over a wide range of programming technologies and was almost the same whether or not the block contained a D flip-flop. To answer these questions, our approach is to implement a set of circuits in a variety of logic blocks and programming technologies, and determine the area required for each. This data will indicate an appropriate choice of logic block, in terms of area, for a given technology.

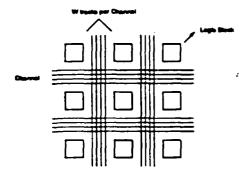

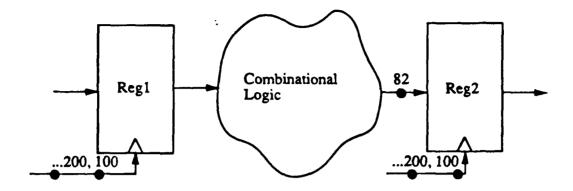

Figure 1 - General Model of Logic Block

Figure 1 depicts the general architectural model used for the logic block. It consists of a K-input arbitrary combinational logic function (referred to as an "Arb-K"), connected to a D flip-flop followed by a multiplexer that selects either the flip-flop output or the Arb-K output. Its output is passed to a tristate driver that can be enabled by another input or left permanently on. To determine if the D flip-flop is beneficial, two variations of this basic model will be considered: one that contains the D flip-flop, and one that does not.

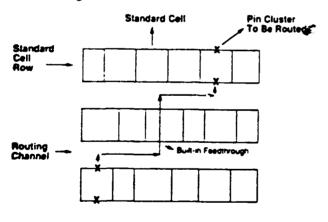

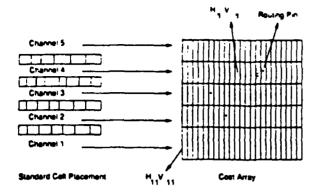

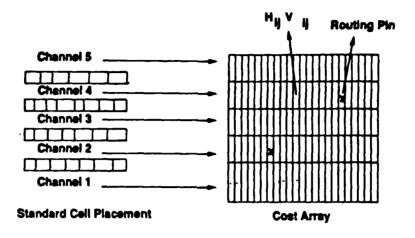

The global architecture of the PGA under consideration is shown in Figure 2. It is a regular array of logic blocks, separated by horizontal and vertical routing channels. The number of tracks in all of the routing channels, W, is the same. Since we want to know the area requirements of a logic block architecture, a crucial concept in this procedure is that W is determined by the placement and routing for each circuit.

The following procedure performs the circuit implementation:

Input: a logic circuit, a range of K's indicating how many inputs on the Arb-K block, and a set of programming technologies.

This work was supported by DARPA Contract #N00014-87-K-0828, and NSERC Operating Granus #A4029 and #A4053.

Figure 2 - Rowing Model of PGA

Output: for each (K, programming technology) pair the area required to implement the circuit with a logic block that contains a D flip-flop, and the area for a logic block that does not.

Procedure: For each logic block type:

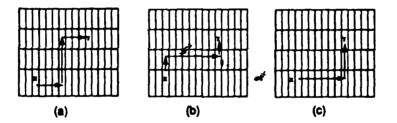

- Partition the original circuit into the current logic block. This is sometimes called *technology mapping* [Detj87], but is a more difficult problem for PGAs because each logic block can collapse many combinational logic functions. The *Chortle* program was developed to do this mapping [Fran88]. It uses a greedy algorithm that tries to collapse as many standard cells as it can into each logic block.

- Perform the placement of the resulting circuit. This is don using the Altor placement program [Rose85], which is based on the min-cut placement algorithm [Breu77]. Altor makes the array as square as possible.

- 3. Perform the global routing of the circuit. Global routing determines the path of channels that each wire is to take, and bence determines the maximum number of tracks required in each channel, W. The algorithm used is similar to the one described in [Rose88], but is changed to fit the routing model pictured in Figure 2.

- 4. Section 3 describes a model for the logic block area and routing area as a function of K and programming sechnology. With this model, W, and the placement dimensions, the circuit area for a range of programming technologies is calculated.

The above procedure makes the approximation that the global routing track count determines the number of tracks required in a channel. This is generally accepted as true for tinconstrained channel routers, but may not be true for switchbased routing schemes. We have reason to believe, however, that the error in this assumption is only a few tracks [EIGa88b].

### **3 Architecture Model**

The area of a logic block is a function of the number of its inputs, the amount of fixed hardware it contains, and the programming technology. The pitch of the routing track can be approximately modeled as a function of the programming technology.

The programming technology is represented by one parameter: the area required to store one bit in the technology, or Bit Area (BA). For example, in the Xilinx PGA [Hsie88], the Bit Area is the area of a static RAM bit. In the Actel PGA [EIGa88a] the bit area is much smaller, close to the space required by an anti-fuse. The overhead required to access the Arb-K block and the area required by the D flip-flop (if it is present) and all other non-arbitrary logic function hardware is represented by a second parameter, called the Fixed Overhead Area (FA).

An Arb-K block, because it can implement any K to 1 logic function, requires  $2^{K}$  bits of information to be stored and so must have area proportional to  $2^{K}$ . Using this, we can derive the following expression for logic block area:

$$Logic Block Area = BA \times 2^{K} + FA$$

where BA is the bit area in the programming technology and FA is the fixed overhead.

The basic technology is assumed to be  $1.25\mu m$  CMOS. FA has been calibrated using data acquired from Xilinx [Cart88], giving FA =  $1200\mu m^2$  for logic blocks without a D flip-flop and  $16000\mu m^2$  for logic blocks with a D flip-flop. The corresponding Bit Area for an SRAM programming technology is  $400\mu m^2$  and is roughly  $40\mu m^2$  for an anti-fuse technology. In our experiments, we will vary the Bit Area between and above these two values.

1

Though the PGA interconnection scheme is not addressed directly in this paper, the area required by routing is an important factor in determining the logic block. We need to know the *pitch* of the routing track as a function of programming technology. Each routing track will need at least one bit of information in it, and probably several — to determine if a set of switches or fuses is open or closed. Since it is difficult to lay out a bit with highly non-square aspect ratios, the pitch of a routing track is approximated as the square root of the area required by a bit, i.e. Routing Pitch =  $\sqrt{BA}$ .

### **4** Experimental Results

The circuits used in these experiments are five standard-cell circuits obtained from Bell-Northern Research [Mart88],

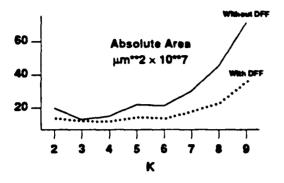

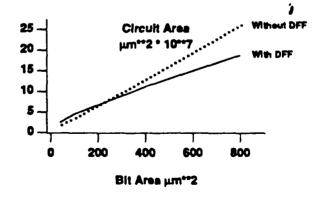

ranging in size from 420 to 1681 standard cells. They consist of a mix of random logic and data path circuits. Figure 3 is a plot of absolute area for the PGA versus number of inputs to the arbitrary combinational logic block, K, for a 1073 standard cell circuit.

Figure 3 - Area for versus K for One Circuit

There are two curves - one giving area when the logic block contains a D flip-flop, and one without. The programming technology,  $BA = 415 \mu m^2$ , corresponds to an SRAM-based approach [Hsie88]. Using similar data for all of the circuits, with more programming technologies, the questions raised in the introduction were addressed.

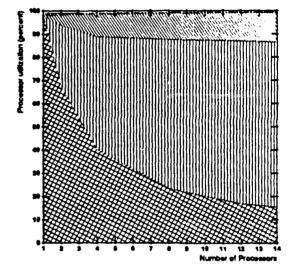

#### 4.1 Number of Inputs to Logic Block

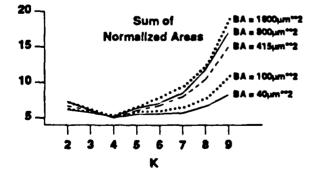

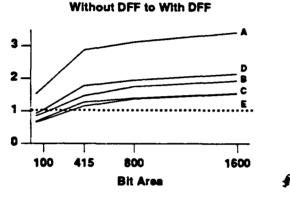

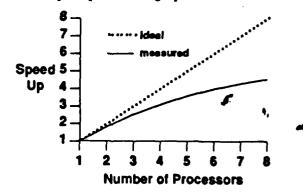

Figure 4 shows the sum of the normalized areas over all of the circuits, versus K. The normalized area for a circuit is determined by dividing the area using logic block K by the best area over all K. The logic block used in this data contains a D flip-flop. Figure 4 gives several plots for different bit areas (programming technologies).

Figure 4 - Sum of Normalized Areas versus K Using DFF

It is clear, from the dip at K = 4, that a 4-input arbitrary logic block consistently achieves the lowest area. Surprisingly, this number is constant over a wide range of bit areas. It is due to the fact that, for a given K, the area is predominantly a linear function of the bit area.

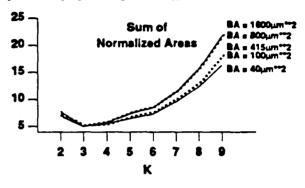

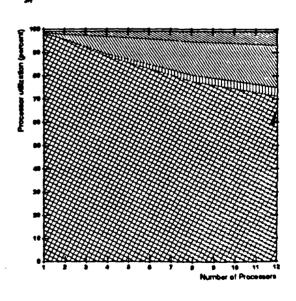

The number of logic blocks increases when the logic block has no flip-flop because the D flip-flops must then be implemented in combinational gates. Since the size of each logic block is less, the final area may or may not be smaller. Figure 5 is a normalized area plot for logic blocks that do not contain D flip-flops. The best number of inputs in this case is three, only slightly different than the D flip-flop case. Again, this number is independent of programming technology.

Figure 5 - Sum of Normalized Areas versus K Without DFF

In both cases, the best K is low (3 or 4) primarily because the circuits cannot make effective use of the larger K blocks. because the increasing functionality comes at the cost of a much greater agtive area, which exponentially increases in K, it doesn't pay to use the larger logic blocks.

### 4.2 Utility of the D Flip-Flop

Figure 6 is plot of circuit area using and not using a D flipflop versus Bit Area for a 1073 standard cell circuit. The circuit area used is the one obtained with the lowest area K.

Figure 6 - Area versus Bit Area 1 Circuit

This figure shows that, for very small bit areas, it is advantageous not to use a D flip flop, but larger bit areas perform better by using a D flip flop. This is true for all of the circuits, but the cross-over point is different for each.

Figure 7 is a plot of <u>Area Without Flip-Flop</u> versus Bit Area for each circuit, indicating when it is advantageous to use a flip-flop. In the smaller bit areas, corresponding to an anti-fuse programming technology, the use of a D flip flop is unprofitable. This is the case in the Actel PGA [ElGa88]. The middle and larger bit areas, corresponding to the SRAM program technology, can benefit by including a D flip-flop, and in fact the Xilinx PGA [Hsie88] uses two D flip-flops.

**Ratio of Area**

Figure 7 - Without DFF: With DFF versus Bit Area

### **5 Conclusions and Future Work**

We have presented a procedure and model to evaluate different logic block architectures for Programmable Gate Arrays, on the basis of circuit area. Using this method, for a particular set of circuits, we have demonstrated a good number of inputs to use for the arbitrary combinational logic block. In addition, we have displayed the trade-off between programming technology area and utility of a D flip-flop in the logic block.

There is an enormous amount of future work to be done in this field. We would like to investigate more kinds of logic blocks - in particular those with less arbitrary logic functions. Other work will directly address questions dealing with circuit speed. This relates to the specific architecture of the interconnection scheme. All of this work needs to be implemented on a wider range of circuits. New CAD algorithms need to be developed for PGAs. Our technology mapper needs more development, and the placement and routing needs to address the specific needs of PGAs. PGAs, because they promise such enormous economic advantages, are a fertile and growing field of research and development.

#### 6 Acknowledgements

The authors are grateful to Grant Martin of Bell-Northern Research for supplying the circuits and cell functional descriptions.

### 7 References

#### [Breu77]

M.A. Breuer, "Min-Cut Placement," Journal of Design Automation and Fault-Tolerant Computing, pp. 343-362, Oct 1977.

[Cart86]

W. Carter et. al, "A User Programmable Reconfigurable Gate Array," Proc. 1986 CICC, May 1986, pp. 233-235.

[Cart88]

W. Carter, Private Communication.

(Detj87)

E.Detjeus et. al, "Technology Mapping in MIS", Proc. ICCAD 87, Nov 1987, pp. 116-119.

[ElAy88]

K. El-Ayat, et. al, "A CMOS Electrically Configurable Gate Array," Proc. 1988 ISSCC, pp. 76-77.

[ElGa88a]

A. El Gamal, et. al, "An Architecture for Electrically Configurable Gate Arrays," Proc. 1988 CICC, May 1988, pp. 15.4.1 - 15.4.4.

[**E**Ga88b]

A. El Climal, Private Communication.

[Fran88]

R.J. Francis, "Chortle: A Technology Mapping Algorithm for Programmable Gate Arrays," in preparation.

[Hsie87]

H. Hsich et. al, "A Second Generation User Programmable Gate Array," Proc. 1987 CICC, May 1987, pp. 515-521.

#### [Hsie88]

H. Hsieh, et. al "A 9000-Gate User-Programmable Gate Array," Proc. 1988 CICC, May 1988, pp. 15.3.1 - 15.3.7.

[Mart88]

Grant Martin, Bell-Northern Research, private communication. [Rose85]

J. Rose, et. al., "ALTOR: An Automatic Standard Cell Layout Program," Proc. Can. Conf. on VLSI, Nov. 1985, pp. 168-173.

### (Rose88)

J. Rose, "LocusRoute: A Parallel Global Router for Standard Cells," Proc. 25th DAC, June 1988, pp. 189-195.

# Memory-Reference Characteristics of Multiprocessor Applications under MACH

Anant Agarwal<sup>\*</sup> and Anoop Gupta Computer Systems Laboratory Stanford University, CA 94305

# Abstract

Shared-memory multiprocessors have received wide attention in recent times as a means of achieving high-performance cost-effectively. Their viability requires a thorough understanding of the memory access patterns of parallel processing applications and operating systems. This paper reports on the memory reference behavior of several parallel applications running under the MACH operating system on a sharedmemory multiprocessor. The data used for this study is derived from multiprocessor address traces obtained from an extended ATUM address tracing scheme implemented on a 4-CPU DEC VAX 8350. The applications include parallel OPS5. logic simulation. and a VSLI wire routing program. Among the important issues addressed in this paper are the amount of sharing in user programs and in the operating system, comparing the characteristics of user and system reference patterns, sharing related to process migration, and the temporal spatial, and processor locality of shared blocks. We also analyze the impact of shared references on cache coherence in shared-memory multiprocessors.

# **1** Introduction

Although we now have a reasonably good understanding of memory system design for uniprocessors, very little is understood about memory system design for multiprocessors. A major reason for this has been the lack of real data about memory reference patterns for multiprocessors, because of the difficulty of tracing such machines. The problem of getting realistic trace data is even more acute if one wishes to the study the effects of operating system references, process migration, and other such real system events. This paper attempts to correct this situation and analyzes memory reference patterns of several parallel applications running under the MACH operating system on a shared-memory multiprocessor. The address traces used in our study were obtained from a 4-processor VAX 8350 multiprocessor using an extended version of the ATUM [1] address tracing technique. These traces contain both system and user memory references, including process migration information.

\*Anant Agarwal is currently with the Laboratory for Computer Science (NE43-418). M.I.T. Cambridge, MA 02139

Analysis of shared-memory reference patterns is needed to determine the most suitable organization of the memory hierarchy in multiprocessors. For example, several cache consistency algorithms proposed in the literature are based on subtle differences in the expected memory reference patterns; lacking detailed data, the benefits of one scheme over another cannot be assessed accurately. While some previous studies have looked at shared-memory reference patterns. e.g., [2]. they did not fully address issues such as the temporal, spatial, and processor locality of shared data, sharing in the operating system, and the impact on cache consistency. For example, we show that shared references display a significant amount of processor locality. The average number of read and write references to a write-shared block before a remote reference are 4 and 2 respectively. This locality is exploited by the write-back class of cache coherence schemes to significantly reduce the cost of references to shared data. Another surprising result that we observed for shared data references is that the total bus bandwidth required is minimized when block size is 4 bytes and increases as the block size is increased. We also observe that processor migration causes a large increase in the sharing level as observed by the caches, which can greatly increase cache coherence traffic on the bus.

This paper is organized as follows. Section 2 presents background information about the ATUM address tracing technique, the applications measured, and the MACH operating system. Section 3 defines our multiprocessor model and the terminology used throughout the paper. Section 4 constitutes the bulk of the paper and is devoted to analyzing the traces. This section characterizes shared-memory reference patterns and looks at the impact of the reference characteristics on cache consistency algorithms. Specifically, in Section 4.1 we present data about the general characteristics of the traces, including statistics about interlocked instructions. Section 4.2 assesses the temporal and processor locality of shared references. Section 4.3 focuses on how the memory reference characteristics affect the performance of various cache consistency algorithms. Section 5 concludes the paper.

# 2 Background and Methodology

Our study is based on trace analysis. The traces are obtained using a multiprocessor extension of the ATUM tracing scheme [1]. ATUM stands for Address Tracing Using Microcode and works as follows: During the execution of each instruction, the microcode writes out the memory references

In Proceedings of SIGMETRICS '88

made by the processor to a portion of memory reserved for tracing. In the multiprocessor extension of ATUM, each access to trace memory is interlocked to enable the microcode in several processors to write their references to this memory. Thus a trace contains interleaved address streams of several processors. The traces used for this study were gathered on a 4-CPU VAN 8350 machine running the MACH operating system. ATUM traces are "complete" in that they capture all operating system and multiprogramming activity. Each trace is roughly 3.5 million references long. In addition to addresses. ATUM records the opcodes, and the virtual-tophysical translations that occur during translation-lookasidebuffer (TLB or TB) misses. A location is considered shared when it is referenced by more than one CPU. Because different processes could access a given shared location with different virtual addresses, sharing is detected by translating the various virtual addresses of a shared location to its common physical address.