| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                  | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| REPORT NUMBER                                                                                                                                                                                                                                                                                                                                 | 2. GOVT ACCESSION NO.                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |

| ARO 25297. MS-CF                                                                                                                                                                                                                                                                                                                              | N/A                                                                                                                                                                                                                                                                                                                                              | N/A                                                                                                                                                    |

| 4. TITLE (and Subtitio)<br>1988 World Materials Congress Proceedings                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                  | 5. TYPE OF REPORT & PERICD COVERED                                                                                                                     |

| 24-30 Sep 88, Chicago <u>Eight Volumes</u>                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                  | 1 Oct 87 - 31 Mar 89<br>6. performing org. report number<br>N/A                                                                                        |

| 7. AUTHOR(*)<br>S. G. Fishman and A. K. Dhingra, editors                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                  | 8. CONTRACT OR GRANT NUMBER(*)<br>DAAL03-87-G-0128                                                                                                     |

| PERFORMING ORGANIZATION NAME AND ADDRE                                                                                                                                                                                                                                                                                                        | 55                                                                                                                                                                                                                                                                                                                                               | 10. PROGRAM ELEMENT. PROJECT, TASK<br>AREA & WORK UNIT NUMBERS                                                                                         |

| ASM International<br>Detroit, MI 48202                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |

| . CONTROLLING OFFICE NAME AND ADDRESS                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                  | N/A                                                                                                                                                    |

| U. S. Army Research Office                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                  | 1988                                                                                                                                                   |

| P. 0. Box 12211                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                  | 13. NUMBER OF PAGES                                                                                                                                    |

| Research Triangle Park NC 27709<br>Monitoring agency name & Address(1/d)/61                                                                                                                                                                                                                                                                   | ent from Controlling Office)                                                                                                                                                                                                                                                                                                                     | 15. SECURITY CLASS. (of this report)                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                  | Unclassified<br>154. DECLASSIFICATION/DOWNGRADING<br>SCHEDULE                                                                                          |

| Submitted for announcement of the abetract entered                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                  | à<br>an Report)                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                               | ings contained in<br>ld not be construe<br>, policy, or decis<br>Dn.<br>and (dentify by block number)<br>ctronic Materials,                                                                                                                                                                                                                      | this report are<br>ed as an official<br>sion, unless so<br>Wear Resistance,                                                                            |

| <ol> <li>DISTRIBUTION STATEMENT (of the ebetrect entered<br/>s. SUPPLEMENTARY NOTES<br/>The view, opinions, and/or find<br/>those of the author(s) and shou<br/>Department of the Army position<br/>designated by other documentati</li> <li>KEY WORDS (Continue on reverse side if necessary<br/>Composites, Sheet Steels, Elered</li> </ol> | ings contained in<br>Id In Block 20, If different fro<br>ings contained in<br>Id not be construe<br>, policy, or decision.<br>and (dentify by block number)<br>ctronic Materials,<br>Integrity Casting<br>and identify by block number)<br>orld Materials Con<br>lowing volumes:<br>Conference Proceed<br>uence on Material<br>Deformation and A | this report are<br>ed as an official<br>sion, unless so<br>Wear Resistance,<br>s, Inclusions, HSLA Steels<br>agress were published<br>ings<br>Behavior |

SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered)

ABSTRACT CONTINUED:

4

SECURITY CLASSIFICATION OF THIS PAGE(When Date Entered)

è

P-rice \$ 75.00

# **Electronic Materials and Processing**

\$

Proceedings of the First Electronic Materials and Processing Congress held in conjunction with the 1988 World Materials Congress Chicago, Illinois, USA 24-30 September 1988

> *Edited by* Prabjit Singh

Sponsored by the Electronic Materials and Processing Division of ASM INTERNATIONAL™

Published by

# 88 12 28 018

The publication of this Conference Proceedings of the 1988 World Materials Congress has been made possible by the generous contributions of the U.S. Bureau of Mines, the U.S. Army Research Office, Cytemp Specialty Steel, ELETROMETAL S.A., and Dofasco Inc.

Copyright© 1988 by ASM INTERNATIONAL™ All Rights Reserved

No part of this book may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical photocopying, recording, or otherwise, without the prior written permission of the publisher. No warranties, express or implied, are given in connection with the accuracy or completeness of this publication and no responsibility can be taken for any claims that may arise.

Nothing contained in this book is to be construed as a grant of any right or manufacture, sale, or use in connection with any method, process, apparatus, product, or composition, whether or not covered by letters patent or registered trademark, nor as a defense against liability for the infringement of letters patent or registered trademark.

Library of Congress Catalog Card Number: 88-071718 ISBN: 0-87170-341-6 SAN: 204-7586

Printed in the United States of America

# **ORGANIZING COMMITTEE**

Dr. Prabjit Singh IBM Corporation Poughkeepsie, NY

Dr. William B. Snyder, Jr. Oak Ridge National Labs Oak Ridge, TN

١

Dr. Wei T. Shieh General Electric Company Utica, NY

> Dr. Jesse H. Chen Cabot Corporation Boyertown, PA

Professor Shyam Murarka Rensselaer Polytechnic Institute Troy, NY

> Dr. James R. Lloyd IBM Corporation Fishkill, NY

Professor Don Preiss North Carolina State University Raleigh, NC

# FOREWORD

The objective of the First Electronic Materials and Processing Congress, organized by the Electronics Materials and Processing Division (EMPD) of ASM INTERNATIONAL, has been to provide an overview of the field of electronic materials by invited speakers who are leaders in their respective specializations. We have tried to cover as much of the field of electronic materials as is possible in four and a half days of programming. The major subjects covered are semiconductor materials, thin-film dielectrics and metallization, materials for packaging including ceramic substrates and printed wire boards, interconnections and hermetic sealing, connector technology, polymers in electronics and advances in electronic materials.

It is hoped that this Congress will be useful to both the specialists and the generalists practicing in the field and to those who are not in the field but are curious about it and may want to get some tidbits of information they could use in their own fields of specialization.

# The Congress was organized by a committee consisting of:

Dr. Prabjit Singh IBM Corporation Poughkeepsie, NY

Dr. William B. Snyder, Jr. Oak Ridge National Labs Oak Ridge, TN

Dr. Wei T. Shieh General Electric Company Utica, NY Professor Shyam Murarka Rensselaer Polytechnic Institute Troy, NY

> Dr. James R. Lloyd IBM Corporation Fishkill, NY

Professor Don Preiss North Carolina State University Raleigh, NC

Dr. Jesse H. Chen Cabot Corporation Boyertown, PA

We wish to recognize the contributions of Dr. R. A. Laudise and Dr. G. Y. Chin of AT&T Bell Labs, Murray Hill, NJ; Mr. R. Moore of Perkin Elmer Corporation, Edison, NJ; Mr. C. MacKay of Microelectronics Computer Corporation, Austin, TX; and Dr. C. Sheldon Roberts, a consultant in private practice. We would also like to acknowledge the excellent support provided by the staff of ASM INTERNATIONAL. Without their help, this Congress and its proceedings would not have been possible.

Prabjit Singh Chairman, First Electronic Materials & Processing Congress

# TABLE OF CONTENTS

| KEYNOTE:<br>Artificially Structured Thin-Film Materials and Interfaces                                                                                                                         | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| SEMI-CONDUCTOR MATERIALS                                                                                                                                                                       |    |

| Materials Science and the Evolution of Integrated Circuit Processing                                                                                                                           | 9  |

| Bulk Crystal Growth of III-V and Other Materials for Optical<br>Communication Beyond 1.5 µm<br><i>R .A. Laudise, W. A. Sunder, R. L. Barns,</i><br><i>J. M. Parsey, Jr., P. M. Bridenbaugh</i> | 17 |

| Materials Aspects of Semiconductor Processing                                                                                                                                                  | 23 |

| New Directions for Semiconductor Device Reliability                                                                                                                                            | 31 |

| THIN FILM DIELECTRICS AND METALLIZATION                                                                                                                                                        |    |

| Kinetics of the Oxidation of Silicon                                                                                                                                                           | 37 |

| Electrical Properties of Thermally Oxidized Silicon                                                                                                                                            | 41 |

| Interlevel Dielectrics and Passivating Films                                                                                                                                                   | 49 |

| Chemical Vapor Deposition of Dielectric and Metal Films                                                                                                                                        | 67 |

|                                                                                                                                                                                                |    |

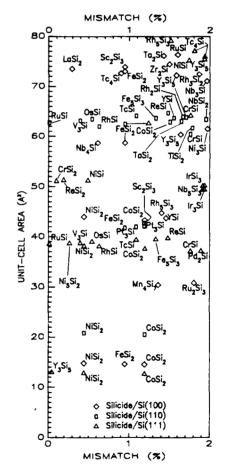

| Transition Metal Silicides for Microelectronics         SJ. Kim, MA. Nicolet                                                                                                                   | 79 |

# MATERIALS FOR ELECTRONIC PACKAGING

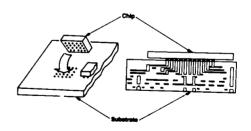

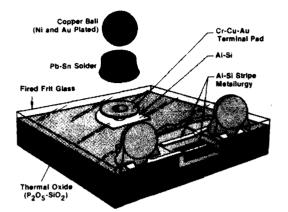

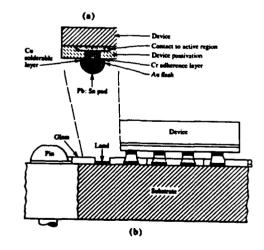

| An Overview of Electronic Packaging101<br>D. P. Seraphim, D. E. Barr, J. M. Brauer                             |

|----------------------------------------------------------------------------------------------------------------|

| High Speed, High Density, Low Loss Interconnections for VLSI, VHSIC, and GaAs on a Variety of Substrates       |

| Electrical Laminates: Where the Industry is Going and Why?                                                     |

| Thermal Expansion Mismatch and Fatigue in Electronic Packages         125           L. S. Goldmann         125 |

| Wire Bonding and Tab Technology                                                                                |

| Controlled Collapse Chip Connections (C4)                                                                      |

| Surface Mount Technology153<br>J. Walker                                                                       |

| Material Considerations in Connector Design                                                                    |

| Alloy Requirements for Electronic Connectors                                                                   |

| Low Cost, High Reliability, Separable Electronic Connectors                                                    |

| The Performance of Electronic Connectors in Flowing Mixed Gas<br>Laboratory Environments                       |

- --

-----

# POLYMERS IN ELECTRONICS

| Flexible Fluoropolymer Laminates                                                              | ) |

|-----------------------------------------------------------------------------------------------|---|

| The Chemistry of Resist Materials213<br>S. A. MacDonald                                       | 3 |

| Electrical Properties of Metal Filled Composites                                              | 5 |

| Materials and Processes of Flexible Printed Circuitry       220         O.C.C. Lin, J. M. Liu | 3 |

| ADVANCES IN ELECTRONIC MATERIALS                                                              |   |

| Hydrogenated Amorphous Silicon: A New Material for Large Area Electronics                     | 1 |

| The Impact of Rapid Thermal Processing                                                        | 7 |

| Principles of STM and Applications in the Semiconductor Ind∟stry                              | 3 |

~

# ARTIFICIALLY STRUCTURED THIN-FILM MATERIALS AND INTERFACES

V. Narayanamurti Sandia National Laboratories Albuguergue, New Mexico, USA

#### ABSTRACT

The ability to artificially structure new materials on an atomic scale by using advanced crystal growth methods such as molecula: beam epitaxy and metal-organic chemical v.por deposition has recently led to the observation of unexpected new physical phenomena and to the creation of entirely new classes of devices. In particular, the growth of materials of variable band gap in technologically important semiconductors such as GaAs, InP, and silicon will be reviewed. Recent results of studies of multi-layered structures and interfaces based on the use of advanced characterization techniques such as high-resolution transmission electron microscopy and scanning tunneling microscopy will be presented.

ADVANCES IN SOLID-STATE ELECTRONICS can usually be traced to a combination of new concepts, materials, and device principles. Integrated circuits, for example, were made possible by the discovery of zone refining, which made possible the synthesis of ultrapure bulk silicon and germanium.

A number of spectacular advances have been made in constructing new materials [1] by ultra-high vacuum and vapor-phase crystal growth techniques. New combinations of materials called heterostructures can be made that have an artificial periodicity and structure which can be controlled at the atomic level. These novel materials include a variety of combinations of metals, semiconductor, and insulators. Quantum mechanical effects can be seen in these thin films and heterostructures, which have dimensions of only a few hundred angstroms. Thus, one can investigate experimentally the one-dimensional quantization of electrons that is familiar to undergraduate physics students. The quantum tunneling of electrons across such thin films can be observed when the thickness of the films is comparable to the extension of electronic wave functions (10 to 100 Å). The control of the electronic and optical properties of materials at the quantum level will have a major impact on new technology, particularly in the area of opto-electronics [2]. Although much work has been done recently in the area of metal films [3], this article will be confined to a discussion of progress in the area of thin-film semiconductor structures grown on technologically important materials such as GaAs, InP, and silicon.

### SEMICONDUCTOR HETEROSTRUCTURES AND EPITAXY

A semiconductor film grows epitaxially if the crystallinity and orientation of the deposited layer are determined by the substrate. If the single crystal formed consists of thin films of dissimilar semiconductors one on top of the other, then the process is called heteroepitaxy. Heteroepitaxy provides new degrees of freedom on the surface of a semiconductor. Although the dominant material in semiconductor electronics has been silicon, researchers are striving to improve its electronic properties through controlled changes in the band structure of the material. For example, compound semiconductors such as GaAs have an intrinsically higher electron mobility than silicon. More importantly, unlike silicon, many III-V semiconductors (semiconductors made from elements in groups III and V, e.g., GaAs) have direct energy band gaps that facilitate the efficient recombination of electrons and holes to generate light.

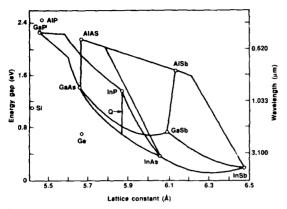

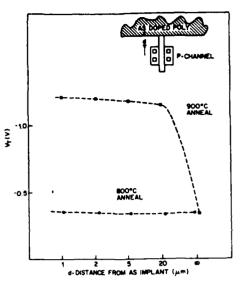

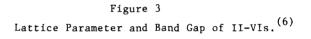

Figure 1 shows a plot of the energy band gap as a function of lattice constant for several III-V semiconductors. The lines that connect points on the graph show how the band gap and the lattice constant vary for mixtures

Fig. 1. A plot of the energy gap versus lattice constant for several III-V semiconductors. The lines that connect points on the graph show how the band gap and the lattice constant vary for mixtures of the binary compounds and for quaternary compounds (Q) to which the points correspond. Also shown are the band gap and lattice constant for the elemental semiconductors silicon and eermanium.

of the binary compounds to which the points correspond. For example, the ternary compound Ga<sub>x</sub>Al<sub>1-x</sub>As, which is closely lattice-matched to GaAs, can be made to have a band gap between 1.4 and 2.2 eV by varying the ratio of gallium to aluminum. The difference in the band gap can be used to confine light and carriers in a GaAs/Al<sub>x</sub>Gal-xAs heterostructure. Quaternary compounds (Q), such as  $In_yGa_{1-y}$ .  $As_yP_{1-y}$ , can be lattice matched to InP and have band gaps in the wavelength range of 1.3 to 1.6  $\mu$ m, which is the range such that light loss from silica-glass fibers (used in fiberoptic communication) is low. Also shown in Figure 1 are the lattice constants and band gaps of elemental silicon and germanium. Silicon has the smallest lattice constant of the semiconductors shown. Thin-film epitaxy on its surface is only possible through the generation of large compressive stresses that cause the alloy layer to deform and thus match the atomic spacing of the substrate.

### FABRICATION OF LAYERED HETEROSTRUCTURES

Great advances in the fabrication of layered heterostructures have taken place in recent years. Among the techniques that have been used are liquid-phase epitaxy (LPE), chemical vapor deposition (CVD), and molecular-beam epitaxy (MBE). In LPE, the epitaxial layer is grown by cooling a heated metallic solution that is saturated with the components needed to grow the layer and that is kept in contact with the substrate. In CVD, the epitaxial layer is grown from a heated source of gaseous elements or compounds that react at the substrate surface. Considerable progress has been made in the growth of quantum well heterostructures with metal-organic chemical vapor deposition (MOCVD). Metal alkyls are used as the compound source. In MBE, the deposition occurs under controlled ultra-high vacuum conditions. Crystal growth results through the reaction of one or more thermal beams of

atoms and molecules of the constituent elements with a crystalline substrate held at a suitable temperature. The growth is monitored through in situ surface diagnostic tools, such as low-energy electron diffraction (LEED). The clean environment, the slow growth rate, and the independent control of the beam sources allow the precise fabrication of atomic scale semiconductor heterostructures.

The clear distinctions among the growth techniques have recently begun to fade, and new techniques have appeared. In the case of III-V compound semiconductors, the high vapor pressure of the group V sources, particularly phosphorus, has led to the development of gassource MBE (GSMBE). In this hybrid technique [4], the gases AsH3 and PH3 are passed through a thermal, catalytic cracker oven and then introduced into the vacuum chamber through a controlled leak. In this way, a stable beam intensity is obtained. For growth of InGaAsP, precise control of the mix of arsenic and phosphorus is possible. In a further variant [5] of GSMBE, the group III elements are organometallic compounds as in MOCVD. Hybrid methods that use the advantages of an ultrahigh vacuum environment and of gaseous sources will likely become the techniques of choice.

Progress in these crystal growth techniques has allowed the construction of atomic scale structures that can have virtually arbitrary potentials for electrons and holes. These potentials include abrupt band discontinuities, which are used to confine carriers in a two-dimensional (2-D) state. Because of their applications to novel and potentially useful devices, the physics of thin-film semiconductor heterostructures has become a subject of intense study.

#### HIGH CARRIER MOBILITY STRUCTURES

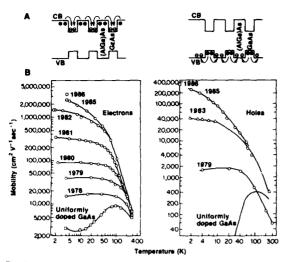

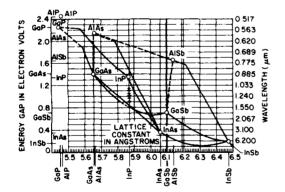

The principal building block of silicon integrated circuits (ICs) is the metal-oxide field-effect transistor (MOSFET), which can be described simply as a layer of 2-D electrons (holes) confined to the interface between crystalline silicon and its native oxide (SiO<sub>2</sub>). In the case of GaAs, the inversion layer can be formed at the interface of a GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As heterostructure. Until 1978, carrier mobilities in such structures were extremely low. At that time, Stormer and his colleagues introduced modulation doping [6]. in which the band-edge discontinuity in the heterostructure is used to separate the electrons (holes) from their parent donors (acceptors), as shown in Figure 2A. This results in greatly enhanced mobilities  $(\mu)$ when compared with uniformly doped materials. The greatest improvement in the mobility is found at low temperatures, where scattering from ionized impurities is the dominant mechanism for reducing mobility in uniformly doped materials. Even at room temperature,

Fig. 2. (A) Schematic illustration of modulation doping for electrons and holes. (The conduction and valence bands are indicated as (CB and VB.) (B) Highest reported electron and hole mobilities as function of temperature during the period 1978 to 1986 (compiled by A. C. Gossard).

modulation-doped structures show an enhancement in mobilities over a uniformly doped material, in spite of the fact that at higher temperatures thermal phonon scattering becomes progressively more important.

Figure 2B shows a plot of the electron and hole mobility that could be achieved with modulation-doped structures during the period 1978 to 1986. The steady improvement in the mobility that could be achieved can be traced to: the introduction of an undoped spacer layer adjacent to the barrier layer that further separates the parent donors (acceptors) from the electrons (holes); the use of a modulation-doped single interface instead of a superlattice; and improvements in growth techniques, such as the introduction of a sample load lock to prevent contamination of the main growth chamber during introduction of the sample. The achievement of high carrier mobilities has led to the observation of novel quantization phenomena (the fractional quantum Hall effect) for 2-D electron and hole systems [7].

Modulation doping causes greatly enhanced conductivity in the plane of the layered structure as compared to that in the direction perpendicular to the layers. This effect is exploited in the modulation-doped field-effect transistor (MODFET). These devices are characterized by high switching speeds and low power consumption. At 77 K, where the modulation doping advantage is already significant, a switching time as short as 5.8 ps has been observed [8]. Such transistors will probably form the basis of advanced GaAs digital circuits. A 4-kilobit static random access memory (RAM) and a high-speed multiplier have been fabricated. The recent demonstration of high-mobility holes has led to the fabrication of low power, complementary (n- and p-type) transistor circuits in the GaAs system.

#### QUANTUM STATES, PERPENDICULAR TRANSPORT, AND TUNNELING

Quantum wells in GaAs with thicknesses of a few hundred angstroms can result in the quantum confinement of electrons. These quantum states were observed in 1974 at low temperatures in electron transport through resonant tunneling [9] and through optical absorption [10] at well-defined energies. The quantum confinement also causes modification of the electronic density of states and has led to the observation of several novel effects, such as room temperature exciton absorption and low-threshold semiconductor lasers.

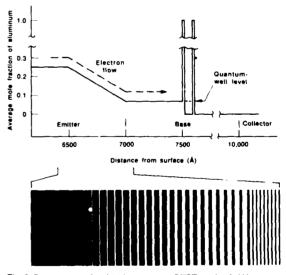

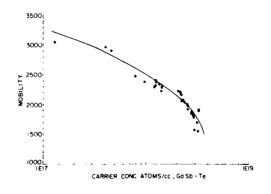

An example of a structure which illustrates the effects of perpendicular resonant tunneling is shown in the upper part of Figure 3, which is a schematic of the first room temperature [11] resonant tunneling bipolar transistor (RTBT). The wide band-gap Al<sub>x</sub>Ga<sub>1-x</sub>As emitter is graded [12] by chopping the beam from the aluminum effusion cell over a distance of about 500 Å to a value of x = 0.07, so that the energy difference between the emitter electrons and the first quantum state in the base of the transistor is near the thermal energy of the electrons. The base itself consists of a 74 Å, undoped GaAs well with 21.5 Å AlAs barriers. Electrons are thermally injected into and transported through the base. The collector current  $(I_c)$ (at a fixed collector-emitter voltage) increases with a gain of ~5 as a function of base current (I<sub>b</sub>) for  $I_b < 2.5$  mA, which is a normal characteristic of a bipolar transistor.

Fig. 3. Resonant tunneling bipolar transistor (RTBT) in the GaAlAs system grown by MBE. The aluminum composition of the emitter is graded by chopping of the effusion cell so that the average composition changes smoothly from a value of 0.25 to 0.07 and so that the emitter electrons are in resonance with the first quantum level in the base (11).

At higher base currents, the current gain is quenched approximately exponentially as a result of the suppression of resonant tunneling, because the conduction band edge of the Al0.07Ga0.93As is above the first energy level of the quantum well. In the region of negative transconductance, the RTBT behaves as an oscillator. The number of possible [13] transistors with unique functions is large. Through careful design of structures with several resonant states in the base, it should be possible to fabricate bipolar transistors with multiple stable states.

## GAS-SOURCE MBE AND QUANTUM WELLS IN INGAASP

There has been significant progress in the growth of heterostructures and quantum wells on InP with the use of GSMBE and low-pressure MOCVD. The entire Q range of quaternary compositions (see Figure 1) of  $Ga_xIn_{1-x}As_yP_{1-y}$  on InP of interest for 1.3 to 1.6  $\mu$ m fiber-optic transmission and heterostructure electronic devices, such as optical modulators and detectors, have been grown.

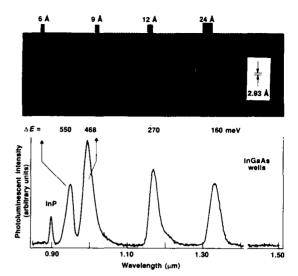

The degree of control [14] that has been achieved in crystal growth is revealed with the transmission electron microscope (TEM) image shown in Figure 4. Micrographs of four Ga0.47In0.53As quantum wells with thicknesses of 6, 9, 12, and 24 Å separated by InP barriers (which are ~150 Å thick) show that there are fluctuations of about one monolayer at the layer interfaces. Similar results were obtained with the quaternary quantum wells, although in that case, the interfaces seem even more abrupt. Figure 4 shows measurements of low-temperature photo-luminescence of these single quantum wells after illumination with light of higher energy than the band gap (632 nm, or 1.95 eV). The figure illustrates the enormous quantum size effect in the quantum well emission compared to that of bulk InGaAs  $(-1.6 \ \mu m)$  which for the thinnest wells (6 Å) corresponds to a shift in energy  $\Delta E$  of 550 meV. For the 6 Å well, the wavelength of emission is about 0.94  $\mu$ m. Thus, by choosing wells of different thicknesses, one can make quantum well laser structures that span a wide wavelength range. The optical data also suggests a high degree of structural perfection (monolayer abruptness).

#### LATERAL QUANTUM CONFINEMENT

MBE has been primarily used to provide quantum-confined structures in the direction of growth. Confinement in one and zero dimensions (quantum wires and quantum boxes) requires fabrication of laterally confined structures on a scale of about 100 Å. Such laterally confined structures can, in principle, be made by lithographically patterning the transverse dimensions of a quantum well structure grown by MBE. Such dimensions are at the present limits of

Fig. 4. Transmission electron microscope image of InGaAs quantum wells of thickness 6, 9, 12, and 24 Å separated by 150 Å InP barriers. The bottom shows photoluminescence spectra taken at 6 K of the quantum wells. The shift  $\Delta E$  is measured from the known energy gap of bulk InGaAs (14).

electron-beam lithography. In small structures, the ratio of surface to volume is large and the patterning must be such that it does not degrade the sidewalls of the layers. Because of modification of the electronic density of states in these confined structures, several novel optical effects, such as an improvement in the performance of quantum wire semiconductor lasers, have been theoretically predicted.

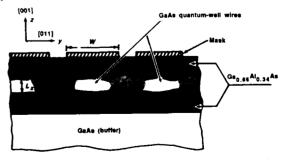

Progress has been made in fabricating such structures in both the GaAs/AlGaAs and the InGaAs/InP systems. Cibert, et al. [15], have fabricated quantum wires and boxes. They used gallium ions to disorder local areas of a GaAs/AlGaAs quantum well structure (see Figure 5). The ion implantation occurred through open areas of an electron-beam defined tungsten mask. They discovered that the inter-diffusion of aluminum in GaAs after a rapid thermal anneal is much larger in the disordered region than in the masked region. Thus, they were able to produce high-quality, laterally confined structures, in which new optical transitions that correspond to the theoretically predicted energy levels for quantum wires and boxes were observed.

Fig. 5. Schematic (not to scale) of GaAs quantum well wire structure after implantation and annealing. The position of the mask (which has a width W) during implantation is indicated. The wires (which have a thickness  $L_t$ ) are actually 1  $\mu$ m apart (15).

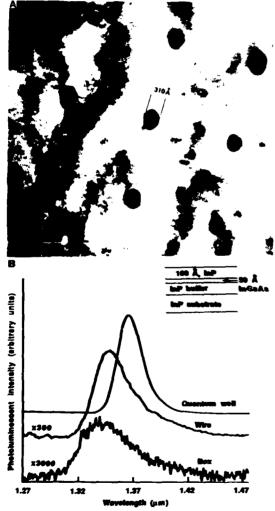

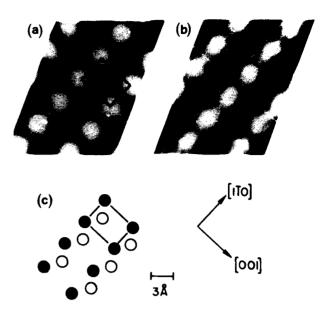

An interesting case for the study of lateral confinement is the InGaAs/InP system. In this system, the surface recombination velocity of electrons and holes is -0.01 of that in the GaAs/AlGaAs system [16]. Thus, high luminescence efficiency may be expected. Temkin, et al. [17], have fabricated quantum wires and boxes on the order of 300 Å in this system with electron-beam lithography. Figure 6A shows an electron micrograph of some typical quantum boxes with an average diameter of 300 (±50) Å. Quantum wires with lateral dimensions ~300 Å have also been fabricated. Figure 6B shows typical photo-luminescence spectra for these quantum structures. The luminescence shift of 8 to 14 meV is consistent with that expected for lateral dimensional confinement. The high photoluminescence efficiency is also consistent with the low surface recombination velocity that is characteristic of InP and its alloys.

Fig. 6. (A) The transmission electron micrograph shows InGaAs/InP quantum boxes that were fabricated by direct electron-beam writing and ion-beam milling. The average box diameter is 300 Å. The initial SO-Å InGaAs quantum well, upper panel, was grown by GSMBE (1/2). (B) Photoluminescence of control quantum well sample, and for lithographically patterned 300-Å quantum well, wires, and boxes. The wires and boxes have thicknesses of ~300 Å.

#### HETEROEPITAXY ON SILICON

The use of silicon in semiconductor applications is ultimately limited by its incompatibility with other semiconductor materials. Silicon as a substrate material alone has attractive properties such as high mechanical strength, high degree of crystalline perfection, large diameters (-20 cm) to which it can be grown, natural abundance, and low cost. It is clear from Figure 1 that if the electronic and optical properties of the silicon surface are to be altered through lattice-matched heterostructures, the number of possibilities are few. Both GaP and AIP, which are latticematched to silicon, are composed of elements that are commonly used as dopants in silicon. Thus, when crystal growth of thin films has been attempted, uncontrolled cross-doping effects (e.g., inter-diffusion of gallium or aluminum into the silicon) have resulted. Two major approaches have been used in heterostructure band-gap engineering on silicon. In the first, the elemental semiconductor germanium and its alloys  $Ge_{X}Si_{1-X}$  are grown. The idea is to use Si/Ge<sub>x</sub>Si<sub>1-x</sub> heterostructure single interfaces and superlattices for altering the band gap and, hence, the electronic and optical properties on the surface of silicon. In the second, silicon is used as a substrate material for growth of GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As heterostructure devices. This approach combines the excellent properties of silicon as a substrate material with the unique electronic and optical properties of GaAs/AlGaAs heterostructures.

Although germanium has the same crystal structure as silicon, its lattice constant is approximately 4% larger. The epitaxial growth can occur either as incommensurate or as commensurate epitaxy. In the former (upper inset of Figure 7), both crystals retain their individual structure; at the interface of germanium and silicon, every 25th row of atoms will have only three bonding neighbors. Rows of these improperly bonded atoms form "misfit dislocations" that can seriously degrade the electronic properties of the interface. In commensurate epitaxy (bottom inset of Figure 7), the fourfold bonding at the interface is preserved by compression of the larger germanium lattice along the interface and by elongation perpendicular to the interface. Such strained-layer epitaxy is possible if the stored strain energy in the film is lower than the reduction in the dangling bond energy.

Heterostructures of Si/SiGe have been grown by MBE by Bean [18]. Figure 7 shows a plot of the thickness of  $Ge_XSi_{1-x}$  alloys on silicon for commensurate epitaxy. The observed thicknesses for commensurate epitaxy are about ten times as large as those predicted by equilibrium theories of dislocation formation. The band gap of the

**Fig. 7.** Plot of critical film thickness for commensurate epitaxy as a function of x for Ge,  $Si_{1-1}$  alloys grown on silicon substrates. The insets show the atomic arrangements for the strained but defect-free material found in sufficiently thin layers and for the bulk material in which misfit dislocations accommodate the lattice mismatch. [Adapted from (18)]

strained GeSi films is considerably smaller than that of corresponding bulk alloys. The growth of GeSi heterostructures on silicon thus allows one to exploit "band-gap engineering" techniques for the production of novel, long wavelength photo-detectors and MODFETs with silicon-based technologies.

The other approach is heteroepitaxial semiconductor (GaAs) growth on silicon [19]. Like germanium, GaAs also has a lattice constant some 4% larger than that of silicon. GaAs is a polar semiconductor with a zinc blend structure. Thus, in addition to misfit dislocations, one must contend with control of additional structural defects such as antiphase domains. An anti-phase domain is a region of the crystal where the nearestneighbor bond is not between a gallium atom and an arsenic atom, but is between two gallium atoms. The formation of such antiphase domains car be minimized by using misoriented silicon substrates. A silicon surface that is cut a few degrees off the <100> direction has a predominant number of double atomic steps (steps whose height is twice that of a single atomic step). Growth on such surfaces leads to a material that is free of anti-phase domains.

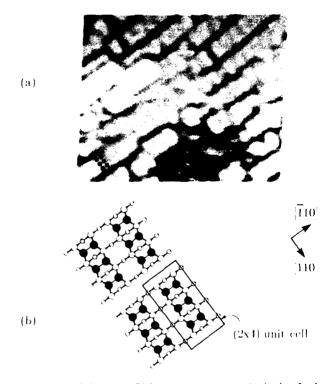

In order to grow thick layers of GaAs on silicon with a low dislocation density, researchers have tried several other approaches besides misoriented substrates. In one approach [20], a germanium film (which has approximately the same lattice constant as GaAs, see Figure 1) is grown by MBE. A GaAs/GaAsP strained-layer superlattice (SLS) is then grown by MOCVD, over which a thick GaAs film is grown (see Figure 8). It is clear from the transmission electron microscope (TEM) image in Figure 8 that the SLS appears to have trapped dislocations that may have moved from the germanium layer during the growth of the GaAs layer. The apparent dislocation density of these films at the surface is low  $(-10^4 \text{ to } -10^5 \text{ cm}^{-2})$ . Such structures have been used to grow GaAs/AlGaAs double heterostructure lasers that have low current thresholds. These lasers are not yet as good as those grown directly on GaAs substrates, but the progress in the growth of such structures, which are extremely sensitive to dislocation, has been remarkable.

MBE also allows the growth of compatible metals, such as silicides and insulators, on silicon. A buried heterostructure [21] of Si/CoSi<sub>2</sub>Si has been grown that demonstrates transistor action with the metal laser as a base. Epitaxial fluorides [22] on silicon have been used both for dielectric isolation and for the fabrication of field-effect transistors (FETs). Most recently, ordered monolayer structures [23] of germanium on silicon have been grown, which represent another class of new materials on silicon.

The possibilities opened by heteroepitaxy with MBE are many and have only just begun to be explored. The low growth temperature and control permitted by MBE are unparalleled and will permit much further development in the area of heteroepitaxy.

Fig. 8. Transmission electron micrograph of a GaAs/GaAs-GaAsP SLS structure grown on Ge/Si composite substrate. The GaAs layer is 2  $\mu$ m thick. The germanium film on silicon was grown by MBE, the GaAs and GaAsP were grown by MOCVD. [Adapted from (20)]

## CHARACTERIZATION OF INTERFACES AND THIN FILMS

The surface and interface characterization of MBE-grown films has been of major importance in understanding the early stages of crystal growth and lattice formation. The earliest advances were made with in situ LEED. More recently, powerful analytical techniques such as high-resolution TEM (HRTEM), x-ray scattering, and Rutherford backscattering have been used to characterize the degree of perfection of thin-film heterostructures. Often the results of a variety of techniques must be combined to obtain a complete picture. I have highlighted electron microscopy, which gives excellent visual images of the degree of perfection of thin-film interfaces and their structure.

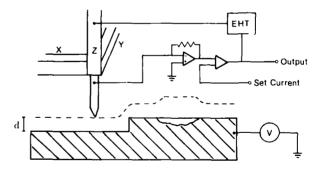

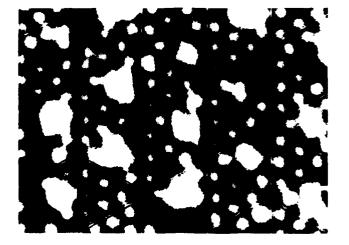

Another microscopic technique that gives detailed and direct information of interface structure is the recently developed scanning tunneling microscope (STM) of Binnig, et al. [24]. The STM measures the very small current that flows when a potential is applied between the surface and a probe tip that is scanned across the interface at a distance of only a few angstroms. The quantum mechanical tunneling current is extremely sensitive to the distance between atoms on the surface and the tip, and serves as a direct method of observing individual atoms at interfaces. The STM has recently been used by Golovchenko and co-workers [25] to obtain the first images of atomic steps and their structure on silicon surfaces. They have also imaged the strainstabilized crystal structure of germanium and GeSi grown by MBE on silicon surfaces.

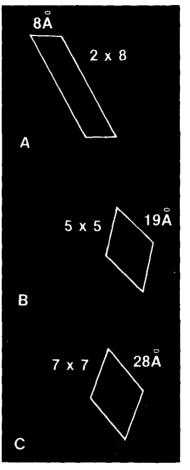

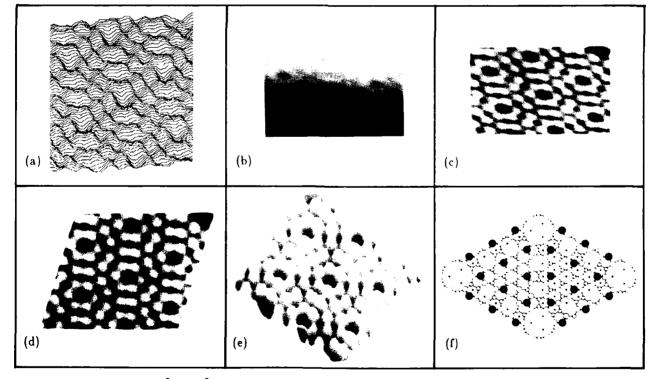

LEED studies [26] showed that germanium epitaxially grown on silicon has a wide variety of reconstructions that depend on heat treatment. The STM images [27] shown in Figure 9 provide the first detailed atomic scale images of the Ge c(2 x 8), GeSi(5 x 5), and  $Ge(7 \times 7)$  reconstructions in silicon. (These are lattice symmetry designations.) These results show the remarkable detail of the surface structure and have helped to resolve many outstanding questions on the relation between clean germanium and silicon surface reconstructions. Of particular interest is the observation of the  $GeSi(5 \times 5)$ reconstruction that has a rhombohedral unit cell with a lattice constant of 19.2 Å. The asymmetry between the two halves of the unit cell is clearly visible and suggests that an ordered alloy with alternate positions around the deep depressions exists on the surface.

These studies, like many of the other cited in this article, are still in their infancy. It is probable that future MBE machines will have capability for *in situ* studies of crystal growth by the most powerful characterization techniques, such as STM and HRTEM. If recent history is any guide, it is likely that such studies will lead to entirely new classes of materials as a fuller understanding is developed of the first stages of crystal growth.

Fig. 9. Scanning runneling microscopy im-ages of germanium and GeSi on silicon grown by MBE and with different heat treatments. (A) The  $c(2 \times 8)$  reconstruction for ger-manium on silicon, which is the normal reconstruction for clean germanium. (B) The wly observed (5 × 5) reconstruction for a 50:50 allov of GeSi. This image also shows indications of order-ing. (C) The  $(7 \times 7)$ reconstruction, which is typical of clean silicon. [Adapted from (27)]

### REFERENCES

- Cho, A. Y., Thin Solid Films <u>100</u>, 291 (1983); and Dupuis, R. D., Science <u>226</u>, 623 (1984).

- Narayanamurti, V., Phys. Today <u>37</u>, No. 10, 24 (1984).

- Falco, C. M., Festkorperprobleme, Advances in Solid State Phys. <u>25</u>, 531 (1985).

- Panish, M. B., J. Electrochem. Soc. <u>127</u>, 2729 (1980); and Panish, M. B., in Proc. of 1986 York Molecular Beam Epitaxy Conf., to be published in J. Cryst. Growth.

- 5. Tsang, W. T., Appl. Phys. Lett. <u>45</u>, 1234 (1984).

- Stormer, H. L., Surf. Sci. <u>132</u>, 519 (1983).

- Stormer, H. L., and Tsui, D. C., Science <u>220</u>, 1241 (1983).

- Shah, N. J.; Pei, S. S.; Tu, C. W.; and Tiberio, R. C., IEEE Trans. Electron Devices <u>ED-33</u>, 543 (1986).

- 9. Chang, L. L. and Esaki, L., "Molecular Beam Expitaxy," Pergamon Press, Oxford (1980).

- Dingle, R., Festkorperprobleme <u>15</u>, 21 (1975).

- 11. Capasso, F.; Sen, S.; Gossard, A. C.; Hutchinson, A. L.; and English, J. H., IEEE Electron Device Lett. <u>EDL-7</u>, 573 (1986).

- 12. Gossard, A. C., IEEE J. Quantum Electron. 22, 1649 (1986).

- 13. Capasso, F., Science 235, 172 (1987).

- 14. Panish, M. B.; Temkin, H.; Hamm, R. A.; and Chu, S. N. G., Appl. Phys. Lett. <u>49</u>, 164 (1986).

- 15. Cibert, J.; et al., Appl. Phys. Lett. <u>49</u>, 1275 (1986).

- Casey, H. C., and Buehler, E., Appl. Phys. Lett. <u>30</u>, 247 (1977).

- Temkin, H.; Dolan, G. J.; Panish, M. B.; and Chu, S. N. G., Appl. Phys. Lett., in press.

- 18. Bean. J. C., Science 230, 127 (1985).

- Wright, S. L.; Kroemer, H.; and Inada, M., J. Appl. Phys. <u>55</u>, 2916 (1984); and Windhorn, T. H. and Metze, G. M., Appl. Phys. Lett. <u>47</u>, 1031 (1985); and Fischer, R.; Kopp, W.; and Morkoc, H., Appl. Phys. Lett. <u>48</u>, 1360 (1986).

- 20. Dupuis, R. D.; et al., J. Electron. Mater., in press.

- 21. Hensel, J. C.; Levi, A. F. J.; Tung, R. T.; and Gibson, J. M., Appl. Phys. Lett. <u>47</u>, 151 (1985).

- Smith, T. P., III; Phillips, J. M.; Augustyniak, W. M.; and Stiles, P. J., Appl. Phys. Lett. <u>45</u>, 907 (1984).

- Bevk, J.; Mannaerts, J. P.; Feldman, L. C.; Davidson, B. A.; and Ourmazd, A., Appl. Phys. Lett. <u>49</u>, 286 (1986).

- 24. Binnig, G.; Rohrer, H.; Gerber, C.; and Weibel, E., Phys. Rev. Lett. <u>50</u>, 120 (1983).

- 25. Golovchenko, J. A., Science <u>232</u>, 48 (1986).

- 26. Gossman, H. J.; Bean, J. C.; Feldman, L. C.; McRae, E. G.; and Robinson, I. K., J. Vac. Sci. Technol. <u>A3</u>, 1633 (1985).

- 27. Becker, R. S.; Golovchenko, J. A.; and Swartzentruber, B. S., Phys. Rev. Lett. <u>54</u>, 2678 (1985); and Phys. Rev. <u>B32</u>, 8455 (1985).

# MATERIALS SCIENCE AND THE EVOLUTION OF INTEGRATED CIRCUIT PROCESSING

D. S. Williams, S. M. Sze, R. S. Wagner

AT&T Bell Laboratories 600 Mountain Avenue Murray Hill, New Jersey 07974, USA

# ABSTRACT

The explosion in our capability to transmit and process information is possible because of the continued improvement in cost and performance of integrated circuits. Although the minimum lithographic feature size is the processing parameter often tracked in the evolution of the technology, much of the innovation that characterizes this progress has been achieved by solving problems familiar to materials scientists.

In this discussion, the path from discrete devices to megabit memory technologies will be outlined. The evolution in fabrication processes will highlight the role of materials in the progress of this remarkable technology. The future will demand further innovation. Scaling of device geometries will continue into the 21st century as the physical dimensions to be controlled become ten's of atom layers. As a result, the challenges in integrated circuit processing will continue to be vibrant to those trained in the materials disciplines.

# Introduction

The electronics industry has grown rapidly for the past two decades as a result of technological innovation in Integrated Circuit (IC) design and manufacture, and as a result of new applications for electronic systems. Electronic equipment sales in the U.S. totaled \$210 billion dollars in 1986 and are projected to grow at an average rate of 12% to reach \$1 trillion by the year 2000.<sup>(1)</sup> At this volume, electronic sales will exceed the sales of the automobile, chemical and steel industries. This phenomenal growth is driven at the component level by the continual improvement of IC performance and cost.

In the 1960's, the IC market was based primarily on bipolar transistors, but since 1975 the metal oxide semiconductor (MOS) transistor has grown to be the dominant device structure. The advantages of MOS in large scale IC production are derived from the processes of miniaturization. The advantages of miniaturization are twofold: increased circuit performance, and increased functional density. The circuit performance of MOS devices improves upon scaling because of the increased switching speed of the transistor itself, and because of the decrease in routing delays as transistors are more densely packed. The increase in functional density originates from the greater number of logic elements of smaller dimensions that can be placed within a given chip size. Miniaturization has resulted in a rapid succession of technologies offering advantages of dimensional scaling, reduction of power requirements and improvements in manufacturing productivity.

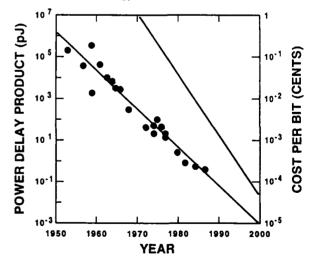

The performance of an MOS IC technology is often described by the product of power and propagation delay. Figure 1 shows that the power-delay product for MOS devices has decreased dramatically for the past 25 years and is projected to do so to the end of the century. Also shown in Fig. 1 is a similarly dramatic decrease in the cost per function through improvements in manufacturing productivity, even while the basic technology continued to evolve.

Figure 1. Power  $\cdot$  delay product and cost per function as a function of time (i.e. the date of introduction of the IC technology.)

Figure 2. Minimum lithographic feature size as a function of the date of introduction of the technology.

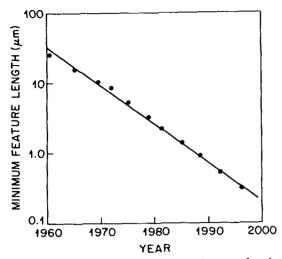

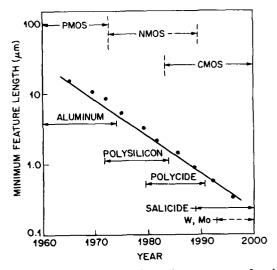

The fabrication of integrated circuits can simplistically be described as the process of growing or depositing thin films and then selectively removing them. To define the regions of selective processing, lithographic technology is required, and the evolution of this technology has traditionally determined the pace of progress. Thus, the minimum feature size that is patterned in the integrated circuit has become a common metric to describe the evolution of MOS technology. Figure 2 shows industry progress as measured by the minimum feature size. Notice that the rate of shrinkage approximates 13% per year and has resulted in a new generation of technology approximately every 2-1/2 years. Characteristically, each new generation occupies one fourth the area and has twice the speed of the previous generation. This rate of innovation has fueled the electronics revolution, but lithographic progress does not describe the total evolutionary process. Much of the progress that has made this remarkable technology possible has required the control and characterization of processes familiar to those trained in the materials disciplines.

# Device Scaling

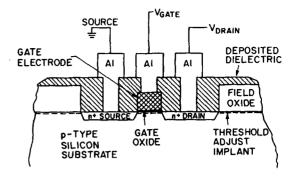

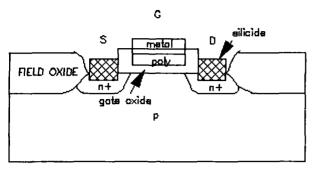

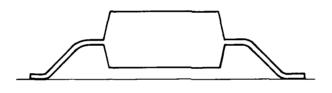

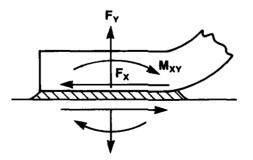

The miniaturization of MOS devices requires the scaling of both lateral and vertical dimensions of the transistor structure as well as scaling of the operating voltages (if constant electric fields are maintained.) This reduction of transistor size has advantages in conserving "lay-out" area of the chip as well as advantages in transistor performance. Figure 3 is a schematic of an n-channel, MOS transistor (called NMOS) showing the essential features of the structure. Under normal operation, a voltage is applied to the drain while the source is grounded. No current flows between source and drain, however, unless a positive voltage is applied to the gate electrode. This gate voltage attracts electrons to the surface, thereby creating a channel beneath the gate oxide that allows current to flow from source to drain. Many such active transistors are combined to form logic elements in a digital circuit design or are combined with passive elements, such as capacitors, resistors or inductors to perform a wide range of analog circuit functions.

Figure 3. Schematic of an MOS device.

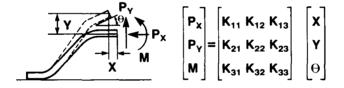

The impact of scaling, or the reduction of dimensions by a scaling factor X > 1, is summarized in Table I.<sup>(2)</sup> In scaling, the vertical dimensions of gate oxide and junction depth are decreased by a factor  $X^{-1}$ . The critical lateral dimension of gate length is also decreased by the factor  $X^{-1}$ , as is the power supply voltage for constant field scaling. The dopant concentration in the substrate increases by the factor X, but the power density on the circuit remains constant because the circuit power scales by  $X^{-2}$  while the density of devices scales as  $X^2$ . The reduction in gate length results in a decrease in the delay time of the transistor logic function itself. The result of this decrease in transit time and the decrease in power of a single device is a power-delay product that scales by the factor  $X^{-3}$ .

# TABLE I

#### MOS Device Scaling<sup>(2)</sup>

# For Constant Field Scaling by Factor of X:

| Gate Length                    | X-1             |

|--------------------------------|-----------------|

| Oxide Thickness                | X-1             |

| Junction Depth                 | X <sup>-1</sup> |

| Supply Voltage                 | X-1             |

| Substrate Dopant Concentration | X1              |

| Power Density                  | 1               |

| Circuit Power                  | X <sup>-2</sup> |

| Gate Delay                     | X-1             |

| Power · Delay Product          | X-3             |

# Crystal Growth

The evolution of IC manufacturing practice has led to significant changes in materials and processes. Some changes were the outgrowth of scaling requirements such as the addition of refractory metal silicides to the gate electrode to decrease interconnect routing delays. However, other materials innovations have been driven solely by manufacturing productivity improvements. The art and science of crystal growth is certainly an example of productivity driven innovation. Because the cost of wafer processing is relatively insensitive to wafer size, economies of scale drive the industry to larger diameter wafers resulting in more chips per wafer. The vast majority of silicon substrates used in IC processing are grown by the Czochralski technique. The requirements of wafers produced by these methods are that they be generally free of dislocations, while the dopant and impurity concentrations, the flatness and the thickness be rigidly controlled. Figure 4 shows the progression as increasingly larger diameter wafers have been introduced into manufacture. The figure shows that from the early days of the industry when the substrates contained only a few devices, the introduction of larger diameter of substrates has been a common event. At this writing, 150 mm diameter wafer processing lines are common, with 200 mm lines under construction. This trend toward larger wafer diameters is expected to continue through the end of the century, as developmental efforts have shown the feasibility of growth for 300 mm diameter boules.

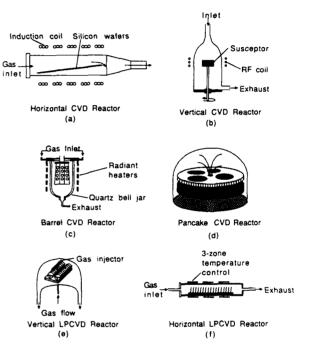

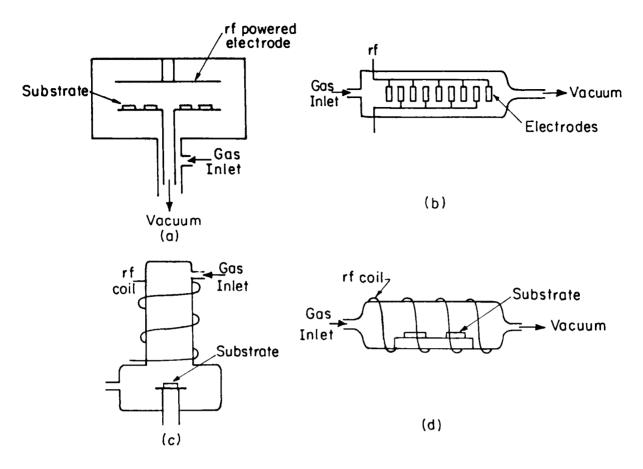

The epitaxial growth of thin layers (<10  $\mu$ m) of lightly doped silicon onto large diameter wafers is another impressively sophisticated materials process that has become commonplace in IC manufacture. The impetus for such structures is the need to dope regions around n-channel devices and p-channel devices differently. When both devices are used in logic arrays, as in Complementary MOS (CMOS) structures, epitaxial silicon with lithographically defined "tubs" is required. The material quality requirements applied to a substrate wafer are extended to epitaxial silicon growth, and crystalline defect formation in epi-wafers is a major cause of device yield degradation. Large diameter wafer requirements have spawned new designs of epi-growth reactors through the need for high throughput, lower temperature variation and robotic loading for improved cleanliness.

# Silicon Oxidation

Silicon has become the dominant semiconductor substrate material for IC manufacture partly because of the properties of its oxide. High quality silicon dioxide can be thermally grown in pure oxygen or in steam as a routine manufacturing process. The thickness and integrity of this oxide is important to device performance, reliability and yield. Figure 3 shows that a thick field oxide provides isolation and a thin gate oxide controls the current flow in the transistor. As a result, the oxidation of

Figure 4. Wafer diameter as a function of date of introduction of the technology. (From K. E. Benson et al., unpublished).

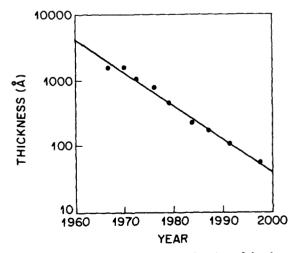

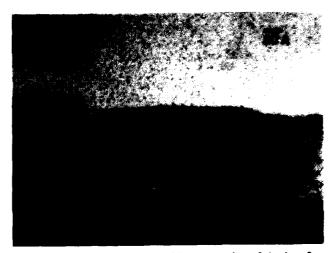

silicon and its properties have been extensively studied and are the topic of complete symposia in support of this industry.<sup>(3)</sup> The thermal growth of gate oxide on <100> single crystal silicon is the most critical step in the entire MOS manufacturing process. Figure 5 shows the progression of gate oxide thickness as succeeding generations of technology were introduced. This gate oxide must endure electric fields of  $-3 \times 10^6$  volt/cm throughout the design lifetime of the device and must endure "burn-in" fields that are higher. In the development of leading edge technologies, devices with 10 nm thick gate oxides that are pin-hole free over areas of 1 cm<sup>2</sup> are routinely fabricated. Furthermore, techniques for growing <10 nm oxides are under development. However, many important processing details remain in growing oxides of the thicknesses required that can sustain such high electric fields. Figure 6 is a high resolution TEM micrograph of thick SiO<sub>2</sub> thermally grown on <100> silicon after improper cleaning procedures. Notice the non-uniformity of the SiO<sub>7</sub>Si interface, which will lead to non-uniform electric field distributions and thus to premature breakdown of the oxide. The nonuniformities of the interface in Fig. 6 are a significant fraction of the total oxide thickness that will be required by device scaling in mid-1990. Clearly many challenges in the field of oxidation of silicon will be encountered as scaling of device dimensions continues

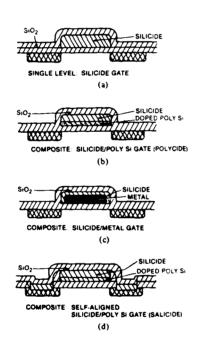

#### Gate Materials

The gate acts as the logic switch in the MOS device by generating a conducting region beneath the gate oxide that allows current to flow from source to drain. The gate electrode length is usually fabricated as the minimum lithographic dimensional, and requires strict dimension control during processing because the device switching speed is directly related to length. Figure 7 shows the selection of gate materials through the evolution of MOS technology. Aluminum gate electrodes were used in the early days of IC fabrication when p-channel transistors dominated the technology (called PMOS). However, the invention of the "self-aligned" polysilicon gate electrode coincided with the conversion to n-type MOS transistors (NMOS) and has been one of the most enduring processing innovations.

Figure 5. Thickness of gate oxide as a function of the date of introduction of the technology.

In the early years of MOS device processing, the junctions in single crystal silicon which form the source/drain areas were formed by diffusion of dopants into the substrate at high temperatures (1000-1100°C) followed by the alignment of the aluminum gate electrode to the diffused regions. A major advance in manufacturing throughput and yield of MOS structures occurred with the selection of a gate material of The chemical vapor deposition of "polysilicon." polycrystalline silicon (polysilicon) onto the gate oxide, which was followed by a gate electrode patterning step, allowed the gate to be used as the "self-aligned" mask for ion implantation or diffusion of source/drain dopants into the substrate. This change of material enabled the elimination of the gate misalignment tolerances from the transistor specifications, thereby greatly improving performance and device yield.

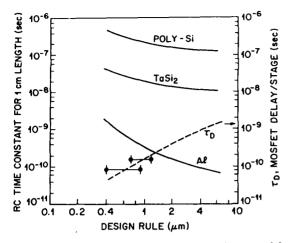

This change in gate electrode material did not come without a penalty, however. Aluminum has a resistivity of  $3 \times 10^{-6} \Omega$ -cm whereas heavily doped polysilicon has a resistivity of  $-5 \times 10^{-3} \Omega$ -cm. When device designs use the gate electrode to route signals long distances, such as in large memory circuits, the propagation delay of the gate electrode can adversely affect circuit performance. Figure 8 shows the impact of gate routing delays on circuit performance for differing interconnect materials.<sup>(4)</sup> For polysilicon gates, the delay in routing a signal 1 cm is several orders of magnitude greater, even at 10 µm design rules, than the MOSFET delay.

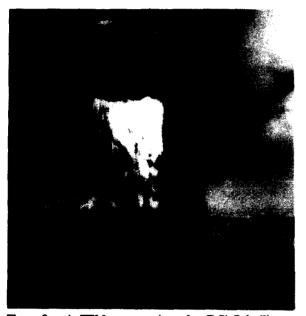

An improvement in gate interconnect delay that has been widely adopted by the MOS industry involves yet another material change, or rather a material addition. By "strapping" a refractory metal silicide onto the self-aligned polysilicon gate material, the advantages and experience base of the self-aligned polysilicon gate can be retained while the gate interconnect resistivity can be decreased by a factor of ~10 (Fig. 8). The silicon saturated refractory metal silicides of Mo, W, Ta and Ti were carefully scrutinized for processing related properties such as high temperature stability, deposition process and stoichiometry control, oxidation rate, wet and dry etch rates and resistivity.<sup>(5)</sup> Figure 9 shows a TEM cross section of a TaSi<sub>2</sub>/polysilicon gate electrode with junction delineation showing the n<sup>+</sup>/p source/drain profiles. This gate electrode structure was introduced into manufacture by AT&T-Microelectronics in a 256K DRAM process in 1981 and remains in large volume manufacture today.

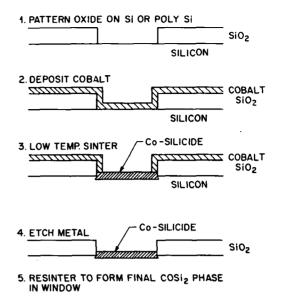

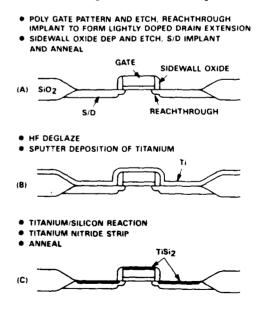

Scaling of device geometry continues to pressure interconnect delay considerations. Figure 8 shows that even with aluminum metallization, interconnect delay will limit logic function performance at sub-micron design rules. In addition, junction depths have become shallower and with smaller window sizes, thus driving the contact resistance of metal to source/drain region higher. Recent processing developments that decrease these parasitic resistivities use a process to form a "self-aligned" silicide in the source, drain and gate. The method of such metallization is illustrated in Fig. 10 where regions of silicon dioxide are patterned to expose substrate silicon or patterned polysilicon. Metal is then deposited and the structure annealed to react metal with the silicon substrate and with the polysilicon gate to form a metal silicide. A selective wet chemical etch then removes the unreacted metal leaving the metal silicide in selective locations. Such processes

Figure 6. High resolution TEM cross-section of the interface between a thermal oxide grown on <100> silicon single crystal. (From J. M. Brown, unpublished).

Figure 7. Gate material and transistor type as a function of date of introduction of the technology.

are well developed for the formation of titanium disilicide and cobalt disilicide. Sub-micron design rule technologies will use such interconnect schemes to enhance the performance of MOS devices through reduced contact resistances and smaller routing delays.

The future of gate electrode technologies may yet lead to other material changes. The refractory metals tungsten and molybdenum are under study as replacements for the polysilicon gate material. Both materials have lower resistivities than polysilicon, have excellent eich properties for patterning sub-micron features, and have appropriate work functions for application to low voltage CMOS processing. Gate electrode processing continues to be an exciting and controversial area of IC process development.

Figure 8. The impact of gate electrode material on interconnect routing delays as a function of design rules. Doped polysilicon (30  $\Omega$ ( $\tau$ ), TaSi<sub>2</sub>/Polysilicon (2.5  $\Omega$ ( $\tau$ ) and Al (0.025  $\Omega$ ( $\tau$ )) with 1  $\mu$ m thick dielectric overlayers on 1  $\mu$ m thick field oxide. (From Sinha et al.<sup>4</sup>).

Figure 9. A TEM cross-section of a  $TaSi_2$ Polysilicon gate structure. Junction staining techniques highlight the heavily doped region of the source/drain. (From T. T. Sheng, unpublished).

# Dopants in Silicon and Silicides

The control of the depth of dopant diffusion in the formation of junctions has been an important aspect in IC processing from its inception. Whether forming emitter/base/collector structures in bipolar transistors or source/drain junctions in MOS transistors, control and reproducibility of dopant diffusion has been an important portion of the technology. The diffusion of dopants from gaseous sources (e.g. PBr<sub>3</sub>, POCl<sub>3</sub>, BBr<sub>3</sub>) in hot walled tube furnaces at high temperatures was satisfactory in the early years

Figure 10. Processing sequence for the formation of a selfaligned silicide.

of IC manufacture. As total dose control became more critical and diffusion depth became more shallow, ion implantation began to replace furnace diffusion in critical stages of device processing. Currently, to set substrate "tub" doping to depths of several microns in the fabrication of CMOS devices, furnace diffusion of dopants is still common. However, the formation of junctions in that tub structure is done by ion implantation. The annealing time-temperature sequence is selected to repair radiation damage and to electrically "activate" the dopant but not to alter the diffused substrate dopant profile.

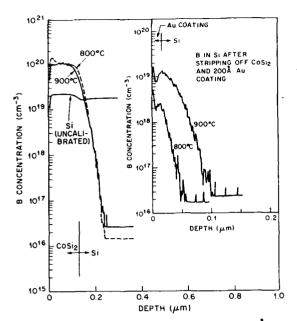

Because scaling to submicron design rules requires the scaling of junction depths as well as the incorporation of silicides into the substrate region, the behavior of dopants in the self-aligned silicide structures is an active area of materials research. The solubility, diffusivity and segregation behavior of dopants in the silicide/silicon systems is poorly understood and critically important to continued device scaling. As an example of the complex interplay between dopants, metalsilicide and silicon, consider the formation of shallow junctions (<100 nm) beneath a self-aligned silicide. As stated, scaling of device geometry requires scaling of junction depths. At submicron design rules, the junction depths required become less than 0.25 µm, and if siliciding of the source/drain area is employed, the silicide thickness plus the junction depth must fall within this maximum depth. The formation sequence of such shallow junctions is further complicated by the segregation behavior of dopants during the silicide formation process. Schemes have been proposed that implant dopant into silicon before silicidation, into or through metal prior to silicidation, into or through intermediate silicides, and into or through the final disilicide. Obviously, these options include a large number of experimental parameters and the problem is made more complex by the lack of fundamental diffusion, solubility and segregation data. One successful method that produces shallow junctions beneath CoSi2 is to implant dopant into the disilicide.<sup>(6)</sup> The implant energy is selected to contain

Figure 11. SIMS profile of boron beneath 1000 Å  $CoSi_2$ . After chemical strip of the  $CoSi_2$  (insert) the interface concentration and junction depth can be determined as a function of anneal temperature. (From Liu et al.<sup>6</sup>).

the implantation damage within the silicide and the dose is selected to exceed the solubility limit of dopants in the silicide. The subsequent anneal can be chosen at a temperature that diffuses dopant into the underlying silicon, but not at the higher temperature necessary to anneal radiation damage. Figure 11 is a Secondary Ion Mass Spectrometry (SIMS) profile of boron difluoride implanted into  $CoSi_2$  in the described fashion. The inserted SIMS profiles following wet chemical removal of the  $CoSi_2$  show accurate junction depths and estimates of interface concentrations. Note that the junction depth is 50-100 nm beneath the silicide/silicon interface. Such junction formation techniques will satisfy scaling requirements well into the next decade.

As a second example of new challenges in dopant-silicide interactions, Fig. 12 shows the threshold voltage behavior of a p-channel device that is electrically connected to an n-doped region by a TaSi<sub>2</sub>Si gate electrode.<sup>(7)</sup> This is a structure common to CMOS IC's and represents a "worst-case" geometry with respect to relative area. The dependent variable plotted in Fig. 12 is the threshold voltage of the p-channel transistor positioned from the n-doped region by a distance measured in microns. Note that the control in this experiment is a p-channel transistor completely separated with respect to the n-doped region (distance ...). Figure 12 shows that for 900°C-30 min anneals, the threshold voltage of the p-channel MOSFET shows the influence of the diffusion of n-type dopant up to a distance of 20 microns. This effect on the threshold voltage, which is shifted to more n-type polysilicon behavior, is the combined effect of the segregation of boron dopant from the p-channel polysilicon gate to the silicide, as well as the high rate of lateral diffusion of n-type dopant in the silicide. Estimates of the dopant diffusivity in silicides suggest several orders of magnitude higher values than in polysilicon but no quantitative studies have been undertaken.

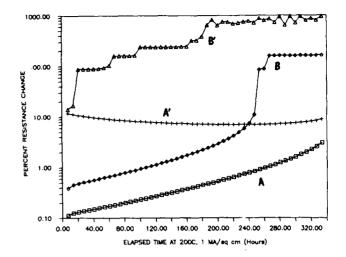

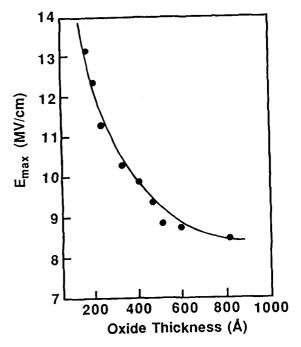

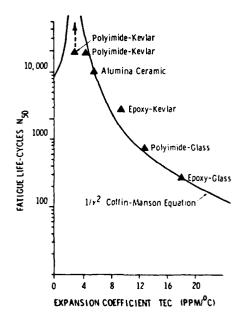

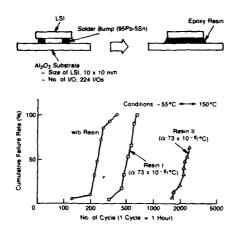

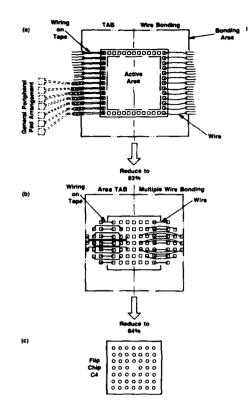

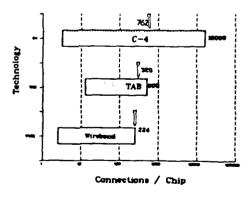

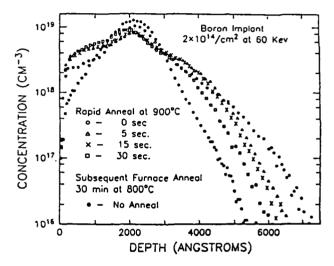

Figure 12. Threshold voltage shifts of a p-channel device resulting from lateral diffusion of arsenic through the  $TaSi_2$  and from segregation of boron to the  $TaSi_2$ . (From S. J. Hillenius et al.<sup>7</sup>).