|       |        | ESP<br>N62 | IRT TE<br>269-8 | ECHNOL<br>5-C-07: | DGY IN<br>L6 | C WALN     | UT CRE | EK CA | PFL     | ANNER | ER(U)<br>AUG 86 | ,        |              |

|-------|--------|------------|-----------------|-------------------|--------------|------------|--------|-------|---------|-------|-----------------|----------|--------------|

| UNCLA | SSIFIE | D          |                 |                   |              |            |        |       |         | F/G 2 | 20/11           | <u> </u> |              |

|       |        |            |                 |                   |              |            |        |       |         |       |                 |          |              |

|       |        |            |                 |                   |              |            |        |       |         |       |                 |          |              |

|       |        |            |                 |                   |              |            |        |       |         |       |                 |          |              |

|       |        |            |                 |                   |              |            |        |       |         |       |                 |          |              |

|       |        |            |                 |                   |              |            |        |       |         |       |                 |          |              |

|       |        |            |                 |                   |              |            |        |       |         |       |                 |          |              |

|       |        |            |                 |                   | 3            |            |        |       |         |       |                 |          | F            |

|       |        |            |                 |                   |              |            |        |       | i Oline |       |                 |          |              |

| -     |        |            |                 |                   |              |            |        |       |         |       |                 |          | _            |

|       |        |            |                 |                   |              |            |        |       |         |       |                 |          |              |

|       |        |            |                 |                   |              |            |        |       |         |       |                 |          |              |

|       |        |            |                 |                   |              |            |        | •     |         |       |                 |          |              |

|       |        |            |                 |                   |              |            |        |       |         |       |                 |          |              |

|       |        | 0          |                 |                   |              | к л<br>1 р |        |       | 111     |       |                 |          | - <b>-</b> 6 |

|       |        |            |                 |                   | 1            |            |        |       |         | Ľ.    |                 | ł        |              |

and a second and a second s

MICROCOPY RESOLUTION TEST CHART NATIONAL BUREAU OF STANDARDS 1963-A

FINAL REPORT

CONTRACT PARAMAN ACCOUNT

SAMANAN DAVARAG

2

E)

"Small, Self-Contained Aircraft Fatigue Data Recorder"

Contract No.: N62269-85-C-0716

10/85 - 08/86

This document has been approved for public release and sale; its distribution is unlimited.

## **DISCLAIMER NOTICE**

THIS DOCUMENT IS BEST QUALITY PRACTICABLE. THE COPY FURNISHED TO DTIC CONTAINED A SIGNIFICANT NUMBER OF PAGES WHICH DO NOT REPRODUCE LEGIBLY.

## DEFENSE SMALL BUSINESS INNOVATION RESEARCH (SBIR) PROGRAM FINAL REPORT

## Title: Aircraft Fatigue Recorder

Phase I Effort – FY 1985 SBIR, Topic #127

Sponsor: Naval Air Development Center, Warminster, PA

Contract No: N62269-85-C-0716

Contractor: **ESPRIT Technology Inc.** 144-A Mayhew Way Walnut Creek, CA 94596

Ancipal Investigator: Philip Flanner, Engineering Manager

August, 1986

## DEFENSE SMALL BUSINESS INNOVATION RESEARCH (SBIR) PROGRAM FINAL REPORT

Title:Aircraft Fatigue Recorder<br/>Phase I Effort – FY 1985 SBIR, Topic #127Sponsor:Naval Air Development Center, Warminster, PAContract No:N62269-85-C-0716

Contractor: **ESPRIT Technology Inc.** 144-A Mayhew Way Walnut Creek, CA 94596

Principal Investigator: Philip Flanner, Engineering Manager

**Summary** – Because of aging airframes and more severe mission requirements, the need to monitor structural fatigue damage on military aircraft has become critical. It is particularly important to be able to study the dynamic loads in remote locations such as the vertical tail, wing spar, landing gear, etc. However, there is presently no small, battery-operated data recorder available to investigate fatigue characteristics at these localized stress "hot spots." Having available a miniature data-logger that could be easily attached to any desired location on an aircraft will enable engineers to quickly examine, and correct, the cause of fatigue cracks and similar structural problems.

The purpose of this program was to investigate the feasibility of utilizing the latest technology in low-power circuitry, transducers and packaging to produce a small, rugged, self-contained fatigue recorder, requiring no tie-in to aircraft wiring for installation.

The project stages included: feasibility study, design evaluation, submittal of an interim report, and culminated in the design layout and construction of a brassboard demonstration unit. This feasibility demonstrator is a single channel device connected to an internal accelerometer and includes a means for automatically activating the micro-processor circuitry by sensing the vibration associated with the start-up and operation of the aircraft's engines. Size of the ultimate unit is targeted at 8 cubic inches, and the demonstrator is approximately three times this volume because of using discrete devices rather than hybrids or SMD's

The design objectives, as achieved on the brassboard unit, and as projected for the Phase II design, may be summarized as follows:

| OBJECTIVE               | BRASSBOARD<br>PERFORMANCE | FINAL UNIT |

|-------------------------|---------------------------|------------|

| Size                    | 22 cu. in.                | 8 cu. in.  |

| No. of channels         | one                       | two        |

| Bandwidth               | 16 Hz                     | 50 Hz      |

| Duration of self-power  | 5 days (est.)             | 30 days    |

| Auto. turn-on circuit   | demonstrated              | achievable |

| programmable range      | demonstrated              | achievable |

| programmableoffset      | demonstrated              | achievable |

| programmable bandwidth  | demonstrated              | achievable |

| programmable Algorithms | demonstrated (one)        | achievable |

| Real-time clock         | not included              | achievable |

|                         |                           |            |

It is concluded that the success of this feasibility study justifies a follow-on effort to develop a final design featuring hybrid or SMD packaging, and the delivery of 3 units for lab evaluation and flight test by the Navy.

A miniature, easily-installed, battery-operated structural recorder will also be extremely valuable for use on commercial aircraft, buildings, bridges, earthquake monitors and oil platforms.

### TABLE OF CONTENTS

- 1.0 Introduction

- 2.0 System Description

- 3.0 Specification

- 4.0 Packaging

R

- 5.0 Circuits

- 6.0 Components

- 7.0 Transducers

- 8.0 Power

- 9.0 Data Channels

- 10.0 Data System

- 11.0 System Accuracy

- 12.0 Cost Estimate

- 13.0 Conclusion

Appendix A: Interim Report Small-Self-Contained Aircraft Fatigue Data Recorder

#### 1.0 INTRODUCTION

#### 1.1 Identification and Significance of Phase I Effort

There is a steadily increasing need to monitor and record the fatigue life consumption of aircraft structural members. With the adoption of Service Life Extension Programs to extend the life of older airframes and with changes in mission and loading from the original design criteria, aircraft are being subjected to fatigue environments far greater than were originally planned. Additionally, for newer aircraft, the advent of special-purpose alloys, the incorporation of sophisticated but stressful automatic flight control systems, and the narrowing of structural design margins, all serve to heighten concerns over the accumulation of fatigue damage.

Accordingly, there is a requirement for a fatigue data recorder readily installed on various structural locations in military aircraft to measure and store data on the number of times that various flight dynamic loads have been exceeded. In the past these measurements were accomplished either by a specially-instrumented test aircraft using a large on-board tape recorder, or by the existing Counting Accelerometer system installed at the C.G. and totalizing four levels of vertical acceleration data. In the former case, the instrumentation task is bulky, expensive and time consuming; and in the latter case, the data is very limited in scope and has no flexibility as regards location on the aircraft.

Technology now exists for the mechanization of microprocessor based data recorders featuring solid-state memory and electronic data retrieval.

The results of the Phase I effort have confirmed that a fatigue data recorder can be developed which is small, self-contained, easily installed, self-powered to store up to one month of flight data, and designed for mounting in a variety of critical locations on an aircraft.

The basic concept behind the device demonstrated in Phase I is to solve structural problems and these problems could be anywhere on the aircraft -wing, empennage, tail, landing gear, etc. The resultant production instrument will be able to be readily attached to any structural member, either internally or on the skin, and flown operationally for up to one month to assess the type of loads that the structural member normally The recorder would then be removed and the accumulated experiences. fatigue data read-out on a simple desk-top computer. The entire procedure will feature simplicity, ease of installation, and versatility of investigative parameters. It will be a major advancement to help structural engineers solve critical fatigue problems, not only on military aircraft, but on commercial airlines, buildings, bridges, and all safety-conscious structures.

#### 1.2 Technical Objectives - Phase I

The ultimate goal of this three-phase program is the production of a small  $(1" \times 2" \times 4" \text{ typical})$  self-powered data recording system comprising transducers and electronics to monitor physical parameters (acceleration, strain, pressure, temperature) of interest to fatigue monitoring programs. The recorder combines transducers, CMOS circuitry and software for low power operation. The measurement ranges, data compression schemes, and data variation exclusion levels will be under software control and can be set by the user. The data will be recorded in solid state memory and retrieved by removing the recorder from the aircraft and mating it with a data Transcriber, thereby transferring the data from the recorder to a suitable medium (e.g. disk) in the Transcriber. The Transcriber will also be used to reprogram the Recorder and could be used for preliminary data reduction.

The feasibility study of Phase I was an investigation of the application of existing technology to a miniaturized data recording system. In particular we have investigated development of a minimum battery-drain device through such techniques as strobed power-control, as well as an automatic power-up and power-down circuit based on sensing of the vibration associated with the aircraft engine's operations. We also sought to achieve maximum user flexibility by investigating low power usage algorithms for internal data compression and processing, as well as the feasibility of configuring the unit with different bandwidths, to be able to handle low frequency-low bandwidth parameters such as Nz, as well as higher (50Hz) bandwidths to monitor buffet loads.

Additionally, we have endeavored to provide installation flexibility by configuring the recorder for use with a variety of external signals such as temperature sensors, pressure transducers, cat/arrest sensors, etc.

The Phase I effort, in providing a conceptual design, design performance analysis and brassboard model represents the normal first step in a phased engineering development program. Phase I sets the stage for moving into a Phase II engineering development program intended to result in a finished, documented, tested recording system.

The technical objectives of Phase I were:

- 1) To determine the feasibility of melding transducers, electronics and software in a compact device which will accurately measure and internally classify the parameters of interest while:

- a) Achieving very low power operation; and

- b) Packaging the resultant configuration in a small volume.

- 2) To provide a hardware design concept and design performance analysis for the projected recording system.

The major question to be answered was: Can a power control methodology based on an interplay between transducers, low-power circuitry and smart algorithms be devised and packed in a small volume?

#### 2.0 SYSTEM DESCRIPTION

The system provided under the SBIR contract is a version of Esprit's ELAPS I battery-operated flight data recorder which had been developed for a variety of remote monitoring uses. For their application the Navy has adopted the nickname "Slap-Track" unit, to reflect its easy installation and ability to track the fatigue loads on a particular structure.

#### 2.1 The Slap-Track System

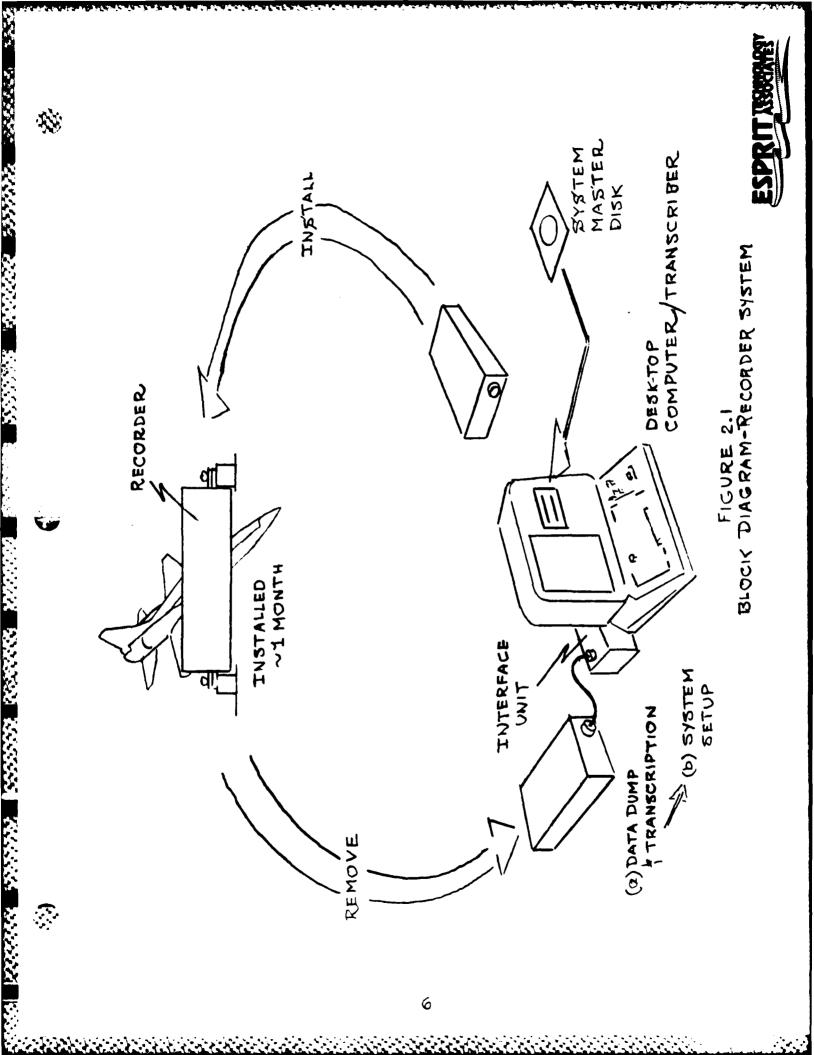

The Slap-Track system has two major components: the airborne system and the ground support system, each of which can be considered to be made up of two or more subcomponents.

The airborne system includes the recorder and the transducer set. The recorder is completely self-contained and self-powered; it includes a power source, a microcomputer, program memory, data memory, a digitizer, analog signal conditioners, a power control transducer and associated circuitry and at least one optional accelerometer. The transducer set includes any strain-based transducer of reasonable input impedance and bridge-like circuitry. Pressure, acceleration and strain transducers are presumed to be of the greatest interest. Current source temperature sensors or medium to high impedance resistance thermometers could also be handled.

A desktop computer, computer interface and master program disk comprise the ground based system. Virtually any small desktop computer would suffice to handle the recorder programming, data retrieval and data transcription tasks assigned to the computer. An IBM compatible unit appears to offer the greatest flexibility. The computer interface assures that the handshake protocol and logic voltage levels between the computer and the recorder serial interface are compatible. The system master disk contains the algorithm menus and user interactive software.

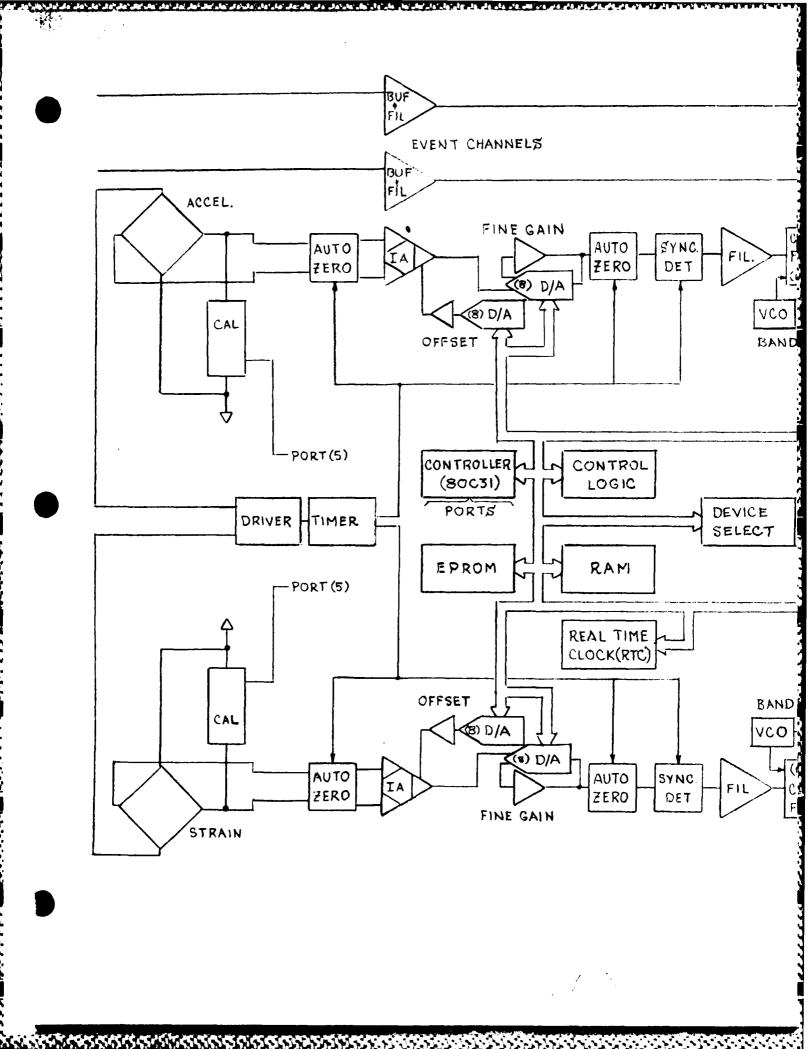

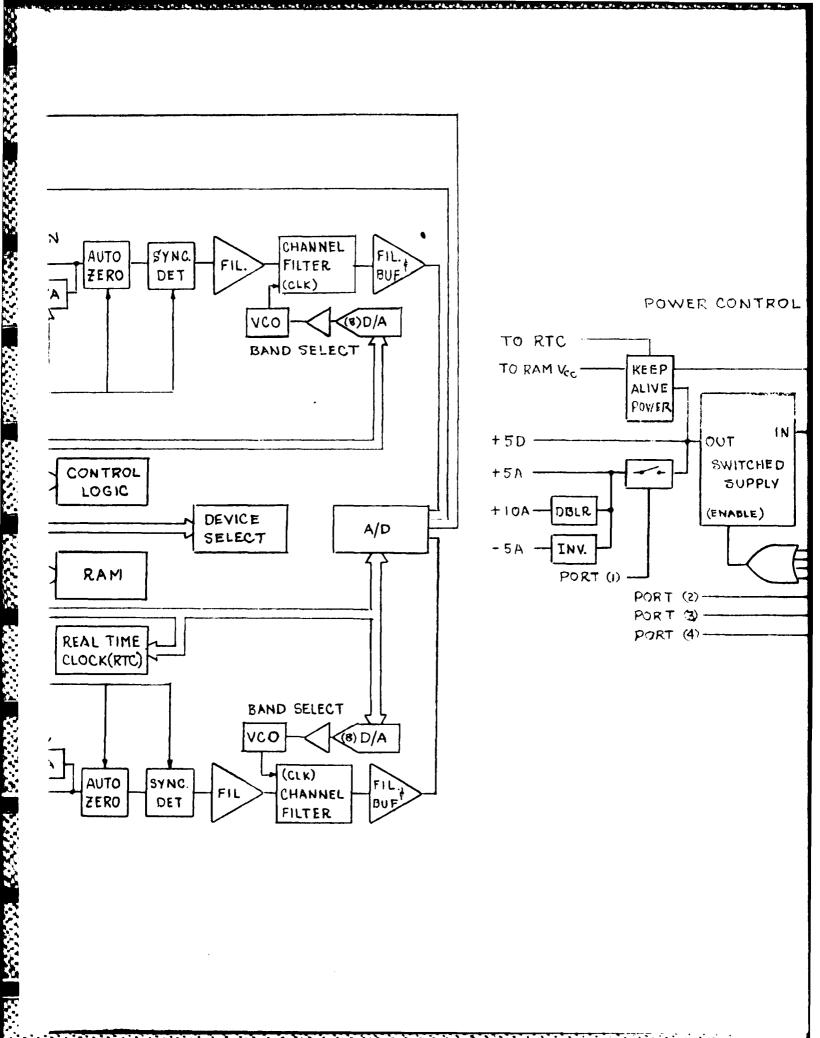

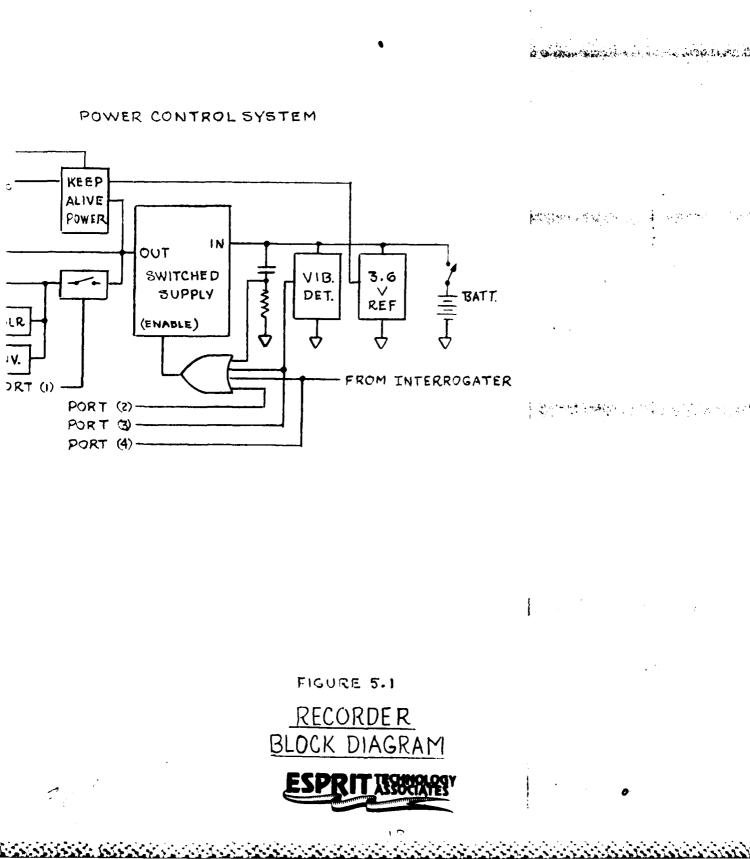

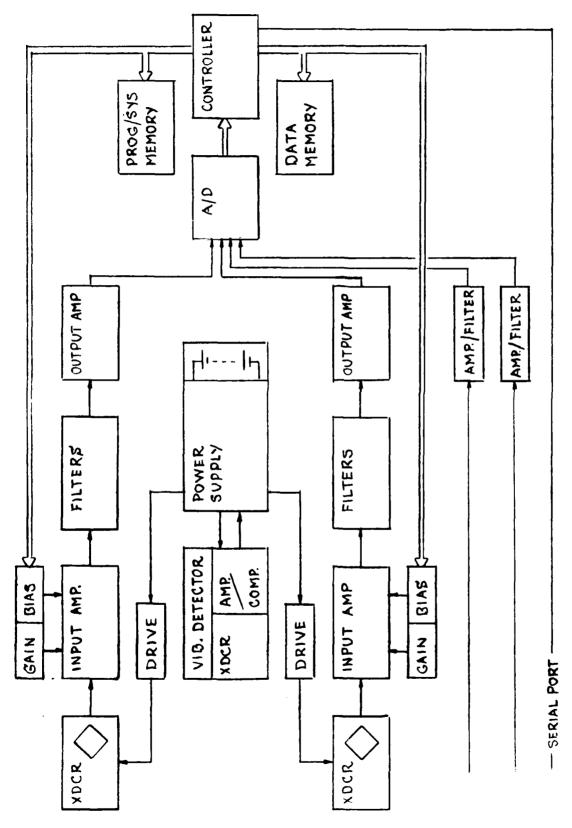

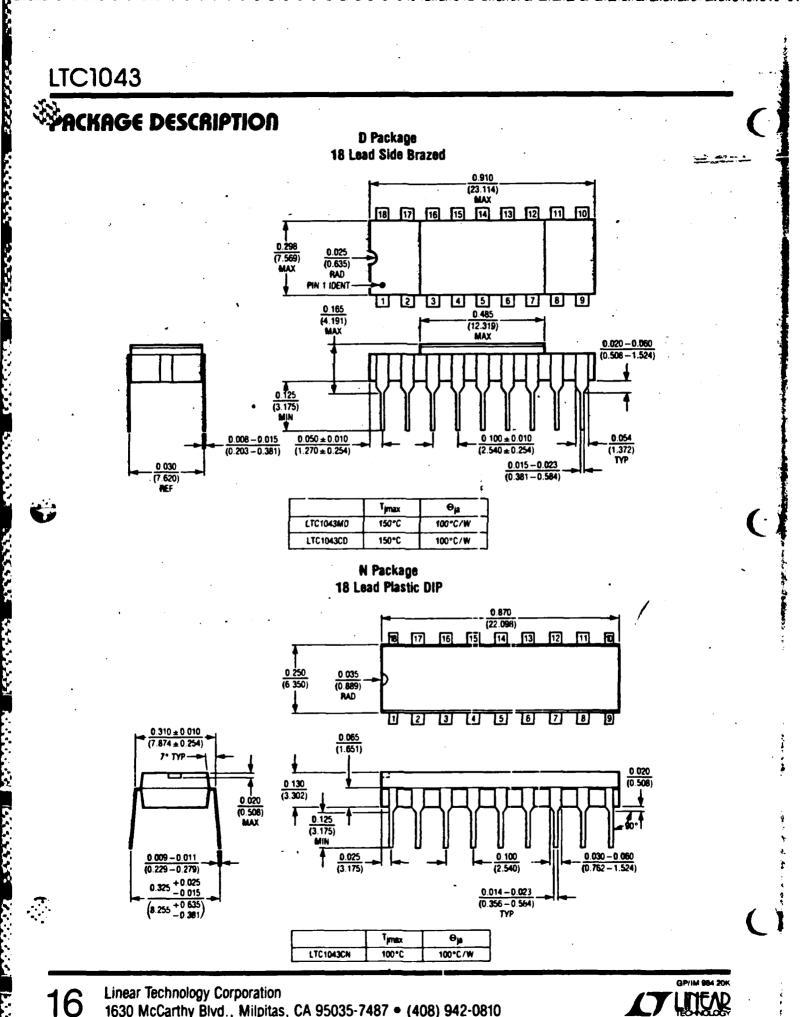

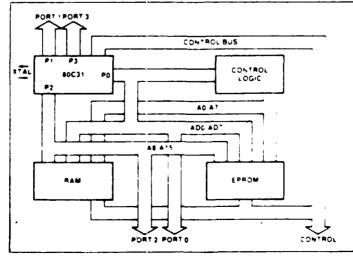

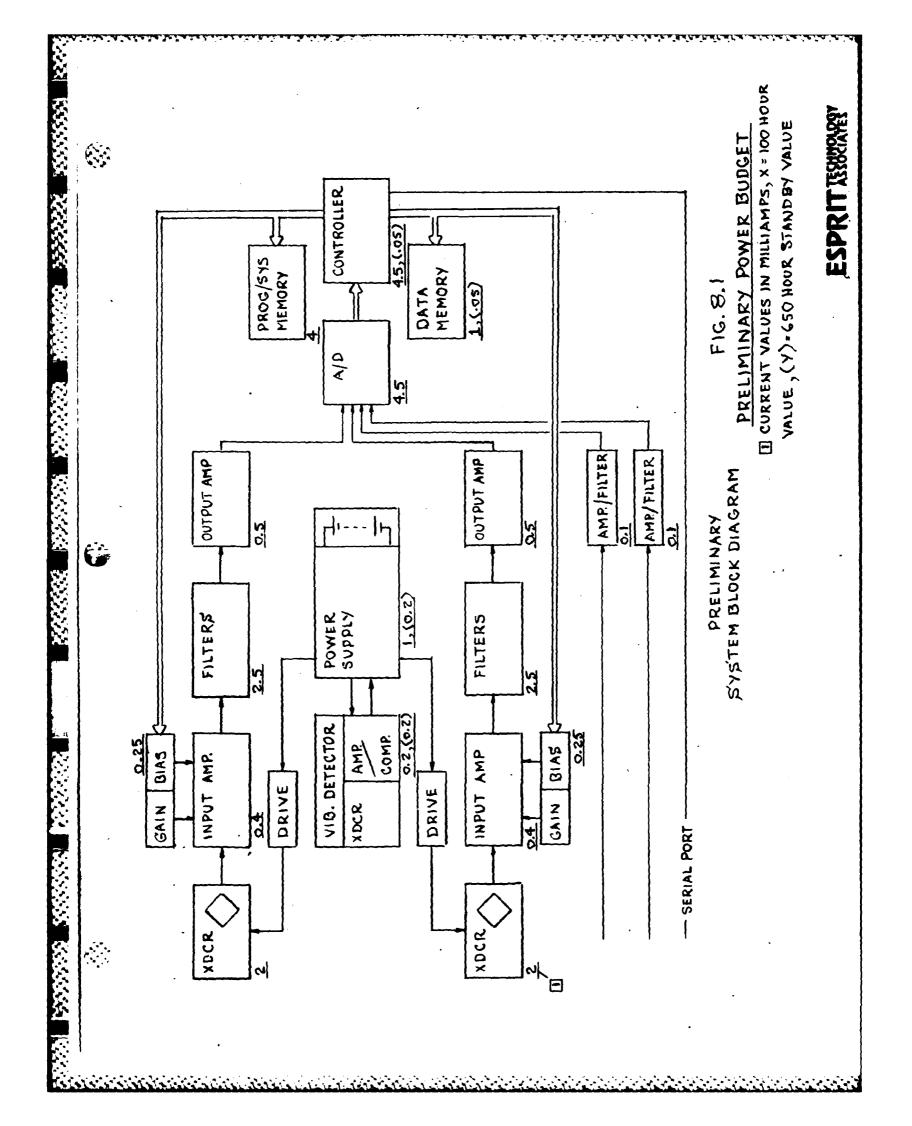

Block diagrams of the Recorder System and the Recorder are given in Figures 2.1 and 5.1 respectively.

#### 2.2 The Recorder

The Recorder is a battery powered, four channel data monitoring, compression and storage system. Three major subsystems make up the Recorder, namely the power supply, analog signal conditioning and digital sections. (See Figure 5.1, the Recorder Block Diagram.)

The power supply includes a set of lithium batteries, a step down switch mode power supply, a transducer, a rectifier/comparator circuit and transducer drive circuitry. The switch mode supply derives the nominal 5 volt operating power from a 7 to 11 volt battery supply and provides for use of battery chemistries to match the expected temperature range. The transducer and rectifier/comparator act to conserve the system power by

6

.....

keeping the system in a low power mode when valid data signals are not present. A self-generating velocity transducer will be built into the system. (Other types of transducers could provide this function.) The data transducers are driven by switched, low duty cycle sources to reduce their power consumption.

The analog signal conditioning section includes two main and two auxiliary data channels. The main channels have high impedance inputs and feature software controllable gains, offsets and bandwidths. The available bandwidths range from 2.5 to 50 Hz and are set by clocking of the 4th order, low pass, butterworth, switched capacitor filter. The auxiliary channels are included to provide for event monitoring (e.g., catapults and arrests) and simple two wire transducer temperature monitoring).

X

The digital section contains an A/D converter, four D/A converters, a CMOS microcontroller and CMOS memory. The A/D converter is an 8 bit successive approximation converter with a built-in 8 channel multiplexer. The D/A converters are 8 bit, latched multiplying converters, included to provide software control of offset and bandwidth. The microcontroller is the 80C31 Intel 8 bit, low power CMOS device. The memory includes U.V.EPROM containing the operating system and counting algorithms and static RAM for data storage. Each of the two memories has a 64 K bit capacity arranged in 8 kilobyte format. The software includes provisions for adjusting the analog gains, bandwidths and offsets, as well as selection of the counting algorithms. The algorithms include load level, peak valley and rain flow data compression of the physical parameter being monitored.

#### 3.0 DESIGN GOAL SPECIFICATION

- General: The equipment shall be a self-contained, self-powered data recorder capable of monitoring a variety of environmental transducers. The recorder shall perform preliminary data reduction/compression and store the results in non-volatile memory for later retrieval.

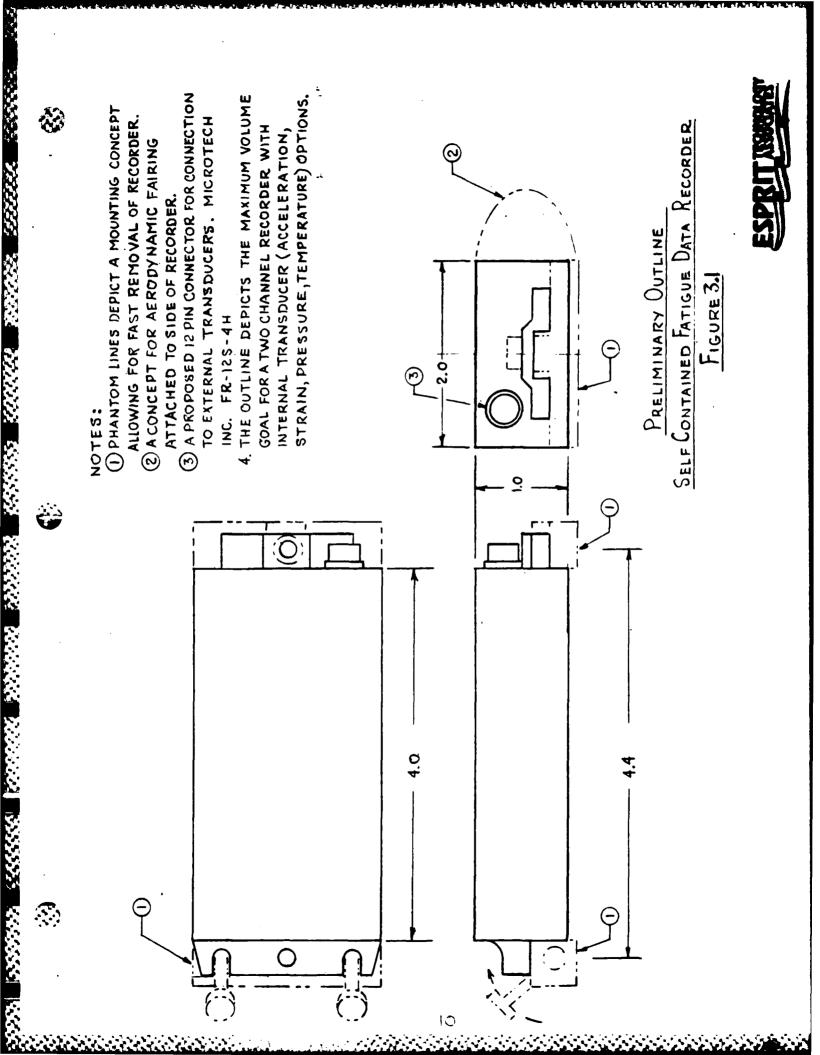

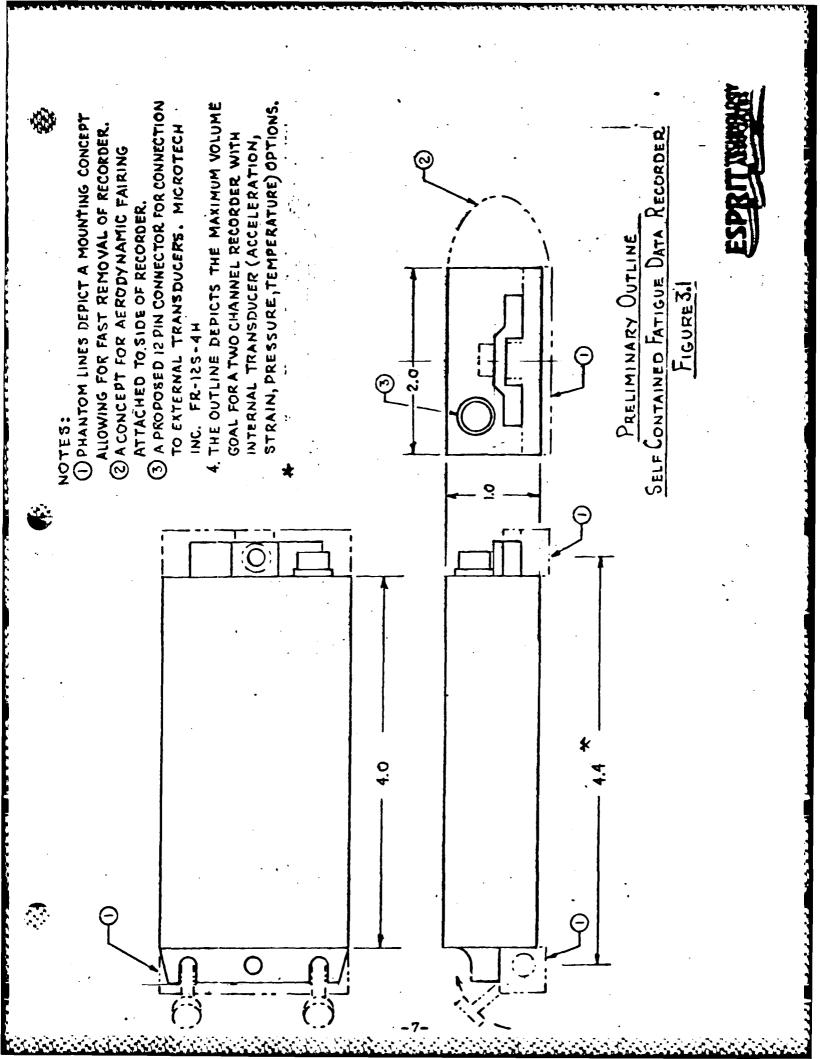

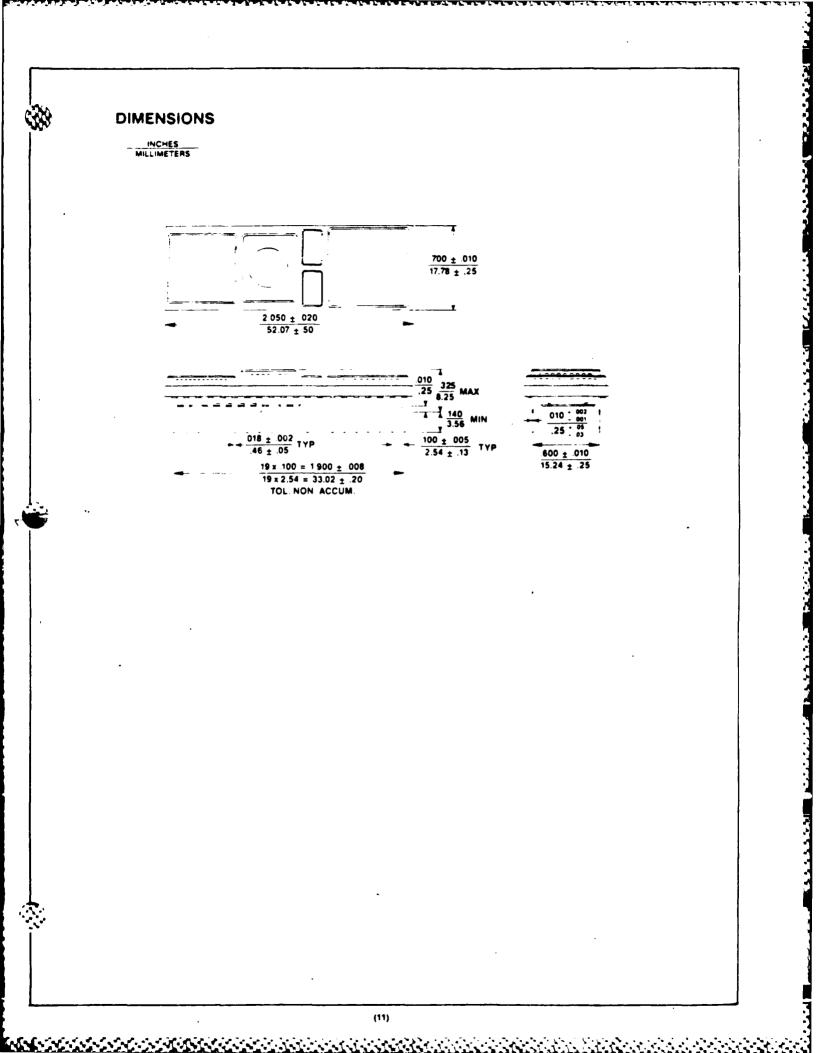

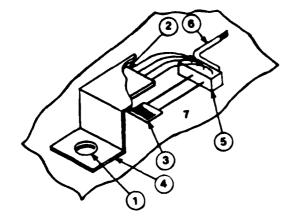

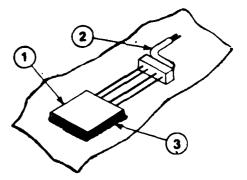

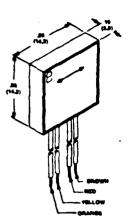

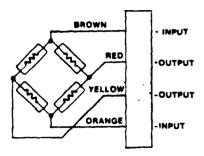

- Size: 1" x 2" x 4" maximum volume (See Figure 3.1).

- Mounting: To mounting pads. Mounting pads bonded or bolted to the aircraft. (See Figure 3.1)

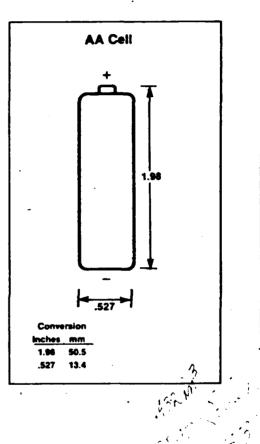

- Power: Supplied by internal batteries. Up to 1 month supply per battery set. Projected - 3AA lithium cells to support up to 100 hours of data gathering and one month or more of untended installation.

- Powera)CMOS static RAM, continuously supported.Control:b)Other circuitry activated and<br/>de-activated by turn-on circuit sensitive<br/>to engine vibrations.

- c) In flight algorithms designed to utilize CMOS processor standby and wait states.

Data Two channels max plus 2 event counts (e.g., Channels: count of catapults and arrests.)

ChannelUp to 50 Hz (one channel system)Bandwidth:Up to 20 Hz (two channel system)2.5 Hz minimum bandwidth

By software.

Bandwidth Control:

Conversion Resolution: 8 bits.

Conversion

Type: Absolute.

Data Choice of: Compression: a) level classification (exceedance count). b) peak valley pairs. c) simple rainflow.

8

Compression Control: By software.

Level classes - up to 32 (over 16 x  $10^{\circ}$ Data a) counts per level). Format: Peak valley pairs - up to 32 x 32 peak-valley matrix (496 cells, up to 2 bytes per cell, 65 x  $10^3$  counts per cell). b) c) Rainflow - up to 32 vector magnitudes and starting values.  $65 \times 10^3$  counts per magnitude. (cell sizes for (b) & (c) can be doubled for data bandwidths above 20 Hz.) Data 2K x 8 CMOS Static RAM Memory: Data Module removed from aircraft and transported **Retrieval:** to Transcriber (commercial microcomputer, e.g., an IBM PC plus associated interface hardware). Data transfer through a serial port and software UART. Transducer Location: Options for internal or external mounting. Transducer Internal - Powered by system. Power: External - Powered by system if low power device capable of pulsed power operation. Supplementary battery pack or ships' power required for high-drain servo type transducers. Operation The mode of operation is controlled by soft-Options: ware. The transcriber is used to program the recorder. The following features are under software control: Channel Bandwidth Channel Ranges Channel Sample Rate Data Compression Method Data Format System Accuracy: 5% max; 3% design goal. To meet the intent of MIL-E-5400T Class Design: 3 equipment.

ENERGY AND ADDRESS ADDR

<u>\_\_\_\_</u>

$\langle \cdot \rangle$

#### 4.0 PACKAGING

The packaging approach is described in paragraph 4.0 of Appendix A (The Interim Report).

Since the report was submitted, further study of the volume requirements has led us to select and propose a mix of surface mount and hybrid modules for use in the final design. The latter has been selected for the analog circuitry to minimize volume.

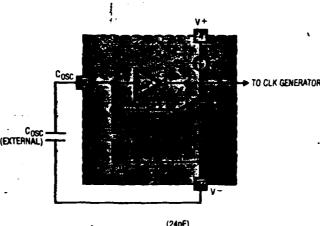

5.0 CIRCUITS (Also see paragraph 5.0 of Appendix A.)

A recorder system block diagram is given in Figure 5.1. The major system components are:

(5.1) Data Source

- (a) Transducer

- (b) Transducer driver/timer

- (5.2) Power Supply

- (a) Batteries

- (b) Power Control

- (i) reset control

- (ii) vibration detector

- (iii) ram and clock save

- (iv) switched supply

- (5.3) Analog Chain

- (a) Input amplifier

- (b) Fine gain

- (c) Auto zero

- (d) Sample & hold

- (e) Filters

- (f) A/D converter

- (5.4) Digital Section

- (a) Controller

- (b) Program memory

- (c) Data memory

#### 5.1 DATA SOURCE

#### (a) <u>Transducers</u>

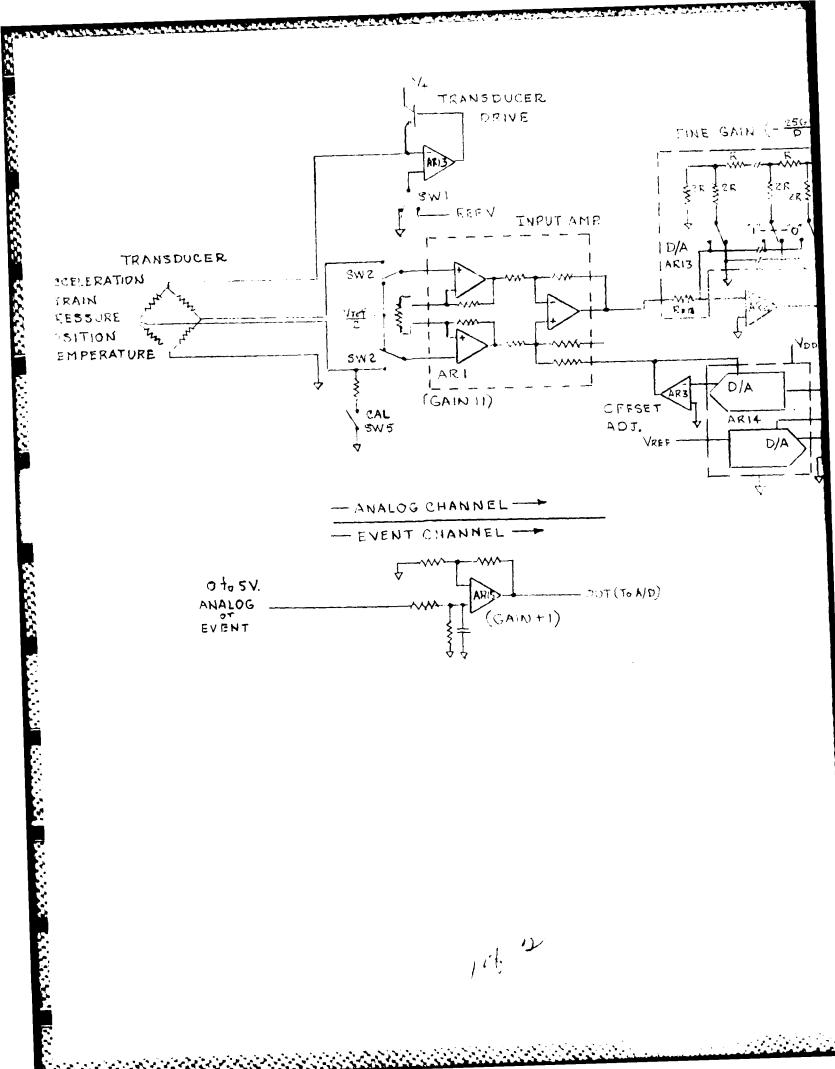

The transducers are discussed in paragraph 7.0 of Appendix A. The analog channels are intended to drive and accept signals from strain based transducers. The channels also can accept and process signals from other types of transducers so long as adequate grounding is maintained between the transducer and the recorder.

いたまたかべ ないないかい

55.4.4.4.5 (D.S.S.S.S.)

1000000 X 2227000

Also included are two event channels that will accept either digital ("O" and "1") or simple analog signals from various transducers such as parameter driven switches (e.g., acceleration) or high level analog devices.

#### (b) <u>Transducer Driver/Timer</u>

ANALY CONTRACT ALLOCAL ANALYS SYNDYN

$\langle \cdot \rangle$

$(\mathbf{x})$

A number of different transducer drive schemes were studied in Phase I. They are described in paragraph 5.0 of Appendix A.

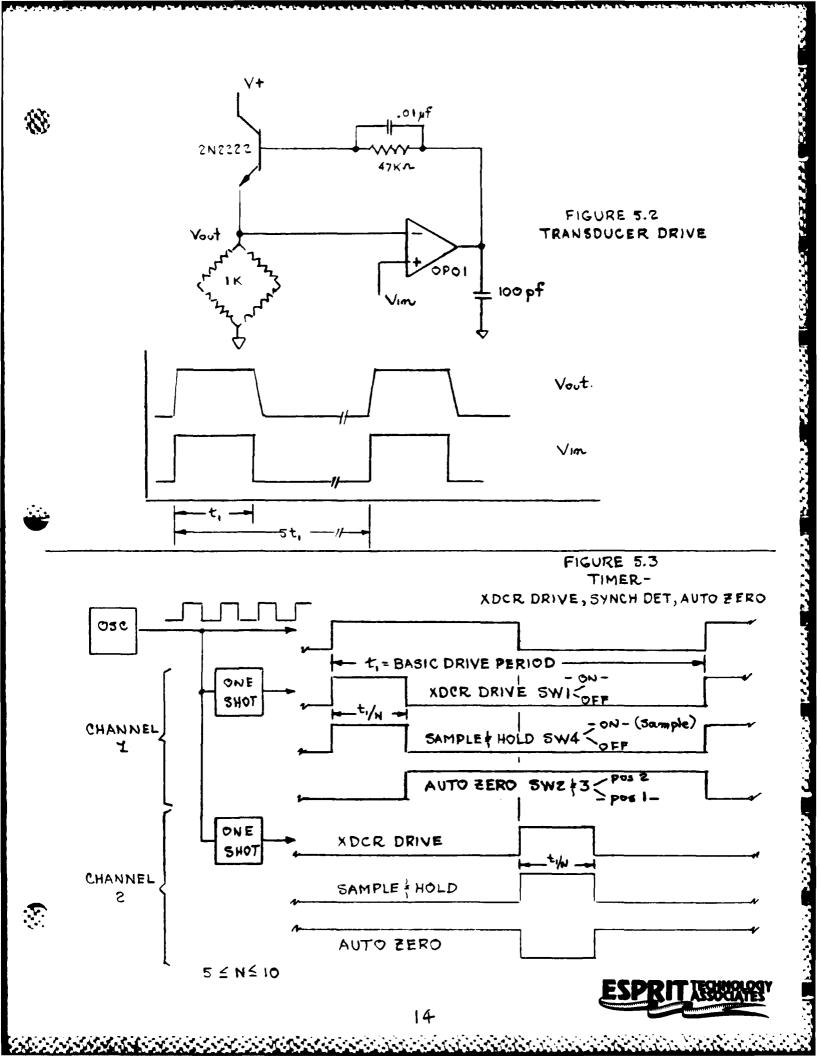

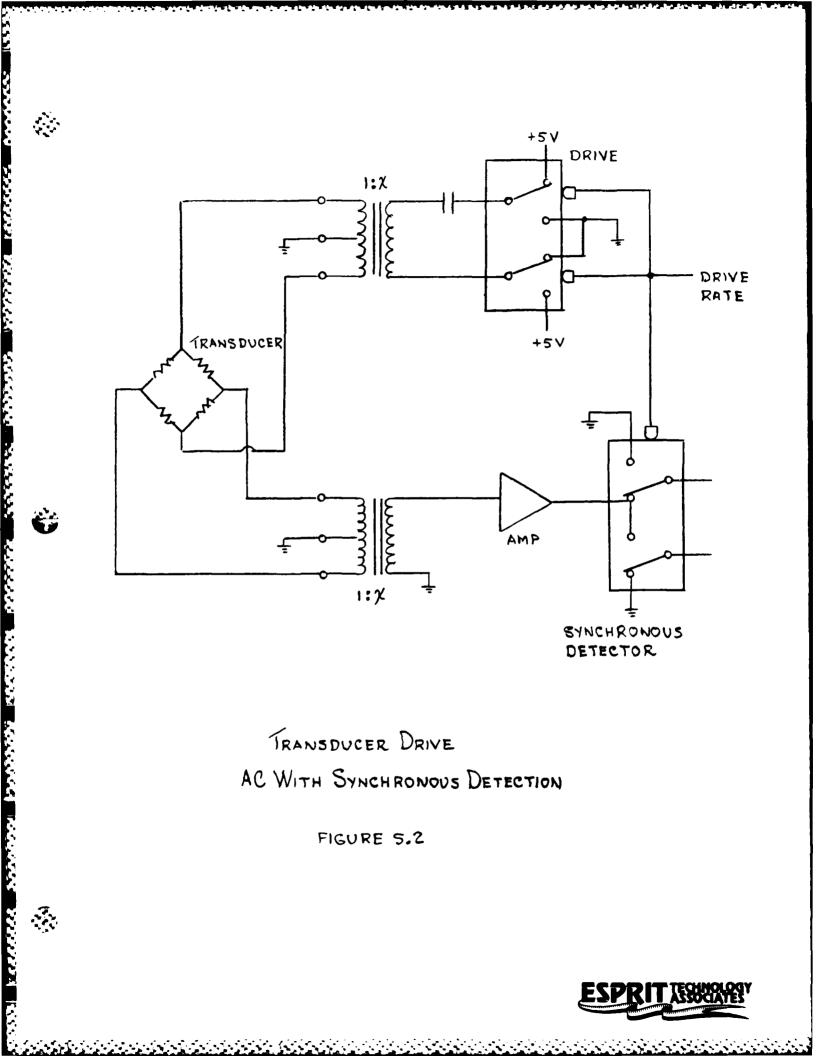

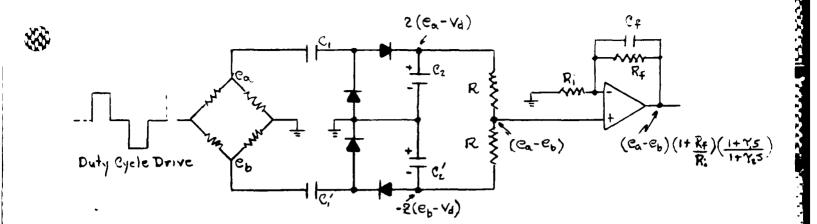

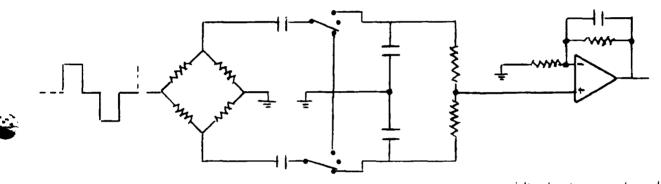

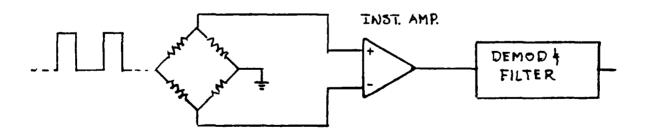

The transducers will be driven by a switched D.C. voltage operating at a 10% to 20% duty cycle in order to minimize transducer power and yet attain as high a level signal as possible from the transducer. A conceptual drive system is shown in Figure 5.5 (Analog Channel Conceptual Schematic). Figure 5.2 shows a simple breadboard circuit and the input/output waveforms obtained in a bench test.

The circuit is intended to drive the transducer with a fixed amplitude voltage pulse. Fixed amplitude voltage drive leading to absolute value conversion in the A/D converter has been selected for two reasons:

- If the recorder is to be easily adapted to monitor a variety of transducers, especially signal sources not powered by the recorder, it is virtually imperative that the recorder be designed for absolute rather than ratiometric voltage measurements.

- 2. Most commercially available temperature compensated strain transducers are designed for voltage rather than current drive.

The transducer driver is controlled by a timer circuit that acts to synchronize the transducer drive, synchronous detection and auto zero functions. A timer scheme is shown in Figure 5.3. The two analog channels are timed on and off by one shot circuits triggered by the basic square wave timer oscillator. Channel one is triggered by the rising edge and channel two by the falling edge of the square wave in order to minimize the current pulses drawn by the transducers. As shown in the diagram, the signal sampling (synchronous detection) is coincident with the transducer drive pulse while the auto zero occurs when the transducer drive is off. In the final configuration, time delays may be introduced between signals to assure both settling of the analog chain before sampling and entry to the hold mode before auto zeroing. In addition, the offset D/A converter may be removed from the circuit during auto zero.

#### 5.2 POWER SUPPLY

AND AND ADDRESS AND ADDRESS ADD

#### (a) <u>Batteries</u>

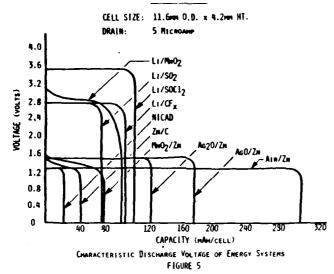

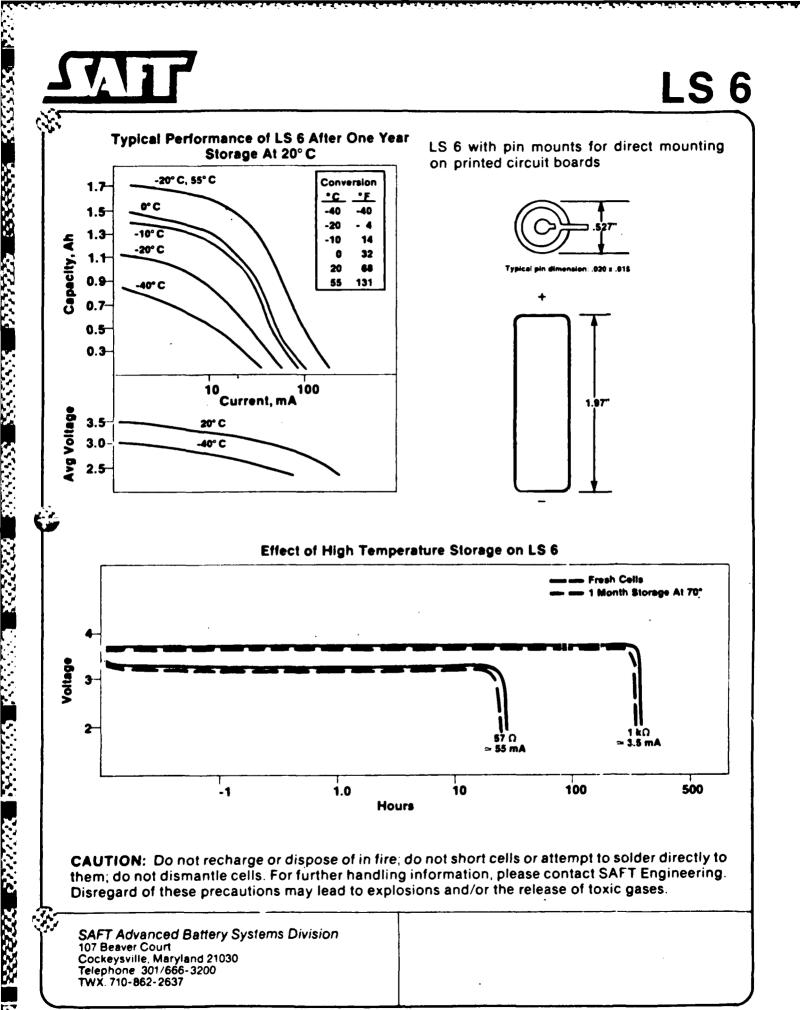

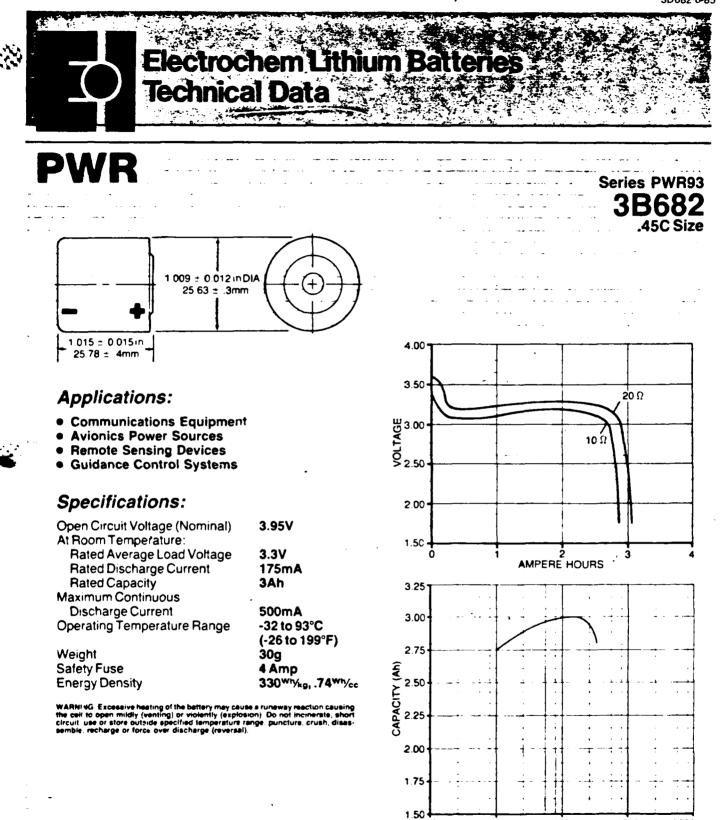

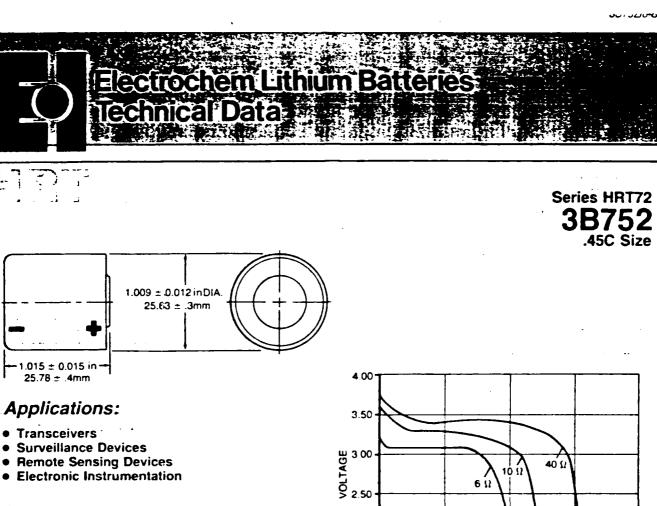

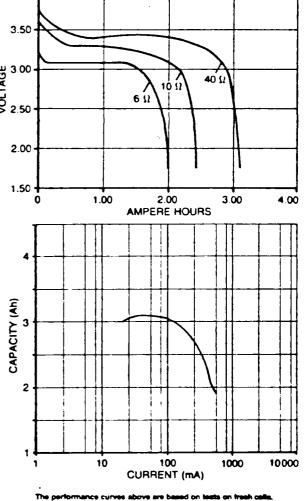

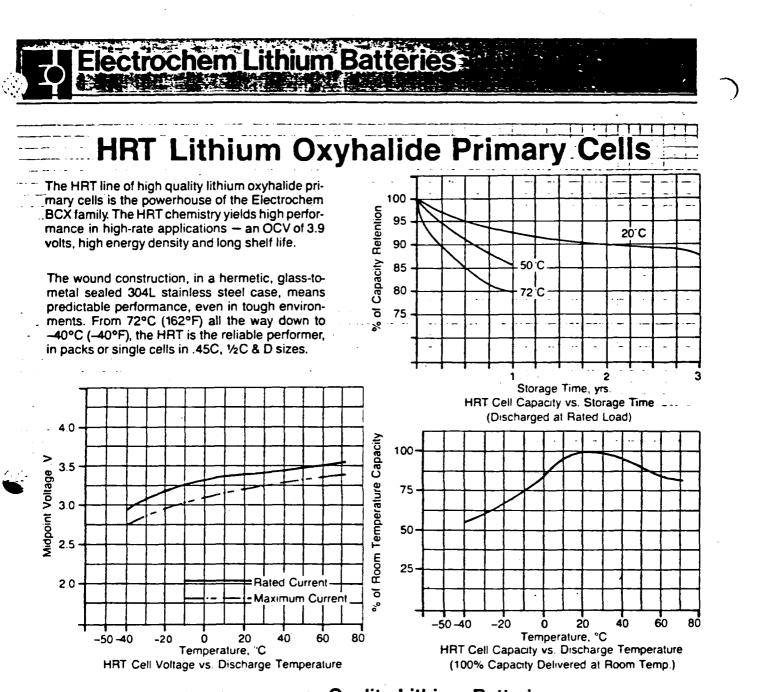

The system is designed to use lithium batteries and presently calls for a series pack of 3 AA size cells. AA size has been chosen to ease procurement as it is a standard size supplied by a number of manufacturers.

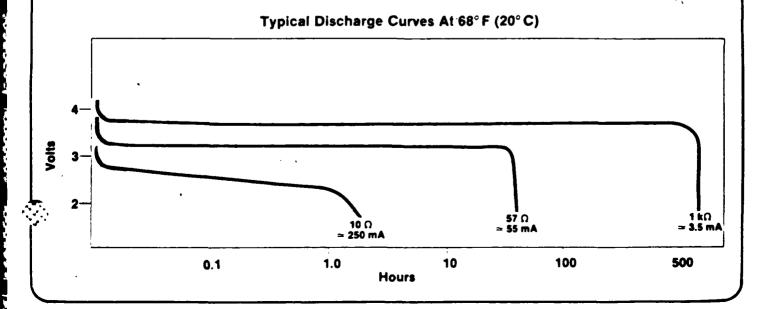

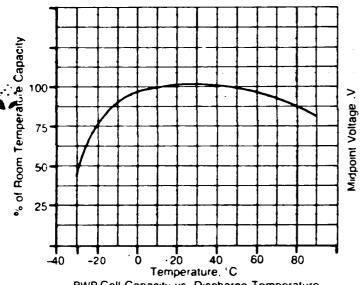

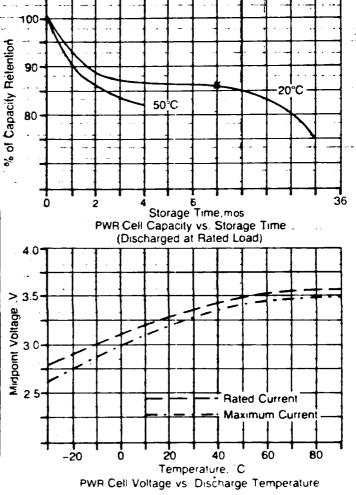

Different battery chemistries will probably be required to cover different temperature ranges of operation. For instance, Lithium Thionyl Chloride can be used over the range -40 C to +71 C (source 1) or -40 C to +125 C (source 2), Lithium Poly-carbon Monofluoride over the range -73 C to +93 C (source 2) and Lithium Copper Oxyphosphate over the range 0 C to +175 C (source 3). In the preceding, "source" refers to various battery suppliers.

We note that a part of the Phase II effort is to study the application safety of these batteries.

Paragraph 8.0 of Appendix A describes the battery selection effort carried out in Phase I and presents various papers and data items pertaining to the batteries.

#### (b) <u>Power Control</u>

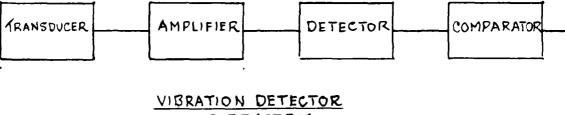

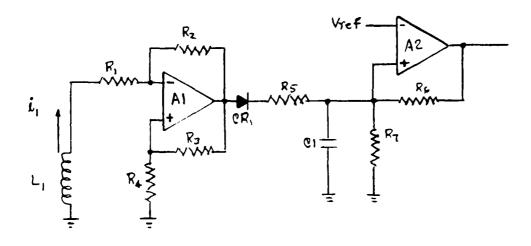

The power control system is shown on the block diagram of Figure 5.1. Included in the power control system is a vibration detector, an initial battery on detector (RC circuit), an OR gate power enable driver, a reference supply to keep the data RAM and RTC (real time clock) alive, and a switched-buck converter followed by inverters and doublers required to supply the system voltages.

The power control system keeps the recorder in a low power mode until the buck converter is enabled by any of three events, namely: (1) battery switched on, (2) interrogator plugged in, or (3) vibration is detected. This subsystem is best described by relating the sequence of events as the recorder is set up and used.

Assume the operator has completed the initial recorder set up with the transcriber; i.e., the counting algorithm, bandwidth and initial gains and offsets have been programmed in. After completing the programming, the operator leaves the battery switch open as the recorder is transported to the installation site. The recorder is then mounted and connected to the previously installed transducer(s). The battery switch is closed. The signal from the RC timer enables the switched supply and, as the +5D power comes on, the processor is reset. The first reset of the processor causes it to initialize and ready itself for the measurement task. During initialization

sal sobrars kozost (skorotk karaba) vrakaci karasart (

the processor holds port 2 high to keep the switched supply on until initialization is complete at which time port 2 goes low, the power goes off, and the system is in a low power mode. The operator then plugs in the interrogator to complete the system check out and trim the gains and offsets to match the installed transducer(s). (Note that the "interrogator" and "transcriber interface" are the same device - see Figure 2.1) When the interrogator is plugged in, the switched supply is enabled and the processor is reset. As the processor comes on, it detects (through port 4) the interrogator presence and goes to that portion of the internal software allowing the operator to make adjustments as required. When the interrogator is removed, the power supply goes off and the system enters the low power mode.

The recorder is now set up, installed, trimmed and ready to perform the data monitoring, compression and storage task. Data monitoring is initiated by a signal from the vibration detector. When the vibration detector senses aircraft vibration, it enables the switched supply through the OR gate. The processor applies power to the analog system by signaling through port 1 and x minutes later starts the monitoring task.

During the data monitoring mode the processor holds the power on through port 2 and watches port 3 for loss of the vibration signal. If the vibration signal disappears, the processor waits y minutes, completes its data storage and shut down steps and goes to the low power mode to wait for the next indication the aircraft is operating.

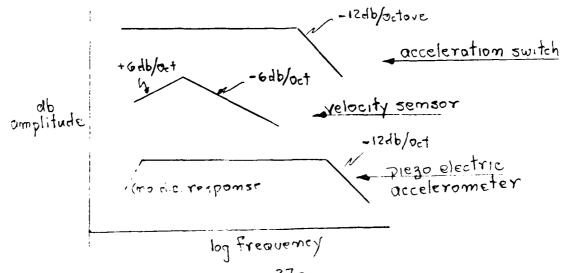

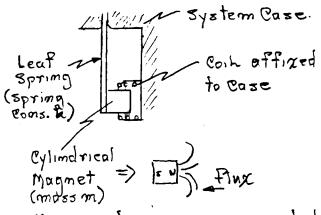

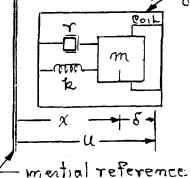

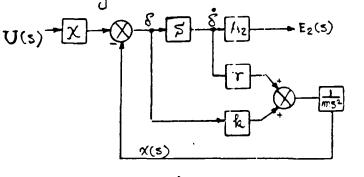

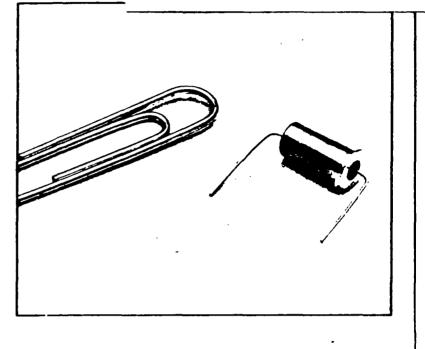

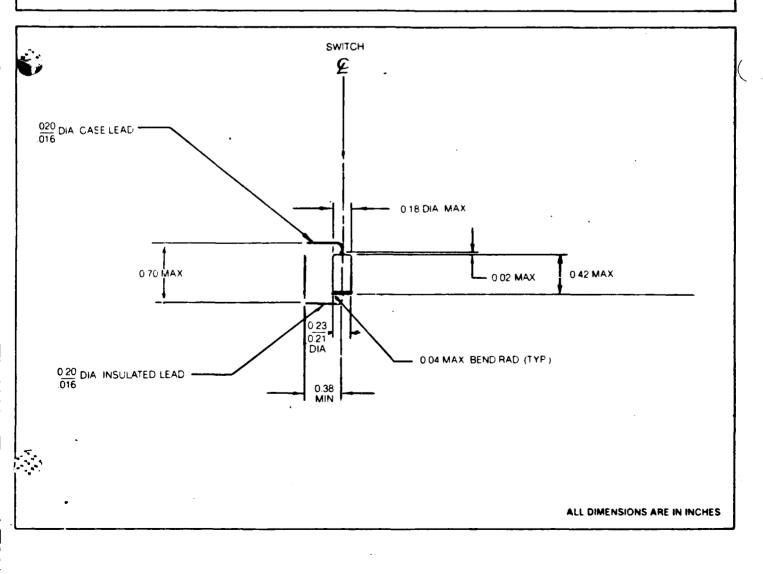

A vibration detection scheme using an acceleration switch was demonstrated in the brassboard system. The results showed that a vibration transducer with no D.C. term; i.e., that gives no output for constant acceleration or velocity inputs, is required. If the transducer does have a D.C. term, its sensitivity is dependent on its orientation in the installation. Phase II thus includes incorporation of vibration transducer(s) with no D.C. term - namely a dynamic velocity sensor. The sensor is described in paragraph 5.0 of Appendix A under the Power Supply heading. We note that the sensor described in that paragraph and in Exhibit 3 to that paragraph does not exhibit stick-slip ("stiction") - it is based on a leafspring supported mass.

The RAM and clock save reference power supply keeps the real time clock and RAM alive when the switched supply is not running; i.e., when the recorder is in the low power mode. This supply is driven directly from the battery and its output is enabled when the 5D voltage from the switched supply goes low. A RAM keep alive supply scheme is shown in Figure 5.4. The circuit applies a 2.2 to 2.4 volt Vcc to the RAM when 5D is turned off. Coincidentally, the RAM CS is pulled high to prevent an inadvertent write to the

| + 50 | DI, DZ         | 91,92 | <u> </u> | Vee         |

|------|----------------|-------|----------|-------------|

| ON   | REVERSE BIASED | ON    | ENABLED  | +5 V.       |

| OFF  | FORWARD BIABED | OFF   | DISABLED | +2.26+2.4 V |

DIODES DI DE PREVENT CURRENT FLOW INTO THE BATTERY WHEN 50 13 ON.

A CS LOW IS PASSED THROUGH Q3 TO THE RAM CS PIN WHEN 5D IS ON \$ CS IS ENABLED.

Q2 ISOLATES THE BATTERY AND RAM FROM THE SYSTEM GROUND. WHEN 5D IS OFF. CARE IS TAKEN TO ASSURE NO HIDDEN PATHS EXIST FROM +5D THROUGH OTHER CHIPS + BACK THROUGH THE RAM SIGNAL LINES.

92

-11-C2 343.

GRD

memory when the 5D power is off. A similar circuit is applicable to the real time clock.

The keep alive system shown in Figure 5.4 requires a separate battery in the keep alive circuit. This feature is worth consideration. A keep alive battery separate from the power supply batteries can offer an increase in the data retention reliability for if, in the middle of an installation/removal cycle, the main battery goes bad, the separate battery will retain the previously collected data. This design feature will be considered in Phase II.

The Phase II effort includes development of the switched supply. The supply will be a switch mode D.C. to D.C. converter developing 5 volts from a 7-11 volt battery input. The goal is to attain a 75% to 80% efficiency in the conversion to give 2.6 to 2.8 ampere hour capacity from the battery/converter system.

The converter will be optimized both for the 10 to 10.5 volt input operating voltage provided by three Thionyl Chloride AA cells and for the system operating current required when driving two transducers and using a peak/valley data compression scheme.

Our preliminary approach is to use one of the CMOS micropower switching regulators as the kernel of the supply. A step down mode has been selected to avoid the approximate 8% loss of power in protection diodes used for parallel battery systems. We note that either the battery safety or the supply efficiency investigation may point the design towards a step up configuration. (batteries in parallel).

#### 5.3 THE ANALOG CHAIN

فكمحمد وكال

The record r has four analog channels; two intended as event channels and two for general analog data handling. The latter two channels feature software control of gain, offset and bandwidth.

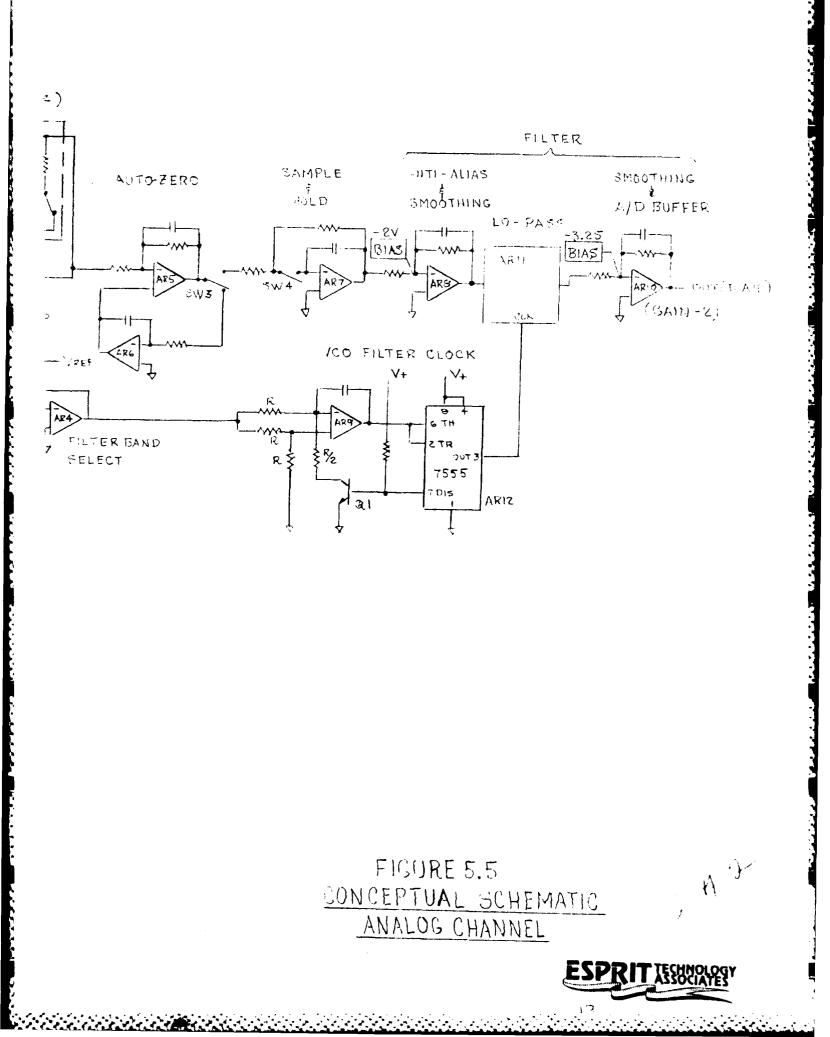

The proposed packaging scheme is to include two identical analog hybrids each of which contains one general analog and one event channel. A conceptual schematic of the circuitry in one hybrid is given in Figure 5.5.

The signal flow in the analog channel is from left to right in the figure - the channel contains the following elements:

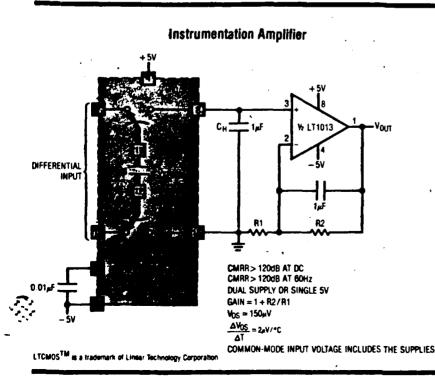

(a) Input Amplifier -- The input amplifier is a standard three op amp instrumentation amplifier with fixed gain. The amplifier presents a high impedance to the source and can accept signals from either differential or single-ended output devices. The high impedence input ensures no degradation of the signal source due

and the second second

to loading by the recorder. A software controlled offset voltage is added to the signal at the amplifier's output stage. The offset can be used for either or both of counteracting transducer bias and shifting the channel range to cover asymmetrical inputs. The offset level is determined by a digital word to the offset D/A converter and its value is: 22222222

Printered

where the digital word ranges from 0 to 255.

(b) Fine Gain -- The fine gain stage provides for software control of the channel gain. The D/A converter (AR13) presents a variable (digitally controlled) feedback to the inverting amplifier AR2. The gain is:

$$G = \frac{-256}{(\text{Digital Word})_{10}}$$

and thus ranges from -256/255 to -256. In use, this gain adjust would normally be restricted to gains of 25 or less to preserve a 10% or finer step adjust of gain. (The percentage change in gain for a  $\Delta D$  of 1 is given by:

$$100 \quad \left| \begin{array}{c} \frac{G}{G} \\ \frac{G}{G} \end{array} \right| = \left| \begin{array}{c} \frac{100}{D} \\ D \end{array} \right| \bigtriangleup D$$

and for 100/D to be 10 or less, D  $\geq$  10 which gives a gain of 25.6 or less).

(c) Auto Zero -- The auto zero acts to zero out the bias drifts associated with the amplifiers and circuits preceding it in the analog chain. The basic auto zero is an inverting amplifier (AR5) with a wash out integrator feedback (AR6). With the switches in the positions shown, no power is applied to the transducer, the differential input signals are shorted together and tied to the transducer common mode voltage, the offset voltage D/A (AR14) is set for zero out, the previous signal is held on the capacitor in the feedback of AR7 and the integrating capacitor in the feedback of AR6 is charging to whatever value is required to drive the output of AR5 to zero. The washout integrator thus sums into AR5 the voltage required to counteract any common mode signal not attenuated by AR1 as well as offset voltages associated with the AR1, AR2, AR3, and AR5 circuits. When the switches are thrown to their other position, the auto zero integrator adds the above voltage to the signal and thus negates the error voltages. The switching functions are synchronized to assure auto

10.00 A

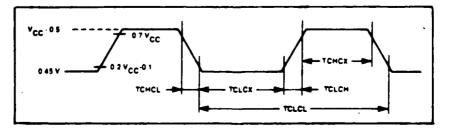

zero, sample and hold and transducer drive are all operating together in the correct temporal relationship. A timing diagram is given in Figure 5.3.

- (d) Sample & Hold -- The sample and hold circuit (AR7) has a dual function; it, (1) is a synchronous detector operating in conjunction with the transducer drive circuit and (2) it "holds" the analog signal during the auto zero. The functions are performed simultaneously as shown in the timing diagram of Figure 5.3.

- (e) Filter -- The filter includes an anti-aliasing and sample and hold output smoothing filter (AR8), a switched capacitor - 4 pole - low pass butterworth filter (AR11), an output smoothing filter and A/D buffer (AR10) and voltage controlled clock for the switched capacitor filter (AR14, AR4, AR9 & AR12).

The corner (-3db point) of the switched capacitor filter is 0.01 times the clocking frequency. This filter is the main channel filter and its corner is controlled by software through the VCO and D/Aconverter. The band selection is intended to extend from 2.5 Hz (250 Hz clock) to 50 Hz (5000 Hz clock).

The switched capacitor filter is a sampled data system and as such requires the signal input to have little or no energy content above 1/2 the sampling rate if aliasing errors are to be avoided. The active filter section AR8 supplies this prefilter function. This filter is shown as a simple low pass in the conceptual schematic. The final design may require a higher order or a degree of tuneability in this filter to reduce aliasing errors - especially if low bandwidth signals are to be abstracted from signals with large high frequency content.

The output of the switched capacitor filter appears as small steps following the input signal (below the filter bandwidth). These steps are "smoothed" out by the output smoothing filter so as to present a clean signal to the A/D converter.

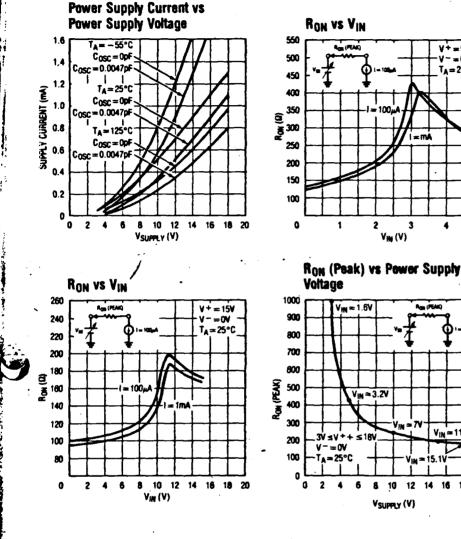

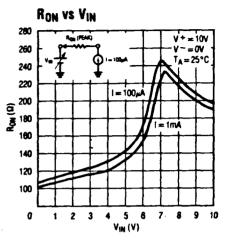

The supply voltages to the switched capacitor filter will be V+ = +5 volts and V- = ground in order to minimize the filter power usage. (11.5 milliwatts versus 35 milliwatts for a  $\pm$  5 volt supply). In addition, the A/D converter will be unipolar; i.e., it wll accept signals in the zero to +5 volt range. The bias networks indicated at AR8 and AR10 shift the signal zero level as needed for operation over the requisite voltage ranges. (f) A/D Converter -- The A/D converter we plan to use is an 8-channel, 8-bit data acquisition device with a built-in multiplexer and sample and hold. It is a low power CMOS device consuming 2.5 milliwatts or less power and yet performing a successive approximation conversion in 25 microsec.

Figure 5.6 outlines an example of the set up and scaling of analog channel for a particular application. The example illustrates how the offset is applied to the output stage of the input amplifier to handle an asymmetric signal source. The calculations performed to select the gain and offset digital word values would be carried out with interactive software menus on the desktop computer in the final system.

#### 5.4 DIGITAL SECTION

$\hat{\mathbf{x}}_{i}$

BARRAR BARRAR BARRAR BARRAR BARRAR BARRAR

2

The digital section is described in 5.0 of Appendix A.

The only change made in the digital section since the interim report was written is the addition of the real time clock.

The EDH687C31 microPak described in Exhibit 6 to paragraph 5 of Appendix A includes the microcontroller, the program memory and the data memory. Phase II includes a task to isolate the data RAM power and ground so the RAM can be kept alive to serve as the nonvolatile data memory. A keep alive circuit scheme is sown in Figure 5.4.

#### 6.0 <u>COMPONENTS</u>

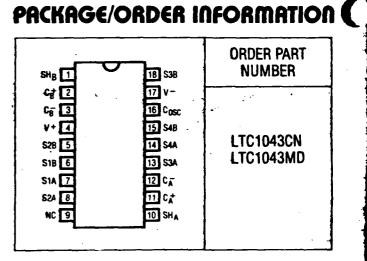

The major digital component, the EDH687C31 microPak, is described in Exhibit 6 to paragraph 5 of Appendix A.

Table 6 gives a listing of components that fit the scheme of the conceptual schematic of Figure 5.5.

The system A/D converter is not shown on the schematic. The converter used in the brassboard unit was the Siliconix 8 channel, 8 bit, CMOS data acquisition system and is currently the converter of choice for the final unit. The converter has a total unadjusted error of  $\pm$  0.75 LSB over the full temperature range. The converter is powered by +5 volts for both Vcc and Vref with a total current draw of 1ma maximum over the full temperature range.

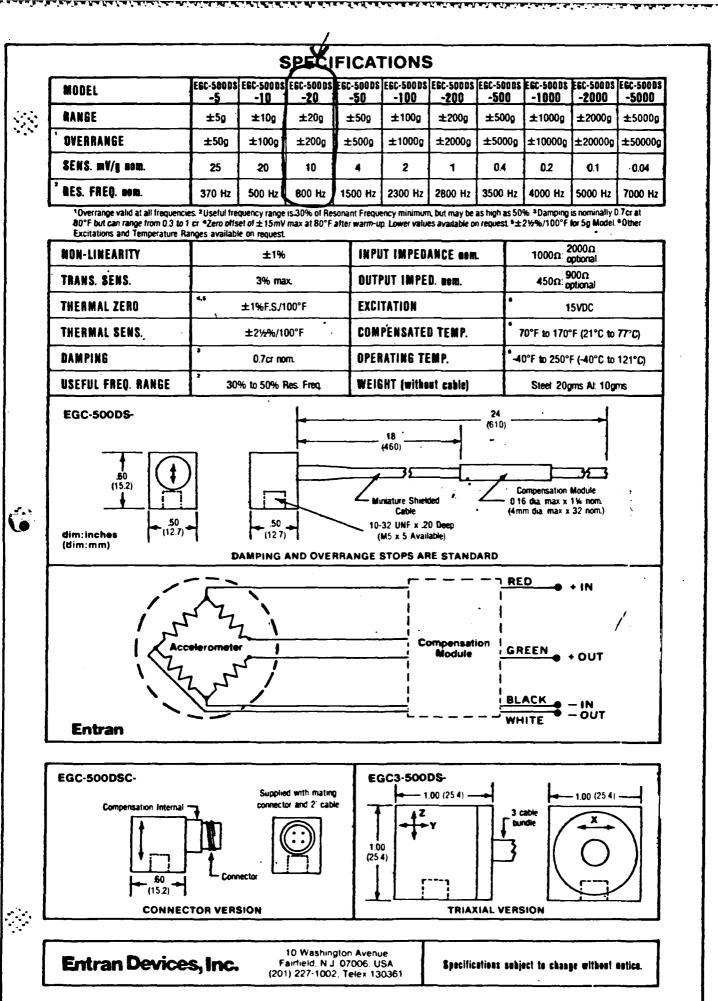

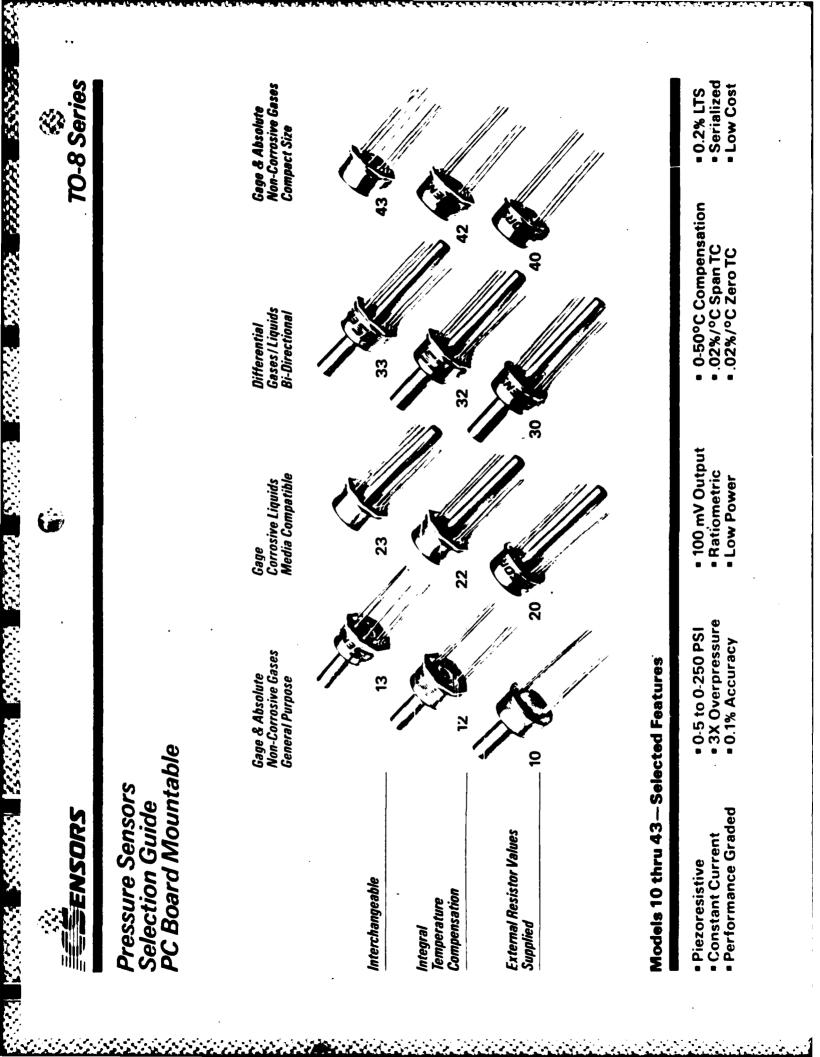

#### 7.0 TRANSDUCERS

The transducers are described in paragraph 7.0 of Appendix A.

| EXPECTED RANGE - Oto 4000                                                     | руе                   |                           |

|-------------------------------------------------------------------------------|-----------------------|---------------------------|

| TRANSDUCER - STRAINBRIN<br>1.025 MV/V/<br>0.5 MV/V OF                         | 1000 46 BENS.         |                           |

| TRANSDUCER EXCITATION -                                                       | 4 VOLT PULSES         |                           |

| TRANSDUCER OUT PUT                                                            | AT O IN<br>.002 Volts | AT 4000 NE<br>.0184 Volts |

| ARI GAIN = 11                                                                 |                       |                           |

| : WITH O OFFSET OUT=<br>WITH D/A REF V. = 2.5 V SET<br>DIO=11 OFFSET=1074Volt | .022                  | +.2024                    |

| : OUTPUT FROM ARI =                                                           | -0.0854               | +.095                     |

| AR2 SET D <sub>10</sub> = 20<br>GAIN = - 256/20 = -12.8                       |                       |                           |

| . OUTPUT FROM ARZ =                                                           | +1.0931               | -1.216                    |

| ARS GAIN = - 1 : OUTPUT =                                                     | -1.0931               | +1.216                    |

| ART GAIN = -1 :. OUTPUT =                                                     | +60931                | - 1.216                   |

| ARB GAIN = -1, ADD -2V BIAS<br>TO SUMMING JUNCTION.                           |                       |                           |

| : OUTPUT FROM AR8 =                                                           | + .9069               | +3.216                    |

| ARII GAIN=1 :OUTPUT=                                                          | +.9069                | + 3.216                   |

| ARIO GAIN = -2, ADD - 3.25V<br>BIAS TO SUMMING JUNCT.                         |                       |                           |

| : OUTPUT FROM ARIO =                                                          | + 4.686               | +0.068                    |

THUS - GIVEN A 5 VOLT REF TO THE A/D CONVERTER THE INPUT SPAN OF 4000 VE RESULTS IN AN OUTPUT BIT SPAN OF

# $\frac{4.686 - .068}{5} \times 256 = 236.4 \text{ Bits}$

GIVING A BENSITIVITY OF

4000 NE 2 16.8 NE/BIT 2364 BITS

#### FIGURE 5.6

AN EXAMPLE OF ANALOG CHANNEL SCALING

| \$        |            |                                               |                               |                               |              |               |                    |                                                          |

|-----------|------------|-----------------------------------------------|-------------------------------|-------------------------------|--------------|---------------|--------------------|----------------------------------------------------------|

| MFR       | DN TREA    | SCHEMATIC<br>DESIG                            | Τs                            | 4.0<br>V.0 T.C.               | 110-16       | Lh TC         | BAND<br>WIDTH      | •                                                        |

| NATIONAL  | LH0>36     | AR1                                           | GO µa<br>(± 5 V)              | 20/2421<br>20/2421<br>20/2421 | . <u>ज</u>   | 100ma.        | ~ ЭКН <del>г</del> | 3 OP ALLE TWET                                           |

| FINCOLIS  | L144       | (AR3,4 \$ 15)<br>(AR2,5 \$ 6)<br>(AR7,8 \$ 9) | 100 Ja<br>(± 5 V)             | 5 MV<br>3.3 uv/~ :            | 50ma<br>-    | 200ma         | ZHNCOF~            | 3 OP AMP NOUSE THE                                       |

| HARRIS    | 1125114A-2 | ARIO                                          | 75µa                          | 2MV<br>3 µv/°C                | 10ma<br>15ma | 75ma<br>100ma | ~ 100 KHZ          | N POWER OPAMP.<br>OUT SWINGS TO LT ? RATE                |

| Σ<br>ŭ,   | DART NO    | SCHEMATIC<br>DESIG.                           | I S                           | GAIN                          | I SET        | GAIN          | GAIN DRIFT         |                                                          |

| PMI       | PN17524A   | AR13                                          | 100 μα (25°0)<br>500 μα (01.) |                               | + 1%         | 00.+          | ÷.004%/°C          | BBIT D/A CONV.                                           |

| IWd       | PM7528A    | AR14                                          | 100 µa<br>600 µa(REF)         | ++1                           | ± 1150       | 1.00          | ±.007%/°C          | DUAL & BIT D/A CONV.                                     |

| XINCUIN   | D5307A     | 3W1, 2, 3                                     | 10040                         |                               | NJA          |               | N/A                | SPOT CM35 SW - DUNL                                      |

| SILICONIX | DG304A     | 5.44                                          | looya                         |                               | N/A          |               | N/A                | SPST CMOS SW- DUAL                                       |

| MFR       | PART NO    | 5CHEMATIC<br>DESIG                            | Ţs                            | GAIN                          | OUT OFFSET   |               | OUT OFFSET T.C.    | DESCRIPTION                                              |

| NATIONAL  | MF4-100    | ARII                                          | 2.3ma<br>(+5v)                | ±.15 dB                       | - 300mv      | 2 ~           | ~ 163 µv/.c        | 4 POLE, LOW PASS<br>BUTTERWORTH, SWITCHED<br>CAP. FILTER |

|           |            |                                               |                               |                               |              |               |                    |                                                          |

.

ور او ا

Satisfie States

1

ESPRIT MUMBY

TABLE 6. COMPONENTS

SEE FIG. 5.5

.

#### 8.0 POWER

ş

.

مر مر ريا

A discussion of batteries is included in Paragraph 8.0 of Appendix A. A preliminary power budget was presented in that paragraph. An updated estimate of the power requirement for the system (exclusive of the processor and memory) is presented in Table 8.

Combining the updated estimate with the earlier figures for the processor and memory we get:

Operating  $(15.24 + 9.5) \times 100$  hours = 2474 mah Standby 0.5 ma x 650 hours = <u>325 mah</u> 2799 mah

Considering that our battery and switched supply estimate lies in the range of 2600 to 2800 milliampere hour capacity, the goal appears realistic.

#### 9.0 DATA CHANNELS

The recorder has four data channels. Two channels will have software control of gain, offset and bandwidth. They will handle differential or single ended signals and will present a high impedance to the signal source. The other two channels are called event channels and will have a fixed gain of +1 with no bandwidth or offset adjustments internal to the recorder.

The event channels would normally be used to monitor the occurrence of isolated events such as landings, catapults etc. They are analog rather than digital however, and can be used to monitor analog signals in much the same way as the two main analog channels.

The data channels are also disussed in Paragraph 9.0 of Appendix A.

#### 10.0 DATA SYSTEM

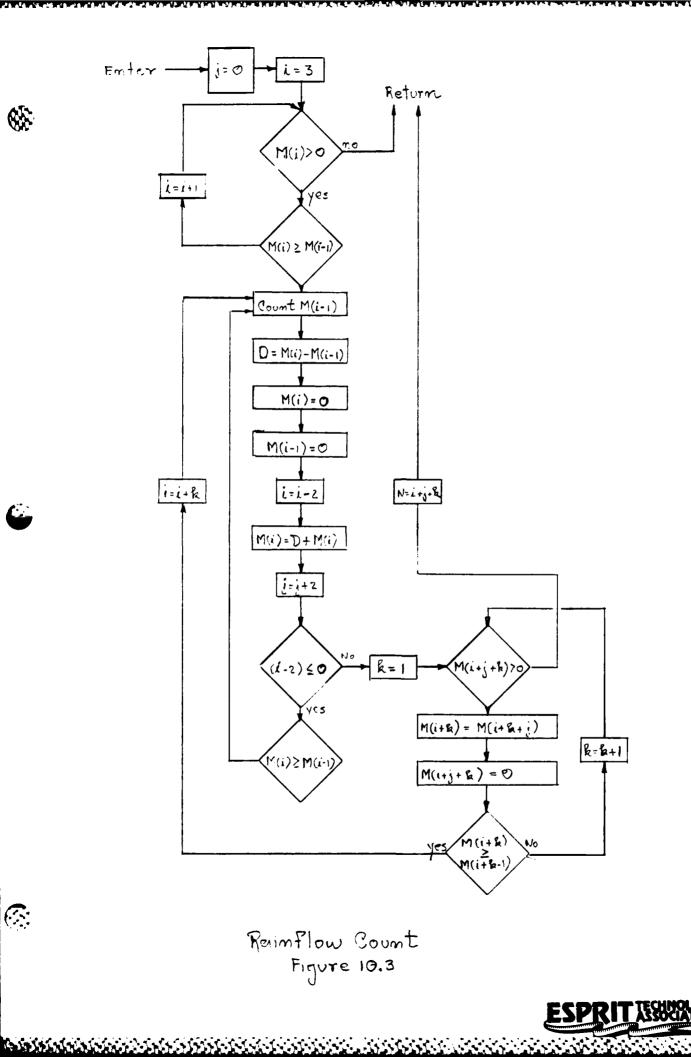

The counting algorithms are described in Paragraph 10 of Appendix A.

#### 11.0 SYSTEM ACCURACY

The specification of Paragraph 3.0 calls for a system accuracy of 5% with a design goal of 3%.

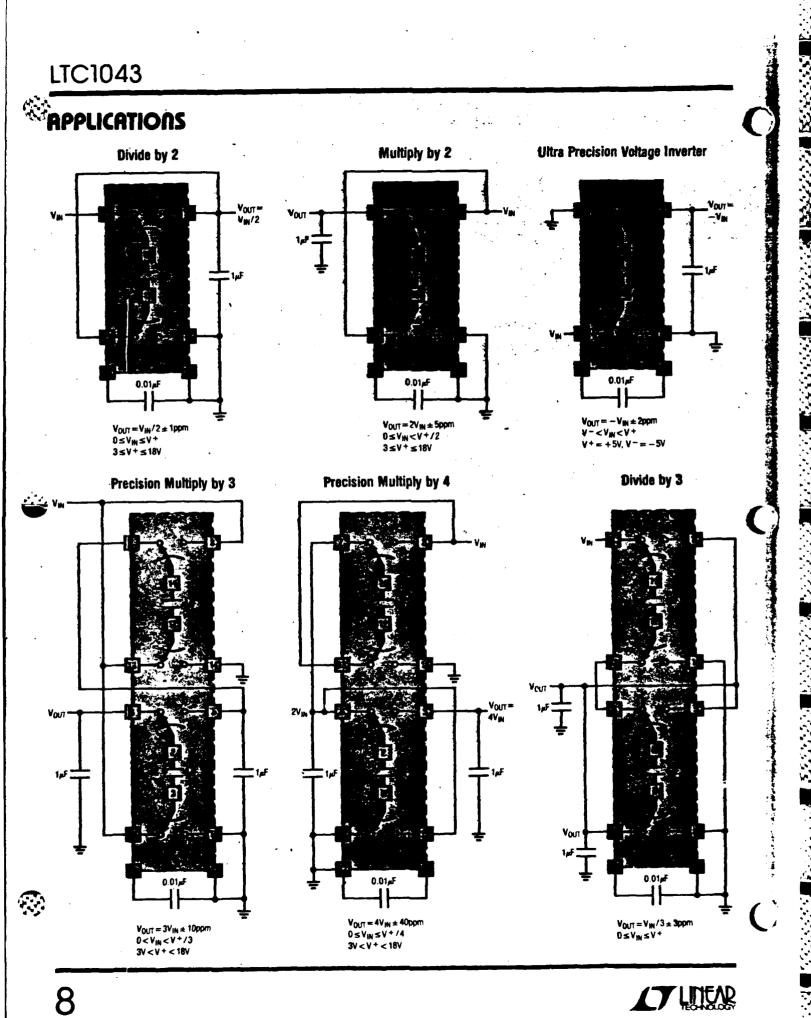

An accuracy assessment of the analog chain presented in Figure 5.5 was performed using the manufacturer's published data. The result is tabulated in Figure 11.1.

In Figure 11.1, accuracies are noted as percent of value figures and are given for half scale and full scale signals

TABLE B POWER ESTIMATE

26

CURRENT DRAIN EXCLUSIVE OF PROCESSOR MEMORY = 15.24 ma.

| CON PONENT      | DRIVE CURRENT | SIGNAL CUFFENT        |

|-----------------|---------------|-----------------------|

| TEAUSDOTERS     |               | 2.0 (10° Fri 2 -      |

| DEIVER          | 0.2           |                       |

| TIMER           | 0.2           |                       |

| A 注)            | 0.12          | 5.4                   |

| AF2             | <b>0.0</b> 0% | 0.3                   |

| ARIS            | 1.0           |                       |

| AR5             | 0.066         | 0.05                  |

| ARG             | 0.066         |                       |

| ART             | 0.066         | 0.05                  |

| ARS             | 0.066         | 0.05                  |

| ARB BIAS        | 0.2           |                       |

| ARH             | 4.6           |                       |

| ARIO            | 0.15          | 0.07                  |

| ARIO BIAS       | 0.2           |                       |

| AR9             | 3.066         | 0.2                   |

| ARIZ            | 0.2           |                       |

| AR4             | 0.066         | 0.2                   |

| AR3             | 0.066         | 0.25                  |

| AP14            | 1.4           |                       |

| AR15            | 0.066         | 0.2                   |

| 501,3           | 0.2           |                       |

| 5W2             | 5.0           |                       |

| 5w4             | 0.2           |                       |

| A/D             | 1.0           | and the second second |

|                 | 10.464        | 3.77                  |

| VIB DET         | 0.3           |                       |

| REF SUPPLY      | 3.3           |                       |

| RAM/ RTE SUPPLY | O. 3          |                       |

| RTC             | 0.1           |                       |

|                 | 11.47         |                       |

Ŵ

7

| reduction by | Q. Zero |              |       | ×            | ×     |              | ×                | ×               | ×      |                 |                     |         |           | ×                   | ×      | 1          |           | ×           | ~          |                 |             |                 |              |                     |                    |                 |                  |   |

|--------------|---------|--------------|-------|--------------|-------|--------------|------------------|-----------------|--------|-----------------|---------------------|---------|-----------|---------------------|--------|------------|-----------|-------------|------------|-----------------|-------------|-----------------|--------------|---------------------|--------------------|-----------------|------------------|---|

| reduc        | (ca).   |              |       | ×            | -1    | ×            |                  | ×               |        |                 |                     | ×       |           | ×                   |        | ×          |           | ×           |            |                 |             | ×               |              |                     |                    | ×               |                  | _ |

| 1=2 V-21     | 95°C    | Full         | Scale |              |       |              |                  |                 |        | 003             | <b>30</b><br>0      | 0       | 0.3       |                     |        |            | 0.25 0.25 |             |            | 0.00            | 0.25        |                 | 0.01         | 0.03                | 0.25               |                 | 201 3:00         | _ |

| error-gval   | ଚ୍ଚ     | 20           | Scale |              |       |              |                  |                 |        | 0.03            | د<br>               | 5       | 0.3       |                     |        |            | 0.25      |             |            | 0.18            | 0.25        |                 | 0.02         | 0.05                | 0.25               |                 | 5                |   |

| residual     | 25 °C   | full         | Scale |              |       |              |                  |                 |        | 0.03            | 1                   | ธิ      | }         | -                   |        |            |           |             |            | 0.09            | 1           |                 | 1            | 0.03                | 1                  |                 | 1                |   |

| 763          | જી      | ×~           | Scale |              |       |              |                  |                 |        | 0.03            |                     | -<br>10 | }         |                     |        |            |           |             |            | 0.18            |             |                 | 1            | 0.05                | 1                  |                 | ۱<br>            |   |

| :- 7º Val.   | ູ່      | lint         | Seale | <br>         | 4.3   | 0.0          | ы.<br>Э.         | 30<br>N         | 0.6    | 0.03            | 0<br>1)             | 2.1     | 0.3       | 5.3                 | -<br>0 | 0)<br>01   | 0.25      | 0.22        | 0.01       | 90.0            | 0.25        | 3.22            | 0.0          | 0.03                | 0.25               | 0.22            | 10.0             |   |

| 6            | 6 P)    | <u>- 1</u> 2 | Scale | 12.2         | 9.0   | 0.<br>~      | 1.6              | ы.<br>6         | در<br> | 0.03            |                     | 2.1     | 0.3       | 0.C                 | 0.1    | ন<br>ন     | 0.25      | 0.44        | 0.02       | 0.0             | 0.25        | 0.44            | 0.02         | 0.05                | 0.25               | 3.44            | 0.05             | _ |

| basic er     | 20052   | tull         | Scale | 6.I          | 1     | 0.5          | 9.<br>19.<br>19. | જી.<br>હો       | 1      | 0.03            |                     | ~       | ١         | 00<br>10<br>10      | 1      | (1)<br>(1) | 1         | 0.22        |            | 90.0            | !           | 0.22            | (            | 0.03                | I                  | 0.22            | 1                |   |

| bas          | ©<br>0  | 22           | Scale | 12.2         | 1     | 0.           | 7.6              | و<br>ن          | 1      | 0.00            | }                   | -2      | }         | <i>৩</i><br>১       | )      | 4.         | ۱         | 0.44        | 1          | <u></u>         | !           | 3.44            | !            | 0.05                |                    | 3.44            | 1                |   |

| 9            |         |              |       | ତ 22 ଂତ      | ++    | \<br>\       |                  | ¥               | drift  | carity          | taritt              |         |           | 0,52 Q              | チェーシャ  | <b>ہ</b> . |           | V@256       | c\rift     | 00 D            | -           | V @ 250         | دب           | ároop               | -                  | Y⊛25℃           | - <del>1</del> - |   |

| SOUTCE       |         |              |       | rt < ©       | druft | faet         |                  | ifset           | d'     | mlime           | sultr               | 43      | かけた       | set V               | ÷      |            | drift     | tast        | <b>г</b> о | rodr            | 6124        | fiset           | arift        | Hald                |                    | itset           | 15:11            |   |

| error        |         |              |       | mp. offset V | =     | imput offset | CMRR             | output sifet V. | -      | gain nonlineari | offset adjust drift | gain ?  | व छा भ छ  | limp. Offset V@25°C | -      | imput bia  | gaim d    | input sifet | 11         | Auto zero droop | gaim ciritt | imput offset v@ | - <u>-</u> - | Sample : Hold Iroop | gaim Arift         | input affect ve | 1                |   |

|              |         |              |       | -            |       |              |                  |                 |        |                 |                     |         |           |                     |        |            |           |             |            |                 |             |                 |              | -                   |                    |                 |                  | - |

| component    | •       |              |       | ARI          | ARI   | ARI          | ARI              | ARI             | ARI    | ARI             | ARI, ARI3, ARH      | AR2 AR  | AR2, AR13 | AR2                 | AR2    | AR2        | ARS       | ARS         | ARS        | いた              | AR7         | LA F.           | AR7          | A R7                | AR3                | A 83            | ARB              |   |

| item         |         |              |       | -            | 2     | m            | 4                | م               | و      | 1               | Ø                   |         | 5         |                     | 27     | 3          | 14        | 2           | 202        | <u> </u>        | ñ           | 61              | 20           | 5                   | נו <i>ג</i><br>נוס | ц<br>С          | ナ-<br>カ          |   |

いたからのないです。  $\times \times$  $\succ$  $\times$  $\times$ いた いたがいたい たんたいからの 0.15 0.08 0.25 0.25 . 10.0 0.50 0.25 0.13 0.18 0.25/0.25 0.02/0.04 3.30 0.15 0.02 0.01 0.3 0.3 2.1 4.  $\hat{\mathbf{C}}$ ~ 3.25 0.25 4; () 0.9 9 0.9 0.0 ي. ف 9.4 70 of Val. Absolute error 8 0.57 0.04 0.02 3.02 0.25 0.25 5 0.09 0.18 0.09 0.8 1.7 34.6 117.3 3.02 0.01 J.30 0.15 0.9 3.15 0.25 3.50 () () () 5.0 0. 0.25 0.15 3.08 0.15 1. ( 0.3 2.25 3 7.04 10.02 0.3 1 ۱ ł 1 0.12 50 رب) د ک Under visted evision いたいとう 1.1.2.4 された () () () mout affect i Ref. V. 181 Ft 12 2 8205 BIAS duilt Bras a nift C (1) (1) (1) Jugar imput Barce 2:2 BIDS CARIO Xder drive BIDS@ARE A/D Zamv. A/D Comu. A RIO ARIO APIO AR,O AP 10 6 RH 11 12 12 A RS いメタ 1 2 2 2 2 50-0M 4) 1 10 0 T ୀ) .ମ 39 500

2. Calculations based on signal levels presented in figure 5.6 Note: 1. See figure 5.5 (Conceptual schematic.)

FICURE II. I RECORDER ERROR ANALYSIS

2 6 6

at 25 C and 95 C. The calculations were made in relation to the sample system set up of Figure 5.6 in which a strain bridge is used to measure strains in the range 0 to  $40000 \oplus$ .

Both absolute and RSS errors are given - the former would be a worst case while the latter should be closer to the actual error in any measurement situation.

Perusal of the table shows that bias drifts are the major error source and further, that the intentionally added bias voltages (at AR1, AR8 and AR10) as well as the output drift of the switched capacitor filter make up the bulk of the irreducible errors. The latter error might be reduced by providing a temperature sensitive bias at either AR8 or AR10 while the other three sources are strictly dependent on the excellence of the bias source.

This accuracy assessment does not cover errors associated with signal frequency content - the main one being aliasing at the switched capacitor filter. As noted previously, the prefilter (AR8) may require more poles or a degree of tuneability. Aliasing will be covered in Phase II.

The results of the accuracy assessment are promising. The final system should meet the specification requirement.

#### 12.0 COST ESTIMATE

Our preliminary cost estimate for the recorder is \$3000 to \$3500 each in quantities of 99 and up. The final price will have a strong dependence on the packaging, with the cost of the surface mount and hybrid modules being the major cost drivers.

#### 13.0 <u>CONCLUSION</u>

The study to date leads us to conclude the project goals are realistic. An engineering program in Phase II will result in the recorder system described in the initial solicitation and proposal.

A summary of the program to date, the work completed, and the results obtained is given on the summary page and in the introduction of Paragraph 1.0 of this report. APPENDIX A: Interim Report Small-Self-Contained Aircraft Fatigue Data Recorder

Ú

8

St. 46 . 46 . 48 . 48 . 4

144-A Mayhew Way, Walnut Creek, California 94596, USA • (415) 947-0400

ESPRIT TECHNOLOGY INC. N62209-05-C-0710 \$49,084.00 COMPELITIVE A. NEGRI NAVAL AIR DEVELOPMENT CENTER CODE 6042, WARMINSTER, PA. 10974-5000

3

INTERIM REPORT SMALL-SELF-CONTAINED AIRCHAFT FATIGUE DATA RECORDER Cont. No. No2269-05-C-0710 Oct. - Dec. 1905

Submittal Date: January 21, 1906

LIMITED RIGHTS LEGEND CONTRACT NO. No2269-85-C-0716 CUNIMACTUR: ESPRIT TECHNULOGY INC.

Inis technical data shall not, without the written permission of the above contractor, be either (A) used, released or disclosed in whole or in part outside the Government, (B) used in whole or in part by the Government for manufacture, or (C) used by a party other than the Government. This legend shall be included on any reproduction of this data, in whole or in part.

Ine design information contained herein is the sole property of ESPRIT technology Inc. and the disclosure of this information does not constitute the release of the proprietary rights thereof.

## TABLE OF CONTENTS

and accesses here press seconded

- 1.0 Introduction/Summary

- 2.0 System Description

- 3.0 Specification

- 4.0 Packaging

- 5.0 Circuits

- b.0 Components

- 7.0 Transducers

- 8.0 Power

- 9.0 Data Channels

- 10.0 Data System

- 11.0 System Accuracy

- 12.0 Cost Estimate

- 15.0 Conclusion

## 1.0 <u>Introduction/Summary</u>

لاستعامتهم

This interim report describes the work carried out on contract N52259-55-C-0715 from October, 1985 through early January, 1985. The intent of the report is to apprise the sponsor of the progress to date and to solicit comments from the sponsor on the report content and the direction the design is taking.

The initial design study has turned up no technical problems precluding attainment of the design goal. We have no reason to believe a Phase 11 effort will not culminate in creation of a small, battery powered data recorder configured to support operational surveys of military aircraft.

Each paragraph of the report covers a specific segment of either a design task or program element. Although some tasks and elements remain to be completed, short paragraphs have been included to illustrate the form planned for the final report.

The early stages of the design effort have been particularly directed at circuits (paragraph 5), component selection (paragraph b), power sources (paragraph b) and the data system (paragraph 10). A brief summary of the design approach follows.

The recorder is powered by lithium batteries. The final design includes a small DC-DC converter to provide for use of various battery chemistries to cover different temperature ranges of operation. The power supply system contains a vibration transducer and associated circuitry to activate and deactivate the recorder according to whether the aircraft is in use or not. Two main and two auxiliary data channels are included. The main channels interface with most transducers of interest since their input circuits are classic high impedance, high CMR instrumentation amplifiers. The system is designed to drive strain based transoucers with switched current sources run at a low duty cycle to limit power consumption. The analog chains of the two main channels consist of an input amplifier, a synchronous demodulator, a post demodulation pre-sampling filter combination, a switched capacitor low pass filter, a smoothing filter and an output amplifier. The channel gain, offset and bandwidth are under software control. The available bandwidths range from 2.5 Hz to 50 Hz and are set by the clocking of the 4th order, low pass, butterworth switched capacitor filter. The auxiliary channels are included to provide for event monitoring (e.g. catapults and arrests) and simple two wire transducer temperature monitoring. The conditioned analog signals are digitized by an o-bit, successive approximation converter that has a built-in four channel analog multiplexer. The digital portion of the recorder has a CMUS microcontroller and CMOS memory - the latter being UV EPROM to contain the operating system and counting algorithms and static RAM for data storage. Ine software includes provisions for controlling the aforementioned gains, offsets and bandwidths as well as for selection of the desired counting algorithms. The counting

algorithms provide for load level, peak-valley or rainflow counting of the physical parameter being monitored.

$\overline{\mathcal{N}}$

F

Expanded descriptions of the design approach are given in the body of the report with the main content lying in paragraphs 5, 8 and 10.

#### 2.0 System Description

The system being designed has two major components, the airborne system and the ground support system, each of which can be considered to be made up of two or more subcomponents.

The airborne system includes the recorder and the transducer set. The recorder is completely self-contained and self-powered; it includes a power source, a microcomputer, program memory, data memory, a digitizer, analog signal conditioners, a power control transducer and associated circuitry and at least one accelerometer. The transducer set includes any strain based transducer of reasonable input impedance and bridge-like circuitry. Pressure, acceleration and strain transducers are presumed to be of the greatest interest. Current source temperature sensors or medium to high impedance resistance thermometers could also be handled.

A desktop computer, computer interface and master program disk comprise the ground based system. Virtually any small desktop computer would suffice to handle the recorder programming, data retrieval and data transcription tasks assigned to the computer. An IBM compatible unit appears to offer the greatest flexibility. Ine computer interface assures that the handshake protocol and logic voltage levels between the computer and the recorder serial interface are compatible. The system master disk contains the algorithim menus and user interactive software.

Although not strictly a system component, an operation manual is also required for user support.

#### J.0: **Specification**

**`**}

in the second

1. 14

The initial design studies lead us to make some minor adjustments to the original design goal specification. The updated specification is included below with changes or additions indicated by an asterisk.

PARA CALL LALLAN

#### Design Goal Specification

| General:                 | The equipment shall be a self-contained, self-powered<br>data recorder capable of monitoring a variety of<br>environmental transducers. The recorder shall perform<br>preliminary data reduction/compression and store the<br>results in non-volatile memory for later retrieval. |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Size:                    | 1" x 2" x 4" maximum volume (See Figure 3.1)                                                                                                                                                                                                                                      |

| Mounting:                | To mounting pads. Mounting pads bonded or bolted to<br>the aircraft. (See Figure 3.1)                                                                                                                                                                                             |

| *ŕower:                  | Supplied by internal batteries. Minimum 1 month<br>supply per battery set.<br>Projected - 3000 man batteries to<br>support up to 100 hours of data<br>gathering and one month or more of<br>untended installation.                                                                |

| Power<br>Control:        | <ul> <li>a) CMOS static RAM, continuously supported.</li> <li>b) Other circuitry activated and de-activated by turn-on circuit sensitive to engine vibrations.</li> <li>c) In flight-algorithms designed to utilize CMOS processor standby and wait states.</li> </ul>            |

| Data<br>Channels:        | Two channels max plus 2 event counts (e.g. count of catapults and arrests.)                                                                                                                                                                                                       |

| ⁺Channel<br>Bandwidtns   | Up to 50 Hz (one channel system)<br>: Up to 20 Hz (two channel system)<br>2.5 Hz minimum bandwidth                                                                                                                                                                                |

| Bandwidth<br>Control:    | By software.                                                                                                                                                                                                                                                                      |

| Conversion<br>Resolution | : ö bits                                                                                                                                                                                                                                                                          |

| Conversion<br>Type:      | Absolute or ratiometric                                                                                                                                                                                                                                                           |

| Data Compr               | ession: Choice of a) level classification<br>(exceedance count).                                                                                                                                                                                                                  |

b) peak valley pairs.c) simple rainflow.

Compression Control: By software.

\*Data a) level classes - up to 32 (over 16 x 10<sup>6</sup> Format: counts per level.)

- b) Peak valley pairs up to 32 x 32 peak-valley matrix (496 cells, up to 2 bytes per cell, 65 x 10<sup>3</sup> counts per cell).

- c) Kainflow up to 32 vector magnitudes and starting values.  $65 \times 10^3$  counts per magnitude)

(cell sizes for (b) & (c) can be doubled for data bandwidths above 20 hz.)

Data Memory: 2K x & CMOS static RAM.

Data Module removed from aircraft and transported to Retrieval: Transcriber (commercial microcomputer, e.g. an IBM PC plus associated interface hardware). Data transfer through a serial port and software UART.

Transducer Location: Options for internal or external mounting.

Transducer Internal - Acceleration, strain or pressure; all Types: strain type devices. Temperature; two-terminal 1C device. External - General environmental transducers.

Transducer Internal - Powered by system. Power: External - Powered by system if low power device capable of pulsed power operation. Supplementary battery pack or ships power required for high power servo type transducers.

Uperation The mode of operation is controlled by software. Options: The transcriber is used to program the recorder. Ine following features are under software control:

> Channel Bandwidth Channel Ranges Channel Sample Rate Data Compression Method Data Format

System Accuracy: 5% max; 5% design goal. Design: To meet the intent of MIL-E-5400T Class 3 equipment.

- 5-

#### 4.0 <u>Packaging</u>

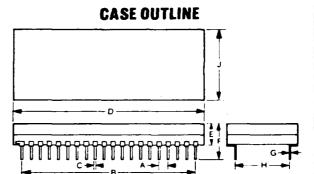

Conventional discrete component/printed circuit board packaging does not provide the volumetric efficiency required to meet the package volume goal.

We plan to use a combination of hybrid and surface mount technology. The Electronic Designs EDHoo7C31 JAPAK shown in exhibit 6 to paragraph 5 is an example of a practical approach to packaging. The device is essentially a surface mount module with the major 1.C's in chip carriers being mounted to a ceramic substrate (i.e. surface mount) with the subassembly then being finished as a "standard" 40 pin DIP for mounting in conventional P.C. boards.

The EDHbb7C31 meets some of the criteria we have set for packaging. First, it provides a major system component (the digital subassembly) as a module and second it illustrates the availability of external vendors to perform this type of assembly. The latter is important - we do not propose to emphasize high volume, capital intensive manufacturing within our company but rather prefer to concentrate on system assembly and engineering design.

in addition to the modular surface mount technique described above, we are also considering true hybrids. Exhibit 1 to this paragraph is an example of a microcomputer built as a true hybrid. This device, the White Technology Inc. DHCO-PO5 is very attractive - note the -55 C to +200 C operating temperature range - but may require too much power for the present application. It does, however, exhibit the availability of hybrid technology for our application - in fact White Technology Inc. will do custom designs.

hybridizing is more costly, both for the initial design and for the production, than is modular surface mount. As we move into the conceptual package design, modular surface mount will be considered as first choice.

Our packaging approach will thus be to design a system made up of major subassemblies, each of which is a surface mount module.

#### Package Mounting

we plan to mount the package as described in the original proposal. (See also paragraph 3.0)

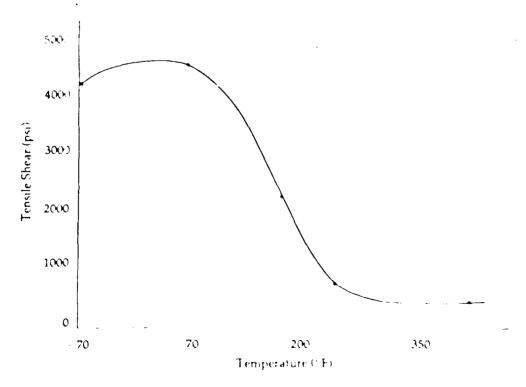

The package will mount to blocks that are attached to the airframe. The mounting will be with self-locking quick aisconnects to provide for simple exchange of recorder modules. In addition, the recorder package will be designed with an expansion joint to prevent build-up of shear stress at the interface of the mounting blocks and the airframe. The blocks will be bolted or cemented to the airframe. A precedent exists for cementing in the mounting of the Leigh Instruments MSR strain recorder currently in use in a number of military aircraft. An example of an adhesive used for this purpose is included as exhibit 2 to this paragraph.

Detailed instructions for cementing the blocks to the airframe must be developed and included in the recorder operating instructions.

たんたいでする

Ī

$\{ \hat{\boldsymbol{y}}_{i} \}^{T}$

EXHIBIT 1

The White Technology Inc.

DHC8-P65

- - Oscillator, Crystal in Pa Full 8085 Instruction Set

- 2K Byte Static RAM

- 2K Byte CMOS ROM

- Hardware UART (50 to 9600 Baud

- Built-In Power-On Reset

- Direct Operation of Terminal With

- Built-In Monitor-RS232 at 9600 Baud

- Low Power Hibernate Mode

## DESCRIPTION

The White Technology DHC8-P85 is a high performance 8 bit microcomputer arranged around a CMOS 8085 microprocessor. Also contained in the 40 pinteramic package is a 14.74559 MHz crystal clock oscillator with the crystal contained within the package. Communication with virtually any RS-232 compatible terminal is provided for using a Programmable Asynchronous Communication Interface (PACI). Initial program storage is accommodated with an internal 2K byte CMOS ROM and program data is stored in the internal 2K byte CMOS static RAM. All output lines and many input lines are buffered with high speed, high current drive CMOS 3-state buffers

White Technology has sought to satisfy a wide range of high performance microcomputer needs for Oil Logging, Engine Instrumentation and other Hostile Environments. The dense thick film multilayer substrate interconnects over 17 IC's in a standard

Technology,

40 pin ceramic package.

White Technology has enhanced the quality and reliability by manufacturing and processing the units with the HE-1 Hostile Environment quality and reliability specification. Included are rigorous inspections, tests and reliability evaluations to assure the users that the finished assemblies are suitable for operation in some of the more severe applications.

The DHC8-P85 is the core module of the DHC8 family. Other members include RAM, ROM, I/O and DATA ACQUISITION modules. The members of the family are intended to be interconnected readily with little design effort to realize a wide variety of data acquisition and process control functions. The widely used 8085 series microprocessor bus was chosen as the main communication link between the various modules. Most modules feature address' data demultiplexing and address decoding to reduce the system device count.

4246 EAST WOOD STREET + PHOENIX, ARIZONA 85040 TEL: 802-437-1520 + TWX: 910-951-4203

For CHC185 Classifyinght white Technicupy Inc. 198

# 8-BIT MICROCOMPUTER SYSTEM-DHC8-P85

| Specifications (-55°C to +200°C) |                                           |           |      |      |      |

|----------------------------------|-------------------------------------------|-----------|------|------|------|

| Symbol                           | Parameter                                 | Min.      | Max. | Тур. | Unit |

| VOCIOPI                          | Supply Voltage (Operating)                | 4.75      | 5.0  | 5.25 | Vdc  |

| VCCISBI                          | Supply Voltage (Stand-By)                 | 3.5       | -    | 7.0  | Vdc  |

| ICCIOPI                          | Supply Current (Operating)                |           | 35   | -    | mA   |

| ICCISBI                          | Supply Current (Stand-By)                 | 1         | 4.0  | -    | mA   |

| ViH                              | Input High Voltage                        | 2.0       | —    | -    | Vdc  |

| V <sub>IL</sub>                  | Input Low Voltage                         | -         | -    | 0.8  | Vdc  |

| V <sub>OH</sub>                  | Output High Voltage                       | 3.0       | -    | —    | Vdc  |