MICROCOPY RESOLUTION TEST CHART NATIONAL BUREAU OF STANDARDS-1963-A

(COCCOC)

Ľ

AD-A171 706

HIGH SPEED POLYCRYSTALINE SILICON PHOTOCONDUCTORS FOR ON-CHIP PULSING AND GATING

> CPT Douglas R. Bowman HQDA, MILPERCEN (DAPC-OPA-E) 200 Stovall Street Alexandria, VA 22332

Final Report - June 1986

Approved for Public Release; Distribution is Unlimited.

A thesis submitted to Stanford University, Stanford, California in partial fulfillment of the requirements for the degree of Doctor of Philosophy of Electrical Engineering

86

9

09

026

IT FILE COPY

| REPORT NUMBER                                                                                                                                                             | A CONT ACCEPTION N                                                                                                                                                                                                                  |                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                           | 2. GOVT ACCESSION IN                                                                                                                                                                                                                | 3. RECIPIENT'S CATALOG NUMBER                                                                                                                                                                                       |

|                                                                                                                                                                           | IAD-4171                                                                                                                                                                                                                            | 706                                                                                                                                                                                                                 |

| TITLE (and Subtitie)                                                                                                                                                      |                                                                                                                                                                                                                                     | 5 TYPE OF REPORT & PERIOD COVERED                                                                                                                                                                                   |

|                                                                                                                                                                           |                                                                                                                                                                                                                                     | FINAL REPORT JUNE 1986                                                                                                                                                                                              |

|                                                                                                                                                                           | ne Silicon Photoconductors                                                                                                                                                                                                          |                                                                                                                                                                                                                     |

| for On-Chip Pulsing and                                                                                                                                                   | CT 11)3;                                                                                                                                                                                                                            | 5 PERFORMING ORG. REPORT NUMBER                                                                                                                                                                                     |

| AUTHOR(a)                                                                                                                                                                 |                                                                                                                                                                                                                                     | U CONTRACT OR GRANT NUMBER(A)                                                                                                                                                                                       |

|                                                                                                                                                                           |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                     |

| Douglas R. Bowman                                                                                                                                                         |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                     |

| PERFORMING ORGANIZATION NAM                                                                                                                                               | F AND ADDRESS                                                                                                                                                                                                                       | 10 PROGRAM ELEMENT. PROJECT. TASK                                                                                                                                                                                   |

| Student, HQDA, MILPERCE                                                                                                                                                   |                                                                                                                                                                                                                                     | AREA & WORK UNIT NUMBERS                                                                                                                                                                                            |

| 200 Stovall Street                                                                                                                                                        |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                     |

| Alexandria, Virginia 22                                                                                                                                                   | \$ 3.1                                                                                                                                                                                                                              |                                                                                                                                                                                                                     |

| 1 CONTROLLING OFFICE NAME AN                                                                                                                                              | DADDRESS                                                                                                                                                                                                                            | 12 REPORT DATE                                                                                                                                                                                                      |

| HQDA, MILPLRCEN, AFEN:                                                                                                                                                    | DAPC-OPA-F                                                                                                                                                                                                                          | JUNE 1986                                                                                                                                                                                                           |

| 200 Stovall Street                                                                                                                                                        |                                                                                                                                                                                                                                     | 13 NUMBER OF PAGES                                                                                                                                                                                                  |

| Mexandria, Virginia 22                                                                                                                                                    | 33. DDRESS.if Alterent from Controlling Office)                                                                                                                                                                                     | 15 SECURITY CLASS, (of this report)                                                                                                                                                                                 |

| 4 MONITORING AGENCY NAME 5 A                                                                                                                                              |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                     |

| 4 MONITORING AGENCY NAME & A                                                                                                                                              |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                     |

| 4 MONITORING AGENCY NAME & A                                                                                                                                              |                                                                                                                                                                                                                                     | UNCLASSIFIED                                                                                                                                                                                                        |

| 4 MONITORING AGENCY NAME & A                                                                                                                                              |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                     |

| M DETHICTION STATEMENT 300<br>Approved for public rel                                                                                                                     | <pre>(a Kopon) (a Separat ( ) Set; distribution unlimit) ( ) obstract ontered in Block 20, H different i </pre>                                                                                                                     | UNCLASSIFICATION DOWNGRADING<br>SCHEDULE                                                                                                                                                                            |

| The permination statement and<br>Approved for public rel                                                                                                                  | cese; distribution unlimite                                                                                                                                                                                                         | UNCLASSIFICATION DOWNGRADING<br>SCHEDULE                                                                                                                                                                            |

| M DETHICTION STATEMENT 300<br>Approved for public rel                                                                                                                     | cese; distribution unlimite                                                                                                                                                                                                         | UNCLASSIFICATION DOWNGRADING<br>SCHEDULE                                                                                                                                                                            |

| Approved for public rel<br>Approved for public rel<br>Poistribution statement of th                                                                                       | cese; distribution unlimite                                                                                                                                                                                                         | UNCLASSIFICATION DOWNGRADING<br>SCHEDULE                                                                                                                                                                            |

| Approved for public rel<br>Approved for public rel<br>DE SUPPLEMENTARY NOTES                                                                                              | erse; distribution unlimite<br>• abaument entered in Block 20, 11 different f                                                                                                                                                       | UNCLASSIFIED<br>15. DECLASSIFICATION DOWNGRADING<br>SCHEDULE<br>ed.                                                                                                                                                 |

| Approved for public rel<br>Spproved for public rel<br>Sistribution statement of th<br>Supplementary notes<br>Thesis submitted to Stor                                     | e (se; distribution unlimit)<br>• • • • • • • • • • • • • • • • • • •                                                                                                                                                               | UNCLASSIFIED<br>15. DECLASSIFICATION DOWNGRADING<br>SCHEDULE<br>ed.<br>rom Report)<br>ed in part by the Fannic &                                                                                                    |

| Approved for public rel<br>Spproved for public rel<br>Statement of the<br>Instrumentary notes<br>Thesis submitted to State<br>John Hertz Foundation,                      | e (se; distribution unlimit)<br>• • • • • • • • • • • • • • • • • • •                                                                                                                                                               | UNCLASSIFIED<br>15. DECLASSIFICATION DOWNGRADING<br>SCHEDULE<br>ed.                                                                                                                                                 |

| A DESTRIBUTION STATEMENT of the<br>Septement of the supplementary notes<br>Thes is submitted to Stat<br>John Hertz Foundation,                                            | e (se; distribution unlimit)<br>• • • • • • • • • • • • • • • • • • •                                                                                                                                                               | UNCLASSIFIED<br>15. DECLASSIFICATION DOWNGRADING<br>SCHEDULE<br>ed.<br>rom Report)<br>ed. in part by the Fannic &                                                                                                   |

| To permination statement and<br>Approved for public rel<br>substribution statement of th<br>Thesis submitted to Stat<br>John Hertz Foundation, a<br>Department of Energy. | e (se; distribution unlimit)<br>• • • • • • • • • • • • • • • • • • •                                                                                                                                                               | UNCLASSIFIED<br><sup>15.4</sup> DECLASSIFICATION DOWNGRADING<br>SCHEDULE<br>ed.<br>rom Report)<br>ed in part by the Fannic &<br>t DAAG29-83-K-0125), and the                                                        |

| To permination statement and<br>Approved for public rel<br>substribution statement of th<br>Thesis submitted to Stat<br>John Hertz Foundation, a<br>Department of Energy. | e se; distribution unlimite<br>• obstract entered in Black 20, Holdferent f<br>nford University. Sponsore<br>Army Research Office (Gram)                                                                                            | UNCLASSIFIED<br>15. DECEASSIFICATION DOWNGRADING<br>SCHEDULE<br>ed .<br>tom Report)<br>ed in part by the Fannic &<br>t DAAG29-83-K-0125), and the                                                                   |

| Approved for public rel<br>Approved for public rel<br>Distribution statement of th<br>John Hertz Foundation, a<br>Department of Energy.                                   | <pre>cise; distribution unlimite o abatract onterod to Block 20, BlotBlocent b ford University, Sponsore Army Research Office (Gram) ide if no esserv and identity by block numbe Microstrip Transmission Integrated Circuits</pre> | UNCLASSIFIED<br>15. DECLASSIFICATION DOWNGRADING<br>SCHEDULE<br>ed.<br>tom Report<br>ed in part by the Fannic &<br>t DAAG29-83-K-0125), and the<br>main Lines Dispersive<br>Propagation                             |

| Approved for public rel<br>Approved for public rel<br>Distribution statement of th<br>Thesis submitted to Stat<br>John Hertz Foundation, a<br>Department of Energy.       | <pre>cise; distribution unlimite o abatract onteroid to Block 20, Blockment d iford University. Sponsore Army Research Office (Grand Microstrip Transmission Integrated Circuits, Bligh Speed Integrated 0</pre>                    | UNCLASSIFIED<br>15. DECLASSIFICATION DOWNGRADING<br>SCHEDULE<br>ed.<br>ed.<br>tom Report)<br>ed in part by the Fannic &<br>t DAAG29-83-K-0125), and the<br>m<br>n Lines Dispersive<br>Propagation<br>Circuits VHSIC |

.

7

ς.

## Abstract

ݥݲݡݡݚݠݚݠݚݠݚݠݚݠݚݠݔݠݞݵݾݔݠݞݚݔݞݞݚݵݞݡݵݑݠݲݕݵݞݸݑݵݠݥݵݠݪݥݵݞݾݲݵݠݪݪݑݵݪ ݕݲݚݞݕݠݚݖݮݚݠݚݠݚݠݚݠݔݠݬݠݔݠݾݔݔݞݞݚݔݞݞݚݵݞݸݔݵݞݸݑݵݪݥݑݵݪݥݵݥݥݲݵݠݪݪݑݵݪ

Salat Cal X Alan Sec.

anners second and strates

Photoconductor based time-domain measurement techniques for testing silicon integrated circuits are the focus of this research. The objective is to produce a very high speed sampling system which may be integrated using standard integrated circuit (IC) processing technology and provide for on-chip characterization at frequencies higher than current measurement systems allow.

Integrated photoconductors constructed on shoon wafers of 6 to 70 ohm cm resistivity from annealed polycrystaline silicon and damaged by ion-beam irradiation are reported. They are used in an optoelectronic sampling system to perform high frequency measurements of picosecond pulse propagation in IC microstrip interconnections. Optoelectronic correlation measurements of photoconductor pulsers and photoconductor sampling gates are used to characterize both the photoconductors and the IC interconnections. A subpicosecond pulsed laser system is used to excite the photoconductors to generate and sample the high frequency pulses.

Photoconductors processed as fast pulsers produced  $\approx 20$  mV peak magnitude, 3 picosecond Full Width at Half Magnitude (FWHM) pulses while photoconductors processed as large-signal step pulsers produced  $\approx 200$  mV peak magnitude, 6 picosecond risetime pulses of fifty picosecond duration. Sampling gate photoconductors demonstrated 3-dB measurement bandwidths in excess of 100 GHz. Due to the virtual absence of noise and jitter, high resolution sampling of small, high speed signals is possible with sub-picosecond accuracy. High frequency losses and dispersive propagation in the integrated microstrip transmission system are measured and characterized. © Copyright 1986 by Douglas Roland Bowman

## HIGH SPEED POLYCRYSTALINE SILICON PHOTOCONDUCTORS FOR ON-CHIP PULSING AND GATING

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> By Douglas Roland Bowman June 1986

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as dissertation for the degree of Doctor of Philosophy.

btn Robert W. Dutton

(Principal Adviser)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as dissertation for the degree of Doctor of Philosophy.

Jarase Krishna C.

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as dissertation for the degree of Doctor of Philosophy.

Mark A. Enton Mark A Linton

Approved for the University Committee on Graduate Studies:

Hizabeth Closs Tranget

Dean of Graduate Studies & Research

## Abstract

Photoconductor based time-domain measurement techniques for testing silicon integrated circuits are the focus of this research. The objective is to produce a very high speed sampling system which may be integrated using standard integrated circuit (IC) processing technology and provide for on-chip characterization  $\bigstar$  at frequencies higher than current measurement systems allow.

Integrated photoconductors constructed on silicon wafers of 6 to 70 ohm-cm resistivity from annealed polycrystaline silicon and damaged by ion-beam irradiation are reported. They are used in an optoelectronic sampling system to perform high frequency measurements of picosecond pulse propagation in IC microstrip interconnections. Optoelectronic correlation measurements of photoconductor pulsers and photoconductor sampling gates are used to characterize both the photoconductors and the IC interconnections. A subpicosecond pulsed laser system is used to excite the photoconductors to generate and sample the high frequency pulses.

Photoconductors processed as fast pulsers produced  $\approx 20$  mV peak magnitude, 3 picosecond Full Width at Half Magnitude (FWHM) pulses while photoconductors processed as large-signal step pulsers produced  $\approx 200$  mV peak magnitude, 6 picosecond risetime pulses of fifty picosecond duration. Sampling gate photoconductors demonstrated 3-dB measurement bandwidths in excess of 100 GHz. Due to the virtual absence of noise and jitter, high resolution sampling of small, high speed signals is possible with sub-picosecond accuracy. High frequency losses and dispersive propagation in the integrated microstrip transmission system are measured and characterized.

## Acknowledgments

I would like to thank all the people who have aided me in the completion of this work. Particular thanks go to Dr. Robert Dutton for his help as my advisor at Stanford University and the one who pointed me in the direction of this research, Dr. William Eisenstadt who did much of the initial work in silicon and provided the foundation upon which this research is based, and to Dr. Robert Hammond who provided guidance and the facilities to perform the experimental measurements at the Los Alamos National Laboratory. Additional thanks go to Nick Paulter and others at the Los Alamos National Laboratory, Ronald Reedy at the Naval Ocean Systems Center, and the entire staff of the Stanford Integrated Circuits Laboratory for their help in fabricating, preparing, and measuring the test devices. I'm indebted to John Acken for his tireless help in producing this document in absentia and to Fely Barrera for taking care of the variety of administrative details. I also wish to thank my wife, Trish, for all she has done during the time it took to complete this research and thesis. Her patience, understanding, and support contributed significantly to my efforts to complete this work.

I would like to acknowledge that this research was sponsored in part by the Fannie and John Hertz Foundation and the U.S. Army Research Office under Grant Number DAAG29-83-K-0125. The measurement system at the Los Alamos National Laboratory was provided by the Department of Energy.

# Contents

| Al                  | bstra      | ct                                                          | v        |

|---------------------|------------|-------------------------------------------------------------|----------|

| Acknowledgments vii |            |                                                             | ii       |

| 1                   | Intr       | oduction                                                    | 1        |

|                     | 1.1        | Introduction to Pulsed Laser Measurements                   | <b>2</b> |

|                     | 1.2        | Introduction to High-Speed Polysilicon PCE's                | 3        |

|                     | 1.3        | Introduction to Microstrip Measurements                     | 5        |

|                     | 1.4        | Discussion of Future Work                                   | 6        |

| 2                   | Puls       | ed Laser Measurements                                       | 7        |

|                     | 2.1        | Picosecond Optoelectronic Switching                         | 7        |

|                     | <b>2.2</b> | Optoelectronic Sampling                                     | 12       |

|                     |            | 2.2.1 Electro-optic Methods                                 | 12       |

|                     |            | 2.2.2 Integrated Optoelectronic Samplers                    | 4        |

|                     |            | 2.2.3 PCE Measurement System Considerations and Implementa- |          |

|                     |            | tion                                                        | 19       |

|                     | 2.3        | Summary                                                     | 23       |

| 3                   | Dev        | elopment of Polysilicon PCE's 2                             | 25       |

|                     | 3.1        | Advantages of Polysilicon PCE's                             | 25       |

|                     | 3.2        | Device Design Optimization                                  | 27       |

|                     |            | 3.2.1 General Layout                                        | 27       |

|                     |            | 3.2.2 Size Optimization                                     | 29       |

|   | 3.3         | PCE Process Development                      | 33        |

|---|-------------|----------------------------------------------|-----------|

|   |             | 3.3.1 Generic Polysilicon PCE Fabrication    | 34        |

|   |             | 3.3.2 IC Fabrication Compatibility           | 46        |

|   | 3.4         | Summary                                      | 50        |

| 4 | Pol         | PCE Device Modeling                          | 53        |

|   | 4.1         | Circuit Approximation                        | 53        |

|   | 4.2         | Gap Resistance Model                         | 56        |

|   |             | 4.2.1 General Expressions                    | 56        |

|   |             | 4.2.2 Continuity Solutions                   | 57        |

|   |             | 4.2.3 Gap Geometry Modifications             | 60        |

|   |             | 4.2.4 Simplified Gap Resistance Model        | 62        |

|   | 4.3         | Model Verification                           | 64        |

|   |             | 4.3.1 DC Response                            | 66        |

|   |             | 4.3.2 Transient Response                     | <u>59</u> |

|   | 4.4         | Summary                                      | 72        |

| 5 | IC          | licrostrip Characterization 7                | '5        |

|   | 5.1         | Propagation on IC's                          | 75        |

|   |             | 5.1.1 General Microstrip Theory              | 76        |

|   |             | 5.1.2 High Frequency Microstrip Models       | 78        |

|   |             | 5.1.3 Picosecond Pulse Propagation           | 81        |

|   | 5.2         | Sampling Measurements for Model Verification | 32        |

|   |             | 5.2.1 Measurement and Simulation Techniques  | 82        |

|   |             | 5.2.2 Dispersive Propagation                 | 36        |

|   |             | 5.2.3 Propagation Velocity                   | 88        |

|   |             |                                              | 93        |

|   | 5. <b>3</b> |                                              | 95        |

| 6 | Sur         | mary and Conclusions 9                       | 97        |

| 2 | 6.1         | •                                            | 97        |

|   | 6.2         | •                                            | 99        |

|   |             |                                              |           |

|    | 6. <b>3</b> | Future Directions                   |

|----|-------------|-------------------------------------|

| A  | PCI         | E Model Equations 103               |

|    | A.1         | PCE Capacitances                    |

|    | A.2         | Effective Illuminated Area          |

|    | A.3         | PCF Model Circuit Analysis          |

| в  | PCI         | E Bandwidth Derivation 109          |

| С  | PCH         | E Fabrication Schedules 113         |

|    | C.1         | Poly PCE Fabrication Schedule       |

|    | C.2         | NMOS-Poly PCE Fabrication Schedule  |

| D  | MI          | CEM Program 127                     |

|    | D.1         | Simulation Overview                 |

|    | D.2         | Available Simulation Results        |

|    | D.3         | Computation Algorithms              |

|    | D.4         | User Interface                      |

|    |             | D.4.1 Output                        |

|    |             | D.4.2 Input                         |

|    | D.5         | Examples                            |

|    |             | D.5.1 Microstrip Loss Calculation   |

|    |             | D.5.2 Pulser PCE Response           |

|    |             | D.5.3 Cross-correlation Calculation |

| ם: | hlian       | non h.v                             |

#### Bibliography

# List of Tables

| 3.1         | Implant Species Parameters         | 2 |

|-------------|------------------------------------|---|

| 3.2         | Damage Profile Estimates           | 3 |

| 3.3         | PCE Operation Requirements         | 2 |

| <b>B</b> .1 | Photoconductor Bandwidth Estimates | L |

# List of Figures

20

| 2.1  | Auston Photoconductive Switch                                 | 8          |

|------|---------------------------------------------------------------|------------|

| 2.2  | Platte's Gap-shunt Structure                                  | 10         |

| 2.3  | Eisenstadt Bulk Silicon Switch                                | 11         |

| 2.4  | Electro-optic Sampling Structure                              | 13         |

| 2.5  | Generic thin-film photoconductor                              | 15         |

| 2.6  | Photoconductive gap circuit approximation                     | 16         |

| 2.7  | Theoretical photoconductive gap response                      | 17         |

| 2.8  | Optoelectronic measurement system block diagram.              | 20         |

| 2.9  | Impulsive pulse and sample system process                     | 21         |

| 2.10 | Idealized PCE waveforms and correlation                       | 22         |

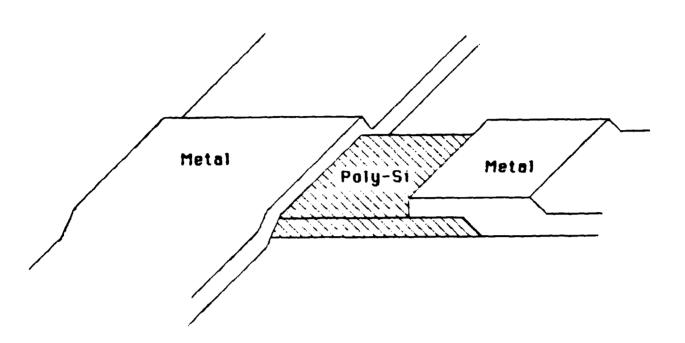

| 3.1  | Generic polysilicon PCE structure.                            | 27         |

| 3.2  | Modified polysilicon PCE structure for use as a sampling gate | 28         |

| 3.3  | Polysilicon PCE test structure                                | 29         |

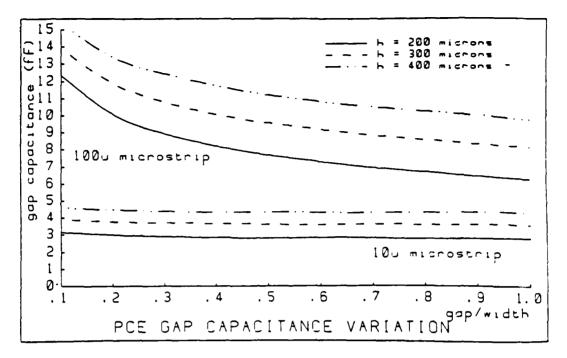

| 3.4  | PCE gap capacitance variation                                 | 31         |

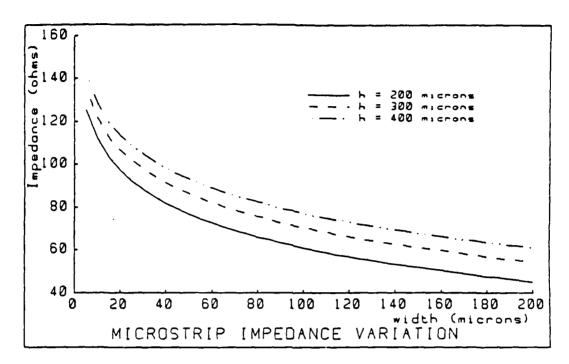

| 3.5  | Microstrip impedance variation                                | 32         |

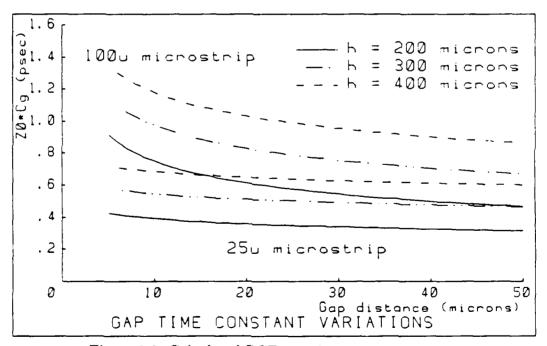

| 3.6  | Gap time constant                                             | 33         |

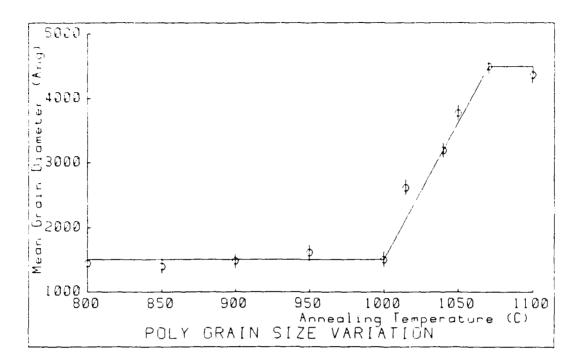

| 3.7  | Grain size variation                                          | 36         |

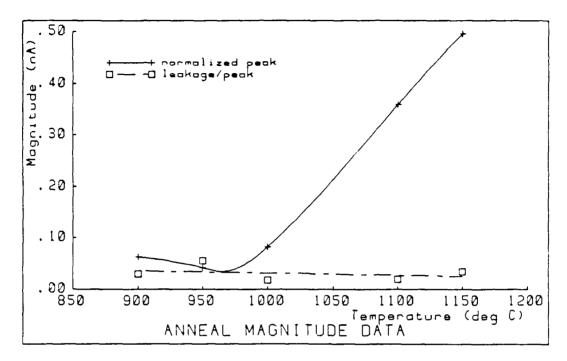

| 3.8  | Anneal magnitude data                                         | 37         |

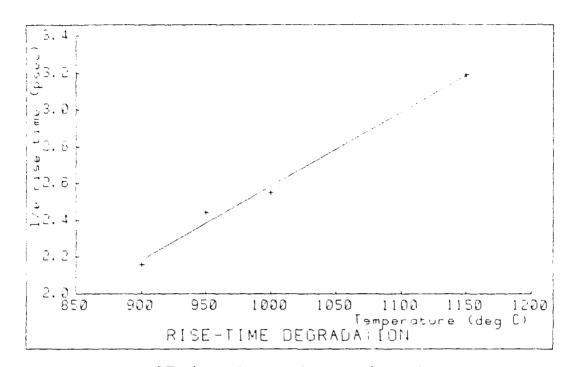

| 3.9  | Rise-time degradation                                         | <b>3</b> 8 |

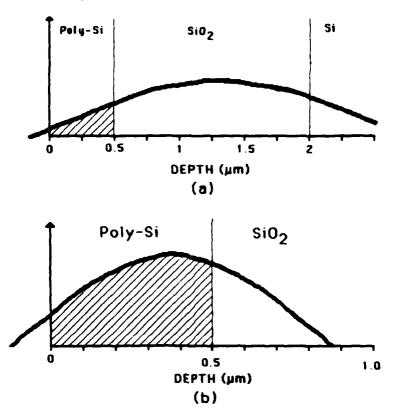

| 3.10 | Typical damage profiles                                       | 40         |

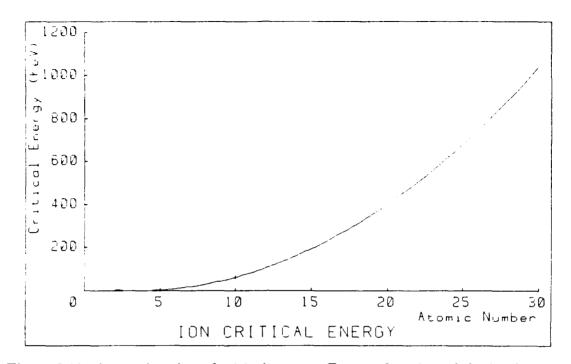

| 3.11 | Implant critical energy                                       | 41         |

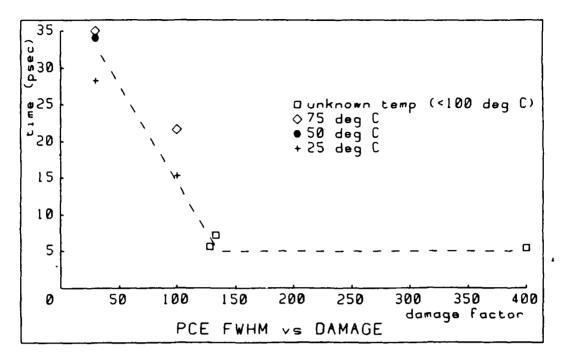

| 3.12 | PCE FWHM versus Damage                                        | 45         |

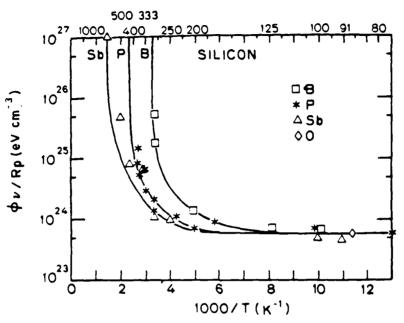

| 3.13       | Temperature dependence of amorphousation dose in silicon       | 46  |

|------------|----------------------------------------------------------------|-----|

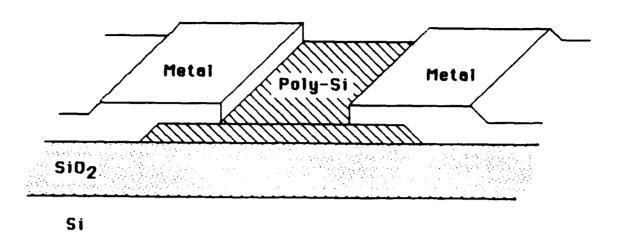

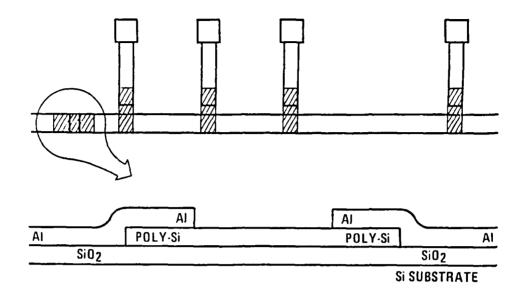

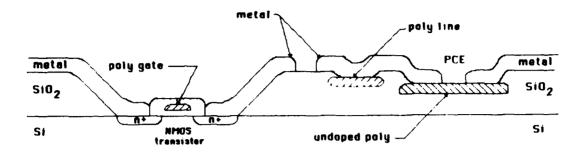

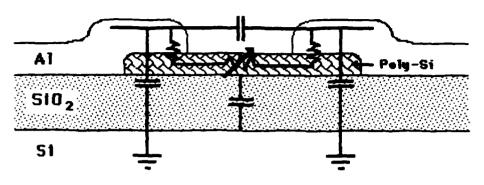

| 3.14       | Cross-section of an NMOS-polysilicon PCE integrated circuit    | 47  |

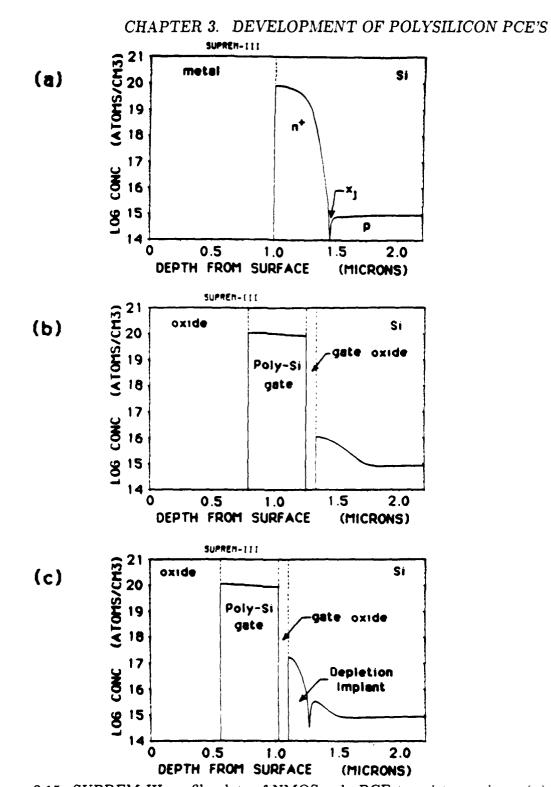

| 3.15       | SUPREM-III profile plots                                       | 48  |

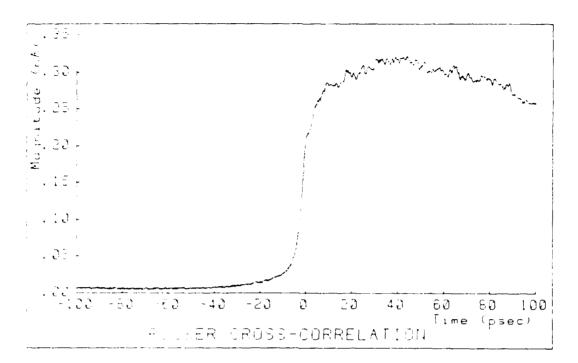

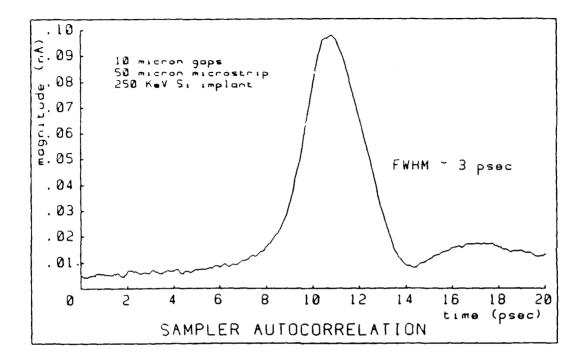

| 3.16       | NMOS-poly PCE cross-correlation measurement                    | 50  |

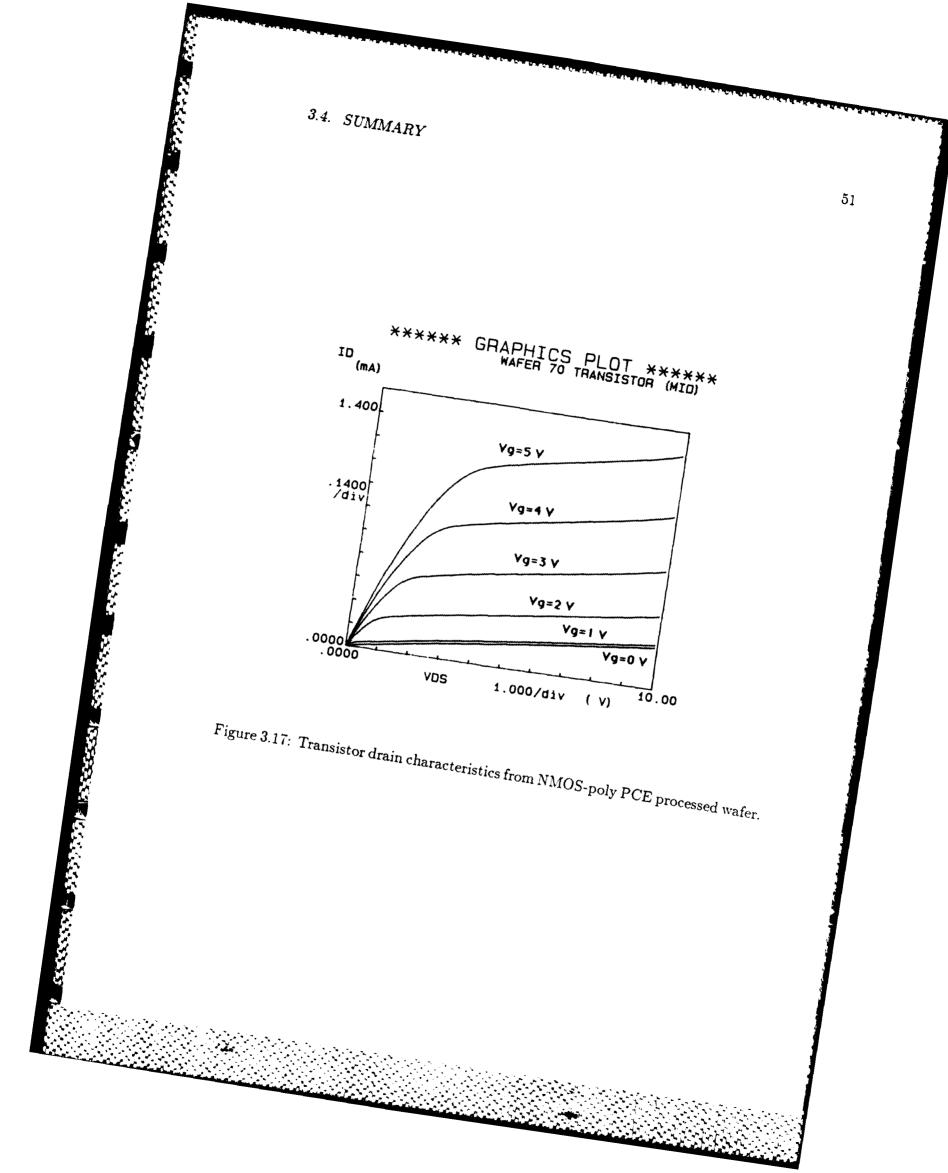

| 3.17       | NMOS-poly PCE transistor characteristics                       | 51  |

| 3.18       | Auto-correlation measurement of PCE's demonstrating a sampling |     |

|            | bandwidth in excess of 100 GHz.                                | 52  |

| 4.1        | Polysilicon PCE cross-section                                  | 54  |

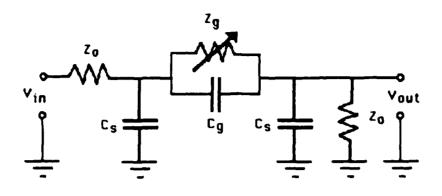

| 4.2        | First order PCE device circuit model.                          | 55  |

| 4.3        | Illuminated PCE                                                | 60  |

| 4.4        | Gap resistance calculations                                    | 63  |

| 4.5        | Gap Resistance Time Response                                   | 65  |

| 4.6        | Calculated PCE responses for varying recombination times       | 66  |

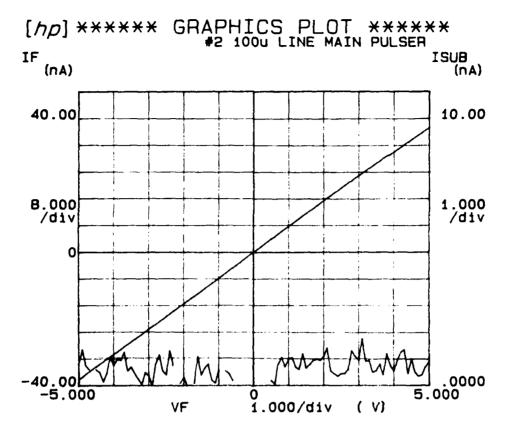

| 4.7        | Undamaged PCE I-V Curve                                        | 67  |

| 4.8        | Damaged PCE I-V Curve                                          | 68  |

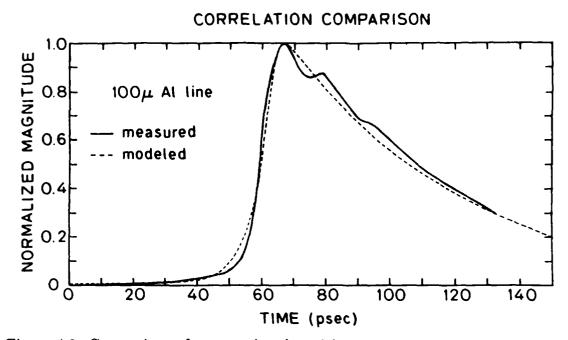

| 4.9        | Correlation comparison of measured and modeled data            | 70  |

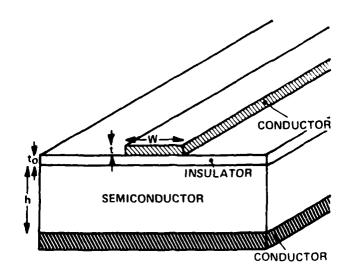

| 5.1        | Semiconductor Microstrip Structure                             | 76  |

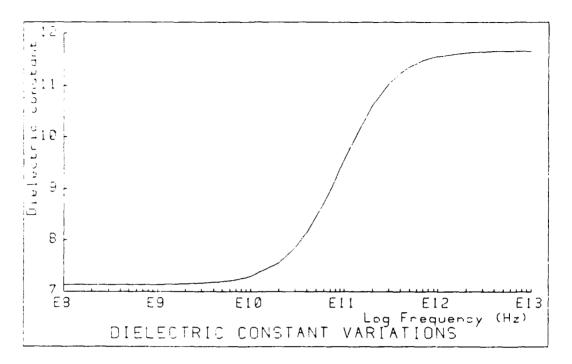

| 5.2        | Computed Frequency Dependent $\epsilon_{eff}$                  | 79  |

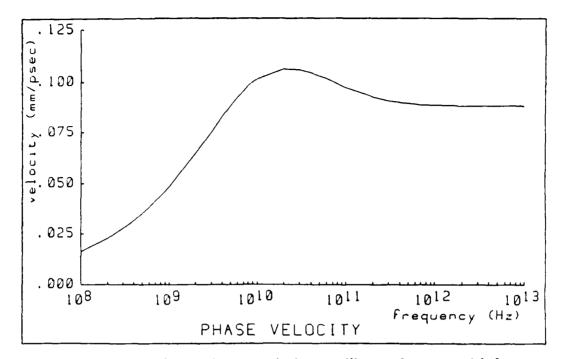

| <b>5.3</b> | Phase Velocity Variation                                       | 80  |

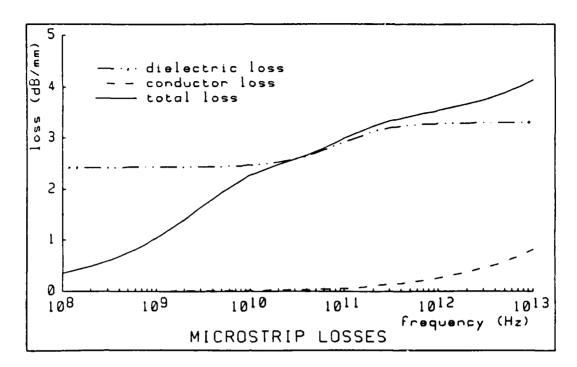

| 5.4        | Frequency Dependent Losses                                     | 81  |

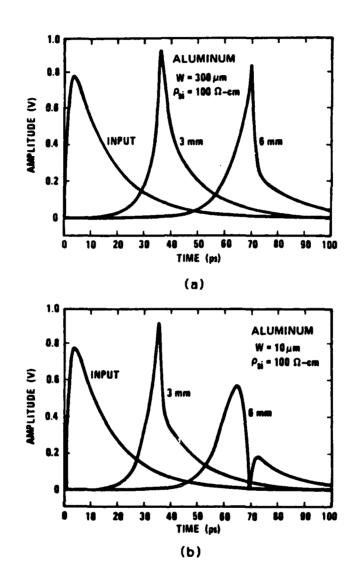

| 5.5        | Predicted Picosecond Pulse Propagation                         | 83  |

| 5.6        | High Frequency Waveform Propagation                            | 85  |

| 5.7        | Risetime Degradation Induced by Dispersion                     | 86  |

| <b>5.8</b> | 3.5 GHz Risetime Degradation Comparison                        | 87  |

| 5.9        | Pulse Propagation Delays                                       | 89  |

| 5.10       | 3.5 GHz Waveform Propagation Comparisons                       | 91  |

| 5.11       | 18 GHZ Waveform Propagation Comparisons                        | 92  |

| 5.12       | Microstrip Loss Comparison                                     | 94  |

| 6.1        | High Frequency Pulse Propagation                               | 100 |

J

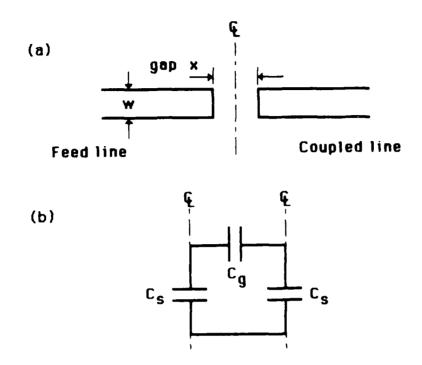

| A.1 | Microstrip series gap model                                       |

|-----|-------------------------------------------------------------------|

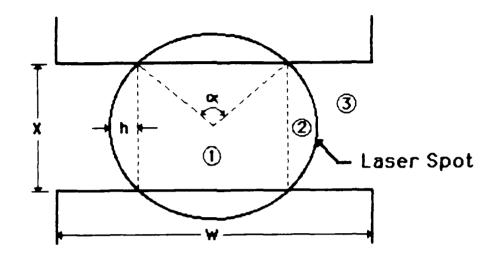

| A.2 | Focused laser spot for effective illuminated area calculation 106 |

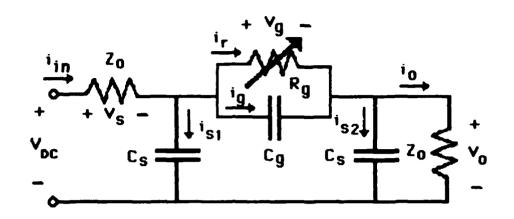

| A.3 | PCE model for circuit analysis                                    |

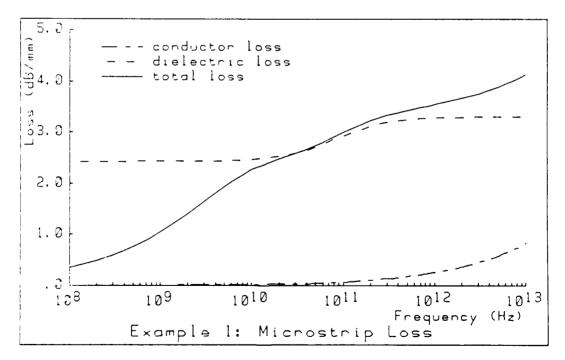

| D.1 | Example 1: Microstrip Loss                                        |

| D.2 | Example 2: Pulser PCE Response                                    |

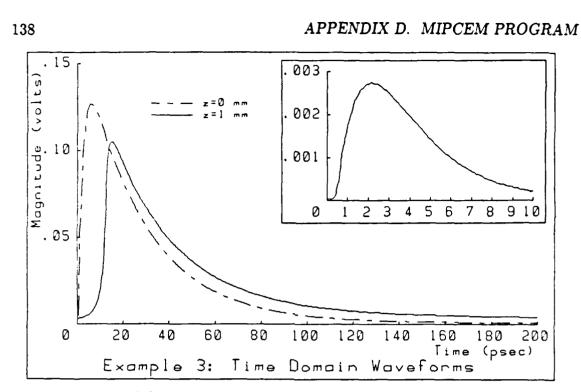

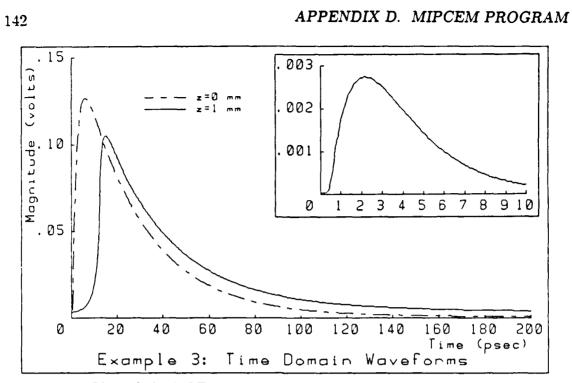

| D.3 | Example 3: PCE Waveforms                                          |

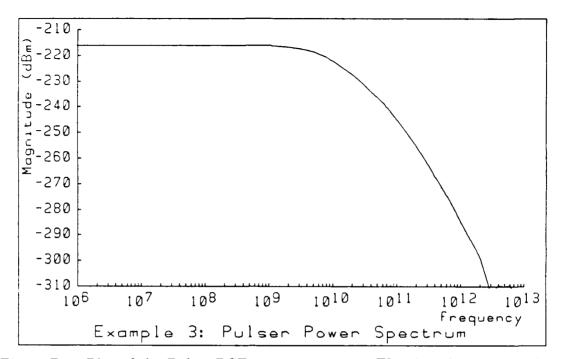

| D.4 | Example 3: Pulser Power Spectrum                                  |

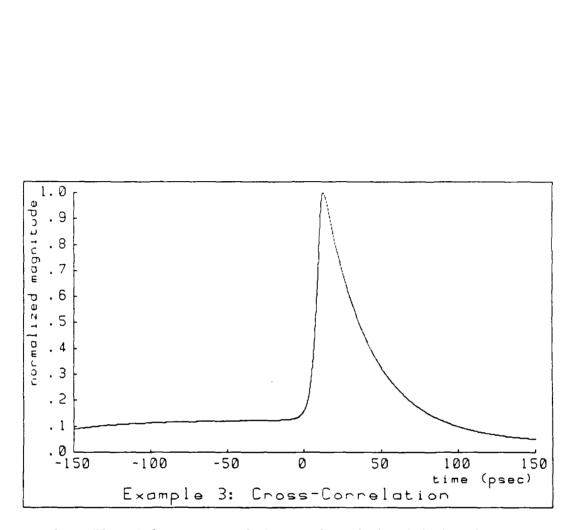

| D.5 | Example 3: Cross-correlation Results                              |

## Chapter 1

## Introduction

The push toward ever faster digital and analog integrated circuits is rapidly causing changes in circuit design requirements as designers attempt to take full advantage of high-speed devices. Accurate high frequency characterization of highspeed integrated semiconductor devices and interconnections is required to provide these designers with the necessary information to properly design very fast circuits. The research reported in this thesis resulted in a device for doing very high speed time domain measurements, in situ, on a silicon integrated circuit. This device is used to characterize interconnecting transmission lines on silicon IC's at microwave frequencies. The subsequent modeling allows for the exploration of an area critical to the improved performance of integrated circuits and VHSIC technology.

Several methods are available for semiconductor device characterization at microwave frequencies.[1.1] Most of these methods work adequately for discrete microwave devices and circuits, but cannot be readily adapted for monolithic IC analysis. This is due to the parasitics introduced by making off-chip high frequency connections and the lack of accurate on-chip references for use as calibration standards. The use of integrated photoconductors overcomes these difficulties and facilitates microwave measurements on silicon substrates with high S/N ratios and excellent sensitivity.

Integrated circuit interconnections are becoming the limiting factor in chip performance and present a serious roadblock to future speed improvements. Signal propagation delays can be as long as the device switching delays in fast circuits.[1.2] This trend becomes more severe as the minimum feature size is scaled down to submicron level and chip size is increased towards wafer scale integration.[1.3] Much effort is being expended to model and overcome the delay of the interconnections, but classic microwave measurement techniques are limited in their ability to verify these models. Picosecond integrated photoconductor measurements, however, have recently demonstrated the ability to make highly accurate picosecond measurements on silicon substrates.[1.4][1.5][1.6]

This thesis presents a description of the design, fabrication and modeling of integrated polycrystaline silicon photoconductors and measurement techniques for using them to make on-chip time domain measurements with subpicosecond resolution. Chapter 2 gives a presentation of previous work conducted in the area of pulsed laser measurements upon which this current research is based. Chapter 3 reports the development of polysilicon photoconductive circuit elements (PCE's) which are fully compatible with standard VLSI fabrication processes and demonstrate picosecond responses. Chapter 4 describes a first order device model developed to predict polysilicon PCE performance and compares the model with experimentally measured responses. This is then followed in Chapter 5 by an application of the PCE's to characterize high frequency pulse propagation on silicon IC interconnections. Finally, Chapter 6 summarizes the relative advantages of polysilicon PCE measurements on integrated circuits over other microwave measurement techniques and points out possible areas for future research.

### **1.1 Introduction to Pulsed Laser Measurements**

Laser technological advances have made possible the generation of subpicosecond optical pulses. Using these lasers measurements are possible that surpass the ability of purely electronic pulse generators to generate short duration pulses. [1.7][1.8][1.9] By using an optoelectric transducer, such as a high speed photoconductor, the very short optical pulses can be converted to picosecond electrical pulses. Proper design and use of photoconductive circuit elements can then lead to high frequency time

domain signal measurements similar to those which would be taken by a very fast sampling oscilloscope.

A variety of methods have been used to generate short electrical pulses from optical pulses. D.H. Auston and A.M. Johnson of Bell Laboratories first demonstrated the generation of picosecond pulses on silicon by using optically triggered gating in 1975. [1.10][1.11] Their early method used quasimetallic photoconductivity produced by the absorption of short optical pulses in silicon transmission line structures to both turn on and off a switching gap. Different wavelength laser beams were required for the on and off triggers in this configuration. Later methods eliminated the need for two different wavelengths [1.12][1.13] and explored the use of high defect density materials for use as photoconductors. [1.4][1.14] The advantages of high defect density materials come from the reliance upon recombination mechanisms for the turn-off transient. All of these optoelectronic switching methods demonstrated the very fast responses possible—the switching being limited primarily by the duration of the optical pulses available. In Chapter 2 the various optoelectronic systems previously employed are briefly discussed. These methods, particularly the latest work of Eisenstadt, provide the foundation upon which the development of the polysilicon PCE is based. A description of the laser measurement system used in this work is also provided.

## **1.2 Introduction to High-Speed Polysilicon PCE's**

The development of high speed photoconductors in thin film polycrystaline silicon comprises the bulk of the work reported in this thesis. The motivation behind using polysilicon for the PCE structure is to improve the compatibility of the fabrication process with standard IC fabrication schedules while achieving at least a factor of two improvement in PCE device performance. The resultant devices permit picosecond pulsing and sampling measurements on a silicon IC substrate with greater resolution than previously reported [1.15] while maintaining the desired fabrication compatibility. Two fabrication processes are developed: a generic polysilicon PCE process and an NMOS-PCE process. The generic PCE process demonstrates the ease with which the basic device can be fabricated. The NMOS-PCE process demonstrates PCE compatibility with other devices. Both of these process schedules are detailed in Appendix C. After fabrication, the PCE's are damaged by ion implantation with other active devices masked by photoresist. The thin-film polysilicon allows for a large reduction in the implant energy from that reported in previous works and insures other devices may be easily masked. A 200 femtosecond colliding-pulse mode-locked (CPM) ring dye laser is used to excite the PCE's and cause rapid conduction during measurements. Trapping sites in the damaged polysilicon cause high recombination rates and lead to a fast turn-off transient when the laser pulse is removed.

Depending upon the specific implant damage process, the PCE's demonstrate both pulse and sampling type responses. Pulser PCE's produce electrical pulses with circuit limited rise times of less than 2 psec and peak amplitudes of up to 500 millivolts for a 50 pJ optical pulse. Sampling PCE's demonstrate a 3-dB measurement bandwidth in excess of 100 GHz. Limited optimization of these sampling PCE's for speed is reported, however, it is felt that further development could lead to even higher cutoff frequencies.

Chapter 3 describes the development of the polysilicon PCE as an integrable device. Improvements over previous PCE performances are enumerated and discussion is presented of how these improvements are achieved with polysilicon PCE's. A description of the process compatibility considerations and their impact upon the NMOS-PCE fabrication schedule is also included.

A simple model to predict polysilicon PCE performance is developed in Chapter 4 and compared with experimental measurements of the devices. It is generally found that the PCE is limited in its speed by the transmission line in which it is embedded. Except at the highest frequencies, the first order model does very well at describing the device's time response.

#### **1.3. INTRODUCTION TO MICROSTRIP MEASUREMENTS**

## **1.3** Introduction to Microstrip Measurements

Characterization of microstrip transmission lines has been important since the beginning of microwave technology.[1.16] This type of interconnection is readily adapted for use in IC's and has proven reliable and easy to fabricate. Understanding the propagation characteristics of these transmission lines on IC substrates has not been a simple task [1.17][1.18] and as semiconductor devices have increased in speed, the limitations of microstrip have become an important consideration in IC performance. Understanding the impact the interconnections have on system performance is vital and the topic of much current research. [1.3][1.19][1.20][1.21][1.22] A goal of these investigators is the development of a model for IC interconnections. High frequency measurement data is vital in the development and validation of such a model and it is in this area that PCE time domain measurements can contribute.

A variety of microstrip transmission lines are fabricated on  $SiO_2/Si$  substrates with PCE's embedded as pulsers and samplers to measure propagation characteristics. These structures comprise a small sampling of the materials, shapes, and sizes of interconnections common to today's IC's. High frequency pulse propagation is measured with subpicosecond accuracy and comparisons made with classical quasi-TEM models. By using measured data for input to the transmission line models the predicted response at various distances can be obtained without the influence of the PCE response. This method results in a close agreement between the measurements and theoretical predictions.

Chapter 5 provides a description of the experimental high frequency characterization of IC interconnections using polysilicon PCE time domain measurements. The structures measured are compared to theoretical calculations based upon a variety of analytical models. Limitations observed in microstrip propagation models are discussed.

## 1.4 Discussion of Future Work

The development and use of the polycrystaline silicon PCE is by no means completed with the conclusion of this thesis. Future efforts envisioned include the exploration of different thin films for use as the photoconductive layer and tayloring the specific film to the type of application. Chapter 6 briefly explores some of the possible materials which may be used. In addition, the development of specific measurement techniques are postulated. These include further characterization of microstrip and ultimately the calculation of s-parameters from PCE time domain data. This is a new field with much room for innovative applications in the future.

## Chapter 2

## **Pulsed Laser Measurements**

The ability to generate ultrafast pulses using state-of-the-art lasers has opened up new possibilities for high speed optoelectronic devices. The use of optoelectronic transducers allows the superior speed of the laser to be converted to fast electrical pulses. Optoelectronic transducers have been developed on a variety of substrates and demonstrated picosecond switching speeds. D.H. Auston, in particular, has done much to characterize generic optoelectronic switches. This chapter reviews the development of picosecond optoelectronic switching with emphasis on the uses of such switches as sampling gates on silicon substrates.

### 2.1 Picosecond Optoelectronic Switching

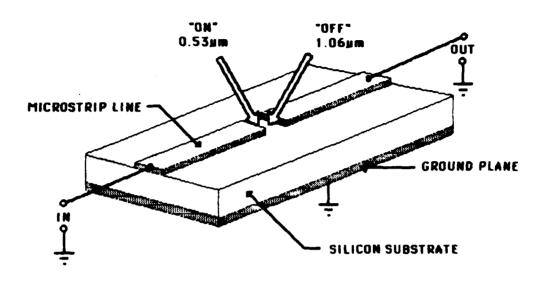

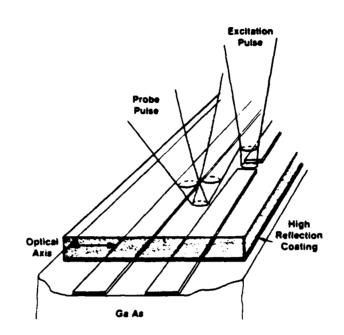

D.H. Auston and A.M. Johnson of Bell Laboratories first demonstrated the generation of picosecond pulses on silicon substrates in 1975 by using optically triggered gating. [2.1][2.2] They used quasimetallic photoconductivity produced by the absorption of short optical pulses in silicon transmission line structures to both turn on and off a switching gap. Figure 2.1 shows an optoelectronic switch using this technique. The 50  $\Omega$  microstrip transmission line is fabricated on high resistivity ( $\rho = 10^4 \ \Omega - cm$ ) silicon and contains a gap which forms the switch. The switching action is produced by two optical pulses generating mobile carriers within the silicon. One beam, in the green region of the spectrum at  $\lambda = 0.53 \ \mu m$ , is used to turn

Figure 2.1: Diagram of D.H. Auston's picosecond photoconductor using two different optical beams.[2.1]

the switch on while a second beam, in the infrared at  $\lambda = 1.06 \ \mu m$ , turns it off. The on/off effect of these two beams is caused by the different absorption properties in silicon of the two wavelengths. The green pulse has a large absorption coefficient  $(\approx 8 \times 10^3/cm)$  and produces only a thin surface layer of photoconductivity across the gap. Efficient transmission across the gap is achieved when the green pulse is sufficiently intense to produce a net gap resistance much less than  $Z_0$ , the characteristic impedance of the transmission line. The optical energy required varies as the square of the gap length. but is on the order of  $1 \ \mu J$  for typical structures. [2.2] The infrared beam is used to turn the switch off by effectively shorting the transmission line to prevent further transmission of an incident signal. This is possible because the absorption depth in silicon at this wavelength is large and the pulse penetrates through the substrate to the ground plane. A region of high conductivity between the upper and lower conductors is thus produced, creating the short.

Several advantages over pure electronic switching are immediately apparent in the use of this optoelectronic method. Unlike conventional semiconductor junction devices, recombination or carrier sweep out is not relied upon to achieve the switch action. The very fast response observed ( $\approx 15$  psec [2.2]) is therefore primarily

#### 2.1. PICOSECOND OPTOELECTRONIC SWITCHING

limited by the duration of the optical pulses used as triggering signals. Another advantage is that with the use of optical controlling pulses nearly perfect isolation exists between the switched and controlling signals. High power switches are readily formed since a reverse junction breakdown problem does not exist as with semiconductor junction switches.

The method of switching the microstrip gap employed by Auston in his earliest work also had some inherent disadvantages which became the driving force behind later improvements. A significant disadvantage is the repetition rate. Even though carrier recombination is not relied upon to switch the gap, the excess carriers generated by the switching action must either be swept out or allowed to recombine before the switch can be used again. This generally limits the repetition rate to less than 1 MHz.

Early efforts at improving the switching method of Auston and Johnson centered around simplifying the complex optical structure needed to generate the required synchronous pulses at two different frequencies which are used to perform the switching. This involved attempts at using a single frequency for both the turnon and turn-off pulses. In 1976, two basic structures which accomplished this were proposed: a gap-shunt structure (by W. Platte[2.3]) and a coplanar structure (by R. Castagne et al. [2.4]).

The gap-shunt structure, shown in Figure 2.2, allows for the use of a single frequency ( $\lambda = 0.906 \ \mu m$  in Platte's experiment) for both pulses and requires only a variable delay between the on and off pulses. This delay is easily realized by changing the distance covered by the second pulse (the turn-off pulse) with a translation stage and greatly simplifies the optical setup. The switching action is performed in the same manner as Auston's technique except that the shorting path is now to a grounded structure brought around to the surface of the silicon instead of through the substrate. This facilitates the use of a wider range of optical pulse frequencies. The only constraint placed upon the pulse frequency choice is that the absorption depth at the frequency must be significantly less than the substrate thickness to avoid having the turn-on pulse short the transmission line to the ground plane on the back of the substrate. As with the two beam technique, repetition rate

Figure 2.2: Gap-shunt structure used by W. Platte as a modification to Auston's basic switch.[2.3]

is limited to less than 1 MHz due to the need to sweep out or recombine the optically generated carriers prior to using the switch again.

A coplanar transmission line is another structure which can use a single frequency laser source for both beams. The theory of operation is the same as with the gap-shunt structure used by Platte. Switching is performed in exactly the same manner, with one side of the center conductor being shorted to ground (either outside conductor of the coplanar layout) to turn off the switch. Both of these single frequency structures provide switching speeds on the order of two times the rise time of the optical pulses used to control the switch. [2.3][2.4]

After simplification of the optical setup, the next improvements in picosecond optoelectronic switching came with modifications to the substrate so that the second, turn-off, pulse became unnecessary. Auston et al. reported the success of a single beam technique in 1980 using high-defect-density amorphous silicon. [2.5] With this new substrate the speed of response of the gap switch is determined by the relaxation of the photocurrent in the structure. The relaxation time in highdefect-density amorphous films is very short due to the trapping action exhibited

10

### 2.1. PICOSECOND OPTOELECTRONIC SWITCHING

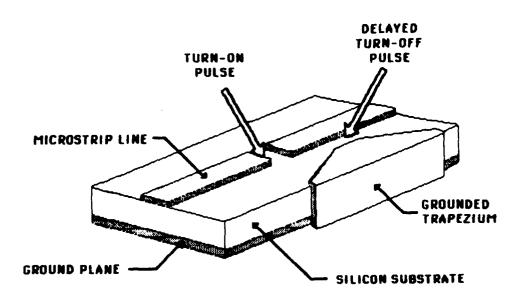

Figure 2.3: Photoconductor test structure used by W.R. Eisenstadt et al. on bulk silicon.[2.8]

by the defect sites. The rapid recombination of carriers (measured as  $\approx$  3-5 psec in [2.5]) is relied upon to turn off the switch instead of using a second beam. Auston's experiments with this technique and switching structures similar to his earlier work (Figure 2.1) resulted in autocorrelation measurements with a full width at half magnitude (FWHM) of 11 psec when triggered with a 3.5 psec optical pulse ( $\lambda = 0.58 \ \mu m$ , incident energy= 0.37 nJ/pulse). This corresponds to a switching response approximately two times broader than the triggering optical pulse. The circuit response of the gap causes a slight asymmetry in the switched pulse and is the predominant factor in limiting the switching speed. (See Section 2.2.2)

The work on amorphous silicon has been extended by W.R. Eisenstadt and R.B. Hammond to produce picosecond optoelectronic switches on bulk silicon. [2.6][2.7] Their effort was geared towards the production of high speed photoconductors which can be integrated along side of other devices on an integrated circuit using standard VLSI fabrication techniques. The photoconductors were fabricated directly on 70  $\Omega$ -cm, < 100 > oriented, n-type Si wafers, similar to wafers used in standard device fabrication. Aluminum microstrip structures were placed on a field oxide with gaps and oxide cuts used to form the photoconductive switch area. (See Figure 2.3). To achieve the rapid recombination required for turn-off, the wafers were ion bombarded with 30 MeV oxygen to locally damage the crystal lattice. This provided the trapping sites needed for rapid carrier recombination after the laser pulse was removed. High energy ions were used to insure that the damage was deep enough to collect carriers generated deep in the substrate under the switch. The switching action of these structures was measured to be on the order of 30 psec FWHM with very short ( $\approx 2$  psec) risetimes [2.6]. As with the amorphous silicon switches, the speed of response appeared to be limited by the circuit response of the gap.

### 2.2 Optoelectronic Sampling

The very fast pulses associated with optoelectronic switches triggered by the fast pulse lasers which have become available, lend themselves readily to high speed sampling applications. Several optoelectronic and electro-optic methods have been demonstrated and performance is generally better than the fastest sampling oscilloscope available commercially. These experimental sampling systems allow for time domain measurements on a sub-picosecond scale with excellent sensitivity.

### 2.2.1 Electro-optic Methods

The use of electro-optic crystals or the electro-optic effect of the substrate is one technique for using high speed laser pulses to sample voltage waveforms on integrated circuits. The electro-optic effect, which is prevalent in such crystals as gallium arsenide (GaAs), lithium niobate (LiNbO), and lithium tantalate  $(LiTaO_3)$ , is a property of the crystal which causes the optical properties of the material to be modified in the presence of an electric field. The manner in which a laser pulse is modified by the birefringence as it passes through such a material can be directly related to the presence and strength of the electric field. J.A. Valdmanis et al. successfully used both  $LiTaO_3$  and LiNbO in sampling systems which achieved a temporal resolution of less than 5 picoseconds. [2.9] K.S. Weingarten et al. have made use of the intrinsic electro-optic properties of gallium arsenide to sample high speed GaAs circuits.[2.10] In one method, shown in Figure 2.4, a GaAs crystal with correct optical orientation is placed on top of the integrated circuit and used

#### 2.2. OPTOELECTRONIC SAMPLING

Figure 2.4: Electro-optic sampling method demonstrated by K.J. Weingarten et al. on GaAs.[2.10]

as the sampling medium. The electric field from the IC transmission line couples into this crystal and is then sensed by the laser pulse being used as a probe. If the substrate is correctly oriented the use of the second crystal can be eliminated and the substrate probed directly. A polarizer converts the change in polarization of the probe laser pulse into a change in intensity which can be easily monitored with a slow photodetector. Measurements of a GaAs MESFET traveling wave amplifier and an 8-bit multiplexer/demultiplexer have been reported using this method. [2.10]

For materials which do not have a strong electro-optic effect the method of sampling with the second crystal on top of the substrate must be utilized. Silicon is such a material. In this case an electro-optic crystal such as  $LiTaO_3$  is placed over the substrate at the point where sampling is to be done. The electric field from the propagating voltage pulse couples into this crystal, which replaces the air dielectric over the transmission line, and is sensed by the laser pulse in the same manner as described above for gallium arsenide. In either case, care must be taken in selecting the laser system to insure that the the photon energy is well below the band gap

energy of the electro-optic medium. This is necessary to allow the laser pulse to pass through the medium rather than be absorbed by it.

### 2.2.2 Integrated Optoelectronic Samplers

The integration of very high speed optoelectronic transducers within an integrated circuit has some inherent advantages over electro-optic sampling. For substrates without pronounced electro-optic effects, such as silicon, it allows for the exact placement of the sampling location at the time of fabrication rather than relying upon crystal placement during sample preparation. Also, by not using a separate material (the electro-optic crystal) the unknown effect of coupling the field through a different dielectric is removed and a more accurate representation of the actual voltage waveform may be obtained. Care must be taken in the design of the transducers, usually photoconductive switches, to insure that they do not alter the measured circuit performance. When not triggered and even when "on" the pertabation on the circuit from these devices must be negligible.

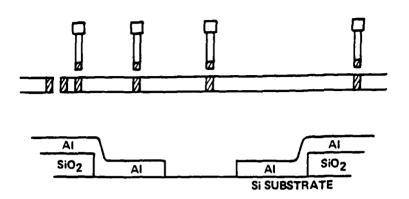

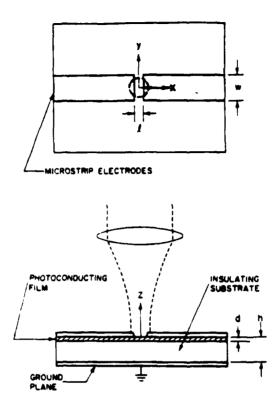

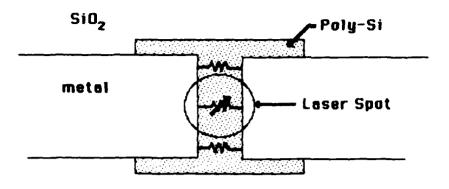

For simplicity of fabrication and operation, the Photoconductive Circuit Element (PCE) is the best laser driven optoelectronic transducer for sampling applications to integrate on a silicon substrate. The PCE itself is just a rectangular area of photoconductive semiconductor with metal transmission lines contacting the opposite sides of the rectangle. (See Figure 2.5). The PCE must have an extremely low conductivity between the metal lines when not illuminated by a laser pulse and a high conductivity when stimulated. Thus, the semiconductor material in which the PCE is fabricated must have a low conductivity and, therefore, a low doping level. Materials with greater than 10  $\Omega$ -cm resistivity have been shown to be acceptable for PCE use.[2.12]

For successful operation of an integrated PCE several features are desired. The primary goal is to achieve an ideal impulsive sampling gate using the PCE. As such, the unilluminated resistance of the switch must be several orders of magnitude greater than the highest resistance expected to be sampled from. This insures a minimum of leakage will occur during dark (off) periods and does not require the circuit designer to consider the PCE's impact upon the circuit performance, as it

#### 2.2. OPTOELECTRONIC SAMPLING

Figure 2.5: Schematic diagram of a generic thin-film photoconductor constructed in a microstrip transmission line.[2.11]

is effectively isolated from the circuit. To approximate impulsive sampling, the effective on time must be very short compared to the length of the event being sampled (At least an order of magnitude faster is desirable.) The effective on time is dependent upon the resistance of the circuit being sampled, ie when the resistance of the PCE becomes low enough to draw some percentage of the current relative to the circuit, it is considered on. To compensate for this circuit dependency, the turn-on and turn-off transients should be very rapid. This minimizes the differences in effective on time between circuits of different resistivities and is important in standardizing PCE performance across a chip or wafer. Another consideration in the design of PCE's is that the minimum on resistance should be small so as to generate a large sampled signal from even a weak input waveform, but not so low as to have a serious impact upon the circuit being sampled.

#### CHAPTER 2. PULSED LASER MEASUREMENTS

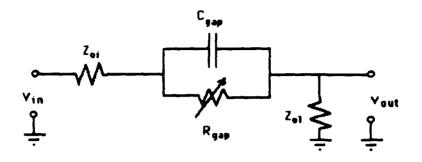

Figure 2.6: Circuit approximation of a photoconductive gap in a microstrip transmission line.

A simple device circuit model for the generic PCE shown in Figure 2.5 can be developed independent of the actual construction, when only considering first order effects. In this case the parasitics from the specific geometry can be ignored and the circuit of Figure 2.6 gives a good approximation for the PCE. In this circuit  $Z_{0i}$  and  $Z_{0l}$  represent the characteristic impedance of the transmission lines contacting the photoconductive region. The gap itself is modeled as a fixed capacitance between the ends of the transmission lines and a variable resistance modulated by the optical energy introduced via the laser pulse. Parasitic capacitances generally exist between the ends of the transmission lines and the substrate but these only have a second order effect and will be ignored until Chapter 4 when a model for the specific case of the polysilicon PCE is developed. Auston has analyzed the generic PCE model for a variety of configurations and found that an upper limit upon switching performance is set by the circuit limitations of the PCE gap capacitance and transmission line impedance. [2.11] As shown in Figure 2.6 the effective load seen by the PCE is the characteristic impedance of the transmission line in which it is imbedded. Focussing on the instantaneous charge, q(t), on the gap capacitance, Auston has shown that the reflected and transmitted waveforms for an arbitrary incident signal,  $v_i(t)$ , are expressed by Equations 2.1 and 2.2 respectively.

$$v_r(t) = \frac{1}{2C_g}q(t)$$

(2.1)

### 2.2. OPTOELECTRONIC SAMPLING

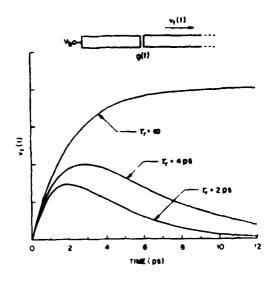

Figure 2.7: Predicted response of a photoconductive gap with varying carrier recombination times.[2.11]

$$v_t(t) = v_i(t) - \frac{1}{2C_g}q(t)$$

(2.2)

For the specific case of a DC bias of value  $V_b$  and a single exponential photoconductance, the transmitted signal is of the form:

$$v_t(t) = \frac{g_0 V_b}{2C_g} \left| \frac{e^{-t/\tau_r} - e^{-t/\tau_c}}{\frac{1}{\tau_c} - \frac{1}{\tau_r}} \right|; t \ge 0$$

(2.3)

where  $\tau_c = 2Z_o C_g$ ,  $\tau_r$  is the carrier relaxation time, and  $g_o$  the maximum conductance.

Figure 2.7 shows the time response of the generic PCE as described by Equation 2.3 for varying relaxation times. Note that the peak amplitude of the signal is reduced as  $\tau_r$  decreases and the peak delayed from the impulsive optical excitation assumed to occur at time zero.

The production of an electrical pulse from an optical one within the PCE is a very complex physical process which must be modeled if the magnitude of the transmitted pulse is to be determined. Several simplifying assumptions must initially be made if the task of understanding the laser pulse interaction with the PCE is to be made manageable. These assumptions include: 1) the laser pulse is short enough to appear as an impulse to the PCE so that the laser delivers an impulse of optical energy which generates electrical carriers, 2) the laser is perfectly focused on the test substrate so that optimal energy transfer is obtained, and 3) the PCE absorbs all the light which is incident upon it. Describing the electrical operation of the PCE is simplified by assuming: 1) the connecting transmission lines make perfect ohmic contacts with the photoconductive region, 2) no significant surface charge effects are present, and 3) bulk recombination governs the PCE carrier lifetimes. These last three assumptions are the conditions most desirable for proper PCE electrical operation and enable PCE measurements to achieve large signal to noise ratios. [2.13] In Chapter 4 some of the laser assumptions will be reconsidered when a more rigorous model is developed.

If it is also assumed that one electron-hole pair is generated in the PCE gap by each incident photon, then the PCE resistance, mobility and peak current can be derived from the laser pulse energy and photon energy. For a laser with pulse energy, E, and photon energy,  $E_p$ , it can be shown that the on-resistance for the PCE,  $R_{on}$ , is represented by Equation 2.4, where w is the width of the PCE gap,

$$R_{on} = \frac{w^2 E_p}{q(\mu_n + \mu_p)(1 - R)E}$$

(2.4)

$\mu_n$  and  $\mu_p$  the electron and hole mobilities respectively, R the surface reflectivity, and q the electronic charge. A desirable factor concerning PCE control is shown by this equation. Geometry, in the form of the gap width, and laser energy have a significant controlling effect upon the on-resistance of the PCE. This makes the PCE structure much easier to taylor to a specific application over a wide range of resistances independent of the photoconductive material chosen for its fabrication.

$$I_{max} = \frac{q(\mu_n + \mu_p)(1 - R)EV_b}{w^2 E_p}$$

(2.5)

The maximum current generated by the laser pulse due to conduction from the photogenerated carriers can be calculated by dividing the bias voltage applied to one side of the gap by the on-resistance of Equation 2.4.  $I_{max}$ , the peak current if the conductance is a step response is then represented by Equation 2.5 where  $V_b$  is the bias across the gap.

# 2.2.3 PCE Measurement System Considerations and Implementation

From the above discussion of PCE performance and the assumptions leading to the analysis, limitations upon the nature of the optical excitation become apparent. The choice of an excitation source has a significant impact upon the PCE performance. With the type of geometries considered in this research, the circuit limitations on the PCE result in a time constant on the order of 2 picoseconds. To insure that the laser pulse appears as an optical impulse to the PCE thus requires an ultrashort pulse width (< 1 psec). This criteria removes the requirement to consider the laser pulse shape when determining the PCE response. A second consideration when selecting an optical source for excitation is the photon energy. To enable the laser pulse to create electron-hole pairs in the semiconductor material chosen for the photoconductor, the photon energy must be above the semiconductor's band gap energy. Higher energies are desirable since if the photon energy is well above the band gap then carrier generation will be confined to the surface or within the thin photoconductive layer. Deep generation adds to the time needed to remove the excess carriers and can significantly slow the PCE turn-off transient.

The colliding pulse mode-locked (CPM) ring dye laser is one optical source which meets the requirements for use in a PCE system. It has the demonstrated ability to generate 55 femtosecond pulses with optical compression techniques[2.14] and operates typically at a wavelength of 610 nm. This wavelength has a photon energy well above the band gap energy of most semiconductor materials used in integrated circuits and does not limit the choice of photoconductive layers. To operate, the CPM laser employs two counter-rotating beams of pulses propagating along the same optical path within the laser cavity. The pulses are timed to arrive simultaneously at a saturable absorber placed in their paths. This absorber produces a shorter set of optical pulses via a non-linear transient grating effect.[2.15]

The specific laser system used in this research is a CPM dye laser located at the Los Alamos National Laboratory. This laser is capable of producing 200 femtosecond FWHM pulses at a 125 MHz repetition rate and with optical energies

#### CHAPTER 2. PULSED LASER MEASUREMENTS

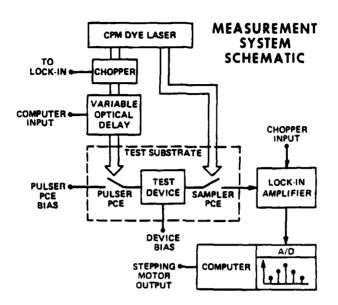

Figure 2.8: Optoelectronic measurement system block diagram.

in excess of 100 pJ. Figure 2.8 is a block diagram of the system used for PCE measurements. The CPM laser generates two synchronous pulse trains. One pulse train is passed through a mechanical chopper which turns the pulsed beam on and off at a fixed interval. The frequency of the chopper is fed directly to a Princeton Applied Research lock-in amplifier (Model 124A) for synchronization to insure that the PCE output charge is only measured in a low noise region. This pulse train also passes through a computer controlled translation stage to introduce a variable optical delay. The translation stage introduces a difference in path lengths which corresponds to a difference in the time of arrival of the laser pulses on the test substrate.

The test substrate shows two PCE's. One is biased and used as a pulser to provide an impulsive input to the device under test. This causes a transient response which is sampled by the second PCE. The sampling PCE is sampling charge from the output waveform at a constant difference in time from the pulser PCE as determined by the beam arrival times on the substrate. This sampled charge is integrated by the lock-in amplifier over many events and provided to an IBM PC for data display

#### 2.2. OPTOELECTRONIC SAMPLING

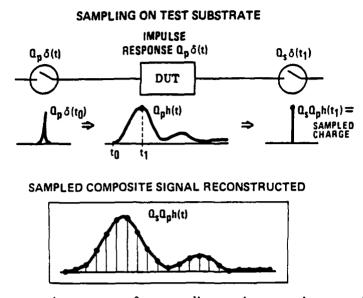

Figure 2.9: Reconstruction process for sampling a time varying waveform with an impulsive pulse and sample system.

and storage via an analog-to-digital converter. The data represents the output waveform at a single point in time. By varying the relative arrival times of the laser beams with the translation stage, the entire pulse response of the test device can be reconstructed as shown in Figure 2.9. This capability provides an extremely fast, low noise, sampling oscilloscope type trace when displayed after an entire sweep. Averaging data over multiple sweeps of the time range can also be done to further reduce any random noise present in the measurement.

When attempting to characterize the response of a device which is fast enough to negate the assumption of impulsive sampling, the above description does not adequately demonstrate the nature of the final output trace. This is the case when PCE's are used to measure their own response. The test device in Figure 2.8 is replaced by a short microstrip transmission line so that only the response of the PCE's themselves can be measured. The result is known as a cross-correlation measurement (or autocorrelation if two identical structures are used) and is commonly used in the field of lasers to measure extremely short duration optical pulses.

Eisenstadt et al. idealized the PCE response and illustrated the nature of the resultant cross-correlation waveform.[2.6] To achieve the idealized PCE waveform

CHAPTER 2. PULSED LASER MEASUREMENTS

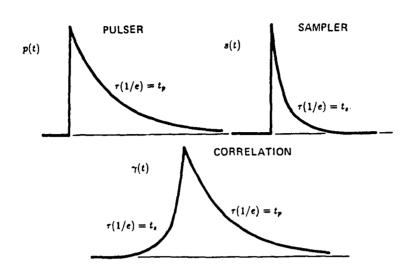

Figure 2.10: Idealized PCE waveforms with the resultant cross-correlation. [2.6]

the rising transient is assumed to be a step, followed by a decaying exponential. Hwang et al. showed that the decaying (turn-off) transient is at least a double exponential.[2.16] A reasonable approximation is, however, achieved by the use of a single time constant exponential decay. Given the resultant idealized PCE response and generalizing the functions such that the pulser and sampler PCE's have different characteristic decay times ( $\tau_p$  and  $\tau_s$  respectively) then Equation 2.6 shows the crosscorrelation function,  $\gamma(t)$ . From this equation it is seen that the exponential decay of the sampling PCE waveform is mirrored by the left side of the cross-correlation peak while the pulser PCE waveform is equivalent to the right side. This is shown graphically in Figure 2.10.

$$\gamma(t) = \begin{cases} \frac{\tau_{\bullet} \tau_{p}}{\tau_{\bullet} + \tau_{p}} e^{\frac{t}{\tau_{\bullet}}} & t < 0 \\ \\ \frac{\tau_{\bullet} \tau_{p}}{\tau_{\bullet} + \tau_{p}} e^{\frac{t}{\tau_{p}}} & t > 0 \end{cases}$$

$$(2.6)$$

22

As expected, actual PCE cross-correlation measurements vary from this ideal. As will be seen in the measurements presented in the following chapters, the most obvious differences lie in the rounding of the peak. This is due to the finite rise times actually observed in the experimental devices.

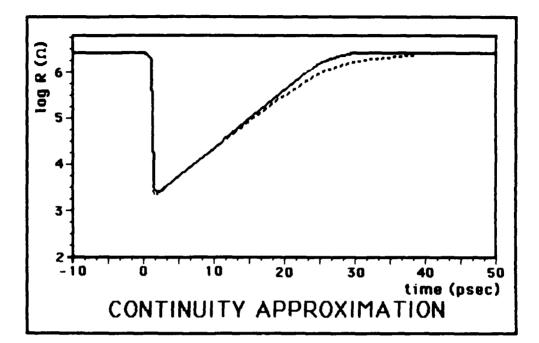

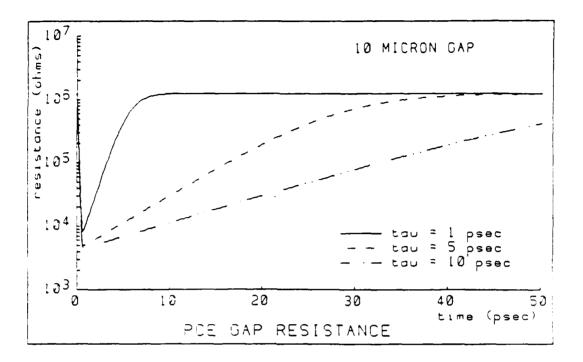

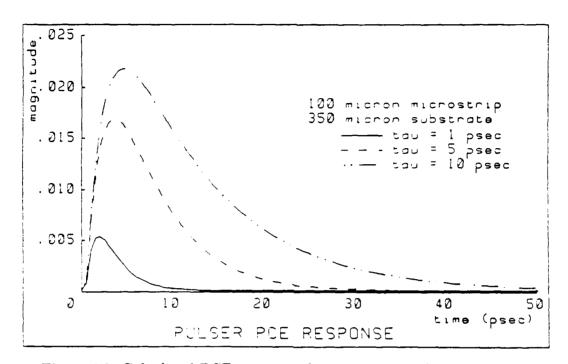

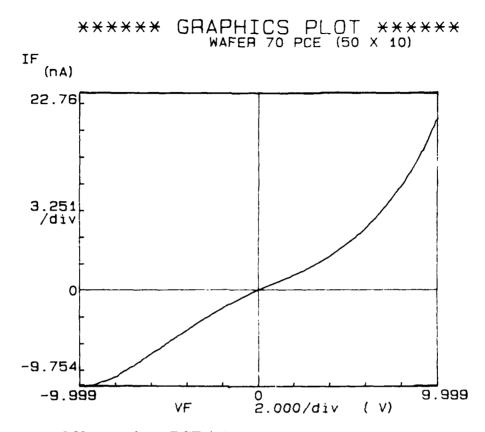

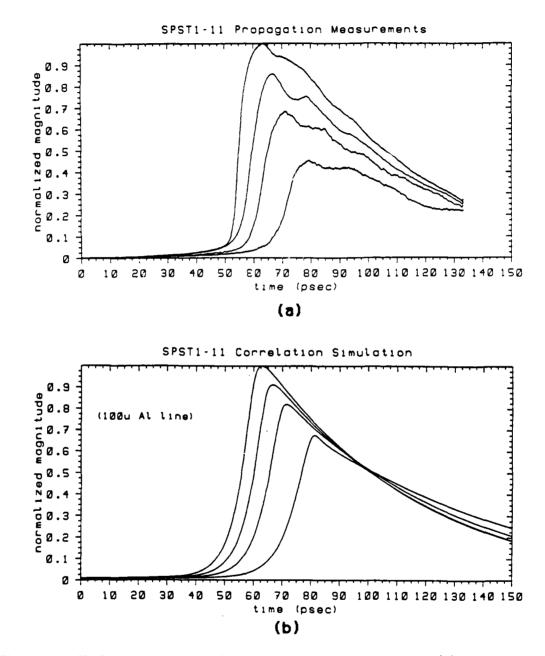

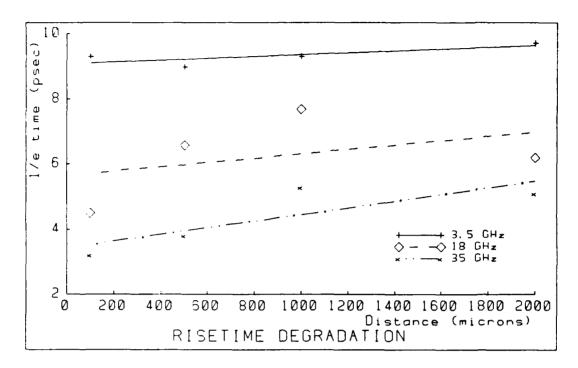

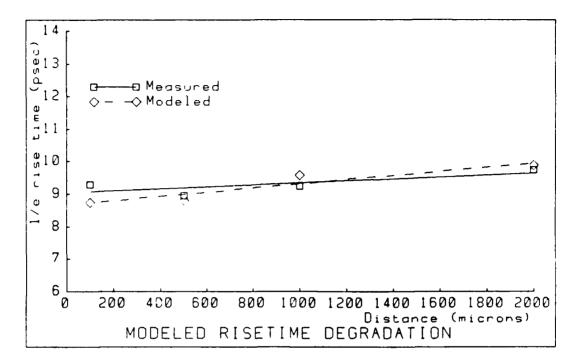

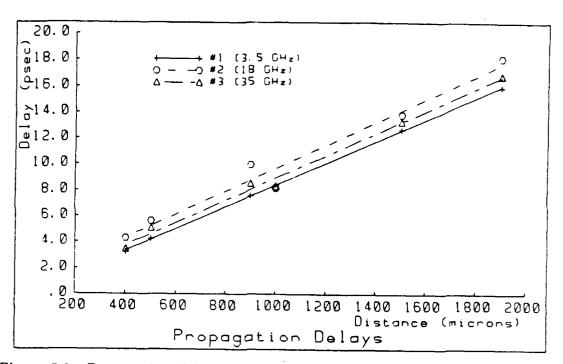

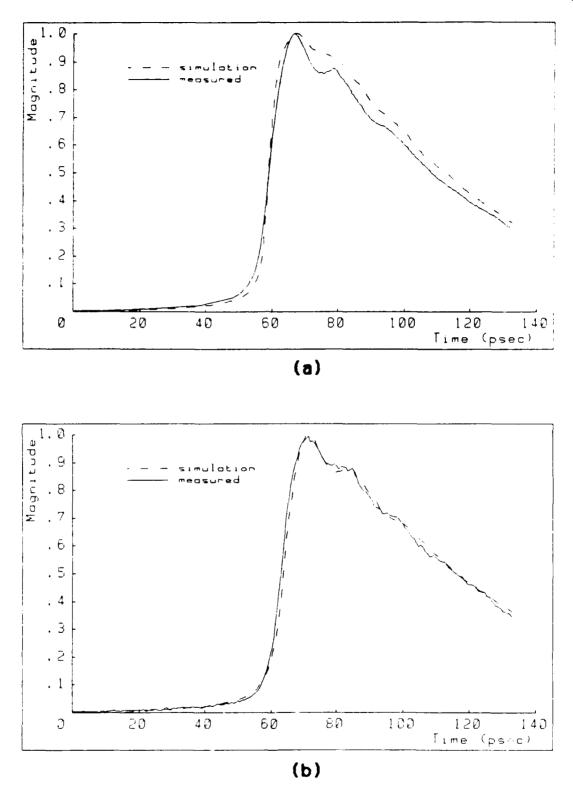

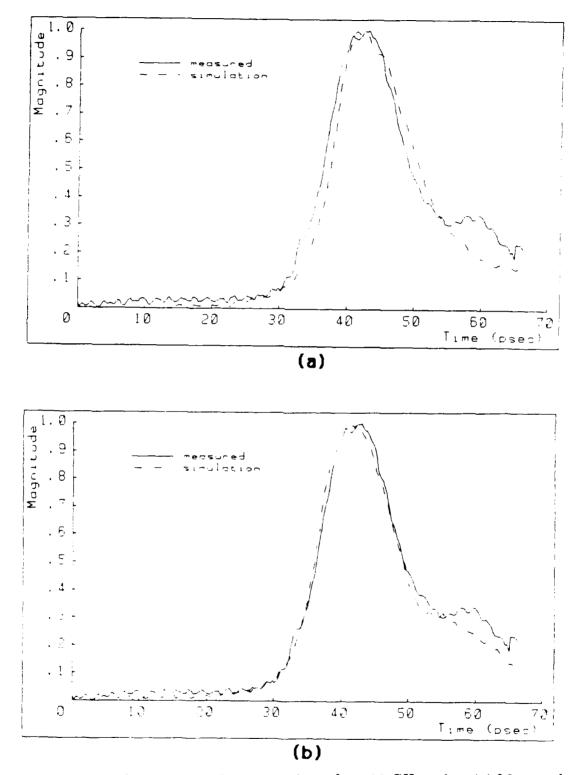

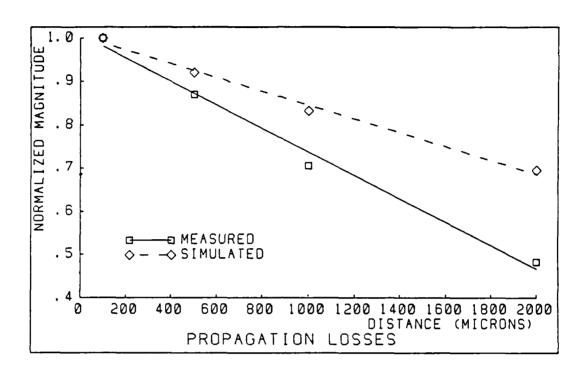

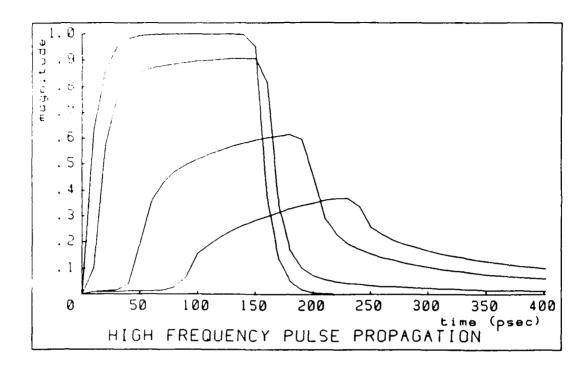

## 2.3 Summary