| SIFIED | > MAR       | 86 AF | ELEL  | IKICHL  |        |        | <b>.</b> | TOMTE                           |       |            |    |  |

|--------|-------------|-------|-------|---------|--------|--------|----------|---------------------------------|-------|------------|----|--|

|        |             |       | -Tol: | 98. 17- | EL DAA | G29-84 | 2-K-81   | ESSING<br>LAFAYE<br>JAMIE<br>01 | F/G S | HL.<br>7/2 | NL |  |

|        | -<br>- 3-0, |       |       |         |        |        |          |                                 |       |            |    |  |

|        |             |       |       |         |        |        |          |                                 |       |            |    |  |

|        |             |       |       |         |        |        |          |                                 |       |            |    |  |

|        |             |       |       |         |        |        |          |                                 |       |            |    |  |

|        |             |       |       |         |        |        |          |                                 |       |            |    |  |

|        |             |       |       |         |        |        |          |                                 |       |            |    |  |

|        |             |       |       |         |        |        |          |                                 |       |            |    |  |

|        |             |       |       |         |        |        |          |                                 |       |            |    |  |

NICROCOP

CHART

18790.17.EC

# AD-A167 315

# Distributed Computing for Signal Processing: Modeling of Asynchronous Parallel Computation

# **Final Report**

L.H. Jamieson, H.J. Siegel, P.H. Swain, G.B. Adams III, J.T.Kuehn, W.E. Kuhn III, G-M. Lin, R.J. McMillen, T.A. Rice, R.R. Seban, B.W. Smith, K.D. Smith, D.L. Tuomenoksa

March 1986

U.S. Army Research Office Contract No. DAAG29-82-K-0101

School of Electrical Engineering Purdue University West Lafayette, Indiana 47907

Approved for public release; distribution unlimited.

ELECTE Apr 2 9 1990

D

| REPORT DOCUMENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                     |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| REPORT NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2. GOVT ACCESSION NO.                                                                                                                                                                                                                                                                                                      | BEFORE COMPLETING FORM<br>3. RECIPIENT'S CATALOG NUMBER                                                                                                                                             |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | N/A                                                                                                                                                                                                                                                                                                                        | N/A                                                                                                                                                                                                 |  |

| TITLE (and SubHile)<br>Distributed Computing for Signal Processing:<br>Modeling of Asynchronous Parallel Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                            | <b>5. TYPE OF REPORT &amp; PERIOD COVERE</b><br>Final Report: April 1, 1982<br>September 30, 1985                                                                                                   |  |

| Final Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                            | 6. PERFORMING ORG. REPORT NUMBER                                                                                                                                                                    |  |

| AUTHOR(=)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                            | 8. CONTRACT OR GRANT NUMBER(+)                                                                                                                                                                      |  |

| L.H. Jamieson, H.J. Siegel, P.H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                                          | Contract No.                                                                                                                                                                                        |  |

| Adams III, J.T. Kuehn, W.E.Kuhn I<br>R.J. McMillen, T.A. Rice, R.R. Se<br>K. D. Smith. D.L. Tuomenoksa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                            | DAAG29-82-K-0101                                                                                                                                                                                    |  |

| (. D. Smith. D.L. Tuomenoksa<br>PERFORMING ORGANIZATION NAME AND ADDRES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | \$                                                                                                                                                                                                                                                                                                                         | 10. PROGRAM ELEMENT. PROJECT, TASK                                                                                                                                                                  |  |

| School of Electrical Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                                          | ARÉA & WORK UNIT NUMBERS                                                                                                                                                                            |  |

| Purdue University                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                     |  |

| Nest Lafayette, IN 47907                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                     |  |

| CONTROLLING OFFICE NAME AND ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                            | 12. REPORT DATE<br>March 1986                                                                                                                                                                       |  |

| U. S. Army Research Office                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                            | 13. NUMBER OF PAGES                                                                                                                                                                                 |  |

| Post Office Box 12211<br>Research Triangle Park, NC-27709                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>.</b>                                                                                                                                                                                                                                                                                                                   | 168                                                                                                                                                                                                 |  |

| MONITORING AGENCY WAME & ADDRESSI dillor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nt from Controlling Office)                                                                                                                                                                                                                                                                                                | 15. SECURITY CLASS. (of this report)                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                            | Unclassified                                                                                                                                                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                            | 15. DECLASSIFICATION/DOWNGRADING<br>SCHEDULE                                                                                                                                                        |  |

| Approved for public release; dis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                     |  |

| DISTRIBUTION STATEMENT (of this Report)<br>Approved for public release; dis<br>DISTRIBUTION STATEMENT (of the obstract entered<br>NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                     |  |

| Approved for public release; dis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | in Block 20, it different fro<br>ings contained in<br>ld not be construct<br>policy, or decis                                                                                                                                                                                                                              | this report are<br>ed as an official<br>sion, unless so                                                                                                                                             |  |

| Approved for public release; dis<br>DISTRIBUTION STATEMENT (of the obstract entered<br>NA<br>SUPPLEMENTARY NOTES<br>The view, opinions, and/or finds<br>those of the author(s) and shoul<br>Department of the Army position<br>designated by other documentation<br>KEY WORDS (Continue on reverse olds if necessary<br>distributed computing, parallel                                                                                                                                                                                                                                                                                                                              | ings contained in<br>Id not be construe<br>policy, or decision<br>ind identify by block number)<br>processing, asynch<br>ults of the reseat<br>AAG29-82-K-0101, of<br>The work is in the                                                                                                                                   | this report are<br>ed as an official<br>sion, unless so<br>mononous computation,<br>covering the period April 1,<br>he area of modeling<br>n for applications in the                                |  |

| Approved for public release; dis<br>DISTRIBUTION STATEMENT (of the obstract entered<br>NA<br>SUPPLEMENTARY NOTES<br>The view, opinions, and/or finds<br>those of the author(s) and shoul<br>Department of the Army position<br>designated by other documentation<br>KEY WORDS (Continue on reverse olds if necessary of<br>distributed computing, parallel<br>signal processing<br>ABSTRACT (Continue on reverse olds if necessary of<br>This report compiles the rest<br>Research Office Contract Number D.<br>1982 through September 30, 1985.<br>asynchronous parallel architectur<br>areas of digital image and signal<br>into three areas:<br>1. Case studies of parallel image | ings contained in<br>Ings contained in<br>Id not be construe<br>policy, or decise<br>and identify by block number)<br>processing, asynch<br>allowing by block number)<br>ults of the reseat<br>AAG29-82-K-0101, of<br>The work is in the<br>es and computation<br>processing. The                                          | this report are<br>ed as an official<br>sion, unless so<br>moronous computation,<br>covering the period April 1,<br>he area of modeling<br>n for applications in the<br>work can be broadly divided |  |

| Approved for public release; dis<br>DISTRIBUTION STATEMENT (of the obstract entered<br>NA<br>SUPPLEMENTARY NOTES<br>The view, opinions, and/or finds<br>those of the author(s) and shoul<br>Department of the Army position<br>designated by other documentation<br>KEY WORDS (Continue on reverse olds if necessary of<br>distributed computing, parallel<br>signal processing<br>ABSTRACT (Continue on reverse olds if necessary of<br>This report compiles the rest<br>Research Office Contract Number D.<br>1982 through September 30, 1985.<br>asynchronous parallel architectur<br>areas of digital image and signal<br>into three areas:<br>1. Case studies of parallel image | ings contained in<br>Ings contained in<br>Id not be construe<br>policy, or decise<br>and identify by block number)<br>processing, asynch<br>ad identify by block number)<br>ults of the reseat<br>AAG29-82-K-0101, of<br>The work is in the<br>es and computation<br>processing. The<br>e processing algonon<br>next page) | this report are<br>ed as an official<br>sion, unless so<br>moronous computation,<br>covering the period April 1,<br>he area of modeling<br>n for applications in the<br>work can be broadly divided |  |

LINCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE(Then Date Enter

objective of which is to study the interaction of parallel processes and parallel architectures. These are described in Papers 1 through 5 and in portions of Appendices A, B, C, and D.

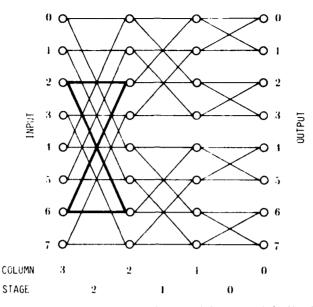

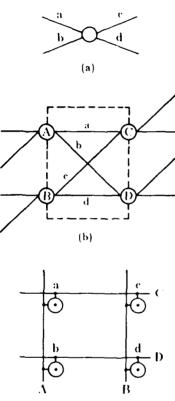

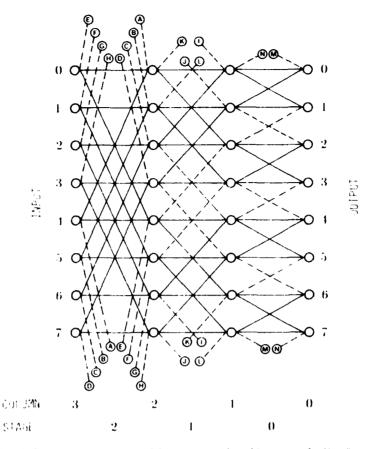

- 2. Modeling of interconnection networks. An important component of any largescale distributed system is the interconnection network. Different techniques for modeling interconnection networks were developed and are described in Papers 6 through 9 and in portions of Appendices A, C, and E.

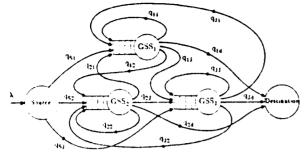

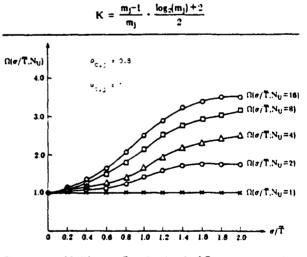

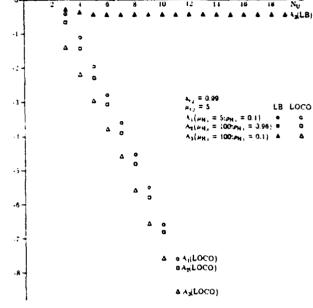

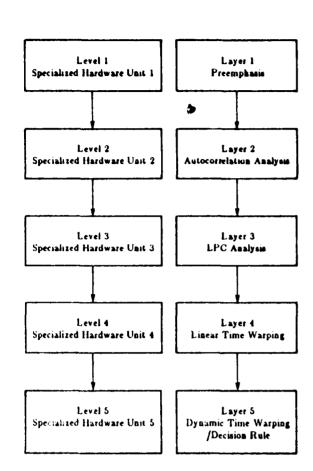

- 3. Aspects of the problem of modeling parallel processes and parallel architectures. This includes mechanisms for describing MIMD algorithms (Paper 11 and portions of Appendices A and D), application of a Petri net based modeling scheme to SIMD and pipeline implementations of example image processing algorithms (portions of Appendices A and F), consideration of performance criteria for parallel image processing algorithms (portions of Appendix F), matching algorithms with macropipelined distributed systems (Paper 12 and portions of Appendix G), new models for the organization of distributed systems comprised of collections of special purpose computing devices (Paper 10), and companion features for describing parallel processes and parallel architectures (portions of Appendices A and D).

#### UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE(When Date Entered)

# DISTRIBUTED COMPUTING FOR SIGNAL PROCESSING: MODELING OF ASYNCHRONOUS PARALLEL COMPUTATION FINAL REPORT

L.H. Jamieson, H.J. Siegel, P.H. Swain, G.B. Adams III, J.T. Kuehn, W.E. Kuhn III, G.-M. Lin, R.J. McMillen, T.A. Rice, R.R. Seban, B.W. Smith, K.D. Smith, D.L. Tuomenoksa

March 1986

U.S. Army Research Office Contract No. DAAG29-82-K-0101

School of Electrical Engineering Purdue University West Lafayette, Indiana 47907

Approved for public release; distribution unlimited.

# **Table of Contents**

# Introduction

# Paper #1

Thomas A. Rice and Leah J. Siegel (Jamieson), "Parallel Algorithms for Computer Vision," Proceedings of the Workshop on Computer Architecture for Pattern Analysis and Image Database Management (IEEE Catalog No. 83CH1929-9), pp. 93-100, Pasadena, California, October 1983

# Paper #2

Thomas A. Rice and Leah H. Jamieson, "Parallel Processing for Computer Vision," in *Integrated Technology for Parallel Image Processing*, S. Levialdi, editor, Academic Press, London, pp. 57-78, 1985

# Paper #3

David Lee Tuomenoksa, George B. Adams, III, Howard Jay Siegel, and O. Robert Mitchell, "A Parallel Algorithm for Contour Extraction: Advantages and Architectural Implications," Proceedings of the 1983 IEEE Computer Society Symposium on Computer Vision and Pattern Recognition (CVPR) (IEEE Catalog No. 83CH1891-1), pp. 336-374, Arlington, Virginia, June 1983

# Paper #4

James T. Kuehn, Howard Jay Siegel, George B. Adams III, and David L. Tuomenoksa, "The Use and Design of PASM," in *Integrated Technology for Parallel Image Processing*, edited by S. Levialdi, Academic Press, London, pp. 133-152, 1985

# Paper #5

Kirk D. Smith and Leah H. Jamieson, "A Parallel Algorithm for Normalized Fourier Descriptors," Twenty-second Annual Allerton Conference on Communication, Control, and Computing, pp. 765-774, University of Illinois-Urbana, Monticello, Illinois, October 1984

# Paper #6

Robert R. Seban and Howard Jay Siegel, "Theoretical Modeling and Analysis of Special Purpose Interconnection Networks," *Proceedings of the Fourth International Conference on Distributed Computer Systems* (IEEE Catalog No. 84CH2021-4), pp. 256-265, San Francisco, California, May 1984

| Accesion For                                             |                      |

|----------------------------------------------------------|----------------------|

| NTIS CRA&I N<br>DTIC TAB<br>Unannounced<br>Justification |                      |

| By<br>Dist ibution /                                     | QUALITY<br>INSPECTED |

| Availability Codes                                       | 3                    |

| Dit Avail and/or<br>Dit Special<br>A-1                   |                      |

# Paper #7

Robert R. Seban and Howard Jay Siegel, "Analysis of Partitionability Properties of Topologically Arbitrary Interconnection Networks," *Proceedings of the Fifth International Conference on Distributed Computer Systems* (IEEE Catalog No. 85CH2149-3), pp. 173-181, Denver, Colorado, May 1985

# Paper #8

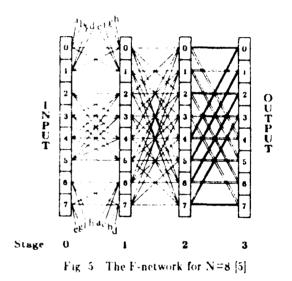

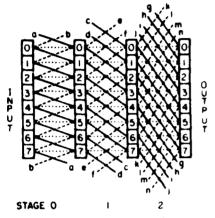

Robert J. McMillen and Howard Jay Siegel, "Evaluation of Cube and Data Manipulator Networks," *Journal of Parallel and Distributed Computing*, Vol. 2, No. 1, pp. 79-107, February 1985

# Paper #9

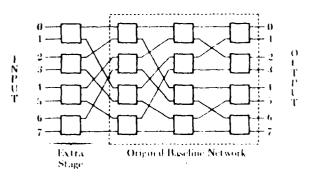

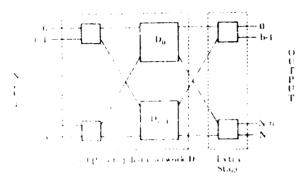

George B. Adams III and Howard Jay Siegel, "A Survey of Fault-Toleran Multistage Networks and Comparison to the Extra Stage Cube," Proceedings of the Seventeenth Hawaii International Conference on System Sciences, pp. 268-277, Honolulu, Hawaii, January 1984

# Paper #10

Veljko M. Milutinovic, J. J. Crnkovic, L. Y. Chang, and Howard Jay Siegel, "The LOCO Approach to Task Allocation AIDA by VERDI," *Proceedings of the Fifth International Conference on Distributed Computer Systems* (IEEE Catalog No. 85CH2149-3), pp. 359-368, Denver, Colorado, May 1985

## Paper #11

Kirk D. Smith and Leah H. Jamieson, "MIMD Algorithm Analysis: Low Level Algorithm Descriptions," *Fifth International Conference on Distributed Computing Systems* (IEEE Catalog No. 85CH2149-3), pp. 150-157, Denver, Colorado, May 1985

# Paper #12

Bradley W. Smith and Howard Jay Siegel, "Models for Use in the Design of Macro-Pipelined Parallel Processors," *Proceedings of the Twelfth Annual International Symposium on Computer Architecture* (IEEE Catalog No. 85CH2144-4), pp. 116-123, Boston, Massachusetts, June 1985

# Appendix A

Distributed Computing for Signal Processing: Modeling of Asynchronous Parallel Computation 1983 Progress Report, Purdue Electrical Engineering Technical Report TR-EE 83-11, March 1983

#### Appendix B

Design of the Operating System for the PASM Parallel Processing System, Ph.D. Thesis by David Lee Tuomenoksa, Faculty Advisor: Howard Jay Siegel

# Appendix C

Fault Tolerant Interconnection Networks and Image Processing Applications for the PASM Parallel Processing Systems, Ph.D. Thesis by George B. Adams III, Faculty Advisor: Howard Jay Siegel

# **Appendix D**

Analysis of MIMD Algorithms: Features, Measurements, and Results, Ph.D. Thesis by Kirk D. Smith, Faculty Advisor: Leah H. Jamieson

# Appendix E

Topological Properties of Interconnection Networks for Parallel Processors, Ph.D. Thesis by Robert R. Seban, Faculty Advisor: Howard Jay Siegel

# Appendix F

Studies in Parallel Image Processing, Ph.D. Thesis by Gie-Ming Lin, Faculty Advisor: Philip H. Swain; Purdue Electrical Engineering Technical Report TR-EE 84-29, August 1984

# **Appendix G**

On the Design and Modeling of Special Purpose Parallel Processing Systems, Ph.D. Thesis by Bradley Warren Smith, Faculty Advisor: Howard Jay Siegel

# INTRODUCTION

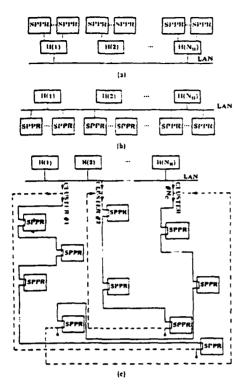

<sup>1</sup> This report compiles the results of the research performed under U.S. Army Research Office Contract Number DAAG29-82-K-0101, covering the period April 1, 1982 through September 31, 1985. The work is in the area of modeling asynchronous parallel architectures and computation for applications in the areas of digital image and signal processing. The work can be broadly divided into three areas:

- 1. Case studies of parallel image processing algorithms and tasks, the objective of which is to study the interaction of parallel processes and parallel architectures; These are described in Papers 1 through 5 and in portions of Appendices A, B, C, and D.

- 2. Modeling of interconnection networks. An important component of any large-scale distributed system is the interconnection network. Different techniques for modeling interconnection networks were developed and are described in Papers 6 through 9 and in portions of Appendices A, C, and E.

- 3. Aspects of the problem of modeling parallel processes and parallel architectures. This includes mechanisms for describing MIMD algorithms (Paper 11 and portions of Appendices A and D), application of a Petri net based modeling scheme to SIMD and pipeline implementations of example image processing algorithms (portions of Appendices A and F), consideration of performance criteria for parallel image processing algorithms (portions of Appendix F), matching algorithms with macropipelined distributed systems (Paper 12 and portions of Appendix G), new models for the organization of distributed systems comprised of collections of special purpose computing devices (Paper 10), and companion features for describing parallel processes and parallel architectures (portions of Appendices A and D).

Paper 1

Parallel Algorithms for Computer Vision

Dž.

From the Proceedings of the 1983 Computer Society Workshop on Computer Architecture for Pattern Analysis and Image Database Management, Pasadena, CA, October, 1983.

#### PARALLEL ALGORITHMS FOR COMPUTER VISION

Thomas A. Rice Leah Jamieson Siegel

School of Electrical Engineering Purdue University West Lafayette, IN 47907

#### Abstract

An application of parallel processing to the computationally intensive task of computer vision is presented. Computational speedups, both theroretical and experimental, are derived and presented for the extraction of several parameters based upon the SRI vision module and Fourier descriptors. Good results are obtained for moderate numbers of processing elements. The use of parallel processing allows easier expansion and modification of the vision algorithms as compared with a hardware approach.

#### 1. Introduction

Parallel processing offers the potential of providing fast, flexible solutions to many computationally intensive tasks. In this paper, the use of parallelism for computer vision is described. Theoretical analyses and simulation results are presented. Considerations for the design of a parallel architecture for computer vision are discussed.

#### 2. Definitions for the Parallel Simulation

In this section, two general models of parallel computation are defined and the specific model used for the computer vision task is presented. The implementation of the parallel simulation is described.

#### Model

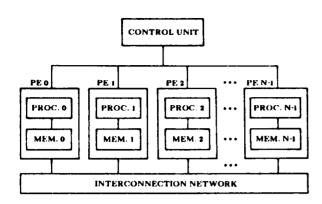

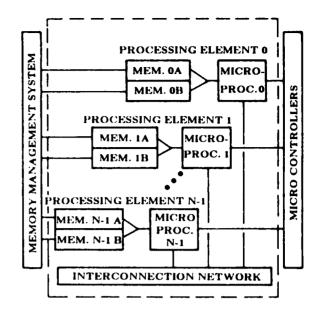

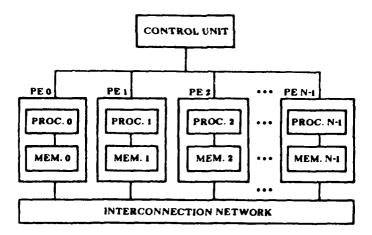

Single instruction stream - multiple data stream (SIMD) machines [4] represent a form of synchronous, highly parallel processing. Systems with up to 1,000 full processors have been proposed [10, 14]; systems with as many as 9,000 and 16,000 simple processors have been built [2, 3]. An SIMD machine typically consists of a control unit, a set of P processing elements (PEs), each a processor with its own memory, and an interconnection network. The control unit broadcasts instructions to all PEs and each active PE executes the instruction on the data in its own memory. The interconnection network allows data to be transferred among the PEs. SIMD machines are especially well-suited for exploiting the parallelism inherent in certain tasks performed on vectors and arrays.

Multiple instruction stream - multiple data stream (MIMD) machines [4] represent asynchronous parallel processing. MIMD systems with 16 [18] and 50 [16] processors have been built; MIMD systems with as many as 4,000 processors [6] have been proposed. An MIMD

This research was supported by the United States Army Research Office, Department of the Army, under grant number DAAG29-82-K-0101. machine typically consists of P processors and M memories,  $M \ge P$ , where each processor can follow an independent instruction stream. As with SIMD machines, there is a multiple data stream and an interconnection network. Thus, there are P independent processors that can communicate among themselves. There may be a coordintor unit to oversee the activities of the processors.

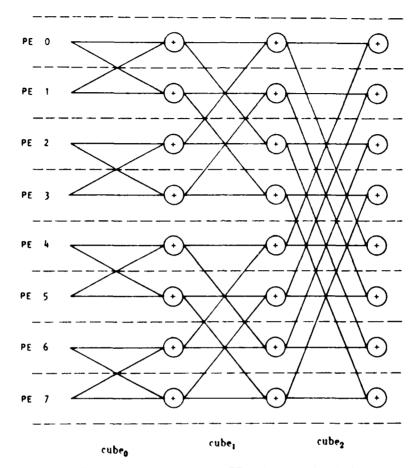

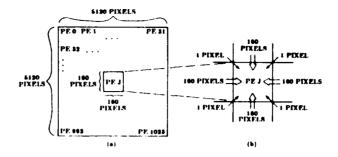

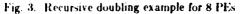

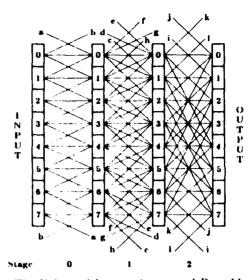

The parallel machine model assumed for the computer vision task consists of a set of PEs under the management of a control unit. The number of PEs is a power of two:  $N=2^n$ . Each of the PEs has a unique "address" between 0 and N - 1. In addition, there exists an interconnection network to allow the simultaneous transfer of data among the PEs. For the computer vision task, the transfer patterns required will be uniform modulo shifts and "cube" interconnection functions. In a uniform modulo shift, PE j transfers data to PE (j+d) modulo N for all j,  $0 \le j < N$ , given a positive or negative integer distance d. The value of d may vary from one transfer to the next; however, for a given transfer, all PEs will send their data the same distance d. The set of cube interconnection functions consists of  $n = \log_2 N$  functions, cube<sub>i</sub>, for  $0 \le i < n$  [13]. If  $p_{n-1} \cdots p_i \cdots p_0$  is the binary representation of a PE's address, then the cube<sub>i</sub> function exchanges data between all pairs of PEs whose addresses differ in bit i:

$$cube_i(p_{n-1}\cdots p_i\cdots p_0)=p_{n-1}\cdots p_i\cdots p_0$$

The model assumed here combines SIMD and MIMD attributes. Each PE will contain the same code but will execute the code on a different subimage. However, within each PE, the code can run in MIMD mode. This modification to the basic models allows faster execution on some code than a pure SIMD model without incurring the expense of the full flexibility of an MIMD machine. The gains in speed will occur on the execution of conditional statements:

> where <condition> do <block1> elsewhere do <block2>

In SIMD mode, those PEs satisfying the <condition>execute <block1>. Then the remaining PEs execute <block2>. In the model here, <block1> and <block2> will be executed concurrently, but in different sets of PEs. On the other hand, this is not full MIMD mode, as it is required that the code in each PE be the same. This aids in insuring synchronization and thus helps enforce data coherence, e.g., insuring that a PE acquires the correct version of a variable from another PE.

Synchronization can take place in one of two ways. First, synchronization is required at all data transfer points. This is done because data transfers often involve the same variable for all of the PEs. Thus, it does not matter if the separate processors take different times to execute their code, as they will be forced to synchronize at transfers to insure coherence. Explicit synchronization will also be possible by one of the simulation language constructs that requires that all PEs finish a section of code before any can move to the next section of code.

The motivation for the assumed model comes about from two directions. First, for many image processing operations, it is natural to consider executing the same code on subimages of the original image. Each subimage is a valid image and the same types of operations are needed on the pixels of each subimage. Second, since the actual quantities of the various operations that will be performed on each subimage may vary, asynchronous operation may allow higher PE utilization.

#### Simulation

and the second second second

There are two major approaches to the development of parallel software. Either the software can be of a generally descriptive nature to illustrate the parallelism (or lack thereof) inherent in a task, or the software can be designed to be compilable and testable, either by parallel execution or via serial simulation. Due to the computational intensity and intricacy of the computer vision task, the most reliable way to insure correctness is via testing. This will guarantee that typical problem cases are being handled correctly by testing the software for a variety of mages. A set of test images, some with multiple objects, was used for debugging and for analyzing computational speedup. Therefore, the software was designed so that it could be compiled and tested.

Programming was done in a modified version of the 'C' bacguage [7]. This language was chosen for the capabilities it provides for developing parallel data structures and the high degree to which one can manipulate system information (such as memory areas). The latter played a barge part in the simulating of parallel data transfers. The actual conversion of the serial 'C' language to a parallel merginage was done via macros and support subtion in the set features were designed to facilitate the tevelope and of parallel code without requiring the user to have the specific details of the serial implementation. This was can simply use the macro file without knowing the details and can then write parallel code.

The major points of this implementation are as follows:  $A_{\rm construct}$  of the form

## in pe { codiblock: }

Let us the inclosed block of code in each of the PEs. I a prefix "i E" prepended to a variable indicates that the variable is local to a PE. All other variables are assumed to be global (i.e., the control unit has one copy i the variable). Global variables are used for such operations as bop control and overall conditional testing. There are also versions of the "in pe" construct that sllow the code to be executed in a limited subset of the  $PI_{init}$  These schemes use an address mask [12], which is a insteining format that the PE address must match for execution to occur in that PL.

Interprocessor communication is accomplished via a "transfer" subroutine:

transfer(destination\_address,source\_address,offset).

The transfer routine uses these addresses along with information shout the size and structure of the PE data space to simulate the transfer via a memory-to-memory nove Recursive transfers and broadcasts (where one value is transferred to the all of the PEs) are similar. Synchronization is needed at transfer points to insure data coherence.

The vision software and simulations were run on a dual-processor Vax 11/780 [5].

# 3. Overview of the Vision Algorithms

In this section, an overview of the computer vision algorithms is provided. The parameters described are based on the SRI vision module [9] and Fourier descriptors [17].

A simple mechanism for entering an image into the system was desired. In the method chosen, the user employs a terminal with cursor control to draw an image on the screen and enter that image into the data memory. This section of the code used a small subsection of the "curses" [1] utilities available on the test system.

After an image has been entered into the data memory, the first task is to classify the image. This consists of transforming an image comprised of edge and non-edge pixels into an image with edge, internal, and external pixels. An internal pixel is a pixel that represents a point on an object, whereas an external pixel represents a point external to an object (such as the external background or a hole in the object).

After the inside and the outside of the image have been identified by the classification step, the holes in the image are located. A hole is defined as an area outside the object. Thus, the background also fits the definition of a hole. These holes are identified so that later merging can be accomplished easily. This capability is needed since holes that are initially thought to be separate may actually be joined.

The areas of the holes are computed and recorded at the same time as the original hole identification, since the data search patterns are quite similar. For purposes of isolating the object parameters, the background is defined to have an area of zero.

Once the inside of the object is known, the center of mass of the object if determined. Although in and of itself the center of mass is not a particularly useful parameter, it is used to normalize some of the perimeter statistics to be derived later.

To find the perimeter, the edge points that are adjacent to the background are identified. Once this has be done, it is a simple matter to find the distances from the perimeter points to the center of mass. These distances are used to calculate the average, minimum, and maximum perimeter distance from the center of mass.

Finally, using the already determined perimeter, a description of this perimeter is produced in the form of a list of coordinate pairs. This list can then be used to determine Fourier descriptors or other similar parameters. Provisions have been made for the processing of images that contain multiple (non-overlapping) objects.

#### 4. Detailed Description of the Parallel Software

In this section, details of the vision algorithms and of their parallel implementation are presented. Results of the simulation of the parallel algorithms and analysis of the performance of the parallel vision system are presented in Section 5.

#### **Image Initialization**

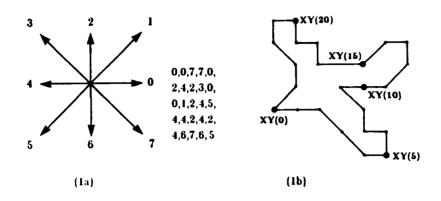

To be able to test the system easily, a simple method by which a user could enter an image into the system was developed. The user executes the vision program and then uses a standard keyboard to direct the cursor and draw an image border. The user also has the option of turning the cursor on and off to allow him/her to draw unconnected borders (such as an internal border). The connection pattern for the drawing is an eight neighbor scheme. That is, from a given point, the user can direct the cursor in any of the four horizontal and vertical directions as well as along the diagonals between these directions. After the user has created the image to bis/her satisfaction, an exit command automatically starts the image processing on the given image.

The produced image can be saved for later testing and can be reloaded and modified. The user also has the option of either saving the results in a text file or of simply viewing the results as they are produced.

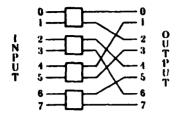

For the parallel implementation, once the image has been created, it is divided among the PEs with each of the PEs having an equally dimensioned stripe (either horizontal or vertical) of the image. Subsequently, each PE operates on the section of the image contained in its local memory, communicating with other PEs when further information is needed.

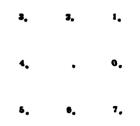

#### Internal / External Classification

As a result of the internal/external classification, each pixel is labeled as being on the inside of the object, outside the object, or on the border. The classification scheme implemented is a two-pass method. The first pass traverses the image from the upper left to the lower right. The initial classification of a pixel is based upon the two neighboring points (to the left of the current point and above the current point) that have already been classified. The method tries to classify the new point as external if either of the previous points is external. If the adjacent points are both edges (border pixels), then information about the length of the edge and the previous region classifications are used to make the classification.

The second pass traverses the image from the lower right to the upper left (backwards as compared to the forward pass). This pass uses the four major compass points in relation to the current point to attempt to correct any classification errors. Again, the bias is toward external classification.

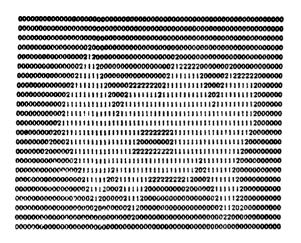

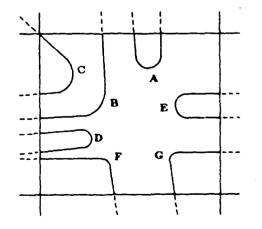

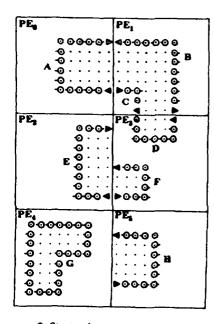

This section of the vision software uses several schemes to insure robustness. Besides the ability to reclassify points on the second pass, the software also looks for the specific case of tracing an edge. In addition, several trouble patterns are checked to prevent major misclassifications. Figure 1 illustrates the classification procedure. Figure 1a is the image before classification (border only). The edges are represented by '2.' Figures 1b and 1c are the image after the first and second passes of the classification, respectively. Internal points are represented by '1' and external points are represented by '0.' An example of a reclassification on the second pass is illustrated by the outlined areas in Figures 1b and 1c.

وم و و و و و و و

In the parallel implementation, each PE works with its own stripe of the image data. The communication between PEs is limited to the values of the border elements of a subimage. One such transfer will take place for each border element on one of the sides of the subimage. These transfers will be uniform modulo shifts of distance one. As the results show later, this section of the software demonstrates good speedup. Thus, the assumption of a two-pass classifier gives a conservative speedup estimation: if more passes were used, each pass would exhibit the same good speedup.

#### Fig. 1a. Initial image.

#### Fig. 1b. Classification: Pass 1.

#### Fig. 1c. Classification: Pass 2.

#### **Identifying Image Holes**

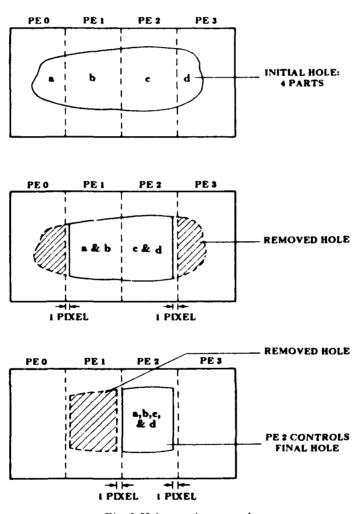

After the object has been separated from its surroundings by the classification operation, the holes in the image are identified. This process consists of two steps: initial local hole identification within each PE, followed by merging of holes between PEs. Initial hole labeling is initially performed separately within each PE. This is done by creating a template array in each PE that is of the same size as the subimage in the PE. Each template location contains an identifier that indicates the local hole number for the corresponding subimage point or zero for non-hole points. Each time an external point is located that is not adjacent to a previous hole, a new hole identifier is used and entered for that point in the template. If the external point is adjacent to a previous hole, then the previous identifier is continued. A two-neighbor scheme is used for all of the pixels except those on one of the subimage borders. Since the points on one edge will have only points from the previous row (or column, in the case of horizontal stripes) to base a decision upon, a oneneighbor scheme is used at the borders. The software maintains a set of parameters that keep track of merged holes and their statistics in order to handle the special case of an external point adjacent to two different previous hole identifiers. Experimentation showed that no accuracy problems were encountered due to the small number of neighbors used in the classification.

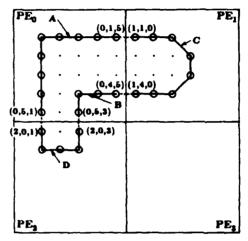

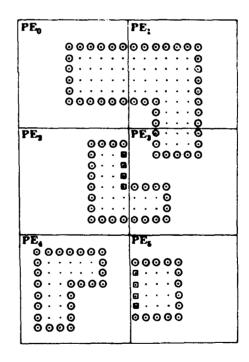

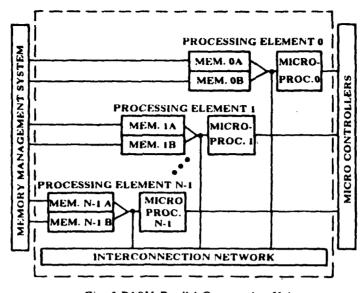

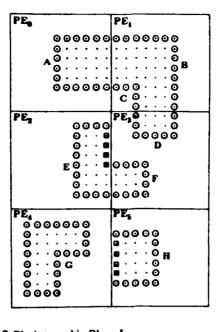

These operations are performed totally within a PE: no communication with other PEs is needed. Each PE owns the information about its own holes. This information is transferred to other PEs during hole merging (described later). Figure 2 shows the internal hole identifiers for each PE. Hole identifiers that are adjacent (e.g., labels 3, 4, 5, and 6 in PE 2) are considered common. That is, only one of the identifiers contains the information for the hole. All of the others contain a pointer to the "master" information.

| FI C                                    | PE 1                  | PE 2                  | PE 3                                    |

|-----------------------------------------|-----------------------|-----------------------|-----------------------------------------|

| 111.141.011111111                       | 1111111111111111      | 11111111111111        | 11111111111111111                       |

| - G19130 (1.1111)                       | 311111111111111111    | 111111111111111111111 | 1111111111111111111                     |

| 1111111111111111                        | \$1111111111111111111 | 1111111111111111      | 111111111111111                         |

| 101110441011                            | 1 11111111111111      | 111111111111111111    | 11111111111111111                       |

| 341.110.1101.1101                       | 11111111111111        | mmi mmi               | 100000000000000000000000000000000000000 |

| 310.34093444.                           | 1111111111111         | 11111 1111            | 141 111111111111                        |

| 3414-44-54-64                           | 1111111111111         | 1111 111              | 11 111111                               |

| 1.1111111111                            | 11111                 | 1 11                  | 1 111111                                |

| 1111111111111111                        | 111                   | 1                     | 111111                                  |

| AD41.4391                               | 1                     |                       | 111111                                  |

| MARTHER, N.                             |                       |                       | 111111                                  |

| 1114.1114                               |                       |                       | 111111                                  |

| 111111111                               |                       |                       | 3333331                                 |

| PETTER 353                              | 83                    | 22222                 | 4444444                                 |

| 11111.1 44444                           |                       |                       | 855555551                               |

| nareunnant                              |                       |                       | 6666666661                              |

| 10111111111111                          |                       | 4                     | <b>77777</b> 777771                     |

| 14(1111111111)11                        | 4                     | 865                   | 777777771                               |

| 11111111111111111                       | 2 555                 | 333333333 66666       | 77777777                                |

| 1111111111111111111111                  | 22 66666 7            | 333333333333333333    | 77777777                                |

| 111111111111111111111111111111111111111 | 222 8688888 97        | 333333333333333333    | 2 8 77777771                            |

| 1111111111111111111                     | 7772227722227 7       | 333333333333333333    | 22 000000000001                         |

|                                         | 722222222222222227    | 3433333333333333333   | 2222222222222222                        |

Nole determination 2 total holes is image fotal Hole Areas 7

Fig. 2 Image hole determination.

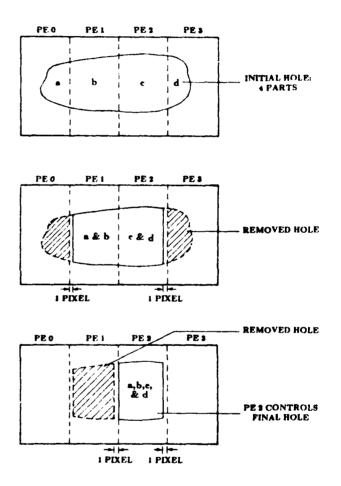

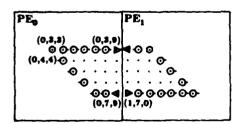

Once the holes have been identified within each PE, they are merged across the PE borders. This is done by transferring the borders of the PE hole template to adjacent processors and searching for matching holes. The areas are merged at the same time that holes are joined. In the scheme used, if a hole has only one edge on a PE border, then the statistics for that hole are transferred to that adjacent PE. This results in each hole being "controlled" by one PE. The information that needs to be transferred from each PE is placed on a transfer stack. These stacks are then transferred. All of these are transfers to logically neighboring PEs (uniform modulo shifts of a distance of one). The amount of information transferred is highly dependent upon the actual image. For purposes of easy identification and to separate holes within an object from the background, the border background is defined as having an area of zero. The process of merging is illustrated in Figure 3.

#### Fig. 3. Hole merging example.

This method of merging holes across PEs is deterministic in that the maximum number of passes needed can be determined by the types of images being examined. For example, the more an object tends to spiral (a spring, for example, as compared to a wheel), the more passes that will be needed. In order to analyze performance, a fixed number of passes (more than necessary for the images considered) was assumed. In simulation, it was found that this section provides poor speedup. Thus, the net result of the fixed large number of passes is again to provide a conservative estimate of the computational speedup of the algorithm.

#### **Computing Image Hole Areas**

The areas to be computed are tabulated at the same time as the hole identifiers are placed in the template in each PE. The area computation is therefore divided among the PEs. To handle the merging of holes, either within a PE of between PEs, an indirection table that points to the actual hole area is used.

#### Locating the Center of Mass

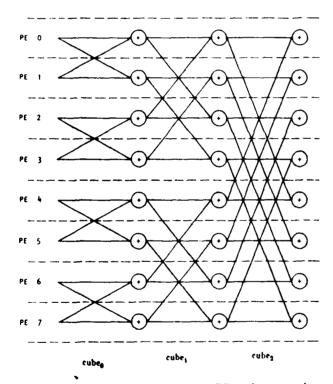

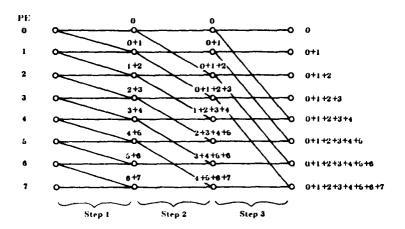

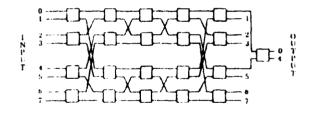

After the points that comprise an object are known, the center of mass of the object can be easily determined. In this system this step is performed by computing the moments in each PE separately and then summing across PEs using recursive doubling [15] (Figure 4). The transfers used are the cube; functions,  $0 \le i \le \log_2 N$ . This scheme requires that each PE know its absolute position in the configuration since the weighting of one of the moments in each PE is dependent upon the PE address. For example, if the stripes are in the vertical direction, the the x axis will be split among the PEs. Moments that involve the absolute distance along the x axis will depend upon the PE address. To obtain the center of mass, log<sub>2</sub>N sets of transfers will be needed. After the center of mass has been determined, it is broadcast to all PEs since this information will be needed at a local PE level in later processing.

Fig. 4. Example of summing across PEs using recursive doubling.

#### Perimeter Identification and Perimeter Statistics Determination

Identifying the perimeter is straightforward once the external background hole has been identified. This hole has area zero by definition. An edge point next to an external hole (or next to another perimeter point) is a perimeter point. Since the area of holes is determined through an indirection table, all one needs to do is see if the hole has zero area. When a perimeter point is located in a PE, a counter in that PE is also incremented so that the total perimeter can be determined by a simple application of recursive doubling to accumulate the total across the PEs.

After the perimeter has been identified, it is a simple matter to find the distances between the perimeter points and the previously determined center of mass. This is done by scanning through the image template looking for perimeter points. Each PE scans its stripe of the image. For each perimeter point so found, the radial distance from the perimeter point to the center of mass is determined. A running sum is kept of these distances, along with the minimum and the maximum distances. When the entire image has been scanned, recursive doubling is used to find the average, minimum, and maximum such distances. Three stages of recursive doubling transfers will be needed, one set for each of the perimeter statistics being gathered. This results in a total of  $3\log_2N$ transfers.

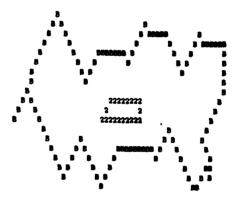

Figure 5 shows the identified perimeter for an image. The perimeter is noted by "B," as compared to "2" for a non-perimeter edge point. Figure 6 shows an example of the overall output of the vision software.

#### **Data Preparation for Fourier Descriptors**

As an illustration of some of the higher level functions that can be performed once the basic parameters have been extracted, the image can be converted into the information necessary to calculate Fourier descriptors [17]. This information is simply an ordered list representation of the perimeter of the object. Each entry in this list consists of a set of coordinates representing a perimeter point. Fourier descriptors have been proposed as a method of performing shape analysis.

Total Object Perimeter 109 Ceater of Mage (33.11) Perimeter Statistics distances from Ceater of Mage NIM = 3, MAX = 24, AVG = 12

Fig. 5. Object perimeter determination and center of mass statistics.

Hole determination 2 total holes is sunge

Total Object Perimeter 109

Total Hole Areas 7

Cester of Nass (33,11)

Perimeter Statistics distances from Center of Mass NIW = 3, MAX = 24, AVG = 12

1 Object(s) in Image

Fig. 6. Example of vision software output.

The vision software begins this step by forming the perimeter nodes into a multiply-linked list. This is done to facilitate the removal of false perimeter points (spikes). This converts the perimeter into a traceable contour. Next, these linked-lists are transferred to one PE which completes the processing. This requires uniform modulo shifts of distances from 1 to N-1. This processing includes converting the lists into partial ordered lists and then combining these lists. Other schemes, such as forming the partial lists in each PE separately, were found to in them such a large amount of overhead in transfers that any advantages in parallelism were lost. The final contours in the single PE are then broadcast to the remainder of the PEs in preparation for the Fourier description of deutlations. If the perimeter is equally distributed around the PFs, (N - 1)/N of the partial ordered testings and need to be transferred. Each of the objects in one of these lists contains ten data fields (two link fields for the linked-list and eight neighbor pointers). If the permater is not equally distributed, then the perimeter could be gathered into the PE with the largest number of perimeter points, and this will require fewer total transfers. Thus, if there are P perimeter points, a maximum of (N - 1)P/N transfers will be needed.

#### Multiple Object Images

The software that has been described to this point has treated the contents of the image field as one object. If there is more than one object in the image field, the same software can still be used, but the results will be a composite of the information for the separate objects. However, it is not exceedingly difficult to separate the information for the separate objects.

Once the contours of the image have been determined, the software knows how many separate objects are in the image. This involves the classification, hole and area identification and merging, and perimeter determination steps described above. That is, the number of contours will equal the number of objects in the image given that the objects do not overlap and that no object is inside another (such as a bolt within a wheel rim). The items can be processed individually by removing the objects corresponding to the undesired contours and reprocessing the image. This can be done for each object in the image. The individual processing involves all the the previous steps, from classification through perimeter determination and perimeter statistics.

To remove an object from the image, its perimeter points (which are known from the contour) are marked to be removed. Two passes are made over the image (similar to the initial classification) to convert internal, perimeter, and edge points bordering the removal points to removal points themselves. This is similar to the erosion scheme used by CLIP4 [11]. A final pass is made over the image to convert all removal points to external points, effectively erasing the object from the image.

If the program detects multiple images, it will still give the composite results, but it will also sequentially erase all but one of the objects and then process the remaining object. This additional processing is identical to the main processing sequence, except the checks for multiple objects are omitted.

#### **Additional Parameters**

Other parameters may be added to a vision system in order to improve the robustness of object identification. Some of these additional parameters are simply combinations of previous parameters. An example of such a parameter is the factor of roundness (how circular the image is), which is computed by dividing  $4\pi$  times the area by the square of the perimeter. The area of the object could also be calculated at the same time that the second classification pass is made. This area could be combined with the internal hole area to provide a total of the areas occupied by the object. The ratio of hole area to total area is similarly obtainable.

There are other parameters that would require additional computation in the main processing sequence. This class of parameters would include such features as second moments, ratios of major and minor axes, finding the bounding rectangle, and line fitting. Others could be added based upon the specific task at hand.

Finally, one needs to consider the non-ideal cases where either multiple objects in the image overlap or the objects are not entirely contained within the borders. Much information for the latter case can be obtained from processing the object as usual and then applying statistical methods to determine possible matches with known objects. The other case is not as simple - some type of image reduction would be necessary if it was determined that an object was not known. Such software could selectively reduce protrusions of an object until a known object was found.

#### 5. Analysis

In order to evaluate the use of the parallel architecture for computer vision, analytical comparisons of the parallel and serial algorithms were performed and the simulation of the parallel software was compared to the serial implementation. An estimation of the computational speedups was derived by an examination of the structure of the parallel software. Table 1 summarizes the speedups for the major algorithms. The proportions

| Algorithm Division | Approx. Speedup     | Serial Time | Time Proportions |

|--------------------|---------------------|-------------|------------------|

| class()            | N(I/(I + N-1))      | 15.36       | 0.3531           |

| holes()            | N/((N-1)(SPIFAC+1)) | 15.70       | 0.3630           |

| areas()            | (called by holes)   | N/A         | N/A              |

| center()           | N                   | 1.64        | 0.0377           |

| pstats()           | N                   | 10.71       | 0.2462           |

Table 1

Computational Performance Results

I = Image Border (I by I image) N = Number of PEs

SPIFAC = How many times a section of the object in the image can switch directions in crossing the image (for example, the letter "Z" would have a SPIFAC of 2). For the images analyzed, SPIFAC = 6.

of time required by different sections of the code were determined by executing a serial version of the algorithm. The time proportions are used to provide a weighting of the parallel speedup results. In this way, a section with low speedup that requires only a small fraction of the serial processing time will not falsely lower the overall speedup. Similarly, a section with high speedup that requires only a small fraction of the serial processing time will not falsely raise the overall speedup. Using the time proprotions, the total weighted speedup S(N) can be computed:

$$S(N) = \frac{0.3531NI}{1+N-1} + \frac{0.3630N}{(N-1)(SPIFAC+1)} + 0.0377N + 0.2462N$$

$$= N \left[ \frac{0.3531I}{1+N-1} + \frac{0.3630}{(N-1)(SPIFAC+1)} + 0.2839 \right]$$

One measure of the performance of a parallel algorithm is the efficiency E(N), defined to be the ratio of the speedup to the number of processors [8]. Table 2 shows the speedup and efficiency for the case of a 64 by 64 image. For the example, although the speedup increases with N, the rate of increase is not proportional to N and the efficiency decreases gradually with N.

The experimental results for the major sections of the software are presented in Table 3. The simulations were designed to provide a conservative estimate of the speedup; assumptions about transfer timings and synchronization delays could only be approximated. The problem of non-determinism in speedups was handled by using deterministic versions of non-deterministic routines. Again, these routines were designed to provide a conservative estimate of the speedup. No overlap of processing and transfers was assumed, although in many situations, inter-PE transfers can be performed at the same time

Table 2

Speedup and Efficiency for I=64

| N  | S(N) | E(N)  |

|----|------|-------|

| 2  | 1.37 | 0.683 |

| 4  | 2.55 | 0.638 |

| 8  | 4.88 | 0.610 |

| 16 | 9.17 | 0.573 |

| 32 | 16.7 | 0.523 |

| 64 | 29.6 | 0.463 |

To be compatible with the "curses" input method, images were 64 by 23. The image was divided into 64/N by 23 stripes.

that independent processing is occurring. The simulation results can therefore be used as a rough indicator of the speedup obtained by the parallel algorithms. Both the analytic and experimental results bear out the observation that the speedup will not grow as N, because the algorithms in which the largest proportion of time is spent (classification and hole location) have less than ideal speedup. (The experimental speedups are somewhat less than the analytic speedups due to the conservative assumptions made throughout the simulation and the non-square image used.) Simulation demonstrated that the major problem with the parallel implementation is

| T            | ible 3  |         |

|--------------|---------|---------|

| Experimental | Speedup | Results |

| Algorithm       | Serial Time | N=2 Time | N=4 Time | N=2 Speedup | N=4 Speedup |

|-----------------|-------------|----------|----------|-------------|-------------|

| classification  | 15.36       | 9.47     | 6.02     | 1.62        | 2.55        |

| holes and areas | 15.79       | 13.47    | 17.11    | 1.17        | 0.92        |

| center          | 1.64        | 1.11     | 0.66     | 1.48        | 2.48        |

| perimeter       | 10.71       | 5.61     | 2.79     | 1.91        | 3.84        |

| overall         | 43.50       | 29.84    | 26.88    | 1.47        | 1.62        |

basically of one form: the number of transfers needed reduces the effectiveness of the parallelism. This can occur when the amount of information that is needed to make a proper decision (such as for hole merging) is large. This problem can manifest itself in several forms, such as algorithms that are inherently serial or that require data from the entire image. Such tasks might better be performed in one PE or in the control unit.

#### **8.** Architectural Considerations

A specific type of architecture has been assumed throughout this simulation and analysis. At this point, this restriction will be removed and the tasks considered will be examined to explore a parallel architecture tailored to the characteristics of the vision task.