NATIONAL BUREAU OF STANDARDS MICROCOPY RESOLUTION TEST CHART

AP- #350038 (2)

## AD-A158 515

**NSWC TR 85-133**

## MASS MEMORY STORAGE DEVICES FOR AN/SLQ-32(V)

By L. C. TRIOLA

**ELECTRONICS SYSTEMS DEPARTMENT**

1 JUNE 1985

Approved for public release; distribution unlimited

NAVAL SURFACE WEAPONS CENTER

Algren, Virginia 22448 • Silver Spring, Maryland 20910

85 9 03 134

SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered)

| REPORT DOCUMENTA                                                       | TION PAGE                              | READ INSTRUCTIONS BEFORE COMPLETING FORM                       |

|------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------|

| 1. REPORT NUMBER                                                       | 2. GOVT ACCESSION NO.                  | 3. RECIPIENT'S CATALOG NUMBER                                  |

| NSWC TR 85-133                                                         | AD-A158515                             |                                                                |

| 4. TITLE (and Subtitle)                                                |                                        | 5. TYPE OF REPORT & PERIOD COVERED                             |

| MASS MEMORY STORAGE DEVICES                                            | FOR AN/SLQ-32(V)                       | Final, fiscal year 1985                                        |

|                                                                        |                                        | 6. PERFORMING ORG. REPORT NUMBER                               |

| 7. AUTHOR(a)                                                           |                                        | 8. CONTRACT OR GRANT NUMBER(*)                                 |

| L. C. TRIOLA                                                           |                                        |                                                                |

| 9. PERFORMING ORGANIZATION NAME AND AD                                 |                                        | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS |

| Naval Surface Weapons Cent                                             | ter (Code F24)                         | 57/77450                                                       |

| Dahlgren, VA 22448                                                     |                                        | 5F46KMA50                                                      |

| 11. CONTROLLING OFFICE NAME AND ADDRES                                 | 1                                      | 12. REPORT DATE 1 June 1985                                    |

|                                                                        |                                        |                                                                |

|                                                                        |                                        | 13. NUMBER OF PAGES                                            |

| 14. MONITORING AGENCY NAME & ADDRESS(I                                 | "forent from Controlling Office)       | 18. SECURITY CLASS. (of this report)                           |

|                                                                        |                                        | Unclassified                                                   |

|                                                                        |                                        | 18a, DECLASSIFICATION/DOWNGRADING                              |

| 16. DISTRIBUTION STATEMENT (of this Report)                            |                                        | <del></del>                                                    |

| A                                                                      |                                        |                                                                |

| Approved for public releas                                             | se; distribution unii                  | mited.                                                         |

|                                                                        |                                        |                                                                |

|                                                                        |                                        |                                                                |

| 17. DISTRIBUTION STATEMENT (of the abstract                            | entered in Block 20, if different fre  | en Report)                                                     |

|                                                                        |                                        |                                                                |

|                                                                        |                                        |                                                                |

|                                                                        |                                        |                                                                |

| 18. SUPPLEMENTARY NOTES                                                |                                        |                                                                |

|                                                                        |                                        |                                                                |

|                                                                        |                                        |                                                                |

|                                                                        |                                        |                                                                |

| 19. KEY WORDS (Continue on reverse side if neces<br>Electronic Warfare |                                        | _                                                              |

| Electronic warrare<br>Electronic Countermeasures                       | RP-16 Microprocessor<br>Memory Storage | Dynamic RAM                                                    |

| AN/SLQ-32(V) Suite                                                     | Magnetic Hard Disk                     | Bernoulli Disk Drive                                           |

| AN/UYK-19 Computer                                                     | Optical Disk                           |                                                                |

| 20. ABSTRACT (Continue on reverse side if neces                        | eary and identify by block number)     | _                                                              |

This technical report documents the investigation of mass memory storage devices for use with AN/SLQ-32(V) electronic warfare suites. The device is to be incorporated into the AN/SLQ-32(V) systems in order to reduce the program loading time and the operator actions required for the load. The report includes specific details on five types of mass memory storage devices: magnetic hard disks, optical (laser) disks, magnetic bubble memory, dynamic RAM with battery backup, and Bernoulli disk drives.

DD 1 JAN 73 1473

EDITION OF 1 NOV 68 IS OBSOLETE

UNCLASSIFIED

S- N 0102- LF- 014- 6601

SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered)

# MASS MEMORY STORAGE DEVICES FOR AN/SLQ-32(V)

By L. C. TRIOLA

**ELECTRONICS SYSTEMS DEPARTMENT**

1 JUNE 1985

Approved for public release; distribution unlimited

**NAVAL SURFACE WEAPONS CENTER**

Dahlgren, Virginia 22448 • Silver Spring, Maryland 20910

#### **EXECUTIVE SUMMARY**

The purpose of the investigation of mass memory storage devices was to find a way to improve the speed of loading the AN/SLQ-32(V) computer programs. If the present system is not augmented for future software expansion, the time to load a complete set of tactical programs and libraries into the AN/UYK-19 computer, the RP-16 microprocessor, and other peripheral processors (e.g., ADLS and Band 1) will be five minutes or more. This time span is unacceptable for combat situations.

The approach of the investigation included three stages:

- 1. Evaluation of the requirements for software storage

- 2. Consideration of all options which might meet these requirements

- 3. Detailed investigation of the most feasible options

An evaluation of the requirements for data storage revealed that the storage capacity would have to be a minimum of 700 kilobytes for the tactical programs and libraries alone or 3 megabytes if the diagnostic software also resides in the memory device. Data access and transfer rates should be such that the entire tactical software set could be loaded within ten seconds or less.

Consideration of all options which might meet these requirements included modification of the present tape system. It was determined that neither modification of the present tape drive nor obtaining a new tape drive system would sufficiently improve software load time. Ten different types of mass storage systems were also considered: magnetic hard disk, floppy disk, optical disk, magnetic bubble memory, EPROM, EEPROM, nonvolatile RAM, magnetic core, static or dynamic RAM with battery backup, and Bernoulli disk drives. Five were eliminated from consideration because of functional problems or expense.

The five remaining types (hard disk, optical disk, bubble memory, RAM with battery backup, and Bernoulli disk drive) were investigated in detail. No type of device was found to be ideal. Each had both advantages and disadvantages, which are described in this report.

Engineering and programming considerations for interfacing a new storage device with the present AN/SLQ-32(V) system are also discussed. The device will require a direct connection to the AN/UYK-19 computer, either by the I/O bus or by direct memory addressing. The device will have to be mounted close to the AN/UYK-19 in already crowded equipment rooms. Software for the computer and the peripheral processors, including the RP-16, will have to be

rewritten to accommodate the new concept of loading directly from the mass storage device. At the same time the current method of program loading must be retained for the purposes of program backup and software delivery.

This report recommends prototyping the most promising devices if sufficient time and funds are available. These prototypes should be tested to prove survivability and performance aboard ships operating under extreme environmental conditions. The production contract should be submitted for competitive bids to ensure the best cost/performance ratio.

#### FOREWORD

This work has been performed under a NAVELEX PDE-107 funded task to investigate mass memory storage devices for the purpose of improving AN/SLQ-32(V) program load time. The requirements for such a device are described in Chapter 2. Present system modification and hardware options which would decrease load time are discussed in Chapters 3 and 4. The most feasible hardware options are described in detail in Chapter 4. Engineering and programming considerations, conclusions, and recommendations are included in the last three chapters.

This report, which has been reviewed by the head and members of the System Engineering Group (F2450), by the head of the Electronic Countermeasures (ECM) Branch (F24), and by the head of the Electronic Warfare Division (F20), is hereby released for publication.

Approved by:

R. T. RYLAND, Jr., Head

Electronics Systems Department

RE: Classified Reference, Distribution Unlimited No change per Mrs. Pulliam, NSWC/Library

| Access        | ion For           | /     |

|---------------|-------------------|-------|

| NTIS          |                   |       |

| DTIC 1        |                   |       |

| Unama         | naiced<br>Hontion | LJ    |

| 1 (11311)<br> | . 10/10/10 1      |       |

| Py            |                   |       |

|               | iouties/          |       |

| h             | lebility :        | Cades |

|               | avall nod         |       |

| Dist          | Spental           |       |

|               |                   |       |

| 14-1          |                   |       |

| <b>/</b>      | 1                 |       |

### CONTENTS

| Chapter  |                                                                                                                                               | Page                             |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1        | INTRODUCTION                                                                                                                                  | 1                                |

| 2        | REQUIREMENTS                                                                                                                                  | 3<br>3<br>4<br>7                 |

| 3        | MODIFICATION OF PRESENT SYSTEM                                                                                                                | 9                                |

| 4        | HARDWARE OPTIONS  MAGNETIC HARD DISK  OPTICAL DISK  MAGNETIC BUBBLE MEMORY  RAM INTEGRATED CIRCUITS WITH BATTERY BACKUP  BERNOULLI DISK DRIVE | 11<br>15<br>20<br>21<br>23<br>24 |

| 5        | INTERFACE CONSIDERATIONS                                                                                                                      | 25<br>25<br>28                   |

| 6        | CONCLUSIONS                                                                                                                                   | 31                               |

| 7        | RECOMMENDATIONS                                                                                                                               | 33                               |

|          | NOMENCLATURE                                                                                                                                  | 35                               |

| Appendix |                                                                                                                                               | Page                             |

| A        | SUPPLEMENTARY TECHNICAL INFORMATION ON MASS MEMORY STORAGE DEVICES                                                                            | A-1                              |

| В        | DISPLAY AND CONTROL CONSOLE INFORMATION                                                                                                       | B-1                              |

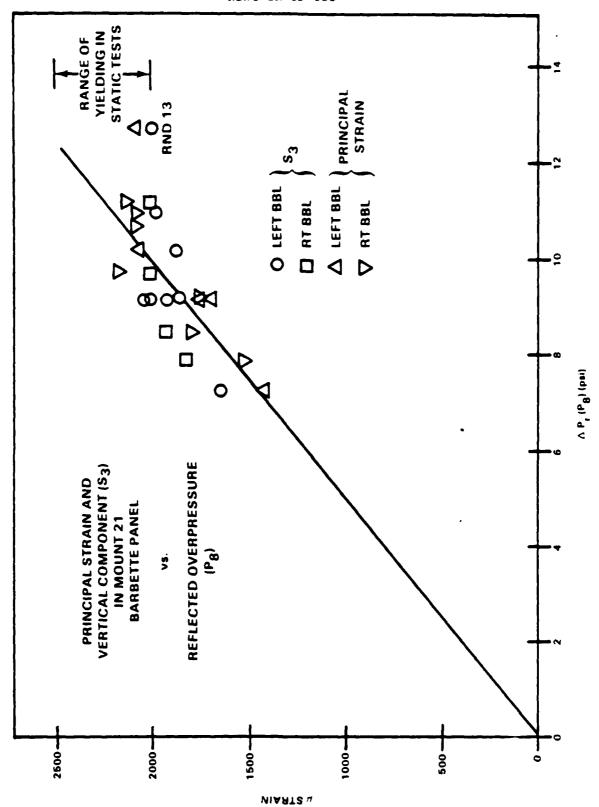

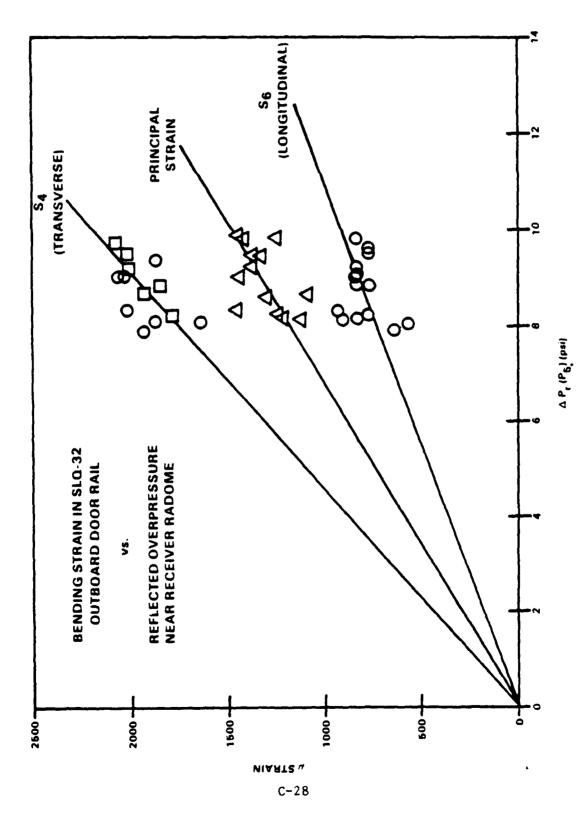

| С        | SHOCK AND VIBRATION REPORT FROM THE USS NEW JERSEY                                                                                            | C-1                              |

## ILLUSTRATIONS

| <u>Figure</u> |                                                                                                 | Page |

|---------------|-------------------------------------------------------------------------------------------------|------|

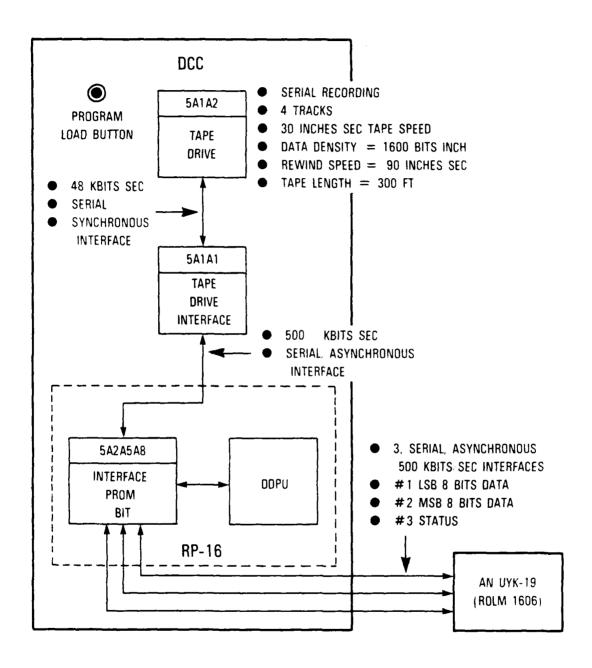

| 1             | PRESENT AN/SLQ-32(V) TAPE DRIVE/COMPUTER INTERFACE                                              | 5    |

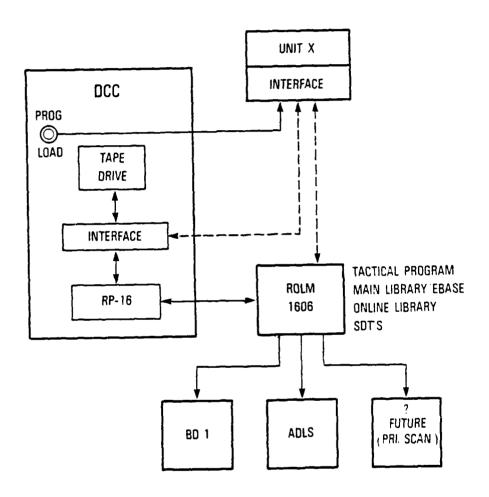

| 2             | AN/SLQ-32(V) COMPUTER INTERFACES WITH PROPOSED MASS<br>STORAGE DEVICE AND PERIPHERAL PROCESSORS | 6    |

| 3             | PRESENT PROGRAM LOAD PROCESS                                                                    | 26   |

| 4             | MODIFIED PROGRAM LOAD PROCESS TO INCORPORATE NEW MASS STORAGE DEVICE                            | 27   |

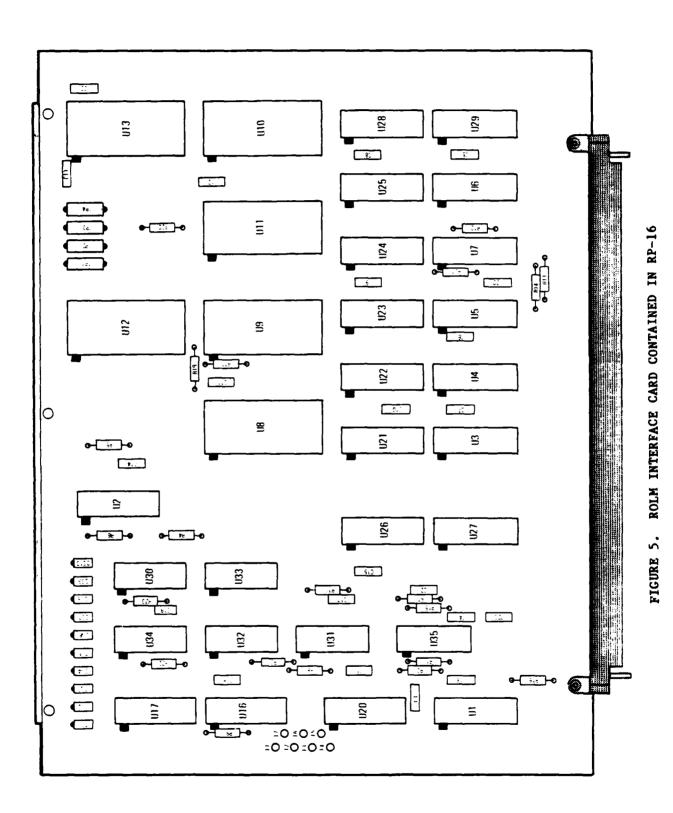

| 5             | ROLM INTERFACE CARD CONTAINED IN RP-16                                                          | 30   |

|               | TABLES                                                                                          |      |

| <u>Table</u>  |                                                                                                 | Page |

| 1             | AN/SLQ-32(V) PROGRAMS AND DATA FILES                                                            | 4    |

| 2             | HIGH MEMORY CAPACITY HARDWARE OPTIONS                                                           | 12   |

| 3             | LOW MEMORY CAPACITY HARDWARE OPTIONS                                                            | 14   |

| 4             | MAGNETIC HARD DISK SPECIFICATION COMPARISON                                                     | 16   |

| 5             | AN/SLQ-32(V) ENVIRONMENTAL REQUIREMENTS                                                         | 18   |

#### CHAPTER 1

#### INTRODUCTION

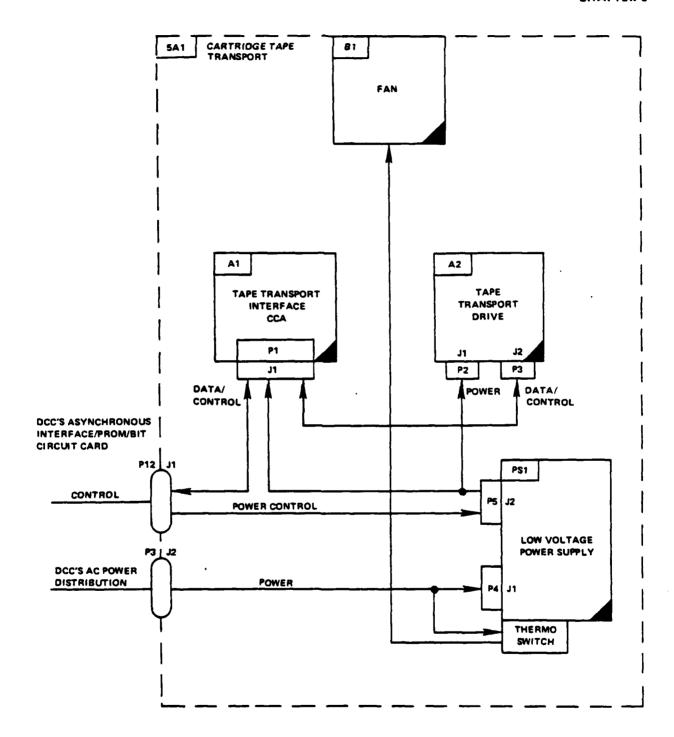

AN/SLQ-32(V) electronic warfare (EW) systems are installed aboard ships in the U.S. Naval fleet to detect, analyze, and identify radio frequency emitters. They also recommend or activate electronic countermeasures against emitters identified as hostile (e.g., missiles). For the system to become operational, the system software must be loaded into computer memory from the 4-track magnetic tape cartridges (MTCs) on which the programs are stored.

Program load begins when the operator inserts the operational program MTC and presses the Program Load button on the Display and Control Console (DCC). Loading current versions of the operational program requires over one minute; and loading future, expanded versions of the program will require even more time. If an operator wishes to use a threat summary library geographically tailored to that ship's global region, the library must be loaded from a separate MTC after operational program load is complete. With future software expansion the entire loading process could require five minutes or more. This time span is unacceptable for combat situations since a ship could be targeted and destroyed before the AN/SLQ-32(V) system became operational.

NAVELEX PDE-107 tasked the Electronic Countermeasures (ECM) Systems branch (F24) at the Naval Surface Weapons Center (NSWC) in Dahlgren, VA, to investigate the addition of a mass memory storage device to the AN/SLQ-32(V) system in order to reduce the time required for program load. This report summarizes the investigation. It includes the requirements for such a mass storage device, the options available, and the engineering considerations for implementing the device in the AN/SLQ-32(V) system.

#### CHAPTER 2

#### REQUIREMENTS

Any mass memory storage device incorporated into the AN/SLQ-32(V) system must meet certain minimal requirements in its storage capacity and in its speed of data access and transfer. Chapter 2 describes these requirements and other considerations.

#### STORAGE CAPACITY

An auxiliary mass storage device should be capable of storing all present and future AN/SLQ-32(V) operational and diagnostic programs and data bases. Present software includes the following:

- 1. Operational Program. The operational (tactical) program, which resides in AN/UYK-19 memory, contains data bases and decision-making processes to identify radar emitters, to inform the operator of threat and system statuses, and to command the system hardware to activate countermeasures.

- 2. RP-16 Program. The RP-16 program is used in conjunction with the operational program to enable the operator to communicate through the DCC to the AN/UYK-19.

- 3. <u>CP-32 Program.</u> The CP-32 program, which resides in the RP-16, performs debug functions.

- 4. System Diagnostic Tests. The System Diagnostic Test (SDT) software is used to detect and isolate hardware faults.

- 5. Threat Libraries. Independent main and on-line libraries are data bases of radar parameters used by the tactical software.

Future computer programs, which will reside in peripheral processors, include the Automated Decoy Launching System (ADLS) and Band 1.

As shown in Table 1, which lists the storage requirements for present and future programs, the total storage capacity of an auxiliary mass storage device would have to be at least 3 megabytes (1.5 megawords). This capacity could be reduced if SDT software were separately stored on tape. The slower load time resulting from the separate storage would be inconvenient but not combat critical.

TABLE 1. AN/SLQ-32(V) PROGRAMS AND DATA FILES

| PROGRAM                | 16-BIT WORD LENGTH         |

|------------------------|----------------------------|

| OPERATIONAL            | 192 K                      |

| RP-16/CP-32            | 4 to 16 K                  |

| MAIN LIBRARY/EBASE     | 6.4 K<br>7.2 K (CDS)       |

| ON-LINE LIBRARY        | 3 K each                   |

| SYSTEM DIAGNOSTIC TEST | 750 K                      |

| FUTURE PROGRAMS        |                            |

| ADLS                   | ? (64 K - Not Completed)   |

| BAND 1                 | 20 to 32 K (Not Completed) |

#### DATA ACCESS/TRANSFER

An auxiliary mass storage device for the AN/SLQ-32(V) system must be capable of accessing and transferring data from all current and future software within the shortest time span possible, certainly within ten seconds. In .der to obtain this rapid loading time, the new mass storage device would require an access (to beginning of information file) rate in milliseconds and a transfer (from device to device) rate of at least one megabit (125 kilobytes) per second.

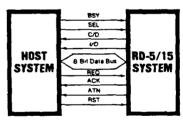

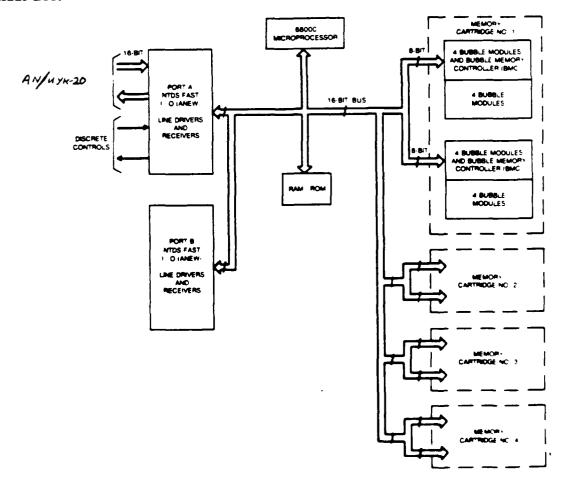

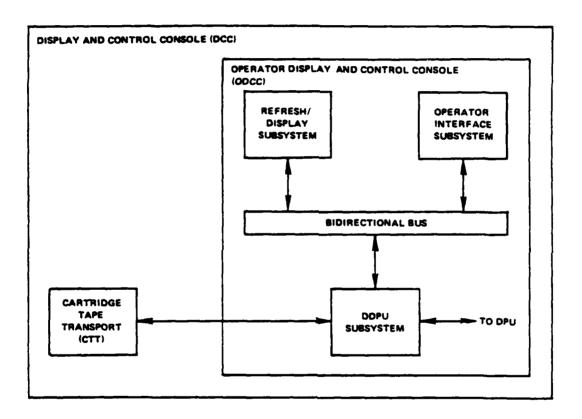

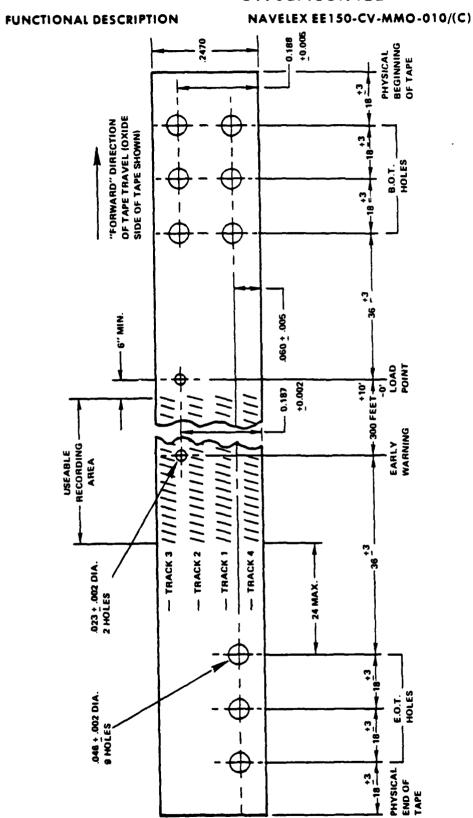

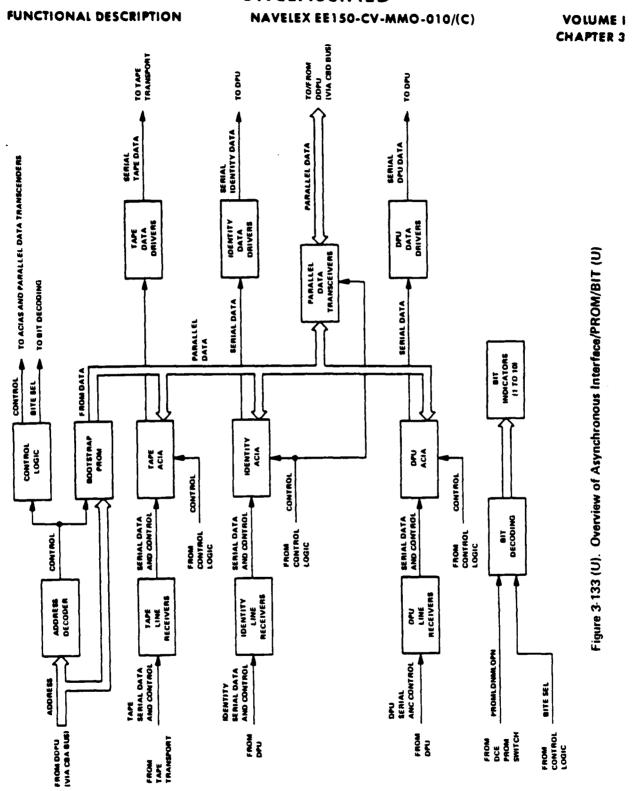

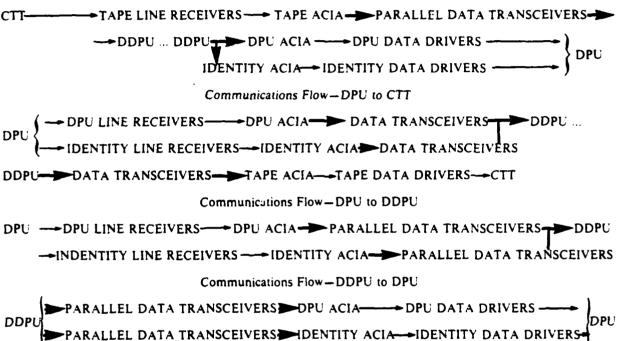

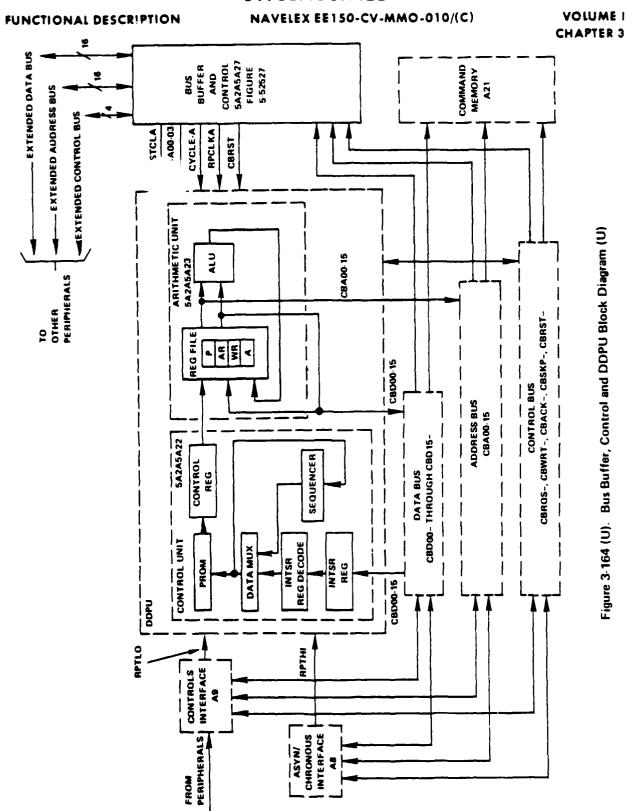

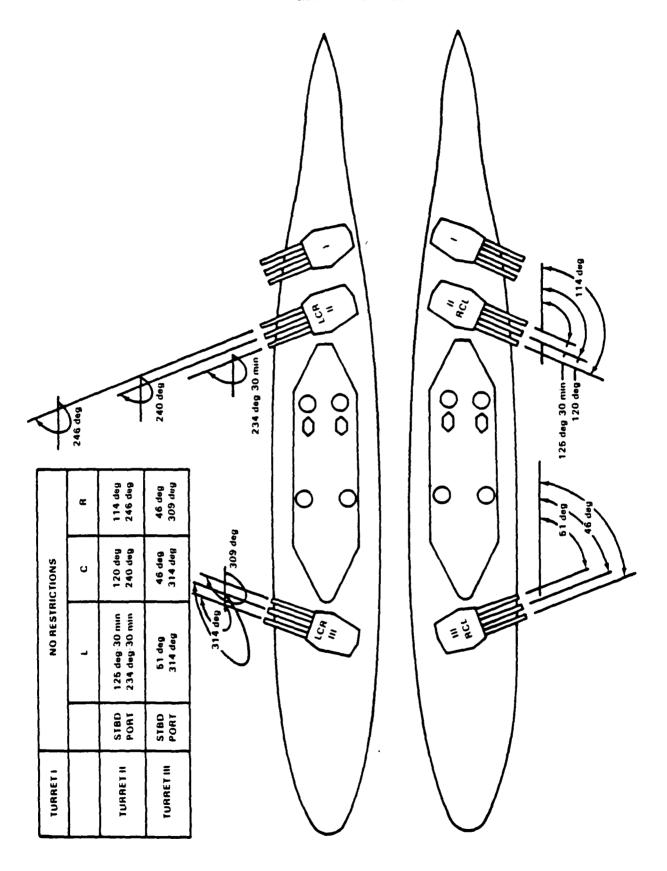

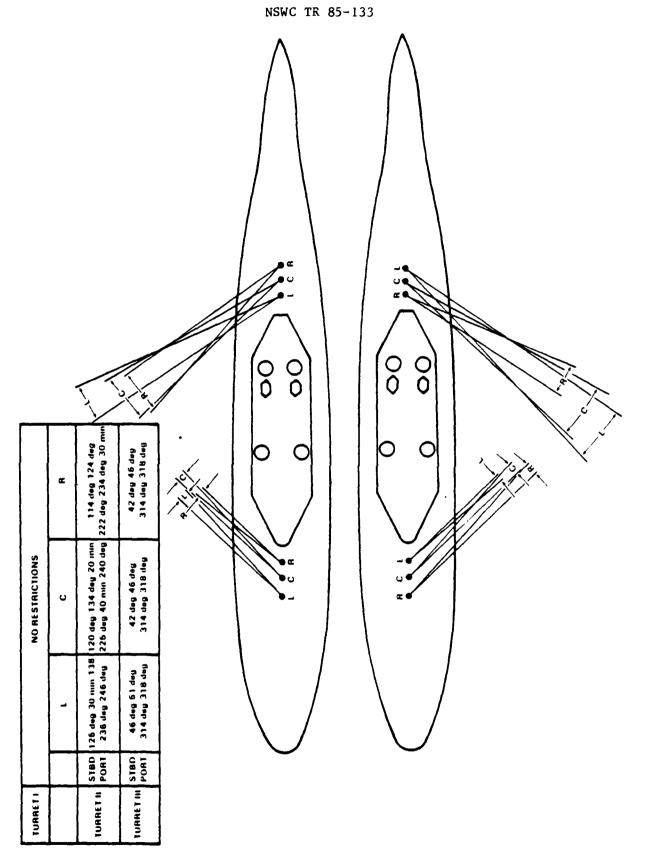

As shown in Figure 1, the current computer/tape drive interface occurs within the DCC. When the operator presses the Program Load button, the RP-16 microprocessor firmware transfers data into the RP-16 random access memory (RAM). The AN/UYK-19 computer is loaded via the RP-16 program and the interface programmable read only memory (PROM) card.

Data access and transfer with a mass storage device would require the configuration shown in Figure 2. The AN/SLQ-32(V) system would have to be modified to permit direct communication between the AN/UYK-19 computer and the mass storage device for quick load of the peripheral processors and the AN/UYK-19 itself. Chapter 5 provides further details of the necessary configuration changes.

FIGURE 1. PRESENT AN/SLQ-32(V) TAPE DRIVE/COMPUTER INTERFACE

FIGURE 2. AN/SLQ-32(V) COMPUTER INTERFACES WITH PROPOSED MASS STORAGE DEVICE AND PERIPHERAL PROCESSORS

#### OTHER CONSIDERATIONS

Other considerations in the selection of a mass storage system for AN/SLQ-32(V) include reliability, ease of interface, physical size and mounting, conformance to military specifications, and cost.

#### CHAPTER 3

#### MODIFICATION OF PRESENT SYSTEM

NSWC personnel considered several options in its investigation of ways to reduce software load time. The first option was a modification of the present AN/SLQ-32(V) system.

Current program load involves the following steps (also see Appendix B):

- 1. Operator loads tactical program MTC into DCC tape transport unit.

- 2. Operator presses Program Load button.

- 3. MTC loads AN/UYK-19 and RP-16 memories at a maximum rate of 48,000 digital bits of information per second.\*

- 4. Tape transport automatically rewinds MTC to beginning of tape.

- 5. Operator removes tactical program MTC.

- 6. Operator may opt to load separate geotailored threat libraries.

(The operator who chooses a separate loadable library must follow further load instructions cued on the DCC CRT screen.)

The speed of data transfer in steps 3 and 6 could be improved through a modification of the present system. Current tactical software is stored on one half of a single track of the MTC at a storage density of 1,600 bits per inch. Two changes could increase the data transfer rate from 48,000 to 768,000 bits per second. First, a new tape drive could quadruple the tape's storage density, increasing it from 1,600 to 6,400 bits per inch. Second, data could be stored in parallel across all four tracks of the tape. These changes would require both a new, faster interface to allow the faster transfer of data bits and substantial software modification. Future computer load time might be reduced to one minute; however, the tape spooling and rewinding time and the operator's tape handling time are inherent to the system and could not be eliminated. Because modifying the present system as described would require substantial software modification for the parallel track storage and would still not reduce the load time sufficiently, it is not a good memory expansion option.

<sup>\*</sup> Actual testing by F24 personnel at NSWC has determined that loading the AN/UYK-19 and the RP-16 with the current C6R1-11 program (~140K words) requires 70 seconds.

#### CHAPTER 4

#### HARDWARE OPTIONS

Ten different types of mass memory storage hardware options were considered for the AN/SLQ-32(V) system. Pertinent characteristics of high memory capacity options (3+ megabytes) are presented in Table 2. Characteristics of low memory capacity options are presented in Table 3. None of the low memory capacity options are recommended, however, since each would require considerable nonrecurring engineering (NRE) expenses, which would make its cost as great as the higher capacity options. Five hardware options were not investigated in detail because of inherent characteristics which made them unacceptable for AN/SLQ-32(V) use. These five are as follows:

- 1. Magnetic Floppy Disk. Magnetic floppy disks have limited storage density and a relatively slow data transfer rate, and they are easily damaged.

- 2. Electrically Erasable Programmable Read Only Memory (EEPROM). EEPROM chips have limited speed and storage density. Writing a lengthy set of programs could require hours since the write time is listed in milliseconds per byte. One EEPROM chip can hold approximately four kilobytes of data; consequently, storage of the AN/SLQ-32(V) software would require 750 EEPROM chips. The cost of the chips alone would be \$15,000 for each unit, not including packaging, control circuitry, and engineering. The chips would also require periodic replacement since they can accept only a finite number of write cycles before they are unusable.

- 3. Nonvolatile RAM. Like the EEPROM chips, nonvolatile RAM chips have inadequate speed and storage density for AN/SLQ-32(V) requirements. Another limitation is that each chip's built-in battery is non-rechargeable, thus limiting its lifetime to the lifetime of the battery. (However, battery lifetime might be up to ten years long.)

- 4. Magnetic Core Memory. Magnetic core memory, already used in the AN/UYK-19, is inadequate as a mass storage device because of its storage density. Two new input/output units containing 47 core memory cards would be required for 1.5 megawords of storage capacity, and they would offer no possibility of further software capability expansion.

TABLE 2. HIGH MEMORY CAPACITY HARDWARE OPTIONS

| SYSTEM<br>OPTIONS         | AVERAGE DATA<br>TRANSFER RATE<br>(KBYTES/SEC) | MEMORY<br>CAPACITY<br>(MEGABYTES) | MEETS<br>MIL-<br>SPECS | MTBF<br>(HR)<br>MTTR<br>(MIN)       | EST. WORST-<br>CASE DEVICE<br>BOUND LOAD<br>TIME (SEC) | COST                                        |

|---------------------------|-----------------------------------------------|-----------------------------------|------------------------|-------------------------------------|--------------------------------------------------------|---------------------------------------------|

| HARD DISK                 |                                               |                                   |                        |                                     |                                                        |                                             |

| VRC 8010                  | 625                                           | 10                                | 64                     | 10000 hrs<br>15 min                 | 2                                                      | \$20,000                                    |

| VRC 8520                  | 625                                           | 10–22                             | No                     | 10000 hrs<br>30 min                 | 2                                                      | 000*9 \$                                    |

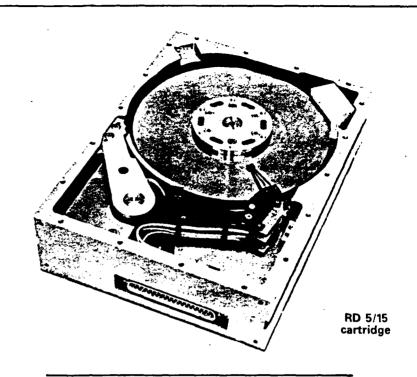

| MILTOPE<br>RD-5/15        | 625                                           | 5-15                              | Yes                    | 8000 hrs<br>15 min                  | 7                                                      | \$24,000                                    |

| ROLM 4150                 | 390                                           | 35.6                              | Yes                    | 3900 hrs<br>20 min                  | 7                                                      | \$36,500                                    |

| GENISCO<br>EDR-100        | 687.5                                         | 11.22-<br>30.06                   | MIL-<br>STD-<br>810    | ~9000 hrs<br>~15 min<br>(Estimated) | 7                                                      | \$12,000                                    |

| BUBBLE                    |                                               |                                   |                        |                                     |                                                        |                                             |

| MILTOPE<br>BMS-1000 (MOD) | 128                                           | e                                 | Yes                    | 10000 hrs<br>15 min                 | 9                                                      | 000,04\$                                    |

| LIBRASCOPE<br>RD-509/G    | 128                                           | ω                                 | Yes                    | 7000-10000 hrs<br>15 min typ.       | 9                                                      | \$190,000                                   |

| SPERRY/AEDAS              | 250                                           | 4-32                              | Yes                    | 7390 est.<br>15 min                 | 3                                                      | \$100,000<br>(for 25 to AEDAS<br>(PMA-253)) |

NSWC TR 85-133

\$125/64 kbyte chip+ Environment \$11,400 MIL-SPEC \$16,900 Extreme COST \$90,000 \$12,000 EST. WORST-CASE DEVICE

BOUND LOAD

TIME (SECS) 1 ~ S 7000-10000 hrs 15 min typ. 7000 hrs 15 min 10000 hrs 15 min 10000 hrs 30 min (MIN) MTBF (HR) MTTR Based MEETS MIL-SPECS on NRE Yes Yes (MEGABYTES) CAPACITY MEMORY 6.4 3+ S AVERAGE DATA TRANSFER RATE (KBYTES/SEC) 62.5 136 813 625 LIBRASCOPE MSS MILTOPE DD-400 BUBBLE (Cont.) BERNOULLI DISK MILTOPE BDS-501R WITH BATTERY OPTICAL DISK (see text) FLOPPY DISK DYNAMIC RAM OPTIONS SYSTEM DRIVE

(Cont.)

TABLE 2.

13

TABLE 3. LOW MEMORY CAPACITY HARDWARE OPTIONS

| SYSTEM                           | AVERAGE DATA<br>TRANSPER RATE<br>(KBYTES/SEC) | MEMORY<br>CAPACITY                    | COST                                                     | NRE    | DISADVANTAGES                                                                    |

|----------------------------------|-----------------------------------------------|---------------------------------------|----------------------------------------------------------|--------|----------------------------------------------------------------------------------|

| DYNAMIC RAM<br>WITH BATTERY      | 813                                           | 64 KBYTES/CHIP<br>12 CHIPS=768 KBYTES | \$125/CHIP<br>12 CHIPS=\$1500<br>BATTERY=\$21.50 OR LESS | YES    | NEEDS BATTERY CIRCUIT                                                            |

| NVRAM                            | 813                                           | 8 KBYTES/CHIP<br>90 CHIPS=720 KBYTES  | \$ 55.25/CHIP<br>90 CHIPS=\$4972.50                      | YES    | LIMITED CHIP LIFE<br>LOW MEMORY DENSITY<br>SOME HAVE SLOW WRITE<br>TIME          |

| KEPROM                           | 625                                           | 8 KBYTES/CHIP<br>90 CHIPS=720 KBYTES  | ~\$ 57/CHIP<br>90 CHIPS=\$5130                           | YES    | LIMITED WRITE CYCLES 10,000 TYP. LOW MEMORY DENSITY SLOW WRITE TIME              |

| EPROM                            | 488                                           | 64 KBYTES/CHIP<br>12 CHIPS=768 KBYTES | \$250/CHIP<br>12 CHIPS=\$3000                            | YES    | HIGH COST FOR LARGER MEMORY NEED UV LIGHT SOURCE ON SHIP TEDIOUS ERASE PROCEDURE |

| STANDARD BMS-1000 MILTOPE BUBBLE | 128                                           | 512 KBYTES                            |                                                          | INTER- | COST OF LOW MEMORY CAPACITY IS EQUIVALENT TO HIGH MEMORY CAPACITY OPTIONS        |

5. <u>Erasable Programmable Read Only Memory (EPROM)</u>. EPROM chips require ultraviolet lamps to erase their contents and are relatively expensive (as much as \$250 each).

The five other hardware options considered in this investigation were found to be feasible. These options (magnetic hard disk, optical disk, magnetic bubble memory, RAM with battery backup, and Bernoulli disk drive) are discussed in detail below.

#### MAGNETIC HARD DISK

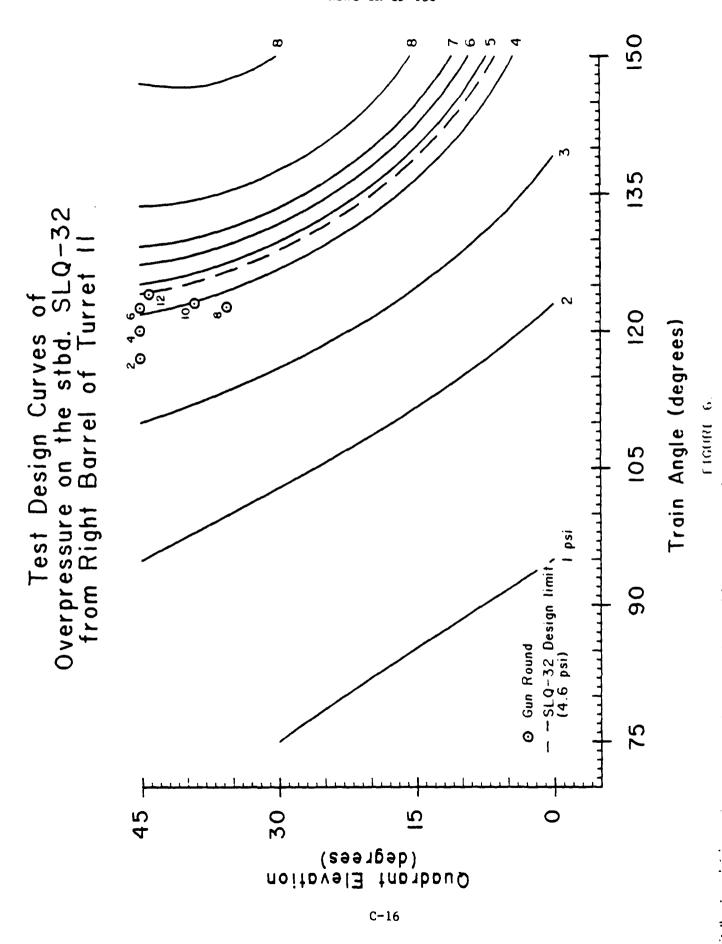

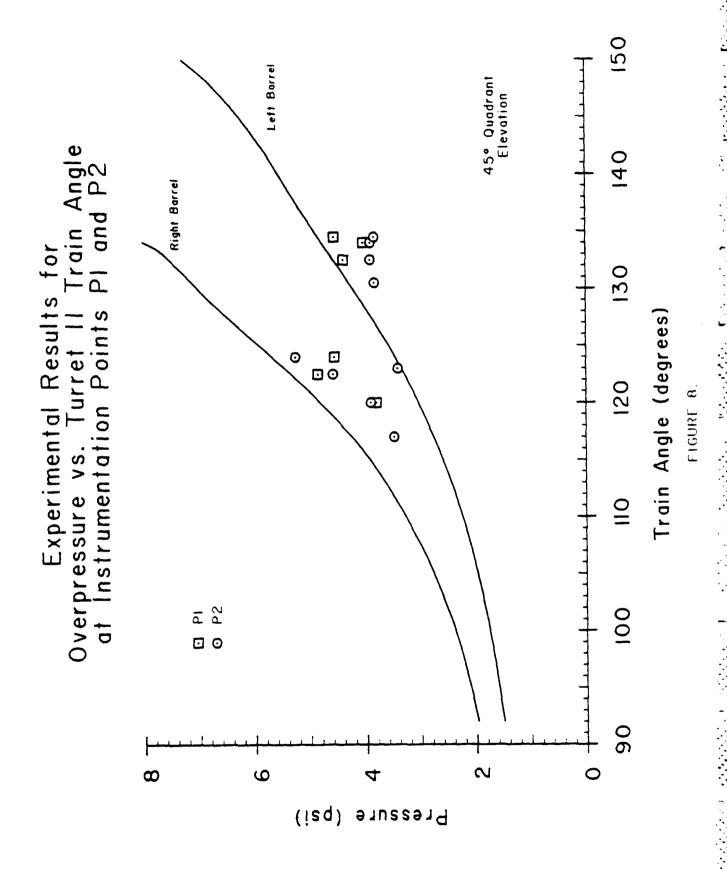

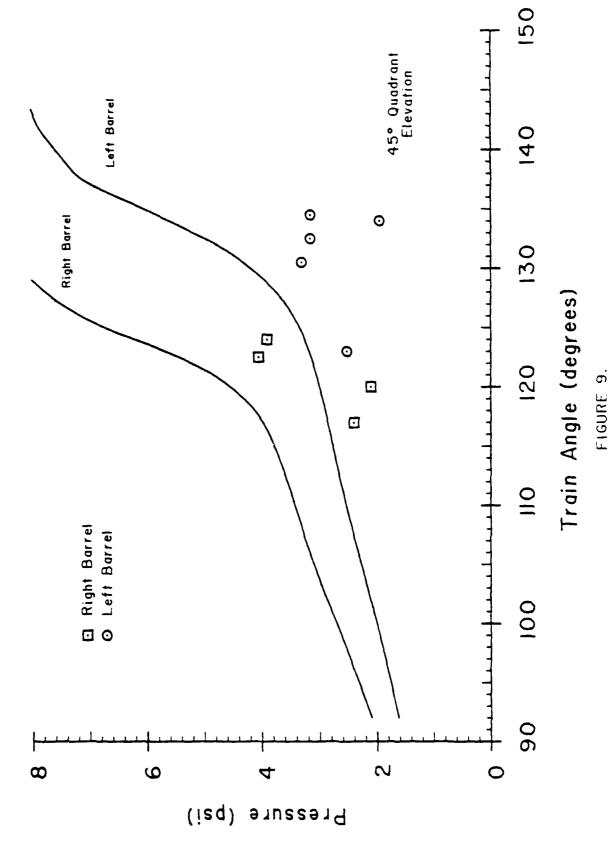

The magnetic hard disk is an electro-mechanical device which offers dense memory storage and rapid data access and transfer. Its dense storage and rapid access time require that the read heads, which perform the data extraction, be situated very close to the recording medium. If the disk is vibrated, impacted, or accelerated too quickly, the high-speed rotating medium can be damaged by contact with the read heads or the enclosure. Shock and vibration from the firing of 5-inch guns on a Naval ship could destroy a disk not designed to withstand such treatment. Only a very sturdy disk system built to conform to rigid military specifications could withstand the shock and vibration from a ship with 16-inch guns, such as the battleship New Jersey. (Appendix C presents shock and vibration test results from the New Jersey.)

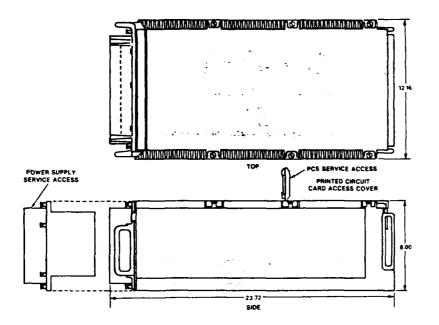

A wide variety of magnetic hard disks is available, but only two are military standard: the UYH-2 and the UYH-3. These disks are large (refrigerator-sized), heavy (~300 pounds), and expensive (~\$200,000), making them unrealistic choices except perhaps for the battleships New Jersey and Iowa. This section of the report describes the investigation of some smaller and less expensive commercial hard disks. Table 4 shows a comparison of cost, size, memory capacity, and environmental sturdiness for four of these disks: the Miltope RD-5/15, the ROLM 4150, the VRC 8520, and the Genisco EDR-100. Advertising sheets for the Miltope, VRC, and Genisco disks are included in Appendix A. The ROLM sheet is not included because ROLM copyrights its advertisements.

Any nonmilitary standard hard disk selected for AN/SLQ-32(V) use should first be thoroughly tested on ship or in a simulated environment to ensure that the device can withstand the shock and vibration of the firing of guns.

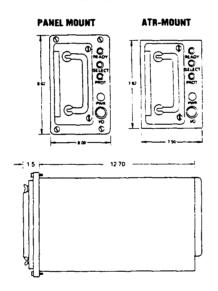

#### Miltope RD-5/15

The Miltope RD-5/15 hard disk offers up to 15 megabytes of memory storage, a data access rate of 40 milliseconds (msec), and a data transfer rate of 625 kilobytes per second. These exceed requirements for AN/SLQ-32(V) use.

The Miltope RD-5/15 disk is "militarized," which means that it has been built to conform to military specifications for shock, temperature, and vibration. Militarized does not mean that the disk has passed government tests ensuring this conformity, however. Table 5 lists the requirements for the AN/SLQ-32(V) system. Although the RD-5/15 appears to meet or exceed these requirements, testing is essential if this disk is selected for shipboard use.

TABLE 4. MAGNETIC HARD DISK SPECIFICATION COMPARISON

|                          | MILTOPE RD-5/15                                              | ROLM 4150                          | VRC 8520                            | GENISCO EDR-100                 |

|--------------------------|--------------------------------------------------------------|------------------------------------|-------------------------------------|---------------------------------|

| COST                     | \$24,000                                                     | \$36,500                           | 000*9\$                             | \$12,000                        |

| SIZE                     | ATR PANEL<br>W 7.5" 8.0"<br>D 13.63" 13.63"<br>H 7.62" 8.62" | W 19.0"<br>D 24.0"<br>H 12.25"     | W 8.55"<br>D 16.61"<br>H 7.0"       | W 19.0"<br>D 20.0"<br>H 7.0"    |

| WEIGHT                   | 25 lbs                                                       | 125 1bs                            | 34 1bs                              | 50 lbs                          |

| MEMORY<br>CAPACITY       | 5 to 15 megabytes                                            | 35.6 megabytes                     | 10 to 22 megabytes                  | 11 to 30 megabytes              |

| OPERATING<br>ENVIRONMENT |                                                              |                                    |                                     |                                 |

| TEMPERATURE              | -30° to 55°C                                                 | -30° to 55°C                       | 0° to 55°C                          | 0° to 50°C                      |

| RELATIVE<br>HUMIDITY     | 5% to 100%                                                   | MIL-STD-810C CAT 1                 | 5% to 90%                           | 0% to 95%                       |

| ALTITUDE                 | 1                                                            | 1                                  | -1000 to 8000 ft                    | 0 to 1000 ft                    |

| SHOCK                    | 15 g for 11 msec                                             | 15 g for 11 msec                   | 2 g for 11 msec<br>2 per second max | 20 g for 11 msec                |

| VIBRATION                | .075" displacement<br>5 to 2000 Hz                           | .075" displacement<br>5 to 2000 Hz | .01" displacement<br>5 to 20 Hz     | 0.1" displacement<br>5 to 10 Hz |

| MTBF                     | 8000 hrs                                                     | 3900 hrs                           | 10000 hrs                           | ~9000 hrs                       |

| MTTR                     | 15 min                                                       | 20 min                             | 30 min                              | ~15 min                         |

|                          |                                                              |                                    |                                     |                                 |

TABLE 4. (Cont.)

|                       | MITTODE BID-5/15                        | ROI.M 4150                | VRC 8520           | GENISCO EDR-100                          |

|-----------------------|-----------------------------------------|---------------------------|--------------------|------------------------------------------|

|                       | arrior an experience                    |                           |                    |                                          |

| SERVICE LIFE          | Not Listed                              | Not Listed                | 5 yrs or 30000 hrs | Not Listed                               |

| NONOPERATING<br>SHOCK | 30 g for 11 msec                        | 30 g for 11 msec          | 6 g for 16 msec    | MIL-STD-810<br>Method 516.1,             |

|                       |                                         |                           |                    | Procedure V for<br>nonoperating<br>shock |

| MILITARY              | MIL-STD-810                             | MIL-STD-810C              | None               | MIL-STD-810                              |

| STANDARDS<br>CITED    | MIL-E-16400<br>MIL-E-5400<br>MIL-E-4158 | MIL-E-16400<br>MIL-E-5400 |                    |                                          |

|                       | MIL-STD-461<br>TEMPEST NACSEM 5100      |                           |                    |                                          |

TABLE 5. AN/SLQ-32(V) ENVIRONMENTAL REQUIREMENTS (From ELEX-C-241E)

| CONDITION    | MIL SPEC CITING<br>REQUIREMENTS     | EXC                                  | EXCEPTIONS TO MIL SPEC REQUIREMENTS         | C REQUIREMEN                                            | TS                                                     |                                                                    |

|--------------|-------------------------------------|--------------------------------------|---------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------|

| TEMP ERATURE | MIL-E-16400                         | Equipment Interior Exterior Exterior | Class 4 2 2                                 | Operating  0°C to +50°C  -28°C to +50°C  -28°C to +65°C |                                                        | Nonoperating<br>-54°C to +75°C<br>-54°C to +75°C<br>-54°C to +75°C |

| SHOCK        | MIL-S-901,<br>Grade A,<br>Class III |                                      | None                                        |                                                         |                                                        |                                                                    |

| VIBRATION    | MIL-STD-167-1,<br>Type 1            | Equipment t                          | Direction Relative to Ship's Heading 3 axes | Frequency (Hz) 4-10 11-15                               | Level (Double Amplitude) mm inches 5.08 0.20 1.52 0.06 | 1<br>plitude)<br>inches<br>0.20<br>0.06                            |

|              |                                     | Interior                             | 3 axes                                      | 10-25<br>4-15<br>16-25                                  | 1.02<br>1.02                                           | 0.06                                                               |

|              |                                     | Exterior (except<br>Band l antenna)  | Vertical,<br>athwart                        | 4-11<br>12-15<br>16-20<br>21-25                         | 2.29<br>1.52<br>0.77<br>0.51                           | 0.09<br>0.06<br>0.03<br>0.02                                       |

|              |                                     | Exterior (except<br>Band l antenna)  | Longitudinal                                | 4-15<br>16-25                                           | 1.02                                                   | 0.04                                                               |

The Miltope RD-5/15 has the advantage of being cheaper (~\$24,000) and less bulky than the other militarized disk investigated for this report. It has the disadvantage of not having a proven reliability record in government service. ROLM Corporation has agreed with Miltope to develop an interface to the ROLM computer (AN/UYK-19) which would be compatible with the Miltope SCSI interface. At the time of this report, however, the RD-5/15 had not been delivered to ROLM for the engineering work to begin.

#### ROLM 4150

The ROLM 4150 hard disk offers up to 35.6 megabytes of memory storage, a data access rate of 42 msec, and a data transfer rate of up to 390 kilobytes per second. These exceed the requirements for AN/SLQ-32(V) use.

The militarized ROLM 4150 has been designed and built to conform to rigid military specifications. ROLM products (e.g., AN/UYK-19 computer) have proved their reliability in government service. Since ROLM engineered and produced the AN/UYK-19 computer, the engineering required to interface the computer to the hard disk is minimal. If selected for shipboard use, however, the ROLM 4150 would be difficult to mount because of its relative bulkiness: 125 pounds and 3 cubic feet. It is also more costly (\$36,500) than the other disks investigated for this report.

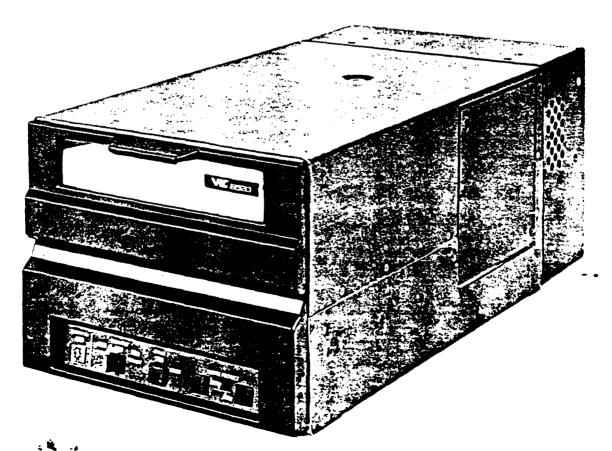

#### VRC 8520/VRC 8010

The third hard disk investigated, the Vermont Research Corporation (VRC) model 8520, offers up to 22 megabytes of memory storage, a data access rate of 58 msec, and a data transfer rate of 625 kilobytes per second. These exceed the requirements for AN/SLQ-32(V) use.

The V°C 8520 is the least expensive of the hard disks investigated for this report. The basic cost for each unit would be \$6000 for the disk, \$125 for each cartridge, and \$250 for the mounting rack.

Unfortunately, the VRC disk is a "ruggedized" unit. Ruggedized means that the disk is usable in an industrial environment without being shackled to an office worker's desk. It is much less resistant to vibration and shock than the militarized Miltope RD-5/15 and ROLM 4150. Dr. Jon Yagla, an NSWC expert in the area of shipboard shock and vibration, has determined that the ruggedized VRC 8520 could not survive operationally in combat situations, even if it were mounted to dampen vibration and shock.

VRC produces another hard disk, the VRC 8010, with specifications almost identical to the VRC 8520. This disk is presently being modified by ROLM to increase its environmental durability and to facilitate its interface with ROLM military computers. The modification will increase the height and width of its chassis by approximately two inches. Graham Hall, AN/SLQ-32(V) project manager for Raytheon Corporation, has estimated the cost of the modified VRC 8010 to be \$20,000 per unit.

#### Genisco EDR-100

The Genisco EDR-100 hard disk offers up to 30 megabytes of memory storage, a data access rate of 68 msec, and a data transfer rate of 687.5

kilobytes per second. These exceed the requirements for AN/SLQ-32(V) use.

Although the Genisco EDR-100 is classified as ruggedized, it has been designed and built to meet the shock and vibration specifications of MIL-STD-810. These are itemized in its advertisement sheet in Appendix A.

The EDR-100 offers several advantages over the other hard disks investigated. It can be mounted in any orientation, its dual disk drive permits separate storage of classified information, and its price is \$12,000.

#### OPTICAL DISK

Optical disk systems store data by burning the recording medium (i.e., disk) with a high-powered laser, causing pits or blisters on the surface. A lower-powered laser is used to read the recorded data. Data storage and access requires a precise alignment of the laser, mirror, and disk components of the device. This alignment on a nonmilitarized device could be disturbed by the shock and vibration of guns firing. Only a militarized unit should be considered for fleet use.

Two types of optical disk systems are currently in production. Readonly devices are relatively inexpensive, selling for several hundred dollars each. These are not recommended for AN/SLQ-32(V) use, however, since the entire process of software delivery to the fleet would have to be changed. Devices capable of both reading and writing data have been investigated for this report because they would more likely meet fleet requirements.

At present optical disks can be written only once since they are nonerasable. However, the storage capacity of most present optical disks is l gigabyte, and this is sufficient for all current AN/SLQ-32(V) programs to be written 300 times on a single disk. This capacity would certainly meet storage requirements for all anticipated software expansion.

The following optical disk systems, listed by manufacturer, were investigated for possible AN/SLQ-32(V) use:

1. RCA. RCA has developed an impressive optical disk system containing 1250 gigabytes of data on 128 optically recorded disks. This system, which was developed for the U.S. Air Force, has a random access time of six seconds or less for any byte. It works in a manner similar to a juke box except that multiple disks can be accessed simultaneously. The unit requires 32 square feet of floor space and costs approximately \$1 million dollars.

RCA is currently developing a smaller-sized militarized single-disk optical system which will be available for \$100,000 per unit in 1987. No specifications are readily available for this system.

2. Alcatel Thompson. The GD 1001 produced by Alcatel Thompson has a data access rate between 5 and 200 msec, depending on whether the search is within or outside a current band of tracks. Its data transfer rate is 479 kilobytes per second. The GD 1001 weighs 50 pounds and is approximately the size of a phonograph. It uses both

single-sided and dual-sided disks, and its cost is \$13,000 per unit plus \$315 for each single-sided disk.

The Combat Systems Engineering branch (N24) of NSWC recently acquired by competitive contracting a GD 1001 as a possible replacement for their RD 358 tape drive system. Personnel from N24 could supply additional information on this optical disk system.

- 3. Shugart Corporation. The Optimem 1000 manufactured by Shugart has a storage capacity of 1 gigabyte per disk and a data transfer rate of 625 kilobytes per second. Its cost is approximately \$13,600 plus \$400 for each disk.

- 4. Storage Technology. An optical disk system produced by Storage Technology has a storage capacity of 4 gigabytes per disk and a data transfer rate of 1500 kilobytes per second. Unfortunately, it costs \$130,000 per unit.

- 5. Sony Corporation. A Sony optical disk system will be available in both 8" and 12" disk sizes in August, 1985. The data access rates are listed as 1.2 seconds across tracks and 0.5 seconds within a track. The data transfer rate is listed as 300 kilobytes per second. The 8" disk system is a compact 14.75" x 6.75" x 7.875". The projected cost is \$9,300.

- 6. Cherokee Data Systems. A 250 megabyte optical disk system being developed by Cherokee Data Systems, a newly-formed optical disk company, will be available in 1987. This unit will be ruggedized and will occupy the space of a standard desk-top floppy disk unit. The projected price for this system is \$2,700 per unit.

- 7. National Memory Systems. National Memory Systems makes a 12" optical disk which uses the Optimem 1000 drive. Its storage capacity is 1 gigabyte, and its cost is \$23,500 in quantities of one.

The optical disk systems investigated for this report present two major problems in their consideration for AN/SLQ-32(V) use. First, none of the reasonably priced units currently available are built to military specifications. Second, availability is limited and delivery time is substantial, based on the experience of the NSWC acquisition of the GD 1001. Thus, the optical disk systems do not seem likely candidates for immediate AN/SLQ-32(V) use.

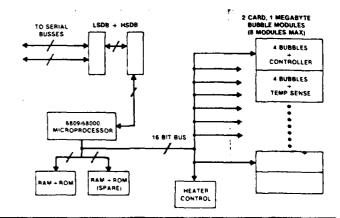

#### MAGNETIC BUBBLE MEMORY

A magnetic bubble memory system is a high density, solid state, nonvolatile serial read/write storage device. It is compact and reliable, requires no routine maintenance, and can operate under harsh conditions such as high humidity, dust, vibration and shock, and temperature extremes. The basis of bubble memory technology is the existence of magnetic domains within a thin film. The domains shrink to cylindrical "bubbles" in the film when they are exposed to an external magnetic field. A rotating magnetic field is then used to move the bubbles along their data loop.

Bubble memory systems have both advantages and disadvantages over magnetic hard disk systems. Because the bubble memory system is a solid state device, it offers an inherent reliability and sturdiness not offered in the electro-mechanical hard disk. The software required for interfacing bubble memory to the AN/SLQ-32(V) is less extensive than that required for disk because of the sector checking required for disk. On the other hand, bubble memory storage capacity and data transfer rates, although adequate, are not as good as those of the hard disks and optical disks. The cost per unit of storage capacity is substantially more for bubble memory than for disk. Its technology is expanding rapidly, however, and this should drive the costs down.

Only two vendors presently make bubble memory for general use--Motorola and Intel. Sperry uses the Motorola product, which is reputed to offer better functional performance. Librascope uses the more widely sold Intel product.

Three bubble memory systems were investigated for this report and are described below. Three other systems were proposed by manufacturers who could provide the systems.

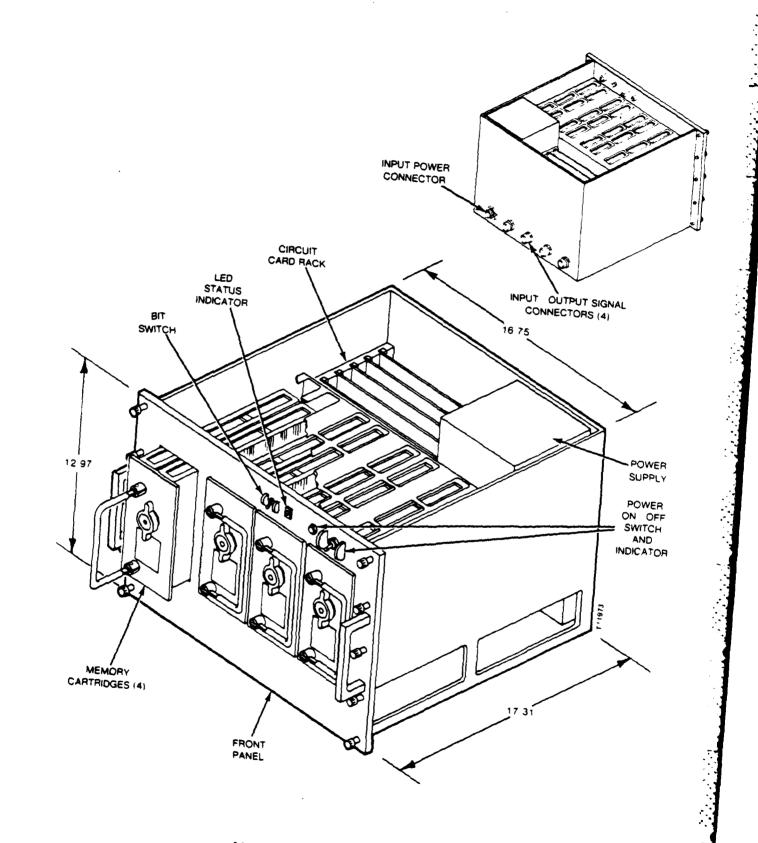

#### Librascope Expanded Memory

The Librascope Expanded Memory (RD-509/G) has a storage capacity of 8 megabytes, a data access rate of 40 milliseconds, and a data transfer rate of 1 megabit per second. These meet the requirements for AN/SLQ-32(V) use.

The RD-509/G is 1.48 cubic feet in size and weighs 75 pounds. Because the unit has been built and tested to military specifications (U.S. Army contract DAAK80-79-0016), it should be capable of withstanding the rigors of sea duty. At \$190,000 per unit, though, it is too expensive for widespread fleet use. An advertisement sheet for the Librascope Expanded Memory is included in Appendix A.

#### Librascope Mass Storage Subsystem

The Librascope Mass Storage Subsystem (MSS) is an 8-megabyte bubble memory system being developed for use in the MX Peacekeeper missile, the U.S. Army's Communication Control Switch in the Tactical Fire Support Systems, and the Royal Australian Navy's Mark I Torpedo Fire Control System. Information on this military-standard bubble memory system is included in Appendix A. Librascope has proposed building a similar system for AN/SLQ-32(V) use at a cost of \$90,000 per 4-megabyte unit. The price would be prohibitive for widespread fleet use but is worth consideration for battleship use.

#### Sperry/AEDAS

Sperry is developing a militarized bubble memory system in an Air Transport Receiver (ATR)-sized package for the AEDAS program (PMA-253). The functional features of this device are much better than those of other devices investigated for this report. It will have an NTDS interface, a storage capacity variable from 4 to 32 megabytes, a data transfer rate of 250 kilobytes per second, a data access rate of 12.5 msec, and rapid memory purge at the press of a button. The cost for the four initial units is \$700,000.

Twenty-five additional units will be delivered for \$100,000 each. If units were purchased in quantity for AN/SLQ-32(V)-equipped ships, the price would probably be further reduced.

#### Other Proposed Systems

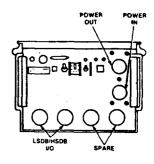

The Miltope BMS-1000 is a militarized bubble memory unit which offers a maximum storage capacity of 256 kilobytes. An advertisement sheet for the BMS-1000 is included in Appendix A. Although the BMS-1000 would be inadequate for AN/SLQ-32( $\forall$ ) use, the Miltope marketing director has indicated that Miltope could produce a similar 3-megabyte unit for approximately \$40,000 per unit.

A ROLM sales representative proposed two bubble memory options which ROLM could produce for the AN/SLQ-32(V). It could produce a 4-megabyte system in a half-sized ATR chassis for approximately \$50,000 per unit. No operating specifications for this proposed device were offered. The ROLM representative also proposed the installation of two bubble memory cards in two presently empty core memory planes in the AN/UYK-19 I/O boxes of the AN/SLQ-32(V). These two cards would provide enough memory to store the tactical programs and libraries but not the SDT programs. The cost for this proposed bubble memory system would be approximately \$700,000 in initial engineering costs and \$30,000 for each unit.

#### RAM INTEGRATED CIRCUITS WITH BATTERY BACKUP

Recent advancements in electronic technology have produced RAM integrated circuit chips with large memory capacities, rapid data access, low power requirements, and low cost. These characteristics make a mass memory storage system using RAM chips a feasible alternative to a hard disk, optical disk, or bubble memory system.

A 3-megabyte mass memory system using low-power (CMOS-technology) dynamic RAM chips would require a constant power supply of only 23 milliamps for data storage. Unfortunately, the refresh circuitry required to sustain the electrical charge necessary for memory retention is not yet readily available on these CMOS chips. If higher-power (NMOS-technology) RAM chips were used, the storage system would require approximately 300 milliamps of continuous current to retain memory.

Because a RAM chip storage system would lose all of its data if power were removed, it would require a rechargeable battery circuit as a backup for the power supply. A nickel cadmium or lead acid battery could provide the power necessary to keep memory intact for hours or days. Gelyte manufactures a 20-amphour rechargeable lead battery which could retain memory for 60 hours. This battery, which sells for \$21.85, is 7.5" x 2.3" x 5.7"; but smaller batteries offering fewer amphours are available.

The memory storage capacity of a dynamic RAM system is very attractive. Several manufacturers, including Texas Instruments and Intel, produce 16-pin dynamic RAM chips with a storage capacity of 32 kilobytes per chip. A 3-megabyte system could be developed using 93 RAM chips on five or six printed

circuit cards. If such a system were designed and built to military specifications, the cost for the RAM chips, back-up circuitry, packaging, and engineering might be approximately \$30,000 per unit. However, the CMOS technology of these low-power chips is still relatively new, and prices are likely to decrease substantially in the future. Various normilitary standard systems are already available off the shelf for under \$10,000, but these are not recommended for AN/SLQ-32(V) use in the fleet.

The data access rate of the RAM chip is extremely rapid. For example, the Intel 51C256-L RAM chip has a maximum bit-access rate of 150 nanoseconds. At that rate 813 kilobytes could be accessed in a single second.

The dynamic RAM concept of memory storage offers the reliability of solid state design. Its functional capability, relatively small size, and potential for software expansion make it an attractive option. Future advances in CMOS circuit technology will undoubtedly provide the potential for months of sustained memory from a small battery, even greater storage density and speed, and reduced costs.

## BERNOULLI DISK DRIVE

The Bernoulli disk drive system uses the principle of Bernoulli's Law to maintain a close distance and an air bearing between its flexible recording medium and its read/write head. The basic concept of the device is that the flexible recording medium (disk) spins next to a planar surface called the Bernoulli plate. A thin cushion of circulating air between the flexible spinning disk and the Bernoulli plate maintains a relatively constant distance between the two, greatly reducing damage from contamination and from shock and vibration. This concept of data storage and retrieval using Bernoulli's Law was developed by personnel at IOMEGA Corporation.

Miltope Corporation has developed ruggedized versions of this Bernoulli disk drive system. The BDS-5R series of ruggedized disks has impressive characteristics. The BDS-50lR stores 5 megabytes of data and has an average access rate of 39 milliseconds and a data transfer rate of 625 kilobytes per second. Larger storage capacities are available in other versions. The BDS-50lR weighs twenty pounds and measures 8 1/2" x 9 3/8" x 11 3/4". Its cost is approximately \$12,000.

The flexible disk comes enclosed in a hard plastic cartridge which automatically exposes the recording surface when the cartridge is placed in the disk drive. The disk cartridges cost about \$50. An advertisement sheet for the BDS-5R series of Bernoulli disk drive systems is included in Appendix A.

#### CHAPTER 5

#### INTERFACE CONSIDERATIONS

Regardless of the type of mass storage device chosen, substantial changes would be required to interface the device to the AN/SLQ-32(V) system. The programming and engineering changes described in this chapter would require several man-years of effort and could comprise the greatest cost of implementing mass storage devices in the fleet. The changes will be even greater and more costly if the mass storage devices on the battleships are different from those in the rest of the fleet.

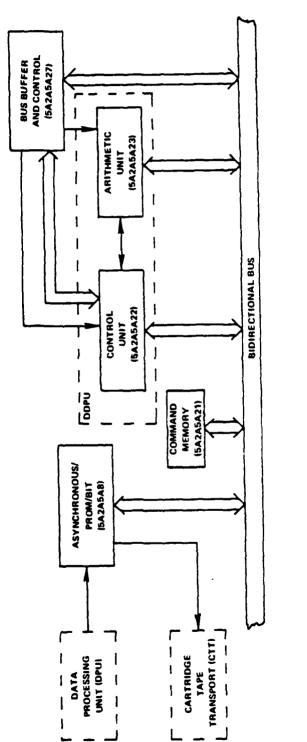

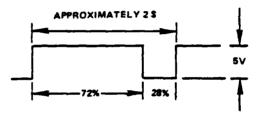

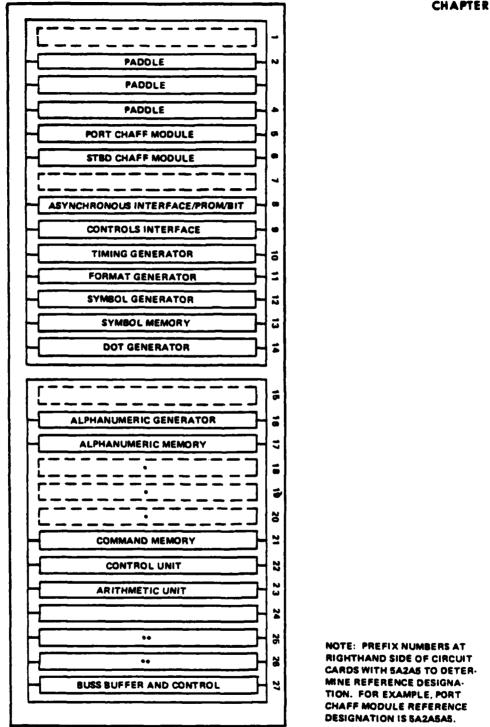

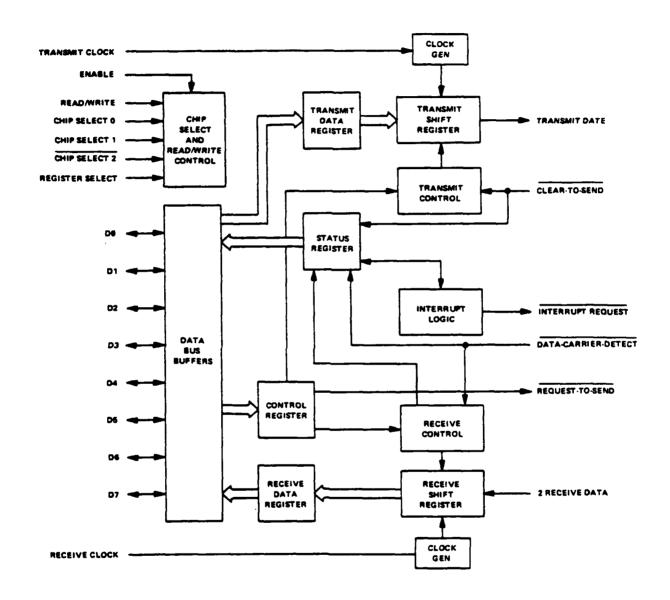

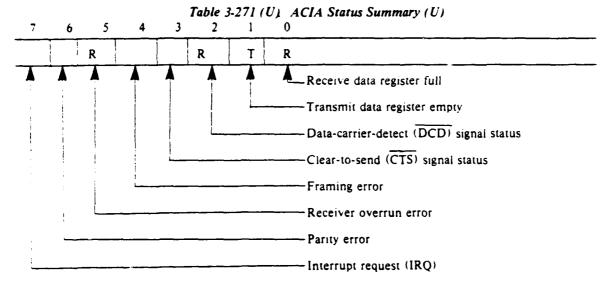

The firmware, software, and hardware of the AN/SLQ-32(V) are presently designed so that all information flows through the RP-16 to the AN/UYK-19 during program load. The program load process is accomplished by two programmable read only memories (PROMs). When the operator presses the Program Load button on the DCC, the RP-16 PROM loads the RP-16 random access memory (RAM) with two programs stored on tape: the primary RP-16 program and the CP-32 debug program. The AN/UYK-19 PROM communicates with the RP-16 PROM and loads AN/UYK-19 memory with the tactical software. The program logic for this loading process (Figure 3) would have to be retained for the purposes of backup and for software delivery via MTC.

At the same time a new loading concept for use with a mass storage device would have to be developed so that the benefits of quick loading and data access could be realized. The new program logic (Figure 4) would have to provide the AN/UYK-19 with a direct connection to the device via the I/O bus or direct memory addressing (DMA) so that the AN/UYK-19 could load itself and all peripheral processors, including the RP-16. The new loading process would involve changes to the present firmware (PROMs), software, and hardware.

#### SOFTWARE CHANGES

#### ROLM 1606 Auxiliary Memory Program

A new AN/UYK-19 program must be designed to load the new mass storage device from the old tape system so that the MTC can still be the transportable medium for software delivery. This new program, which is identified in this report as RAMP (ROLM 1606 Auxiliary Memory Program), should also provide several other options to allow full utilization of the new unit:

1. Cataloging new memory unit files. This capability would allow the operator to know the programs available.

#### RP-16 PROM Program Logic

if No tape is in tape drive then

if CP-32 program is loaded in RP-16 RAM then

Execute CP-32 program;

<u>else</u>

Dump DCC status to display screen; endif

#### else

if Operational tape is in tape drive then

Load RP-16 program from tape;

Transfer control to RP-16 RAM;

RP-16 RAM program transfers UYK-19 program data to

UYK-19 PROM;

UYK-19 PROM loads UYK-19 program data,

including loader program (TPLDR), into

UYK-19 RAM;

UYK-19 PROM transfers control to TPLDR in UYK-19

RAM;

TPLDR loads remainder of operational program

into UYK-19 RAM and begins program execution;

#### <u>endif</u>

#### endif

#### FIGURE 3. PRESENT PROGRAM LOAD PROCESS

### RP-16 PROM Logic to Incorporate a Mass Storage Device

if No tape is in tape drive then

if New memory unit is operational then

Transfer control to UYK-19 PROM;

UYK-19 PROM loads new loader program into UYK-19 RAM;

UYK-19 RAM loader program gets RP-16 RAM program from memory unit and transfers it to the RP-16, loads peripheral processors, if any (Band 1, ADLS, etc.), from the memory unit, loads operational program in UYK-19, loads preselected main and on-line libraries, and begins program execution;

<u>else</u>

Give an error message or execute CP-32 program; endif

else -- A tape is in tape drive

if Tape drive contains operational program or SDT tape then RP-16 PROM performs same processing as present program load (see Figure 3);

endif

if Tape drive contains RAMP program tape then RP-16 PROM transfers control to a RAMP loader section of UYK-19 PROM; UYK-19 PROM inputs the RAMP loader, which will load and begin executing RAMP program;

<u>endif</u>

endif

FIGURE 4. MODIFIED PROGRAM LOAD PROCESS TO INCORPORATE NEW MASS STORAGE DEVICE

- 2. Transferring programs/files from the storage unit to tape. This capability would permit the creation of back-up tapes from the new unit.

- 3. Transferring programs/files from tape directly into the new unit.

- 4. Loading and executing SDT programs from the new unit.

- 5. Loading and executing tactical programs from the new unit.

- 6. Designating main and on-line libraries from the selection contained in the new unit. This capability would eliminate all operator loading actions except pressing the Program Load button, an essential feature for combat situations.

The capabilities for auto-dumping and for building and storing libraries on the new unit would also be desirable features.

#### Tactical Software

The present tactical software would have to be modified in order to provide the option to load and execute RAMP directly from the mass storage device. This capability could be included within ANAL FAB or READ LIBRARY FAB processing. The tape I/O handler would also require expansion to process data from either the tape or the new unit. Finally, the software must provide decision logic for determining the proper source (i.e., tape or mass storage device) for reading in libraries and for loading peripheral processors.

#### SDT Software

The SDT software would have to be modified in order to execute the diagnostic programs directly from the new unit. NSWC experts have made the following recommendations for maximizing use of the new unit while preserving hardware integrity:

- 1. Continue to load tests for CTT, DCC, DPU, and associated interfaces from tape.

- 2. Add a new SDT to check the new unit and its associated interface.

- 3. Rewrite overlay-segment handling section of full master supervisor, branch and control supervisor, and DPU master supervisor.

#### HARDWARE/FIRMWARE CHANGES

The actual complexity of the hardware and firmware changes cannot be assessed until a mass storage device has been selected and designed. This section addresses the mounting and interfacing considerations which will be required regardless of the device chosen.

The location of the mass storage device will depend on the device chosen, but it could be critical to the functioning of the system. If it is not located close to the AN/UYK-19, a high-speed fiber-optic communications link might be required. Although (V)3 systems have an empty slot in Rack 2, this space should be reserved for the additional equipment required for atsea system tests.

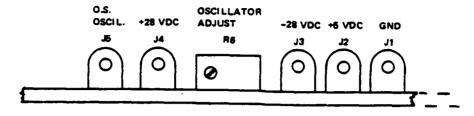

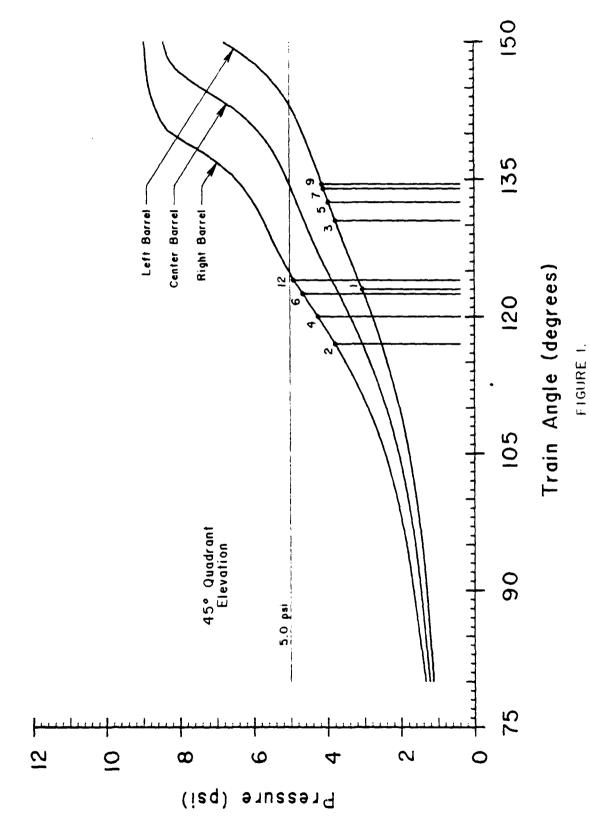

Interfacing the new device to the AN/UYK-19 I/O bus will require a modification of both the RP-16 PROM and the AN/UYK-19 PROM. The RP-16 PROM resides in two 1-kilobyte chips (Ul2 and Ul3) on the ROLM interface card (Figure 5). Only 14 words remain unused in these chips. Since the card offers no space for additional chips, present chips must be replaced with new chips offering denser memory storage in order to do the new processing. This modification might also involve backplane wiring changes in the DCC. The AN/UYK-19 PROM must be replaced with a new PROM containing the firmware to accommodate the storage device. However, the special interfacing required between the storage device and the AN/UYK-19 could be located in the new unit, eliminating the need for further AN/UYK-19 PROM modification.

30

#### CHAPTER 6

#### CONCLUSIONS

The investigation conducted for this report has established a definite need for a mass memory storage device for AN/SLQ-32(V) use. Present program loading requires more than a minute, and future software expansion could extend that time to five minutes or more. This time span could be fatal in a combat situation.

The most important considerations in reducing current load time are storage capacity and data access and transfer rates. Storage capacity should be sufficient to store all current and future tactical and diagnostic software. Data access and transfer should be accomplished in ten seconds or less. Another important consideration for a mass memory storage system is its reliability. Once a device of this type is implemented, its uses may expand to the point where the AN/SLQ-32(V) system could not function without it. Other considerations in this investigation included the size of the device, the cost per unit, and the ease of installation.

Modification of the present magnetic tape system would not reduce load time sufficiently. Storage density and data transfer rates could be increased, but the operator handling and rewinding times inherent to the tape system cannot be improved.

Five hardware options were investigated in detail and were found to be feasible in improving program load time, but none of these were ideal. Magnetic hard disks are readily available but may not be durable enough in a high shock and vibration environment. Optical (laser) disks offer enormous storage capacities; however, they are relatively untried devices, and they require expensive write-once disks. Magnetic bubble memory devices have low maintenance requirements but are very expensive. Dynamic RAM with battery backup offers great potential in speed, sturdiness, and reliability; but no militarized systems with sufficient storage capacities are available. The Bernoulli disk is most promising with its large storage capacity, fast data access and transfer rates, resistance to shock and vibration, and low cost. Testing for military use has not yet been completed, however.

Regardless of the type of device or devices selected for fleet use, considerable changes to the software, firmware, and hardware will be required. These changes will be even greater if one type of device is selected for battleships with extreme shock and vibration conditions and another type is selected for the rest of the fleet. Program load, which now flows from the magnetic tape through the RP-16 PROM to the AN/UYK-19 computer, must be changed to permit a direct connection between the new storage device and the

#### NSWC TR 85-133

AN/UYK-19. At the same time, the current loading method must be retained for the purposes of program backup and software delivery. The engineering and programming efforts required to accomplish these changes are likely to comprise the greatest cost of implementing mass storage devices in the fleet.

#### CHAPTER 7

#### RECOMMENDATIONS

As a result of the investigation conducted for this report, the following recommendations are made:

- 1. Any device selected for use in the fleet must be tested to military specifications to withstand extreme shock and ibration conditions.

- 2. A single type of device should 1 selected for both battleships and other ships in the fleet in order to prevent possible software and hardware incompatibility problems.

- 3. The present method of software delivery via magnetic tape cartridges should be retained.

- 4. The storage capacity of the selected device(s) should be great enough to contain both the tactical and the diagnostic software.

- 5. The greater storage capacity should not be used to increase the size of the emitter threat library since additional emitters increase, rather than decrease, ambiguities. The size of the threat library should only be increased if more or better discriminants become available.

- 6. If sufficient time and money are available, some or all of the most promising hardware options should be prototyped. These include the Miltope, Genisco, and VRC magnetic hard disks, the Alcatel Thompson optical disk, the dynamic RAM memory system, and the Miltope Bernoulli disk.

- 7. As an alternative to prototyping, the U.S. Navy could advertise a "Sources Sought" for a mass memory storage device which meets the required specifications.

- 8. Competitive contracting should be used for the production contract in order to obtain the optimum cost/performance ratio.

#### NSWC TR 85-133

#### NOMENCLATURE

ADLS Automated Decoy Launching System

AN/UYK-19 ROLM model 1606 computer ATR Air Transport Receiver

CMOS Complementary metallic oxide semiconductor

CP-32 AN/SLQ-32(♥) debug program

CRT Cathode ray tube (display screen)

CTT Cartridge Tape Transport unit

DCC Display and Control Console

DMA Direct memory addressing

DPU Digital Processing Unit

ECM Electronic countermeasures

EEPROM Electrically erasable programmable read only memory

EPROM Erasable programmable read only memory

EW Electronic warfare

MSS Mass Storage Subsystem

MTC Magnetic tape cartridge

NMOS Noncomplementary metallic oxide semiconductor

NRE Nonrecurring engineering (expenses)

NSWC Naval Surface Weapons Center

NTDS Naval Tactical Data System

PROM Programmable read only memory

RAM Random access memory

RAMP ROLM 1606 Auxiliary Memory Program RP-16 Microprocessor located in DCC

SDT System Diagnostic Test

UYH-2 and UYH-3 Magnetic hard disks (military standard)

VRC Vermont Research Company

#### APPENDIX A

## SUPPLEMENTARY TECHNICAL INFORMATION ON MEMORY STORAGE DEVICES

## **RD-5/15**

## CARTRIDGE-LOADED \*\* WINCHESTER DISC DRIVE

#### DESCRIPTION

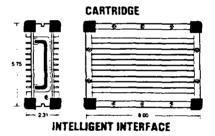

Miltope's RD-5/15 is a cartridge loaded Winchester Technology Disk Drive designed for high speed mass data storage for military computers. The random access memory device stores up to 15 megabytes with an average access time of 40 milliseconds. The system has an intelligent interface that allows easy system integration to the host computer.

Each RD-5/15 cartridge is configured to allow complete plug-in interchangeability, thereby providing the user with a data storage medium that features manual interchange of files.

The cartridge load capability eliminates the need for program-loading devices such as magnetic tape or floppy discs, thereby dramatically improving "booting" time. A compact size and full militarization makes the RD-5/15 ideally suited for airborne and ground mobile applications.

#### **FEATURES**

- Winchester Disk Technology

- Up to 15 MBYTES Capacity

- Compliance to MIL-E-16400/MIL-E-5400/MIL-E-4158

- Removable, Sealed Cartridge

- Fast Access Time, 40 MS Average

- Intelligent Interface

- Compact Size, ATR or Panel Mount

#### **OUTLINE DIMENSIONS**

#### RELIABILITY

| Mean-Time-Between-       |            |

|--------------------------|------------|

| Failures (MTBF)          | 8000 hours |

| Mean-Time-Between-Repair |            |

| (MTTR)                   | 15 minutes |

|                          |            |

#### **ERROR RATES**

| Recoverable (soft)     | 1 in 10 <sup>9</sup> read |

|------------------------|---------------------------|

| Non-recoverable (hard) | 1 in 1011 read            |

| Seek errors            | 1 in 10 <sup>6</sup> read |

#### INTERFACE

The intelligent interface of the RD-5/15 allows easy interfacing to most host computers. Formatting, error detecting/correcting, addressing, and device controlling is contained within the RD-5/15. Data communication with the host computer bus is accomplished via a host adapter which is normally embedded within the host computer chassis.

#### PHYSICAL DIMENSIONS

ATR mount . . . . . . . . 7.50"W × 7.62"H × 13.63"D

Power requirements ..... 115 VAC/48-440 Hz single i

phase optional

Optional ..... 28 VDC

Power dissipation . . . . . . . 100 watts

(drive & formatter)

Weight ...... 25 lbs. max.

(ATR configuration)

**CONFIGURATIONS:**

RETMA rack . . . . . Three RD-5/15 cartridges

and electronics can be mounted in 19" RETMA

enclosure

Full ATR ..... Dual RD-5/15 cartridges

and electronics can be mounted in a one ATR

chassis

**FORMATTER**

Bus type ..... Per ANSI X3T9.2 (SCSI)

Format code ..... MFM encode/decode

Seek and verify ..... Automatic

Error handling ..... Auto error detect/correct up

to 8-bit burst

Multi-sector transfer ..... Auto switch to next head

on cylinder

selectable

Sector buffer ..... Full sector

buffer I'O

Sector interleaving ...... Programmable

Multi-porting ...... Up to four computers

Self-test ...... Internal diagnostics

1770 WALT WHITMAN ROAD • MELVILLE, NEW YORK 11747 TEL 516-420-0200 TWX: 510-221-1803 PERFORMANCE/FUNCTIONAL

Capacity, formatter ..... 5.24 mbytes (RD-5)

15.72 mbytes (RD-15)

Platters ..... One (5.24 megabytes)

Two (15.72 megabytes)

Media ..... 5.25" Plated disc

Access time ...... 10 ms, track-to-track

40 ms, average

8.3 ms, latency

Transfer rate ...... 5 mbps

Rotational speed . . . . . . . . 3600 rpm

Record density ...... 10,000 frpi, max.

Track density ...... 680 tpi

Cylinders ..... 640

Heads ..... Two (RD-5)

Four (RD-15)

ENVIRONMENTAL

Temperature,

Operational ..... -30°C to +55°C

Humidity ...... 5% to 100%

Altitude ..... - 1300 to 50,000 ft.

Vibration, Operational .... .075 DA to 3 G's, 5-2,000 Hz

Non-operational . . . . . 5 G's, 5-2,000 Hz

Shock, Operational ...... 15 G's, 11ms

Non-operational ...... 30 G's, 11ms

Bench handling ...... Per MIL-STD-810

Sand Salt Spray ...... Per MiL-STD-810

EMI compatibility ...... Per MIL-STD-461

Tempest, design ...... NACSEM 5100

MILTUPE:

CORPORATION

1

VERMONT RESEARCH CORPORATION

PRECISION PARK NORTH SPRINGFIELD VERMONT 05150 TEL. 802/886-2256 TWX: 710/363-6533

# ONDIEL PRIVE