CMU-CS-85-104

AD-A158 217

THE FILE CORY

1

3

-

## DEPARTMENT of COMPUTER SCIENCE

### Carnegie-Mellon University

This document has been approved for public release and sale; its distribution is unlimited.

85 8 7

AUG 1

CMU-CS-85-104

### Ada as a Hardware Description Language: An Initial Report

Mario R. Barbacci<sup>1</sup>, Steve Grout <sup>2</sup>, Gary Lindstrom<sup>3</sup>, Mike Maloney<sup>3</sup>, Elliott Organick<sup>3</sup>, Don Rudisill<sup>2</sup>

8 December 1984

1. Carnegie-Mellon University, 2. Martin Marietta Corporation, 3. University of Utah.

The work reported in this report was sponsored in part by Martin Marietta Corporation and in part by the Defense Advanced Research Projects Agency (DOD). DARPA Order No. 3597, monitored by the Air Force Avionics Laboratory under Contract F33615-31-K-1539, and DARPA Order 4395, monitored by the Office of Naval Research, under Contract MDA 903-81-C-0411.

The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, other expressed or implied, of their opensors.

### Table of Contents

| 1 Introduction                         | 1  |

|----------------------------------------|----|

| 1.1 Description of the Approach        | 2  |

| 1.2 Elements of Style                  | 2  |

| 1.3 Overcoming Language Limitations    | 4  |

| 2 Elements of the Description Language | 4  |

| 2.1 Representing Connections           | 4  |

| 2.2 Representing Buses                 | 8  |

| 2.3 Representing Hardware Objects      | 8  |

| 2.4 Operations on Objects              | 9  |

| 3 Shift Register Example               | 10 |

| 4 Timing Models: An Example            | 13 |

| 5 Conclusions                          | 16 |

| 6 Acknowledgements                     | 17 |

| 7 References                           | 17 |

| Package Listings                       | 18 |

#### Abstract

This paper reports on our initial results in using Ada as a Hardware Description Language. Ada provides abstraction mechanisms to support the development of large software systems. Separate compilation as well as nesting of packages, tasks, and subprograms allow the construction of modular systems communicating through well defined interfaces. The complexity of modern chips (e.g. those proposed in the VHSIC program) will require the use of those features that make Ada a good language for programming-in-the-large.

The key to our approach is establishing a writing style appropriate to the objective of describing both the behavior and the structure of hardware components. We model a hardware system as an ensemble of typed objects, where each object is an instance of an abstract data type. The type definition and the associated operations are encapsulated by a corresponding package. In this paper we illustrate our approach through a series of examples, building up a hypothetical hierarchy of hardware components. We conclude by discussing ways to describe arbitrarily complex simulation models and synthesis styles.

### 1 Introduction

The work that load to this report started in response to a DoD request for proposals to design a Hardware Description Language for the Very High Speed Integrated Circuit (VHSIC) program. After analyzing the requirements we found that Ada<sup>1</sup> [ANSI, 1983] could be a powerful, cost-effective hardware description language since it provides abstraction mechanisms to support the development of large software systems. Separate compilation as well as nesting of packages, tasks, and subprograms allow the construction of a modular system communicating through well defined interfaces.

A desire for a hardware description language should not obscure the strong commonality of approaches and techniques between designers of complex hardware and software systems. While the full power of Ada may not seem appropriate for the design and specification of small components, the design of moder chips (e.g. those proposed in the VHSIC program) will require the use of advanced complexity management techniques. We argue that these techniques are directly supported by those features of Ada which make it a good language for programming-in-the-large.

We hasten to add that what we are proposing is Ada, not an Ada-like language. We are not

<sup>&</sup>lt;sup>1</sup>Ada is a trademark of the US Goverment. Ada Joint Project office.

contemplating the writing of a special compiler; any off-the-shelf Ada compiler will do. We are not even proposing adapting or modifying some existing Ada support system; any validated Ada implementation will  $do^2$ .

#### 1.1 Description of the Approach

We model a hardware system as an ensemble of typed objects, where each object is an instance of an abstract data type. The type definition and the associated operations are encapsulated by a corresponding package. Thus, each package manages a particular kind of hardare component (e.g., wire, nand gate, multiplexor). The public operations of each package include object creation, object construction (from its component parts, interconnection of those parts, and association of these parts with the outer object's interface pins), and simulation. The semantics of these operations are explained in later sections.

Central to cur representation of hardware objects are the dual concepts of behavioral and structural views of a hardware description. For example, a multiplexor may be described behaviorally as an object that selects among a list of inputs. Alternatively, it can be described as a collection of interconnected nand gates (in a multiplexor configuration, of course). A behavioral description is generally a more abstract view; it hides structural details which introduce implementation decisions. The structural description includes only the information about an object's components and their interconnections. The behavior implied by a structural description is determined by the behavior of its components and by the way they are interconnected. Behavior is not intrinsically "higher" than structure since, at the lowest level, some components are taken as primitives; their structure is hidden, and their description is purely behavioral. In fact, as we shall see in some of our examples, mixing structural and behavioral descriptions at the same "level" can be used to enhance the descriptive power of the notation, making the intentions of the designers more apparent.

#### 1.2 Elements of Style

Discussions about programming styles often degenerate into theological arguments (witness the long standing arguments about indentation and capitalization of keywords and identifiers). We do not pretend to say that the style we have used in our examples is the best or that it should adopted by all users. As a matter of fact, the examples are contrived to display the features of the language, at the expense of having perhaps too many levels in the hierarchy of components. In a production environment we would expect say, latches and flip-flops, to be implemented as primitive components

<sup>&</sup>lt;sup>2</sup>Actually, we do not need the full language: a reasonable subset, containing the right features is sufficient. Talk about Ada subsets is, however, considered heresy in some circles and we will not raise this point again.

whose descriptions are carefully handcrafted for simulation efficiency, rather than to be implemented by building them up from inverters and nand gates. In addition, to save space, in this paper we have limited ourselves to illustrate our approach via simple examples, although we have explored other, more complex descriptions in [Maloney et al., 1985].

In constructing the examples we have followed a few guidelines to emphasize readability and modularity and to define appropriate layers of abtractions.

<u>Readability.-</u> The complexity of many hardware systems and their equivalent software representations requires that the code be easily understood. We do rely on comments and the flexibility Ada provides for writing extended and legible identifiers. Appropriate selection of names for variables, types, and operations are also important.

Ada permits the overloading of enumeration literals and subprogram names. We take advantage of this to reduce the names of distinct identifiers that must be learned by the user. The basic operations needed to create, construct, and simulate hardware components have the same identifier, independent of the component type. The language provides mechanisms to resolve the ambiguities.

<u>Modularity.</u> We define this as the ability to connect objects that are of different types through compatible interfaces. The strong typing in Ada prevents the kind of error in which a component of the wrong type is used by mistake (e.g. passing a nand gate to a D Latch simulation procedure). To permit the connection and transfer of signals between components, we use universal interface types (e.g. pins and buses). All components define their interface in terms of these types.

1

Lavers of abstraction.- We define this as the ability to have multiple levels of representation for the structure and behavior of hardware objects. In our approach we use packages to define libraries of abstract types, one per package. Each package is built upon types and operations defined in other packages, in a hierachical fashion. In addition, the separation of specifications and bodies for these packages, permits the use of multiple versions of bodies supporting the same specification. This has important advantages in that we can quickly "plug-in" more efficient simulation models or synthesis algorithms or design rule checkers, etc. without ever having to alter a client package, or even recompile it. The switch happens at link time.

#### **1.3 Overcoming Language Limitations**

Ada was not designed with hardware descriptions in mind, thus we have adopted some conventions to overcome two shortcomings in the language.

Lack of Timing Primitives.- Ada has no primitives for expressing time and time-based relationships. Mapping a hardware description written in Ada to actual hardware requires either that the hardware be implemented using fully asynchronous circuitry, a practice not widely advocated, or that timing specifications be introduced in the process of mapping to hardware. The direct-mapping approach is the object of current research at the University of Utah [Organick et al., 1984.]

We overcome this deficiency by building into the packages operations that perform the synthesis of the abstract data type into hardware, incorporating the appropriate synchronization and timing information. Thus, rather than counting on a "smart" compiler to decipher the designer's intentions, we use "smart" programs and libraries, where these intentions are explicitly stated.

Ada does not treat packages as first class objects. Ada packages may not directly model hardware components unless such packages are elaborated at compile time; they cannot be created dynamically as values that can be assigned to variables or passed as parameters. Ada tasks do have some of these desirable features, however they suffer from other limitations (e.g. a task specification cannot define and "export" data types, constants, or objects, only entries.)

This is an unfortunate but not unsurmountable difficulty. In our approach, we use packages to manage instances of (first class) record types which in turn model hardware components.

### 2 Elements of the Description Language

#### 2.1 Representing Connections

Before we present the details of how hardware objects are represented, it is necessary to address the problem of intermodule connections.

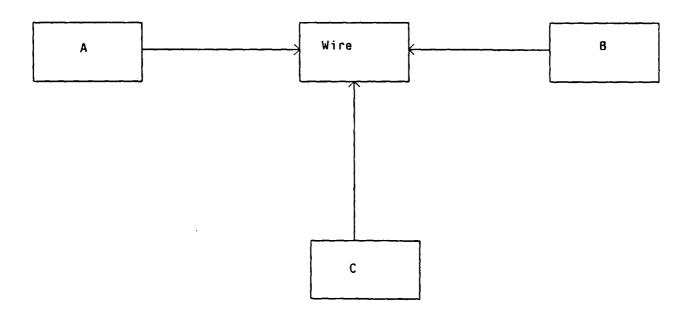

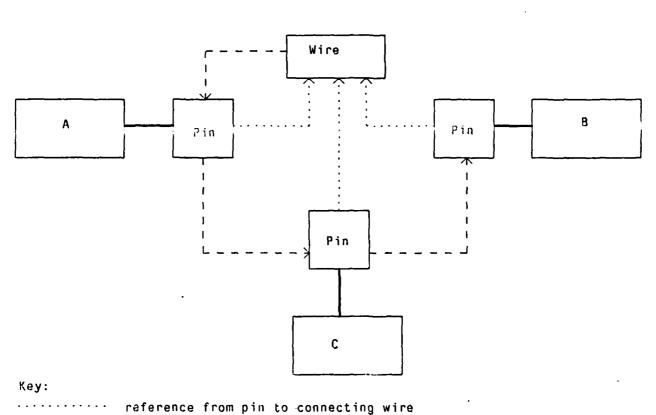

The relationship that exists between hardware objects<sup>3</sup> and interconnections is many-to-one; that is, many objects can be connected through one connection. A first representation of this relation could have each object reference the "wire" to which it is connected. For example, if components A, B and C are all connected, we have the arrangement depicted in Figure 1. This representation is

<sup>&</sup>lt;sup>3</sup>Actually, here we are referring to an input or output of an object. For example, the output of a nand gate.

#### Figure 1: Three components connected by a simple wire

adequate for most situations. Here we treat the wire itself as an object. For simulation purposes, the wire object can have a value attribute that could be set and read by the components that it "joins". Information about how many components the wire is connecting can also be maintained in the wire object.

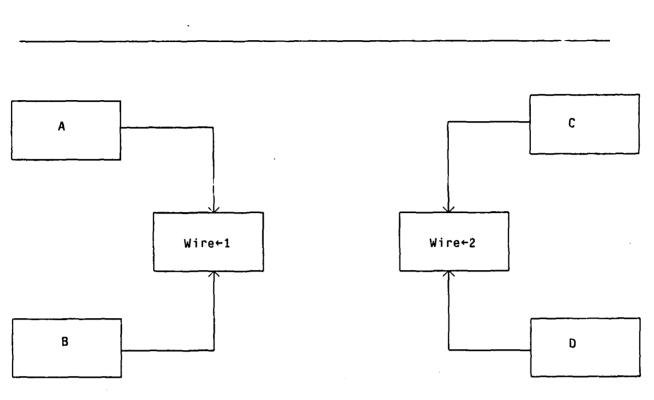

The deficiency in this representation becomes apparent when we allow components to be connected in an arbitrary order. In that situation, we must be able to connect objects that are already connected by wires. Figure 2 illustrates this point. In connecting components A and C, we would like the resulting configuration to have one wire that is referenced by components A, B, C and D. To accomplish this requires that we change C and D to reference wire\_1 or A and B to reference wire\_2. Note that either of these operations assumes the capability to find all references to a wire.

The desire for freedom in the order that connections are made motivates a slightly more complex representation of wire interconnections. The deficiency or the previous simple strategy is that there is no way to reference all of the objects connected by a wire. An intermediate "pin" data structure solves this problem in the following way. If a wire actually establishes connections between pins of

#### Figure 2: Two components already connected by simple wires

objects, it can reference, through a linked list of "pins", all of the "pins" that are connected to it. This is illustrated by the three pins connected as shown in Figure 3. The task of connecting pins that are already connected thus involves trivial linked-list operations to reconfigure the interconnection and merge the pin connections to one wire.

To support the abstractions or wires and pins, we have written a package, Pin\_Mgr that declares wires and pins as data types and defines appropriate operations for manipulating objects of these types. The package is written so that most details about intermodule connections are placed in the body of the package and are therefore hidden from the users (the complete package listings appear in the Appendix). The public operations of this package are:

- The procedure CONNECT, which connects two pins (i.e. links them in a 'wire' list.)

- The procedure DISCONNECT, which breaks a connection (i.e. removes a pin from a 'wire' list.)

- The procedure EQUATE, which associates an internal pin of an object with an external pin (i.e. brings cut an internal component pin.)

6

---- linked list of pins

Figure 3: Three components connected by a simple wire using pins.

- The procedure UNEQUATE, which undoes an equate.

- The procedure SET\_VALUE, which sets the value on a wire. This procedure and the following function can be used for simulation.

- The function VALUE\_OF, returns the value of (i.e. level on) a wire.

- The function FAN\_OUT, returns the number of pins connected to a wire.

The strategy, then, in building and connecting components is to provide each external input or output of an object (representing a component) with a "pin" that can be used in connecting the object with other objects. Pins and wires are not limited to modeling the idealized connections in our sample package: physical attributes such as capacitance, delays, loads, distances, locations, etc. can be easily described as "attributes" of (i.e. fields of the record types modeling) pins and wires.

#### 2.2 Representing Buses

A bus can be described as an array of pins, using conventions similar to those of a pin. A package supporting this abstraction is listed in the Appendix. The visible operations of the Bus\_Mgr package are:

- The procedure CONNECT, which connects two internal buses (provided the buses have the same width.)

- The procedure UNCONNECT. which breaks a connection.

- The procedure EQUATE, which associates an internal bus of an object with an external bus of the same width.

- The procedure UNEQUATE, which undoes an Equate.

- The procedure SET\_VALUE, which sets the value on a set of wires, again as long as the width is the same.

- The function VALUE\_OF, which returns the value of a set of wires.

The strategy, then, in building and connecting components is to provide each external input or output of an object with buses or pins that can be used in connecting the object with other objects.

#### 2.3 Representing Hardware Objects

We can identify three possible approaches to the problem of representating hardware objects as typed data objects.

The first approach is to declare hardware objects as totally "private" (in the Ada sense). All operations on objects are defined by a set of procedures and functions that involve such objects, but nothing about the objects' structure is visible outside these procedures. Here problems arise when attempting to interconnect such objects, since we have no knowledge about an object's interface.

The other extreme is to declare hardware objects as totally "public" (again, in the Ada sense). However, this method exposes information about an object's structure that is irrelevant for connecting the object with another object.

The third approach is a combination of the previous two: we represent hardware structures using data types that contain both public and private parts. The public part of an object contains its interface information only, while the private part contains implementation details. The example in Figure 4, shows the (public) specifications for D flip flops.

```

type d_ff_components is private;

type d_flip_flop_record is

record

-- inputs

dbar

--Input data signal d (inverted).

: pin;

clkbar : pin;

--Input clock signal (inverted) to run slave latch.

clear

: pin;

-- Input signal to clear the flip-flop.

clock

: pin;

--Clock signal to run master latch.

output

--Output data signal q (inverted).

qbar

: pin;

-- private

components : d_ff_components;

end record;

```

Figure 4: Structure of the D Flip-Flop

In the example, the COMPONENTS field of the D Flip-Flop record is a component of a private type. Although it is visible as a record component outside its enclosing package, its structure is private. Alternatively, the publically visible fields of an object could be defined as the discriminants of an Ada private record type, with the hidden parts declared in the full type declaration, in the private part of the package specification. With this approach, not even the COMPONENTS field is visible outside the package. The drawback is that, in Ada, the values of discriminant fields cannot be mcdified except by a full record assignment.

#### 2.4 Operations on Objects

100

D

1.1.1.18

)

)

Now we will describe how to use a hardware data object, that is to instantiate it, to establish its functionality, and to simulate it. To begin this process one must first create the object. The function CREATE allocates storage to hold values for a component's interface.

Once a data object has been instantiated we may perform other operations on it, such as CONSTRUCT and SIMULATE. The CONSTRUCT procedure establishes a structural description of the object by creating and connecting the object's subcomponents.

Once the function CREATE and optionally the procedure CONSTRUCT have been invoked, objects are ready to be simulated. For each object type that we define, we provide a SIMULATE procedure. This procedure operates upon information that is placed on the input pins to produce the results on the output pins. Objects at the lowest design level (primitive objects) are simulated by executing their behavioral description.

An object can either be simulated directly, by executing a SIMULATE procedure that implements its behavior or indirectly, by executing a SIMULATE procedure that invokes the procedures that simulate the subcomponents. Details of the algorithms used to simulate or construct objects are hidden. The subprogram specifications only describe the types of the parameters and the results.

Using this approach, mixed-level simulation is easily implemented (A similar approach to mixed level simulation using Simula 67 is described in [Lindstrom, 1983]). The order of simulation of components should begin with the input pins and follow the flow of new data throughout the network of components. Once all of the components have been simulated the appropriate output values will be placed on the output pins.

### **3 Shift Register Example**

This section presents a complete example of the specification of a composite hardware object (i.e. an object that has subcomponents.)

Our specification of a shift register (National Semiconductor MM 74C168 [National, 1981]) is built bottom-up. We begin by creating certain low-level components, namely 2- and 3-input nand gates and inverters, described by packages named Two\_Input\_Nand\_Gate\_Mgr, Three\_Input\_Nand\_Gate\_Mgr, and Inverter\_Mgr, respectively. These packages define primitive objects. Primitives have inputs and outputs and only a behavioral description; they are not represented by inter-connected subcomponents.

The package supporting the abstraction of an inverter declares two data types and two operations. The data types describe an inverter as a record with two fields, the input and output pins respectively. Since inverters (as well as other gates) are easier to handle as Ada access (i.e. pointer) types, the operations defined on inverters do not take an inverter record directly but rather they manipulate pointers to inverter records.

The CREATE operation is used to instantiate an inverter. Since this is a primitive component, there is no need to create and connect internal components, as we shall see in later examples. The SIMULATE operation computes the value at the output pin, depending on the value at the input pin. Notice that we are ignoring internal delays; these are idealized inverters.

The package supporting the abstraction of a nand gate is described as a generic package. This permits the definition of nand gates of arbitrary number of inputs by simply instantiating the generic package, with the right parameter (the number of input pins), without having to rewrite the type and

operation declarations. The input pins are modeled by a dynamic array of pins, whose dimension is specified when the generic package is instantiated.

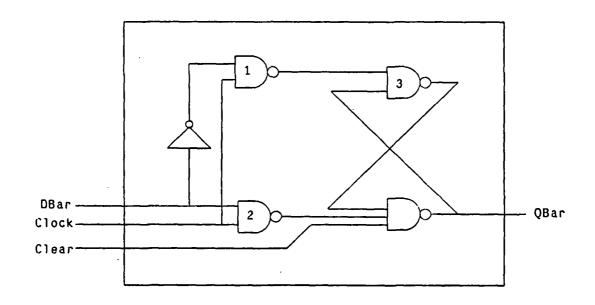

Using these component definitions, we can establish a structural description for a D Latch. (See Figure 5.) The package D\_Latch\_Mgr package establishes the structural description of D latches by creating and interconnecting an inverter and four nand gates whenever the CONSTRUCT procedure (in the D Latch package) is invoked.

Figure 5: Inside view of the D Latch.

In the definition of the D Latch record type, we are hiding from the users of the abstraction the nature of the implementation of the latch. That is, only the input and output pins are directly available. The fact that there are components is revealed by the definition of the COMPONENTS field; however, since this field is declared to be of a private type (D\_LATCH\_COMPONENTS), no user of the package can make assumptions about its structure.

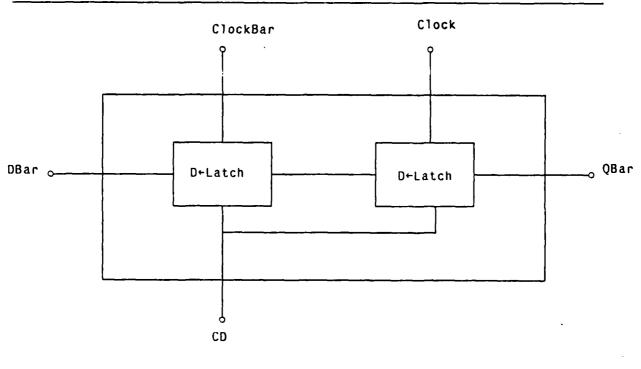

In addition to the CREATE and SIMULATE operations, the D Latch package also provides a CONSTRUCT operation. This operation must be invoked after a D Latch has been created and before it can be simulated. It builds the latch by instantiating the internal components, connecting them in the right configuration, and equating some internal component pins to the input and output pins of the latch. The construction of components continues for the D flip-flop, the next level up in this component hierarchy. The package D\_Flip\_Flop\_Mgr defines data objects that are composed of D latches (See Figure 6.)

Figure 6: Inside view of the D Flip-Flop.

Notice the parsimonious nature of our approach. Every new component type is supported by a package which exports a record type and an associated access type; this permits the manipulation of the object by the support subprograms. In addition, the package exports procedures to create, construct, and simulate the component. By hiding the internal structure of a component and the implementation of the operations, the designer is free to correct or enhance the abstraction, without having to worry about amending packages that import the abstraction (provided of course, that the changes do not affect the visible part of the abstraction.) Any hardware system built out of components described in this fashion can in turn be used as a primitive component in later designs, provided these simple rules of style are observed.

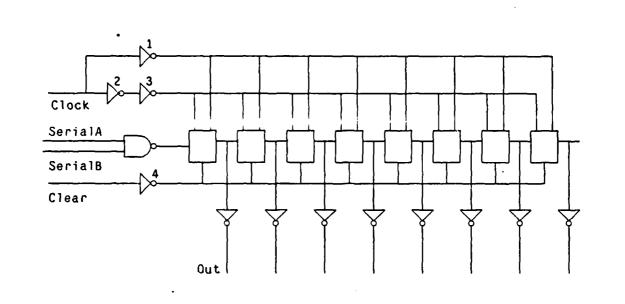

As with the D latch and the D flip-flop, the serial shift register (Figure 7) is constructed by connecting components such as the inverter, nand2, and D flip-flop together in the correct (graph) structure. Once constructed, the shift register can be simulated by invoking the procedures that simulate its components.

Figure 7: Inside View of the MM 74C168 Shift Register.

This hierarchical design is represented in the compilation dependency graph for the corresponding Ada packages, as shown in Figure 8.

### 4 Timing Models: An Example

•

In the preceding examples we have exhibited the power of the language to describe the structure and interconnections of hardware components. In this section we describe how it is possible to implement, within the same framework, arbitrarily complex timing and synchronization models, as well as synthesis algorithms.

By way of example, we have chosen to describe how the element of delay can be added to our library. We will represent time after the CONLAN model of computation [Piloty et al. 1983]. CONLAN uses the notion of a history of values to model digital hardware. Computation *step signals* correspond to transient values, due to the propagation of state changes in the system. The duration of a step is negligible and possible intermediate values in the carriers are invisible to the hardware designer -- only the final value of a step signal has significance. *Time signals* are sequences of step signals along time: one step signal per unit of time. Time signals can be inspected for past values (the last value of the step signal associated with a given point in the past) as well as current values (the last value of the current step signal).

(

ļ

Figure 8: Compilation Dependency Graph for the Shift Register

Using this two-layered model of time, we modify our simple pin package as shown in the Appendix (under "Extended Pin Specification" and "Extended Pin Body".) Notice that in addition to the additional history carried by a wire, we have added an extra parameter (DELAY\_VALUE) to the VALUE\_OF function. The function now returns a previous value of a signal. We can now use this function to model a more realistic inverter gate, by rewriting the SIMULATE function, as shown in Figure 9.

Notice that the VALUE\_OF function in the new pin package specifies a default for the DELAY\_VALUE

```

procedure Simulate(v : in inverter_gate)

Function:

This function simulates the logic of an inverter by inverting

the value of the input pin and placing the value on the output pin.

The function assumes a 10-unit gate delay.

1s

begin

case Value_of(v.input,10) is

when low =>

-- If input is low the output is high.

Set_value(v.output,high);

return:

when high =>

-- If input is high the output is low.

Set_value(v.output,low);

return;

when others =>

~- If input is undefined, no change

nu11:

end case:

end Simulate;

Figure 9: Inverter with Internal Delay

```

parameter. If no delay is provided by the caller, the last value assigned to the pin is returned (i.e. no delay is assumed.)

In this example, we have made a radical change in the package supporting the abstraction of a pin, yet the only externally visible change is the addition of one extra parameter to the VALUE\_OF function. In addition, by providing a default value corresponding to the previous, no-delay version, all we have to do is recompile, without changes, any existing library packages. That is, older, idealized (i.e. no-delay) components still work; new, more realistic components can now be described, and both kinds of components can be mixed in a design.

To conclude this section, we point out that in our approach we are not limited to using pins and internal components as the fields of a record modeling some hardware component. We can just as easily declare fields whose values correspond to physical dimensions, power requirements, locations, etc. Since the process of constructing components is done by calls to operations defined in the library packages (CREATE and CONSTRUCT), it is rather easy to keep track of all instances of these components and to check that no design rules are being violated. The data structures needed for the bookkeeping provide an internal representation of the design: translating it into masks, wire-lists, or other manufacturing information gives us the path towards powerful and flexible design automation systems<sup>4</sup>.

<sup>&</sup>lt;sup>4</sup>As powerful and flexible as the code we are willing to write, and we have all the power of Ada to do this.... Don't be surprised, the emperor in the fairy tale was naked!

### 5 Conclusions

In a conventional CAD environment, the separation between the user and the toolmaker is very sharp. Tools (translators, simulators, synthesis programs etc.) are written in different languages, by separate groups of individuals, who may in turn be distinct from those in charge of maintaining the ensemble. Users are bound by the implementers' decisions (and mistakes) and are not usually in a position to do anything about them, short of waiting for upgrades or fixing the problems themselves. One of the most serious deficiencies with this conventional approach is that often an implementation will bind knowledge about a particular technology, synthesis style, or simulation models into the implementation in such a way that it is often not possible to change it to reflect new technologies or better design methods.

The technique we are describing is certainly no panacea; errors can still be made. However, we are eliminating the middle men and exposing to the users (i.e. designers) the full implementation, technology dependent decisions, timing models, and synthesis styles. Since the implementation language is the same language that is used in the day-to-day activities of the designers, they can understand the source of the problem, can propose solutions, and finally, can implement the solution themselves, without further ado. Good system management practices will probably impose some mechanisms to prevent chaos from arising; in particular, it is likely that only expert designers will be allowed to implement such changes. Ada provides powerful features to support the development, maintenance, and graceful evolution of large software systems; these same features will be invaluable in CAD systems of the 80's and beyond.

The advantages of using the same language for both the design of hardware and software are evident. The flexibility in delaying the binding of (hardware) implementation decisions discussed in this paper is easily extensible to a more basic decision, namely, whether a portion of a system is to be built in hardware or in software. The use of a single language together with a convention on style, permits a designer to write an abstract interface to a computing engine while retaining the freedom to implement this engine in either hardware or software. The flexibility continues throughout the life-cycle of the engine; the decision can be reversed at a later time, if the trade-offs change, without affecting in any way the users of the abstraction.

In addition to the obvious superiority of Ada as a programming language over existing special purpose hardware description languages, there are other reasons why Ada is an attractive hardware design tool.

Ada is a standard language that enjoys the support of the largest software user in the world, the U.S. Department of Defense. Thus, it is inevitable that rich programming environments will be built around Ada and that the community of users will be several orders of magnitude larger than that of any existing or proposed HDL. Not only are modern software development technologies easier to apply by the use of Ada but large user communities provide a continuous supply of tools, methods, training materials, etc. All of these contribute to a reduction of the life cycle costs of a project.

### 6 Acknowledgements

We would like to acknowledge the helpful input from David Barton, Peter Tinker, and Jay Woodward, graduate students in the Department of Computer Science, University of Utah.

#### 7 References

- [ANSI, 1983] <u>Reference Manual for the Ada Programming Language</u>, American National Standards Institute, Inc., New York, ANSI/MIL-STD-1815A-1983.

- [Lindstrom, 1983] G. Lindstrom and P. Tinker, "VHDL Simulator Design", Technical report, Department of Computer Science, University of Utah, 1983.

[National, 1981] <u>CMOS Databook</u>, National Semiconductor Corp., 1981, p 1-68.

[Organick et al., 1984]

E. Organick, T. Carter, M. Maloney, A. Davis, A. Hayes, D. Klass, G. Lindstrom, B. Nelson, and K. Smith, "Transforming an Ada Program Unit to Silicon and Verifying its Behavior in an Ada Environment: A First Experiment", IEEE Software, Vol. 1, No. 1, January 1984, pp. 31-49.

[Piloty et al., 1983] R.Piloty, M. Barbacci, D. Borrione, D. Dietmeyer, F. Hill, and P. Skelly, <u>CONLAN</u> <u>Report</u>. Lecture Notes in Computer Sciences No. 151, Springer-Verlag, 1983.

[Maloney et al., 1985]

M. Maloney, M. Barbacci, E. Organick, J. Woodward, and D. Barton, "Examples of Ada as a Hardware Description Language". Technical Report, Department of Computer Science, University of Utah, 1985. Also Technical Report, Department of Computer Science, Carnegie-Mellon University, 1985.

I. Package Listings

C

# **Pin** Specification

# package Pin\_Mer is

-- Furchast

This puckage defines the value that a pin can have and the 1

preventures to connect disconnect, equate, unequate, set values, and find values on pins. 1

type wire\_kevel\_value is (low, high, undefined):

type pin is private:

null\_pin : constant pin; -- deferred constant

procedure (Connect(pin\_l. pin\_2: in out pin);

-- Function:

This procedure will connect two pins

procedure Disconnect(pin\_l, pin\_2: in out pin);

-- Function:

This providure will disconnect a pin from whatever it is ł

connected to.

procedure Fiquate(pin\_1. pin\_2: in out pin);

This precedure will connect an external pin to the internal -- Function: ł

pin of a component.

procedure Unequate(pin\_l. pin\_2: in out pin);

-- Function:

They proceedure will disconnect an external pin from whatever it is t

Interation of a conconent

procedure Sei\_value(p : pin; v : wire\_level\_value);

-- Function:

This procedure wil' 9, we the specified pin the given value

function Value of (p : pin) return wire level value;

!

This junction returns the pin\_level\_yalue of a pin. -- Function: -- This fu

function Fan\_out(p : pin) return natural;

-- Function: ;

pirs that are currently connected by the wire that This function returns the total number of

this pin is connected to.

private

C

.

-- I. pins are connected by adding them to the list of pins of

a created wire.

-- 2. the global attributes of the connection are stored

in the wire record

When pins are connected, a pin record and a wire record are created. :

The wire record points to the first pin record in the list and that ;

-- pin record points to the next until the last pin contains a null

indicating the end of the list. Each pin record contain: a pointer to the wire record so the head of the list can be found from any pin. 1

type pin\_record;

type pin is access pin\_record;

type wire record;

type wire is access wire\_record;

null\_pin : constant pin := null;

null\_wire : constant wire := null;

type pin\_rccord is

-- next pin in list : wire := null\_wire; : pin := null\_pin; connecting\_wire next\_pin record

end record;

: wire\_level\_value := undefined; type wire\_record is record value

:= null\_pin; := 0; list\_of\_pins : pin number\_of\_pins : natural end record;

end Pin\_Mgr;

## Pin Body

# package body Pin\_Mgr is

- I unction:

- Pins allow value access to all components, these values are stored in

- wire records. This package determines how to connect pins with the

- procedures: connect disconnect for internal components) and equate.

- unequat. (for internal to external connection). The function Connected

- returns a book an value stating if the pin is connected or not. The

- function Value\_of returns the value of the pin Function Fan returns

- the number of pins connected to a specific wire Procedure Set\_value

- sets the value of a wire record

function Cornected(p : pin) return boolean

- -- Function:

- -- Returns a boolean value true if pin is connected, and false if the

- pin is not connected.

begin 2

- if p = null pin or else p.connecting\_wire = null\_wire then

- return ialse;

- return ine; else

- end it:

- end connected;

procedure Connect(pir. i. pin\_2 : in out pin) <u>.</u>

- -- Function:

- -- pins are connected by linking them into a list

- -- und creating a wire common to them both.

- first\_pin, last\_pin, loop\_pin : pin;

- Degin

- first make sure that pin\_records exist for each

- nid --

- if pin\_l = null\_pin then -- create a pin\_record for pin\_l

pin\_l := new pin\_record;

- end if:

- if pin\_2 = null\_pin then -- create a pin\_record for pin\_2

pin\_2 := new pin\_record;

- - end if:

- if not Connected(pin\_1) and not Connected(pin\_2) then

- -- Cave I: neither pin is connected

- If north, r pin is connected a new wire record is created and

- both pins fount to it. The pin\_l becomes the head pin and is

- pound I to by the ware record The pin 2 becomes the next wire

- for the pin I. Finally the number of pins pointing to the wire

- ;

- record is incremented by 2.

- pin\_l.connecting\_wire := new wire\_record;

- pin\_2. connecting\_wire := pin\_1. connecting\_wire:

- 1. connecting wire list of pins := pin\_1; := pin\_2; pin\_l.next\_pin pin\_1

- pin 1. connecting wire. number of pins :=

- pin\_1.contecting wire.number\_of\_pins + 2;

- elsif Connected(pin\_1) and not Connected(pin\_2) then -- Case 2: pin\_l is connected and pin\_2 isn't

- -- If pin\_l is connected to a wire and pin\_2 is not. Pin\_2 wire record

- -- becomes pin\_I wire record pin\_2 is now the head of the pin list

- -- which is pointed to by wire record Pin\_I becomes the next pin for

- -- pin\_2 and the number of pins for the wire is incremented by I.

- pin\_2.connecting\_wire := pin\_1.connecting\_wire; pin\_2.next\_pin := pin\_1.connecting\_wire.list\_of\_pins; pin\_1.connecting\_wire.list\_of\_pins := pin\_2; pin\_1.connecting\_wire.number\_of\_pins := pin\_2;

- pin\_1.connecting\_wire.number\_of\_pins + 1;

- elsif Connected(pin\_2) and not Connected(pin\_1) then

- Case 3 : pin\_2 is connected and pin\_1 isn't

- If pin\_2 is connected to a wire and pin\_I is not. Pin\_I wire record

- -- becomes pin\_2 wire record pin\_l is now the head of the pin list

- -- which is pointed to by wire record Pin\_2 becomes the next pin for

- -- pin\_l and the number of pins for the wire is incr.mented by 1.

- pin 1. connecting wire := pin 2. connecting\_wire; pin\_1. next\_pin := pin 2. connecting\_wire. list\_of\_pins; pin\_2. connecting\_wire. list\_of\_pins := pin\_1; pin\_1. connecting\_wire. number\_of\_pins :=

- pin\_1. connecting\_wire. number\_of\_pins + 1;

### else

- -- Case 4 : both are connected

- The two wire records will be merged and the head will be the ł

- -- already connected to each other -- head of the pin\_2 record list. if pin\_1 connecting\_wire = pin\_2 connecting wire then

- return;

- end if:

- pin\_1.connecting\_wire.number\_of\_pins :=

- pin\_2. connecting\_wire. hist\_of\_pius; loop\_pin := pin\_2. connecting\_wire. list\_of\_pius; first\_pin := loop\_pin; pin\_1. connecting\_wire. number\_of\_puns

can't be null

- while loop\_pin /= null\_pin

- 000

- loop\_pin.connecting\_wire := pin\_l.connectung\_wire;

- last pin := loop\_pin;

- loop\_pin := loop\_pin.next\_pin;

- end loop:

- -- Insert the (pin\_1) list at the tail of the list\_of\_pins of the wire last\_pin.next\_pin := pin\_l.connecting\_wire.list\_of\_pins; pin\_l.connecting\_wire.list\_of\_pins := first\_pin;

- end if;

- end Connect;

- procedure Disconnect(pin\_l, pin\_2 : in out pin) 2

- - begin

null

- -- The functionality is not yet defined. -- Function:

## Pin Body

Ç

C

```

-- Determines the number of pins pointing to a wire record and returns

-- that value

-- The connections from internal pins to external pins is disconnected.

-- Function:

-- The connections are from internal pins to external pins.

procedure Sci_value(p : pin; v : wire_level_value)

is

function Value_of(p : pin) return wire_level_value

is

-- Determines the value of a pin and returns that value.

procedure Unequate(pin_l, pin_2 : in out pin)

is

procedure l_{i}quate(pin_l, pin_2 : in out pin) is

return p.connecting_wire.number_of_pins;

function Fan_out(p : pin) return natural is

begin

if Connected(p) then

p.connecting_wire.value := v;

-- Function:

-- Assigns a vulue to a wire record.

return p.connecting_wire.value;

null: -- raise some exception

Disconnect (pin_l.pin_2);

connect(pin_l.pin_2);

-- Function:

-- Finction:

-- Function:

end;

end Pin_Mgr;

end if;

begin

begin

begin

begin

end;

end

end

end:

1

```

# **Bus Specification**

0

with Pin\_Mgr; use Pin\_Mgr;

package Bus\_Mgr is 1

-- Function:

- Buses are a defined as arrays of pins, and bus values as arrays

- of levels. This package provides procedures for connecting and disconnecting buses. The function Value of returns the bus value of a bus. The procedure Set value sets the value of a bus.

- 1

type bus\_value is array (natural range <>) of wire\_level\_value;

type bus is array (natural range <>) of pin:

procedure Connect(bus\_l, bus\_2 : in out bus);

-- Function:

- Creates a bus connecting a pair of (conforming) pin arrays 1

- belonging to subcomponents of a given component.

procedure Disconnect(bus\_1, bus\_2 : in out bus);

-- Function:

1

Undoes the Connect operation. :

procedure Equate(bus\_1, bus\_2 : in out bus);

- 1

- -- Function: 1

- Creates a bus connecting a pair of (conforming) pin arrays, one array belongs to a component and the other to a subcomponent. 1

procedure Unequate(bus\_1. bus\_2 : in out bus);

-- Function:

!

Undoes an Equate ţ

procedure Set\_value(b : bus; v : bus\_value);

- -- Function:

- Assigns a bus value to a specified bus 1

function Value\_of(b : bus) return bus\_value;

- 1

- -- Function:

- Returns the bus value of a specified bus ł

- bus\_mismatch : exception: -- Raised when operations are attempted on nonconforming buses end Bus\_Mgr;

## **Bus Body**

with Pin\_Mgr; use Pin\_Mgr;

# package body Bus\_Mgr is

- -- Function:

- This puckage provides implementutions of procedures for connecting and disconnecting buses. The function Value\_of returns the bus value

- - of a bus The procedure Set\_value sets the value of a bus

function Nonconforming\_buses(bus\_1, bus\_2: bus) return Boolean

### begin

if bus\_l'length /= bus\_2'length then

- return true;

- return false; else

- end if:

- end Nonconforming buses;

function Nonconforming\_bus\_and\_value(b: bus; v: bus\_value) return Boolean

begin if b'length /= v'length then return true;

- else

- return false; end if:

- end Nonconforming\_bus\_and\_value;

procedure Connect(bus\_1, bus\_2 : in out bus)

- 2

- -- Function:

- Creates a bus connecting a pair of (conforming) pin arrays ł

- belonging to subcomponents of a given component.

- begin

- if Nonconforming\_buses(bus\_1, bus\_2) then raise bus\_mismatch;

- - end if:

- -- Curnect the buses by connecting their respective pins

- for i in bus\_l'range

- Connect(bus\_l(i), bus\_2(i)): 000

- end loop;

- end Connect;

- procedure Disconnect(bus\_1, bus\_2 : in out bus)

- <u>e</u>

- -- Function:

- -- The functionality is not yet defined

- Han begin

. pup

procedure liquate(bus\_l.bus\_2 : in out bus) -- Function:

.

- Creates a bus connecting a pair of (conforming) pin arrays, one array belongs to a component and the other to a subcomponent.

- ŝ

- Connect(bus\_l, bus\_2); begin

- end

- procedure Unequate(bus\_1, bus\_2 : in out bus)

- -- Undoes an Equate -- Function:

- 2

- begin

- Disconnect (bus\_l, bus\_2):

- end Uncquate;

- procedure Sci\_value(b : bus; v : bus\_value) -- Function:

- Assigns a bus value to a specified bus

- begin <u>.</u>

- if Nonconforming\_bus\_and\_value(b, v) then raise bus\_mismatch; for i in b'range end it; 000

- Set\_value (b(i), v(i)); end loop;

- end Set\_value;

- function Value\_of(b : bus) return bus\_value

- -- Function:

- -- Returns the value of a bus b

- temp\_val : bus\_value (b' range): <u>s</u>

- for i in b'range begin

- temp\_val(i) := Value\_of(b(i)); 000

- return temp\_val; end loop:

- end Bus Mgr; end

# Inverter Specification

# with Pin\_Mgr; use Pin\_Mgr;

# package Inverter\_Mgr is

- -- Function: ł

- :

- This package specifies the external pin connections of an inverter and a function to create a specified inverter. The procedures to

- construct and simulate inverter execution are also described.

# type invener\_record is

### input : pin; output : pin; record

- end record;

# type inverter gate is access inverter record;

# Iunction Create return inverter\_gate;

- -- Function:

- Space is allocated for the inverter and all pins are set to a disconnected state.

procedure Simulatc(v: in inverter\_gate);

- -- Function:

- The procedure Simulate will read input values and generate the ;

- proper output signal for the inverter gate.

- end Inverter Mgr.

## Inverter Body

•

use Pin\_Mgr; with Pin\_Mgr:

# package body Invenur\_mgr is

۱

- -- Function:

- This package body contains procedure and function details to 1

- implement a nend gete, namely Create and Simulate. :

# function Create return Inventor\_Gate

- -- Function:

- Creates a new instance of a inverter. !

- 27

### begin

- return new Inverter record; and Create;

- procedure Simulate(v: in inverter\_gate)

- -- Function:

- This function simulates the logic of ...n inverter by Inverting the value of the input pin and placing the vulue on the output pin. 1 !

- <u>0</u>

### begin

- case Value of( v. input) is when low =>

- -- If input is low the output is high. Set\_value(v.output.high); seturn;

- -- If input is high the output is low. when high => Set\_value(v.output.luw):

- return;

- -- If input is undefined no change when others =>

## end case;

end Inverter Mgr; end Simulate;

# Generic Nand Specification

with Pin\_Mgr; use Pin\_Mgr;

### N : in integer: generic

-- Number of inputs for nand gate.

package N\_Input\_Nand\_Mgr is

-- Function:

Package creates a nand gate with an input array of length N. ;

type nand\_input\_array is array(1..N) of pin:

type nand\_record is

-- Array of input pins for nand gate input : nand\_input\_array; output : pin; end record; record

type nand\_gate is access nand\_record:

function Create ret<sub>u</sub>rn nand gale:

-- Function:

-- Creates a new instance of the nand gate.

procedure Simulate (gate: in nand gate);

-- Function:

Simulates the nand gate by reading input values and determining ł

-- appropriate output and N\_Input\_Nand\_Mgr:

# Generic Nand Body

with Pin\_Mgr; use Pin\_Mgr:

package body N\_Input\_Nand\_Mgr is

-- Function:

This package body contains procedure and function details to implement a nand gate, namely Create and Simulate. 4

function Create return nand\_gate

-- Function:

-- Creates a new instance of a nand\_gate Space is allocated for a -- nand\_record and all pins are initialized to NULL

begin 9

return new nand\_record;

end Create;

procedure Simulate (gate : in nand gate)

-- Function:

-- This function simulates the logic of a nand gate from the input -- pins and sets the value of the output pin.

2

begin

for p in 1..N loop

if Value of (gate input(p)) = low then --I/all inputs are low Set value(gate output, high); refurn;

end if;

-- Otherwise output pin is -- low.

end N\_Input\_Nand\_Mgr; end Simulate: return;

Set\_Value(gate.output.low):

end loop:

# **Two-Input Nand Gate**

with N Input Nand Mgr;

package Two Input Nand Mgr is new N\_laput\_Nand\_Mgr{n => 2);

- ---- Instantiation of generic N\_Input\_Nand\_Mgr package creating a 2 -- input nand gate

# Three-Input Nand Gate

with N\_Input\_Nand\_Mgr;

package Three\_Input\_Nand\_Mgr is

new N\_Input\_Nand\_Mgr(n => 3);

- ---- Instantiation of generic N\_Input\_Nand\_M&r puckage creating a 3 -- input nand gate --

# **D** Latch Specification

with Pin\_Mgr. Inverter\_Mgr. Two\_Input\_Nand\_Mgr. Three\_Input\_Nand\_Mgr;

use Pin\_Mgr. Inverter\_Mgr. Two\_Input\_Nand\_Mgr. Three\_Input\_Nand\_Mgr;

package D\_latch\_Mgr is

- -- Function:

- This package specifies the external pin connections of a d\_latch and a function to create un instance of a d\_latch. The procedures to construct and simulate its execution are also described. Note that the d\_latch specified in this package is somewhat specialized in pin-out for use in constructing National Semiconductor's 74164 components.

- 1

- 1

type d\_latch\_components is private;

type d\_latch\_record is pin; :uiq Din pin: --- output pins -- private part -- input pins clock : dbar : clear : qbar record

type d\_latch is access d\_latch\_record;

components : d\_latch\_components; end record;

function Create return d latch;

- -- Function:

- Creates u d\_latch instance ;

procedure Construct(dlt : in d\_latch);

- -- Function:

- The specified d\_latch is constructed by first creating then connecting all internal components ł -

precedure Simulate(dlt : in d\_latch);

- -- Function:

- The specified d latch components are simulated in the exact order 11

- as a real chip would operate.

is array(1..3) of two\_input\_nand\_mgr.nand\_gate; type nand2\_array private

.

type d\_latch\_components is

: three\_input\_nand\_mgr\_nand\_gate; : inverter\_gate; nand2\_gates : nand2\_array; end D\_Latch\_Mgr; end record; inverter nand3 record

# D Latch Body

with Pin Mgr. Inverter Mgr. Two Input Nand Mgr. Three Input Nand Mgr. use Pin\_Mgr. Inverter Mgr. Two Input Nand Mgr. Three Input Nand Mgr;

# package body D\_latch\_Mgr is

- -- Function:

- This package describes the functions and procedures to produce

- a specified d latch to construct it from its components, and to simulate an actual electrically static case of reading input

- ;

- values and returning output values

function Create return d\_latch

- -- Function:

- This function creates an instancse of a d\_latch.

### begin 2

return new d\_latch\_record; end Create;

procedure Construct(dlt:in d latch)

- -- Function:

- This procedure builds the components of a d latch and

- interconnects them

- 9

## begin

- for i in 1..3

- **0**00

- dit.components.nand2 gates(i) := Create;

end loop:

:= Create; := Create: dit. components. inverter dit. components. nand3

-- three input nand\_gate. -- This creates a

## -- Equates Section

Equated dit. dbar dit. components. nard2\_gates(2). input(2)); Equated dit. clock dit. components. nand2\_gates(1). input(2)); Equated dit. clock dit. components. nand2\_gates(1). input(1)); Equated dit. clock dit. components. nand2\_fates(2). input(1)); Equated dit. clock alt. components. nand3\_input(3)); Equated dit. components. nand3. output dit. qbar); Equated dit. components. nand3. input(2) , dit. qbar); dlt . components . inverter . input ); Equate( dlt. dbar

## -- Connects Section

-----

Connect(dlt.components.inverter.output , dlt.components.nand2\_gates(1).input(1)); Connect(dlt.components.nand2\_gates(1).output , dlt.components.nand2\_gates(3).input(1)); Connect(dlt.components.nand2\_gates(2).output , dlt.components.nand3.input(2));

Connect(dlt.components.nand2\_gates(3).output . dlt.components.nand3.input(1)):

end Construct;

procedure Simulate(dlt:in d latch)

- -- Function:

- Each component of the d\_latch is simulated by reading input values

- and generating its output in the order that the circuit would normally be executed

## 0

### begin

Simulate( dlt. components. nand2\_gates( 1) ); Simulate( dt. components. nand2\_gates(2)) Simulate( dlt. corrponents. inverter);

- - Feedback loop exists between nand gates two und three. Simulate( dlt. components. nand2\_gates( 3) );

Simulate( dlt. components. nand3) ;

-- When a feedback loop exists then the first gate involved Simulate( dlt. components. nand2\_gates(3)); – is executed again.

end D Latch Mgr; end Simulate:

# **D** Flip-Flop Specification

Pin\_Mgr. D\_latch\_Mgr; Pin\_Mgr. D\_latch\_Mgr; with ļ

# package D\_Flip\_Flop\_Mgr is

- -- Function:

- This pockage specifies the input and output pins to a D\_Flip\_Flop provides operations to create and simulate instances of this component. ;

type d\_ff\_components is private:

# type d\_flip\_flop\_record is

-- Input clock signal (inverted) -- Input signal to clear the flip flop -- Clock signal to nun master latch -- Input data signal d (inverted). -- Output data signal q (invertad) : Dia: citbar : pin; clock : pin; clear : na; Indino ---- privale singni -dbar **P** record

type d\_Nip\_Nop is access d\_Nip\_Nop\_record;

componen : d fi components;

end record

unction Create return d\_flip\_flop;

- -- Function:

- -- Creates ad Aip flop

procedure Construct(dff: d\_flip\_flop);

- -- Function:

- Creates and interconnects components of a d flip flop

procedure Simulate( dff: d\_flip\_flop);

- -- Function:

- The specified d Aip Jop components are simulated in order. according to the pattern of signal flow from inputs to outputs

### private

type d bich array is array (1..2) of d bich;

type d\_ff\_components is

d\_latches : d\_latch\_array; end\_record; end D\_Flup\_Flop\_Mgr: record

# D Flip-Flop Body

ł

r

with P:n\_Mgr, D\_Latch\_Mgr; use Pin\_Mgr, D\_Latch\_Mgr;

# package body D\_Flip\_flop\_Mgr is

- -- Function:

- -- This puckage contains the procedure and function details required to execute the specifications given in the package D\_Hip\_Hop\_Mgr.

function Create return d\_flip\_flop

- -- Function:

- -- Creates a d Rip flop

begin 2

return new d\_flip\_flop\_r.v.ord; end Create; procedure Construct(dff: in J\_Nip\_Nop)

- -- Creates and interconnects . In ponents of a d flip flop -- Function:

- - begin 2

- -- Creates two instances of a 1 laich

- dff. components. d latches(1) := Create; dif. components. d\_latches(2) := Create;

- . . . . . . . . . . . . . . . . . . . -- Equates Section

Equate( dff. dbar , dff. components. d\_latches(1). dbar); Equate( dff. clock, dff. components. d\_latches(1). clock); Equate( dfi. clkbar, dff. components. d\_latches(2). clock); Equate( dff. components. d\_latches(2). qbar , dff. qbar);

- -- Connects Section

- Connect(dff.components.d\_latches(1).qbar, dff.components.d\_latches(2).dbar);

end Construct;

procedure Simulate (dff:in d\_flip\_flcp)

- -- Function:

- This procedure simulates the operation of the 1 fip\_flop ;

- by simulating its components i.e. by executing the functional behavior of its components

- - 2

- begin

- Simulate( dff. components. d latches(1)); Simulate( dff. components. d latches(2)); end D\_Flip\_Hop\_Mgr; end Sumulate;

# Shift Register Specification

Pin\_Mgr, Inverter\_Mgr, Two\_Input\_Nand\_Mgr, D\_Flip\_Flop\_Mgr; Pin\_Mgr, Inverter\_Mgr, Two\_Input\_Nand\_Mgr, D\_Flip\_Flop\_Mgr; with **156**

package Fight\_Bit\_Parallel\_Shift\_Register\_Mgr is

- -- Function:

- This package specifies an 8-bit serial-in parallel out shift register. The Crease function, and the procedures Construct, and Simulate are provided for this register. ł

- !

- ;

type output\_index is (a.b.c.d.e.f.g.h);

type pin\_array is array(output\_index) of pin;

type shifter\_components is private:

type shifter\_record is suid indui --record

- : Din : senal a : pin; senal b : pin; : biu : ciock clear

- : pin\_array; -- output pins output

- -- private part

components : shifter components; end record;

type shifter is access shifter\_record;

function Create return shifter;

- -- Function:

- Creates an instance of a shifter (shift register).

procedure Construct(sr: in out shifter);

- -- Function:

- Constructs the shifter's internal components and :

- interconnects them. ;

procedure Simulate(sr: in shifter);

- -- Function:

- -- 7 he specified shifter's components are simulated in order,

- -- according to the pattern of signal flow from inputs to outputs

- of the shifter.

type misc\_inverters\_atray is array(1..4) of inverter\_gate; private

type output\_inverter\_array is array(output\_index) of inverter\_gate;

type d\_flip\_flop\_array

is array(output\_index) of d\_flip\_flop;

type shifter\_components is record

output inverters : output inverter array; d flip\_flops : d flip\_flop\_array; : misc\_inverters\_array; : d\_flip\_flop\_array; : nand gate; misc inverters end record; nand

end Eight\_Bit\_Parallel\_Shift\_Register\_Mgr;

# Shift Register Body

with Pin\_Mgr. Inverter Mgr. Two\_Input\_Nand\_Mgr. D. Filp\_Fiop\_Mgr. usa Pin\_Mgr. Inverter\_Mgr. Two\_Input\_Nand\_Mgr. D\_Filp\_Flop\_Mgr;

package body Eight\_Bit\_Parallel\_Shift\_Register\_Mgr is

- -- Function:

- This package body specifies an 8-bit seriat-in parallet-out shift register whose internal structure conforms with the National

- Semiconductor 74164.

- The Create function, and the procedures Construct, and Simulate are provided for this register.

function Create return shifter

- -- Function:

- Creates an instance of a shifter. 3

- begin

- return new shifter record

- end Create;

procedure Construct(sr: in out shifter)

- -- Function:

- Constructs the suffer's internal components and

- interconnects the 'm ł

### begin .92

- Create all the components

- for m in output index

- 000

- -- Create the flip flops

- sr. components. d\_llip\_llops(m) := Create;

- -- Urvate the output inverters

- sr. components. output\_inverters(m) := Create;

- end loop

- -- Create (4) misc\_inverters

- for i in 1.4

- sr. components. mise inverters(i) :\* Create; dool

- end loop:

- -- Cruste a nand\_gate

- sr. components. nand := Create;

- -- Fquetes Section

- lor m in output\_index

- Fquate(sr.components.output\_inverters(m).output . sr.output(m));

- Fquate(sr.clear, sr.components.misc inverters(4).input); end loop;

- Fquate(sr.scrial\_a, sr.components.nand.input(1)); Equate(sr.scrial\_b, sr.components.nand.input(2));

- Equate (sr. clock, sr. components. misc inverters(1). input);

- -- Connects Section

- 000

- Connect(sr.components.misc inverters(1).output .

- sr. components. d flip\_flops(m). clkbar); Connect(sr. components. misc\_inverters(3). output.

- sr.components.d.fip\_flops(m).clock); Connect(sr.components.misc\_inv.rters(4).output,

- sr components. d flip\_flops(m).clear); Connect(sr.components. d flip\_flops(m).ybar

- sr. components. output\_inverters(m).input);

### end loop: also

- sr. components. misc\_inverters(3) mput); Connect(sr.components.misc\_inverters(2).coutput sr. components. d\_ flip\_flops(a). dtuar); for i in output\_index'(a).. output\_index'(g) Connect(sr.components.nand.output, -- and also chain the flip flops

- 000

- Connect(sr.components.d\_flip\_flops(i).ubar , sr.components.d\_flip\_flops(output\_index\*succ(i)).dbar); end loop;

## end Construct;

- procedure Simulate(sr:in shifter)

- -- Function:

- The specified shifter's components are simulated in order, ł

- according to the pattern of signal flow from inputs to outputs ;

- of the shifter. <u>.</u>2

1

### begin

- Simulate(sr.components.misc\_inverters(1)); Simulate(sr. components. misc inverters(3)) Simulate(sr.components.misc\_inverters(4)) Simulate(sr.components.misc\_inverters(2)) Simulate (sr. components. nand);

- -- These components can be simulated in a loop since all their inputs

- will have been generated dynamically.

- tor m in output\_index

- Simulate(sr.components.output\_inverters(m)); Simulate(sr.components.d\_flip\_flops(m); 000

- end loop:

- end Simulate;

- end Eight\_Bit\_Parallel\_Shift\_Register\_Mgr;

# Extended Pin Specification

0

(

## package Pin\_Mar is ;

This is an abrilyed writion of the pin manager package. It shows only

those declarations that are new or different from the original version.

;

## function Value\_of(

p : pin; de!ay\_value: natural := 0) return wire\_level\_value;

#

private

type time signal\_record;

type tune stand is access time signal record;

type step signal record;

type step signal is access step signal record;

type step send record is record is

stop value : wire level value := undefined; prev stop value : step.signal; end record;

# type time signal record is

unce value : step signal; previture value : time\_signal; end record; record

Let of prest the mathematical and the mathematical of press the mathematical is 0; end record; end Pra Mark : tume\_signal; type wire record is record velue

# **Extended Pin Body**

package body Pin\_Mgr is

This is an abruly. A version of the pin manager package. It shows only

those declarations that are new or different from the original version.

. . . . . . . . . . .

procedure Set\_valuc(s : in out step\_signal; v : wire\_level\_value) is

sl : step\_signal;

-- Function:

ALLS a value to a step\_signal history. 1

begin

sl := new step\_signal\_record:

sl.step\_value := v; si.prev\_scp\_value := s; s := sl; end Set\_value;

procedure Sci\_valuc(t : in out time\_signal; v : wire\_level\_value) is

-- Function:

ALLS a value to a time\_signal history begin

if t = null then t := new time\_signal\_record; end if; Set\_value(1.time\_value, v);

end Set\_value;

procedure Set\_value(p : pin; v : wire\_level\_value) is

-- Function:

-- Assigns a value to a wire record.

begin

if Connected(p) then

Set\_value(p.connecting\_wire.value, v): else

null: -- raise some exception

end if:

enci

function Value\_of(s : step\_signal) return wire\_level\_value is

-- Erene

-- Determines the value of a step\_signal and returns that value.

begin

if s = null

then return undefined; else return s.step\_value;

end if:

end

function Value\_of(1: tume\_signal; delay\_value: natural) return wire\_level\_value

tl: time\_signal;

if i = dclay\_value then return Value\_of(tl.thme\_value); else tl := tl.prev\_time\_value; end if; -- Function: -- Determines the value of a time\_signal and returns that value. then return undefined; if t1 = null for i in natural else tl := t; 000 begin

end loop; end:

end if;

function Value\_of(p: pin; delay\_value: natural := 0) return wire\_level\_value 5

-- Function:

Determines the value of a pin and returns that value. 5

return Value\_of(p. connecting\_wire.value, delay value); begin

end:

end Pin\_Mgr;