ASD(ENA)-TR-82-5031 VOLUME II

# 2nd AFSC STANDARDIZATION CONFERENCE

COMBINED PARTICIPATION BY: DOD-ARMY-NAVY-AIR FORCE-NATO

30 NOVEMBER - 2 DECEMBER 1982 TUTORIALS: 29 NOVEMBER 1982

## DAYTON CONVENTION CENTER DAYTON, OHIO

HOSTED BY

110

26

06

AD-A142 777

Approved for Public Release Distribution Unlimited

بلألجو

84

#### NOTICE

When Government drawings, specifications, or other data are used for any purpose other than in connection with a definitely related Government procurement operation, the United States Government thereby incurs no responsibility nor any obligation whatsoever; and the fact that the government may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data, is not to be regarded by implication or otherwise as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture use, or sell any patented invention that may in any way be related thereto.

This report has been reviewed by the Office of Public Affairs (ASD/PA) and is releasable to the National Technical Information Service (NTIS). At NTIS, it will be available to the general public, including foreign nations.

This technical report has been reviewed and is approved for publication.

Henry L Pester

JEFFERY L. PESLER Vice Chairman 2nd AFSC Standardization Conference

FOR THE COMMANDER

lest

ROBERT P. LAVOIE, COL, USAF Director of Avionics Engineering Deputy for Engineering

"If your address has changed, if you wish to be removed from our mailing list, or if the addressee is no longer employed by your organization please notify ASD/ENAS W-PAFB, OH 45433 to help us maintain a current mailing list".

Copies of this report should not, be returned unless return is required by security considerations, contractual obligations, or notice on a specific document.

ERWIN C. GANGL

Shief, Avionics Systems Division Directorate of Avionics Engineering

| UNCLASSIFIED<br>SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3. RECIPIENT'S CATALOG NUMBER                                                                                                                                                                                                                                                                                                                                                                              |

| AD 4142777                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4. TITLE (and Subtitle)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5. TYPE OF REPORT & PERIOD COVERED                                                                                                                                                                                                                                                                                                                                                                         |

| Proceedings Papers of the Second AFSC Avionics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Final Report<br> 29 November - 2 December 1982                                                                                                                                                                                                                                                                                                                                                             |

| Standardization Conference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6. PERFORMING O'G, REPORT NUMBER                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B. PERFORMING O'RG. REPORT NUMBER                                                                                                                                                                                                                                                                                                                                                                          |

| 7 AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8. CONTRACT OR GRANT NUMBER(S)                                                                                                                                                                                                                                                                                                                                                                             |

| Editor: Cynthia A. Porubcansky                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9. PERFORMING ORGANIZATION NAME AND ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS                                                                                                                                                                                                                                                                                                                                             |

| HQ ASD/ENAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            |

| Wright-Patterson AFB OH 45433                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1. CONTROLLING OFFICE NAME AND ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12. REPORT DATE                                                                                                                                                                                                                                                                                                                                                                                            |

| HQ ASD/ENA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | November 1982                                                                                                                                                                                                                                                                                                                                                                                              |

| Wright-Patterson AFB OH 45433                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13. NUMBER OF PAGES                                                                                                                                                                                                                                                                                                                                                                                        |

| 14. MONITORING AGENCY NAME & ADDRESS(if different from Controlling Office)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15. SECURITY CLASS. 'of this report)                                                                                                                                                                                                                                                                                                                                                                       |

| Same as Above                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Unclassified                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 154. DECLASSIFICATION DOWNGRADING<br>SCHEDULE                                                                                                                                                                                                                                                                                                                                                              |

| 16. DISTRIBUTION STATEMENT (of this Report)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | J                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                                                                                                                                                                                                                                                                                                                                                                                                          |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the ebstract entered in Block 20, If different fro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                            |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the ebetract entered in Block 20, If different fro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                            |

| Approved for public release; distribution unlimited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                            |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the abetract entered in Block 20, if different fro<br>N/A<br>18. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                            |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the abetract entered in Block 20, if different fro<br>N/A<br>18. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                            |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the obstract entered in Block 20, if different fro<br>N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                            |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the obstract entered in Block 20, if different fro<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | m Report)                                                                                                                                                                                                                                                                                                                                                                                                  |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the obstract entered in Block 20, if different fro<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,<br>Computer Instruction Set Architecture, Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <pre>&gt;m Report) &gt;m Report) &gt; Compiler sr Support Software</pre>                                                                                                                                                                                                                                                                                                                                   |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the obstract entered in Block 20, if different for<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,<br>Computer Instruction Set Architecture, Multiplexing,<br>Data Bus, Rational Standardization, Digital Avionic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <pre>m Report) m Report)  Compilers Support Software System Integration/ Stores</pre>                                                                                                                                                                                                                                                                                                                      |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the obstract entered in Block 20, if different ind<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,<br>Computer Instruction Set Architecture, Multiplexing<br>Data Bus, Rational Standardization, Digital Avionic<br>Interface, Standardization, MIL-STD-1553, MIL-STD-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <pre>&gt;m Report) &gt; Compilers&gt; Support Software&gt; &gt; &gt; &gt; &gt; &gt; &gt; System Integration&gt; Stores 5 &gt; &gt;</pre>                                                                                                                                 |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the observant entered in Block 20, if different ind<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,<br>Computer Instruction Set Architecture, Multiplexing<br>Data Bus, Rational Standardization, Digital Avionic<br>Interface, Standardization, MIL-STD-1553, MIL-STD-1<br>MIL-STD-1760, MIL-STD-1815 (ADA), MIL-STD-1862 (NEB)                                                                                                                                                                                                                                                                                                                                                                                                                                          | <pre>m Report)  Compilers, Support Software, System Integration, Stores 589 (JOV1AL), MiL-STD-1750, ULA).</pre>                                                                                                                                                                                                                                                                                            |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the obstract entered in Block 20, if different for<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,<br>Computer Instruction Set Architecture, Multiplexing<br>Data Bus, Rational Standardization, Digital Avionic<br>Interface, Standardization, MIL-STD-1553, MIL-STD-1<br>MIL-STD-1760, MIL-STD-1815 (ADA), MIL-STD-1862 (NEB)<br>20. ABSTRACT (Continue on reverse side if necessary and identify by block number)                                                                                                                                                                                                                                                                                                                                                      | <pre>&gt; Compilers, Support Software,<br/>&gt; System Integration, Stores<br/>589 (JOVIAL), MiL-STD-1750,<br/>ULA).</pre>                                                                                                                                                                                                                                                                                 |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the obstract entered in Block 20, If different fro<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,<br>Computer Instruction Set Architecture, Multiplexing<br>Data Bus, Rational Standardization, Digital Avionic<br>Interface, Standardization, MIL-STD-1553, MIL-STD-1<br>MIL-STD-1760, MIL-STD-1815 (ADA), MIL-STD-1862 (NEB)<br>10. ABSTRACT (Continue on reverse side If necessary and identify by block number)<br>This is a collection of UNCLASSIFIED papers to be d<br>of the Second AFSC Avionics Standardization Conference                                                                                                                                                                                                                                     | <pre>im Report)  Compilers, Support Software, S, System Integration, Stores S89 (JOVLAL), MiL-STD-1750, ULA).  istributed to the attendees nce at the Convention Center, </pre>                                                                                                                                                                                                                            |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the observed entered in Block 20, If different for<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,<br>Computer Instruction Set Architecture, Multiplexing<br>Data Bus, Rational Standardization, Digital Avionic<br>Interface, Standardization, MIL-STD-1553, MIL-STD-1<br>MIL-STD-1760, MIL-STD-1815 (ADA), MIL-STD-1862 (NEB<br>10. ABSTRACT (Continue on reverse side If necessary and identify by block number)<br>This is a collection of UNCLASSIFIED papers to be d<br>of the Second AFSC Avionics Standardization Conference<br>Dayton, Ohio. The scope of the Conference includes                                                                                                                                                                                | <pre>&gt;&gt; Compilers, Support Software,<br/>&gt;&gt; Compilers, Support Software,<br/>&gt;&gt; System Integration, Stores<br/>589 (JOV1AL), MiL-STD-1750,<br/>ULA).<br/>istributed to the attendees<br/>nce at the Convention Center,<br/>the complete range of DoD</pre>                                                                                                                               |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the observed entered in Block 20, If different for<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,<br>Computer Instruction Set Architecture, Multiplexing<br>Data Bus, Rational Standardization, Digital Avionic<br>Interface, Standardization, MIL-STD-1553, MIL-STD-1<br>MIL-STD-1760, MIL-STD-1815 (ADA), MIL-STD-1862 (NEB<br>10. ABSTRACT (Continue on reverse side If necessary and identify by block number)<br>This is a collection of UNCLASSIFIED papers to be d<br>of the Second AFSC Avionics Standardization Conference<br>Dayton, Ohio. The scope of the Conference includes<br>approved embedded computer hardware/software and re                                                                                                                         | <pre>&gt;&gt; Compilers, Support Software,<br/>&gt;&gt; System Integration, Stores<br/>589 (JOVIAL), MiL-STD-1750,<br/>ULA).<br/>istributed to the attendees<br/>nce at the Convention Center,<br/>the complete range of DoD<br/>lated interface standards as</pre>                                                                                                                                        |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the obstract entered in Block 20, If different inc<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,<br>Computer Instruction Set Architecture, Multiplexing<br>Data Bus, Rational Standardization, Digital Avionic<br>Interface, Standardization, MIL-STD-1553, MIL-STD-1<br>MIL-STD-1760, MIL-STD-1815 (ADA), MIL-STD-1862 (NEB)<br>10. ABSTRACT (Continue on reverse side if necessary and identify by block number)<br>This is a collection of UNCLASSIFIED papers to be d<br>of the Second AFSC Avionics Standardization Conference<br>Dayton, Ohio. The scope of the Conference includes<br>approved embedded computer hardware/software and re<br>well as standard subsystems used within the Tri-Ser-                                                                | <pre>&gt;&gt; Compilers, Support Software,<br/>&gt;&gt; Compilers, Support Software,<br/>&gt;&gt; System Integration, Stores<br/>589 (JOV1AL), Mil-STD-1750,<br/>ULA).<br/>istributed to the attendees<br/>nce at the Convention Center,<br/>the complete range of DoD<br/>lated interface standards as<br/>vice community and NATO. The</pre>                                                             |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the obstract subserved in Block 20, If different ind<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,<br>Computer Instruction Set Architecture, Multiplexing<br>Data Bus, Rational Standardization, Digital Avionic<br>Interface, Standardization, MIL-STD-1553, MIL-STD-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <pre>&gt; Compilers &gt; Support Software&gt;<br/>&gt; System Integration&gt; Stores<br/>589 (JOVIAL)&gt; MiL-STD-1750&gt;<br/>ULA).<br/>istributed to the attendees<br/>nce at the Convention Center&gt;<br/>the complete range of DoD<br/>lated interface standards as<br/>vice community and NATO. The<br/>n<sup>m</sup>: Lessons learned as well</pre>                                                 |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the obstract entered in Block 20, If different income<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,<br>Computer Instruction Set Architecture, Multiplexing,<br>Data Bus, Rational Standardization, Digital Avionic<br>Interface, Standardization, MIL-STD-1553, MIL-STD-1<br>MIL-STD-1760, MIL-STD-1815 (ADA), MIL-STD-1862 (NEB)<br>10. ABSTRACT (Continue on reverse side if necessary and identify by block number)<br>This is a collection of UNCLASSIFIED papers to be d<br>of the Second AFSC Avionics Standardization Conference<br>Dayton, Ohio. The scope of the Conference includes<br>approved embedded computer hardware/software and re<br>well as standard subsystems used within the Tri-Service<br>theme of the conference is "Rational Standardization | <pre>&gt; Compilers &gt; Support Software&gt;<br/>&gt; System Integration&gt; Stores<br/>589 (JOVIAL)&gt; MiL-STD-1750&gt;<br/>ULA).<br/>istributed to the attendees<br/>nce at the Convention Center&gt;<br/>the complete range of DoD<br/>lated interface standards as<br/>vice community and NATO. The<br/>n<sup>m</sup>: Lessons learned as well</pre>                                                 |

| Approved for public release; distribution unlimited<br>17. DISTRIBUTION STATEMENT (of the obstract entered in Block 20, If different income<br>N/A<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block number,<br>Computer Instruction Set Architecture, Multiplexing,<br>Data Bus, Rational Standardization, Digital Avionic<br>Interface, Standardization, MIL-STD-1553, MIL-STD-1<br>MIL-STD-1760, MIL-STD-1815 (ADA), MIL-STD-1862 (NEB)<br>10. ABSTRACT (Continue on reverse side if necessary and identify by block number)<br>This is a collection of UNCLASSIFIED papers to be d<br>of the Second AFSC Avionics Standardization Conference<br>Dayton, Ohio. The scope of the Conference includes<br>approved embedded computer hardware/software and re<br>well as standard subsystems used within the Tri-Service<br>theme of the conference is "Rational Standardization | <pre>&gt;&gt; Compilers &gt; Support Software&gt;<br/>&gt;&gt; System Integration&gt; Stores<br/>5&gt; System Integration&gt; Stores<br/>589 (JOVIAL)&gt; MiL-STD-1750&gt;<br/>ULA).<br/>istributed to the attendees<br/>nce at the Convention Center&gt;<br/>the complete range of DoD<br/>lated interface standards as<br/>vice community and NATO. The<br/>n<sup>m</sup>: Lessons learned as well</pre> |

6

•

### This is Volume 2

| votruue t | Proceedings pp. 1-560    |

|-----------|--------------------------|

| Volume 2  | Proceedings pp. 561-1131 |

| Volume 3  | Governing Documents      |

| Volume 4  | MIL-SID-1553 Tutorial    |

| Volume 5  | MIL-STD-1589 Tutorial    |

| Volume 6  | MIL-STD-1679 Tutorial    |

| Volume 7  | MIL-SID-1750 Tutorial    |

| Volume 8  | MIL-STD-1815 Tutorial    |

| Volume 9  | Navy Case Study Tutorial |

|           |                          |

### PROCEEDINGS OF THE

# 2nd AFSC STANDARDIZATION CONFERENCE

30 NOVEMBER - 2 DECEMBER 1982

DAYTON CONVENTION CENTER DAYTON, OHIO

Sponsored by:

Hosted by:

Air Force Systems Command

برالحد

Aeronautical Systems Division

#### FOREWORD

THE UNITED STATES AIR FORCE HAS COMMITTED ITSELF TO "STANDARDIZATION." THE THEME OF THIS YEAR'S CONFERENCE IS "RATIONAL STANDARDIZATION," AND WE HAVE EXPANDED THE SCOPE TO INCLUDE US ARMY, US NAVY AND NATO PERSPECTIVES ON ONGOING DOD INITIATIVES IN THIS IMPORTANT AREA.

WHY DOES THE AIR FORCE SYSTEMS COMMAND SPONSOR THESE CONFERENCES? BECAUSE WE BELIEVE THAT THE COMMUNICATIONS GENERATED BY THESE GET-TOGETHERS IMPROVE THE ACCEPTANCE OF OUR NEW STANDARDS AND FOSTERS EARLIER, SUCCESSFUL IMPLEMENTATION IN NUMEROUS APPLICATIONS. WE WANT ALL PARTIES AFFECTED BY THESE STANDARDS TO KNOW JUST WHAT IS AVAILABLE TO SUPPORT THEM: THE HARDWARE; THE COMPLIANCE TESTING; THE TOOLS NECESSARY TO FACILITATE DESIGN, ETC. WE ALSO BELIEVE THAT FEEDBACK FROM PEOPLE WHO HAVE USED THEM IS ESSENTIAL TO OUR CONTINUED EFFORTS TO IMPROVE OUR STANDARDIZATION PROCESS. WE HOPE TO LEARN FROM OUR SUCCESSES AND OUR FAILURES; BUT FIRST, WE MUST KNOW WHAT THESE ARE AND WE COUNT ON YOU TO TELL US.

AS WE DID IN 1980, WE ARE FOCUSING OUR PRESENTATIONS ON GOVERNMENT AND INDUSTRY EXECUTIVES, MANAGERS, AND ENGINEERS AND OUR GOAL IS TO EDUCATE RATHER THAN PRESENT DETAILED TECHNICAL MATERIAL. WE ARE STRIVING TO PRESENT, IN A SINGLE FORUM, THE TOTAL AFSC STANDARDIZATION PICTURE FROM POLICY TO IMPLEMENTATION. WE HOPE THIS INSIGHT WILL ENABLE ALL OF YOU TO BETTER UNDERSTAND THE "WHY'S AND WHEREFORE'S" OF OUR CURRENT EMPHASIS ON THIS SUBJECT.

MANY THANKS TO A DEDICATED TEAM FROM THE DIRECTORATE OF AVIONICS ENGINEERING FOR ORGANIZING THIS CONFERENCE; FROM THE OUTSTANDING TECHNICAL PROGRAM TO THE UNGLAMOROUS DETAILS NEEDED TO MAKE YOUR VISIT TO DAYTON, OHIO A PLEASANT ONE. THANKS ALSO TO ALL THE MODERATORS, SPEAKERS AND EXHIBITORS WHO RESPONDED IN SUCH A TIMELY MANNER TO ALL OF OUR PLEAS FOR ASSISTANCE.

ROBERT P. LAVOIE, COL, USAF DIRECTOR OF AVIONICS ENGINEERING DEPUTY FOR ENGINEERING

ji hark

DEPARTMENT OF THE AIR FORCE HEADQUARTERS AIR FORCE SYSTEMS COMMAND ANDREWS AIR FORCE BASE DO 20334

2 8 AUG 1982

ACHLY TO CV

Second AFSC Standardization Conference

#### -- ASD/CC

1. Since the highly successful standardization conference hosted by ASD in 1980, significant technological advancements have occurred. Integration of the standards into weapon systems has become a reality. As a result, we have many "lessons learned" and cost/benefit analyses that should be shared within the tri-service community. Also, this would be a good opportunity to update current and potential "users." Therefore, I endorse the organization of the Second AFSC Standardization Conference.

2. This conference should cover the current accepted standards, results of recent congressional actions, and standards planned for the future. We should provide the latest information on policy, system applications, and lessons learned. The agenda should accommodate both government and industry inputs that criticize as well as support our efforts. Experts from the tri-service arena should be invited to present papers on the various topics. Our AFSC project officer, Maj David Hammond, HQ AFSC/ALR, AUTOVON 858-5731, is prepared to assist.

ROBERT M. BOND, Lt Gen, USAE Vice Commander

رداله

### 2nd AFSC STANDARDIZATION CONFERENCE

- -----

• .\*

۰.-

- - --

### **ORGANIZATION COMMITTEE**

EXECUTIVE CHAIRMAN Erwin C. Gangl

EXECUTIVE VICE CHAIRMAN Jeffery L. Pesler

> PROGRAM CHAIRMAN Jerry L. Duchene

CO-CHAIRMAN Harold J. Alber

ľ

È

CO-CHAIRMAN Maj Lee Cheshire

CO-CHAIRMAN David J. Krile

EXHIBITS CHAIRMAN Lt C.W. (Bud) Meyaard

SPECIAL ARRANGEMENTS CHAIRMAN Lt Dennis A. Shoulders

> ADMINISTRATIVE CHAIRMAN Marie P. Jankovich

CO-CHAIRMAN John Slivinski

PUBLICATIONS CHAIRMAN Cindy Porubcansky

PROTOCOL OFFICER Capt Francis A. DeCurtis

TREASURER Richard H. McBride

CONFERENCE MANAGER Systems Productivity & Management Corporation

# Tuesday Luncheon Keynote Speaker

### Major General Marc C. Reynolds

Major General Marc C. Reynolds is Commander of the Air Force Acquisition Logistics Division, and Deputy Chief of Staff for Acquisition Logistics, Air Force Logistics Command, Wright-Patterson Air Force Base, Ohio.

General Reynolds was born in Chamberlain, S.D., on June 2, 1928, and graduated from Chamberlain High School in 1946. He subsequently attended Dakota Wesleyan University and the University of Denver until the outbreak of the Korean War. He holds a Bachelor's Degree in Political Science from the University of Rhode Island and is a graduate of the Air Command and Staff College and the Naval War College.

General Reynolds entered the Air Force as an aviation cadet in January 1951 at Perrin Air Force Base, Texas, and was commissioned upon graduation from pilot training at Vance Air Force Base, Okalahoma, in February 1952. He then attended jet interceptor training at Moody Air Force Base, Georgia, and Tyndall Air Force Base, Florida.

In July 1952, General Reynolds was assigned pilot duty with the 83rd Fighter-Interceptor Squadron at Hamilton Air Force Base, California, and in September he moved with the squadron to Paine Air Force Base, Washington. In March 1953, he was transferred to the 4th Fighter-Interceptor Squadron at Naha Air Base, Okinawa, where he continued to serve as a fighter-interceptor pilot, flying the F-94B.

His next assignment, in September 1954, was Otis Air Force Base, Mass., where he served with the 437th and 60th Fighter-Interceptor Squadrons as a tactical and training flight commander, flying the F-94C and F-101B, and with the 602d Consolidated Maintenance Squadron as a maintenance officer.

General Reynolds was transferred to Europe in November 1961, assigned to the 10th Tactical Reconnaissance Wing, with duty at RAF Station Bruntingthorpe, England, as a Flight Commander, and later at Toul-Rosieres Air Base, France, as Chief of the Wing Standardization Evaluation Branch.

After Command and Staff College at Maxwell Air Force Base, Alabama, General Reynolds was assigned to the 22d Tactical Reconnaissance Squadron, Mountain Home Air Force Base, Idaho. In November 1966, he moved to the 460th Tactical Reconnaissance Wing at Tan Son Nhut Air Base, Republic of Vietnam, and flew 230 combat missions over North and South Vietnam in RF-4C.

(over)

vii

yr Unob

Following his Southeast Asia tour, he served in Japan as Deputy Chief of the Reconnaissance Division, Headquarters Fifth Air Force, Fuchu Air Station. In April 1970, he moved to Misawa Air Base as Commander of the 16th Tactical Reconnaissance Squadron.

General Reynolds returned to the United States in February 1971, assigned to Shaw Air Force Base, S.C., where he served as Assistant Deputy Commander for Operations in the 363d Tactical Reconnaissance Wing. He attended the Naval War College at Newport, R.I., in 1972-73 and was subsequently assigned to Ogden Air Logistics Center, Hill Air Force Base, Utah, initially as the Director of Distribution and later 33 Director of Maintenance. In July 1976, he was transferred to McClellen Air Force Base, California, as the Director of Materiel Management, Sacrossito Air Logistics Center. In March 1978, he became the Center Vice Commander. He transferred to the Air Force Acquisition Logistics Division in May 1980, where he served as Vice Commander until October 1981, when he assumed his present duties.

General Reynolds is a command pilot with more than 5,200 hours flying time, including 475 combat hours. His military decorations and awards include the Distinguished Service Medal, Legion of Merit, Distinguished Flying Cross, Meritoricus Service Medal with one cak leaf cluster, Air Medal with 15 cak leaf clusters, and Air Force Commendation Medal with two cak leaf clusters.

He was provoted to Madow General Sept 8, 1980, with date of rank July 1, 1977.

General Reynolds was married to the former Judy Coppage of Falmouth, Mass., who died in February 1982. Their children are Barbara and Scott.

### COMPONENT PART NOTICE

THIS PAPER IS A COMPONENT PART OF THE FOLLOWING COMPILATION REPORT:

(IIILE): Proceedings Papers of the AFSC (Air Force Systems Command) Avionics

Standardization Conference (2nd) Held at Dayton, Ohio on 30 November-

2 December 1982. Volume 2.

(SOURCE); Aeronautical Systems Div., Wright-Patterson AFB, OH.

TO ORDER THE COMPLETE COMPILATION REPORT USE AD-A142.777

THE COMPONENT PART IS PROVIDED HERE TO ALLOW USERS ACCESS TO INDIVIDUALLY AUTHORED SECTIONS OF PROCEEDINGS, ANNALS, SYMPOSIA, ETC. HOWEVER, THE COMPONENT SHOULD BE CONSIDERED WITHIN THE CONTEXT OF THE OVERALL COMPILATION REPORT AND NOT AS A STAND-ALONE TECHNICAL REPORT.

JUL 1 3 198/

Α

THE FOLLOWING COMPONENT PART NUMBERS COMPRISE THE COMPILATION REPORT:

### AD#: TITLE:

| AD-P003 | 561              | Standards and Integrated Avionic Digital System<br>Architecture.                                                             |

|---------|------------------|------------------------------------------------------------------------------------------------------------------------------|

| AD-P003 | 562              | Achieving the Benefits of Modular Avionics Design.                                                                           |

| AD-P003 |                  | Standard ISAS (Instruction Set Architectures) and<br>VISI (Very Large Scale Integration): Two Interacting<br>Trends.         |

| AD P003 | 561              | Navy Packaging Standardization Thrusts.                                                                                      |

| AD-P003 |                  | An Introduction to the Avionics Integrity Program.                                                                           |

| AD-P003 |                  | Elements for Successful Implementation of Computing Standards.                                                               |

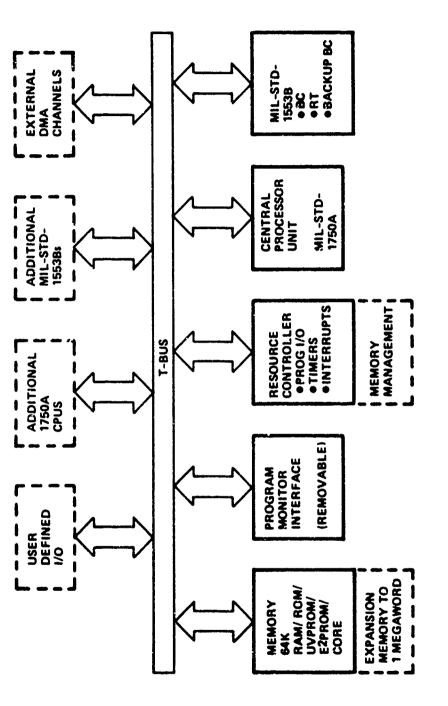

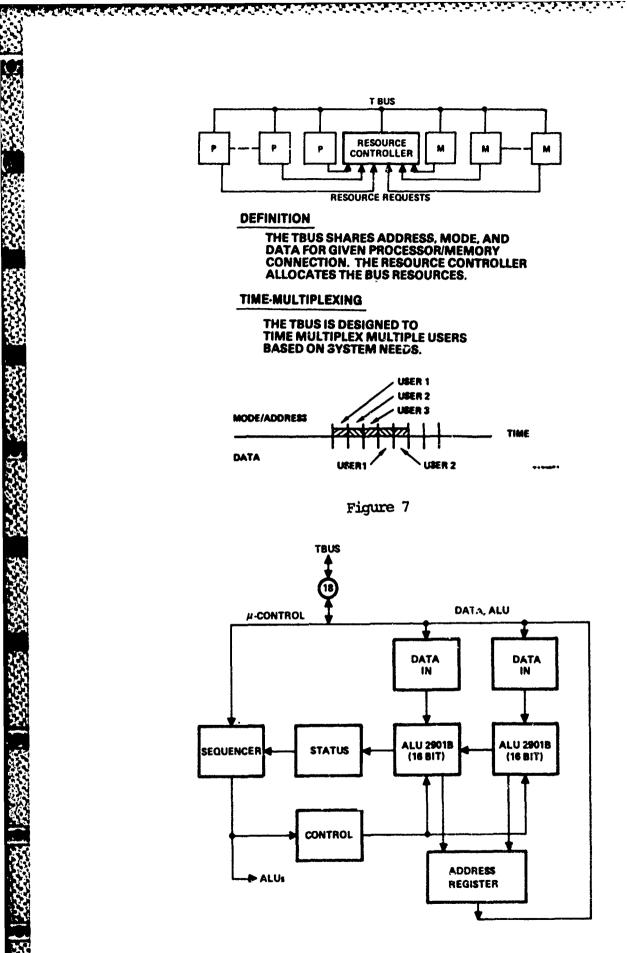

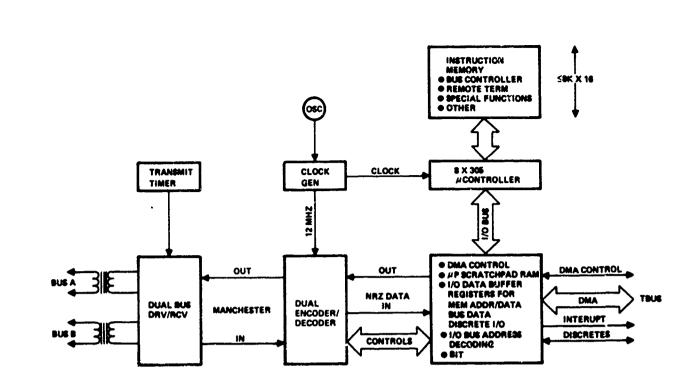

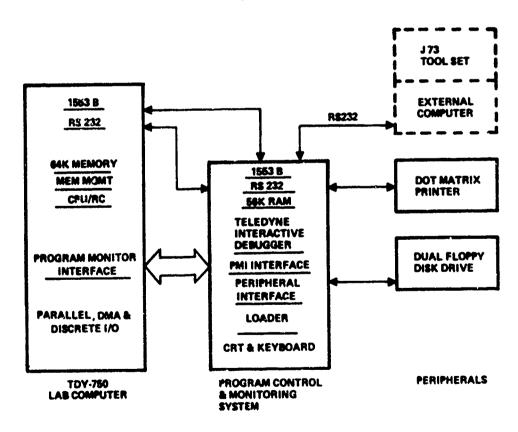

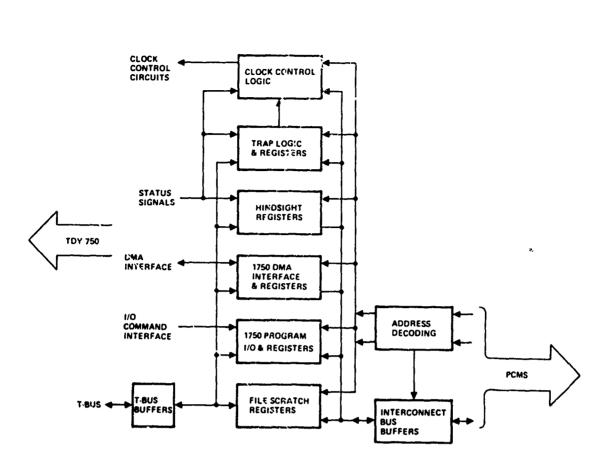

| AD-P003 | 567 <sup>.</sup> | The Application of Standards to the TDY-750<br>(Tigershark) Mission Computer.                                                |

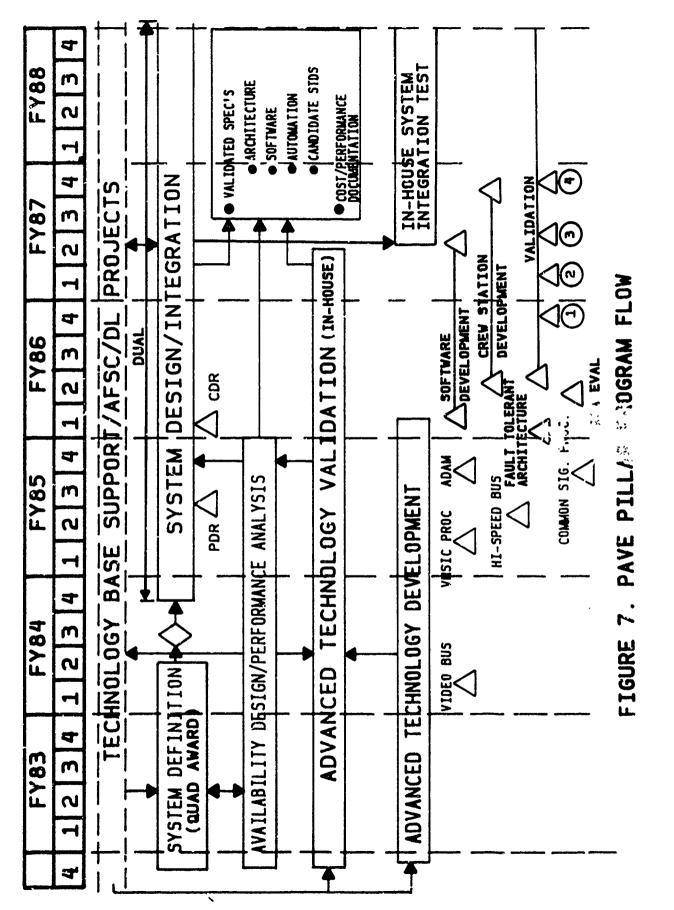

| AD-P003 | 568              | Pavo Pillar: A Maturation Process for an advanced                                                                            |

|         |                  | Avionics Architecture.                                                                                                       |

| AD-P003 | 569              | Advanced Cockpit-Systems Integration,                                                                                        |

| AD P003 | 570              | Defense Industry Attitudes About Air Force Interface<br>Standards Report of an Electronics Industries<br>Association Survey. |

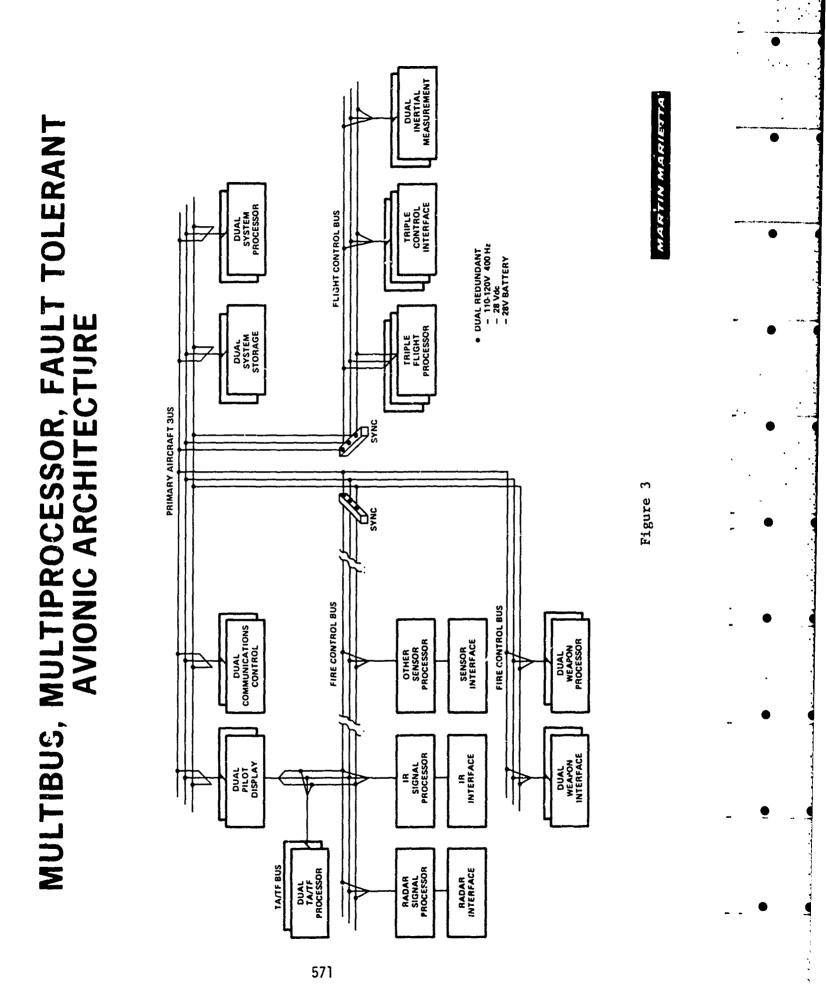

| AD-P003 | 571              | Digital Avionics Design for Validation.                                                                                      |

| AD-P003 |                  | Westinghouse Uses U.S. Air Force-Developed Standards.                                                                        |

| AL-P003 |                  | A General Purpose Computer Architecture Investigation Facility.                                                              |

| ADP003  | 574              | Integrated Approach to a Successful Embedded ;<br>Computer Resource Project.                                                 |

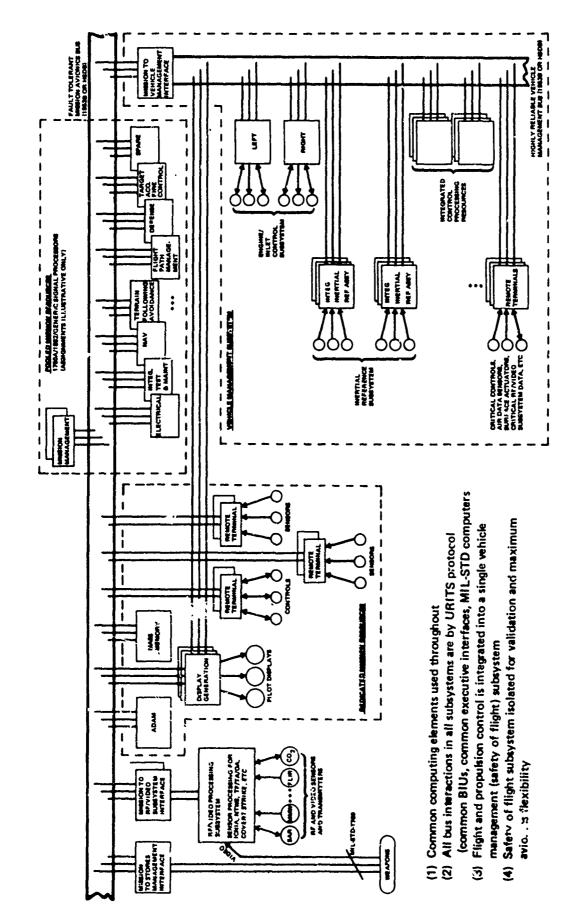

| AD P003 | 575              | Concepts for LHX Avionics.                                                                                                   |

| AD-P003 |                  | MIL-Prime Program System,                                                                                                    |

| AD-P003 |                  | Options and Opportunities for Standards: A<br>NATO/AGARD Viewpoint.                                                          |

| AD-P003 | 578              | Proposed MIL-STD for Avionics Installation Interfaces.                                                                       |

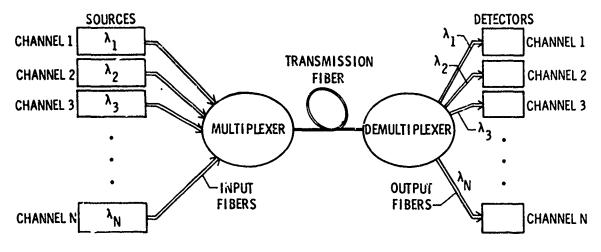

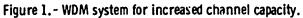

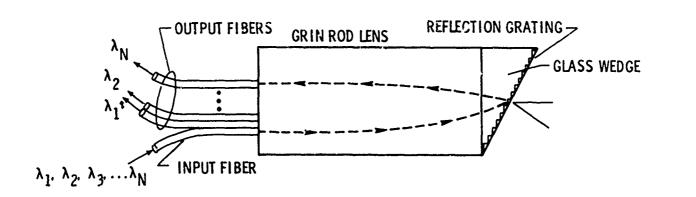

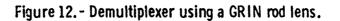

| AD-P003 | 579              | Fiber Iptics for the Future - Wavelength Division<br>Multiplexing.                                                           |

### COMPONENT PART NOTICE (CON'T)

AD#: TITLE:

| AD-P003 | 580 | Integrated CNI (Communication Navigation and<br>Identification) Avionics and Future<br>Standardization.                   |

|---------|-----|---------------------------------------------------------------------------------------------------------------------------|

| AD-P003 | 581 | Architecture, Hardware and Software Issues in<br>Fielding the Next Generation DOD Processors.                             |

| AD-P003 | 582 | Standard Avionics Software: The Future Strategy<br>for Cost-Effective Avionics.                                           |

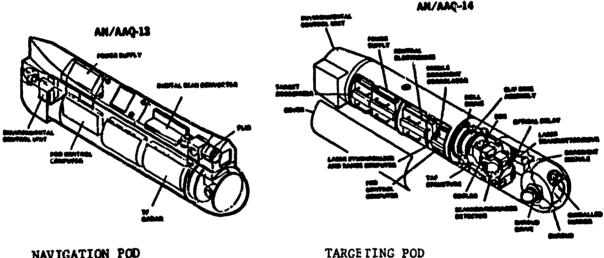

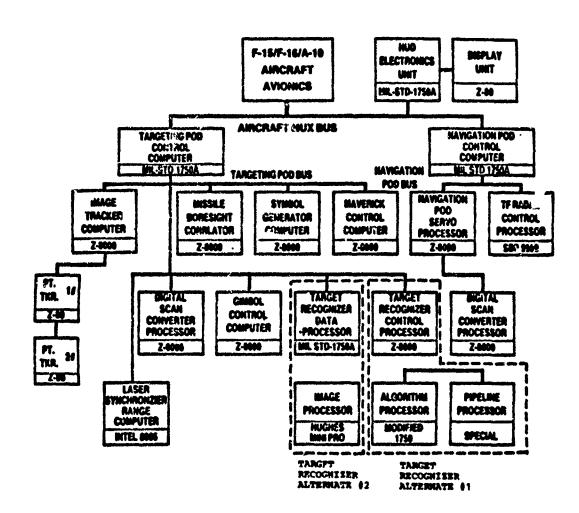

| ADP003  | 583 | Lantirn (Low Altitude Navigation and Targeting<br>Infrared System for Night) - Tommorrow's<br>Software Development Today. |

| AD-P003 | 584 | Quantum Leap in Avionics.                                                                                                 |

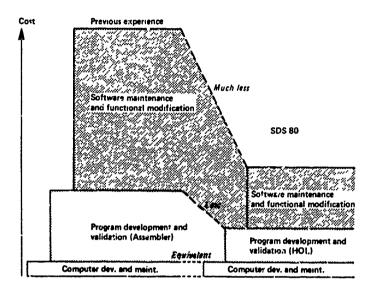

| AD-P003 |     | Standardiged Computing System SDS80.                                                                                      |

| AD-P003 |     | Tri-Service Combined Altitude Radar Altimeter                                                                             |

|         |     | (CARA): The Army Perspective.                                                                                             |

| AD-P003 | 587 | Mate Standardization.                                                                                                     |

| AD-P003 |     | System Planning Tool to Measure Cost Avoidance                                                                            |

|         |     | Resulting from Indendent Assessment Techniques<br>Applied to Test Program Software Development.                           |

| AD-P003 | 589 | A Corporate Approach to an Embedded Software                                                                              |

| •       |     | Development and Support Standard.                                                                                         |

| AD-P003 | 590 | MIL-STD Defense System Software Development.                                                                              |

| AD-P003 |     | Cost/Schedule Management for Software                                                                                     |

|         |     | Development.                                                                                                              |

| AD-P003 | 592 | Software Configuration Management in a                                                                                    |

|         |     | Project Environment.                                                                                                      |

| AD-P003 | 593 | APSE Datapase User Scenario.                                                                                              |

| AD-P003 |     | Architectural and Control Considerations for                                                                              |

|         |     | a High Speed Signal Processor Implemented with<br>an Ada (Prademark) Executive.                                           |

| AD-P003 | 595 | Planning of Operational Software Implementation                                                                           |

| -       |     | Tcol.                                                                                                                     |

|      | ing son<br>wasi<br>RP<br>tuncod<br>Classion_ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|