MICROCOPY RESOLUTION TEST CHART NATIONAL HUBBAD OF STANDARDS (2004) CHILTON, DIDCOT, OXON, OX11 OQX

RL-82-020

# A Floating Point Processor for INTEL 8080A Microprocessor Systems

AD-A141 993

3. 3. j. - 1.

R Bairstow, J Barlow, M Jires and M Waters.

March 1982

FILE COPY

MARCH 1982 CONTROLLER HMSD LONDON BELECTE JUN 1 2 1984 E 84 06 11 075

6

COPYRIGHT

#### A FLOATING POINT PROCESSOR FOR INTEL 8080A

#### MICRO PROCESSOR SYSTEMS

R. Bairstow, J. Barlow, M. Jires<sup>\*</sup>, M. Waters

Summary

An A.M.D. 9511 Floating Point Processor<sup>(1)</sup> has been interfaced to the Rutherford Laboratory Bubble Chamber Group's micro computers<sup>(2)</sup>. These computers are based on the INTEL 3080A micro processor. The interface uses a memory mapped I/O technique to ensure rapid transfer of arguments between processors. The A.M.D. 9511 acts as a slave processor to the INTEL 3080A system. The 8080 processor is held in 'WAIT' status until completion of the A.M.D. operation.

A software Macro Processor has been written to effectively extend the basic INTEL 8080A instruction set to include the full range of A.M.D. 9511 instructions.

Visitor from the Faculty of Mathematics and Physics, Charles University, PRAGUE.

## CONTENTS

Page

| ι.    | Intro   | duction                                     | r) |

|-------|---------|---------------------------------------------|----|

| 2.    | Inter   | facing the AM 9511 to an INTEL 8080A system | 7  |

|       | 2.1     | The Hardware Interface                      | 7  |

|       | 2.2     | The Software Interface                      | S  |

| 3.    | The M   | 9511 Macro Language                         | 9  |

|       | 3.1     | Basic Definitions and Comments              | ò  |

|       | 3.2     | The Mainstream Data Set                     | 10 |

|       | 3.3     | The Input Data Set                          | 10 |

|       |         | 3.3.1 Description of the Structure          | 10 |

|       |         | 3.3.2 M9511 Syntax Definition               | 11 |

|       |         | 3.3.3 M9511 Semantics                       | 13 |

|       | 3.4     | The Output File                             | 14 |

|       |         | 3.4.1 Description of Structure              | 14 |

|       |         | 3.4.2 Syntax of M9511 Expansion             | 15 |

|       | 3.5     | The Print File                              | 15 |

|       |         | 3.5.1 Description of Structure              | 15 |

|       |         | 3.5.2 Errors and Warnings                   | 16 |

|       |         | 3.5.3 AM 9511 Stack Simulation              | 16 |

| 4.    | The M   | 9511 Macro Processor - Translator           | 13 |

|       | 4.1     | Basic Structure                             | 18 |

|       | 4.2     | Coding Method                               | 18 |

| 5.    | Conclu  | usion                                       | 19 |

|       |         |                                             |    |

| Apper | ndix I  | INTEL 3080A - Partial Syntax Definitions    | 20 |

| Appe  | ndix I  | I M9511 Macro Instruction Set               | 21 |

| Apper | ndix II | II Code Generators                          | 24 |

-2-

|             |                                                               | Page |

|-------------|---------------------------------------------------------------|------|

| Appendix IV | Examples                                                      | 29   |

| Appendix V  | Using the M9511 Macro Processor on a VAX 11/780 host computer | 37   |

-3-

#### 1. INTRODUCTION

At the present time, the largest sector of the micro computer market is that covered by the 8 bit micro-processors of which INTEL 8080A/8085/8048. MOTOROLA 6800 and FAIRCHILD F8 are well known examples. These microprocessors have found wide acceptance for many control and data handling tasks and indeed provide highly satisfactory solutions to many problems. They are particularly suited to many communication problems that are S bit orientated. However, their 8 bit architecture is somewhat of a limiting factor in applications involving numerical computation. Such computations requiring cnly single (16 bit) or perhaps even double (32 bit) precision integer or fixed point arithmetic can be handled without too much difficulty by software methods. These methods are slow to execute. More complex calculations, particularly those usually encountered in a scientific environment require the use of floating point arithmetic with 32 bit wide words. This can also be implemented via software but is very slow and inefficient. It is far preferable to provide such facilities via special high speed hardware.

This hardware now exists in the form of a single L.S.I. component; the AM 9511 produced by ADVANCED MICRO DEVICES<sup>(1)</sup>. This device provides the basic arithmetic operations of Add, Subtract, Multiply and Divide in Fixed Point single and double precision (16/32 bit) and Floating Point single precision (32 bit) formats. It also provides a set of derived functions based on 32 bit floating point format, namely:-

- (i) Trigonometric and inverse trigonomentric functions.

- (ii) Square roots.

- (iii) Logarithms (common, naturel).

- (iv) Exponentiation (e<sup>x</sup>, y<sup>x</sup>).

- (v) Conversions from fixed point to floating point and vice versa.

- (vi) Data Manipulation Instructions.

It has a general purpose bi-directional 8 bit data bus allowing simple interfacing to 8 bit micro-processor systems.

The overall system architecture of a micro-computer employing this device can be considered as that of a distributed system using two asynchronous CPU's operating in parallel. One CPU handles the basic 8 bit orientated problems such as computer/memory organisation, communication (I/O) etc., whilst the other is dedicated to handling the arithmetic operations.

-5-

This architecture makes very efficient usage of the basic component resources. In many micro-computer applications, 32 bit floating point operations are required relatively infrequently. It is therefore uneconomic to have to provide full 16/32 bit architecture with its associated wide address and data paths; far better to use an economical 8 bit architecture with a special purpose processor to handle the arithmetic requirements.

The speed with which the arithmetic operations are executed in a dual processor system is limited by:-

- (i) The basic speed of the arithmetic processor.

- (ii) The number and speed with which the basic arguments can be passed to the arithmetic processor.

The AM 9511 is currently available with a choice of two basic clock speeds, 2 and 4 M.Hz. The execution time for a floating point multiply operation with the 4 M.Hz. device is quoted as  $\sim 40$  µsecs. The speed with which arguments can be passed to the device depends upon the basic speed of the host micro-processor, its memory cycle time and the level of sophistication of its interface to the arithmetic processor. With the AM 9511, the arguments must be transferred in a byte-serial manner. As an example, a 32 bit floating point operation with two input and one output arguments requires the transfer of at least 9 bytes to the device and 4 bytes from the device. With an INTEL SO80A based host using a 2 M.Hz. clock and conventional programmed I/O, these transfer times are of the order 170 µsecs. The transfer time is small compared to the time taken by the AM 9511 to evaluate a trigonometric function, ( $\sim$  2 msec) but long compared to the time taken to perform a single precision floating point add operation (28 -175 µsec).

The full instruction set of the AM 9511 comprises 41 instructions, 32 of which operate on full 32 bit word length variables. This instruction set together with execution times in terms of basic clock cycles can be found in Reference 1.

-5-

#### 2. INTERFACING THE AM 9511 TO AN INTEL 8080A SYSTEM

#### 2.1 The Hardware Interface

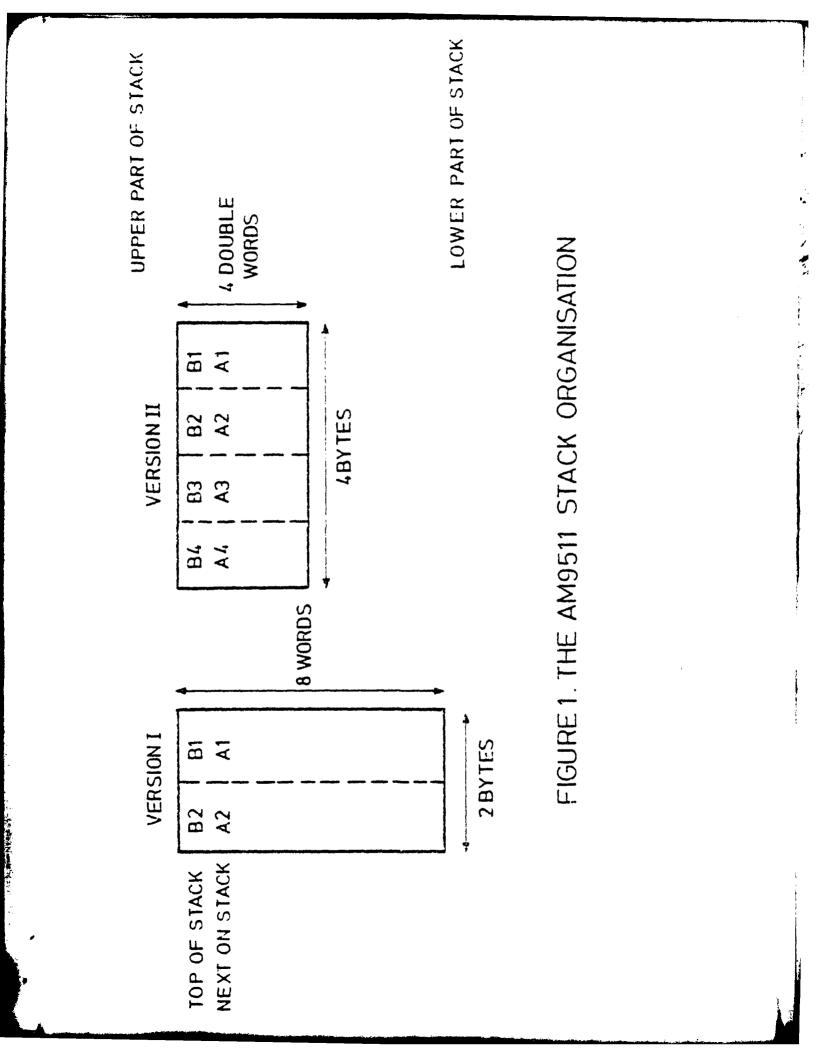

The simplest way to interface the AM 9511 device to an 8080 system is to treat the device as a peripheral I/O component. Conventional programmed I/O can then be used to output arguments, a byte at a time, to the AM 9511. These arguments are input by the AM 9511 and stored on its internal stack. This stack can be either 16 bits wide and 8 levels deep or 32 bits wide and 4 levels deep. Its organisation is illustrated in Figure 1. The entry of each new byte to the stack causes the stack to shift, the previously entered byte being pushed down and the new byte remaining on top of the stack. Single precision integer (16 bit) arguments require two entries to the stack. Double precision integer or real (32 bit) arguments require four entries to the stack.

A command instruction is output to the AM 9511 to initiate the required operation. The AM 9511 has a 'PAUSE' output line which it uses as a busy indicator. This can be used to hold the 8080 CPU in a 'WAIT' state until the AM 9511 is ready with the result of its operation. This result is available on the top of the stack and can be read by the 3030 system by a series of normal I/O read instructions. Special commands enable the stack to be manipulated independently of any arithmetic operation. Memory mapped I/O techniques can be used rather than conventional I/O. With memory mapping, the AM 9511 interface can be considered as analogous to a slow memory.

This simple interface is easy to implement at the hardware level but has the disadvantage that the host CPU is inactive for the duration of the required operation. This could be for a time of the order of milli-seconds for some operations. For some time-critical environments, this dead time may be unacceptable. In such cases it is better to ignore the 'PAUSE' line and to use an alternative signal (END) issued by the AM 9511 device on completion of its operation as an interrupt to the host CPU. The interfacing is slightly more complicated, requiring the use of an interrupt controller, but has the advantage that the host CPU can service other tasks whilst the AM 9511 device is busy. There is a slight penalty in effective execution time with this method due to the overheads of context switching on receipt of the interrupt.

-7-

Another interface method for higher performance systems is to use a Direct Memory Access controller. A simple DMA system provides only a very slight decrease in transfer time for the arguments and unless care is taken can actually worsen the transfer time. This is due to the overheads in DMA systems of the need to pass the address and number of bytes for transfer to the DMA controller. Where only a small number of bytes have to be transferred, this overhead can be significant. The method can be useful in situations where many intermediate results have to be stoled and a very high speed buffer or cache memory is used.

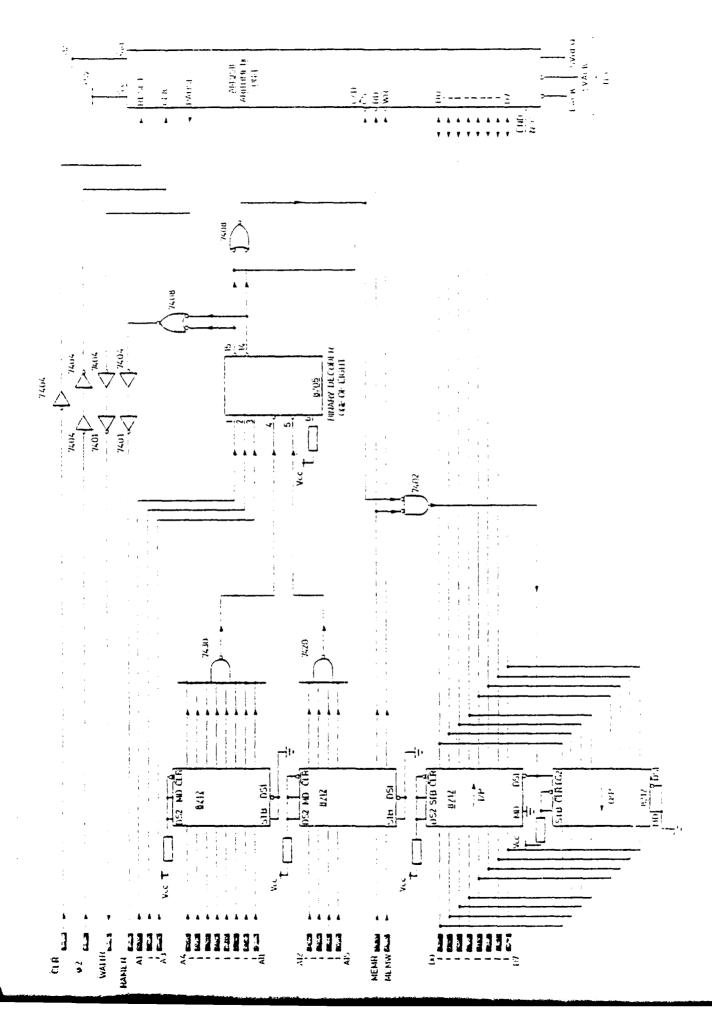

Figure 2 shows a block diagram of a simple programmed or memory mapped I/O interface.

## 2.2 The Software Interface

The function of the software interface is to isolate the programmer from the hardware. It cught not to be necessary for the programmer to have to know details of either AM 9511 device or hardware interface. The software interface can be provided by an extension of the host micro-computer instruction set in the form of additional macro instructions. Assemblers running on local micro-computer development systems can be modified to provide the necessary macro instruction translation. However, a more powerful and flexible approach is to use a Macro Processor written in a high level language and running as a cross product on a large host computer. This Macro Processor can run as a pre-step to a conventional cross assembler or can produce an output file of standard micro-computer instructions for use with local assemblers. The Macro Processor should be modifiable to handle different host micro-computers and different hardware interfacing techniques.

-3-

#### 3. THE M9511 MACRO LANGUAGE

#### 3.1 Basic Definitions and Comments

The syntax of all data sets and hardware files is described according to BNF (Backus Normal Form) production rules<sup>(3)</sup>. The hardware representations of all data sets (<M 9511 data set>) are called files.

#### Survey of all data sets (Software):

<output data set >::= <output data set><output logical record>/

<output logical record>

#### Survey of all corresponding files (Hardware):

<input file> ::= <file>

<output file> ::= <file>

<print file> ::= <file>

<file> ::= <row of closed physical records> <EOF>

<EOF> means "end of file" or equivalent

<row of closed physical records> ::= <row of closed physical records> <closed physical record> <closed physical record>

<closed physical record> ::= <physical record> <IRG>

...

<IRG> means "inter-record gap" or equivalent (new line, new card)

Each <physical record> is a hardware representation of exactly one <input logical record> or <output logical record>

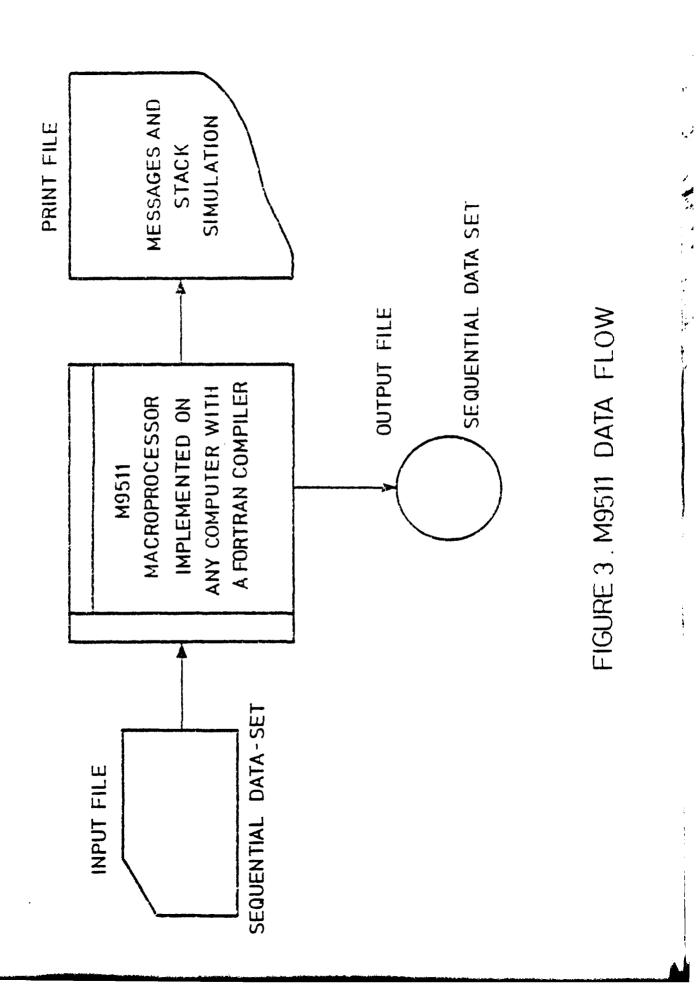

The input file consists of card images. The input text contains 3080 instructions, macroinstructions and comments. All input cards are printed on the printer (print file) together with error or warning messages and description of the content and status of the M 9511 stack. The output file can be realised on any medium that can hold sequential data sets and consists of 3080 assembler instructions in card image format (fig. 3).

#### 3.2 The Mainstream data set

The 3080 assembler instructions differ from the instructions of the AM 9511 (written in macro language M 9511) by the name of the instruction (mnemonics) and by the definition of the parameter subfields.

The general pattern of the statement of both kinds of instructions is as follows:-

where

$$\begin{bmatrix} a \\ b \end{bmatrix}$$

means a or b or nothing

$\begin{cases} a \\ b \end{cases}$  means a or b

$\begin{bmatrix} u \end{bmatrix}$  means nothing or one (or more) blank

$\langle u \rangle$  means one (or more) blank

means "a"

## 3.3 The Input data set

#### 3.3.1 Description of the structure

The input data set consists of 8080 assembler language instructions, 8080 assembler language macro instructions (if any), M 9511 macro instructions and comments (if any).

The M 9511 Macro instructions do not differ syntactically from normal 8080A instructions. The only difference lies in the name of the instruction operation and in the meaning of the parameters. Names that are defined for the M 9511 Macro instruction set must be reserved exclusively for this set and cannot be duplicated for normal 8080A macros.

#### 3.3.2. M 9511 Syntax definition:

The Syntax of input logical records as described by ENF production rules is as follows:-

<input logical record>::= <logical record 3080>|<logical record M>

<logical record 8080>::= <statement 8080><sequence number field>

<logical record M>::= <statement M><sequence number field>

<sequence number field><sup>8</sup>::= <blankety><sequence number>

<seq. of blanks>

<seq. of blanks>::= <seq. of blanks><blank>|<blank> <sequence number>::= <sequence number><digit>|<digit> <digit>::= 0|1|2|3|4|5|6|7|8|9 <blank>::= u <blankety>::= <seq. of blanks>|<empty> <empty>::= <statement 3030> See appendix I

The definition of M 9511 macrolanguage now follows:-

<label>::= <label><letter> <label><digit> <letter>

Only the first five characters in the label are significant.

<letter>::- A|B|C|D|E|F|G|H|I|J|K|L|M|N|O|P|Q|R|S|T|U|V|N|X|Y|J|} <instruction>3;:= <instruction><letter>|<letter></letter>

<comment field>::= <seq. of blanks>|<blankety>;<comment>

3

1 <parameter field>::= <parameter>|<parameter subfield><parameter field>

<parameter subfield>::= <parameter>|<empty>

<parameter>::= <shift>|<register pair>|<variable>

<variable>::= <label>

<register pair>::= 3/D/H

<shift>::= 3

いたちまたのでもあってい

<comment>::= <any char> <comment><any char>

<any char>::= <digit>:<letter> <spec char> <blank>

<spec char>::= + - |\*'/|; :: |, \$ ':(\_)

A restriction is that the single letters S, B, D, H cannot be used as labels since these are defined as register pairs and shifts.

N.B.: Comment on BNF production rules:

The length of the character strings produced by production rules or the number of recursive repetitions is described by these rules:

M means the minimal N and maximal M length of the string N

I means that the length L of the string is mandatory

M<> means the minimal number N and maximal number M of recursive repetitions of the production rule

-12-

#### 3.3.1. <u>M 9511 Semantics</u>:

All M 9511 macro instructions are expanded into the sequences of 8030 assembler instructions in order to provide the required operations.

The meaning of some syntactical symbols is as follows:-

<label> means label

<instruction> corresponds to a specific instruction in the AM 9511

instruction set

<parameter> represents a Direct Address or Indirect Address and/or an AM 9511 Stack Operation

a) Instructions

A full description of M 9511 Macro Instructions is provided in Appendix II. To a large extent the same mnemonics as are used in Reference 1 are repeated in the Macro Instruction set. The following list of instructions however differ:-

| <u>M 9511</u> | AM 9511 (Original Set) |

|---------------|------------------------|

| NOPM }        |                        |

| NOPS          |                        |

| NOPD          | NCP                    |

| NOPF )        |                        |

| DSTM          |                        |

The NOPM instruction is so named as to distinguish it from the INTEL 8080 instruction NOP. The remaining NOP  $(\stackrel{S}{\underline{D}})$  instructions are used to read/write parameters into/out of the AM 9511 stack without performing any operation. The DSTM instruction is used to read the AM 9511 device status information (see Ref. 1). This instruction affacts the 8080 condition bits accordingly.

b) Parameters

Apart from the S parameter that will be described later, the presence of a parameter in the parameter list implies the reading/writing of

-13-

information to the AM 9511 stack. The number of bytes read, written to the stack depends upon the instruction (see Appendix II). The first two parameters refer to the sending of information to the stack and the third parameter refers to reading information from the stack.

The parameters can be specified in four different ways:-

- I. <empty> means that the parameter is not used and any operation relevant to this parameter is not performed.

- 2. <variable> means the 'direct address' of the value that is to be sent/read from the top of the stack.

- 3. <register pair> neans the register pair containing the address of the value that is to be sent/read from the top of the stack.

- 4. <shift> The meaning depends upon the position in the parameter list.

- a) For the first two positions, the stack is shifted down, the TOS (top of stack) being copied to the NOS (next to top of stack). The bottom of the stack is lost.

b) For the third position, the stack is shifted up in circular manner (i.e. rotated).

For both cases a) and b) the number of shifts is determined by the instruction (See Appendix II).

3.4 The Output File

A STATE OF A

#### 3.4.1 Description of Structure

The structure of the <output data set> is the same as that for the <input data set> except that each <logical record M> from the <input data set> is expanded by the M 9511 Macro processor into <logical record M expanded> of the <output data set>. This <logical record M expanded> consists of Intel 3080 assembler instructions only.

The original <logical record M> is added as a comment to the <output data set> before the expansion is performed. A comment containing blanks is added to the end of the <output data set> after the expansion The expansion is described in Appendix III.

-11-

## 3.5 The Print File

#### 3.5.1 Description of Structure

The <print data set> consists of a listing of each instruction from the <input data set>. For M 9511 Macro instructions, the contents of the AM 9511 stack are simulated and printed for each step in the instructions execution. Warning and error messages are added as necessary. Each instruction in the listing is numbered.

The print file is usually printed on the system printer. The records in the file are grouped into numbered pages.

a) The Syntax

<print data is::= <file heading><print data set M><file ending> <print da M>::= <print data set M><printed page><printed page> <printed r New page action><page heading><printed page M> 65 1 <printed page M>::= <printed page M><printed line> <printed line> <printed line>::= <new line action><print record> 130 <print record> ::= <print record><any char> <any char>

b) The Semantic

The <file heading> consists of a title and late

-15-

The <file ending> is a summary of totals for numbers of input, output, print records and various error messages and warnings.

The <page heading> is a page number

The <new page action> and <new line action> are appropriate actions taken by hardware to display new page or new line.

P

The <print record> consists of five types of messages:

- 1. All input logical records are listed step by step, always preceeded by the print record number

- 2. Error messages see 3.5.2

- 3. Error warnings see 3.5.2

- 4. After each M 9511 Macro Instruction, the status of the AM 9511 internal stack is described (four lines) together with warnings concerning any meaningless information on the stack. (This check is only formal) see 3.5.3.

- 5. Blank lines

#### 3.5.2 Error and Warnings

There are 15 possible error/warning messages. Error messages are issued wherever an error occurs during card input and syntax checking (label and parameter fields).

Warning messages are concerned mainly with possible inconsistencies in the state of the AM 9511 internal stack.

Checks and appropriate error messages are also issued concerning error conditions arising through possible but hopefully very rare errors in the basic programme logic.

The number of error/warning conditions arising during the macroprocessors operation is counted and a summary printed at the end of the run. Each error condition has attributed to it an appropriate severity code. The highest severity code arising during the run is issued as an IBM 360 completion code for the 360 job step.

#### 3.5.3 AM 9511 Stack Simulation

It is not obligatory that the results of macro instruction execution be returned to the external memory. Intermediate results can be left in the AM 9511 internal stack ready for use with a subsequent instruction. This technique can be used for program optimisation in situations where speed of execution is critical. However, with this tachnique it is essential that the exact content of the stack be known at all stages of the execution of consecutive instructions. Since certain instructions operate on single precision word lengths (16 bits) whilst others operate on double precision word lengths (32 bits) and since some instructions cause movements of the stack, it can become very difficult to be certain as to the content of the stack at any given stage.

Therefore, for ease of verification and as an aid to optimisation the stack behaviour is simulated by the macro processor. The results of the simulation are displayed as four lines in the print file and appear after the macro instruction itself.

The first line shows the contents of the stack after the input of first parameter, the second line the contents after input of the second parameter, the third line the contents after execution of the macro instruction and the fourth line the contents after output of the third parameter.

The format of each line starts with the work STACK and is followed by four fields separated by 'dot' characters. Each field represents one double word (32 bits) of information on the stack with the 'Top of Stack' to the left. The name appearing in each field is either a parameter name or the name of an instruction, implying the result following the execution of the instruction. For double pracision parameters, the field is left extended with 'x' characters. For single precision parameters, two such parameters occupy one field. A totally blank field or half field in the case of single precision characters implies an undefined stack content.

Warning messages concerning possible inconsistencies are issued as necessary between lines.

-17-

## . THE JROSS-MACROPROCESSOR (TRANSLATOR)

#### -.1 <u>Basic Structure</u>

The translator is composed of three main parts: syntactical analyser, synthesiser of the new structure and code generator. The syntactical analyser evaluates each statement step by step starting with the label followed by the instruction, operands and comment. Internal codes are generated and stored for each field indicating its presence or absence and its type and content.

The synthesiser uses the above codes to establish the basic structure of calls to the code generators. These in turn create groups of Intel 3080 instructions to access parameters and initiate operations.

Any future change in method of interfacing the AM 9511 to the 8080 system can be easily accommodated by changes to the code generators and possibly synthesiser.

#### 4.2 Coding Method

A top down structured programming approach was rigourcusly adhered to at all stages in the coding of the macro processor. This approach enabled both the coding and de-bugging stages to be completed quickly with a minimum of errors being encountered during the work and afterwards when in production. The final programme is also easy to understand and can be modified if necessary with relative ease.

The processor was coded in Fortran which although not being ideal for structured programming methods is nevertheless widely used and understood by the user community for whose use the programme was originally intended. Special sequences of comment statements and 'GO TO' instructions were created to simulate the required structures i.e. SEQUENCE, IF-THEN, .IF-THEN-ELSE, WHILE-DO, REPEAT-UNTIL, LCOP-EXITIF-ENDLOOP, SELECT-CASE.

Each programme module was divided into three parts, declaration, main text and formats. The programme was extensively commented which considerably assists its legibility.

It is intended that the macro processor be used as the first step of a two step job, the second step being a conventional assembler. Step Number 1 (Pre-Processor) produces a file containing conventional SO80 assembler instructions which are then used as input to Step Number 2 (assembler).

#### -13-

## 5. Conclusion

The system as described in the previous sections is operational and in use by the Rutherford Appleton Laboratory Bubble Chamber Group in connection with its micro-computer based film digitising table system. The cross macro-assembler runs on the Group's VAX 11/780 computer, the final object code being loaded into a selected micro-computer via a local communication network.

Some examples illustrating the usage of the macro-assembler and the macro expansions produced are given in Appendix IV.

#### APPENDIX I

The partial description of syntax of \$080 assembler statements as described by BNF production rules is as follows:-<statement 3080><sup>72</sup> ::= <instrcom field>|<label>:<instrcom field>|<label> <instruction \$080 field> <instruction \$080 field> <instruction \$080 field>::= <blankety>;<comment>|<instruction \$080 field> <instruction \$080 field>::= <seq. of blanks><instruction \$080><general \$080 parameter field> <instruction \$080><sup>1</sup>/<sub>1</sub>::= <instruction \$080><letter>|<letter> <general \$080 parameter field>::= <seq. of blanks><3080 parameter field> <\$080 parameter field>!<= <8080 parameter subfield>|<8080 parameter subfield> <8080 parameter field>:<= <8080 parameter field> <\$080 parameter field>. APPENDIX II

.

M9511 Instruction Set

| Instruction<br>Number<br>(M1M) | NAME                 | CODE<br>1234 |                                        | DESCRIPTION                            | r1 014                                                                                                |

|--------------------------------|----------------------|--------------|----------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------|

| 7 m                            | SADD<br>SSUB<br>SMUL | S2SY         | NOS + TOS,<br>NOS - TOS,<br>NOS * TOS, | POP up stack, result to TOS            | All operations are made with version I<br>stack organisation (two bytes times<br>eight) see Figure 1. |

| 4                              | SDIV                 |              | , sot / son                            |                                        | For details see also (1).                                                                             |

| 5<br>6                         | DADD<br>DSUB         | D2DY         | NOS + TOS,<br>NOS - TOS,               |                                        |                                                                                                       |

| ~ *                            | DDIV                 |              | NOS * TOS,<br>NOS / TOS,               | FOF UP STACK, FESULT to 103            | rour) see rigure 1.<br>For details see also (1).                                                      |

| 6                              | FADD                 |              | NOS + TOS,                             |                                        | All operations are made with version 11                                                               |

| 10                             | FSUB                 | F2FY         | NOS – TOS,                             | DAD in the second second second second | stack organisation (four bytes times                                                                  |

| 11                             | FNUL                 |              | NOS * TOS,                             | tot of start least to tot              |                                                                                                       |

| 12                             | FDIV                 |              | NOS / TOS,                             |                                        | For details see also (1).                                                                             |

| 13                             | SQRT                 |              | Aros,                                  |                                        |                                                                                                       |

| 14                             | NIS                  |              | sin(TOS),                              |                                        |                                                                                                       |

| 51                             | C03                  |              | cos(TOS),                              |                                        |                                                                                                       |

| 16                             | TAN                  |              | tg(T0S),                               |                                        |                                                                                                       |

| 17                             | ASIN                 | клга         | arc sin(TOS),                          | Result to TOS                          | Vorsion 11 stack oronoisation                                                                         |

| 18                             | ACOS                 |              | arc cos(TOS),                          |                                        |                                                                                                       |

| 19                             | ATAN                 |              | are tg(TOS),                           |                                        |                                                                                                       |

| 20                             | 1.06                 |              | log(TOS),                              |                                        |                                                                                                       |

| 21                             | NI                   |              | ln(TOS),                               |                                        |                                                                                                       |

| ()<br>()                       | EXP                  |              | exp(TOS),                              |                                        |                                                                                                       |

| 23                             | PWK                  | F2FY         | NOS raised to po                       | o power TOS - for details see (1).     |                                                                                                       |

|                                |                      |              |                                        |                                        |                                                                                                       |

-21-

APPENDIX II (Contd.)

and the second

÷

ļ

| DESCRIPTION                    | no-operation, no transfer of parameters allowed |      | conversion functions |      |      |      | change sign operations |      |      |      | bush show and non-in-on-raritons |       |      |      |             | exchange operations |       | <pre># Lo TOS operation: PUSH down stack, # to TOS (version 11 stack operation)</pre> |      | no-operations with allowed transfer of parameters |      | reading of AM 9511 Device Status, see Appendix 111 section D |

|--------------------------------|-------------------------------------------------|------|----------------------|------|------|------|------------------------|------|------|------|----------------------------------|-------|------|------|-------------|---------------------|-------|---------------------------------------------------------------------------------------|------|---------------------------------------------------|------|--------------------------------------------------------------|

| CODE                           | NUOO                                            | FISY | FUDY                 | SIFY | DIFY | SISY | Yata                   | FlfY | VSUO | YOOD | V400                             | V00SY | VODY | 00FY | <b>VSOO</b> | YUOO                | OOFY  | V-100                                                                                 | S2SY | DZDY                                              | F2FY | γSOO                                                         |

| NAME                           | HAON                                            | FIXS | F I XD               | FLTS | FLTD | CHSS | CHSD                   | CHSF | Pros | PTOD | PTOF                             | P01.5 | GHO  | POPF | XCIIS       | XCHD                | XCIIF | PUPT                                                                                  | SHON | GHON                                              | NOFF | MTSU                                                         |

| Instruction<br>Number<br>(ANM) | 5                                               | 25   | 26                   | .27  | 28   | 29   | 30                     | 31   | 32   | 33   | 34                               | 35    | 36   | 37   | 38          | 39                  | 40    | 1.                                                                                    | 4.2  | 4.3                                               | 44   | 45                                                           |

-22-

## APPENDIX III

#### CODE GENERATORS

These are the sets of 3080 instructions that are used for developing the M 9511 Macro Instructions.

For all cases:

| STACK | EQU | OFFFOH | (Hardware Dependent)  |

|-------|-----|--------|-----------------------|

| CONTR | EQU | CFFF1H | (Hardware Dependenz). |

Code Section A (Sending information to the top of stack)

Al) Parameter is a Label (i.e. Direct Address)

| LDA | 3 + CP   |                |           |

|-----|----------|----------------|-----------|

| STA | STACK    |                |           |

| LDA | 2 + CP   |                | Double    |

| STA | STACK    |                | Precision |

| LDA | 1 + OP } | - 1            | and       |

| STA | STACK    | For single     | Floating  |

| LDA | 0 + 02   | precision only | -         |

| STA | STACK    |                |           |

OP is replaced by actual Label Name.

Sequence takes 104 Clock Cycles (Double P) 52 Clock Cycles (Singe P)

A2) Parameter is a <u>Register Pair</u> (BC, DE)

|                | <b>~</b>                                                  |

|----------------|-----------------------------------------------------------|

| INX            | B or D                                                    |

| DIX            | B or D                                                    |

| INX            | 3 or D                                                    |

| LDAX           | 3 or D                                                    |

| STA            | STACK > precision only Double                             |

| DCX            | B or D Precision                                          |

| LDAX           | B or D and                                                |

| STA            | STACK J Floating                                          |

| DCX            | BorD                                                      |

| LDAX           | 3 or D                                                    |

| STA            | STACK                                                     |

| DCX            | 3 or D                                                    |

| LDAX           | 3 or D                                                    |

| STA            | STACK                                                     |

| Sequence takes | 119 Clock Cycles (Double ?)<br>50 Clock Cycles (Single P) |

-1--

- Implanation of Code:-Column number of code: 1 :- Type of Input Parameter 2 :- Maximum Number of Parameters allowed 3 :- Type of Output Parameter 4 :- Third Parameter Allowed Type of code: S :- Single Precision Integer (16 bit)

- D :- Double Precision Integer (32 bit)

- F :- Floating Point (32 bits)'

- Y :- Yes

- М :- Мо

A3) Parameter is a <u>Register Pair</u> (H, L) Ξ INX Н INX Н INX MOV A, M For single STA STACK precision only Ч DCX Double MOV A. M Precision STA STACK / and Н DCX Floating MOV A, M STA STACK DCX Н MOV A, M STACK STA Sequence takes 110 Clock Cycles (Double F) 50 Clock Cycles (Single P) A4) Parameter is S Single Precision: - ::NI А., 77Н STA CONTR Double Precision: - MVI A , 37H CONTR STA Floating:-MVI Δ , 17H CONTR STA In all cases Sequence takes 20 Clock Cycles Code Section B (Retrieving information from TOS) B1) Parameter is a Label (i.e. Direct Address) LDA STACK STA 0 + OP For single precision only LDA STACK Double STA 1 + OP Precision LDA STACK and STA 2 + CP Floating LDA STACK STA 3 ÷ OP Sequence takes 104 Clock Cycles for Double P 11 11

-25-

| LDA                                                                                     | STACK                                                                                 |                              |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------|

| STAN                                                                                    | 3 07 0                                                                                |                              |

| 73X                                                                                     | S T D                                                                                 | i .                          |

| LDA                                                                                     | STACK                                                                                 |                              |

| STAI                                                                                    | B or D                                                                                | ວິດນຽ <sub>ນ</sub> ຊ         |

| INX                                                                                     | B or D                                                                                | Precisi.                     |

| LDA                                                                                     | STACK                                                                                 | and                          |

| STAX                                                                                    | 3 Jr D                                                                                | Floating                     |

| INX                                                                                     | 3 cr D   For single<br>> precision only                                               | - 1                          |

| LDA                                                                                     | STACK                                                                                 |                              |

| STAX                                                                                    | Burd                                                                                  |                              |

| CCX                                                                                     | Bor D                                                                                 | j                            |

| DCII                                                                                    | 3 or D                                                                                | •<br>•                       |

| DCX                                                                                     | 3 or 0                                                                                | <i>_</i>                     |

|                                                                                         |                                                                                       | ~                            |

|                                                                                         |                                                                                       |                              |

| LDA                                                                                     | STACK                                                                                 | /                            |

| M077                                                                                    | М, А                                                                                  | ,                            |

| MOV<br>INX                                                                              | м, А<br>Н                                                                             | ,                            |

| MOV<br>INX<br>LDA                                                                       | M, A<br>H<br>STACK                                                                    | Double                       |

| MOV<br>INK<br>LDA<br>MOV                                                                | M, A<br>H<br>STACK<br>M, A                                                            |                              |

| MOV<br>INX<br>LDA<br>MOV<br>INX                                                         | M, A<br>H<br>STACK<br>M, A<br>H                                                       | Precision<br>and             |

| MOV<br>INX<br>LDA<br>MOV<br>INX<br>LDA                                                  | M, A<br>H<br>STACK<br>M, A<br>H<br>STACK                                              | Precision                    |

| MOV<br>INX<br>LDA<br>MOV<br>INX<br>LDA<br>MOV                                           | M, A<br>H<br>STACK<br>M, A<br>H<br>STACK<br>M, A                                      | Precision<br>and             |

| MOV<br>INX<br>LDA<br>MOV<br>INX<br>LDA<br>MOV<br>INX                                    | M, A<br>H<br>STACK<br>M, A<br>H<br>STACK<br>M, A<br>H                                 | Precision<br>and             |

| MOV<br>LNK<br>LDA<br>MOV<br>LNK<br>LDA<br>MOV<br>LNM<br>LDA                             | M, A<br>H<br>STACK<br>M, A<br>H<br>STACK<br>For single<br>precision only              | Precision<br>and             |

| MOV<br>INX<br>LDA<br>MOV<br>INX<br>LDA<br>MOV<br>INM<br>LDA<br>MOV                      | M, A<br>H<br>STACK<br>M, A<br>H<br>STACK<br>M, A<br>For single<br>precision only      | Precision<br>and             |

| MOV<br>INK<br>LDA<br>MOV<br>INK<br>LDA<br>MOV<br>INM<br>LDA<br>MOV<br>DCX               | M, A<br>H<br>STACK<br>M, A<br>H<br>STACK<br>M, A<br>H<br>STACK<br>M, A<br>H           | Precision<br>and             |

| MOV<br>INX<br>LDA<br>MOV<br>INX<br>LDA<br>MOV<br>INM<br>LDA<br>MOV<br>DCX<br>DCX        | M, A<br>H<br>STACK<br>M, A<br>H<br>STACK<br>M, A<br>H<br>STACK<br>M, A<br>H<br>H<br>H | Precision<br>and             |

| MOV<br>INK<br>LDA<br>MOV<br>INK<br>LDA<br>MOV<br>INM<br>LDA<br>MOV<br>DCX               | M, A<br>H<br>STACK<br>M, A<br>H<br>STACK<br>M, A<br>H<br>STACK<br>M, A<br>H           | Precision<br>and             |

| MOV<br>LNX<br>LDA<br>MOV<br>DNX<br>LDA<br>MOV<br>INM<br>LDA<br>MOV<br>DCX<br>DCX<br>DCX | M, A<br>H<br>STACK<br>M, A<br>H<br>STACK<br>M, A<br>H<br>STACK<br>M, A<br>H<br>H<br>H | Pracision<br>and<br>Floating |

227 Parameter 1s a Register Pair (BC, DE

•

3-) Parametar is S

| Single Precision:- | MIT | A, 73H |

|--------------------|-----|--------|

|                    | STA | CONTR  |

| Double Precision:- | MVI | A, 38H |

|                    | STA | CONTR  |

| Floating:-         | MVI | A, 13H |

|                    | STA | CONTR  |

In all cases sequence takes 20 Clock Cycles

Code Section C (Sending Instruction into AM 9511)

MVI A. INSTR

STA CONTR

INSTR EQU Binary Code of AM 9511 instruction as defined in Command Summary (Ref. 1)

Sequence takes 20 Clock Cycles to send Instruction to AM 9511

N.3. Number of Clock Cycles required for AM 9511 to execute given instruction can be found in Ref. 1.

Code Section D (Reading AM 9511 Device Status)

LDA CONTR RAL JC 3-4 IRI 40HCCCH ANI LDA CONTR RAL DITL 5+4 CMC RAL JNC \$+4 CMC RAL JNC 3+4 CMC RAR RAR RAR RAR

and the second second

-27-

Sequence takes at least 114 Clock Cycles. More synthes may be required of device is busy when request is made.

r

لم و

This sequence corresponds to the Macro Instruction  $\text{DSTM}_{2}$  for a Code Figure from Status Register is transferred to Bits (0-4) of the SOSGA Accumulatic. Sign, Zero and Carry replace the corresponding SOSOA Flags.

SOSCA Parity Flag is not affected.

1.1.1.1.1.1

The above code sections are assembled together according to the M-9511 macro instruction in the following order:-

- 1. Code relevant to first parameter (if any) is selected from Group A.

- 2. Code relevant to second parameter (if any) follows and is also selected from Group A.

- 3. Code for instruction execution follows and is Group C code.

- 4. Code relevant to third parameter (if any) follows and is selected from Group B.

## APPENDIX IV

#### EXAMPLES

- A. Parameter Usage

- 1. Binary Functions

| з) |      | FADD | AM, ALI, VT                    |

|----|------|------|--------------------------------|

|    | AM:  | DS   | +; floating point number (2.3) |

|    | ALI: | DS   | 4; floating point number (3.0) |

|    | VT:  | DS   | 4; floating point result (5.0) |

Whenever an external address is specified for the third parameter the result is copied from the TOS to the external address and the stack is popped up circular (the result of operation is now on the bottom of the stack.

•

| 5) | LHLD        | AM           |   |                                                |

|----|-------------|--------------|---|------------------------------------------------|

|    | MOV         | 3, Н         | ; | Address of AM in BC                            |

|    | MOV         | C, L         |   |                                                |

|    | LHLD        | ALI          |   |                                                |

|    | NCHG        |              | ; | Address of ALI in DE                           |

|    | FADD        | B, D, 3      | ; | Result back in AM                              |

|    |             |              |   |                                                |

|    |             |              |   |                                                |

| c) | LHLD        | ΨW           |   |                                                |

| c) | LHLD<br>MOV |              | ; | Address of AM in BC                            |

| c) |             |              | ; | Address of AM in BC                            |

| c) | MON         | В, Н<br>С, L |   | Address of AM in BC<br>Result stays in the TCS |

| c) | MOV<br>MOV  | В, Н<br>С, L |   |                                                |

, AM, VT

These instructions add floating point number expected in TOS to floating point number stored at AM. The results is sent to location address TT. Both these instructions produce the same result.

é) FADD ,,VT

FADD

This instruction adds floating point number expected in TOS to floating point number expected in NOS. The result is sent to location address VT. E) FADD

This instruction adds floating point number expected in TOS to floating point number expected in NOS. The result stays in the TOS.

.

2) FADD AM, S, VT

This instruction first sends the floating point number expected as a content of AM to TOS. The second parameter(S) causes the stack to be pushed down whilst leaving the original TOS intact. The instruction then adds TOS and NOS the result being placed first in TOS and then sent to VT.

The above result could be obtained in a lass efficient manner by using the following instruction: FADD AM, AM, VT.

h) FADD S,, VT

The expected floating point number in TOS is doubled.

FADD S, SFADD ,, VT

The expected floating point number in TOS is tripled and sent to VT. This example emphasises the importance of understanding the stack behaviour.

2. Unary Functions

SIN AM,, VT sinus of AM is sent to VT

but: SIN AM, ALI, VT

is flagged as an error 009 and parameter ALI is not used and sinus of AM is sent to VT SIN ,, VT sinus of TOS is sent to VT SIN

sinus of TOS replaces TOS

-00-

1

3. Functions that do not require any input parameters

PUPI ,, VT

T is sent to VT

PUPI

T is in TOS

PUPI ,, S

T is in bottom of the stack

## E Part Program Example

Given a triangular coordinate system with fixed base length b. To convert to Cartesian coordinates x, y

Triangular Coordinates are  $r_1$ ,  $r_2$  (Integer 4 bytes each)

Basic Flow Chart

. Salari

134 M

A:

Transform

$$r_1/r_2$$

to Floating Point Format

4

3:

$a_1 = 0.0050 * (r_1 - 9216.0) + Cx$

$a_2 = 0.0050 * (r_2 - 25600.0) + Cy$

C:

$a_2 = 0.0050 * (r_2 - 25600.0) + Cy$

$r_1 = (a_1^2 - a_2^2 + b_2^2)/(2*a_1*b)$

$r_2 = 1 - n^2$

C:

$x = 25.0 - a_1*r_1$

$y = a_1*n$

$y = a_1*n$

-32-

Program Section: ---

|      | CR1:        | CS   | 4         | ; | r. Coora               | inate       | (Tr:  | iangi      | :la <del>r</del> - |

|------|-------------|------|-----------|---|------------------------|-------------|-------|------------|--------------------|

|      | CR2:        | DS   | 4         | ; | τ. "                   |             |       |            |                    |

|      | CX:         | DS   | 4         | ; | Cx                     | <b>71</b> . | Pt 3  | - <b>r</b> | 17,                |

|      | CY:         | DS   | <u> </u>  | ; | Cy                     | 1 11        |       | 1          | ,                  |

|      | CX1:        | DS   | ۱.        | ; | 9216.0                 | "           | "     | 11         | ý                  |

|      | C%2:        | SC   | <u>′</u>  | ; | 25600.0                | 2 <b>H</b>  | ••    | ••         | Ś                  |

|      | CPAD:       | DS   | 4         | • | 0.005                  | ( ''        | *1    | ••         | ì                  |

|      | CB:         | DS   | 4         | ; | b=137.45               |             | **    |            | ý                  |

|      | CETA:       | DS   | <u>∕.</u> | ; | η                      | ( "         | ••    | 11         | ÿ                  |

|      | CGAM:       | DS   | -         | ; | γ                      | -           |       |            | ,                  |

|      | CDVA:       | DS   | ÷         | ; | 25.0                   | ( ''        |       | 18         | )                  |

|      | CONE:       | DS   | 4         | ; | 1.0                    | `"          | **    | ••         | )                  |

|      | CTND:       | DS   | 4         | ; | 2.0                    | ( 11        |       | ۰.         | )                  |

|      | CAl:        | LS   | 4         | : | a                      | ·           |       |            | /                  |

|      | CA2:        | DS   | ,<br>÷    | ; | a2                     |             |       |            |                    |

|      | X:          | DS   | 4         | ; | x Coordin              | ate (       | Cart  | esia       | n)                 |

|      | Y:          | DS   | 4         | ; | у "                    |             |       |            | ,                  |

|      | :           |      |           |   | ,                      |             |       |            |                    |

| Inst | <u>No</u> ; |      |           |   |                        |             |       |            |                    |

| 1.   | START:      | FLTD | CRI       | ; | r <sub>1</sub>         |             |       |            |                    |

| 2.   |             | FSUB | CX1       | ; | $r_1 = 9216$           | .0          |       |            |                    |

| 3.   |             | FMUL | CPAD      | ; | 0.0050*(r              |             | 216.0 | ))         |                    |

| 4.   |             | FADD | CK,, CAI  | : | aj                     | •           |       |            |                    |

| 5.   |             | FLTD | CR2       | ; | =                      |             |       |            |                    |

| 6.   |             | FSUB | CK2       | ; | r <sub>2</sub> - 25600 | 0.0         |       |            |                    |

| 7.   |             | FMUL | CPAD      | ; | C.3050*(r              |             | 5600. | 3)         |                    |

| 8    | •           |      |           |   |                        |             |       | - /        |                    |

2. 3. 4. 5. 6. 7. 8. CY,, CA2 ; FADD  $a_2$ 9. aĵ CAl, S FMUL ; 10. FMUL CA2, S a<sup>2</sup> a<sup>2</sup> b<sup>2</sup> ; 11. FSUB ; 12. FMUL C3, S ; 13.  $a_1^2 - a_2^2 - b_2^2$ FADD ; 14.  $(a_1^2 - a_2^2 + b^2)/2.0$ FDIV CTWO ; 15.  $(a_1^2 - a_2^2 + b^2)/(2.0 + a_1)$ FDIV CAI ; 15. FDIV CB,, CETA ; ٦ 17. NOPF CDVA, CONE ;

## Program Section (Contd.)

NAME OF A

| 19. FSUB ; 1 - 7 <sup>2</sup> |

|-------------------------------|

| 20. FMUL CA1 ; $a_1*\gamma$   |

| 21. FSU3 ,,.: ; X             |

| 22. FMUL CETA, CAL, Y ; Y     |

| Inst.<br>No.                              |         | TOS          | NCS          | 305        |

|-------------------------------------------|---------|--------------|--------------|------------|

|                                           | STACK:  | XXXXXX CR1   |              |            |

| !                                         | STACK:  | XXXXXX CR1   |              |            |

| 1                                         | STACK:  | XICCXX FLTD  |              |            |

| :                                         | STACK:  | MAXXXX FLID  |              | i          |

| 2. ;                                      | STACK:  | KANKA CK1    | XIXXX FLTD   | 1          |

| N. A. | STACK : | XXXXXX CK1   | XXXXX FLTD   |            |

| 1                                         | STACK:  | XXXXXX FSUB  | 1            |            |

|                                           | STACK:  | MMMMM FSUB   |              |            |

| 3.                                        | STACK:  | XICIXI: CPAD | maxia FSUB   |            |

| 1                                         | STACK:  | XXXXX CPAD   | KKKKK FSUB   |            |

|                                           | STACK:  | XXXXXX FMUL  |              |            |

|                                           | STACK : | XXXXX FMUL   |              |            |

| 4.                                        | STACK:  | xxxxxx CX    | KXXXX FMUL   |            |

|                                           | STACK:  | XXXXXX CX    | KICKICK FMUL |            |

|                                           | STACK:  | maaka FADD   | 1            |            |

| 1                                         | STACK:  |              | · · ·        | XXXXXX CA1 |

| 5.                                        | STACK:  | xxxxxx CR2   |              |            |

| 5                                         | STACK:  | XXXXXX CR2   |              |            |

|                                           | STACK:  | xxxxx FLTD   | :            |            |

|                                           | STACK:  | XXXXX FLTD   | f.<br>A      |            |

| 5.                                        | STACK:  | CCCCXX CX2   | XICCCC FLTD  |            |

|                                           | STACK:  | KRIIXX CK2   | XXXXX FLTD   |            |

|                                           | STACK:  | KKKICK FSUB  |              |            |

|                                           | STACK:  | KRAKKA FSUB  | t .          | •          |

| 7.                                        | STACK:  | XXXXXX CPAD  | XXXXX FSUB   |            |

|                                           | STACK:  | XXXXX CPAD   | XXXXX FSUB   | i          |

|                                           | STACK:  | XXXXXX FMUL  |              | i i        |

|                                           | STACK:  | xxxxxx FMUL  |              |            |

| з.                                        | STACK:  | XXXXX CY     | XXXXX FMUL   |            |

|                                           | STACK:  | XXXXXX CY    | XXXXXX FMUL  |            |

|                                           | STACK:  | KITKICK FADD |              |            |

|                                           | STACX:  |              |              | XXXXXX CA2 |

| ġ.                                        | STACK:  | XXXXXX CA1   |              |            |

|                                           | STACK:  | TXXXX CA1    | XXXXXX CA1   |            |

|                                           | STACK:  | XXXXX FMJL   |              |            |

|                                           | STACX:  | XXXXX FMUL   |              |            |

|                                           |         |              |              |            |

Stack Simulation (for Part Program above)

| Stack                                                                                                           | Simulat | ion | (Contd.) |

|-----------------------------------------------------------------------------------------------------------------|---------|-----|----------|

| in the second |         |     |          |

| Inst.<br>No. |        | TOS            | NOS           |              | ECS             |

|--------------|--------|----------------|---------------|--------------|-----------------|

| 10.          | STACK: | XXXXX CA2      | XXXXX FMUL    |              |                 |

|              | STACK: | ихних СА2      | XXXXXXX CA2   | XXXXXX FMUL  |                 |

|              | STACK: | XICXXX FMUL    | HOCK FMUL     |              |                 |

|              | STACK: | ICXICIA FMUL   | XXXXX FMUL    |              |                 |

| 11.          | STACK: | XXXXX FMUL     | XXXXX FMUL    |              |                 |

|              | STACK: | XXXXXX FMUL    | XIGGAX FMUL   |              |                 |

|              | STACK: | XXXXX FSUB     |               |              |                 |

|              | STACK: | XXXXXX FSUB    |               |              |                 |

| 12.          | STACK: | XXXXX CB       | XXXXXX FSU3   |              | •<br> <br> <br> |

|              | STACK: | REPERT CB      | KENERIK CB    | XXXXXX FSUB  | •               |

|              | STACK: | XXXXXX FMUL    | XXXXX FSUB    |              | 1               |

|              | STACK: | MARKIN FMUL    | XXXXX FSUB    |              |                 |

| 13.          | STACK: | KRAXER FMUL    | XIXXXX FSUB   |              | -<br>           |

|              | STACK: | KANNA FMUL     | xicixx FSUB   |              |                 |

|              | STACK: | ITAXICA FADD   |               |              | :<br>1          |

|              | STACK: | XXXXXX FADD    |               |              |                 |

| 14.          | STACK: | KICKICK CTWO   | MINICIC FADD  | 8<br>1<br>1  | :               |

|              | STACK: | XXXXXX CTWO    | MXXXXX FADD   | 1<br>1<br>1  |                 |

|              | STACK: | incide FDIV    |               |              | :               |

|              | STACX: | XXXXX FDIV     |               |              | 1               |

| 15.          | STACK: | ZXXXX CAL      | KKOCK FDIV    |              | i               |

|              | STACK: | MICKER CAL     | xxxxxx FDIV   |              | •               |

|              | STACK: | xxxxx FDIV     |               |              |                 |

|              | STACK: | XXXXX FDIV     |               |              |                 |

| 16.          | STACX: | xicact CB      | NEWSCH FDIV   |              |                 |

|              | STACK: | xxxxxx C3      | KKKKK FDIV    |              |                 |

|              | STACK: | KICKICK FDIV   | 1             | 1            |                 |

|              | STACK: | !              |               | 1<br>•       | · XXXXXX CETA   |

| 17.          | STACK: | RECEIC CDVA    |               |              |                 |

|              | STACK: | ICHICACIA CONE | XICIA CDVA    |              |                 |

|              | STACK: | XXXXXX CONE    | RECEIVER CDVA |              |                 |

|              | STACK: | XXXXXX CONE    | RECENCE CDVA  | 1            |                 |

| 13.          | STACK: | XXXXXX CETA    | XXXXXX CONE   | NUXXXX CDVA  |                 |

|              | STACK: | XXXXXX CETA    | XXXXXX CETA   | MITAXIA CONE | XXXXXX CDVA     |

|              | STACK: | XXICCR FMUL    | XXXXXX CONE   | XXXXXX CDVA  |                 |

|              | STACK: | XXXXX FMUL     | XXIIXX CONE   | XXXXXX CDVA  |                 |

|              |        | :              |               |              |                 |

|              | L      |                |               | 1            | :               |

| Inst.<br>No. |        | TOS           | NOS         |               | BCS      |

|--------------|--------|---------------|-------------|---------------|----------|

| 19.          | STACK: | taciani FMUL  | XIXXX CONE  | KIKICKIK CDVA | ÷        |

|              | STACK: | xxxxxxx FMUL  | XXXXXX CONE | XXXXXX CDVA   | 1        |

|              | STACK: | www.sec. FSUB | XXXXXX CDVA |               | 1        |

|              | STACK: | XXXXX FSUB    | XXXXXX CDVA |               |          |

| 20.          | STACK: | XXXXX CA1     | MAXIA FSUB  | XXXXXII CDVA  |          |

|              | STACK: | XXXXXX CA1    | XXXXXX FSUB | XXXXXX CDVA   | :<br>•   |

|              | STACK: | XXXXXX FMUL   | MARICA CDVA |               | i        |

|              | STACK: | XXXXXX FMUL   | XXXXXX CDVA |               | !        |

| <u> 1</u> 1. | STACK: | XMXXXX FMUL   | XXXXXX CDVA |               | ;        |

|              | STACK: | XXXXXX FMUL   | XXXXX CDVA  | 1             |          |

|              | STACK: | RECEICE FSUB  |             |               |          |

|              | STACK: |               |             |               | XXXXX X  |

| 22.          | STACK: | KITICKK CETA  |             |               |          |

|              | STACK: | XXXXXX CA1    | XXXXXX CETA |               |          |

|              | STACK: | XXXXXX FMUL   |             |               |          |

|              | STACK: | 1             | ]           |               | xxxxx: Y |

Stack Simulation (Contd.)

Appendix V.

Using the M9511 Macro Processor on the Bubble Chamber Groups VAX 11/780 computer.

\_^-\_

INTEL 8080 source code is assembled on the Bubble Chamber Groups VAX 11/780 computer using a cross assembler written in ECPL code.

As this cross assembler is a CPU intensive process then access to it is via a BATCH job running in the SYS\$ASSEA batch queue.

This appendix describes the action of the batch job and how the M9511 Macro Processor is used, along with the commands needed to execute the job.

## (A) BATCH JOB.

The batch job has seven input parameters (P1 to P7) which control the flow of the job. They are as follows:-

| P1 | Input file name      | (If type is .ADD then P1 becomes a concatenation file containing a list of input files) |  |  |

|----|----------------------|-----------------------------------------------------------------------------------------|--|--|

| P2 | Output file name     | (4-character name of program)                                                           |  |  |

| P3 | Default directory    | (directory where P1 exists)                                                             |  |  |

| P4 | Username             | (Used by job to keep user informed of its progress)                                     |  |  |

| P5 | Title                | (String of characters)                                                                  |  |  |

| P6 | Cross reference flag | (YES/NO)                                                                                |  |  |

| P7 | M9511 flag           | (YES/NO)                                                                                |  |  |

The flow of execution through the batch job is as follows -1) Check parameters. 2) Run pre-processor where, P1 Input file name Output file name WORK: P2. TEM 3) If P7 is "YES" then run M9511 Macro Processor where, WORK: P2 . TEM; n (n is Input file name vers no.) WORK: P2. TEM; n+1 Cutput file name WORK: AM9511.LIS List file name 4) Run Cross assembler. where, WORK: P2 . TEM Input file name GO.DAT Output file name WORK . P2. LIS List file name If Program name (P2) is "NULL" then terminate 5) 6) Run Loader. where, GO DAT Input file name SYS\$EXE: [AP04]P2.LCD Output file name

#### (B) BATCH JOB EXECUTION

The batch job is executed by means of one of the following commands:-

1) ASSEM Run cross assembler 2) ASSFP Run cross assembler with M9511 macro processor

Both commands will prompt for the following set of parameters -

File name Program name (4 chars) Title Cross reference (YES/NO)

The only difference between the two commands is the value of 27 which is passed to the batch job, i.e.:-

ASSEM P7 = NO ASSFP P7 = YES

The value of P7 is automatically set up by the respective command.

## ACKNOWLEDGEDENTS

The authors acknowledge the help provided by P. Made of the Track Analysis Maintenance Section in the construction of the hardware. Dr. Jires also thanks Dr. Stafford and the Science Research Council for the hospitality provided by Rutherford Laboratory and Dr. Kalmus for the opportunity to work on this project. e i

.4

## BEFERENCES:

(1) AM 9511 Arithmetic Processing Unit Advanced Micro Devices, 901 Thompson Place, Sunnyvale, Milfornia 170344.  $r^{*}$

• •

1

/

- Rutherford Laboratory Report RL-82-019: Bubble Chamber Research Broun Microcomputer Unit, R Bairctow, J Barlow, P R Made, P Seller, M Waters, J G Watson.

- (3) J W Backus: The syntax and semantics of the proposed international algebraic language of the Zurich ACM-GAMM conference, ICIP Paris June 1907.

- (4) INTEL 8080/8085 Assembly LanguageProgramming Manual 98-940.

FIGHER 2: A SIMPLE REPORT MOLERA BARDWARE BALRENE

\*

The state of the second