MICROCOPY RESOLUTION TEST CHART NATIONAL BUREAU OF STANDARDS 1963-A

.

HD\_E 500 608

ELÉCTE

JAN 2 4 1984

E

84 01 23 032 KM Lag No. HQ 83-25681

## IDA RECORD DOCUMENT D-39

# ELECTRONIC PACKAGING AND INTERCONNECT TECHNOLOGY WORKING GROUP REPORT

(IDA/OSD R&M STUDY)

Richard J. Clark General Electric Company Working Group Chairman

### August 1983

The views expressed within this decument are these of the working group only. Publication of this document does not indicate endersement by IDA, its staff, or its sponsoring agencies.

Prepared for Office of the Under Secretary of Defense for Research and Engineering and

> Office of the Assistant Secretary of Defense (Manpower, Reserve Affairs and Logistics)

INSTITUTE FOR DEFENSE ANALYSES SCIENCE AND TECHNOLOGY DIVISION

6

$\mathbf{c}$

3

00 74

A

B

THE FILE COPY

ide document has been approved to public releans and sules its withouten is unlimited. The work reported in this decument was conducted under contract MDA 903 79 C 9018 for the Department of Defense. The publication of this IDA Record Document does not indicate endorsement by the Department of Defense, nor should the contents be construed as reflecting the official position of that agency.

3.9

W. Ale

3

0

5

C

0

.

2

Approved for public release; distribution unlimited.

Ŧ

UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE (Then Date Entered)

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| T. REPORT NUMBER 2. GOVT ACCESSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NO. 3. RECIPIENT'S CATALOG NUMBER                                                                                                            |

| AN-H137.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 336                                                                                                                                          |

| 4. TITLE (and Subtitio)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S. TYPE OF REPORT & PERIOD COVERED                                                                                                           |

| Electronic Packaging and Interconnect Tech-                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                              |

| nology Warking Group Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | July 1982 - August 1983                                                                                                                      |

| (IDA/OSD REM Study)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6. PERFORMING ORG. REPORT NUMBER<br>IDA Record Document D-39                                                                                 |

| 7. AUTHOR(a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8. CONTRACT OR GRANT NUMBER(+)                                                                                                               |

| Richard J. Clark, General Electric Company                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              |

| Working Group Chairman                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MDA 903 79 C 0018                                                                                                                            |

| . PERFORMING ORGANIZATION NAME AND ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10. PROGRAM ELEMENT, PROJECT, TASK                                                                                                           |

| Institute for Defense Analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

| 1801 N. Beauregard Street                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Task T-2-126                                                                                                                                 |

| Alexandria, VA 22311                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                              |

| 11. CONTROLLING OFFICE NAME AND ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12. REPORT DATE                                                                                                                              |

| Office of the Assistant Secretary of Defense                                                                                                                                                                                                                                                                                                                                                                                                                                                              | August 1983                                                                                                                                  |

| (MRASL), The Pentagon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13. NUMBER OF PAGES                                                                                                                          |

| Washington, D.C. 20301                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 103                                                                                                                                          |

| 14. MONITORING AGENCY NAME & ADDRESS(II dillorent from Controlling Office<br>DOD-IDA Management Office                                                                                                                                                                                                                                                                                                                                                                                                    | e) 15. SECURITY CLASS. (of this report)                                                                                                      |

| 1801 N. Beauregard Street                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | UNCLASSIFIED                                                                                                                                 |

| Alexandria, VA 22311                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 154. DECLASSIFICATION/DOWNGRADING<br>SCHEDULE<br>N/A                                                                                         |

| 16. DISTRIBUTION STATEMENT (of this Report)                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u></u>                                                                                                                                      |

| 17 DISTRIBUTION STATEMENT (of the sharrant entered in Black 20. If differen                                                                                                                                                                                                                                                                                                                                                                                                                               | ( from Report)                                                                                                                               |

| 17. DISTRIBUTION STATEMENT (of the obstract entered in Black 20, if differen                                                                                                                                                                                                                                                                                                                                                                                                                              | t from Report)                                                                                                                               |

| 17. DISTRIBUTION STATEMENT (of the obstract entered in Black 20, if differen                                                                                                                                                                                                                                                                                                                                                                                                                              | t from Report)                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t from Report)                                                                                                                               |

| None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t from Report)                                                                                                                               |

| None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t from Report)                                                                                                                               |

| None<br>18. Supplementary notes<br>N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

| None<br>16. SUPPLEMENTARY HOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block man<br>electronic packaging, component interconnectic                                                                                                                                                                                                                                                                                                                                | (***)<br>DN, reliability, maintainabilit                                                                                                     |

| None<br>16. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block num<br>electronic packaging, component interconnection<br>readiness, Very High Speed Integrated Ciruit                                                                                                                                                                                                                                                                               | ••••)<br>DN, reliability, maintainabilit                                                                                                     |

| None<br>16. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse elds if necessary and identify by block num<br>electronic packaging, component interconnectic                                                                                                                                                                                                                                                                                                                                | ••••)<br>DN, reliability, maintainabilit                                                                                                     |

| None<br>16. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block num<br>electronic packaging, component interconnection<br>readiness, Very High Speed Integrated Ciruit                                                                                                                                                                                                                                                                               | ••••)<br>DN, reliability, maintainabilit                                                                                                     |

| None<br>16. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Centinue on reverse elde if necessary and identify by block man<br>electronic packaging, component interconnection<br>readiness, Very High Speed Integrated Ciruit<br>Integration (VLSI), cabling and connectors                                                                                                                                                                                                                                 | ber)<br>on, reliability, maintainabilit<br>(VHSIC), Very Large Scale                                                                         |

| None<br>16. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block num<br>electronic packaging, component interconnection<br>readiness, Very High Speed Integrated Ciruit<br>Integration (VISI), cabling and connectors<br>18. AESTRACT (Continue on reverse olds if necessary and identify by block numbers                                                                                                                                            | <sup>bor)</sup><br>on, reliability, maintainabilit<br>(VHSIC), Very Large Scale                                                              |

| None<br>16. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Continue on reverse side if necessary and identify by block num<br>electronic packaging, component interconnection<br>readiness, Very High Speed Integrated Ciruit<br>Integration (VLSI), cabling and connectors<br>10. AESTRACT (Continue on reverse olds if necessary and identify by block numb<br>This document records the activities and                                                                                                   | bor)<br>on, reliability, maintainabilit<br>(VHSIC), Very Large Scale                                                                         |

| None<br>None<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A                                                                                                                                                                                                                                                                                                                                                                                                                                      | <pre>ber) on, reliability, maintainabilit (VHSIC), Very Large Scale presents the findings of the ogy Working Group part of the</pre>         |

| None<br>16. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Centinue on reverse side II necessary and Identify by block man<br>electronic packaging, component interconnection<br>readiness, Very High Speed Integrated Ciruit<br>Integration (VISI), cabling and connectors<br>10. ABSTRACT (Centum on reverse side II restorery and Identify by block man<br>This document records the activities and<br>Electronic Packaging and Interconnect Technolo<br>IDA/OSD Reliability and Maintainability Study   | <pre>bon, reliability, maintainabilit<br/>(VHSIC), Very Large Scale<br/>presents the findings of the<br/>ogy Working Group part of the</pre> |

| None<br>18. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Centinue on reverse side if necessary and identify by block man<br>electronic packaging, component interconnection<br>readiness, Very High Speed Integrated Ciruit<br>Integration (VLSI), cabling and connectors<br>18. ABSTRACT (Centinue on centres side if secretary and identify by block man<br>This document records the activities and<br>Electronic Packaging and Interconnect Technolo                                                  | <pre>bon, reliability, maintainabilit<br/>(VHSIC), Very Large Scale<br/>presents the findings of the<br/>ogy Working Group part of the</pre> |

| None<br>16. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Cantinue on reverse side II necessary and Identify by block man<br>electronic packaging, component interconnection<br>readiness, Very High Speed Integrated Ciruit<br>Integration (VISI), cabling and connectors<br>10. ABSTRACT (Continue on reverse side II sectorery and Identify by block man<br>This document records the activities and<br>Electronic Packaging and Interconnect Technolo<br>IDA/OSD Reliability and Maintainability Study | <pre>bon, reliability, maintainabilit<br/>(VHSIC), Very Large Scale<br/>presents the findings of the<br/>ogy Working Group part of the</pre> |

| None<br>None<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A                                                                                                                                                                                                                                                                                                                                                                                                                                      | <pre>ber) on, reliability, maintainabilit (VHSIC), Very Large Scale presents the findings of the ogy Working Group part of the</pre>         |

| None<br>None<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A                                                                                                                                                                                                                                                                                                                                                                                                                                      | (VHSIC), Very Large Scale<br>presents the findings of the<br>ogy Working Group part of the<br>, conducted during the period                  |

| None<br>16. SUPPLEMENTARY NOTES<br>N/A<br>19. KEY WORDS (Cantinue on reverse side II necessary and Identify by block man<br>electronic packaging, component interconnection<br>readiness, Very High Speed Integrated Ciruit<br>Integration (VISI), cabling and connectors<br>10. ABSTRACT (Continue on reverse side II sectorery and Identify by block man<br>This document records the activities and<br>Electronic Packaging and Interconnect Technolo<br>IDA/OSD Reliability and Maintainability Study | <pre>ber) on, reliability, maintainabilit (VHSIC), Very Large Scale presents the findings of the ogy Working Group part of the</pre>         |

### **IDA RECORD DOCUMENT D-39**

# ELECTRONIC PACKAGING AND INTERCONNECT TECHNOLOGY WORKING GROUP REPORT

(IDA/OSD R&M STUDY)

Richard J. Clark General Electric Company Working Group Chairman

August 1983

| Acces       | ssion For    |    |  |

|-------------|--------------|----|--|

| NTIS        | GRA&I        |    |  |

| DTIC        | TAB          | 1  |  |

| Unanı       | nounced      |    |  |

| Just        | ification    |    |  |

| By<br>Disti | ribution/    |    |  |

|             | ····         |    |  |

| Ava         | llability Co |    |  |

|             | Avail and/   | or |  |

| Dist        | Special      |    |  |

|             |              |    |  |

| 1 1 1       |              |    |  |

| A^1         |              |    |  |

INSTITUTE FOR DEFENSE ANALYSES SCIENCE AND TECHNOLOGY DIVISION 1801 N. Beauregard Street, Alexandria, Virginia 22311 Contract MDA 903 79 C 0018 Task T-2-126

# RELIABILITY AND MAINTAINABILITY STUDY

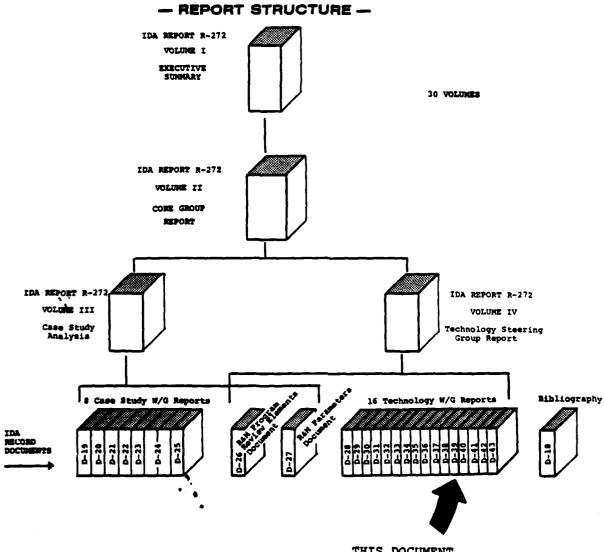

THIS DOCUMENT (IDA Record Document D-39) . . . . . .

#### PREFACE

As a result of the 1981 Defense Science Board Summer Study on Operational Readiness, Task Order T-2-126 was generated to look at potential steps toward improving the Material Readiness Posture of DoD (Short Title: R&M Study). This task order was structured to address the improvement of R&M and readiness through innovative program structuring and applications of new and advancing technology. Volume I summarizes the total study activity. Volume II integrates analysis relative to Volume III, program structuring aspects, and Volume IV, new and advancing technology aspects.

1

The objective of this study as defined by the task order is:

"Identify and provide support for high payoff actions which the DoD can take to improve the military system design, development and support process so as to provide quantum improvement in R&M and readiness through innovative uses of advancing technology and program structure."

The scope of this study as defined by the task order is:

To (1) identify high-payoff areas where the DoD could improve current system design, development program structure and system support policies, with the objective of enhancing peacetime availability of major weapons systems and the potential to make a rapid transition to high wartime activity rates, to sustain such rates and to do so with the most economical use of scarce resources possible, (2) assess the impact of advancing technology on the recommended approaches and guidelines, and (3) evaluate the potential and recommend strategies that might result in quantum increases in R&M or readiness through innovative uses of advancing technology.

P-1

The approach taken for the study was focused on producing meaningful <u>implementable</u> recommendations substantiated by quantitative data with implementation plans and vehicles to be provided where practical. To accomplish this, emphasis was placed upon the elucidation and integration of the expert knowledge and experience of engineers, developers, managers, testers and users involved with the complete acquisition cycle of weapons systems programs as well as upon supporting analysis. A search was conducted through major industrial companies, a director was selected and the following general plan was adopted.

### General Study Plan

| Vol. | III | • | Select, analyze and review existing successful program                                        |

|------|-----|---|-----------------------------------------------------------------------------------------------|

| Vol. | IV  | ٠ | Analyze and review related new and advanced technology                                        |

| Vol. | II  |   | Analyze and integrate review results<br>Develop, coordinate and refine new concepts           |

| Vol. | I   | ٠ | Present new concepts to DoD with implementa-<br>tion plan and recommendations for application |

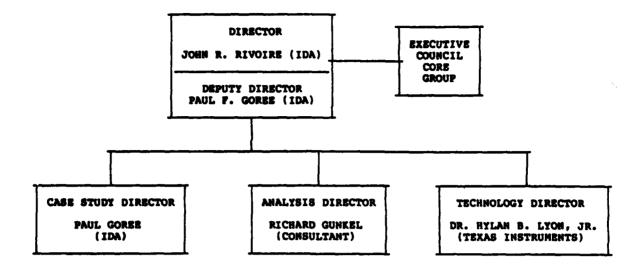

The approach to implementing the plan was based on an executive council core group for organization, analysis, integration and continuity; making extensive use of working groups, heavy military and industry involvement and participation, and coordination and refinement through joint industry/service analysis and review. Overall study organization is shown in Fig. P-1.

The basic technology study approach was to build a foundation for analysis and to analyze areas of technology to surface: technology available today which might be applied more broadly; technology which requires demonstration to finalize and reduce risk; and technology which requires action today to provide reliable and maintainable systems in the future. Program structuring implications were also considered. Tools used to accomplish

P-2

ð.

X

i -

έ.

FIGURE P-1. Study Organization

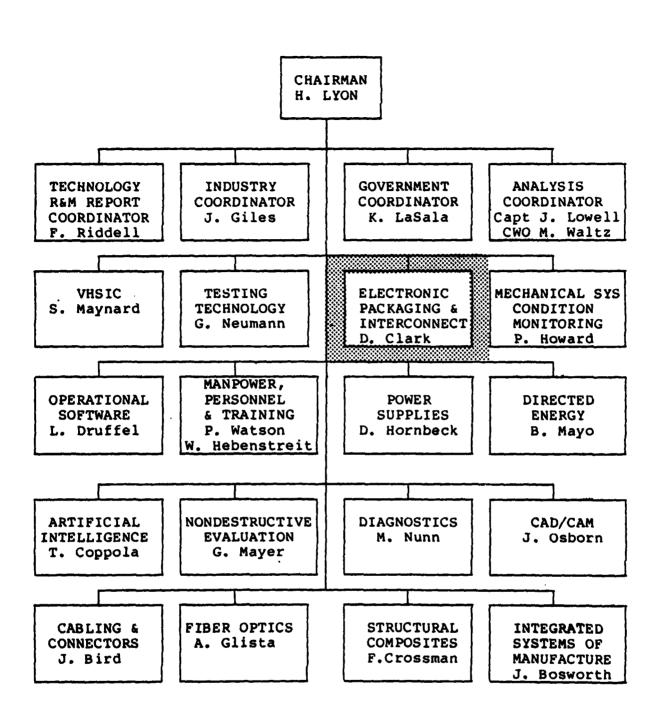

this were existing documents, reports and study efforts such as the Militarily Critical Technologies List. To accomplish the technology studies, sixteen working groups were formed and the organization shown in Fig. P-2 was established.

This document records the activities and findings of the Technology Working Group for the specific technology as indicated in Fig. P-2. The views expressed within this document are those of the working group only. Publication of this document does not indicate endorsement by IDA, its staff, or its sponsoring agencies.

Without the detailed efforts, energies, patience and candidness of those intimately involved in the technologies studied, this technology study effort would not have been possible within the time and resources available.

FIGURE P-2. Technology Study Organization

121/23-1

P-4

### R&M STUDY

### EPIC STUDY GROUP REPORT

### ELECTRONIC PACKAGING AND INTERCONNECTION

FINAL REPORT

May 11, 1983

| Study | Group | Members | - | R. | J.  | Clark - | Chairman |

|-------|-------|---------|---|----|-----|---------|----------|

|       |       |         |   | E. | Bla | ackburn |          |

|       |       |         |   | J. | Cie | ccio    |          |

|       |       |         |   | s. | Kor | nsowski |          |

|       |       |         |   | s. | Liı | nder    |          |

|       |       |         |   | D. | Mc  | Kee     |          |

|       |       |         |   | I. | Pra | att     |          |

|       |       |         |   | J. | Pro | okop    |          |

|       |       |         |   | Μ. | Rol | bbins   |          |

|       |       |         |   | R. | Ung | ger     |          |

|       |       |         |   | D. | Zir | nmerman |          |

58/1-1

8

8

£

i

The views expressed herein are those of the working group only. Publication of this document does not indicate endorsement by IDA, its staff, or its sponsoring agencies. ~,

58/2-1

#### EXECUTIVE SUMMARY

The purpose of the Electronic Packaging and Interconnection of Components Study was to identify potential improvements in Reliability and Maintainability and Readiness through the use of improved electronic packaging technology, and to recommend specific management policies and key technology development programs to accomplish the insertion of these technologies into military systems in the most effective and timely way.

Electronic Packaging for the purpose of this study is defined as the essential mechanical product design functions required to implement the electronic design into the final hardware assembly. Included are the following levels of packaging: chip, package, hybrids, printed wiring board, backplane, system interconnections and environmental control systems.

The primary packaging area with the greatest impact on system R&M is interconnections. These occur at all levels of packaging and have been shown to contribute to the greatest number of system failures in the field.

The interconnection design goal of the future should be to put more functionality or circuits on the silicon chips and thereby significantly reduce the numbers of interconnections at the higher packaging levels. This will result in a corresponding increase in circuit and system reliability due to two factors: (1) the chip level interconnections have proved to be the most reliable, (2) the higher levels of interconnections, which are less reliable, will be reduced in number as the system volume shrinks and numbers of connectors and cables between functional units are reduced.

The quantum improvements in R&M will only be attainable if the system architecture design programs at the basic chip levels include the essential packaging and interconnection parameters which will become part of the final system design. These must be

58/1-2

iii

integrated into an overall CAD program for circuit partitioning, layout and interconnection.

The continued increase in IC device functionality by reduced feature size on the new VLSI chips will make available chip area which can be used for on-chip test and fault location circuits. Some emphasis is required in this area so that the required R&M improvements can be accomplished.

The retooling of our electronic manufacturing facilities will be required to make use of the latest automated processing, assembly and test equipment. These will improve the product producibility by reducing throughput time, improving yields and lowering cost. Incentives are therefore needed to encourage rapid introduction of these equipments into our production facilities.

An integral thread throughout the study has been the interrelationships which exist between major technology areas such as VLSI/VHSIC, CAD/CAM, Packaging, and Cabling and Connectors. An integrated approach to solving these individual requirements is essential to successful implementation of the following recommendations.

- DoD should fund a new task to broaden the VHSIC Integrated Design Automation program to include the determination, during the system architecture design and partitioning, of that mechanical design which best relates to the optimum VHSIC/VLSI chip design to ensure optimum packaging.

- DoD should initiate additional incentive programs to encourage factory modernization including upgrading of existing manufacturing facilities to

58/1-3

include necessary automated production and inspection facilities to ensure that the predicted improvements in R&M are achieved.

- 3. The DoD must upgrade existing military test documents (e.g., MIL-STD-883) to accommodate the new technologies introduced by the VLSI/VHSIC systems. A study should be funded to revise the existing standards by including new or improved tests which have a significant impact on system R&M.

- 4. A DoD study should be funded to determine the real distribution of failures in electronic equipment, including a means of collating and filing failure data with sufficient detail to pinpoint the causes for electronic system failures including the IC chip or any other part of the associated packaging and interconnection levels.

- 5. It is recommended that a combined government and industry study be initiated to establish strategic military requirements in the electronic ceramic technology area. It is recommended that this be done in close cooperation with the VHSIC Program Office.

- 6. Future DoD contracts should include procurement incentives for the total Life Cycle Cost of the system being procured as opposed to singling out performance, initial cost, and MTBF. For long procurement production contracts, incentives should be made for the contractor to improve the reliability and maintainability of the system while a major portion of the production systems are yet to be built.

58/1-4

₹ ₹ ٤.

- 7. Establish a DoD focal point to coordinate and integrate the government packaging and interconnection programs with the cooperative commercial technology research and development ventures to ensure maximum synergistic benefits. The task force should include representatives of major commercial ventures such as microelectronics and Computer Technology Corporation (MCC), the Semiconductor Research Cooperative (SRC), military service, other government and industry members. The task force should provide guidance in the application of specific DoD packaging and interconnection design, development and implementation programs to facilitate VHSIC/VLSI technology insertion into selected DoD systems.

- 8. DOD should fund an effort to promote maximum interfacing and communication between government and industry by having a DoD task force recommend military packaging standards, outlines and configurations to an established standards committee and by having the military services further contribute to package standardization by increased participation and coordination with industry standards groups or committees, such as JEDEC, and by having military equipment designers make concerted efforts to include the packaging standards into new system designs.

58/1-5

#### R&M STUDY

### ELECTRONIC PACKAGING AND INTERCONNECTION

### EPIC STUDY OF COMPONENTS (EPIC) REPORT OUTLINE

| EXECUTIVE SUMMARY              |                                                                                                                                                                                                                                                                                                                                                                                   | iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCOPE                          |                                                                                                                                                                                                                                                                                                                                                                                   | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ELECTRONIC PACKAGIN            | IG STATE-OF-THE-ART                                                                                                                                                                                                                                                                                                                                                               | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TECHNICAL/MANAGEMEN            | IT ISSUES                                                                                                                                                                                                                                                                                                                                                                         | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| B. Commercial/Gove             |                                                                                                                                                                                                                                                                                                                                                                                   | 3-1<br>3-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1. Commercial<br>2. Government |                                                                                                                                                                                                                                                                                                                                                                                   | 3-10<br>3-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                | l                                                                                                                                                                                                                                                                                                                                                                                 | 3-14<br>3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                | .062                                                                                                                                                                                                                                                                                                                                                                              | 3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                |                                                                                                                                                                                                                                                                                                                                                                                   | 3-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RECOMMENDED ACTION             | ITEMS                                                                                                                                                                                                                                                                                                                                                                             | 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| APPENDIX ABibliog              | raphy                                                                                                                                                                                                                                                                                                                                                                             | A-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                |                                                                                                                                                                                                                                                                                                                                                                                   | B-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Lev                            | el Reliability/Availability                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                | SCOPE<br>ELECTRONIC PACKAGIN<br>TECHNICAL/MANAGEMEN<br>A. Technology Impa<br>B. Commercial/Gove<br>Synergism<br>1. Commercial<br>2. Government<br>C. Standardization<br>D. Manufacturing<br>E. Critical Resour<br>F. Testing Methods<br>RECOMMENDED ACTION<br>APPENDIX ABibliog<br>APPENDIX BBack-Up<br>1. Pac<br>2. Imp<br>VHS<br>Lev<br>3. The<br>Coo<br>4. Cos<br>con<br>5. An | SCOPE<br>ELECTRONIC PACKAGING STATE-OF-THE-ART<br>TECHNICAL/MANAGEMENT ISSUES<br>A. Technology Impact<br>B. Commercial/Government Technology<br>Synergism<br>1. Commercial<br>2. Government<br>C. Standardization<br>D. Manufacturing<br>E. Critical Resources<br>F. Testing Methods<br>RECOMMENDED ACTION ITEMS<br>APPENDIX ABibliography<br>APPENDIX BBack-Up Material:<br>1. Packaging Programs<br>2. Impact of the Insertion of<br>VHSIC Technology on System<br>Level Reliability/Availability<br>3. The VLSI Connection in Two New<br>Cooperative Research Programs<br>4. Cost Modeling Across Inter-<br>connection Levels |

58/1-6

44

11

4

41

Í

ſ

vii

#### I, SCOPE

The purpose of the Electronic Packaging and Interconnection of Components Study was to identify potential improvements in R&M and Readiness through the use of improved electronic packaging technology and to recommend specific management policies and key technology development programs to accomplish the insertion of these technologies into military systems in the most effective and timely way.

The basic electronic packaging areas considered are shown in Table 1.

Section II of the Study details the present state-of-theart in electronic packaging and identifies the various critical packaging technologies. Also identified are the interfaces with the other functional areas that will require careful integration for optimized results.

Section III of the report defines the technical/management issues which impact the use of new packaging technology to improve system R&M, and provides a comprehensive listing of present and planned government-sponsored packaging programs including VHSIC R&D, VHSIC M&T, other R&D and M&T programs and planned commercially-sponsored programs such as the Microelectronic and Computer Technology Corporation packaging program.

Section IV makes specific recommendations in each of the identified areas.

Appendix A provides a bibliography of related technical reports, articles and studies which provide the necessary technical backup for the study recommendations. Appendix B consists of some of this backup material.

58/1-7

K

17

#### Table 1. ELECTRONIC PACKAGING SCOPE

1. Device Interconnection and Assembly

2. Packages

Single Chip Multi-chip

- 3. Hybrid Packaging

- 4. Printed Wiring Board/Substate Interconnect (2nd level)

- 5. Backplane Interconnect (3rd level)

- 6. Connectors and Cabling

- 7. Environmental Protection

- 8. Thermal Management

- 9. Cabinets and Structures

- 10. Microwave Packaging

- 11. Packaging Interfaces

- 1. Architecture/Partitioning

- 2. VHSIC/VLSI

- 3. CAD/CAM

- 4. Testing

- 5. Cabling and Connectors

58/1-8

#### II. ELECTRONIC PACKAGING STATE-OF-THE-ART

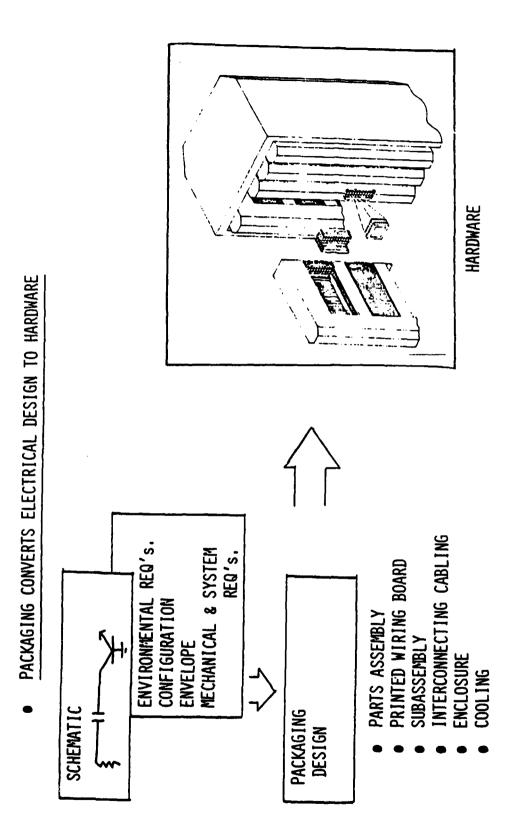

Electronic packaging can be thought of as the "glue" that holds a system together and allows it to properly function. It is the effort necessary to translate electrical, mechanical and environmental requirements into hardware. This is illustrated in Figure 1.

As an effort it is distinct in that it has only just recently begun to emerge as a separate discipline in the field of engineering. It is in fact, a marriage of the established disciplines of mechanical engineering, electrical engineering, manufacturing, materials engineering, device physics and process engineering. It is exactly this required blend of skills that has characterized electrical packaging through the years as more of an art than a science. This general lack of understanding and support of this complex subject has resulted in little generic progress in the field over the last twenty odd years or so.

To be sure, there have been some very clever solutions to systems packaging problems over the years, both in the commercial and military arenas. However, close examination shows these to be very application oriented and difficult to transport from one system to another.

Pieces and part of these specific solutions can be shown to be somewhat generic in nature. These are items such as:

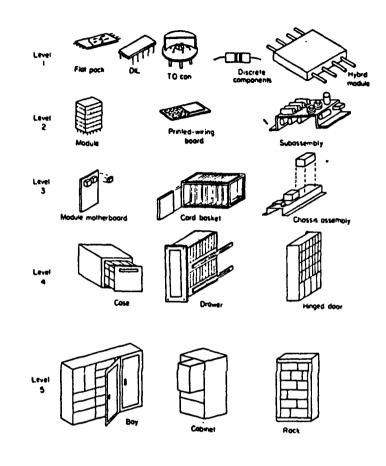

First level interconnect packages such as the dual in-line (DIP) flat-pack and chip carrier. (The phrase "first level interconnect" is associated with electronic components. It can be thought of as the wire bonds that connect an integrated circuit (IC) to the package that houses and protects the IC). Some of these packages are truly generic in that they are industry standards.

58/1-9

÷.

( ]

RJC 9/3/81

- Second level interconnect structures such as multi-layer printed wiring boards (PWB's), double-sided PWB's and microstrip PWB's. These items are generic in the sense that the materials, processes, and techniques associted with their design, manufacturing, testing, and usage are well understood throughout the industry, to the point that they are "standard" items.

- Hybrid microcircuit packaging techniques lie somewhere between the two areas just mentioned. A hybrid microcircuit uses an insulating substrate on which is deposited thick or thin film circuit elements such as conductors, resistors, capacitors, and inductors, and to which is mounted active and passive devices in chip form and which is housed in a package which protects the completed circuit from the surrounding environment and provides a means for interconnecting it to surrounding circuitry. Like a PWB, a hybrid has a conductor pattern incorporated in it, but it is more like a first level interconnect structure in that it uses techniques such as wire bonding to interconnect its active elements to the substrate and it is typically being used as a packaged component on a printed wiring board.

- Third level interconnects can be thought of as those which are used to interconnect printed wiring boards within a Line Replaceable Unit (LRU). Accepted third level interconnect techniques include wiring harnesses, flex

58/1-10

X

circuitry, wirewrap and multi-layer motherboards. There are other techniques as well, but by far, wiring harnesses and motherboards are the most popular ones. Motherboards are gaining in popularity due to their economy and the ease in which they can accommodate controlled impedance circuit paths.

- Level four interconnect techniques are those used typically to interface motherboard assemblies with other elements comprising the LRU and to the LRU's external connectors. Common techniques used are wiring harnesses, cables and flex circuits. Fiber optic techniques are becoming useful in certain specific instances.

- The fifth level of packaging refers to those techniques used to interconnect the various LRU's to each other and to other platform systems. Wiring harnesses, cables and fiber optics techniques are again typically used here. The five levels of electronic packaging are illustrated in Figure 2.

- Connectors and thermal management techniques are other elements of electronic packaging that deserve some mention here. Connectors have evolved over the years into several different commonly used groups of different types styled for particular applications. There are PWB connectors, rack and panel connectors, gas tight connectors, etc. Military

58/1-11

ţ

8

ŝ

Ķ

Ľ

2-5

specifications have played an important role in determining the types of connectors used today.

In like manner, military specifications have guided the evolvement of thermal management techniques. The taboo in the use of direct air impingement for cooling has caused designers to use conduction cooling from the edges of PWB's via card guides nto a "cold wall" through which cooling air flows. In so-called high power situations, thermal planes which cover the front or back of a PWB are used to augment heat conduction into the cold wall. These techniques have been, for the most part, very satisfactory to this point in time.

What does all of this have to do with the reliability and maintainability (R&M) of today's/tomorrow's military electronic systems? Since the execution of electronic packaging tasks is what converts a system design into hardware, what is accomplished during this phase will have a significant impact on a system's ultimate reliability and maintainability.

Recent data indicates that less than two percent of all avionics failures involve IC components. Approximately sixty percent of all avionics failures can be attributed to higher level components (connectors and cabling). Another twenty-five percent were caused by maintenance and test procedures. The remaining failures fell into the category of overstress and abuse of system components. Figure 3 summarizes these failures.

What does this data imply with regard to packaging's effect on system R&M? Given the fact that it is quite easy to reach sweeping conclusions from such limited data, it is quite obvious

58/1-12

| Failure Type                                                                                                                       | Fail        | Failures (%) |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|--|--|

| rallure lype                                                                                                                       | Avionics    | Aircraft     |  |  |

| Cabling (B <sub>n</sub> )                                                                                                          | 60.0        | 33.0         |  |  |

| Maintenance (C <sub>n</sub> )                                                                                                      | 24.8        | 13.6         |  |  |

| Abuse (D <sub>n</sub> )                                                                                                            | 11.4        | 6.3          |  |  |

| Non-IC (E <sub>n</sub> )                                                                                                           | 1.9         | _1.05_       |  |  |

| Total                                                                                                                              | <u>98.1</u> | 53.95        |  |  |

| Adding IC failures (F)<br>(chip involvement)<br>Total avionics failures<br>Adding non-avionics failures<br>Total aircraft failures | <u> </u>    | <u> </u>     |  |  |

FIGURE 3. Avionics and Aircraft Failure Sources

58/1-13

E.

Ľ.

5

ſC.

ł.

مو د ا

bL.

Ċ

L

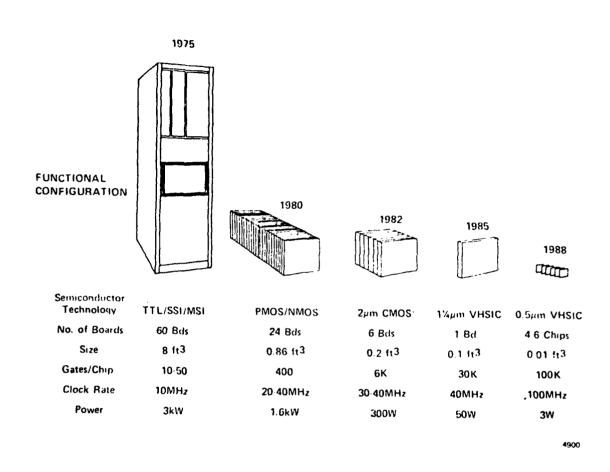

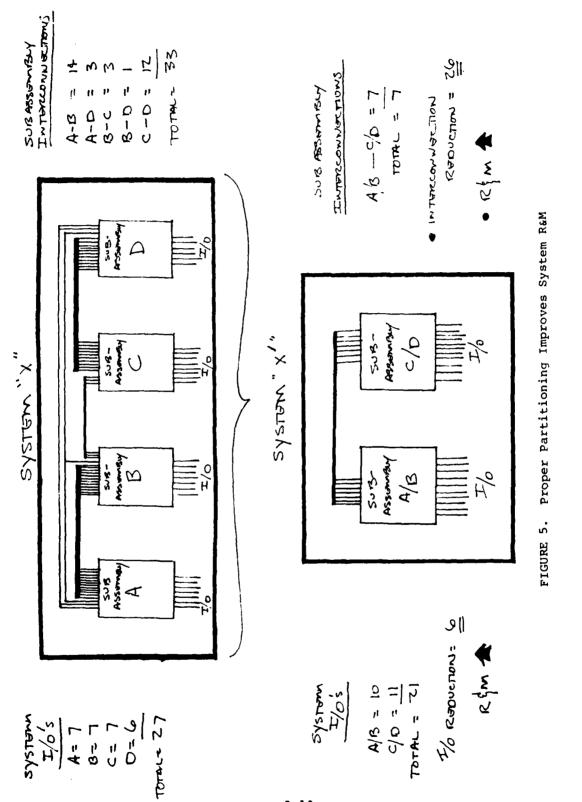

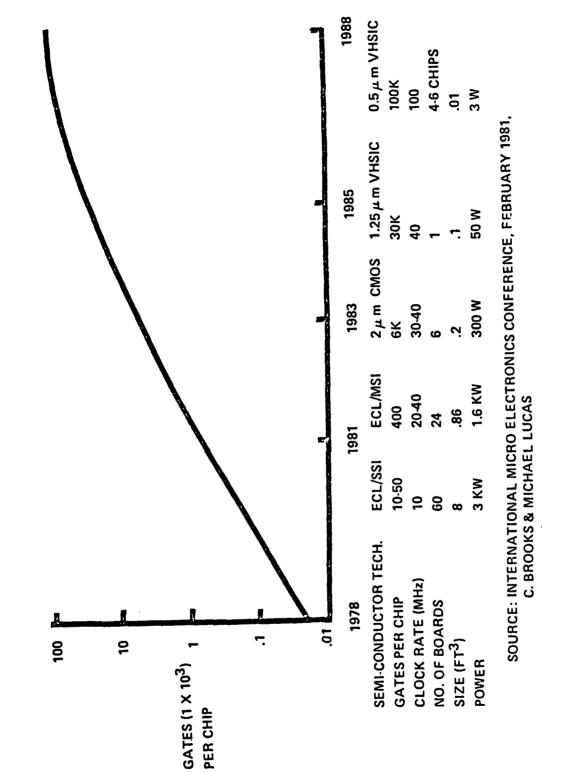

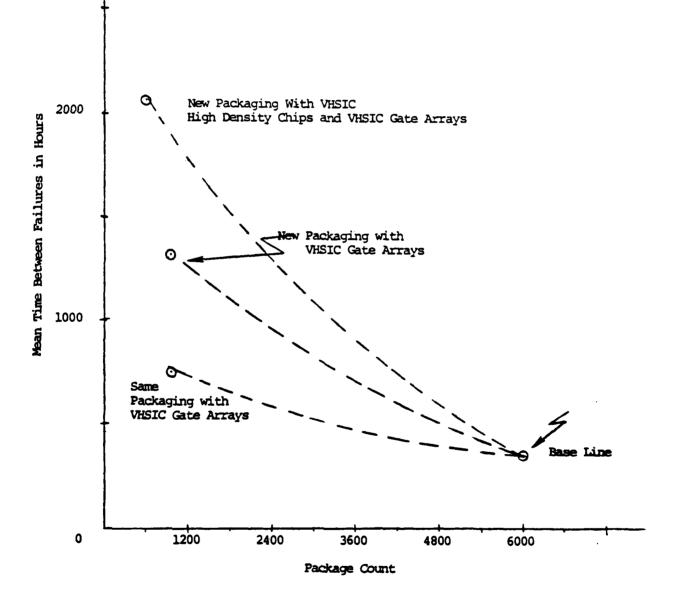

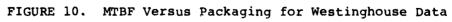

that the existing state-of-the-art of level three, four and five electronic packaging is not optimum with regard to system R&M. The large number of wires, cables, connectors, and contacts per connector appears to be at the root of this problem. If this is the case, then a thrust to reduce the numbers of wires, etc., would tend to lower the failure numbers we see today. Higher levels of integration, optimized system partitioning, data buss usage and fiber optics would tend to produce the desired results, however they bring along problems of their own. The first illustration in Fig. 4 shows that the wires, cables, connectors, etc. required in a 1975 vintage system can virtually all be replaced with the advent of the 1988 VHSIC based system, thus significantly reducing the number of failures associated with these items. Figure 5 is an illustration of the potential effect of system partitioning with an eye toward R&M. In the original system, there are a total of sixty level three and four interconnections. The illustration shows that the bulk of the level three interconnections exist between subassemblies A&B and C&D. By repackaging the system to combine the A and B functions and the C and D functions, a total of 32 interconnections are eliminated with a positive implication for system R&M.

#### SUMMARY

It can be concluded from the above that much can be done to improve the existing packaging state-of-the-art with regard to the reliability and maintainability of military electronic systems. Today's integrated circuits are typically much more reliable than the system's electronic packaging that surrounds them. The trend toward higher levels of integration, currently being augmented by the VHSIC program, is a positive one in that it allows more interconnects to be made at level one, the most reliable and least susceptible to damage of all levels of packaging. One must be

58/1-14

2-8

11

\$

ţ

1

R

FIGURE 4. Integration Levels Reduce System Size, Complexity, Power and Interconnects

•

1 1 1

careful though to use proper system partitioning to make the most of the potential benefits of higher levels of integration.

System cooling techniques of today are reaching the limits of adequacy for dense systems. Newer packaging techniques such as chip carriers will tend to increase system power densities. The higher integration level of VHSIC/VLSI will offset this problem somewhat, but cooling techniques that exist today will not be adequate for tomorrow's denser systems.

Existing PWB materials will be adequate for the near term, but will become less and less adequate as clock speeds climb to and exceed 100 MHz.

Connectors that are common today will follow a like pattern. Pin counts, designs, and insulating dielectrics will suffice for some time, but will prove to be inappropriate with very quick rise times and high speed times.

58/1-15

1.

#### III. TECHNOLOGY/MANAGEMENT ISSUES

#### A. TECHNOLOGY IMPACT

The primary impact of packaging new electronic technology on R&M is in the quantity and type and location of interconnections.

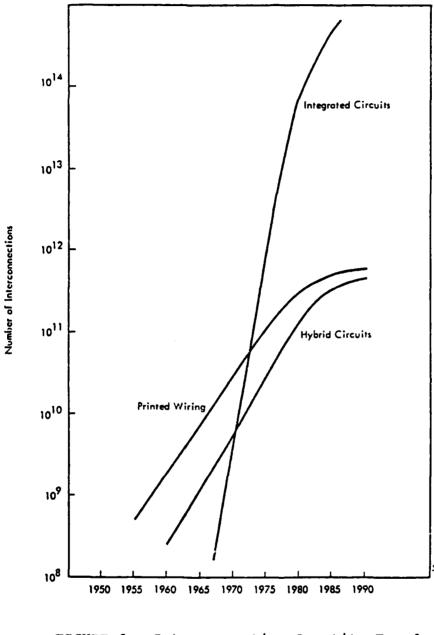

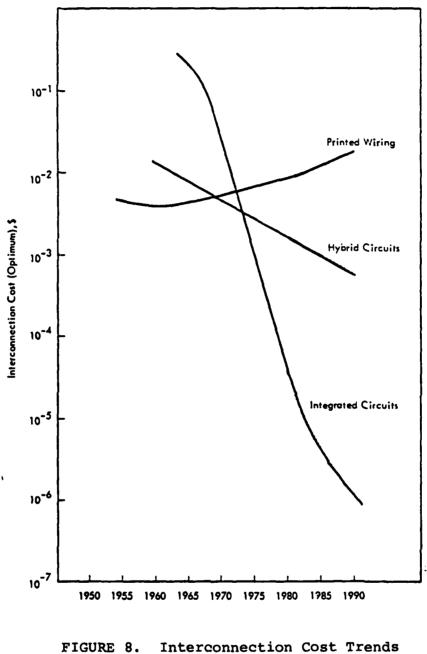

Interconnections in present systems are essentially evenly distributed between the IC level and the PWB level (Fig. 6). Since only about 2% of the system interconnection failures occur at the device level, the vast majority of failures occur at the higher level of system packaging, i.e., printed wiring boards (PWB) backplanes and system and subsystem cabling and connector systems (Fig. 7)(Ref. 1).

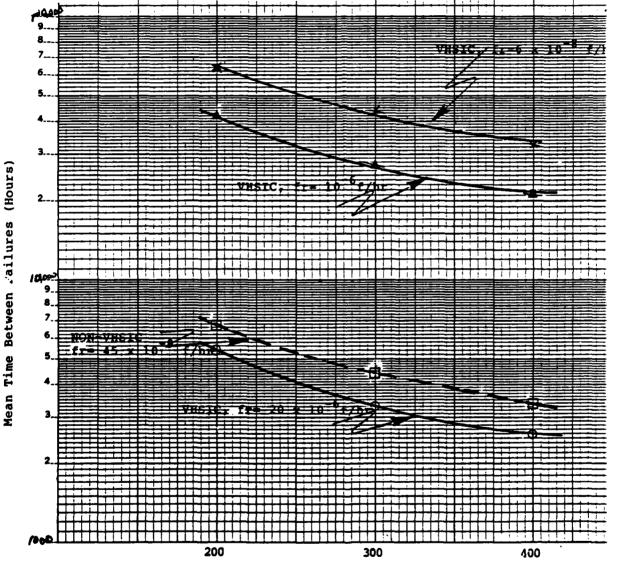

A convenient way to measure interconnection effectiveness is to use the modeling technique proposed by Dr. John Salzer, Salzer Technology Enterprises, in which he uses an interconnection reduction ratio, IRR to characterize the effectiveness of an interconnection method (Ref. 4).