Ň

MICROCOPY RESOLUTION TEST CHART NATIONAL BUREAU OF STANDARDS-1963-A

CRL-0789

GaAs FET LOGIC AT LOW TEMPERATURES

Texas Instruments Incorporated Central Research Laboratories 13500 North Central Laboratories Dallas, Texas 75265

27 July 1983

Final Report for Period 1 September 1979 - 31 August 1982

Prepared for Office of Naval Research 800 North Quincy Street Arlington, Virginia 22217

> This document has been approved for public release and sale; its distribution is unlimited.

28

83

11

v

| REPORT DOCUMEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REPORT NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2. GOVT ACCESSION N                                                                                                                                                                                                                                                                                                                                                 | D. 3. RECIPIENT'S CATALOG NUMBER                                                                                                                                                                     |

| <del>08-80-33</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | HD - A135007                                                                                                                                                                                                                                                                                                                                                        | }                                                                                                                                                                                                    |

| TITLE (and Subtitio)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                     | S. TYPE OF REPORT & PERIOD COVERE                                                                                                                                                                    |

| GaAs FET LOGIC AT LOW TEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PERATURES                                                                                                                                                                                                                                                                                                                                                           | Final Technical Report<br>1 Sept. 1979 - 31 Aug. 1982                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                     | 6. PERFORMING ORG. REPORT NUMBER                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                     | 08-83-40                                                                                                                                                                                             |

| AUTHOR(=)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      |

| M. R. Namordi, W. A. White                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | e, F. H. Doerbeck                                                                                                                                                                                                                                                                                                                                                   | N00014-79-C-0789                                                                                                                                                                                     |

| PERFORMING ORGANIZATION NAME A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                     | 10. PROGRAM ELEMENT, PROJECT, TASP<br>AREA & WORK UNIT NUMBERS                                                                                                                                       |

| Texas Instruments Incorpor<br>Central Research Laborator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rated                                                                                                                                                                                                                                                                                                                                                               | PE 62762N                                                                                                                                                                                            |

| 13500 N. Central Expresswa<br>Dallas, Texas 75265                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ау                                                                                                                                                                                                                                                                                                                                                                  | RF62-582-801<br>NR 383-051                                                                                                                                                                           |

| CONTROLLING OFFICE NAME AND AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                     | 12. REPORT DATE                                                                                                                                                                                      |

| Department of the Navy<br>Office of Naval Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                     | August 1983                                                                                                                                                                                          |

| Arlington, Virginia 2221                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                                                                                                                                                                                                                                                                                                   | 69                                                                                                                                                                                                   |

| MONITORING AGENCY NAME & ADDRI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LSS(It different from Controlling Office,                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                     | Unclassified                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      |

| DISTRIBUTION STATEMENT (of this Re<br>Approved for public relea:<br>DISTRIBUTION STATEMENT (of the ob-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | se; distribution unlimit                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                      |

| Approved for public release<br>DISTRIBUTION STATEMENT (of the edu<br>SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | se; distribution unlimit                                                                                                                                                                                                                                                                                                                                            | .ed                                                                                                                                                                                                  |

| Approved for public release<br>DISTRIBUTION STATEMENT (of the ob-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | se; distribution unlimit                                                                                                                                                                                                                                                                                                                                            | red<br>free Report)                                                                                                                                                                                  |

| Approved for public release<br>DISTRIBUTION STATEMENT (of the ob-<br>SUPPLEMENTARY NOTES<br>ONR Project Engineer: M.<br>KEY WORDS (Continue on reverse elde i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | se; distribution unlimit<br>etrect entered in Block 20, 11 different<br>N. Yoder                                                                                                                                                                                                                                                                                    | ed<br>(rear Report)                                                                                                                                                                                  |

| Approved for public release<br>DISTRIBUTION STATEMENT (of the ob-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | se; distribution unlimit<br>etrect entered in Block 20, 11 different<br>N. Yoder<br>f necessary and identify by block numb<br>Ring Oscillat                                                                                                                                                                                                                         | eed<br>(rean Report)                                                                                                                                                                                 |

| Approved for public release<br>DISTRIBUTION STATEMENT (of the edu<br>SUPPLEMENTARY NOTES<br>ONR Project Engineer: M.<br>KEY WORDS (Continue on referee elde i<br>GaAs Integrated Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | se; distribution unlimit<br>ence entered in Block 20, 11 different<br>N. Yoder<br>I necessary and identify by block mumb<br>Ring Oscillat<br>Propagation D<br>Power Dissipa                                                                                                                                                                                         | eed<br>Report)<br>Ors<br>elay<br>tion                                                                                                                                                                |

| Approved for public release<br>DISTRIBUTION STATEMENT (of the edu<br>SUPPLEMENTARY NOTES<br>ONR Project Engineer: M.<br>KEY WORDS (Continue on reverse elde f<br>GaAs Integrated Circuits<br>Gallium Arsenide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | se; distribution unlimit<br>ence entered in Block 20, 11 different<br>N. Yoder<br>I necessary and identify by block mumb<br>Ring Oscillat<br>Propagation D<br>Power Dissipa                                                                                                                                                                                         | ed<br>from Report)                                                                                                                                                                                   |

| Approved for public release<br>DISTRIBUTION STATEMENT (of the edu<br>SUPPLEMENTARY NOTES<br>ONR Project Engineer: M.<br>KEY WORDS (Continue on reverse elde i<br>GaAs Integrated Circuits<br>Gallium Arsenide<br>Mobility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | se; distribution unlimit<br>etrect entered in Block 20, 11 different<br>N. Yoder<br>Ring Oscillat<br>Propagation D<br>Power Dissipa<br>Temperature C                                                                                                                                                                                                                | eed<br>freen Report)<br>ors<br>elay<br>tion<br>haracteristics                                                                                                                                        |

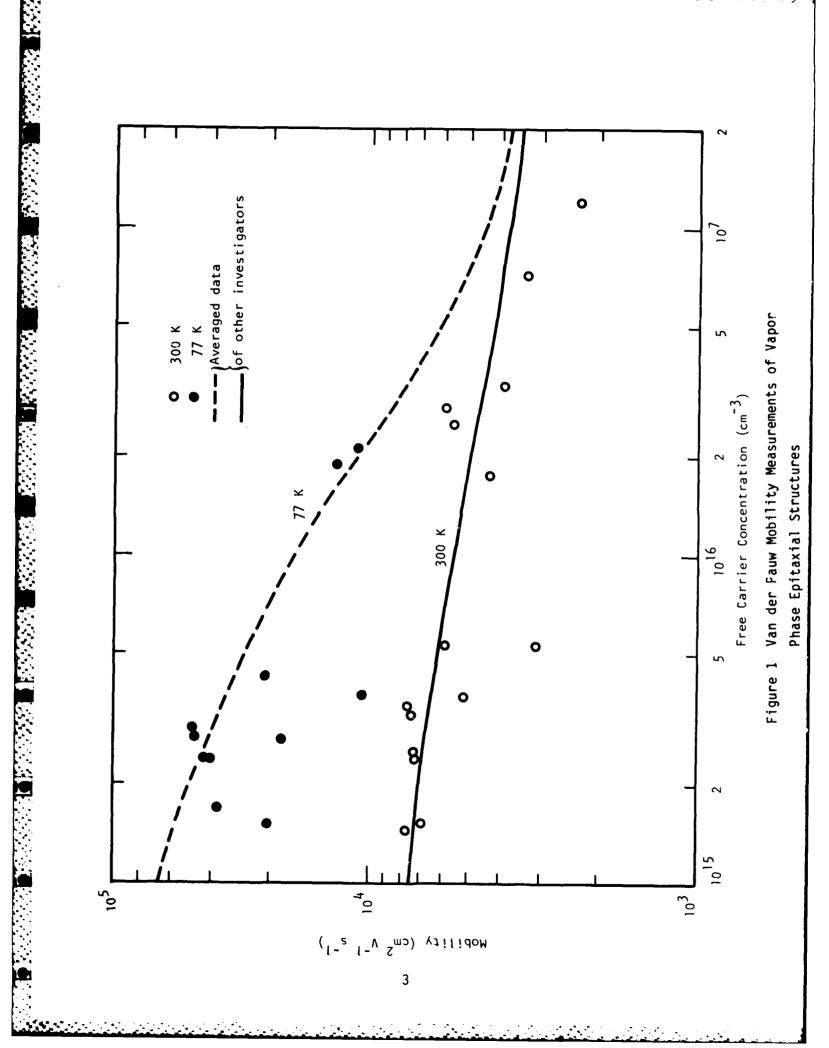

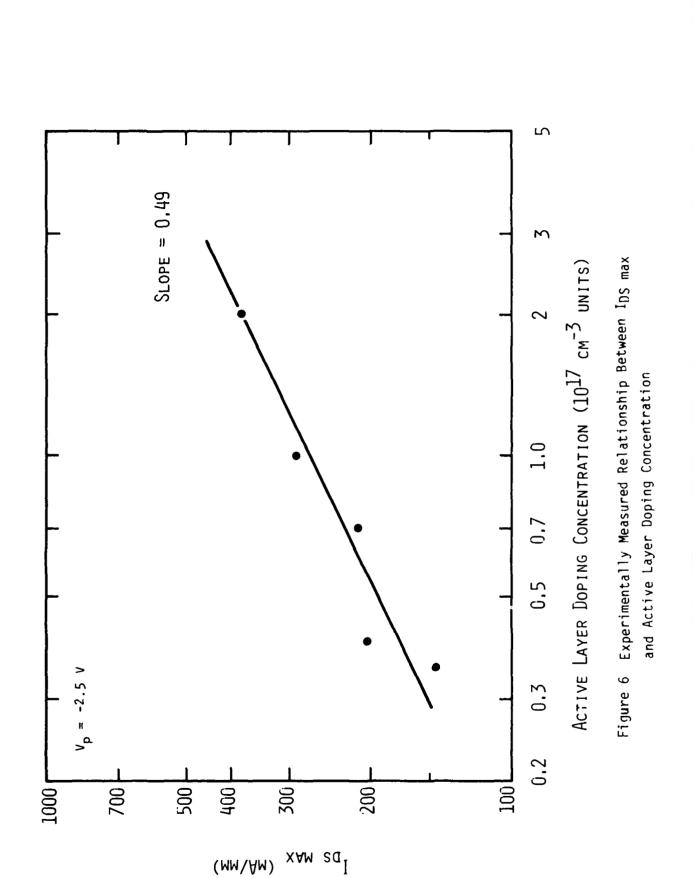

| Approved for public release<br>DISTRIBUTION STATEMENT (of the observed)<br>SUPPLEMENTARY NOTES<br>ONR Project Engineer: M.<br>KEY WORDS (Continue on reverse ofder<br>GaAs Integrated Circuits<br>Gallium Arsenide<br>Mobility<br>ABSTRACT (Continue on reverse ofder<br>Ring oscillator circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | se; distribution unlimit<br>ence entered in Block 20, if different<br>N. Yoder<br>I necessary and identify by block numb<br>Ring Oscillat<br>Propagation D<br>Power Dissipa<br>Temperature C<br>necessary and identify by block numb<br>Luits were fabricated on                                                                                                    | ed<br>(rear Report)<br>ors<br>elay<br>tion<br>haracteristics<br>(r)<br>both VPE and ion-implanted                                                                                                    |

| Approved for public release<br>DISTRIBUTION STATEMENT (of the observed of the ob | se; distribution unlimit<br>ence entered in Block 20, if different<br>N. Yoder<br>I necessary and identify by block numb<br>Ring Oscillat<br>Propagation D<br>Power Dissipa<br>Temperature C<br>necessary and identify by block numb<br>Luits were fabricated on<br>ng the 4 x 10 <sup>16</sup> to 1 x 1                                                            | ed<br>free Report)<br>ors<br>elay<br>tion<br>haracteristics<br>both VPE and ion-implanted<br>017 cm <sup>-3</sup> doping range. The                                                                  |

| Approved for public release<br>DISTRIBUTION STATEMENT (of the edu<br>SUPPLEMENTARY NOTES<br>ONR Project Engineer: M.<br>KEY WORDS (Continue on reverse elde f<br>GaAs Integrated Circuits<br>Gallium Arsenide<br>Mobility<br>ABSTRACT (Continue on reverse elde ff<br>Ring oscillator circuits<br>active layers encompassin<br>nominal pinch-off voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | se; distribution unlimit<br>otract entered in Block 20, if different<br>N. Yoder<br>I necessary and identify by block numb<br>Ring Oscillat<br>Propagation D<br>Power Dissipa<br>Temperature C<br>necessary and identify by block numb<br>Luits were fabricated on<br>ng the 4 x 10 <sup>16</sup> to 1 x 1<br>e was -2.5 V. Using an                                | eed<br>free Report)<br>ors<br>elay<br>tion<br>haracteristics<br>both VPE and ion-implanted<br>017 cm-3 doping range. The<br>especially constructed                                                   |

| Approved for public releases<br>DISTRIBUTION STATEMENT (of the observed of the o | se; distribution unlimit<br>etrace entered in Block 20, 11 different<br>N. Yoder<br>I necessary and identify by block music<br>Ring Oscillat<br>Propagation D<br>Power Dissipa<br>Temperature C<br>necessary and identify by block music<br>Luits were fabricated on<br>ing the 4 x 10 <sup>16</sup> to 1 x 1<br>e was -2.5 V. Using an<br>, the circuits were then | er<br>(real Report)<br>ors<br>elay<br>tion<br>haracteristics<br>()<br>both VPE and ion-implanted<br>017 cm <sup>-3</sup> doping range. The<br>especially constructed<br>characterized on-slice at 77 |