| AD-A128 676<br>UNCLASSIFIED | NEW CCD S | TION OF CHAR<br>IGNAL PROCE<br>LECTRICAL ENG<br>DC-TR-82-322 | (U) NORTHE | ASTERN UNIV E<br>B L COCHRUN | SOSTON MASS | 1/ <b>2.</b><br>IL |  |

|-----------------------------|-----------|--------------------------------------------------------------|------------|------------------------------|-------------|--------------------|--|

|                             | Station , |                                                              |            |                              |             |                    |  |

|                             |           |                                                              |            |                              |             |                    |  |

|                             |           |                                                              |            |                              |             |                    |  |

|                             |           |                                                              |            |                              |             |                    |  |

|                             |           |                                                              |            |                              |             |                    |  |

|                             |           |                                                              |            |                              |             |                    |  |

MICROCOPY RESOLUTION TEST CHART NATIONAL BUREAU OF STANDARDS-1963-A

RADC-TR-82-322 Final Technical Report February 1983

9

63

ELECTE

E

MAY 2 7

#

Northeastern University

Basil 1. Cochrun John G. Proekis

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED

OTIC FILE COPY

ROME AIR DEVELOPMENT CENTER Air Force Systems Command Griffiss Air Force Base, NY 13441

83

05 27 003

This report has been reviewed by the RADC Public Affairs Office (PA) and is releasable to the National Technical Information Service (NTIS). At NTIS it will be releasable to the general public, including foreign nations.

RADC-TR-82-322 has been reviewed and is approved for publication.

APPROVED: Je nay Silverman

JERRY SILVERMAN **Project Engineer**

APPROVED:

arold Roth

HAROLD ROTH, Director Solid State Sciences Division

FOR THE COMMANDER: John P. Kuss

JOHN P. HUSS Acting Chief, Plans Office

If your address has changed or if you wish to be removed from the RADC mailing list, or if the addressee is no longer employed by your organization, please notify RADC (ESES), Hanscom AFB MA 01731. This will assist us in maintaining a current mailing list.

Do not return copies of this report unless contractual obligations or notices on a specific document requires that it be returned.

| SECURITY CLASSIFICATION OF THIS PAGE (When Dece Entered)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                                                                                                                                                      |

| RADC-TR-82-322                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1. SECIPIENT'S CATALOG NUMBER                                                                                                                                                                    |

| والمتحدث والمحافظ والمحافظ والمتحدث والمحافظ المتبه المتبه والمتحد فالمحب المحب المحب المحب والمحاف والمحب والمحاف والمحاف                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                                                                                                                                                               |

| I. TITLE (and Subtilio)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5. TYPE OF REPORT & PERIOD COVERED                                                                                                                                                               |

| INVESTIGATION OF CHARACTERISTICS AND APPLICA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Final Technical Report                                                                                                                                                                           |

| TIONS OF NEW CCD SIGNAL PROCESSING DEVICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | S. PERFORMING OTG. REPORT NUMBER                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | N/A                                                                                                                                                                                              |

| author(a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S. CONTRACT OR GRANT NUMBER(S)                                                                                                                                                                   |

| Basil L. Cochrun                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | F19628-79-C-0165                                                                                                                                                                                 |

| John G. Proakis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                  |

| . PERFORMING ORGANIZATION NAME AND ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS                                                                                                                                   |

| lortheastern University                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 62702F                                                                                                                                                                                           |

| epartment of Electrical Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 46001828                                                                                                                                                                                         |

| SOSTON MA 01731                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12. REPORT DATE                                                                                                                                                                                  |

| tome Air Development Center (ESE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | February 1983                                                                                                                                                                                    |

| anscom AFB MA 01731                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13. NUMBER OF PAGES                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                  |

| A. MON' ORING AGENCY NAME & ADDRESS(II different from Controlling Office)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15. SECURITY CLASS, (of this report)                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | UNCLASSIFIED                                                                                                                                                                                     |

| Same                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15. DECLASSIFICATION/DOWNGRADING                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Report)                                                                                                                                                                                          |

| 17. DISTRIBUTION STATEMENT (of the obstract entered in Block 20, if different in<br>Same                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                  |

| Same<br>18. SUPPLEMENTARY NOTES<br>RADC Project Engineer: Jerry Silverman (ESES)<br>9. KEY WORDS (Cominue on reverse side 11 necessary and identify by black number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                  |

| Same<br>RADC Project Engineer: Jerry Silverman (ESES)<br>S. KEY WORDS (Cominue on reverse aids if necessary and identify by black number<br>Signal Processing Modules Microproces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |

| Same<br>RADC Project Engineer: Jerry Silverman (ESES)<br>KEY WORDS (Continue on reverse side if necessary and identify by block number<br>Signal Processing Modules Microprocess<br>Charge-coupled Devices (CCDs) Recirculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | sor Control Software                                                                                                                                                                             |

| Same<br>ADC Project Engineer: Jerry Silverman (ESES)<br>KEY HORDS (Continue on reverse side if necessary and identify by block number<br>Signal Processing Modules Microprocess<br>Charge-coupled Devices (CCDs) Recirculation<br>Sampled Analog Line Data Analog/Binat<br>CCD Building Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | sor Control Software<br>ng Analog Memory                                                                                                                                                         |

| Same<br>RADC Project Engineer: Jerry Silverman (ESES)<br>Signal Processing Modules<br>Charge-coupled Devices (CCDs)<br>Sampled Analog Line Data<br>CCD Building Blocks<br>Interface Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | sor Control Software<br>ng Analog Memory<br>ry Correlator                                                                                                                                        |

| Same<br>ADC Project Engineer: Jerry Silverman (ESES)<br>Signal Processing Modules Microprocess<br>Charge-coupled Devices (CCDs) Recirculating<br>Sampled Analog Line Data Analog/Binat<br>CCD Building Blocks<br>Interface Circuitry<br>10. ABSTRACT (Continue on reverse side if necessary and identify by block number)<br>This final report on Contract F19628-79-C-0165 of<br>development of two high-speed sampled analog signals<br>based on charge coupled device (CCD) technology<br>serves as the controller for the modules.<br>The CCDs used in the modules are an analog-binar<br>programmable transversal filter (PTF), a refr                                                                                                                                                                                                                      | sor Control Software<br>ng Analog Memory<br>ry Correlator<br>describes the work on the<br>gnal processing modules<br>. A Z-80 microprocessor<br>ry correlator (ABC), a<br>eshable sampled analog |

| ADC Project Engineer: Jerry Silverman (ESES)<br>• KEY WORDS (Continue on reverse side if necessary and identify by block number<br>Signal Processing Modules Microprocess<br>Charge-coupled Devices (CCDs) Recirculatin<br>Sampled Analog Line Data Analog/Bina:<br>CCD Building Blocks<br>Interface Circuitry<br>• ABSTRACT (Continue on reverse side if necessary and identify by block number)<br>This final report on Contract F19628-79-C-0165<br>development of two high-speed sampled analog signated analog signated analog signated on charge coupled device (CCD) technology<br>serves as the controller for the modules.<br>The CCDs used in the modules are an analog-binated programmable transversal filter (PTF), a refromemory (RSAM), a corner-turning memory (CTM) and                                                                         | sor Control Software<br>ng Analog Memory<br>ry Correlator<br>describes the work on the<br>gnal processing modules<br>. A Z-80 microprocessor<br>ry correlator (ABC), a<br>eshable sampled analog |

| ADC Project Engineer: Jerry Silverman (ESES)<br>ADC Project Engineer: Jerry Silverman (ESES)<br>KEY WORDS (Continue on reverse side if necessary and identify by block number<br>Signal Processing Modules Microprocess<br>Charge-coupled Devices (CCDs) Recirculatin<br>Sampled Analog Line Data Analog/Bina:<br>CCD Building Blocks<br>Interface Circuitry<br>0. ASSTRACT (Continue on reverse side if necessary and identify by block number)<br>This final report on Contract F19628-79-C-0165 (<br>development of two high-speed sampled analog signased on charge coupled device (CCD) technology<br>serves as the controller for the modules.<br>The CCDs used in the modules are an analog-binar<br>programmable transversal filter (PTF), a refr<br>memory (RSAM), a corner-turning memory (CTM) and<br>D 1 JAN 73 1473 EDITION OF 1 NOV 68 IS OBSOLETE | sor Control Software<br>ng Analog Memory<br>ry Correlator<br>describes the work on the<br>gnal processing modules<br>. A Z-80 microprocessor<br>ry correlator (ABC), a<br>eshable sampled analog |

a water a second a se

And a second sec

UNCLASSIFIED

#### LECURITY CLASSIFICATION OF THIS PAGE (When Date Entered)

form device. A description of the device is contained in the report and a number of possible inter-connections are considered. Also described are the software and hardware features in the interface between the CCD modules and the microprocessor and the software that was developed for the Z-80 microprocessor.

SECURITY CLASSIFICATION OF THIP PAGE(When Date Entered)

# Preface

This final technical report describes work performed under Contract F19628-79-C-0165 from RADC to Northeastern University, Boston, Massachusetts. The Principal Investigators were Professors Basil L. Cochrun and John G. Proakis. The Technical Contract Monitor for RADC was Dr. Jerry Silverman.

The authors are grateful to S. C. Munroe of the M.I.T. Lincoln Laboratory for discussions regarding the operation of the APC chip and for his suggestions on modification of peripheral circuitry. The authors are also grateful to S. Waldstein of the MITRE Corporation for his assistance in obtaining PTF chips, and for discussions about the characteristics and peripheral circuitry of the PTF.

In addition to the contributions of the Principal Investigators, this report contains contributions by personnel who have worked on this contract during the past three years. Specifically, we wish to acknowledge the work of Mr. George Blustein (software consultant), Ulf Dunberger (a graduate student), and Bill Donaldson, Edward Karaian and Zafer Gulum (Co-op students).

Accession For NTIS GRA&I DTIC TAB Unannounced Justification Bv. Distribution/ Availability Codes Avail and/or Dist Special

i

# Table of Contents

|    | Abstract                                           |

|----|----------------------------------------------------|

|    | List of Illustrations                              |

| 1. | Introduction                                       |

| 2. | Software Development for the Z-80 Microprocessor26 |

| 3. | Microprocessor Interface to CCD Modules46          |

| 4. | Analog Binary Correlator (ABC)85                   |

| 5. | Programmable Transversal Filter101                 |

| 6. | Signal Generator116                                |

| 7. | Design of Two-Dimensional DFT120                   |

| 8. | Concluding Remarks and Further Work                |

|    | References                                         |

•

and the second second

#### Abstract

This final report on Contract F19628-79-C-0165 describes the work on the development of two high-speed sampled analog signal processing modules based on charge coupled device (CCD) technology. A Z-80 microprocessor serves as the controller for the modules.

The CCD's used in the modules are an analog-binary correlator (ABC), a programmable transversal filter (PTF), a refreshable sampled analog memory (RSAM), a corner-turning memory (CTM) and a Reticon chirp-z transform device. A description of the devices is contained in the report and a number of possible interconnections are considered. Also described are the software and hardware features in the interface between the CCD modules and the microprocessor and the software that was developed for the 2-80 microprocessor.

#### List of Illustrations

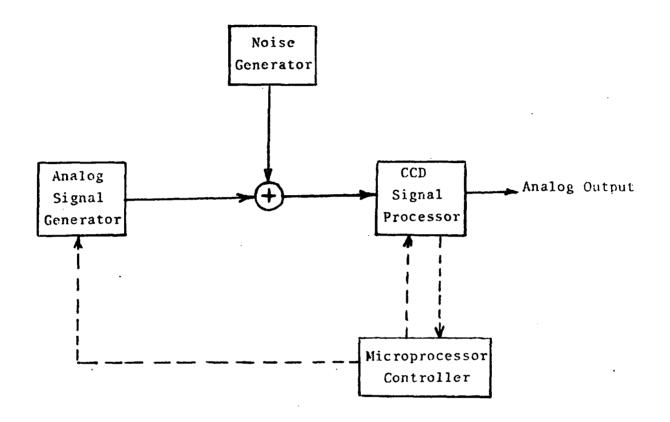

- Figure 1.1 General Configuration of Sampled Analog Signal Processing System

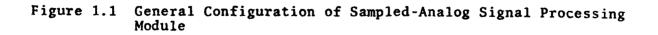

- Figure 1.2 Functional Block Diagram of Signal Processing System with the Interface Board

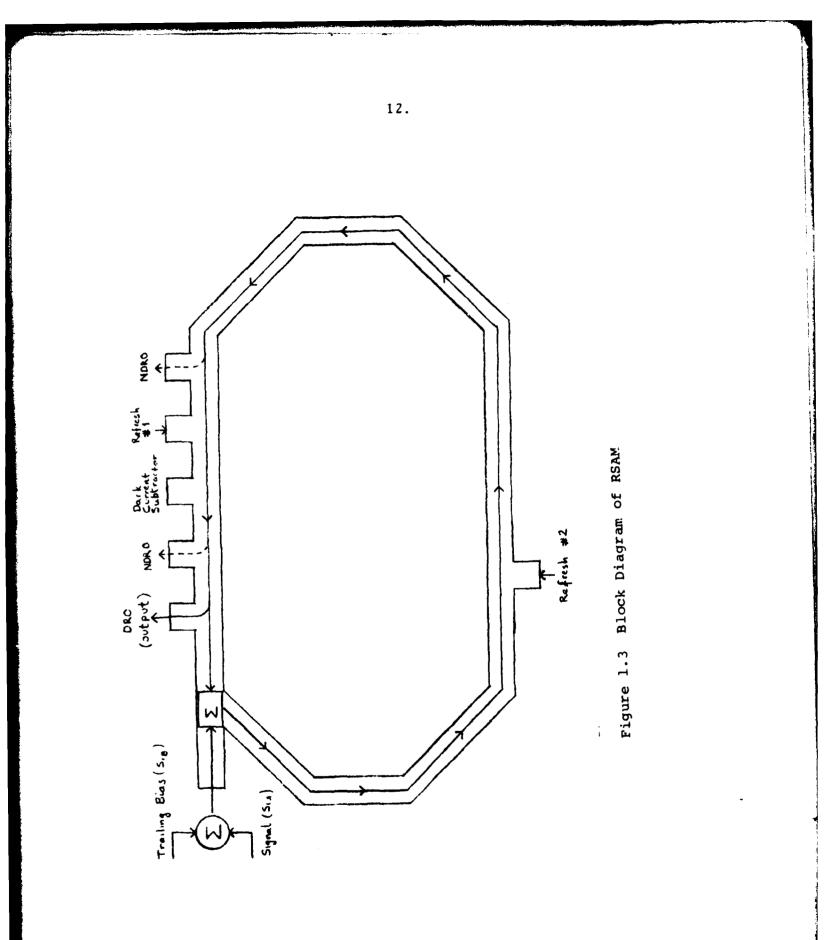

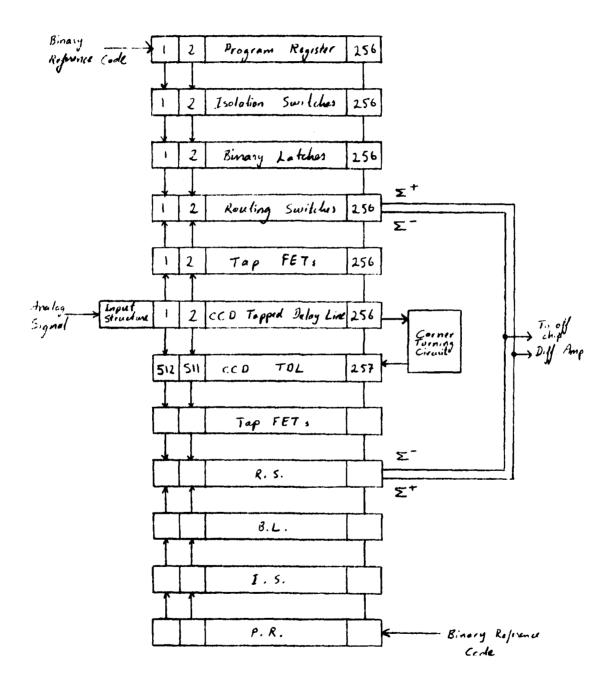

- Figure 1.3 Block Diagram of RSAM

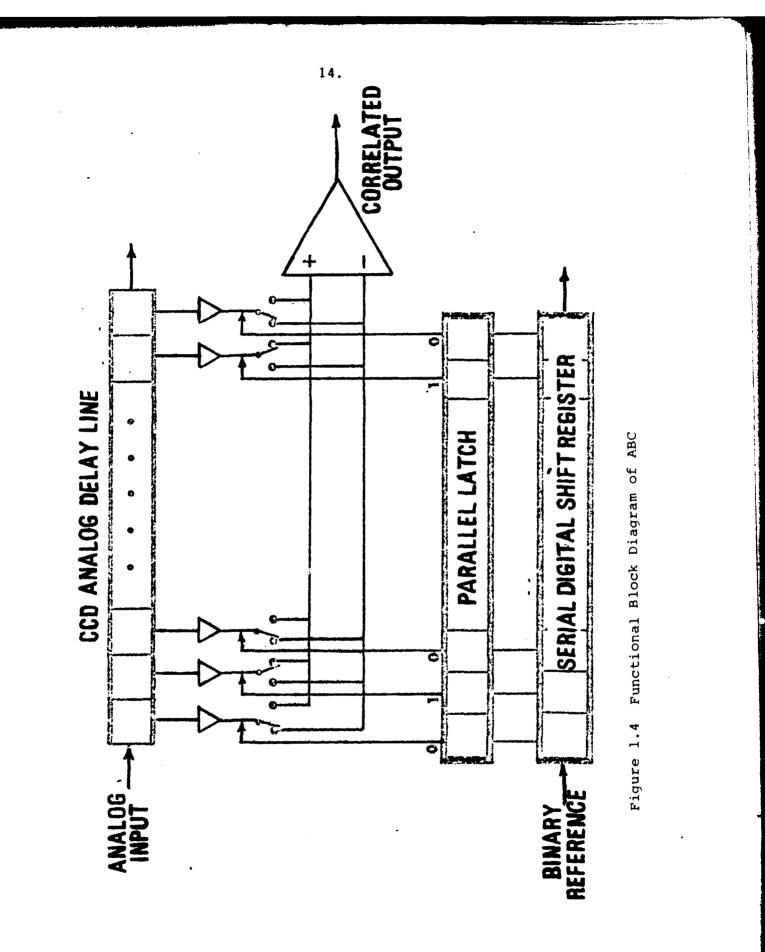

- Figure 1.4 Functional Block Diagram of ABC

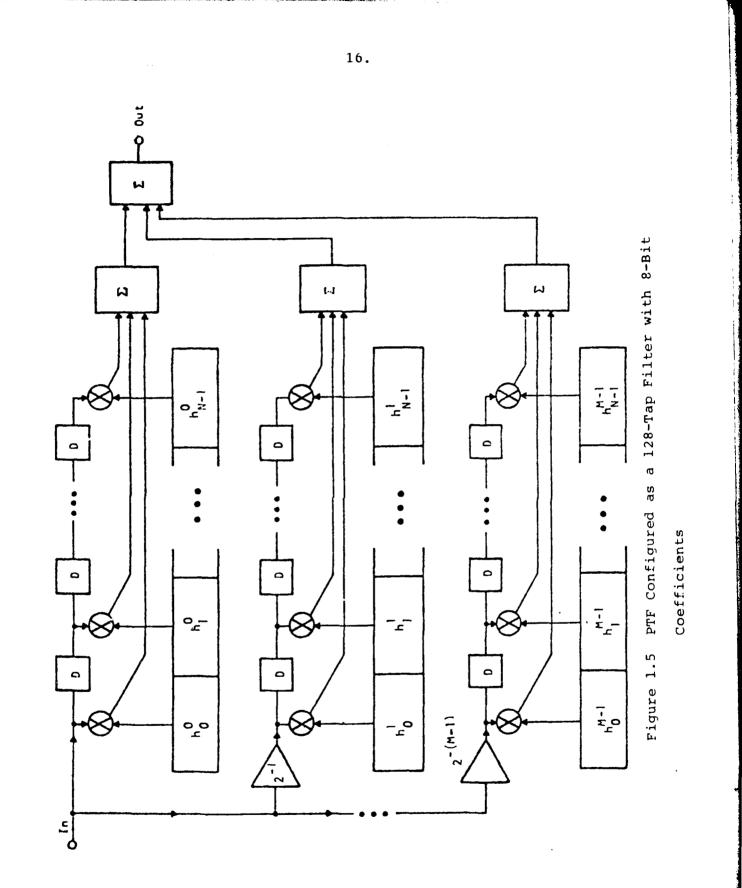

- Figure 1.5 PTF Configured as a 128-Tap Filter with 8-Bit Coefficients

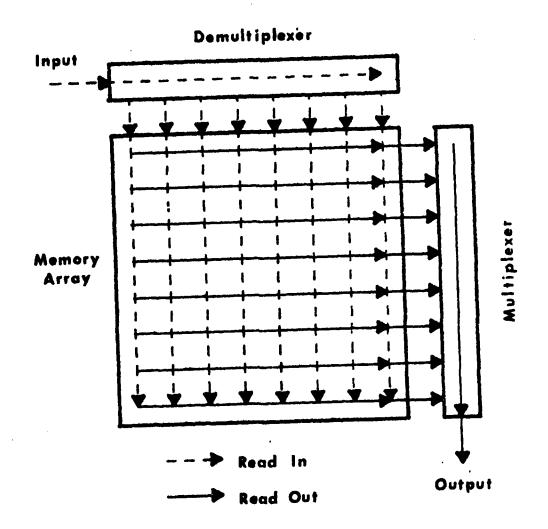

- Figure 1.6 Functional Block Diagram of CTM

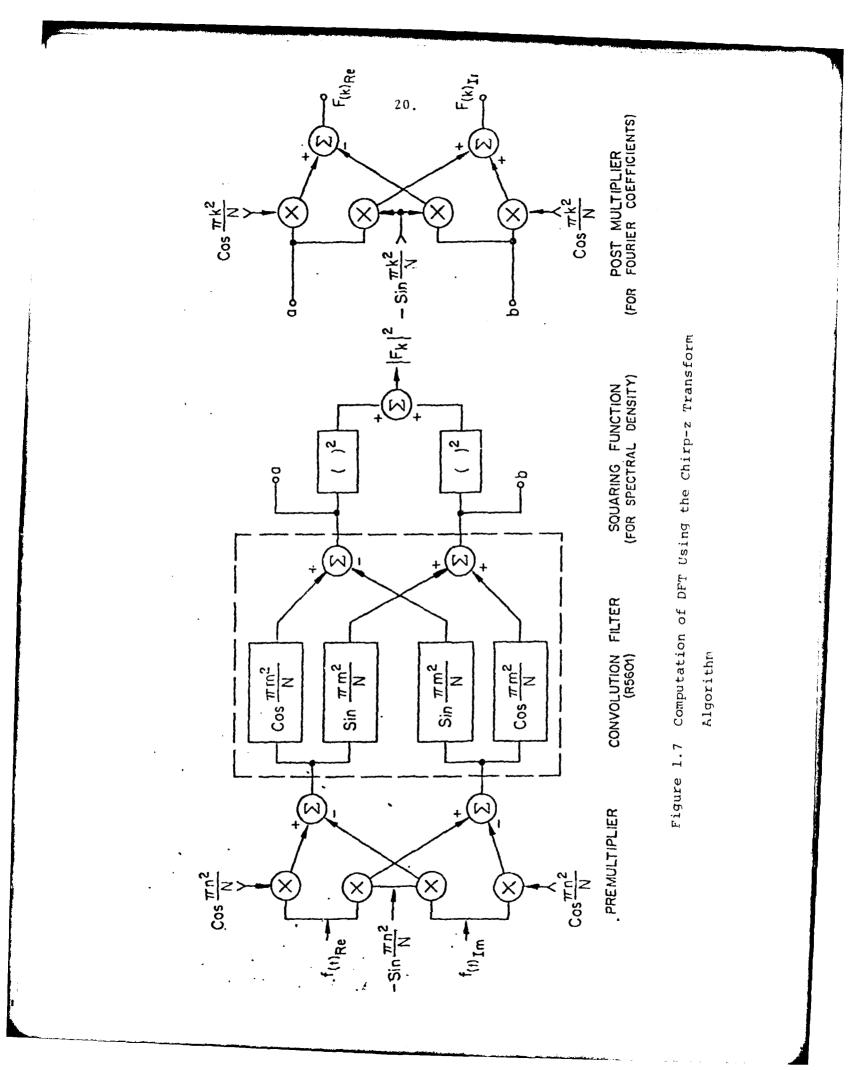

- Figure 1.7 Computation of DFT Using the Chirp-z Transform Algorithm

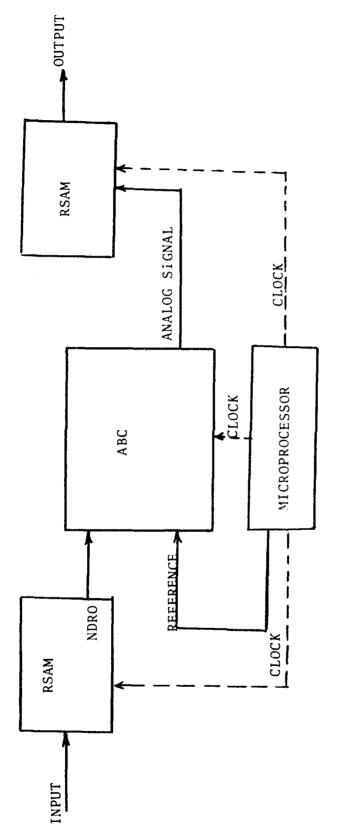

- Figure 1.8 A Configuration of CCD's for Processing Line-Formatted Data

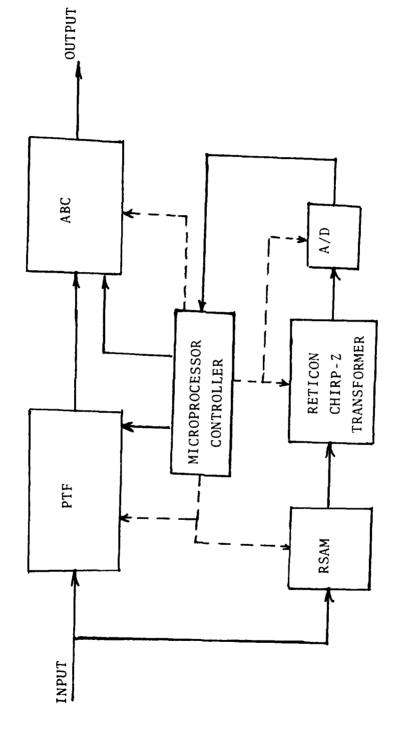

- Figure 1.9 A Configuration of CCD's for Performing Adaptive Notch Filtering

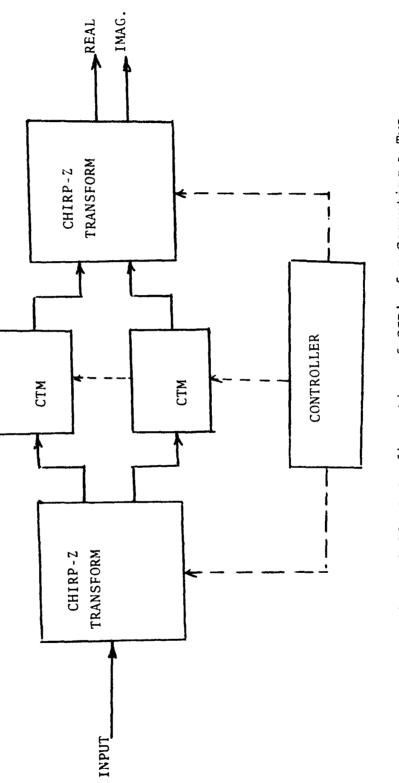

- Figure 1.10 A Configuration of CCD's for Computing a Two-Dimensional DFT

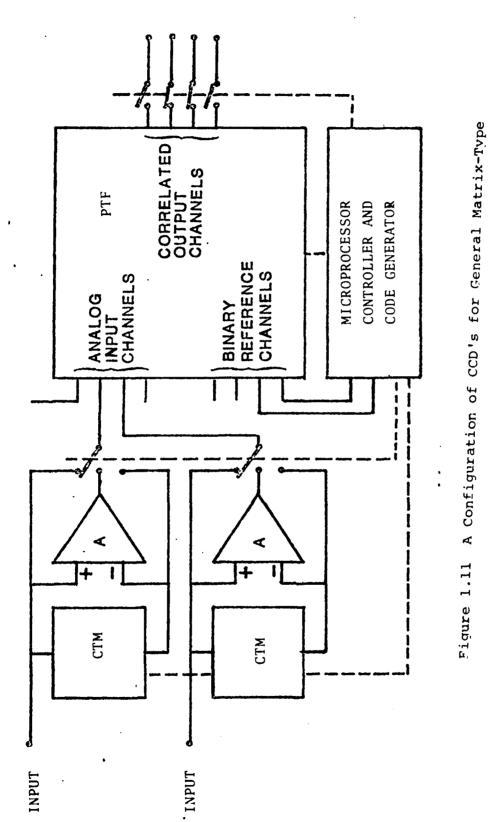

- Figure 1.11 A Configuration of CCD's for General Matrix-Type Signal Processing

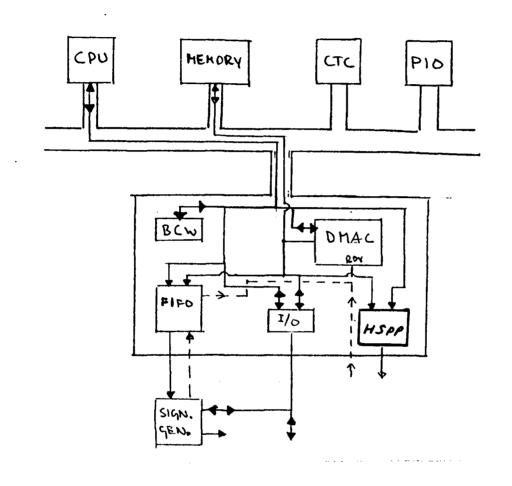

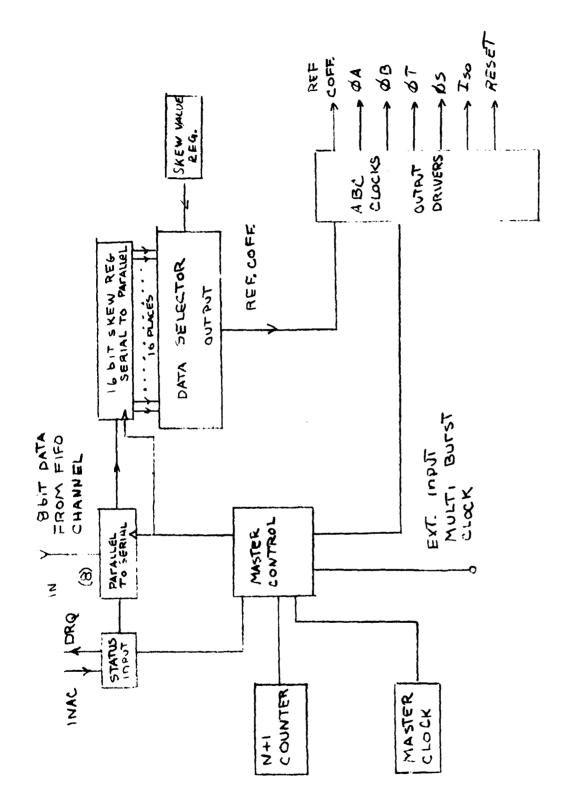

- Figure 3.1 General Configuration of Interface Board

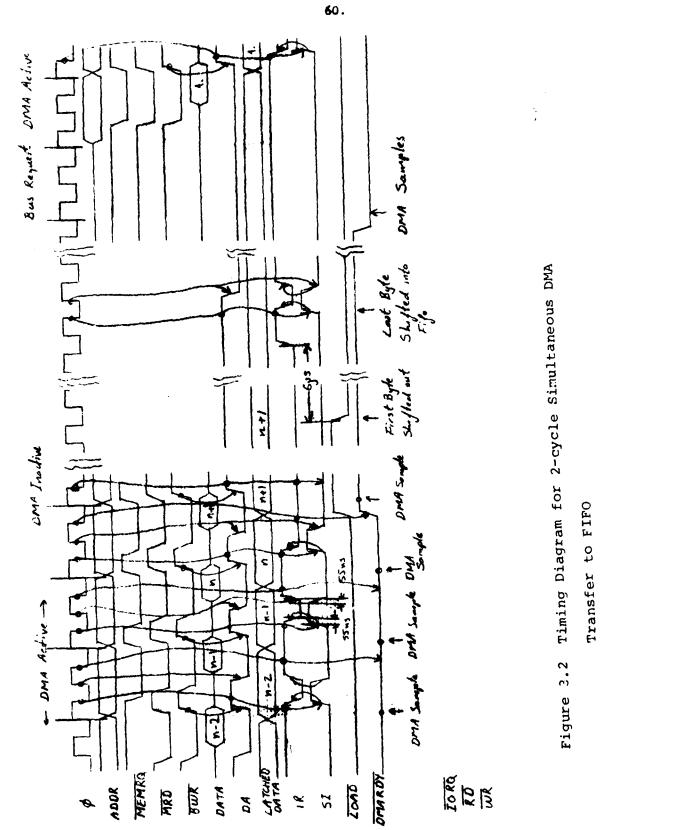

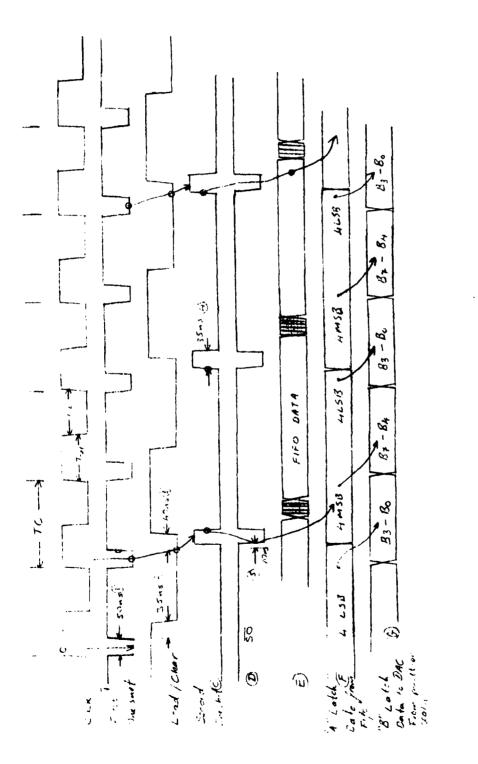

- Figure 3.2 Timing Diagram for 2-cycle Simultaneous DMA Transfer to FIFO

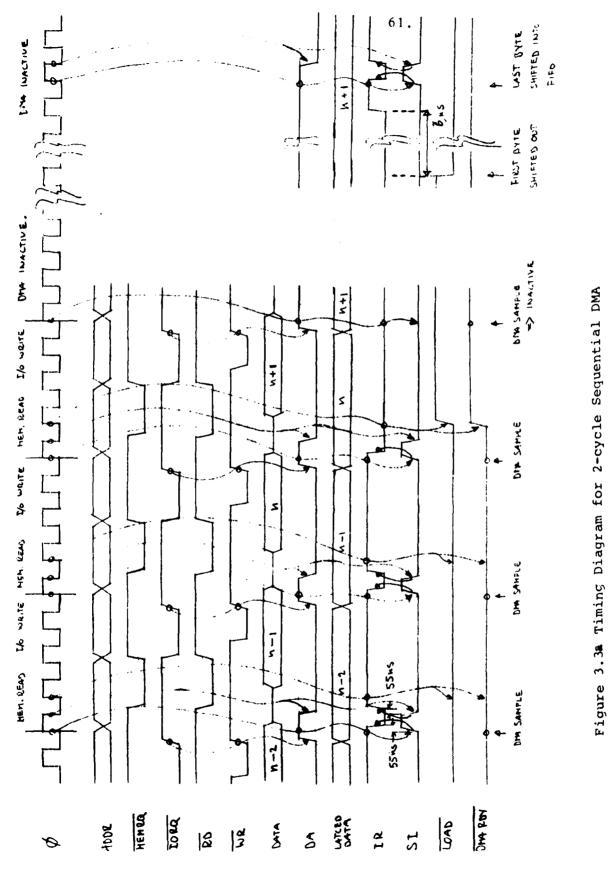

- Figure 3.3a Timing Diagram for 2-cycle Sequential DMA Transfer to FIFO

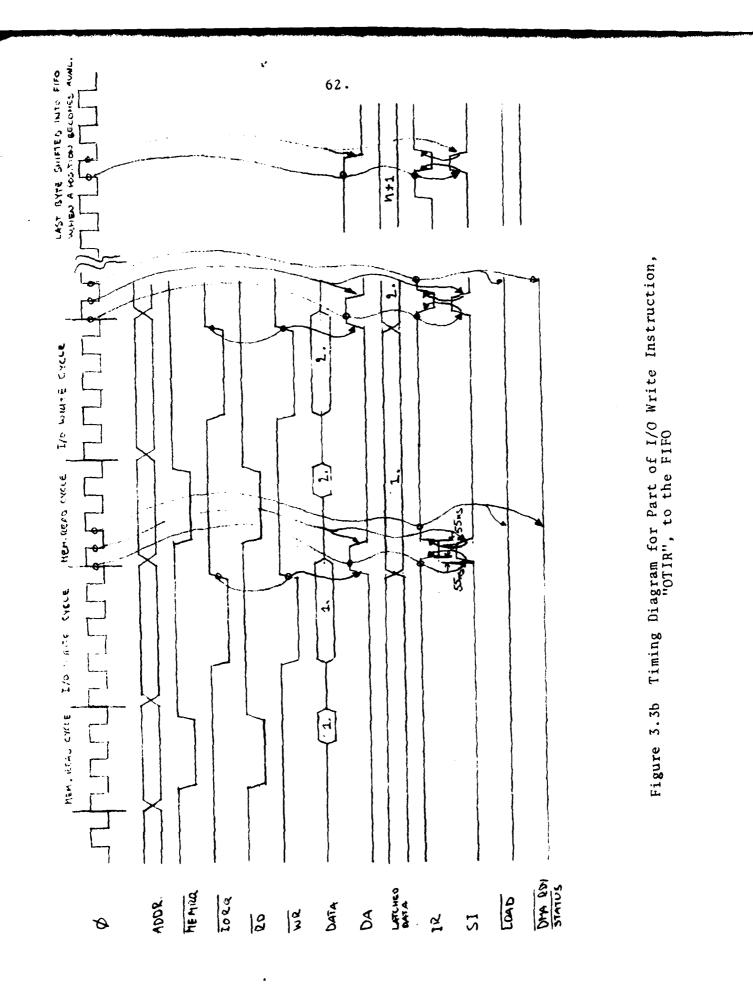

- Figure 3.3b Timing Diagram for Part of I/O Write Instruction, "OTIR", to the FIFO

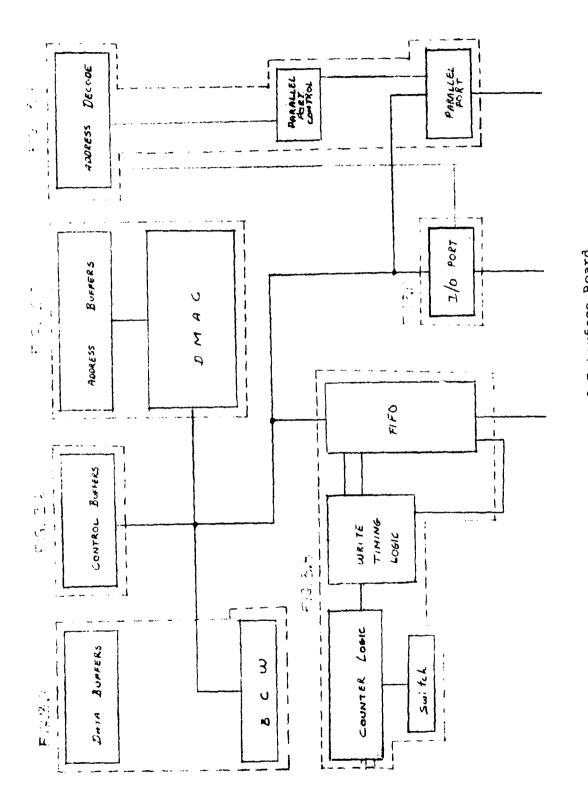

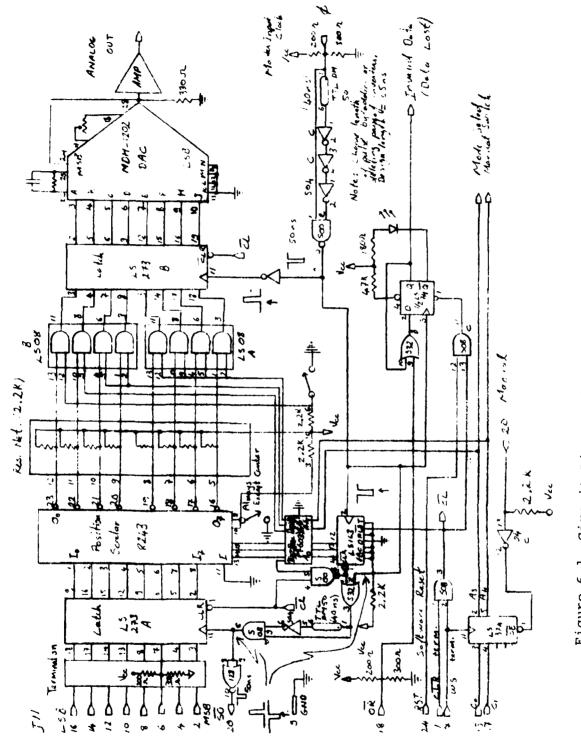

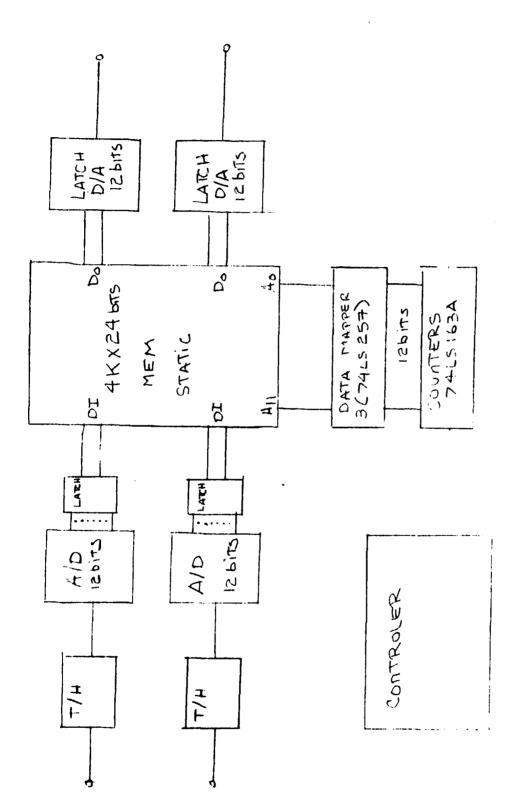

- Figure 3.4 Block Diagram of Interface Board

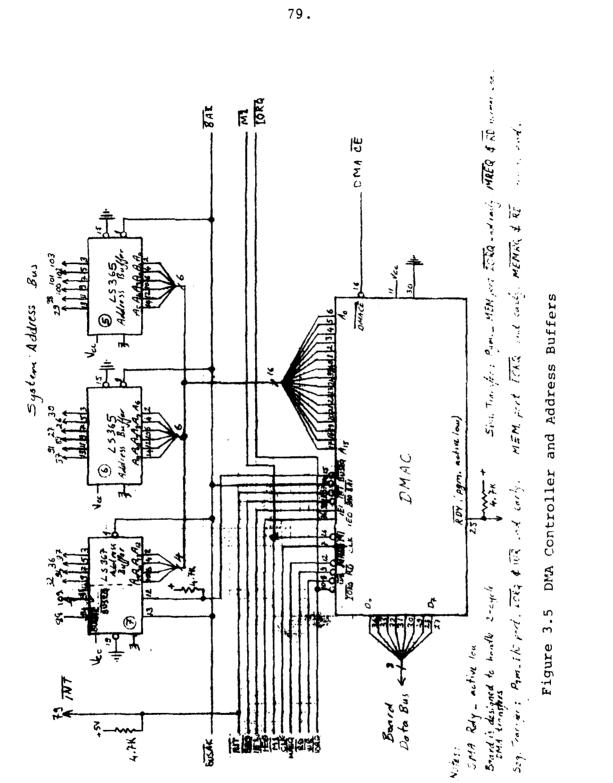

- Figure 3.5 DMA Controller and Address Buffers

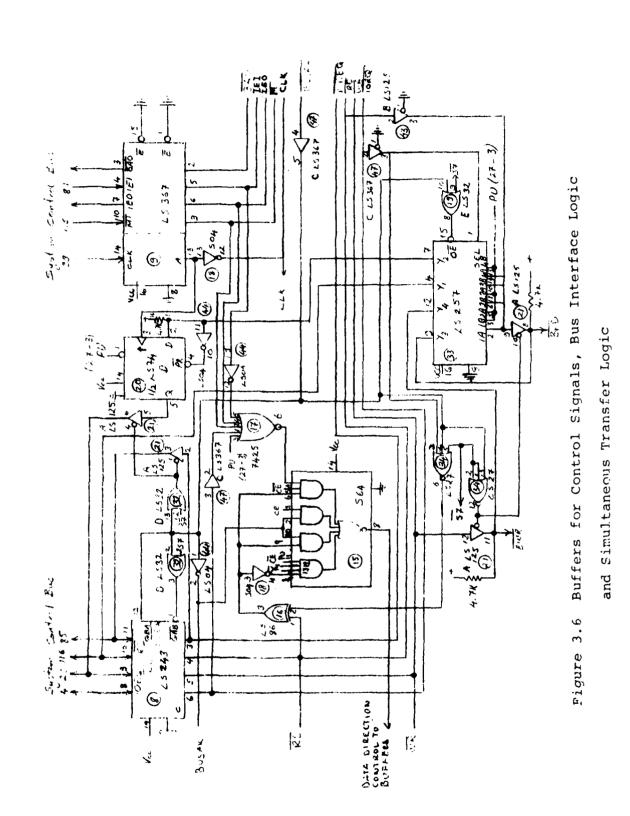

- Figure 3.6 Buffers for Control Signals, Bus Interface Logic and Simultaneous Transfer Logic

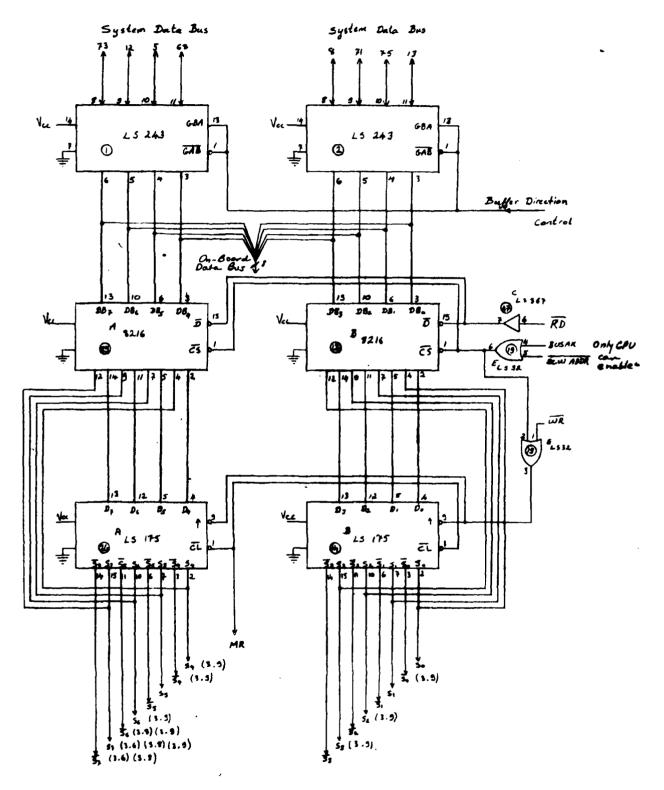

- Figure 3.7 Board Control Word and Buffers

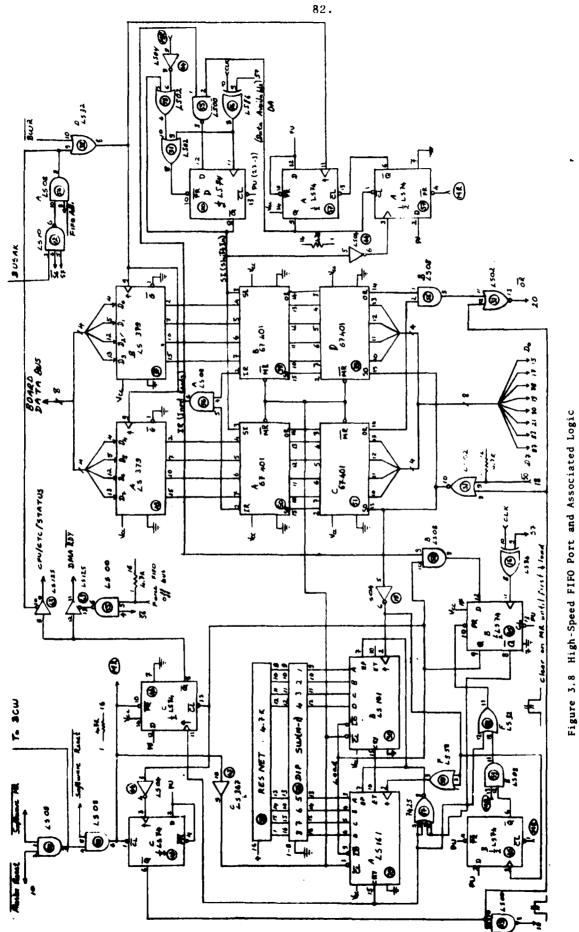

- Figure 3.8 High-Speed FIFO Port and Associated Logic

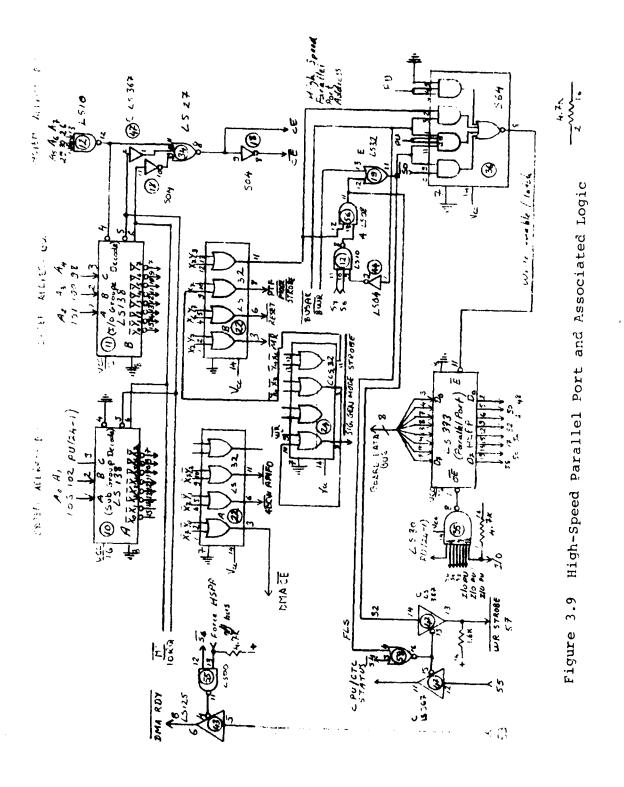

- Figure 3.9 High-Speed Parallel Port and Associated Logic

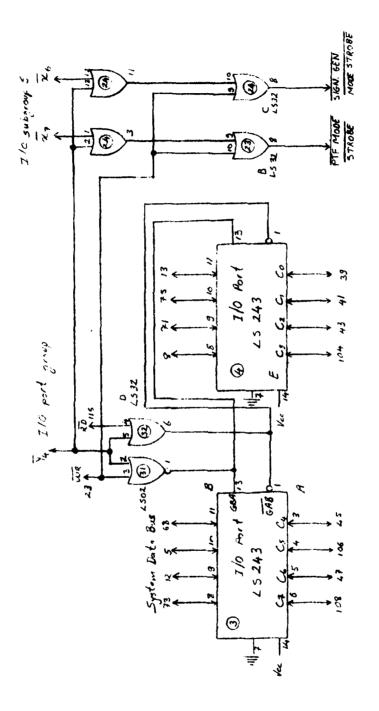

- Figure 3.10 General Purpose I/O Port

- Figure 4.1 Basic Architecture of the ABC

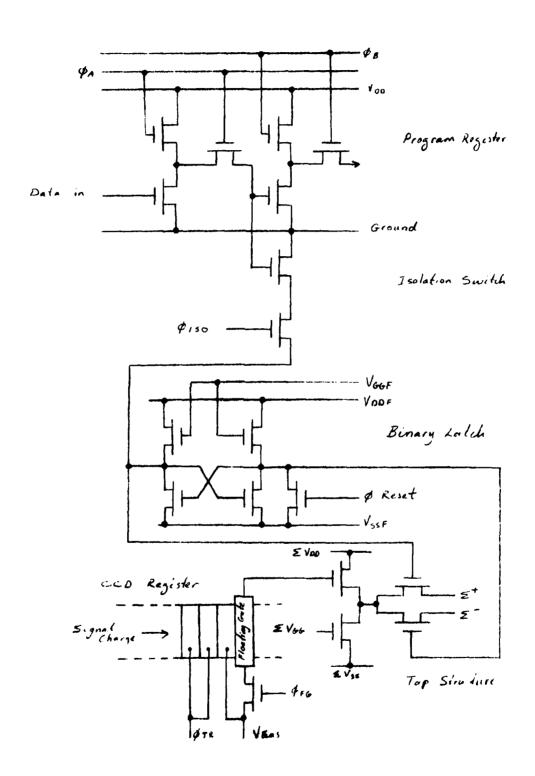

- Figure 4.2 One-Stage Slice Showing all Devices from Program Register to CCD Register

- Figure 4.3 Simplified Block Diagram and Timing for the ABC

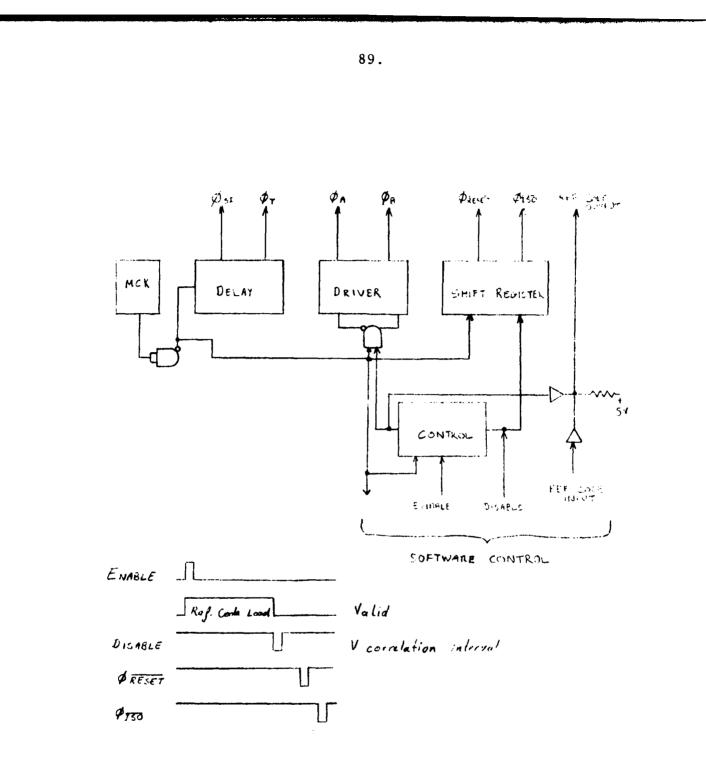

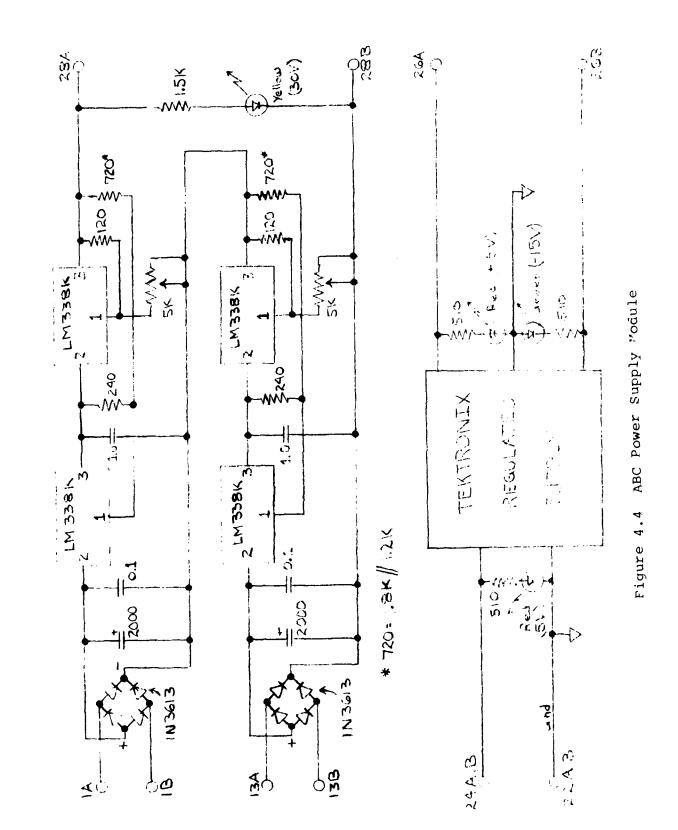

- Figure 4.4 ABC Power Supply Module

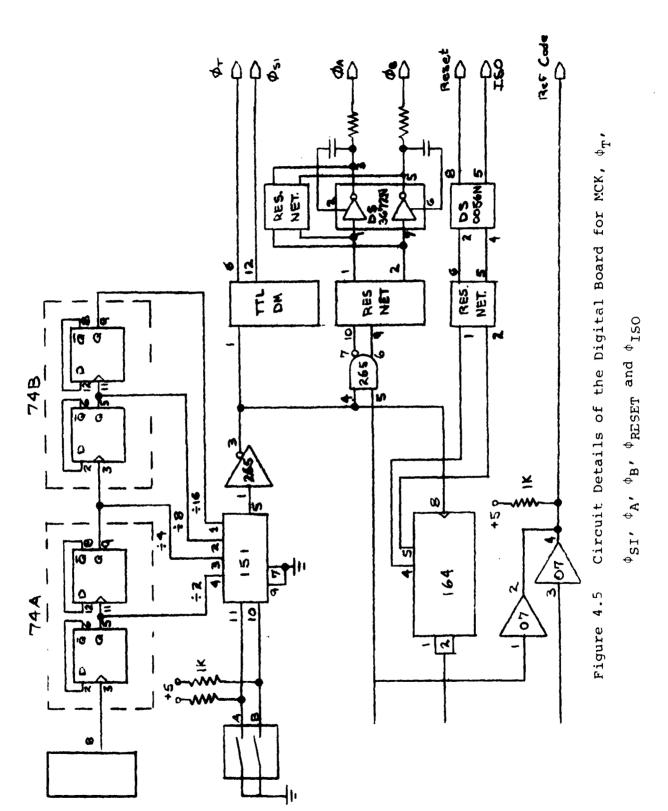

- Figure 4.5 Circuit Details of the Digital Board for MCK,  $\phi_{m}$ ,

$\phi_{SI}, \phi_{A}, \phi_{B}, \phi_{RESET}$  and  $\phi_{ISO}$

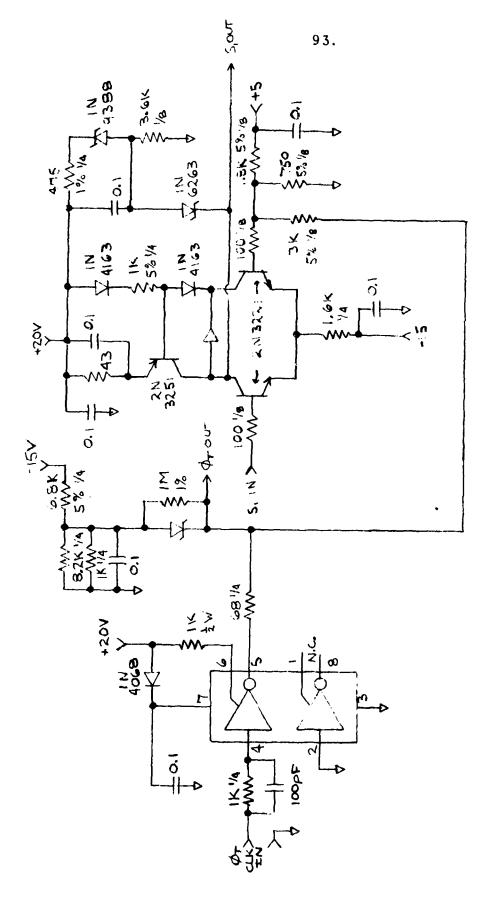

Figure 4.6a Driver Circuit for  $\phi_{T}$  and  $\phi_{ST}$

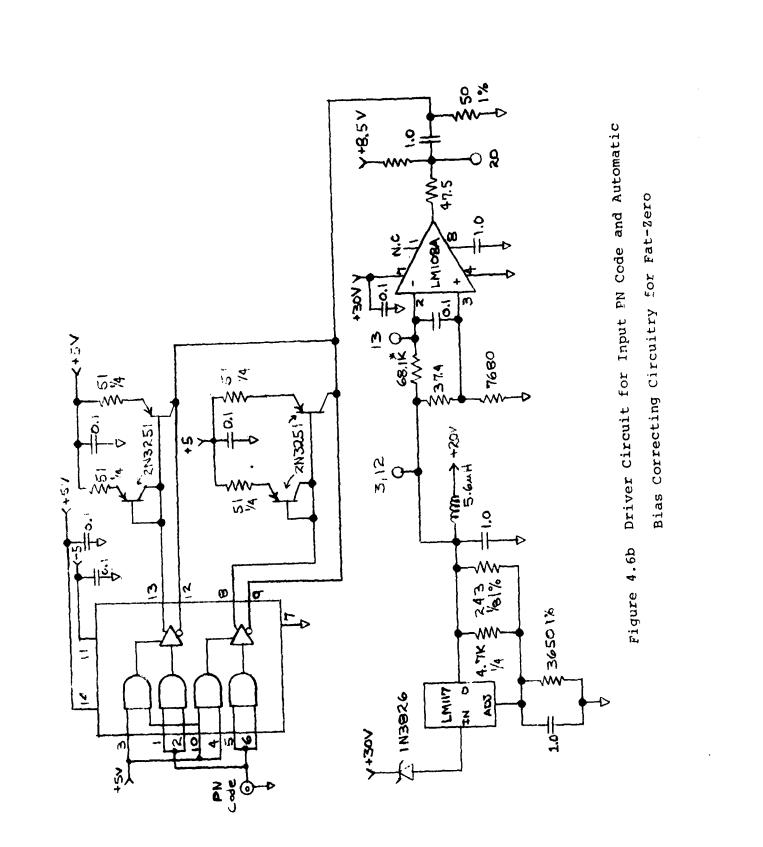

Figure 4.6b Driver Circuit for Input PN Code and Automatic Bias Correcting Circuitry for Fat-Zero

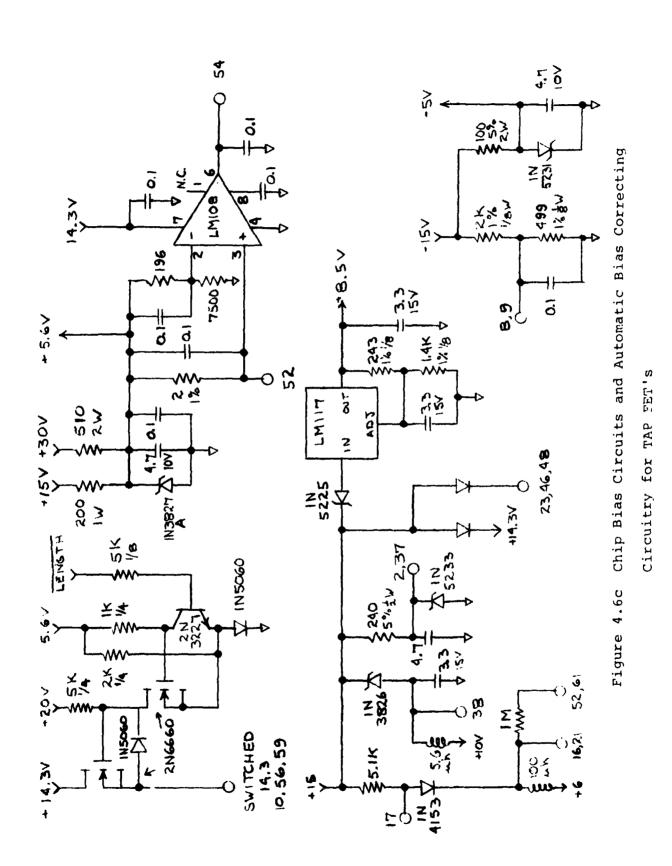

Figure 4.6c Chip Bias Circuits and Automatic Bias Correcting Circuitry for TAP FET's

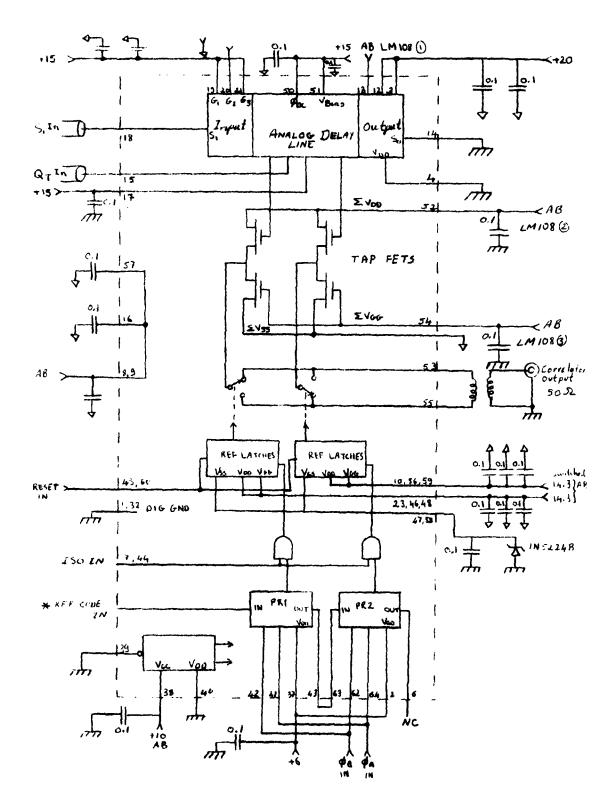

Figure 4.7 Simplified Representation of the ABC Chip

Figure 4.8 Microprocessor-ABC Interface

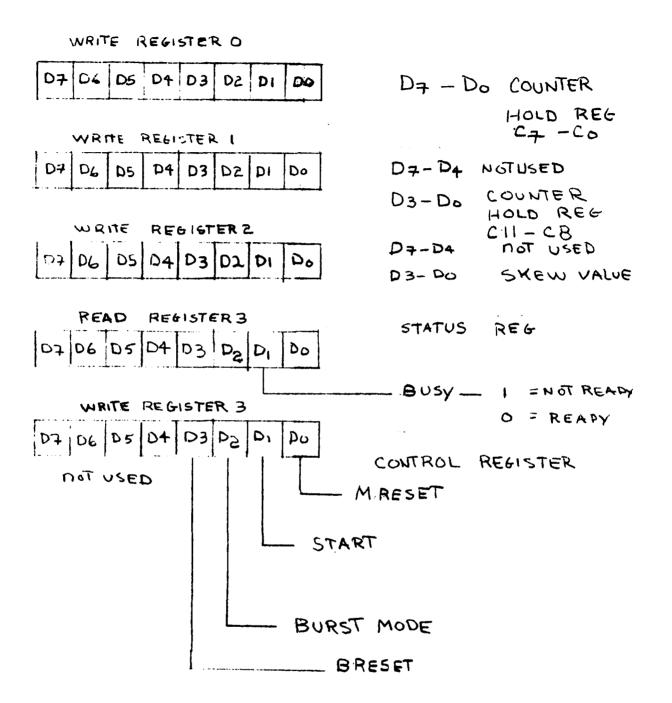

- Figure 4.9 The Four Registers in the Microprocessor-ABC Interface

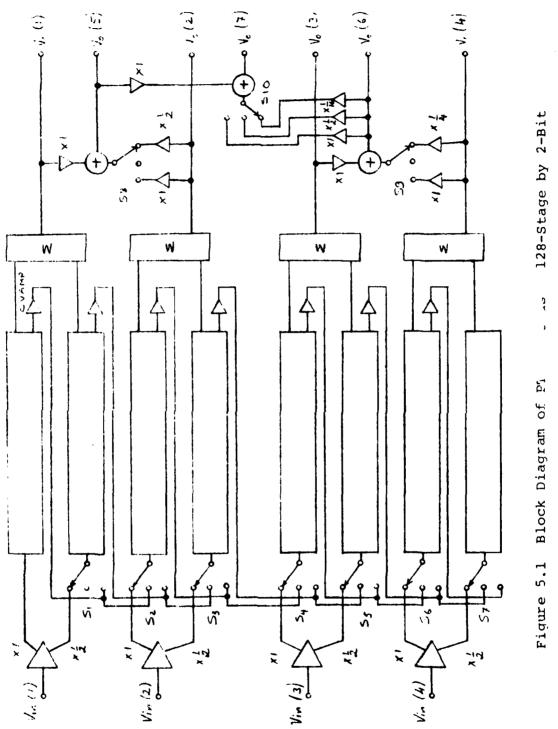

- Figure 5.1 Block Diagram of PTF Used as a 128-Stage by 2-Bit Filter

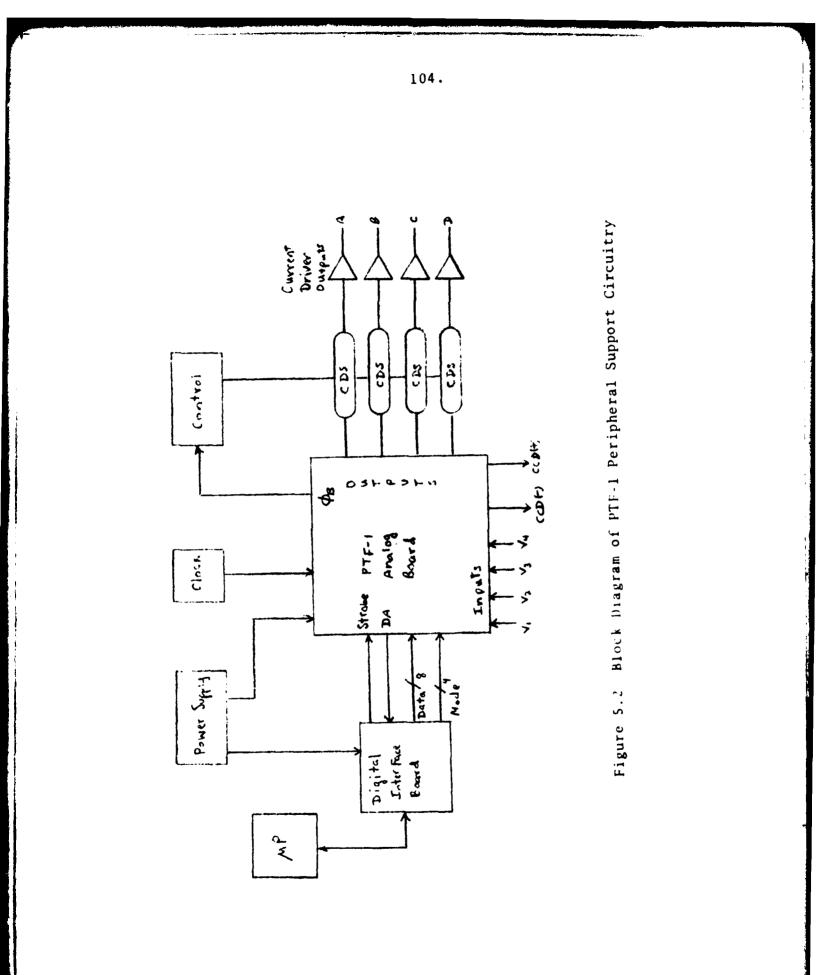

- Figure 5.2 Block Diagram of PTF Peripheral Support Circuitry

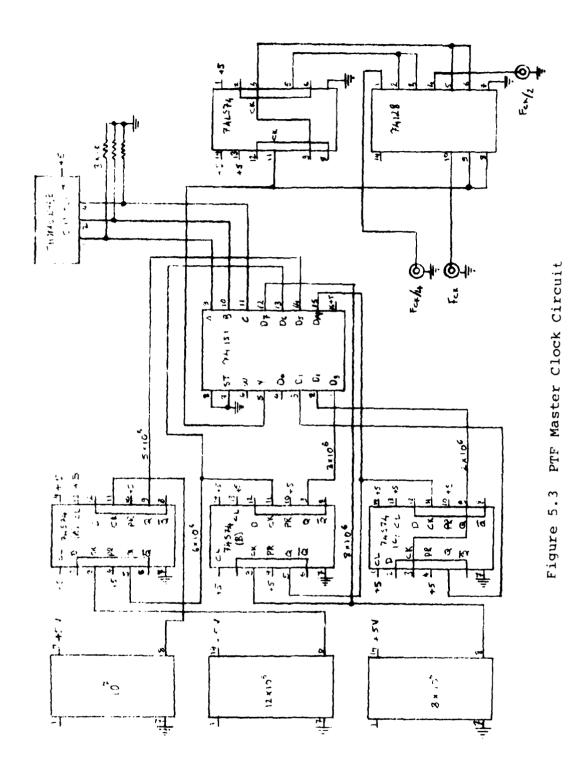

- Figure 5.3 PTF Master Clock Circuit

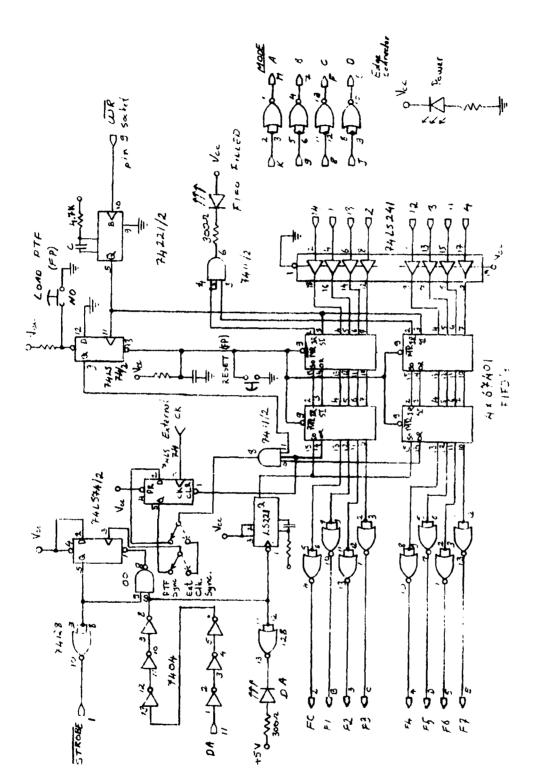

- Figure 5.4 PTF Interface with DMA

- Figure 5.5 PTF Chip Pinout Diagram

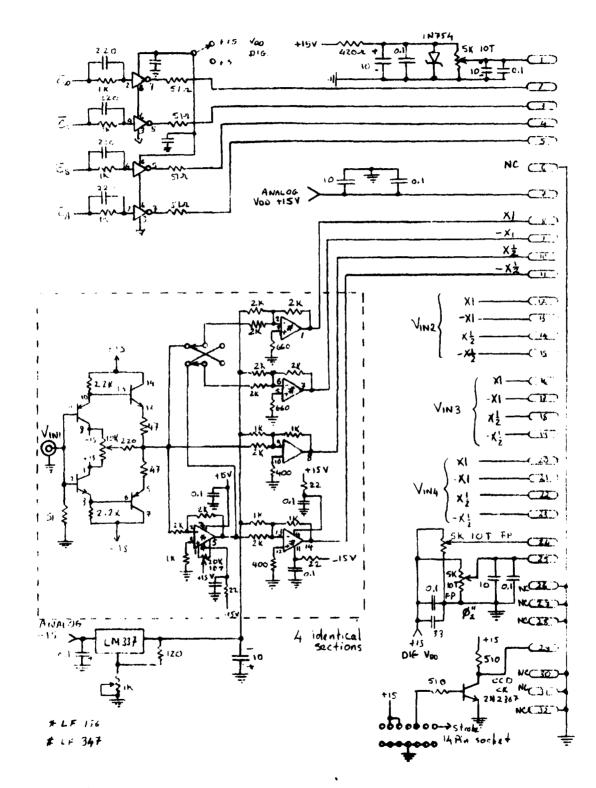

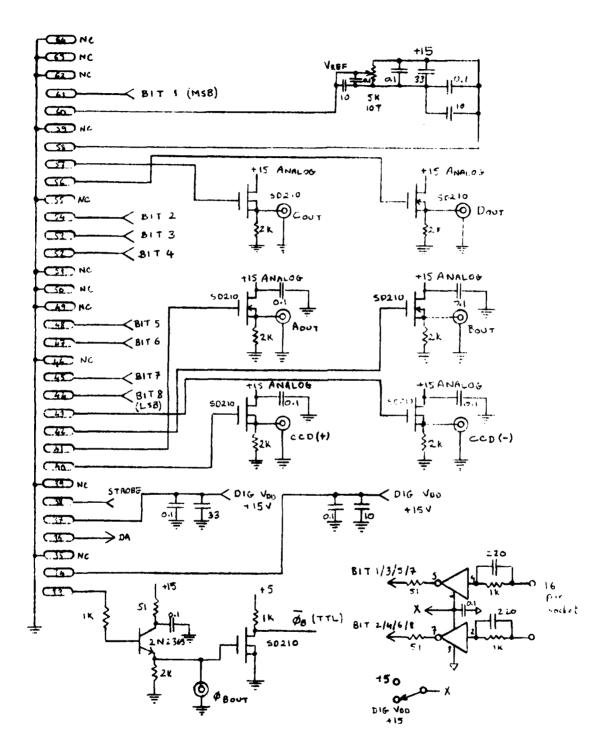

- Figure 5.6a PTF Chip DC Board Peripheral Circuitry

- Figure 5.6b PTF Chip DC Board Peripheral Circuitry

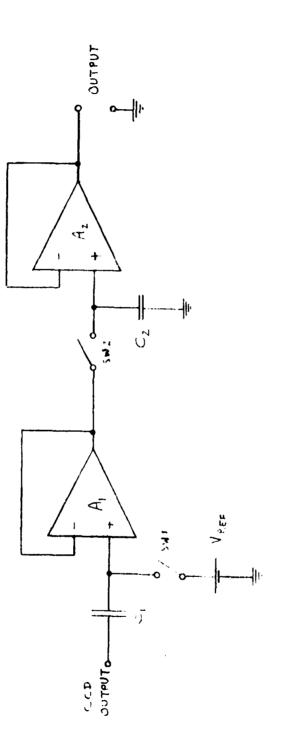

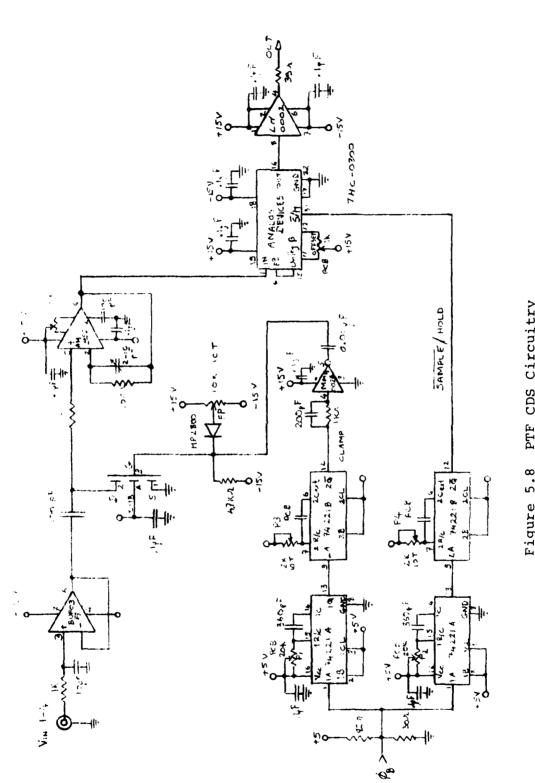

- Figure 5.7 Simplified CDS System

- Figure 5.8 PTF CDS Circuitry

- Figure 6.1 Circuit Diagram for the Signal Generator

- Figure 6.2 Timing Diagram for the Signal Generator Circuitry

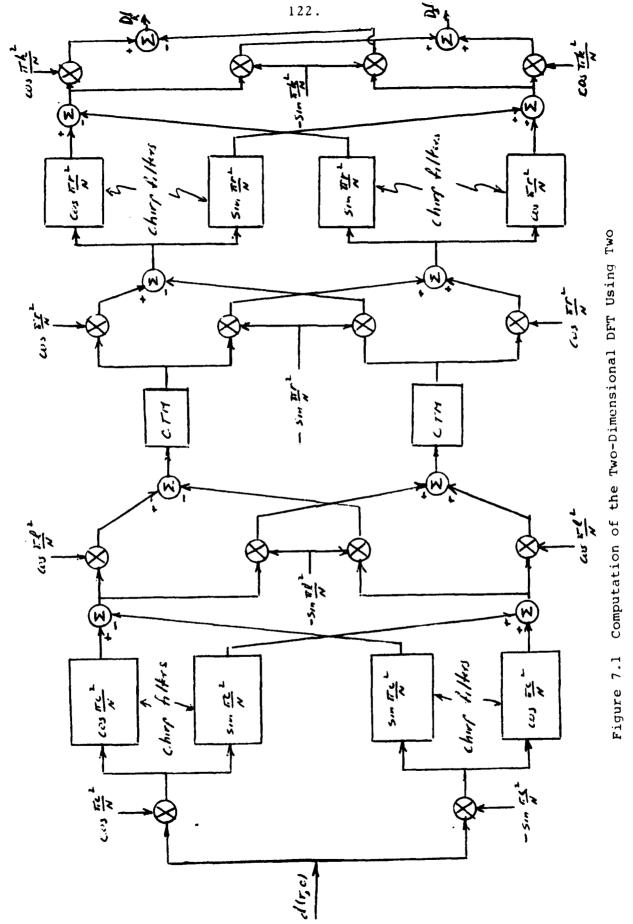

- Figure 7.1 Computation of the Two-Dimensional DFT Using Two Chirp-z Transformers and Two CTM's

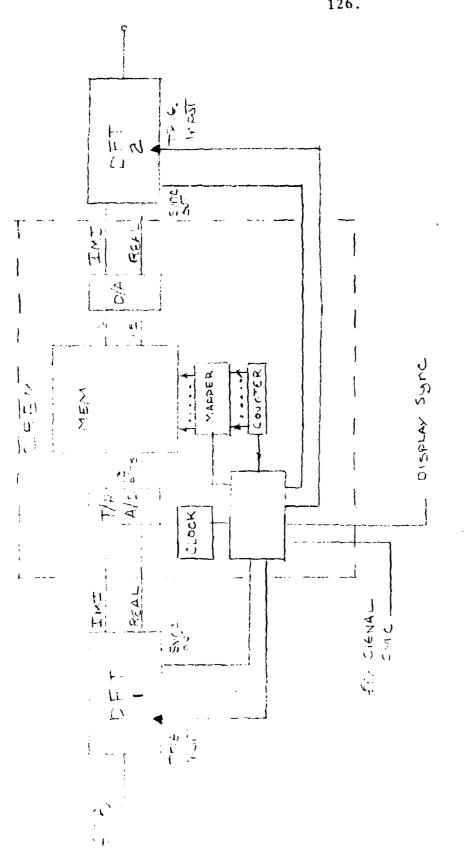

- Figure 7.2 General Block Diagram of CREM

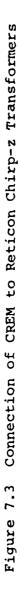

- Figure 7.3 Connection of CREM to Reticon Chirp-z Transformers

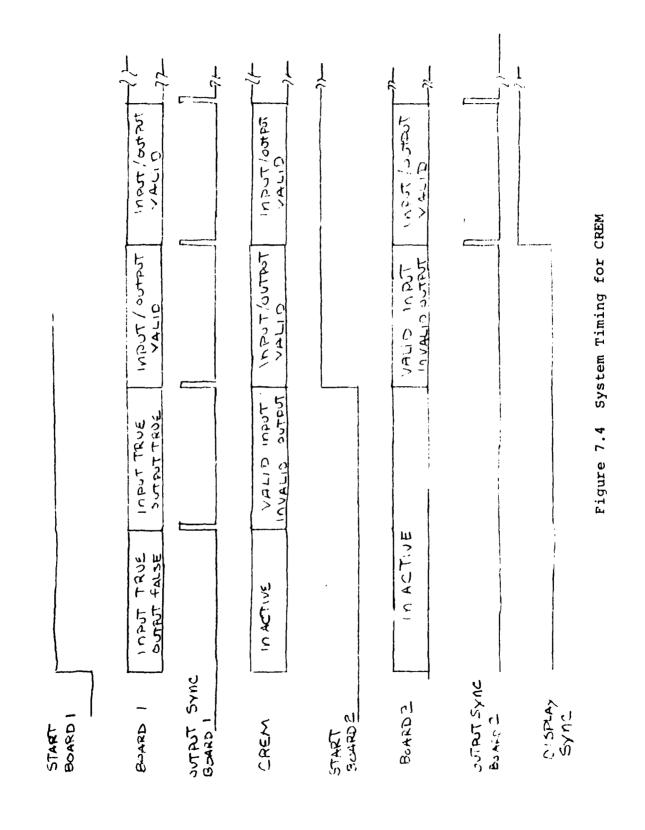

- Figure 7.4 System Timing for CREM

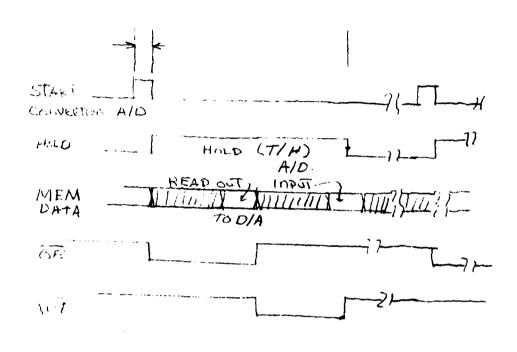

- Figure 7.5 Memory Timing for CREM

#### 1. Introduction

This program involved the development of two high-speed sampled analog signal processing modules based on charge-coupled device (CCD) technology. A microprocessor serves as the controller for the CCD modules. Under program control, each module performs a number of sampled analog signal processing functions, such as correlation, filtering, synchronization, integration and Fourier transformations. The basic building blocks for he modules are the following CCD's.

- (a) A 1,024-tap programmable transversal filter (PTF) nine possible configurations

- (b) A 512-tap analog-binary correlator (ABC)

- (c) A refreshable sampled analog recirculating memory (RSAM)

- (d) A two-dimensional memory, called a corner turning memory (CTM)

- (e) A Reticon R5601 chirp-z transform device.

One of the two signal processing modules is designed to handle sampled analog line data. That is, it is capable of computing quantities of the form

$$y_k = \sum_{n=1}^{N} a_{k-n} b_n$$

where the sequence  $\{a_n\}$  represents a set of N samples of the input signal and  $\{b_n\}$  represents a reference vector consisting of N points. This type of computation is encountered in performing correlation, filtering and synchronization. In addition,

the module has the capability of performing integration. The second signal processing module handles two-dimensional, arrayformatted data. That is, it is capable of performing twodimensional signal processing operations such as filtering, correlation and Fourier transforms.

The general configuration for the sampled analog signal processing system that was designed is illustrated in Figure 1.1. The CCD signal processing module is controlled by the microprocessor through a digital interface. In order to demonstrate that the CCD signal processor is performing its specified functions, it was necessary to also implement an analog signal generator which provides the analog input to the CCD signal processing module. The microprocessor is programmed to control the signal generation in the analog signal generator. Noise may be added to the signal from the signal generator and the combined signal is the input to the CCD signal processing module.

The microprocessor selected to serve as the controller is the Zilog 2-80. For the development of software, the microprocessor was augmented with a dual-floppy disk and a DECWRITER IV terminal.

There are two CCD's that have a d\_gital interface and, thus, lend themselves to microprocessor control. One is the analog/ binary correlator (ABC) which is a 512-tap (transversal) delay line with 1-bit (<u>+</u>1) digitally controlled tap weights. The second device is a programmable transversal filter (PTF) which consists of eight 128-tap delay line sections that may be

interconnected in nine different modes. The 1-bit tap coefficients and the mode are digitally selected. Thus, the tap coefficients for the ABC and the PTF and the mode for the PTF are controlled by means of the microprocessor.

In order to interface the microprocessor to the ABC and the PTF, it was necessary to design and construct interface circuitry. This circuitry was designed and mounted on a single printed circuit board that is connected to the microprocessor chassis. A direct memory access (DMA) device is used for the purpose of achieving high-speed data transfer from the microprocessor to the PTF and the ABC. The DMA is also used to transfer the digital signal from the microprocessor to the input of the signal generator. A functional block diagram of the system is shown in Figure 1.2.

Aside from the ABC and the PTF, the other sampled analog CCD's have no programmability features. The only potentially interesting connection between these devices and the microprocessor is to feed the output of each device back to the microprocessor via an A/D converter.

The ABC, PTF, RSAM and CTM were provided as GFE. In addition to these devices we purchased two RETICON boards which employ a pair of CCD transversal filters to perform a discrete Fourier transform via the chirp Z-transform algorithm. The line formatted CCD module and the array formatted (two-dimensional) CCD module are to be configured from interconnection of these basic CCD building blocks.

In the following discussion, we briefly describe each of the devices and then consider number of potentially interesting interconnections of the devices. The remainder of the report describes the software and hardware developments performed under this contract.

#### Refreshable Sampled Analog Memory (RSAM)

The RSAM is a CCD recirculating delay line with the feature that first-order charge transfer losses are recovered and compensated for in the device. The refresh feature allows one to circulate the signal as many as 1,000 times before the signal begins to show some deterioration. The refreshing operation is made possible by following each signal sample by a fixed (trailing) bias signal. The first-order charge transfer losses are collected by the trailing bias charge and the two signals are periodically recombined. Thus, an RSAM with 1,024 sample stages will accommodate 512 signal samples.

Figure 1.3 illustrates a block diagram of the device. In addition to its refresh feature, the device has a nondestructive readout (NDRO) and a pedestal removal feature (dark current subtractor). The latter allows one to remove a fixed amount of charge from each signal sample circulating in the delay line as it passes through this point in the device.

The RSAM is especially suitable for performing coherent integration by simply adding or merging the charges corresponding to the input signal samples with the corresponding charges circulating in the delay line. In order to suppress the buildup of

DC encountered in coherent integration, the pedestal removal feature can be used. In addition, the device may be used as a simple recirculating delay line or buffer for a set of 512 signal samples.

Support circuitry was constructed for the RSAM and reported in the Interim Report. The circuitry allows us to clock the RSAM at frequencies of  $0.625 \times 2^{n}$  MHz, where n = 0,1,2,3,4. We have tuned and operated the device at clock rates of 1.25 MHz, 2.5 MHz and 5.0 MHz. It operated very well at 1.25 MHz and 2.5 MHz, but its operation at the 5.0 MHz clock rate was marginal. The major problem at 5.0 MHz appears to be the layout of some components in the support circuitry. A modification of the layout of the circuitry will very likely extend the range of operation to 5.0 MHz.

#### Analog-Binary Correlator (ABC)

The ABC is a 512-stage CCD delay line with a corresponding 512-bit digital shift register reference signal. A block diagram of the ABC is shown in Figure 1.4. The binary reference is loaded into the shift register and latched. When the bit in the latch is a 1, the signal in the corresponding tap is routed to the positive output signal while if the bit is zero, the corresponding signal is routed to the negative output signal as shown in Figure 1.4. Thus, the device can be used as a correlator in a pseudo-noise (PN) spread spectrum communication system or for synchronization purposes. The length of the binary reference signal is variable and selectable over the range from

#### 64 to 512 bits.

The circuitry for the ABC has been constructed and it is described in Section 4 of this report.

#### Programmable Transversal Filter (PTF)

The PTF consists of eight sections of 128-tap binaryweighted transversal filters. The eight sections can be connected in nine different ways or modes to realize a variety of different types of correlators and filters. Table 1.1 illustrates the nine different modes and the corresponding four-bit binary representation which allows the mode to be selected automatically.

For example, Figure 1.5 illustrates the device as a 128-tap filter with 8-bit coefficient accuracy. In this configuration, the device is suitable as an FIR (finite-duration impulse response) filter with characteristics of the following types: lowpass, bandpass, band-elimination, Hilbert transformer and

#### Table 1.1

## Filter Configuration Versus Input Select Word

| Filter Configuration |                     | Mode   |   | Input Word |   |   |  |

|----------------------|---------------------|--------|---|------------|---|---|--|

|                      |                     |        | A | 8          | Ç | D |  |

| (1)                  | 1024-stage by 1-bit | Single | 1 | 0          | 0 | 0 |  |

| (2)                  | 512-stage by 2 bits | Single | 0 | 1          | 0 | 0 |  |

| (3)                  | 256-stage by 4 bits | Single | 1 | ۱          | 0 | 0 |  |

| (4)                  | 128-stage by 8 bits | Single | 0 | 0          | I | O |  |

| (5)                  | 512-stage by 1 bit  | Dual   | 1 | 0          | ł | 0 |  |

| (6)                  | 256-stage by 2 bits | Dual   | 0 | 1          | 1 | 0 |  |

| (7)                  | 128-stage by 4 bits | Dual   | 1 | 1          | 1 | 0 |  |

| (8)                  | 256-stage by 1 bit  | Quad   | 0 | 0          | 0 | ١ |  |

| (9)                  | 128-stage by 2 bits | Quad   | 1 | 0          | 0 | 1 |  |

differentiation. It may also be used in this mode as an adaptive filter for equalization or notch filtering. In the other modes the device is suitable for performing correlation and synchronization in PN spread spectrum communication systems, radar systems and navigation or ranging systems.

The support circuitry for the PTF has been constructed. It is described in Section 5 of this report.

#### Corner Turning Memory (CTM)

The CTM is a two-dimensional CCD memory which is appropriate for performing row-column transformations on two-dimensional

array data. Figure 1.6 illustrates a block diagram of the CTM. The device has been designed and fabricated as a  $32 \times 32$  memory and a  $64 \times 64$  memory. Its range of frequencies for good operation is 1 MHz to 7 MHz.

The CTM is especially suitable for array-type signal processing operations, such as in the computation of the twodimensional discrete Fourier transform (DFT) and for Doppler sorting in radar applications. Section 7 describes the use of the CTM in the computation of the two-dimensional DFT.

#### Reticon Chirp-z Transform Device

The Reticon chirp-z transform consists of two 512-tap CCD transversal filters with preset tap weights whose values are of the form  $\cos \pi n^2/N$  and  $\sin \pi n^2/N$  where N = 512 and n = 0,1,...,511.

Figure 1.6 Functional Block Diagram of CTM

The CCD's are used to implement the computation of 512point DFT using the chirp-z transform algorithm. A block diagram illustrating the computations performed in the algorithm is shown in Figure 1.7.

The Reticon devices have a dynamic range of 60 dB and a frequency resolution in the DFT of  $F_S/512$ , where  $F_S$  is the sampling frequency. The latter is limited to below 200 kHz by the support circuitry used to implement the DFT computation.

Section 7 of this report describes the use of the Reticon device in combination with the CTM to implement a twodimensional DFT.

#### Some Potential Interconnections

The signal processing modules for handling line formatted and array formatted data were designed to have the capability of performing correlation, synchronization, moving target indication (MTI) and general programmable filtering such as notch filtering and adaptive equalization. Toward this end we designed a line data module which consists of two RSAM's, one of which can be used as an integrator and the other as a long delay line, a PTF, an ABC and a Reticon R5601. The various configurations of these devices are controlled by a number of programs stored in the microprocessor.

Figure 1.8 illustrates a configuration in which two RSAM's and an ABC are connected together to yield a module that can perform correlation or synchronization of the same input signal

with a number of different pseudo-noise (PN) reference signals, and followed by coherent integration (reference 1).

Another possible configuration is illustrated in Figure 1.9. Here, the PTF is used as an adaptive notch filter and the RSAM serves as a delay line. The Reticon device performs a spectral analysis of the input signal and passes the spectral coefficients to the microprocessor through an A/D. On the basis of the spectral estimate, a notch filter impulse response is designed in the microprocessor and the coefficient data is fed to the PTF for realizing the notch filter.

A configuration appropriate for performing two-dimensional, array-type signal processing is shown in Figure 1.10. In this case two CTM's and two Reticon 5601 devices are interconnected so as to perform a two-dimensional discrete Fourier transform (DFT). The operation of this configuration is described in some detail in Section 7.

Figure 1.11 illustrates yet another configuration, using a PTF and two CTM's. With the various modes available in the PTF, this signal processing configuration can be used for multichannel digital communications, multiple correlation, synchronization, and image processing (Reference 1).

Several other configurations were considered in the course of this contract but for the sake of brevity, these will not be described here. Lack of time and manpower prevented us from implementing the various configurations described above.

;

i

23.

Figure 1.10 A Configuration of CCD's for Computing a Two-

Dimensional DFT

. . .

Signal Processing

i. I:

### 2. Software Development for the Z-80 Microprocessor

The Z-80 microprocessor configures and controls the signal processing modules. It is also a source of selectable test data to exercise the CCD's described in Section 1.

Most of the software written for the 2-80 microprocessor has been done in FORTRAN. This was the case for programs involving microprocessor functions that do not demand great speed and tight coding. Such programs are used primarily for set-up, i.e., interrogation, parameter selection, and data transformation appropriate for loading the PTF. For microprocessor activities that do demand high speed and tight coding, such as signal generation and DMA control functions and transfers, we programmed in assembly language. The benefits of this approach are primarily:

- (a) easier interactive operator control

- (b) avoidance of some assembly language housekeeping functions, such as, stack register set-up and load point selection

- (c) availability in FORTRAN of almost all logical operations present in assembly language

- (d) ability to manipulate 8-bit byte variables

- (e) easier linking of main program with subroutines.

Some minor benefits are surrendered when adopting the FORTRAN framework. Whereas, working under control of the object time debugger affords the programmer access to each memory location and the ability to set breakpoints at any instruction, this FORTRAN has no such non-invasive debugging accessories. To

overcome this we wrote some binary and hexadecimal print-out routines. Since these are subroutines, they are easily invoked and their removal from a running program is no trouble.

#### Description and List of Programs

The following is a list of the programs and a brief description of each.

Routine: BINPRT

Language: FORTRAN

Purpose: Utility

This subroutine accepts as input a one-dimensional stream, and prints the result on the terminal. The order of the printed data is from low order bit to high order bit for each byte. Bytes are outputed in succession, up to 128 bits (16 bytes) per line.

| PRINT E  | INPRT.S                           |

|----------|-----------------------------------|

| PRINT BI | NPRT.S                            |

|          | SUBROUTINE BINPRT(SRC, COUNT)     |

| С        | VERSION 1,12/15/81                |

| _        | BINARY PRINT - 128 BITS TO A LINE |

| С        |                                   |

|          | IMPLICIT INTEGER (A-Z)            |

|          | INTEGER PRT(128),HD(16)           |

|          | LOGICAL SRC(1)                    |

|          | DO 5 I = 1, 16                    |

| 5        | HD(I)=8*I                         |

| 5        | WRITE (1,1001),(HD(I),I=1,16)     |

|          |                                   |

| 1001     | FORMAT(' '16I8)                   |

|          | L=O                               |

|          | .t=1                              |

| 10       | W=SRC(J)                          |

| 10       |                                   |

|          | IF(W .LT. 0) W=256+W              |

|          | T=1                               |

|          | DO 40 K=1,8                       |

|          | L=L+1                             |

|          | PRT(L)≠0                          |

|          |                                   |

|          | IF((W .AND. T) .NE. 0) PRT(L)=1   |

| C     | WRITE (1,2000),K,L,W,T,PRT(L)           |

|-------|-----------------------------------------|

| 00000 | FORMAT(/_/,5(2X,I8))                    |

| 49    | T=T+T                                   |

|       | IF(L .LT. 128) GD TO 60                 |

|       | WRITE(1,1000) (PRT(M),M=1,128)          |

| 1000  | FORMAT(1H ,128I1)                       |

|       | I. ≃0                                   |

| 60    | IF(J .EQ. COUNT) GO TO 90               |

|       | J=J+1                                   |

|       | GO TO 10                                |

| 90    | IF(MOD(J,16) .EQ. 0) GO TO 100          |

|       | <pre>WRITE(1,1000) (PRT(M),M=1,L)</pre> |

| 100   | RETURN                                  |

|       | END                                     |

| ×     |                                         |

Routine: FILCOF

Language: FORTRAN

Purpose: Generate filter coefficients

This subroutine generates binary coefficients to be loaded on to the programmable filter. A total of 1,024 bits are always produced.

The routine is interactive. The operator is requested to input binary strings of up to 24 bits in length and the number of repetitions of the submitted string. Requests are repeated until a 1,024-bit string is produced or until a null string is requested. The latter terminates the process and '0' filler bits are appended until a count of 1,024 is reached.

The program takes care of all counting.

| PRINT      | FILCOF.S                                                          |

|------------|-------------------------------------------------------------------|

| PRINT      | FILCOF.S                                                          |

|            | SUBROUTINE FILCOF(FILT)                                           |

| C          | 6/2/82. VERSION 1                                                 |

| <b>C</b> : | THIS SUBROUTINE LETS THE OPERATOR SPECIFY THE FILTER COEFFICIENTS |

| <b>C</b> : | AS BINARY STRINGS. THE STRING AND ITS REPETITIONS ARE INPUTS.     |

| נ          | 1024 BITS WILL ALWAYS BE PRODUCED. ZERO FILLER BITS WILL BE       |

PLACED AT THE END. С IMPLICIT INTEGER (A-Z) LOGICAL FILT(1), STRING(24), INS(8), BLANK, ONE, ZERO DATA INS/2'80',64,32,16,8,4,2,1/ DATA C128/128/,C8/8/,BLANK// //,ZERO//0//,ONE//1// DATA C24/24/ INITIALIZE C DO 30 K=1,C128 FILT(K)=030 CONTINUE J=1 K = 1WRITE(1,1000) FORMAT( ' THIS PROCESS GENERATES THE COEFFICIENTS TO BE SENT TO '/ 1000 ' THE FILTER. THERE WILL ALWAYS BE 1024 BITS. THOSE UNSPECI- 1/ 1 ' FIED AT THE END WILL BE ZEROS. EACH SUB-STRING MAY BE UP TO '/ 2 / 24 BITS LONG. THE REPETITIONS OF THIS STRING MUST BE A POS- 1/ 3 ITIVE NUMBER. A NULL SUB-STRING OR A REPETITION OF 0 ENDS 17 4 / PROCESSING.(/) 5 WRITE (1,1001) 40 FORMAT( ' PLEASE ENTER A BINARY STRING OF UP TO 24 BITS () 1001 READ(1,1002),(STRING(I),I=1,24) 1002 FORMAT(24A1) DETERMINE LENGTH OF STRING C DO 70 IX=1,CZ4 BIT =STRING(IX) IF(BIT .EQ. BLANK) GO TO 100 STRLEN=IX IF((BIT.NE. ONE) .AND. (BIT.NE. ZERO)) GO TO 90 CONTINUE 70 GO TO 120 WRITE(1+1003) 90 FORMAT(' INVALID CHARACTER.') 1003 GO TO 40 STRLEN NOW HAS STRING LENGTH С 100 IF(IX .EQ. 1) GD TD 500 NOW OBTAIN REPETITIONS C WRITE(1,1004) 120 FORMAT( ' HOW MANY TIMES SHALL THIS STRING BE REPEATED? 13 1004 READ (1,1005) REP 1005 FORMAT(14) IF(REP .EG.0) GD TO 500 NOW PLACE BITS INTO DESTINATION STRINGS С DO 180 IRX=1,REP SINGLE STRING CONTROL C DD 160 JX=1,STRLEN IF(STRING(JX) .EQ. ZERO) GO TO 130 FILT(J)=FILT(J) .OR. INS(K) IF(K ,EQ. C8) GD TO 150 130 K = K + 1GO TO 160

| 150 | IF(J .EQ. C128) GO TO 500 |

|-----|---------------------------|

|     | J=J+1                     |

|     | K = 1                     |

| 150 | CONTINUE                  |

| C.  | CHECK REPETITIONS         |

| 180 | CONTINUE                  |

|     | GO TO 40                  |

| 500 | RETURN                    |

|     | END                       |

| •/  |                           |

7.

Routine: RNGEN Language: Z-80 Assembly Purpose: Generate random bits

This subroutine generates maximal length shift register sequences for polynomials up to degree 31. It is in a form to be used as a FORTRAN subroutine.

A set-up entry uses the degree of the polynomial, initial state of the shift register and the tap positions to initialize the program.

A second entry is called to generate the pseudo-random bit stream. This entry requires the number of 8-bit bytes to be generated, up to 128, and the destination location. Successive entries to this second entry proceed from the conditions in effect when this part of the routine was last used.

If it is desired to institute a new set of initial conditions the first entry must be used again.

PRINT RNGEN.S FRINT RNGEN.S ; TITLE "MAXIMAL LENGTH SRS,TO DEGREE 31" ;THE INITIAL STATE OF THE SHIFT REGISTER WILL BE IN 'DATA'

| ;THE P(<br>;VERSI) | DLYNOMIAL<br>DN 1,6/18<br>GLOBAL | 781, DO NOT INCR      | Y',BOTH RIGHT JUSTIFIED.<br>Ement HL |

|--------------------|----------------------------------|-----------------------|--------------------------------------|

| SRSET              | NOP                              |                       | USE ONE BYTE ONLY                    |

|                    | LD<br>LD                         | A,(HL)<br>(DEG),A     | STORE POLY DEGREE                    |

|                    | ĹĎ                               | (LODAT),BC            | SAVE PTR TO INITIAL STATE OF S.R.    |

|                    | EX                               | DE, HL                |                                      |

|                    | LD                               | DE,POLY               |                                      |

|                    | LD                               | BC,4                  |                                      |

|                    | LDIR                             |                       |                                      |

|                    | LD<br>LD                         | HL,(LODAT)<br>DE,DATA |                                      |

|                    |                                  | BC,4                  |                                      |

|                    | LDIR                             | 00)4                  | POLY AND INITIAL STATE NOW SET       |

|                    | XOR                              | A                     | ZERO THE 5TH BYTE OF THE POLY        |

|                    | LD                               | (POLY+4),A            |                                      |

|                    | LD                               | C,0                   | ;C WILL HAVE MMOD(DEG,8)             |

|                    | LD                               | A, (DEG)              | ;POLYNOMIAL DEGREE                   |

| RPT1               | CP<br>JP                         | 8<br>M,INJP           |                                      |

|                    | SUB                              | 8                     |                                      |

|                    | INC                              | C                     |                                      |

|                    | JR                               | RPT1                  | REG A HAS COUNT OF BITS LEFT         |

| INJP               | LD                               | 8,0                   |                                      |

|                    | INC                              | C                     |                                      |

|                    | INC                              | С                     | LOOP COUNT IS ACTUAL COUNT           |

|                    | LD                               | HL, INLOOP            |                                      |

|                    | LD                               | (HL),C                |                                      |

|                    | DEC<br>LD                        | C<br>HL,DATA+4        | JUNDO 3RD INSTRUCTION UP             |

|                    | CP                               | 0                     | iclear carry flag                    |

|                    | SBC                              | HL,BC                 | Julea Call, Lian                     |

|                    | LD                               | (STRT),HL             |                                      |

|                    | LD                               | E-1                   | SET UP EXTRACTOR                     |

| INLP               | CP                               | 0                     |                                      |

|                    | JR                               | Z,SETXT               |                                      |

|                    | SLA<br>DEC                       | E<br>A                |                                      |

|                    | JR                               | INLP                  |                                      |

| SETXT              | LD                               | HLFEXT                |                                      |

|                    | LD                               | (HL),E                |                                      |

|                    | RET                              |                       | ;END OF INITIALIZATION               |

|                    |                                  | LLED BY CALL(BYT      | ES,DESTINATION )                     |

| RNGEN              | NOP                              | A                     |                                      |

|                    |                                  | A,(HL)<br>(LEN),A     | PATER TO BE GENERATED                |

|                    | LD<br>PUSH                       | DE                    | BYTES TO BE GENERATED                |

|                    | POP                              | IY                    | POINTS TO DELIVERY VECTOR            |

|                    | LD                               | A, BOH                | FIFTH BYTE WILL GET NEW BITS         |

|                    | LD                               | (DATA+4),A            |                                      |

|                    | LD                               | A, (LEN)              | COUTPUT DATA COUNTER IN REG. C       |

|                    | LD                               | C,A                   |                                      |

| NEWBIT              |                | E,0<br>H,0                       | ;START 4 CYCLESTO GET NEXT OUT BIT<br>;WILL HAVE LAST CARRY BIT |

|---------------------|----------------|----------------------------------|-----------------------------------------------------------------|

|                     | LD<br>LD<br>LD | HL,INLOOP<br>B,(HL)<br>IX,(STRT) |                                                                 |

| WSHFT               |                | D,(IX+0)<br>A,(IX+5)             | PROCESS NEXT BYTE                                               |

|                     | AND            | D                                | DATA ANDED WITH POLY TO REG A                                   |

|                     | XOR            | E                                | ;'1' BITS IN SAME POSITION CANCEL<br>;INTERIM RESULTS TO REG E  |

|                     | LD<br>XOR      | E,A<br>A                         | SET TO SAVE NEXT CARRY BIT                                      |

|                     | RR             | H                                | FOLD CARRY TO CY                                                |

|                     | RR             | D                                | SHIFT DATA BIT O TO CY REG                                      |

|                     | ADC            | A-A                              | SAVE CARRY IN                                                   |

|                     | LD             | H,A                              | FREG H                                                          |

|                     | LD             | (IX+0),D                         | STORE SHIFTED BYTE                                              |

|                     | INC            | IX                               | CARRY BITS NOT AFFECTED                                         |

|                     | D JNZ<br>RR    | WSHFT<br>H                       | WHEN 8 BITS DONE CARRY OCCURS                                   |

|                     | JR             |                                  | FIF 8 BITS NOT DONE REPEAT                                      |

|                     | LD             | (IY+0),D                         | REGISTER D HAS NEW BYTE                                         |

|                     | INC            | IY                               |                                                                 |

|                     | LD             | A,80H                            | ;INITIALIZE                                                     |

|                     | LD             | (DATA+4),A                       |                                                                 |

| <i>c</i> . <b>n</b> | DEC            | C                                |                                                                 |

| SUP                 | XOR<br>XOR     | A<br>E                           | DETERMINE PARITY IN REG F                                       |

|                     | JP             | PE,NUTH                          | AND SET HIGH ORDER DATA BIT                                     |

|                     | LD             | IX,(STRT)                        | IN HIGH ORDER BYTE                                              |

|                     | LD             | A, (EXT)                         | VIN MICH ONDER OTHE                                             |

|                     | OR             | (1X+0)                           |                                                                 |

|                     | LD             | (IX+0),A                         |                                                                 |

| NUTH                | XOR            | A                                | SEE IF OUTPUT IS DONE                                           |

|                     | ADD            | A,C                              |                                                                 |

|                     | JP             | NZ,NEWBIT                        |                                                                 |

|                     | RET            | _                                |                                                                 |

| DATA                | DEFS           | 5                                | JOATA SHIFT REGISTER PLUS ONE BYTE                              |

| POLY<br>DEG         | DEFS<br>DEFB   | 5<br>-1                          | ;POLYNOMIAL COEFFICIENTS<br>;DEGREE OF POLYNOMIAL               |

| LEN                 | DEFB           | 4                                | NUMBER OF OUTPUT BYTES                                          |

| EXT                 | DEFB           | 1                                | LEADING BIT THAT IS SET                                         |

| STRT                | DEFW           | 2                                | STARTING ADDRESS FOR LOOP                                       |

| INLOOP              | DEFB           | -3                               | FINNER LOOP(BYTES IN POLY)                                      |

| LODAT               | DEFS           | 2                                | PTR TO INITIAL STATE OF S.R.                                    |

|                     | END            |                                  |                                                                 |

| 7.                  |                |                                  |                                                                 |

ł

| Routine: 1 | HEXPRT |

|------------|--------|

|------------|--------|

Language: FORTRAN

Purpose: Utility

This subroutine converts a one-dimensional array of bytes to a string of ASCII hexadecimal bytes for printing. The leftmost hexadecimal character is followed by the right-most hexadecimal character in the printing format.

Sixteen bytes, 32 hexadecimal characters, are printed on each line.

```

FRINT HEXPRT.S

FRINT HEXPRT.S

SUBROUTINE HEXPRT(HEXB,COUNT)

C CONVERT A VECTOR OF HEX BYTES AND PRINT 16 TO A LINE

C VERSION 1,7/9/81

IMPLICIT INTEGER (A-Z)

LOGICAL HEXB(1), PRT(32), CHAR(16)

DATA CHAR/2'30',Z'31',Z'32',Z'33',Z'34',Z'35',Z'36',Z'37',

1 Z'38', Z'39', Z'41', Z'42', Z'43', Z'44', Z'45', Z'46'/

I = 1

J=1

100

T=HEXB(I)

IF(T .LT. 0) T=256+T

IX = MOD(T, 16) + 1

PRT(J+1)=CHAR(IX)

IX = T/16 + 1

PRT(J)=CHAR(IX)

J=J+2

IF(J .LT. 32) GD TO 140

WRITE (1,1000) (PRT(K),K=1,32)

110

FORMAT(1H ,16(2X,2A1))

1000

J=1

IF(I .EQ. COUNT) GD TD 150

140

I = I + 1

GD TD 100

LST=MOD(COUNT,16)*2

150

IF(LST .EQ. 0) GO TO 160

WRITE (1,1000) (PRT(K),K=1,LST)

RETURN

160

END

%

```

Program: HAFFIL

Language: FORTRAN

Purpose: Test correct loading of output ports and D/A operation through the DMA

This program loads the status words, modes and data to the output ports and devices in order to test the hardware configuration in an orderly manner. After each transfer that changes the system state, the program pauses and permits the engineer to verify that the action occurred. Each action is identified.

The last step causes the DMA to continually feed the D/A through a FIFO. The display can be monitored on a scope.