| 1 | 26 363<br>SSIFIED |   | DBUS AR<br>EGIE-ME<br>WILLIS<br>ECS79-2 | CHITEC1<br>LLON UN<br>ET AL<br>3893 | URE ANI<br>IIV PIT<br>NOV 82 | D REALI<br>Isburgh<br>CMU-RI | ZATION(<br>PA ROB<br>-TR-82- | U)<br>OTICS I<br>13<br>F | INST<br>5/G 9/2 | N | 1/ <b>1</b> | 8    |

|---|-------------------|---|-----------------------------------------|-------------------------------------|------------------------------|------------------------------|------------------------------|--------------------------|-----------------|---|-------------|------|

|   |                   | A |                                         |                                     |                              |                              |                              |                          |                 |   |             |      |

|   |                   |   |                                         |                                     |                              |                              |                              |                          |                 |   |             |      |

|   |                   |   |                                         |                                     |                              |                              |                              |                          |                 |   |             |      |

|   |                   |   |                                         |                                     |                              |                              |                              |                          |                 |   |             |      |

|   |                   |   |                                         |                                     |                              |                              |                              |                          |                 |   |             |      |

|   |                   |   |                                         |                                     |                              |                              | END<br>DATE<br>FILMED        |                          |                 |   |             |      |

|   |                   |   |                                         |                                     |                              |                              | 4 – 83'<br>DTIĈ              |                          |                 |   |             | <br> |

# **Camegie-Mellon University**

| RFI                | PORT DOCUMENTAT                                                                                                 |                                                | READ INSTRUCTIONS                                              |

|--------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------|

| REPORT NUMBER      |                                                                                                                 |                                                | BEFORE COMPLETING FORM                                         |

|                    | TR-82-13                                                                                                        |                                                |                                                                |

| TITLE (and Submite | )                                                                                                               |                                                | S. TYPE OF REPORT & PERIOD COVERS                              |

|                    | RAP1Dbus                                                                                                        |                                                | Interim                                                        |

| Are                | hitecture and Reali                                                                                             | ization                                        |                                                                |

| •                  |                                                                                                                 |                                                | 6. PERFORMING ORG. REPORT NUMBER                               |

| AUTHOR(+)          |                                                                                                                 |                                                | . CONTRACT OR GRANT NUMBER(+)                                  |

|                    | John C. Willis                                                                                                  |                                                | NSF ECS-7923893                                                |

|                    | Dr. Arthur C. Sande                                                                                             | erson                                          |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

|                    | ANIZATION NAME AND ADD<br>e-Mellon Universit                                                                    |                                                | 10. PROSRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS |

|                    | otics Institute                                                                                                 | y                                              |                                                                |

|                    | rgh, PA. 15213                                                                                                  |                                                |                                                                |

| . CONTROLLING OF   | FFICE NAME AND ADDRESS                                                                                          |                                                | 12. REPORT DATE<br>November 1982                               |

|                    | of Naval Research                                                                                               |                                                | ·                                                              |

| Arlingt            | on, VA 22217                                                                                                    | 13. NUMBER OF PAGES<br>82                      |                                                                |

| 4. MONITORING AGE  | INCY NAME & ADDRESS(II di                                                                                       | Illerent from Constalling Office)              | 15. SECURITY CLASS. (of this report)                           |

|                    |                                                                                                                 | UNCLASSIFIED                                   |                                                                |

|                    |                                                                                                                 |                                                | 154. DECLASSIFICATION DOWNGRADING                              |

|                    |                                                                                                                 |                                                | SCHEDULE                                                       |

| S. DISTRIBUTION ST | ATEMENT (of this Report)                                                                                        | ······································         | ······                                                         |

| -                  | Los Statute Art.                                                                                                | anan managana an ang ang ang ang ang ang ang a |                                                                |

|                    | the second se | · · · · · · · · · · · · · · · · · · ·          |                                                                |

|                    | •                                                                                                               |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

| 7. DISTRIBUTION ST | ATEMENT (of the ebetract en                                                                                     | ntered in Black 20, if different tra           | a Report)                                                      |

|                    | ·                                                                                                               |                                                | 2. 26                                                          |

|                    | Approved for publ                                                                                               | lic release; distrib                           | ution unlimited                                                |

|                    | ·                                                                                                               |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

| SUPPLEMENTARY      | Y NOTES                                                                                                         |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

|                    |                                                                                                                 |                                                | • ·                                                            |

|                    |                                                                                                                 |                                                | •                                                              |

| . KEY WORDS (Cont  | inue an reverse size il necese                                                                                  | ary and identify by block number,              | , <u> </u>                                                     |

|                    |                                                                                                                 |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

| 9. ABSTRACT (Canti | nue on reverse side il necessi                                                                                  | ary and identity by block number)              |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

|                    |                                                                                                                 |                                                |                                                                |

| D 1 JAN 73 1473    | EDITION OF \$ NOV 65 15 0                                                                                       | OBSOLETE                                       | UNCLASSIFIED                                                   |

|                    | S/N 0102-014-6601                                                                                               | SECURITY CLA                                   | SSIFICATION OF THIS PAGE (then Date an                         |

•

4

normality for the

### RAPIDbus

### Architecture and Realization

#### Abstract

and the set of a set of the set o

*RAPIDbus: Architecture and Realization* describes a synchronous multiprocessor designed to support sensory processing, image understanding, and control applications. Up to eight board level masters interact with up to eight slaves along a time-multiplexed implementation of a crossbar switch. Two implementations are considered, one based on an Advanced Shottky logic with a bus bandwidth of 16 Mhz and a Versabus host interface. The second implementation, based on an ECL/TTL gate array, permits an estimated 64 Mhz of bus bandwidth and a Versabus/Multibus host interface. Segmented memory management, a multicast capability between one master and multiple destinations, and a standardized host interface aid in making RAPIDbus an appropriate architecture for robotic applications.

This research was support by the National Science Foundation under grant number ECS-7923893.

## **Table of Contents**

| 1. Overview of RAPIDbus Specification            | 2        |

|--------------------------------------------------|----------|

| 1.1 What is RAPIDbus?                            | 2        |

| 1.2 System Elements                              | 6        |

| 2. Summary of Versabus Specifications            | 8        |

| 2.1 Why the Versabus?                            | 8        |

| 2.2 Versabus Protocol Summary                    | 9        |

| 2.2.1 Data Transfer                              | 9        |

| 2.2.2 Bus Arbitration                            | 10       |

| 2.2.3 Interrupt Handling                         | 11       |

| 2.3 Versabus System Modifications                | 12       |

| 3. RAPIDbus Data Transfer Protocols              | 13       |

| 3.1 The Window Structure                         | 13       |

| 3.2 Functional Modules                           | 14       |

| 3.3 Reading and Writing on the Bus               | 18       |

| 3.3.1 Read Operations                            | 18       |

| 3.3.2 Write<br>3.4 Multicast Capability          | 19       |

| 3.5 Definition of Signal Lines for Data Transfer | 20<br>23 |

| 3.5.1 Time-multiplexed Signal Lines              | 23       |

| 3.5.2 Non-Multiplexed Bus Signals                | 25       |

| 4. The Address System                            | 28       |

| 4.1 Address Translation                          | -        |

| 4.1.1 Partitioning of Memory                     | 28<br>28 |

| 4.1.2 Functional Description                     | 30       |

| 4.1.3 Internal Register Manipulation             | 30       |

| 4.1.4 System Performance Considerations          | 35       |

| 4.2 Interface Control Register                   | 36       |

| 4.2.1 Interface Control Register Upper Byte      | 37       |

| 4.2.2 Interface Control Register Lower Byte      | 39       |

| 4.3 RAPIDbus Physical Memory Map                 | 41       |

| 5. The Priority Interrupt System                 | 53       |

| 5.1 Interrupt System Objectives                  | 53       |

| 5.2 Functional Modules                           | 53       |

| 5.3 Interrupt Service Protocol                   | 54       |

| 6. Ibus Arbitration and Control                  | 57       |

| 6.1 Use of the Ibus and Virtual Buses            | 57       |

| 6.2 Master Ibus Access                           | 58       |

| 6.3 Memory Access                                | 62       |

| 6.4 Multicast Access                             | 63       |

| 6.5 Interrupt Vector                             | 64       |

| 6.6 Ibus Operation Summary                       | 66       |

| 7. System Support                                | 67       |

i

| 7.1 System Timing               | 67 |

|---------------------------------|----|

| 7.1.1 The Master Clock          | 67 |

| 7.1.2 The Window Address System | 69 |

| 7.1.3 The Host Clocks           | 70 |

| 7.2 Control Lines               | 71 |

| 7.2.1 ACCLK                     | 71 |

| 7.2.2 Reset                     | 71 |

| 7.2.3 Test Configuration Lines  | 72 |

| 7.2.4 ACFAIL                    | 72 |

| 7.3 I/O Interface               | 72 |

| 7.3.1 I/O Bus                   | 73 |

| 7.3.2 Serial Access             | 74 |

| 8. Where Next?                  | 77 |

| I. Connector CP1 Signals        | 78 |

| II. Connector CP2 Signals       | 80 |

ii

### List of Figures

- Figure 1-1: The interconnection scheme for a multiprocessor system can have a heavy effect on 2 system efficiency.

- Figure 1-2: Common bus architectures trade off simple hardware for increased bus contention in a 3 multiprocessor system.

- Figure 1-3: Multiport Memory requires a unique link between each processor and one or more 3 system memory arrays.

Figure 1-4: Crossbar switching permits multiple connections between processor and memory to be 4 made randomly and simultaneously, but requires complex hardware.

- Figure 1-5: A time multiplexed common bus structure allows multiple simultaneous random paths 4 with a switching circuit that grows in switch bandwidth and not  $N^4$  switch complexity as does a crossbar switch.

- Figure 1-6: A Rapidbus system is composed of many independent elements.

- Figure 3-1: The virtual bus system is implemented using bus windows to link several masters and 14 several slaves simultaneously

- Figure 3-2: Each RAPIDbus interface card is composed of multiple modules, centered around the 15 Ibus.

- Figure 3-3: Several multicast address generators are needed to create the full address range 21 required for a memory access. A single module is shown here. This illustration is adapted from Advanced Micro Devices data sheet on the AMD 294015

- Figure 4-1: The MC68451 memory management unit supports address translation and memory 29 protection.

- Figure 4-2: The address space tables links the incoming function code and memory map bit from 31 the control register with the cycle address space number $^{16}$ .

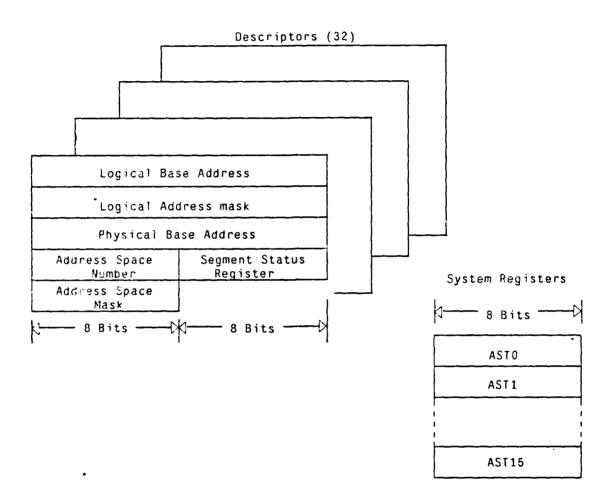

- Figure 4-3: The 32 descriptor arrays each define a translation process. The system registers select 32 the descriptor array that is to be used during this data transfer cycle<sup>16</sup>.

- Figure 4-4: Each processor sees the memory management unit registers assigned to that unit in the 33 same address locations<sup>16</sup>.

- Figure 4-5: Continuation of the memory management unit address map<sup>16</sup>.

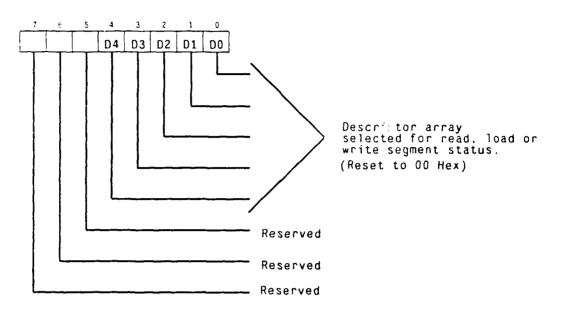

- Figure 4-6: The descriptor pointer selects the descriptor array that is used in a load descriptor 35 operation, read segment status, and the write segment status operation<sup>16</sup>

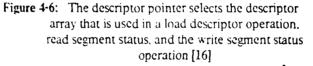

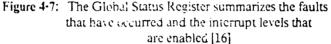

- Figure 4-7: The Global Status Register summarizes the faults that have occurred and the interrupt 36 levels are enabled<sup>16</sup>

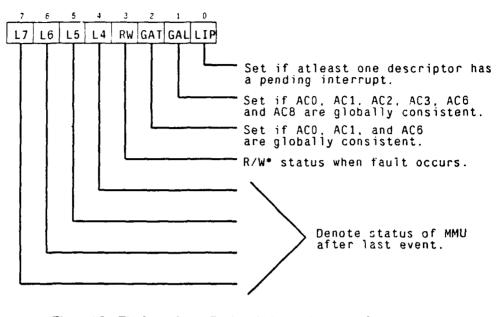

- Figure 4-8: The Local Status Register indicates the status of write\* when a fault occurs, the 37 consistency of the descriptors, and an indication of the highest priority interrupt pending<sup>16</sup>

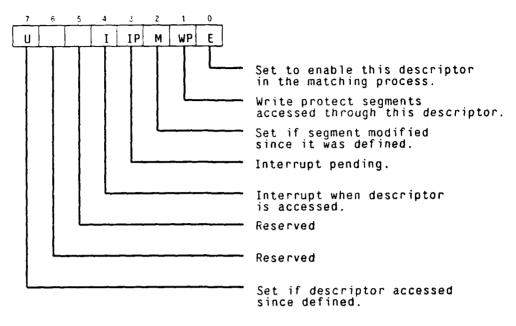

Figure 4-9: The segment status register is selected through the Descriptor Pointer register indirectly 38 16

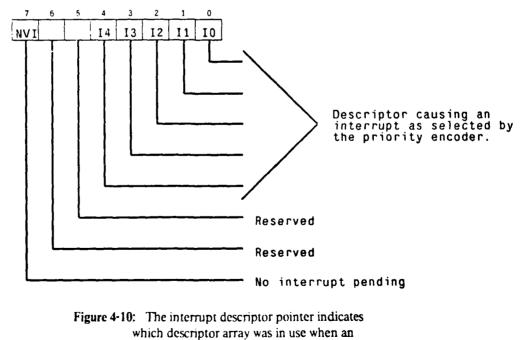

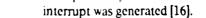

- Figure 4-10: The interrupt descriptor pointer indicates which descriptor array was in use when an 38 interrupt was generated<sup>16</sup>.

- Figure 4-11: The Result Descriptor Pointer identifies the descriptor involved in a write violation, 39 load descriptor failure, or direct translation success<sup>16</sup>. 40

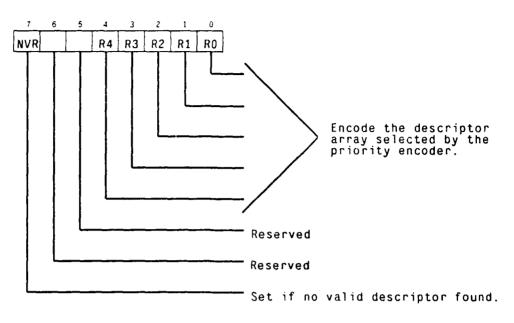

- Figure 4-12: Interface control register low byte

- Figure 4-13: Interface control register high byte

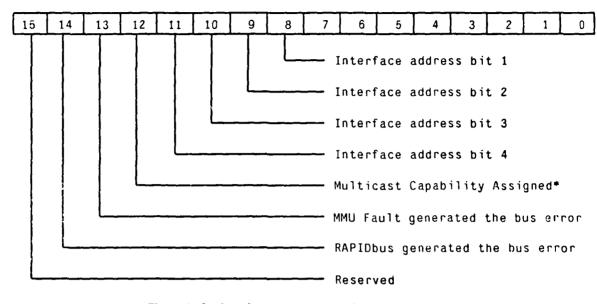

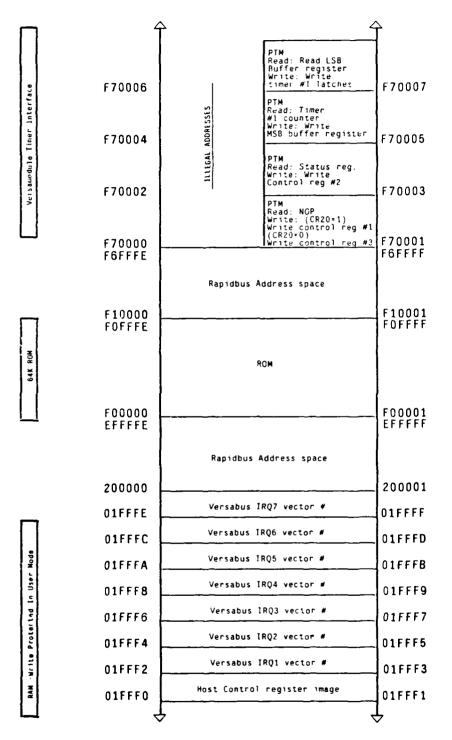

- Figure 4-14: Lower RAM supervisor space

- Figure 4-15: User RAM and upper supervisor space

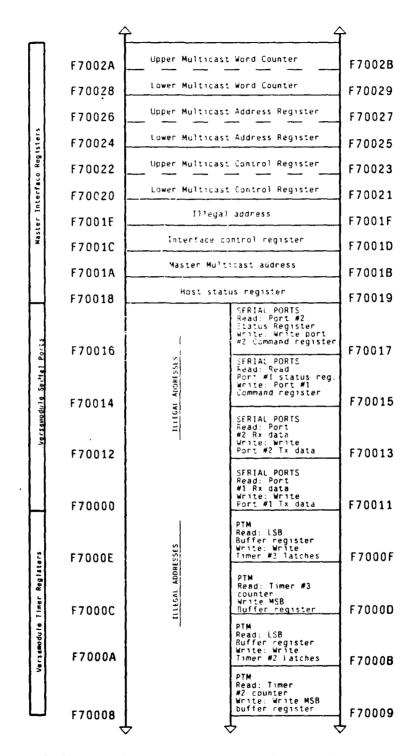

- Figure 4-16: Upper RAM supervisor space, ROM, and Timers 44 Figure 4-17: Versamodule registers, and master interface control page 45

7

34

41

42 43

| Figure 4-18: | Master interface control page                                                           | 46 |

|--------------|-----------------------------------------------------------------------------------------|----|

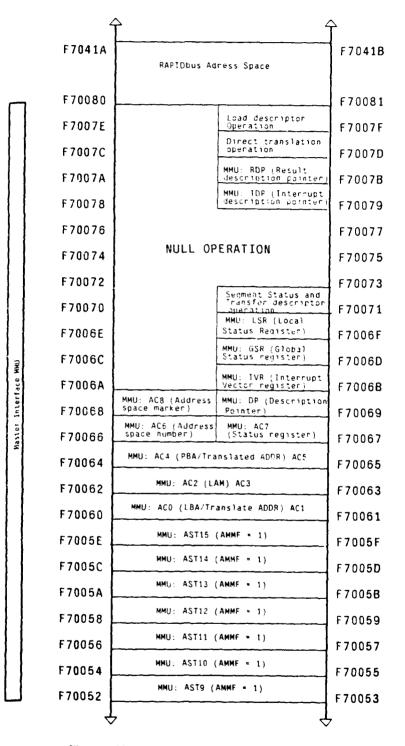

| Figure 4-19: | Master interface control page [MMU]                                                     | 47 |

| Figure 4-20: | Slave #1 and Slave #2 interface control pages                                           | 48 |

| Figure 4-21: | Slave #3 and Slave #4 interface control page                                            | 49 |

| Figure 4-22: | Slave #5 and Slave #6 interface control page                                            | 50 |

| Figure 4-23: | Slave #7 and Slave #8 interface control page                                            | 51 |

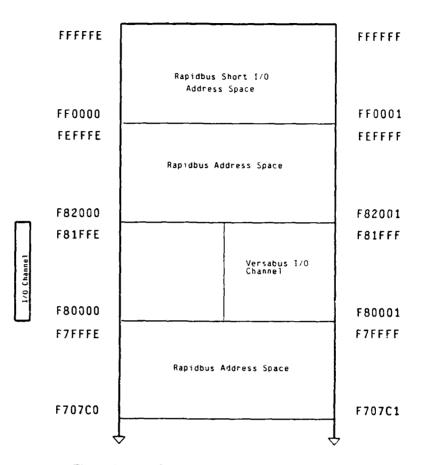

| Figure 4-24: | I/O and RAPIDbus address space                                                          | 52 |

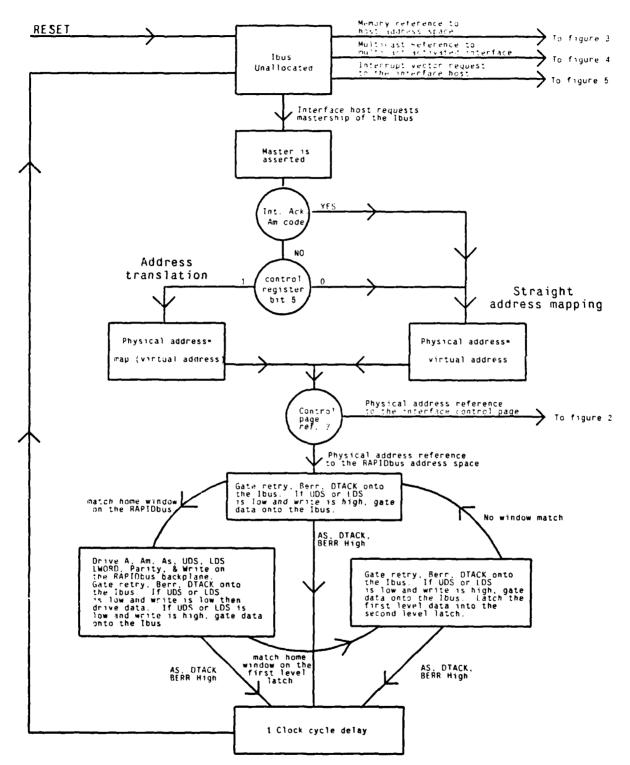

| Figure 6-1:  | $\Lambda$ data transfer begins with a master access.                                    | 59 |

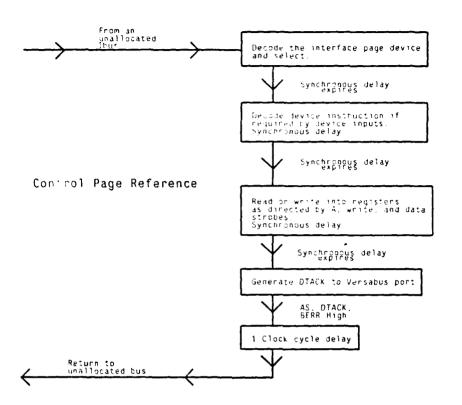

| Figure 6-2:  | Control page references are used to modify the RAPIDbus interface configuration or      | 61 |

|              | that of the memory management unit assigned to the processor's virtual bus.             |    |

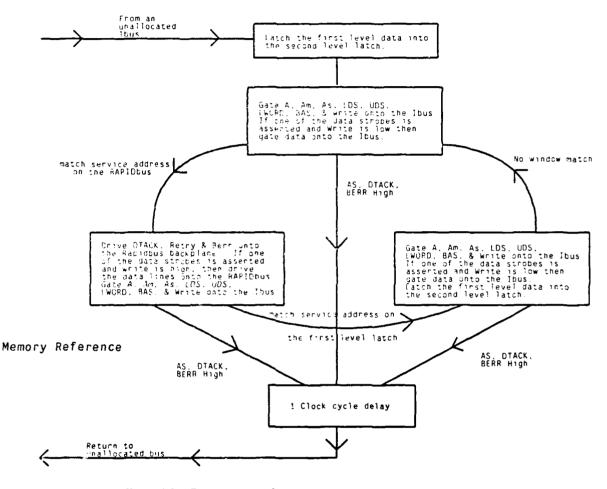

| Figure 6-3:  | The memory reference access to the host allows host processors to examine and modify    | 62 |

|              | memory locations on the host                                                            |    |

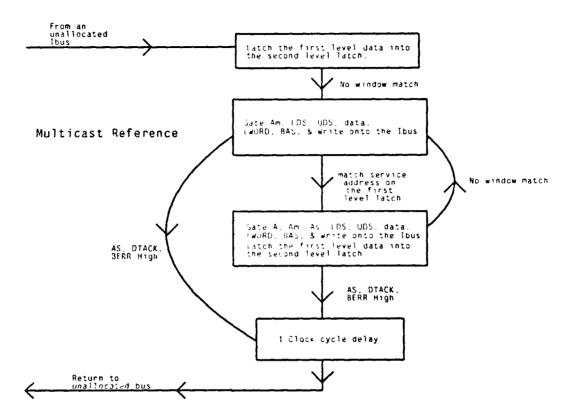

| Figure 6-4:  | The multicast reference to this host allows multiple locations to be written into       | 64 |

|              | simultaneously                                                                          |    |

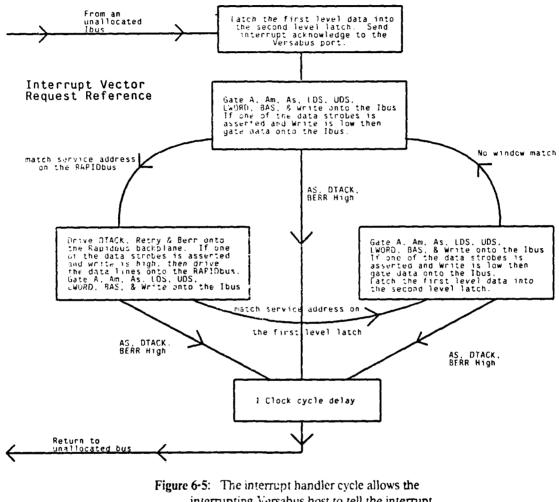

| Figure 6-5:  | The interrupt handler cycle allows the interrupting Versabus host to tell the interrupt | 65 |

|              | handler which service routine to choose to service the interrupt.                       |    |

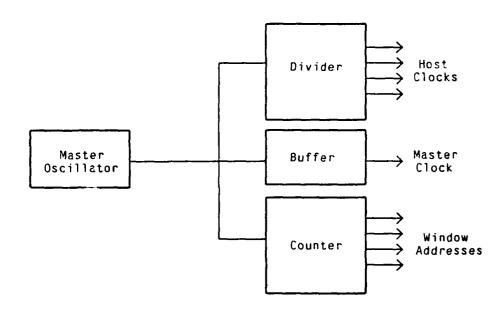

| Figure 7-1:  | All synchronous system timing is derived from a single time base                        | 67 |

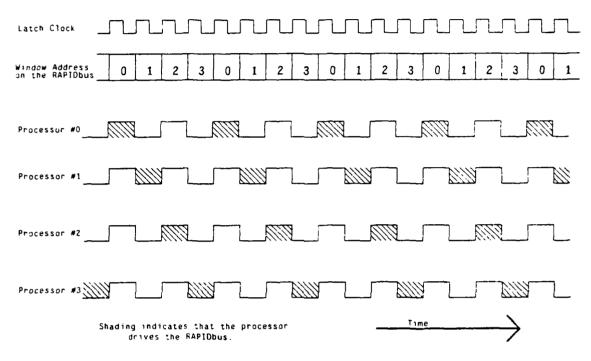

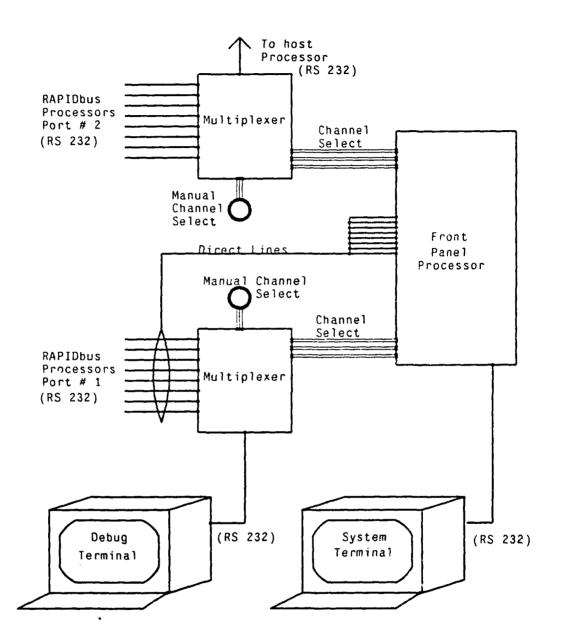

| Figure 7-2:  | An eight processor system requires either a high bandwidth backplane or a low           | 69 |

|              | frequency processor clock                                                               |    |

| Figure 7-3:  | A four processor system can reasonably be implemented in Advanced Schottky TTL to       | 70 |

|              | support eight MHz processor clocks                                                      |    |

| Figure 7-4:  | The front panel processor simplifies interactions with multiple processors.             | 75 |

iv

The concept of a Rotary Access, Parallel Implementing, Digital bus (RAPIDbus) was first proposed as an ECL machine by Zoccoli and Sanderson [1]. Bracho [2] suggested the creation of a TTL machine making use of a time-multiplexed Versabus convention. The adaptation of the Versabus convention as the host interface makes available a wide variety of commercial processors, memory systems, and peripheral processors.

This specification defines an architecture and realization of a RAPIDbus system based on a series of virtual Versabuses. Motorola has described the Versabus architecture [3] in a rigorously defined specification. Thus it is the primary intent of this document to describe the RAPIDbus as an interconnect system for a series of host ports obeying the Versabus convention. Beyond assuming the Versabus convention at the host ports, characteristics of the Versabus hosts such as the presence of a processor and memory mapped to the host port must be known in the configuration of the interface card. Thus tremendous flexibility is made available in the actual processors and resources that RAPIDbus supports.

Prospective users of the RAPIDbus prototype system at Carnegie-Mellon will find sections of this document to be relevant in evaluating the suitability and formulating use of the machine for their applications. Those interested in exploring the different interconnection schemes available for multiple pairings of processors and system resources may find the time-multiplexed switching used here to be relevant to the realization of other architectures.

Two companion reports are in preparation. The first describes an implementation of the RAPIDbus architecture in Advanced Shottky logic, supporting four \$ MHz processors. The Shottky report includes circuit diagrams and a detailed discussion of one possible implementation schema. A performance analysis of the Advanced Shottky implementation and its impact on a higher performance ECL logic version of the RAPIDbus architecture is briefly proposed in the second report. Initial review suggests the ECL version, based on TTL/ECL gate arrays, would be capable of supporting eight processors running at clock speeds approaching 16 MHz. This second version may also allow interfacing Multibus cards at the host interface level along with Versabus hosts.

Credit for this project is due to a great many people who have contributed heavily. Dr. Arthur Sanderson and Mario Zoccoli first proposed a time-multiplexed backplane. Rafael Bracho suggested the use of a Versabus interface to the host and the use of Advanced Shottky as an implementation technology. Dario Giuse heavily supported the graphics and computer aided design system (Drawing Package) [4]. Construction support for the advanced Shottky implementation is being provided by the Computer Science Engineering Laboratory at Carnegie- Mellon University, and Dave Coleman. This research was made possible in part by a grant from the National Science Foundation number ECS-7923893.

### 1. Overview of RAPIDbus Specification

#### 1.1 What is RAPIDbus?

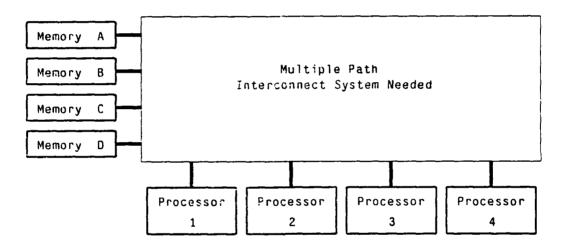

RAPIDbus is a multiprocessor architecture aimed at effectively supporting signal processing, task integration, display, and control algorithms in a real time research environment. Such applications are characterized by a high bandwidth of interprocessor communications. As the size of a system increases, the bandwidth available to connect processors and memory can become a system bottleneck, reducing the rate at which additional system resources increase system throughput. For a multiprocessor system with several processors and a variety of system resources, the interconnection scheme can be an important parameter in determining the efficiency with which multiple processors communicate.

Figure 1-1: The interconnection scheme for a multiprocessor system can have a heavy effect on system efficiency.

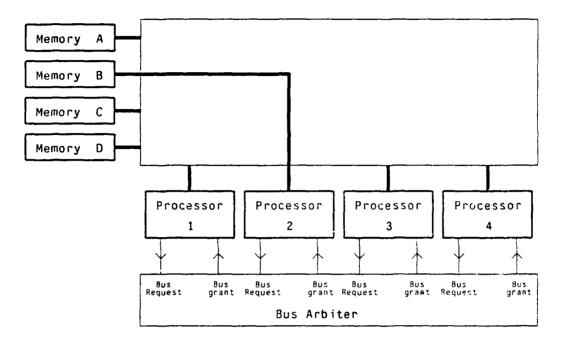

Many current minicomputer systems make use of a common bus architecture such as the Multibus, Qbus, and Versabus protocols. Most common bus multiprocessor architectures resolve bus contention by assigning the bus to one processor-memory pair for the duration of the memory access cycle. Other processors needing the bus are required to wait until the existing request is serviced before obtaining bus mastership. Bus intensive applications can be subjected to a heavy performance penalty due to bus contention.

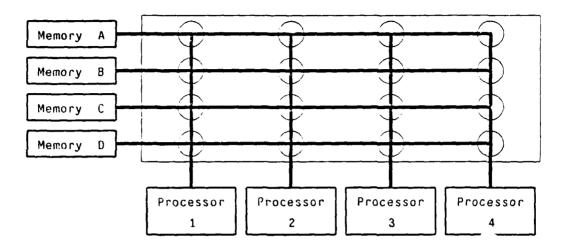

Both crossbar switching and multiport memory configurations reduce contention, but at an increase in the complexity level and a decrease in the expandability. Crossbar switching dedicates a switch for each signal line and each combination of processor and memory. Systems such as C.mmp have shown that up to sixteen processors and sixteen memory arrays can be connected reliably in this way, but the hardware cost and complexity is non-trivial, increasing by the fourth power as new processors are added [5], [6].

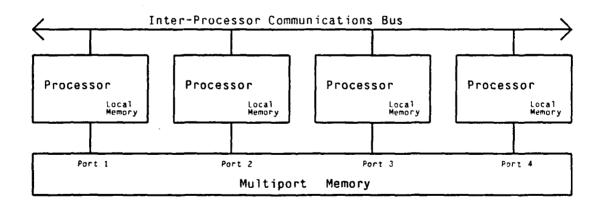

Multiporting provides several ports to one array of memory, depending on logic internal to the multiport memory to arbitrate between requests, making their service seem simultaneous. A unique link between each

Figure 1-2: Common bus architectures trade off simple hardware for increased bus contention in a multiprocessor system.

Figure 1-3: Multiport Memory requires a unique link between each processor and one or more system memory arrays.

processor-memory pairing is required, leading to considerable interconnect complexity, and a lack of easy expandability. The DEC MA-780, connecting up to four VAX 780's together is one example of a successfully executed multiport memory system [7].

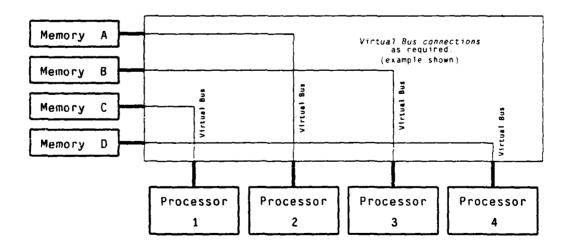

RAPIDbus attempts to remove common bus contention by time-multiplexing the common bus, achieving

Figure 1-4: Crossbar switching permits multiple connections between processor and memory to be made randomly and simultaneously, but requires complex hardware.

the flexibility for multiple paths of the crossbar switch at a potential reduction in the hardwa. Dexity, A set of high speed drivers and latches attached to each RAPIDbus interface port provide a set of virtual buses, one for each processor. A time-multiplexed bus structure implements an increasing number of concurrent paths not by increasing the size of the switching mechanism, but by increasing the speed at which the latches and drivers multiplex, permitting more time slots per processor clock cycle.

Figure 1-5: A time multiplexed common bus structure allows multiple simultaneous random paths with a switching circuit that grows in switch bandwidth and not N<sup>4</sup> switch complexity as does a crossbar switch.

transfer abort.

The RAPIDbus architecture assigns a time-periodic window on the bus to each processor, designated by a window address. Every time its window cycles around, each master interface card has the opportunity to drive the physical RAPIDbus backplane. Comparators and latches on each of the slaves scan the address and control lines, waiting to latch in a reference to their resources. When a slave interface recognizes a reference, it is presented to the slave host, often a memory card. On subsequent occurrences of the master's window, the slave's response is driven onto the RAPIDbus by the slave interface card and latched in by the master interface card initiating the request, terminating with the successful transmission of a single data word or a

As defined in this specification, RAPIDbus provides a set of virtual buses for Versabus convention host cards, memory management, multicast capability, and interrupt handling. The interface serves to synchronize and time-multiplex the asynchronous Versabus protocol. A variety of software configurations are possible, simulating different interconnection schemes for research evaluation. Memory management is provided by the RAPIDbus interface as an option for Versabus processor cards without memory management. A multicast capability allows one processor at a time to send data words into multiple system memory locations through previously prepared multicast address registers on each receiving card. Interrupt handling capability allows any processor to be interrupted and an interrupt vector to be requested explaining the reason for the interrupt handler's virtual bus.

Some Versabus hosts with processors share the same card and Versabus port with memory that is mapped onto the system bus. Arbitration must occur so that a given host resembles either a "processor" or a "memory" for a single data transfer cycle. Thus when the memory on a processor card is being accessed, the processor does not have access to its virtual bus and must wait until the memory access is completed. This conflict is a result of the sharing of a Versabus port by both system memory and a processor. In certain applications separate processors and system memory cards may increase system throughput.

Commercially implemented examples of the bus window structure include the ITT 1240 digital switch for telephone switching [8], [9] and the Digital Equipment Corporation bus window adapter for the PDP-11 [10]. The ITT digital switch is intended to link between up to 100.000 lines using a hierarchica' structure. Sixty lines are controlled by a dedicated microprocessor which supports ringing, supervision, and digital encoding for each line. Each microprocessor communicates through a terminal interface across one or more switching planes to complete the required path between lines. The switching planes are each implemented using a bus window circuit similar to that employed by RAPIDbus. The digital switch supports lower bandwidth links than that intended for RAPIDbus, however a larger number of bus masters are accommodated as a result. The DEC UNIBUS window adapter, the DA11-F, was marketed by DEC in the early 70's as an option for the PDP-11 to link two processors. It allowed a window of up to 32k words to be mapped from the address space of one processor to that of another processor. It appeared as a master on the target UNIBUS and a slave on the originating UNIBUS. A series of DA11-F adapters allowed communication among several processors [10]. The UNIBUS window adapter differs from RAPIDbus primarily in that the RAPIDbus interface goes between host and bus, the DA11-F linked among pairs of buses.

As a research project it is hoped that RAPIDbus will expand our understanding of processor-memory interconnection dynamics. As a research tool RAPIDbus offers an interesting support medium for high bandwidth interprocessor communication applications in robotics and signal processing applications.

#### 1.2 System Elements

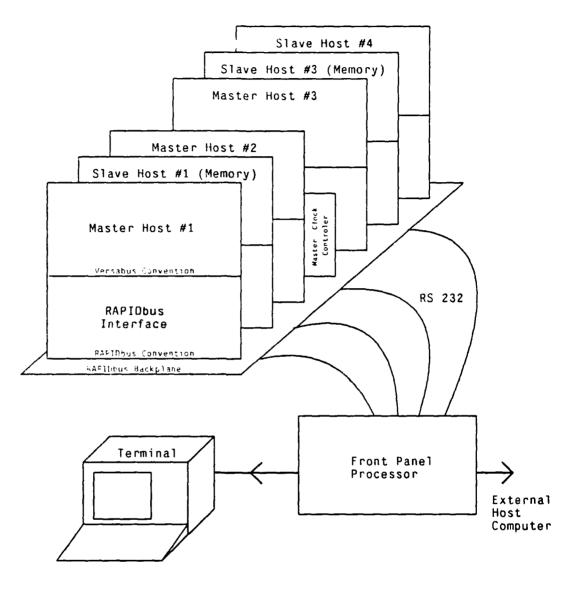

The RAPIDbus architecture allows considerable flexibility the modules that are chosen to form a system, such as that illustrated in figure 1-6. A minimal system has least two processors, two memory sections, interface eards to support the processors and memory, a master clock controller eard, and a backplane. A system may have up to eight processors, depending on the implementation, an equal number of peripherals, and RAPIDbus interface eards for all processors and peripherals. The advantages of the RAPIDbus virtual buses are increasingly evident in terms of reduced common bus contention up to the implementation limit on the number of processors.

Versabus processor/memory hosts contain a processor capable of executing an instruction stream and a memory space which is accessible from the Versabus port. These cards can act as both masters, originating memory references, and as slaves, acting as the target of memory references by other processors. The use of the Versabus convention for the parallel port between the processor and the rest of the system restricts the card to act as either a master or a slave to the rest of the RAPIDbus while a single data transfer operation is in progress. Processor/memory cards may support a local parallel 1/O bus.

Versabus processor-only hosts incorporate a master capability. They must take data in and output data using processor read and write operations. Like the processor/ memory cards, the processor-only cards may support a local I/O bus.

A memory or L/O host can only function as a slave, completing data transfer operations that were initiated by a system master. This class of host may include memory cards, display cards, or controllers for off-line storage.

The interface cards are created in a mother-daughter board configuration, acting as adapters between the asynchronous, low speed Versabus port, where the master/slave host is connected, and the time-multiplexed, high speed RAPIDbus backplane at the RAPIDbus port. Each processor/memory, processor only, or memory only host requires an interface card.

The master clock controller card generates the window addresses, host clocks, and master latch clock. It also acts as the interface with the front panel for utility lines such as the reset and system test lines. Unlike the processor/memory, processor only, and memory only cards, which can have multiple occurrences in a system, the master clock controller only occurs once per system. It is plugged directly into the RAPID bus backplane in a specially prepared slot.

The interface cards and the master clock controller card plug directly into a backplane, supplying the physical RAPIDbus signal interconnect paths, power, and optionally I/O connections to the outside world. The enclosure is high enough to enclose the host/interface card pairs, supplies implementation dependent cooling, and a proper electo-magnetic environment.

A front panel processor takes the variety of serial lines coming from the processor/memory and processor only cards and channels them into a single terminal connection, and a single connection to communicate with an external computer or computer network. This front end processor supplies a user interface, providing serial line multiplexing and an operator/machine interface.

Figure 1-6: A Rapidbus system is composed of many independent elements.

Considerable flexibility is thus provided to support a variety of high speed signal processing tasks. The system hosts can be selected to fit the required application requirements with minimal configuration changes of the accompanying interface. The front panel processor provides a filtration of user messages from each of the system processors, and serves to route messages from the operator to the appropriate processor(s).

7

### 2. Summary of Versabus Specifications

#### 2.1 Why the Versabus?

The RAPIDbus architecture is intended to explore the capability of a time-multiplexed common bus to support complex multiprocessor applications. The adaptation of an established convention to connect processors and memory allows concentration of effort to fall on the time-multiplexed bus design. Choosing a processor and memory bus convention which supports multiprocessor interaction without the RAPIDbus interface simplifies the task of evaluating the improvement in system throughput due to the time-multiplexing and other support functions provided by the RAPIDbus architecture. Potential applications such as machine vision require the manipulation of several data objects of half a megabyte or more, leading to a need for at least several megabytes of virtual address space. The anticipated multiprocessor system should support high speed data transfers between modules that may vary in their time to complete a transfer, leading to a need for an asynchronous system. Reliability requirements in a large system point to a need for at least board level fault localization. These considerations led Bracho to propose the use of Motorola's Versabus as the host interface protocol for a RAPIDbus architecture [2]. Motorola has developed Versabus with many of the system constraints that are required to support the RAPIDbus architecture.

The Versabus is a common bus architecture which supports multiple processors through a system of bus arbitration where one processor is granted the use of the bus at a time [3]. The protocol is asynchronous, accommodating a variety of bus responses. A large data path (up to 32 bits) and address space (up to 32 bits) accommodate considerable capability. Malfunction control helps to localize system failures to the board level. Relatively large cards provide considerable complexity on each host. Versabus offers a direct memory access capability which became the basis for the RAPIDbus multicasting. An additional bonus in the research environment is the clear differentiation between user and supervisor that accompanies each data transfer. Such differentiation allows some protection of the system from errant application code.

The choice of the Versabus host convention is not without drawbacks. The ability to dual port memory to both the Versabus port and an on-board processor led to the possibility of a deadlock in which two processor cards were each trying to access the memory on the other's card simultaneously. Since each processor then occupies it's own virtual bus, the two processors can present their memory requests on their respective buses simultaneously, but be prevented from completing the link through the other processor's Versabus port to the target memory by the second processor's pending request. Thus simultaneous requests for each other's local memory could result in both processors taking a timeout and trapping to a costly bus error routine.

Several solutions exist for this deadlock situation. One could provide separate Versabus ports for processor and processor memory while maintaining a local interconnect. Alternately, the processor hosts could be modified so as to remove their data transfer requests from the Versabus port while the on-board memory was accessed by another master, later completing the aborted transfer. The architects of C.mmp have explored a similar problem, resolving their deadlock situation by going from a circuit switching interconnect, where at one time a path exists from processor to slave, to a packet switching system where the data request is stored in intermediate buffers and does not own the whole virtual link at the same time [5]. Since such host requirements would not be required on a common bus architecture, requiring these features on our host would remove virtually all established common bus from consideration.

Two solutions are proposed to circumvent the problem within the Versabus convention. Routing all communication between processors through an intermediate memory card removes the possibility of deadlock, although it does increase the data transfer time by the difference between a local and a RAPIDbus access. To decrease the possibility of trapping to a bus error routine as a result of a timeout, an additional line had to be imposed on the Versabus convention which allowed the Versabus port to request that the processor retry the instruction. When this line is asserted low in addition to bus error, the processor terminates the existing data transfer request and then generates a new data transfer. When the processor on the host card is a 68000 architecture, connection to the HALT pin accomplishes this function. Thus the interface can be set to timeout before the host does, causing the instruction to be retried after a delay unique to each interface. The interface should optionally limit the number of retries that occur before trapping to a bus error routine. Unfortunately a read-modify-write cannot be retried, and with the 68000 architecture a retry request for a r-m-w instruction leads to a bus error trap. Thus the RAPIDbus architecture can be implemented within the Versabus framework if all semaphore locations used by a read-modify-write instruction are mapped onto memory only hosts.

A less serious problem with the Versabus is its current relative lack of popularity. In contrast to architectures such as \$100, Qbus, and Multibus, only a handful of manufacturers are committed to building Versabus cards. This situation is expected to improve, partially as a result of a formalization of Versabus by an IEEE committee. Cards are also commercially available [11] to use Multibus cards on a Versabus system.

Use of the Versabus as a host processor interface thus appears to be an appropriate choice, resulting in limitations that can be dealt with, and allowing concentration of design effort on the bus itself and not on the hosts that will utilize the virtual bus structure. Other experimental multiprocessor architectures have gone the route of heavily modifier processor and memory cards, expending considerable design effort on the system resources [6]. Versabus architecture objectives assure that many of the provisions required by a true multiprocessor will be supported on a Versabus host without custom design effort.

#### 2.2 Versabus Protocol Summary

The Versabus specification was first proposed by Motorola in 1981 and was implemented on several board level products shortly afterward [3], [12], [13]. This section is intended to familiarize the reader with the most salient features of the Versabus specification. For a critical statement of the Versabus architecture the reader is referred to Motorola document M68KVBS and the report of the IEEE subcommittee. Numerous options are provided by the Versabus specification. It is the intent of the RAPIDbus specification to provide proper virtual bus paths to support these options when available at the host level without limiting or compulsory specification.

#### 2.2.1 Data Transfer

The Versabus architecture is based on data transfer operations occurring between a master that initiates a data transfer and a slave that supports the data transfer. Although a Versabus may have several boards capable of becoming the bus master, only one card can support a bus data transfer operation at a time. A master card at the base of the system daisy chains is configured as system master, supplying arbitration of bus mastership between competing masters and generating system resources such as the system clock.

9

Once a master has gained ownership of the Versabus, making use of the bus arbitration scheme, and after the data acknowledge and bus error signals from the previous cycle have been deasserted, the asynchronous data transfer operation begins. The master places the address and address modifiers on the address lines, and in the case of a write, places the data to be written on the data lines. Then the control lines, address, and data strobes appropriate to the transfer operation are asserted.

A slave recognizes the address and selects the appropriate device. The status of the write line is not examined until after atleast one of the data strobes has been asserted. The address is examined (along with the address modifiers) for parity errors if address parity checking is implemented in the particular system. A read causes the addressed location's contents to be placed on the data bus, and the data acknowledge line is asserted. A write operation causes the contents of the data bus, as supplied by the bus master, to be written into the address previously selected. The completion of this storage is signaled by the assertion of data acknowledge. If an address parity or a data parity error is detected, then the board which detected the error pulls the bus error line and traps to a handler routine. A correct transfer will cause the master to respond to the slave's data acknowledge by removing the address strobe, signaling the completion of the data transfer operation. The slave removes data acknowledge and the other lines that it was driving. The master may either return the control of the bus to the bus arbiter, releasing the lines that it was driving, or proceed with a data transfer as it chooses (and is directed by the arbiter).

If no memory location responds to the address placed on the bus then the master can be configured to timeout and generate a bus error. Different length data transfers can be accomplished. Bytes can be transferred by using the lower data strobe (LDS\*) or the upper data strobe (UDS\*). Words can be transferred by using both of the data strobes. In a system that supports the full 32 bit data path, the longword signal line can be driven to indicate that a longword cycle or four bytes are being transferred.

#### 2.2.2 Bus Arbitration

In order to support several potential bus masters on a single common bus, an arbitration system must take requests from one of more masters desiring to use the bus and designate a unique master for each data transfer cycle via the bus grant lines. The arbitration function is invested in the system controller in the Versabus system. This system controller is always located at the lowest slot number occupied in the Versabus system, at the head of the daisy chains.

The arbiter on the system controller monitors the five prioritized open collector request lines (BR4 through BR0 where BR4 is the highest priority). It can convey bus grant authorizations along five bus grant daisy chains that begin at backplane slot #1 and chain through to the end of the backplane (BG4IN through BG0IN, and BG4OUT through BG0OUT). A master who has received authorization to use the bus must drive the bus busy line to indicate that the bus is in use. The bus clear line is used by the arbiter to inform the current bus master that a higher priority request is pending and that the master should release the bus as soon as possible. The bus release line is the highest priority request for use of the bus, driven by the emergency requester in the result of a power failure. The bus release line takes precedence over even priority 4 requests in order to execute an orderly shutdown in the event of a power failure.

If the bus is not in use when a request for use of the bus appears at the arbiter, then the arbiter sends a bus grant down the bus grant daisy chain at the level requested. The grant is not passed along to the next card in

the sequence until the receiving card has verified that it does not have a bus request pending at this level. When the first of what may be several cards that have requested the bus at this level is reached, the receiving card terminates the daisy chain and drives bus busy to indicate that the Versabus is in use. Depending on the requester options that are in force on the current master, the master may release the bus at the end of a single data transfer, at the end of a block move, or wait until the bus clear or bus release line indicates that the master should release the bus.

If multiple priority level requests are received at the same time at the arbiter, the bus grant signal is sent down the daisy chain of the highest priority requester. If a request is received at a higher priority after the grant has been issued, then the bus clear signal is generated by the arbiter. Lower priority signals are ignored until the current bus master releases the bus and no higher level interrupts are pending.

#### 2.2.3 Interrupt Handling

The priority interrupt system in the Versabus convention is composed of cards that can generate Versabus interrupts at one of seven levels and processor cards that service these interrupts. Bus interrupts are generally distinct from interrupts that are generated on-board a host card and serviced by the processor or other handler on the same card. Versabus interrupt are a way of getting the attention of processors and requesting that they respond in a timely fashion to the needs of the interrupter.

The seven priority levels of interrupts can be divided among one or more interrupt handlers such that each handlers services a continuous range of interrupt levels. In a seven processor system each processor might service a distinct interrupt level. In a system with as few as two processors, one processor may handle all of the interrupts (all though this may not be the most efficient assignment of interrupt handlers). The prioritization of interrupt levels only occurs when more than one interrupt is generated to a handler simultaneously; then the highest level interrupt is serviced first.

With as few as one interrupt level assigned to an interrupt handler, little information can be conveyed about the action needed from the interrupt handler. Thus the interrupter must provide an interrupt vector, on the interrupt handler's request, indicating the action that the interrupt handler should take in the service routine.

In response to an interrupt, the interrupt handler must request Versabus mastership from the arbiter as previously described. When mastership is granted the handler places the level of the interrupt being generated on the lowest three address lines, leaving the others high. The handler drives the address modifier lines with a code that indicates that an interrupt handler cycle is in progress. These are followed by the assertion of interrupt acknowledge out (ACKOUT) by the interrupt handler along the interrupt acknowledge daisy chain. Each interface card in turn passes the acknowledge along to the next interface unless it has generated an interrupt at the level that is being handled.

When an interface card that has generated the level interrupt being handled receives the interrupt acknowledge then it refrains from passing the acknowledge along to the next interface card. Receipt of the interrupt acknowledge at the level at which the interrupter generated the interrupt causes the interrupter to place an interrupt vector on the lower 8 data lines of the bus and drive data acknowledge low. The vector is left on the the data lines until address strobe is revoked by the handler, terminating the interrupt handler

cycle. The returned vector points into an entry on the interrupt vector handler table in the lowest 256 locations in the interrupt handler's memory space. The location in the interrupt vector table directs the handler to a routine which will service the interrupter appropriately.

#### 2.3 Versabus System Modifications

Use of the Versabus architecture in a RAPIDbus system forces five modifications, two to the hosts, and three to the backplane.

In order to minimize the time required for a data transfer operation the phase of the clock used by the host can be optimized such that with high probability the data transfer request and required control signals will arrive at the driver section just before the master's window is to be sent. This requires that the host be capable of or modified to run on the system clock, where the system clock runs at the processor clock speed instead of the 16 MHz clock specified in the Versabus specification and is shifted in phase as indicated by the interface window address.

A retry line was added to the Versabus port at P2: 100. When this line is asserted low prior to and remaining after the assertion of bus error, then the current data transfer is aborted (address strobe goes high), and the transfer is retried. The retry line must be asserted for at least a processor clock cycle after bus error has been removed. In the 68000 architecture this function is accomplished by tying the retry line on the Versabus fingers of the host card to the open collector halt line on the processor. Other processors will generally require other procedures to implement retry.

The Versabus backplane, when adapted for use by RAPIDbus must be modified so that the ACKOUT of the highest number card ("lowest priority" in the Versabus system) is tied to the ACKIN of the lowest number card, creating a circular interrupt acknowledge daisy chain.

Cabling must be added to the standard Versabus backplane to accomodate a star fanout of the clock lines from the master clock controller card to each of the interface cards. Connections must also be made to the RS232 serial port connections on the outside of the machine.

### 3. RAPIDbus Data Transfer Protocols

#### 3.1 The Window Structure

A primary goal of the RAPIDbus architecture is to take advantage of the differential between the bandwidth required by a processor to run a data transfer operation across the system bus to another Versabus resource, and the total bandwidth capable of propagating down the system backplane. By time-multiplexing the backplane each Versabus port capable of initiating a data transfer (master) is assigned a virtual bus. Each traster appears to have an unoccupied link from the RAPIDbus port on its interface card to the RAPIDbus port on all other system resource cards. Versabus master hosts which share the host card with memory mapped into the system address space may have to arbitrate use of their Versabus port and local Ibus with other inasters accessing the master's memory. The outgoing master may also have to contend with other system masters for use of the Versabus port and Ibus belonging to system resources.

The virtual buses connecting the RAPIDbus port on each interface card are implemented using bus windows: ame slots on the RAPIDbus allocated to a particular RAPIDbus interface card which supports a master Versabus host. Each interface which supports a master is sequentially given a window during which the master interface may send a data transfer request to one or more slaves, and/or receive a response from an already activated slave. At least two windows are required to complete a data transfer, and often many more. It is the responsibility of the RAPIDbus port to interface between the time-multiplexed RAPIDbus windows that are perturent to the task that the given interface is engaged in and the time-static lbus that is seen by the Versabus port.

The number of master Versabus hosts that can be allocated virtual buses, with the accompanying assigned window is dependent on the bandwidth which each master demands and the minimum window duration that the implementation can support. In order to increase the number of virtual buses that are available to the system, the virtual link can be updated on every other host clock cycle with minimal performance degradation in processors such as the 68000, as is done in this architecture.

As a result of the overhead inherent in supporting multiple processors, for many of the applications that RAPIDbus is targeted, higher system throughput can be achieved by choosing a microprocessor with the maximal processor throughput, accommodating fewer processors into the system as a result. An alternate approach supporting more numerous, slower processors on a bus with an increased access time is ZMOB, ZMOB, at the University Maryland, supports 256 Z80 processors on a conveyor-belt like bus, trading slower access for brute size [14].

The discussion of the window address system within the support systems section proposes that implementations which are most appropriate for the 68000 architecture will allow either four or eight processors. Assuming the same processor clock speed in both cases, the eight processor version assumes that the RAPIDbus interfaces and the backplane will deliver twice the usable bandwidth of the four processor version. The timing of the processor clocks with respect to the virtual bus windows is illustrated in figure 3-1 where the shaded area indicates the time at which the master and slave RAPIDbus ports onto the Ibus are physically linked.

A variety of signal lines are required to implement data transfer operations, some of which are time-

| Latch Clock                      |                                      |

|----------------------------------|--------------------------------------|

| Window Address<br>on the RAPIDbu | 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 0 1    |

| Processor #0                     |                                      |

| Processor #1                     |                                      |

| Processor #2                     |                                      |

| Processor #3                     |                                      |

| Pracessor #4                     |                                      |

| Processor #5                     |                                      |

| Processor #6                     |                                      |

| Processor #7                     |                                      |

|                                  | Shading indicates that the processor |

|                                  |                                      |

Figure 3-1: The virtual bus system is implemented using bus windows to link several masters and several slaves simultaneously

multiplexed and sent on bus windows. Data and address lines are examples of lines sent on bus windows, having different values on each of the virtual buses. Other lines are time-static and are identical for all virtual buses. The interrupt lines are an example of time-static lines, interrupting a processor handling a given level independent of the virtual bus that the interrupt handler is assigned to.

#### **3.2 Functional Modules**

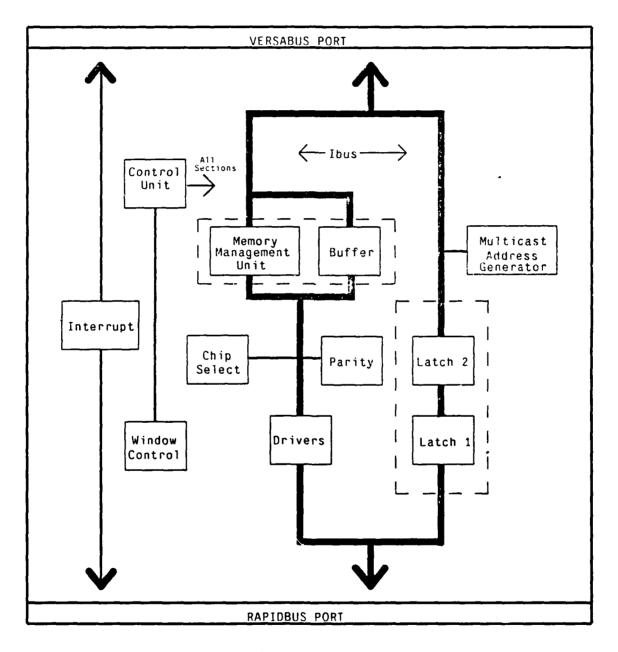

Each RAPIDbus interface card is composed of a series of functional blocks. This compartmentalization of function is intended to improve the readability of a design, simplify debugging, and identify functions that lend themselves to packaging integration. The interface is composed of a window handler, drivers, latches, an address translation unit, a multicast address generator, a parity check section, a chip select section, a timing generator, an interrupt control section, and an interface controller. The lbus links the Versabus port on the top of each interface card with the RAPIDbus port at the bottom. It comprises the address translation section,

the drivers, and the latches. The Versabus port, the RAPIDbus port, the multicast address generators, the parity section, and the chip select section drive or monitor the Ibus. The modules that compose the RAPIDbus interface card are illustrated in figure 3-2.

Figure 3-2: Each RAPIDbus interface card is composed of multiple modules, centered around the Ibus.

The heart of the time multiplexing of the bus is the window handler. The window handler performs three functions. First it scans for either the interface home window address or the window address of a master for which this interface is serving as a slave, as determined by the owner of the Ibus. Through the control register the interface can be configured so as to recognize only one window address for slave accesses. The proper phase of the interface host clock is selected by the window handler and supplied to the host so as to maximize the probability that the host will make a bus request which will reach the drivers just before the master window on the RAPIDbus appears. Each interface port off the RAPIDbus backplane is given a unique interface window identification. This unique identification provides the window address of the interface serving only a slave host, it uniquely maps the interface to reduce deadlock, and for the case of an interface serving only a slave host, it uniquely maps the interface control page of the slave interface into the RAPIDbus physical address space.

The driver section is used to gate the physical address lines, strobes, parity, write, bus error, retry, data acknowledge, and address modifier lines onto the RAPIDbus during a window as directed by the control sequencer. When the control sequencer does not indicate that this interface is to drive a given backplane line in the current window, the lines are to be deasserted. Line drive is to commence as soon as the appropriate window is recognized and last until the next window is recognized.

The latch section holds data at two levels. The first latches all time-multiplexed RAPIDbus lines at the end of every RAPIDbus cycle. During the following RAPIDbus cycle, these latched lines are examined for a slave reference to this interface card. If the Ibus is not being requested or in use, and a slave reference to this interface is detected, then the contents of the first level latch are held by the second level latch. The latch also holds the bus window if the Ibus is already allocated to the virtual bus currently sending the bus window at the first level latch. Under the direction of the control section, lines can be selectively gated onto the Ibus according the current lbus master.

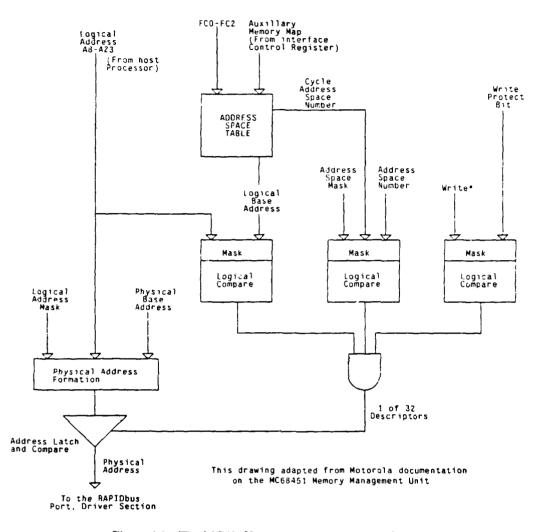

Data transfer exchanges must always be initiated by a master, and each master interface may optionally have a address translation unit positioned between the host processor and the RAPIDbus drivers. The function of the address translation unit is to map A8 - A23 to physical addresses PA8 - PA23. In any interface that incorporates a address translation process unit, the translation must be capable of being circumvented by clearing bit three in the control register so as to map the Versabus address is valid and rescinded when the physical address is no longer valid. The lower seven address lines, A1 - A7 are supplied directly to the driver section without translation. Bit zero of the control register switches between primary and secondary memory maps in interfaces that support memory management. Clearing bit zero accesses the primary memory map, setting bit zero directs the following references for translation by the secondary memory map in the memory management unit.

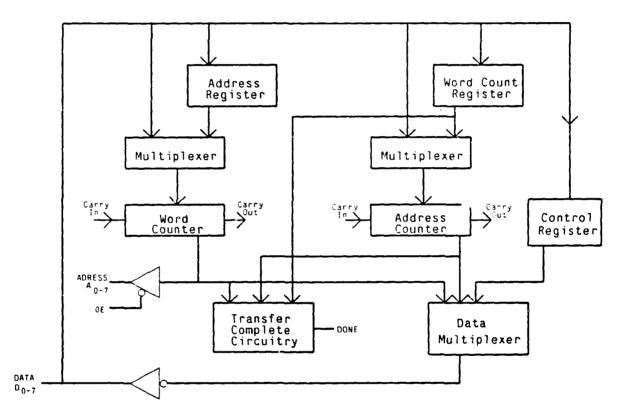

The multicast address generator is required for all interface cards that must function as a slave during a multicast data transfer cycle. The master desiring to multicast must set the multicast request bit in his control register, asking the processor host's interface to try for ownership of the multicast capability. Bit twelve of the interface control register is asserted low by the interface to indicate that the multicast capability has been secured by this interface. Prior to multicast transfers the multicast address generator registers of all interfaces that are to be multicasted into must be loaded with the base address and the number of words that are to be multicasted. For interface cards which support master and slave functional hosts, the master occupying the Versabus port must be asked to initialize his multicast address generator since the MAG registers for a master

interface only appear in that master host's memory map. For slave-only interface hosts, such as a memory card, the MAG registers are mapped into the RAPIDbus physical address space. Following write instructions to the multicast reference address will be multicast to each multicast activated slave card until a slave's word count is exhausted or the master stops writing to the multicast address. Each activated slave depends on its multicast address generator to supply the memory address and maintain the count or words still to be transferred. The MAG address counter is not incremented and the word count not decremented if BRETRY is asserted by any interface being multicast into before the broadcast data acknowledge has gone high.

The parity section generates and checks parity during master and slave data transfer operations. When the interface is acting as a master, the interface parity section generates the physical address parity. If the interface is a master doing a write, then the interface generates the appropriate data parity, if the data transfer is a read, then the incoming data parity is check against that transmitted with the data. If the master is multicasting, then the data parity is generated and sent along with the data. If the interface is acting as a slave handling a memory request or interrupt vector request, then the parity of the address lines is compared with that generated at the slave board. If the slave request is a read then the parity of the data being read is generated and sent along with the data. For a slave being written into, the parity of the incoming data is checked with that generated by the slave interface. During a memory reference or interrupt handler transaction a mismatch in address or data parity causes the slave to send retry back to the master. For a multicast slave reference the parity of the data is generated by the slave and compared with that generated and sent along with the data is generated by the slave and compared with that generated and sent along with the data is generated by the slave generated parity and the slave generated and sent along with the data by the multicasting master. If the multicast cycle.

The **chip select** section serves to direct references by the interface host to the interface control page or RAPIDbus resources. After address translation is completed, the physical address is compared to the control page address. If the master reference is not to the control page, then the reference is directed to the RAPIDbus drivers. If the reference is decoded for the interface control page, then further decoding identifies the reference as a multicast, multicast control, interface control register, or memory management unit reference, selecting the appropriate device or in the case of the multicast, the interface RAPIDbus multicast server.

The timing generation section controls the timing of the interface state sequencing. This section generates the multicast and regular address strobes when the respective address lines are ready for the RAPIDbus drivers, and generates decode enables and DTACK for the interface mapped resources.

The interrupt control section supports interrupt generation and interrupt handler vector requesting. This section presents to the Versabus port on the interface only those interrupts that the interface host is strapped to uniquely handle. At one of these levels the interface MMU, if present, is strapped to interrupt. The interface host is able to generate any one of the seven levels of RAPIDbus interrupts. The interrupt level being generated by the host is binary encoded so that the latch section can recognize the level of interrupt being generated by this interface and latch in the interrupt handler. The interrupt controller also recognizes when the interface host is acting as an interrupt handler, blocking the interrupt handler request from driving the RAPIDbus until the interface that would like to act as an interrupt handler is driving the interrupt block line. After the interrupt block line is being driven by this interface, the acknowledge out for the interrupt daisy chain is delayed by a clock cycle and then supplied to the interrupt handler bus sequence has not been received at

the level generated by this interface, then the interrupt acknowledge output is driven low. If the interrupt acknowledge input is received along the daisy chain and the interrupt handler request has been received, then the interface host has it Versabus ACKIN driven low. The interrupt control section is also responsible for monitoring the RAPIDbus reset line and driving the interface and host reset lines low if the RAPIDbus reset line is asserted.

The control section knits together the other function blocks and controls the logical state of the interface. The ownership of the lbus is decided by the control section. The interface host bus error, retry, data acknowledge, and halt is generated by this section. The RAPIDbus timeout timer and retry limit counter are supplied by the control section. The control section contains the control register which allows dynamic configuration of the interface parameters such as the masking address, the address translation path, and the auxillary memory map. Control signals which gate the drivers onto the RAPIDbus. RAPIDbus signals from the first to second latch levels, and the output enables that gate the second level latch onto the lbus are controlled here.

#### 3.3 Reading and Writing on the Bus

Read and write operations are the primary transfer operations for inputting or outputting data for further processing, storage, or display. Both operations are similar in their use of the RAPIDbus virtual bus structure, differing primarily in the directional configuration of the data lines linking master and slave, and in the handling of the data transfer request by the slave memory system.

#### 3.3.1 Read Operations

Read operations are initiated by an instruction fetch or memory reference within an instruction that is executed by a Versabus host processor. The read operation involves the RAPIDbus if the address received by the Versabus controller on the Versabus host card is interpreted by the controller as being within the RAPIDbus address space, or the master's interface control page, or the control page of a RAPIDbus slave. If the Versabus controller on the host card has not already obtained mastership of the RAPIDbus interface card lbus, then the Versabus controller generates a bus request level one to the interface card. Some Versabus processor cards support a block move option in which bit five of the Versamodule control register is set to initiate a block transfer, holding onto mastership of the interface lbus until bit five is cleared.

After the Versabus port has gained mastership of the Ibus, and the DTACK, bus error, and retry signals have gone high on the Ibus from previous data transfer operations, then the Versabus port drives the address, address modifier, address strobe, write, longword, and data strobe lines. As soon as the address strobe is asserted low the address translation chapter of the RAPIDbus interface card begins translation of the upper address lines A8 through A23. If bit three of the interface control register is cleared, then the Versabus port virtual address is mapped directly into the RAPIDbus physical address. If bit three of the interface control register is set then the address is translated by the memory management unit. For information on the translation function performed by the memory management unit, see the section on address translation. When the address translation process is completed, the physical address strobe is asserted. The physical data strobes are also enabled for assertion by the Versabus port.

The physical address is then mapped by the select unit, either onto the interface control page to access control page registers, or to the RAPIDbus virtual bus assigned to this processor. If the reference is mapped to the processor's interface control page then the lower bits of address are decoded to select the interface control page device. If at least one of the data strobes have not been asserted by this time, the interface waits until one is asserted. When the first data strobe is asserted by the Versabus port, the write line should still be high, indicating a read operation. The selected control page device then decodes the requisite internal register the contents are gated onto the Ibus data lines as selected by the data strobes and the longword control line. The data acknowledge signal is returned to the processor by the interface control section. The processor responds by latching in the requested data and removing the address strobe. The interface then removes the data acknowledge and releases the data lines. If an interface register had been selected that could not be read then a bus error returns to the processor is place of the data acknowledge, terminating the transfer cycle. If the transfer was part of a block move then the Ibus would remain allocated to the Versabus port (unless requested by a higher priority device, see the chapter on the Ibus). If the Ibus were requested by the read instruction directly, then it would be released by the Versabus port.