CMU-CS-82-153

# Local Code Generation and Compaction in Optimizing Microcode Compilers

المراجع والمراجع والمراجع والمراجع والمراجع والمتحر والمراجع والمراجع والمراجع والمراجع والمراجع والمراجع والمراجع

Steven R. Vegdahl

December 1982

Computer Science Department Carnegie-Mellon University Pittsburgh, PA 15213

Submitted to Carnegie-Mellon University in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Copyright © 1982 Steven R. Vegdahl

This work was supported in part by the Fannie and John Hertz Foundation and in part by the Defense Advanced Research Projects Agency (DOD), ARPA Order No. 3597, monitored by the Air Force Avionics Laboratory Under Contract F33615-78-C-1551.

The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the US Government.

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REPORT NUMBER 2. GOVT ACCESSION NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | J. RECIPIENT'S CATALOG NUMBER                                                                                                                                                |

| СМИ-СS-82-153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                              |

| . TITLE (and Subtitle)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5. TYPE OF REPORT & PERIOD COVERED                                                                                                                                           |

| LOCAL CODE GENERATION AND COMPACTION IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Interim                                                                                                                                                                      |

| OPTIMIZING MICROCODE COMPILERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6. PERFORMING ORG. REPORT NUMBER                                                                                                                                             |

| . AUTHOR(+)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | S. CONTRACT OF GRANT NUMBER/0)                                                                                                                                               |

| STEVEN R VEGDHAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | F33615-78-C-1551                                                                                                                                                             |

| SIEVER K VEGEMIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                              |

| PERFORMING ORGANIZATION NAME AND ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS                                                                                                               |

| Carnegie-Mellon University<br>Department of Computer Science                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                              |

| Pittsburgh, Pennsylvania 15213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                              |

| 1 CONTROLLING OFFICE NAME AND ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12. REPORT DATE                                                                                                                                                              |

| Defense Advanced Research Projects Agency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | December 1982                                                                                                                                                                |

| 1400 Wilson Blvd<br>Arlington, Virginia Alecti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13D & COMERING E PAGES                                                                                                                                                       |

| 4. MONITORING AGENCY NAME & ADDRESS(II different from Controlling Office)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15. SECURITY CLASS. (of this report)                                                                                                                                         |

| Air Force Office of Scientific Research (NM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                              |

| Bolling AFB, DC 20332                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 154. DECLASSIFICATION / DOWNGRADING<br>SCHEDULE                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SCHEDULE                                                                                                                                                                     |

| Approved for public release; distribution unlimit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ed.                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                              |

| Approved for public release; distribution unlimit<br>7. DISTRIBUTION STATEMENT (of the about and in Block 20, 11 different fro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                              |

| 7. DISTRIBUTION STATEMENT (of the ediatract entered in Block 20, if different fro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                              |

| 7. DISTRIBUTION STATEMENT (of the abatract entered in Block 20, 11 different fro<br>8. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oan Report)                                                                                                                                                                  |

| 7. DISTRIBUTION STATEMENT (of the ediatract entered in Block 20, if different fro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | oan Report)                                                                                                                                                                  |

| 7. DISTRIBUTION STATEMENT (of the abatract entered in Block 20, 11 different fro<br>8. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oan Report)                                                                                                                                                                  |

| 7. DISTRIBUTION STATEMENT (of the abatract entered in Block 20, 11 different fro<br>8. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oan Report)                                                                                                                                                                  |

| 7. DISTRIBUTION STATEMENT (of the abatract entered in Block 20, 11 different fro<br>8. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oen Report)                                                                                                                                                                  |

| 7. DISTRIBUTION STATEMENT (of the addition of        | ake it difficult for a compiler to                                                                                                                                           |

| 7. DISTRIBUTION STATEMENT (of the abattract entered in Block 20, if different fro<br>8. SUPPLEMENTARY NOTES<br>9. KEY WORDS /Continue on reverse eide II necessary and identify by block number,<br>9. ABSTRACT /Continue on reverse eide II necessary and identify by block number,<br>Horizontal microarchitectures often have features that ma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ake it difficult for a compiler to<br>bugh the problem of compacting                                                                                                         |

| <ul> <li>DISTRIBUTION STATEMENT (of the additional and in Block 20, 11 different from the additional and the state of the additional and the state of the sta</li></ul> | ake it difficult for a compiler to<br>bugh the problem of compacting<br>s has received a great deal of                                                                       |

| 7. DISTRIBUTION STATEMENT (of the abbriract entered in Block 20, 11 different fro<br>8. SUPPLEMENTARY NOTES<br>9. KEY WORDS /Continue on reverse elde II necessary and identify by block number<br>9. Horizontal microarchitectures often have features that ma<br>9. produce good object code from a high-level language. Altho<br>10. microcode into a near-minimal number of microinstructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ake it difficult for a compiler to<br>bugh the problem of compacting<br>s has received a great deal of<br>as thoroughly. This dissertation                                   |

| 7. DISTRIBUTION STATEMENT (of the abbriract entered in Block 20, 11 different fro<br>8. SUPPLEMENTARY NOTES<br>9. KEY WORDS / Continue on reverse elde II necessary and identify by block number,<br>Horizontal microarchitectures often have features that ma<br>produce good object code from a high-level language. Altho<br>microcode into a near-minimal number of microinstructions<br>attention, other phases of the compiler have not been studied                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ake it difficult for a compiler to<br>bugh the problem of compacting<br>s has received a great deal of<br>as thoroughly. This dissertation<br>horizontal microarchitectures, |

#### SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered)

There are often several code sequences that perform the same computation for a given microarchitecture. If the code generation and compaction phases of the compiler are executed sequentially, the code generator may not be able to determine the best code, because a code sequence that compacts well in one situation may contain several bottlenecks in another. This dissertation explores three methods of coupling the *code generation* and *compaction* phases of the compiler, and concludes that subtle micromachine features make it very difficult to produce good code unless the code generator actually produces several candidate code sequences that are compacted and compared with one another.

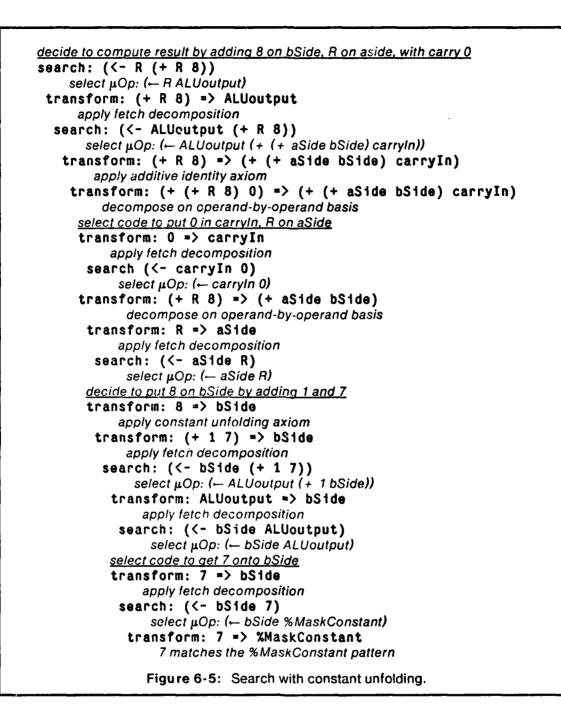

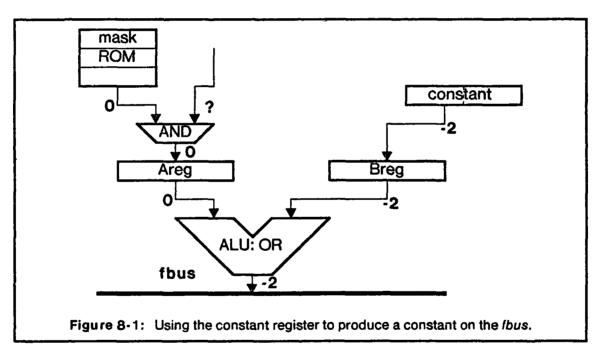

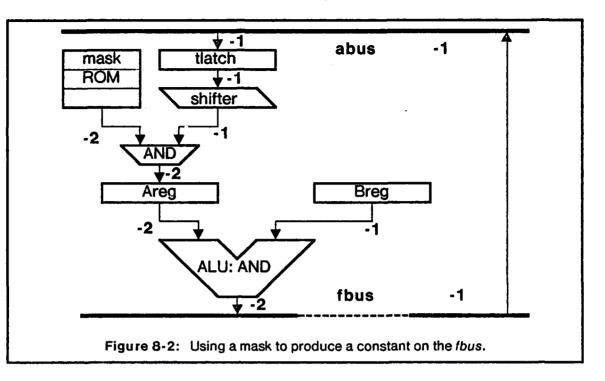

This dissertation also explores machine-independent methods of generating microcode. One aspect of the code generation problem—that of generating constants "intelligently"—is discussed in detail. A technique called *constant unfolding* is presented that can be used to produce code sequences that generate constants in "unusual" ways during execution; such code sequences often lead to more compact code when the literal field of the microinstruction is a bottleneck.

The classical microcode compaction problem is also examined. We show that this NP-hard problem can be solved in polynomial time if the number of registers in the micromachine is bounded, and use this result to argue that the problem is not general enough. A heuristic algorithm is presented for solving the general problem.

# Abstract

i

Horizontal microarchitectures often have features that make it difficult for a compiler to produce good object code from a high-level language. Although the problem of compacting microcode into a near-minimal number of microinstructions has received a great deal of attention, other phases of the compiler have not been studied as thoroughly. This dissertation explores methods of *generating* quality microcode for horizontal microarchitectures, *compacting* the microcode, and the interaction between code generation and compaction.

There are often several code sequences that perform the same computation for a given microarchitecture. If the code generation and compaction phases of the compiler are executed sequentially, the code generator may not be able to determine the best code, because a code sequence that compacts well in one situation may contain several bottlemecks in another. This dissertation explores three methods of coupling the code generator phases of the compiler, and concludes that subtle micromachine features make it very difficult to produce good code unless the code generator actually produces several candidate code sequences that are compacted and compared with one another.

This dissertation also explores machine-independent methods of generating microcode. One aspect of the code generation problem—that of generating constants "intelligently"—is discussed in detail. A technique called *constant unfolding* is presented that can be used to produce code sequences that generate constants in "unusual" ways during execution; such code sequences often lead to more compact code when the literal field of the microinstruction is a bottleneck.

The classical microcode compaction problem is also examined. We show that this NP-hard problem can be solved in polynomial time if the number of registers in the micromachine is bounded, and use this result to argue that the problem is not general enough. A heuristic algorithm is presented for solving the general problem.

# Acknowledgements

I wish to thank my advisor, Anita Jones, for much helpful guidance and encouragement during the course of this research. I would also like to thank the rest of my committee, Rick Cattell, Joe Newcomer and Guy Steele for their many helpful suggestions on improving this manuscript. I am especially grateful to Guy and his wife Barbara for their emotional support during times when the completion of this dissertation seemed an endless task.

I wish to acknowledge the following teachers, professors, and employers who played key roles in my scholastic development during my grade school, high school, or college years: Bill Wright, Maxeye Hanley, Francis Brewer, Ron Henley, Bill Colescott, and Don Knuth.

I am also grateful to the Fannie and John Hertz Foundation for its financial support during my years at CMU.