| AD-A113 633 BOEING MILITARY AIRPLANE CO SEATTLE WA F/6 10/2<br>Advanced Aircraft Electrical System Control Technology Demonstr-etc(U)<br>Jan 82 t r Boldt, 6 L dunn, 0 E Mankins F33615-80-(-2004<br>UNCLASSIFIED D160-25927-3 AFWAL-TR-81-2128 NL |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 1 = 2<br>2)<br>2)<br>2)<br>2)<br>2)<br>2)<br>2)<br>2)<br>2)<br>2)<br>2)<br>2)<br>2)                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

AFWAL - TR - 81 - 2128

AD A11363

A. 1. 1. 1.

3

# ADVANCED AIRCRAFT ELECTRICAL SYSTEM CONTROL TECHNOLOGY DEMONSTRATOR

- Phase I: Analysis & Preliminary Design

G. L. Dunn D. E. Hankins P. J. Leong I. S. Mehdi

BOEING MILITARY AIRPLANE COMPANY

SEATTLE, WASHINGTON

JANUARY 1982

INTERIM REPORT FOR THE PERIOD MARCH 1981 TO OCTOBER 1981

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED

AERO PROPULSION LABORATORY **AIR FORCE WRIGHT AERONAUTICAL LABORATORIES** AIR FORCE SYSTEMS COMMAND WRIGHT - PATTERSON AIR FORCE BASE, OHIO 45433 82 04 089 19

#### NOTICE

When Government drawings, specifications, or other data are used for any purpose other than in connection with a definitely related Government procurement operation, the United States Government thereby incurs no responsibility nor any obligation whatsoever; and the fact that the government may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data, is not to be regarded by implication or otherwise as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture use, or sell any patented invention that may in any way be related thereto.

This report has been reviewed by the Office of Public Affairs (ASD/PA) and is releasable to the National Technical Information Service (NTIS). At NTIS, it will be available to the general public, including foreign nations.

This technical report has been reviewed and is approved for publication.

wane & Ave

DUANE G. FOX Project Engineer Power Systems Branch Aerospace Power Division

FOR THE COMMANDER

ama

UNITS D. REAMS Chief, Aerospace Power Division Aero Propulsion Laboratory

K. Best heard

PAUL R. BERTHEAUD Technical Area Manager Power Systems Branch Aerospace Power Division

"If your address has changed, if you wish to be removed from our mailing list, or if the addressee is no longer employed by your organization please notify <u>AFWAL/POOS</u>-2. W-PAFB, OH \_45433 to help us maintain a current mailing list".

Copies of this report should not be returned unless return is required by security considerations, contractual obligations, or notice on a specific document.

| REPORT DOCUMENTAT                                                                                                                                                                                                                                                                                                | ION PAGE                                                                                                      |                                                                                                                                                                     | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I. REPORT NUMBER                                                                                                                                                                                                                                                                                                 | 2. GOVT ACC                                                                                                   | ESSION NO.                                                                                                                                                          | 3. RECIPIENT'S CATALOG NUMBER                                                                                                                                                                                               |

| AFWAL - TR-81-2128                                                                                                                                                                                                                                                                                               | AD-AI                                                                                                         | 1363                                                                                                                                                                | 3                                                                                                                                                                                                                           |

| 4. TITLE (and Subtitie)                                                                                                                                                                                                                                                                                          |                                                                                                               | 1                                                                                                                                                                   | 5. TYPE OF REPORT & PERIOD COVERED                                                                                                                                                                                          |

| Advanced Aircraft Electrical                                                                                                                                                                                                                                                                                     |                                                                                                               |                                                                                                                                                                     | Interim Technical Report<br>Mar 1, 1981 - Sept 30, 1981                                                                                                                                                                     |

| Technology Demonstrator Phase<br>And Preliminary Design                                                                                                                                                                                                                                                          | I - Analysis                                                                                                  |                                                                                                                                                                     | Mar 1, 1981 - Sept 30, 1981<br>6. PERFORMING O'G. REPORT NUMBER                                                                                                                                                             |

| 7. AUTHOR(e)                                                                                                                                                                                                                                                                                                     |                                                                                                               |                                                                                                                                                                     | D180-25927-3<br>6. CONTRACT OR GRANT NUMBER(*)                                                                                                                                                                              |

| T. R. Boldt P. J. Leong                                                                                                                                                                                                                                                                                          |                                                                                                               | {                                                                                                                                                                   | F33615-80-C-2004                                                                                                                                                                                                            |

| G. L. Dunn I. S. Mehdi                                                                                                                                                                                                                                                                                           |                                                                                                               |                                                                                                                                                                     | -53013-80-6-2004                                                                                                                                                                                                            |

| D. E. Hankins<br>9. Performing organization name and add                                                                                                                                                                                                                                                         | DRESS                                                                                                         |                                                                                                                                                                     | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS                                                                                                                                                              |

| Mechanical/Electrical Systems                                                                                                                                                                                                                                                                                    |                                                                                                               |                                                                                                                                                                     | AREA & WORK UNIT NUMBERS                                                                                                                                                                                                    |

| Boeing Military Airplane Comp<br>M/S 47-03, P.O. Box 3707, Sea                                                                                                                                                                                                                                                   |                                                                                                               | 4                                                                                                                                                                   |                                                                                                                                                                                                                             |

| 11. CONTROLLING OFFICE NAME AND ADDRESS                                                                                                                                                                                                                                                                          |                                                                                                               |                                                                                                                                                                     | 12. REPORT DATE                                                                                                                                                                                                             |

| Aero Propulsion Laboratory (P                                                                                                                                                                                                                                                                                    |                                                                                                               |                                                                                                                                                                     | January 1982                                                                                                                                                                                                                |

| Air Force Wright Aeronautical                                                                                                                                                                                                                                                                                    | Laboratories                                                                                                  | <b>. Afj</b> (                                                                                                                                                      | 13. NUMBER OF PAGES                                                                                                                                                                                                         |

| Wright-Patterson Air Force Ba<br>14. MONITORING AGENCY NAME & ADDRESS()                                                                                                                                                                                                                                          | filferent from Controlf                                                                                       | ing Office)                                                                                                                                                         | 15. SECURITY CLASS. (of this report)                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                  |                                                                                                               | }                                                                                                                                                                   | Unclassified                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                  |                                                                                                               | ŀ                                                                                                                                                                   | 154. DECLASSIFICATION/DOWNGRADING<br>SCHEDULE                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                  |                                                                                                               |                                                                                                                                                                     |                                                                                                                                                                                                                             |

| Approved for public release;                                                                                                                                                                                                                                                                                     |                                                                                                               |                                                                                                                                                                     |                                                                                                                                                                                                                             |

| 16. DISTRIBUTION STATEMENT (of this Report)<br>Approved for public release;<br>17. DISTRIBUTION STATEMENT (of the abstract o                                                                                                                                                                                     |                                                                                                               |                                                                                                                                                                     |                                                                                                                                                                                                                             |

| Approved for public release;<br>17. DISTRIBUTION STATEMENT (of the abotract of<br>18. SUPPLEMENTARY NOTES                                                                                                                                                                                                        | ntered in Block 20, il                                                                                        | f different from                                                                                                                                                    | Report)                                                                                                                                                                                                                     |

| Approved for public release;<br>17. DISTRIBUTION STATEMENT (of the abstract of<br>18. SUPPLEMENTARY NOTES<br>Requirement                                                                                                                                                                                         | ntered in Block 20, 11                                                                                        | USSS                                                                                                                                                                |                                                                                                                                                                                                                             |

| Approved for public release;<br>17. DISTRIBUTION STATEMENT (of the abstract of<br>18. SUPPLEMENTARY NOTES<br>Requirementary<br>19. Key WORDS (Continue on reverse eide it neces                                                                                                                                  | ntered in Block 20, 11                                                                                        | t dillerent from                                                                                                                                                    | Task 2- Onceptual                                                                                                                                                                                                           |

| Approved for public release;<br>17. DISTRIBUTION STATEMENT (of the abstract of<br>18. SUPPLEMENTARY NOTES<br>- Requirementary<br>19. Key WORDS (Continue on reverse eide it neces<br>DAIS                                                                                                                        | ntered in Block 20, il                                                                                        | t dillerent from                                                                                                                                                    | Task 2- Onceptual<br>anagement                                                                                                                                                                                              |

| Approved for public release;<br>17. DISTRIBUTION STATEMENT (of the abstract of<br>18. SUPPLEMENTARY NOTES<br>TREQUITEMENT<br>19. KEY WORDS (Continue on reverse eide if neces<br>DAIS<br>Electrical Load Management Cen<br>Electrical System                                                                     | ntered in Block 20, il                                                                                        | t dillerent from                                                                                                                                                    | Task 2- Onceptual                                                                                                                                                                                                           |

| Approved for public release;<br>17. DISTRIBUTION STATEMENT (of the abstract of<br>18. SUPPLEMENTARY NOTES<br>TREQUITEMENTARY NOTES<br>19. KEY WORDS (Continue on reverse eide if neces<br>DAIS<br>Electrical Load Management Cen<br>Electrical System<br>EMUX                                                    | nter (ELMC)                                                                                                   | t dillerent from<br>USSS<br>Nock number)<br>Load Mi<br>Remote<br>Solld S                                                                                            | Task 2- onceptual<br>anagement<br>Terminal (RT)                                                                                                                                                                             |

| Approved for public release;<br>17. DISTRIBUTION STATEMENT (of the abstract of<br>18. SUPPLEMENTARY NOTES<br>TREQUITEMENTARY NOTES<br>19. KEY WORDS (Continue on reverse eide if neces<br>DAIS<br>Electrical Load Management Cel<br>Electrical System<br>EMUX<br>28. ABSTRACT (Continue on reverse eide if neces | nter (ELMC)                                                                                                   | I dillerent from<br>Nock number)<br>Load M<br>Remote<br>Solld S                                                                                                     | Task 2- onceptual<br>anagement<br>Terminal (RT)<br>State Power Controller (SSPC                                                                                                                                             |

| Approved for public release;<br>17. DISTRIBUTION STATEMENT (of the abstract of<br>18. SUPPLEMENTARY NOTES<br>TREQUITEMENTARY NOTES<br>19. KEY WORDS (Continue on reverse eide if neces<br>DAIS<br>Electrical Load Management Cen<br>Electrical System<br>EMUX                                                    | nter (ELMC)<br>and 2 and do<br>ogram. Task<br>system (AAES)<br>rame two-engi<br>performs the<br>ower to loads | t different from<br>t different from<br>block number)<br>Load Ma<br>Remote<br>Solid S<br>block number)<br>cuments<br>3 is the<br>. The Ai<br>ne taction<br>, system | Task 2- onceptual<br>anagement<br>Terminal (RT)<br>State Power Controller (SSPC<br>the results of Task 3,<br>preliminary design of an<br>AES is designed to meet the<br>cal aircraft with multi-<br>ns of power generation. |

1

a comunication of the second se

ł

UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE(When Data Entered)

- 20. ABSTRACT (continued)

- Integrated avionics and power data bus configuration consisting of Digital Avionics Information System (DAIS) standard elements (MIL-STD-1750 processor, MIL-STD-1553B data bus, controls and displays, and remote terminals (RT)).

- o A Intelligent Electrical Load Management Centers (ELMC) capable of controlling power to loads

- o Built-in-test (BIT) capability to isolate faults to the module level. BIT includes both circuit and data monitoring checks,

- o Solid State Power Controllers (SSPC) to replace circuit breakers and power control switches. SSPCs are turned on/off via computer control,

- o Generator control, protection and status monitoring by a Generator Control Unit (GCU) compatible with DAIS hardware and software.

- o Multimission data information system through programmable system processors, ELMCs and standard DAIS elements.

- o Automatic load management for increased aircraft survivability and probability of mission completion.

### UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE(When Data Entered)

#### PREFACE

This Interim Technical Report presents the results of work performed by the Boeing Military Airplane Company, Seattle, Washington, under Air Force Contract F33615-80-C-2004, during the period from March through September 1981. The work is sponsored by the Aero Propulsion Laboratory, Air Force Wright Aeronautical Laboratories, Wright-Patterson Air Force Base, Ohio, under Project 3145, Task 314529, Work Unit 31452959 with Mr. Duane G. Fox, AFWAL/POOS-2, as project engineer.

This document, which covers Task 3, Preliminary Design, of Phase I, fulfills the requirements of CDRL item number 9.

The program manager is I. S. Mehdi. The report was prepared by T. R. Boldt, G. L. Dunn, D. E. Hankins, and P. J. Leong who were technically responsible for the work.

| DTIB                           | NTIS<br>DTIC T<br>Unenso | AB       |         |  |

|--------------------------------|--------------------------|----------|---------|--|

| DIII<br>COPY<br>INSPECTED<br>2 | By<br>Distr<br>Avei      | lbution, | y Codes |  |

|                                | L <b>I.</b> [-           | 1        | L       |  |

## TABLE OF CONTENTS

| <u>SECTI</u> | ON    |                                         | PAGE |

|--------------|-------|-----------------------------------------|------|

| Ι.           | INTRO | DUCTION                                 | 1    |

|              | 1. 1  | Background                              | 1    |

|              | 2. 1  | Program Objectives                      | 2    |

|              | 3.    | Approach                                | 2    |

| п.           | RE QU | IREMENTS ANALYSIS AND CONCEPTUAL DESIGN | 6    |

|              | 1.    | Requirements Analysis                   | 6    |

|              | ä     | a. Load Analysis                        | 7    |

|              | ł     | b. Generation System                    | 9    |

|              | (     | c. Distribution System                  | 10   |

|              | (     | d. Flight Critical Power                | 11   |

|              | (     | e. Power Bus Configuration              | 13   |

|              | 1     | f. System Control and Protection        | 13   |

|              | ģ     | g. Applicability of J73/I (Jovial)      | 17   |

|              | ł     | n. Controls and Displays                | 17   |

|              | 2. (  | Control System Requirements             | 20   |

|              | ė     | a. Processing Requirements              | 22   |

|              | I     | b. Input/Output Requirements            | 23   |

|              | (     | c. Response Time                        | 23   |

|              | C     | d. Avionics Bus Loading                 | 24   |

|              | 3.    | Technical Analysis                      | 25   |

|              | ė     | a. General Assumptions                  | 27   |

|              | l     | b. Processor Loading                    | 29   |

|              | (     | c. Data Bus Loading                     | 30   |

|              | (     | d. Memory Requirements                  | 30   |

|              | (     | e. Reliability                          | 31   |

|              | 1     | f. Results of the Technical Analysis    | 32   |

|              | 4. 1  | Economic Analysis                       | 33   |

|              | 5.    | Conceptual Design                       | 34   |

|              | i     | a. Data Bus Architectures               | 34   |

|              | l     | . Non-Integrated Data Bus Architecture  | 35   |

## TABLE OF CONTENTS (continued)

| SECTI | ON |                                                      | PAGE |

|-------|----|------------------------------------------------------|------|

|       |    | c. Integrated Data Bus Architecture                  | 37   |

|       |    | d. Hierarchical Data Bus Architecture                | 39   |

|       | 6. | Selected Concept for Preliminary Design              | 41   |

| III.  | ٨D | ANCED A IRCRAFT ELECTRICAL SYSTEM PRELIMINARY DESIGN | 42   |

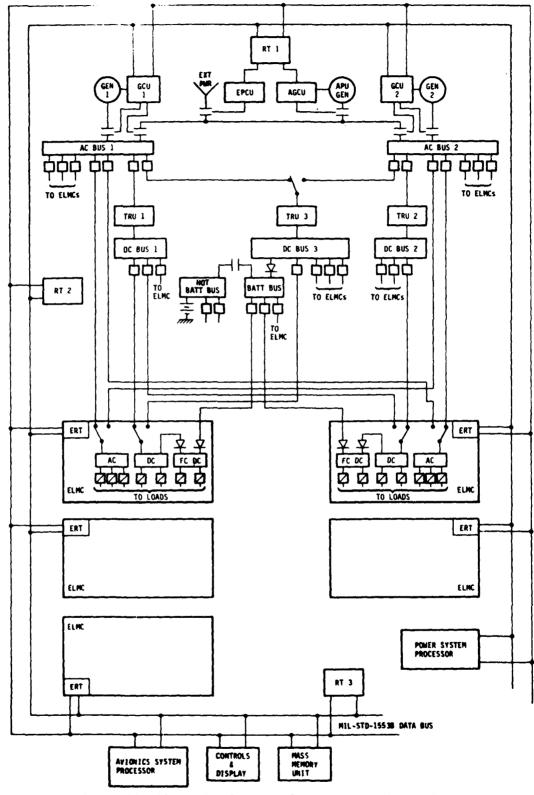

|       | 1. | Power System Configuration                           | 42   |

|       |    | a. System Characteristics                            | 44   |

|       |    | (1) AC System                                        | 45   |

|       |    | (2) DC System                                        | 45   |

|       |    | (3) External Power                                   | 47   |

|       |    | (4) Auxiliary Power                                  | 48   |

|       |    | (5) Generator Control Unit                           | 48   |

|       |    | b. System Operation                                  | 50   |

|       |    | (1) Startup                                          | 51   |

|       |    | (2) Steady State Creration                           | 54   |

|       |    | (3) Generator Failure and Faults                     | 54   |

|       |    | (4) External Power Operation                         | 57   |

|       |    | (5) Auxiliary Power Operation                        | 57   |

|       |    | (6) Processor and Data Bus Failure                   | 57   |

|       |    | (7) Load Management                                  | 57   |

|       | 2. | Integrated Power System Control                      | 58   |

|       |    | a. Multiplex Data Bus Characteristics                | 58   |

|       |    | b. Avionics/Electrical Control System Interface      | 60   |

|       |    | c. Electrical Control System                         | 60   |

|       |    | (1) Power System Processor                           | 64   |

|       |    | (a) PSP Hardware Description                         | 64   |

|       |    | (b) PSP Functional Requirements                      | 64   |

|       |    | (c) PSP Executive Software                           | 67   |

|       |    | (d) PSP Applications Software                        | 75   |

|       |    | (2) Electrical Load Managment Center                 | 82   |

|       |    | (a) ELMC Functional Description                      | 84   |

|       |    | (b) SSPC Control and Monitoring                      | 84   |

#### TABLE OF CONTENTS (continued)

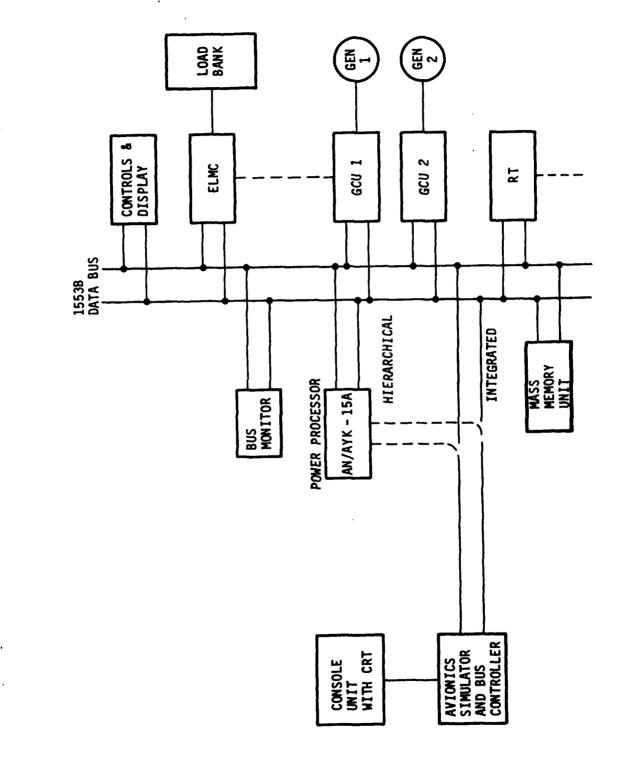

#### SECTION PAGE (c) Aircraft Discretes and Analog Signal Monitoring 86 (d) ERT Software Computations 86 (e) Built in Test 86 (3) Power Controllers 86 (a) Solid State Power Controllers 86 (b) Electro-Mechanical Power Controllers 87 (4) Electrical Remote Terminal 89 (a) ERT Functional Description 89 (b) ERT Executive Software 94 (c) ERT Applications Software 96 (5) Remote Terminal 99 (6) GCU/Data Bus Interface 103 (7) AGCU/Data Bus Interface 103 (8) EPCU/Data Bus Interface 106 3. Reliabililty, Maintainability, and Safety 106 LABORATORY SIMULATOR PRELIMINARY DESIGN IV. 108 1. Configuration 108 2. Hardware 108 a. Bus Monitor 110 b. System Test Console 110 c. Generator Stand 110 d. Load Bank 110 e. Generator Control Unit 110 f. Electrical Load Management Center 111 g. AN/AYK-15A Computer 111 h. Console with CRT 111 i. Avionics Simulator and Bus Controller 111 j. Remote Terminal 112 3. Software 112

vii

## TABLE OF CONTENTS (continued)

| SECT | ION |                               | PAGE |

|------|-----|-------------------------------|------|

| ۷.   | WOR | K EFFORTS FOR DETAILED DESIGN | 113  |

|      | 1.  | Avionics Processor            | 113  |

|      | 2.  | Power System Processor        | 113  |

|      | 3.  | ELMC                          | 114  |

|      |     | a. ELMC Hardware              | 114  |

|      |     | (1) SSPCs                     | 114  |

|      |     | (2) ERT                       | 115  |

|      |     | b. ERT Software               | 115  |

|      |     | (1) ERT Executive Software    | 115  |

|      |     | (2) ERT Application Software  | 115  |

|      | 4.  | Remote Terminals              | 115  |

|      | 5.  | GCU                           | 116  |

|      | 6.  | Controls and Displays         | 116  |

| VI.  | co  | NCLUSIONS AND RECOMMENDATIONS | 117  |

|      | 1.  | Results and Conclusions       | 117  |

|      | 2.  | Recommendations               | 118  |

|      |     |                               |      |

## REFERENCES

## LIST OF FIGURES

| FI | GURE |  |

|----|------|--|

|    |      |  |

f

....

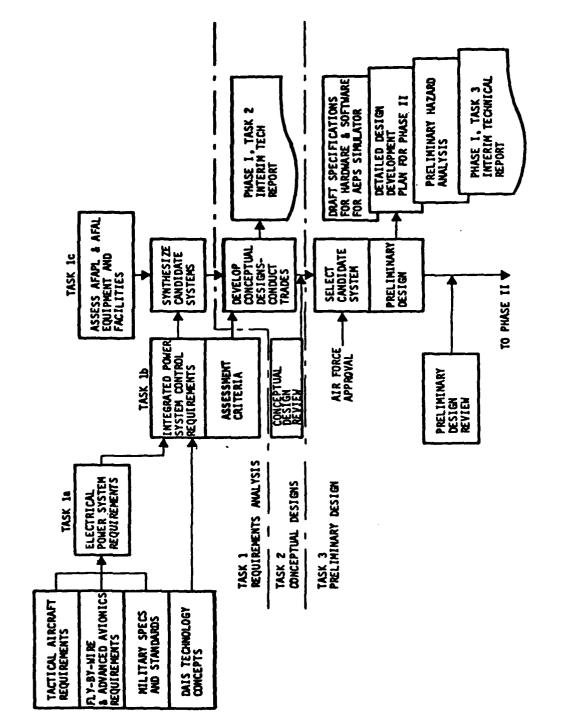

| 1  | Phase 1 Program Flow Chart                          |   | 4  |

|----|-----------------------------------------------------|---|----|

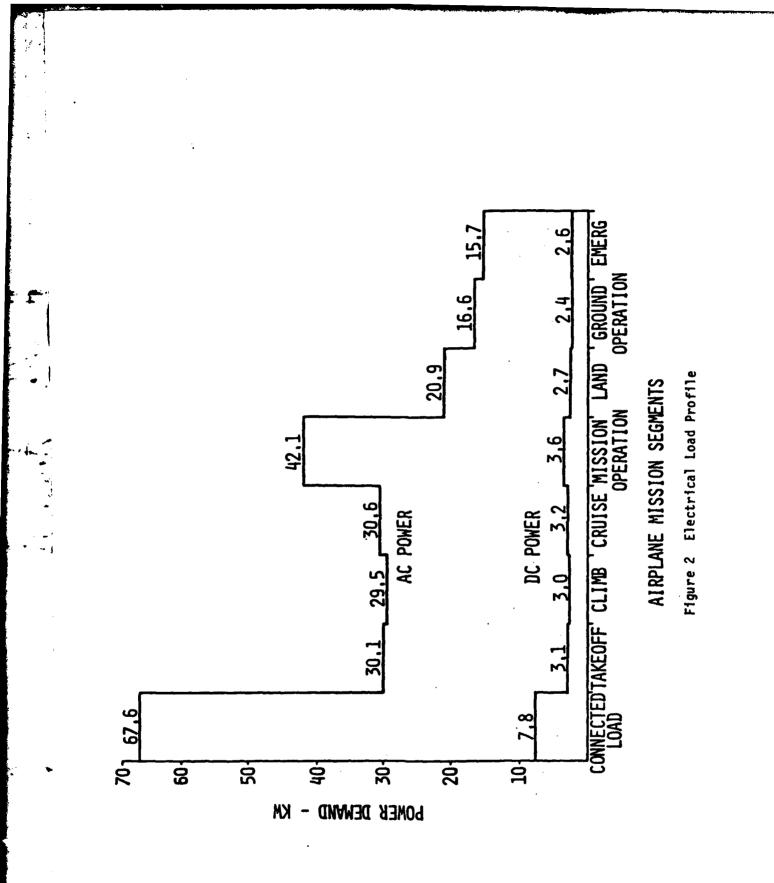

| 2  | Electrical Load Profile                             |   | 8  |

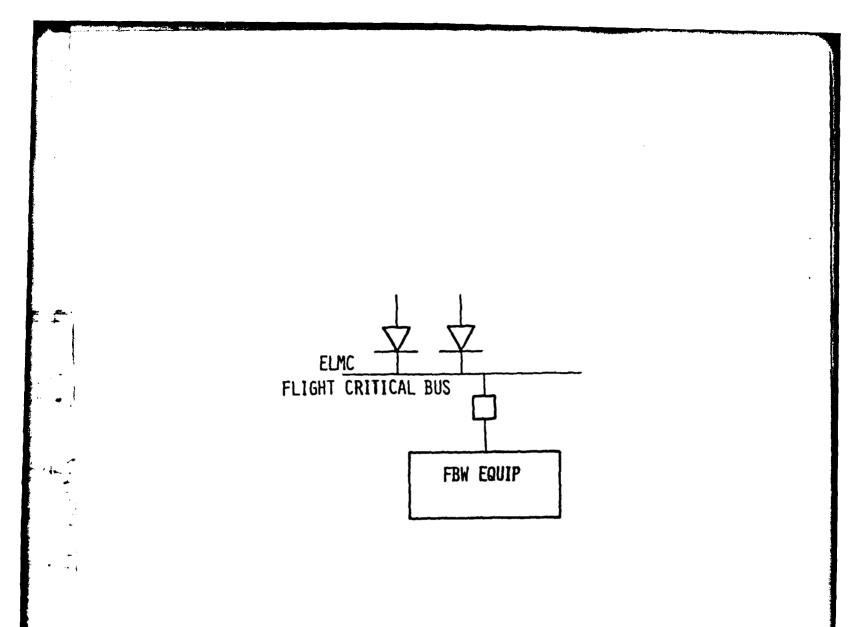

| 3  | Flight Critical Bus in the ELMC                     |   | 12 |

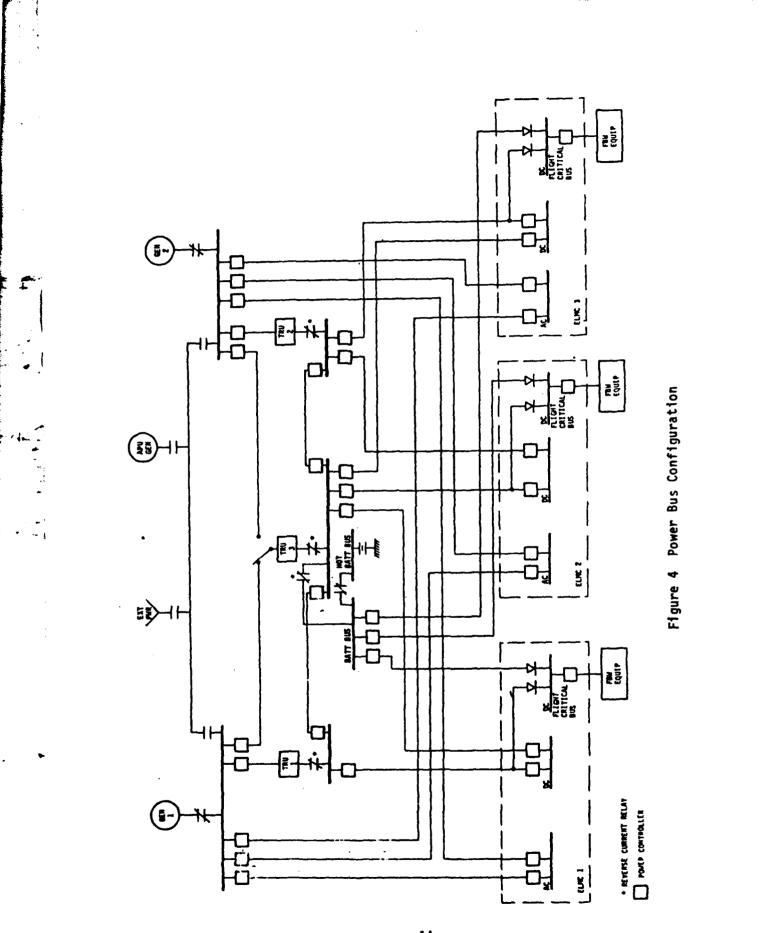

| 4  | Power Bus Configuration                             |   | 14 |

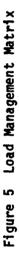

| 5  | Load Management Matrix                              |   | 18 |

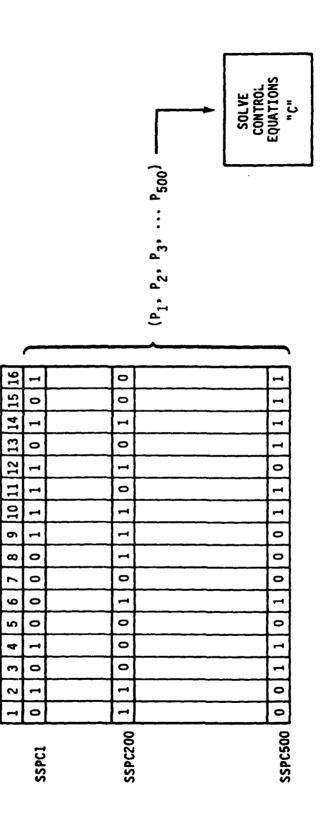

| 6  | Load Management Level Selection                     |   | 19 |

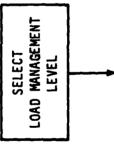

| 7  | DAIS Integrated Controls/Displays                   |   | 21 |

| 8  | Data Bus Architecture Configurations                |   | 26 |

| 9  | Baseline Non-Integrated Architecture                |   | 36 |

| 10 | Integrated Architecture                             |   | 38 |

| 11 | Hierarchical Architecture                           |   | 4C |

| 12 | Aircraft Electrical System Configuration            |   | 43 |

| 13 | AC and DC Power System Configuration                |   | 46 |

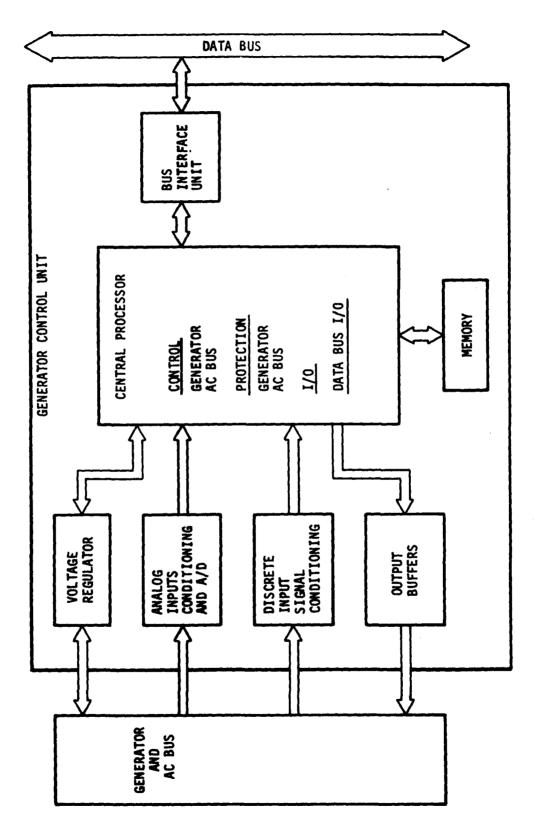

| 14 | Generator Control Unit Functional Diagram           |   | 49 |

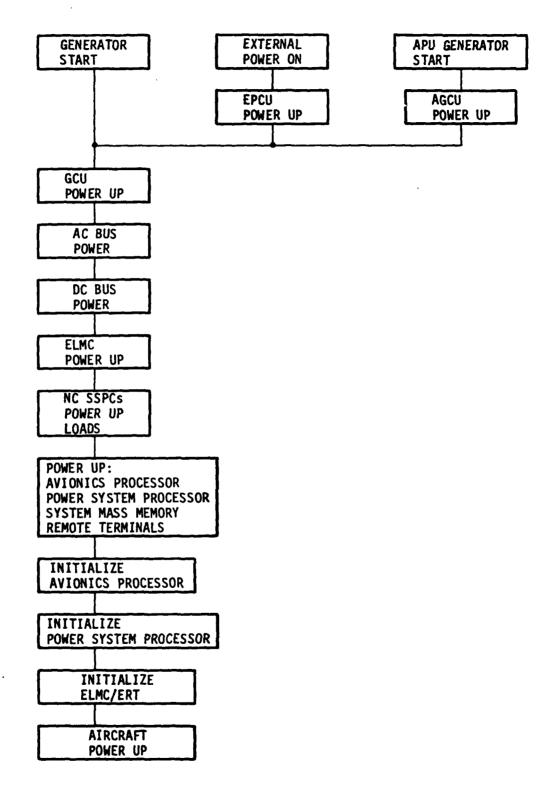

| 15 | Electrical System Startup                           |   | 52 |

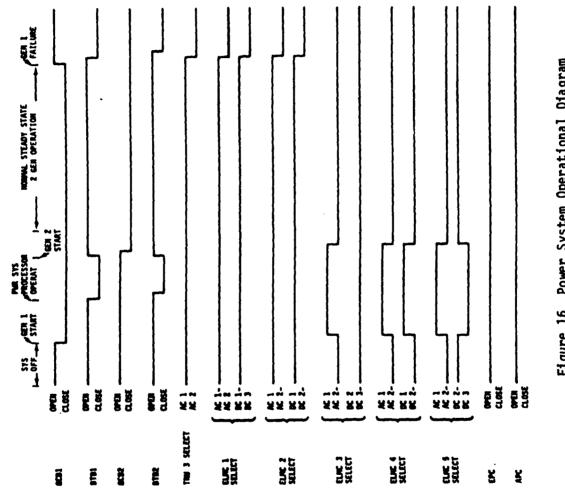

| 16 | Power System Operational Diagram                    |   | 53 |

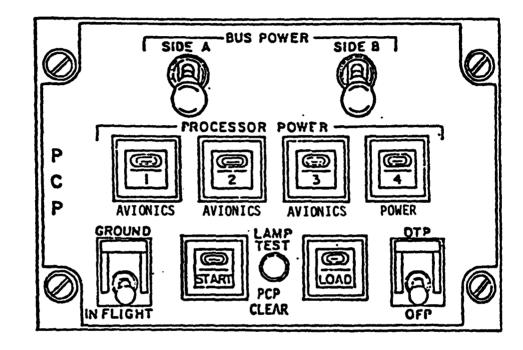

| 17 | Processor Control Panel                             |   | 55 |

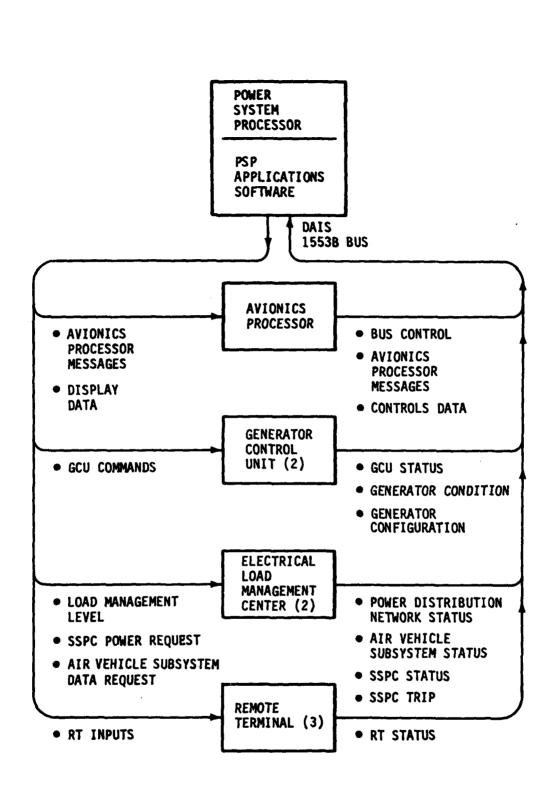

| 18 | Integrated Avionics and Electrical Control System   |   |    |

|    | Functional Diagram                                  | ١ | 59 |

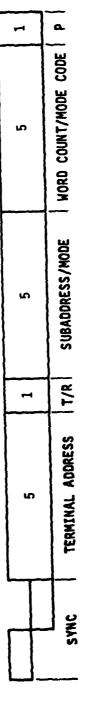

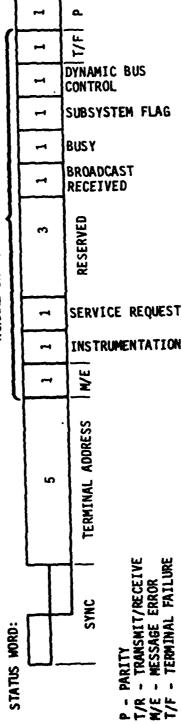

| 19 | 1553B Bus Message Word Formats                      |   | 61 |

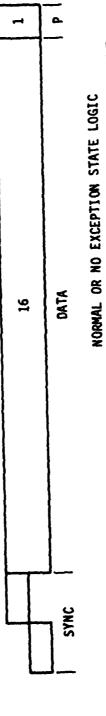

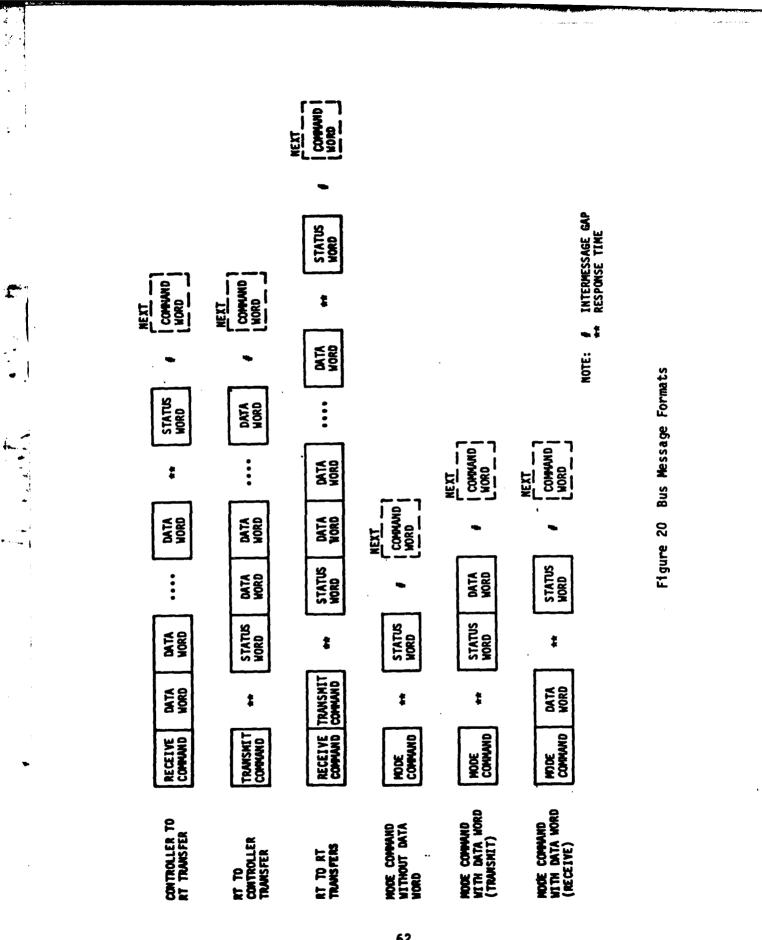

| 20 | Bus Message Formats                                 |   | 62 |

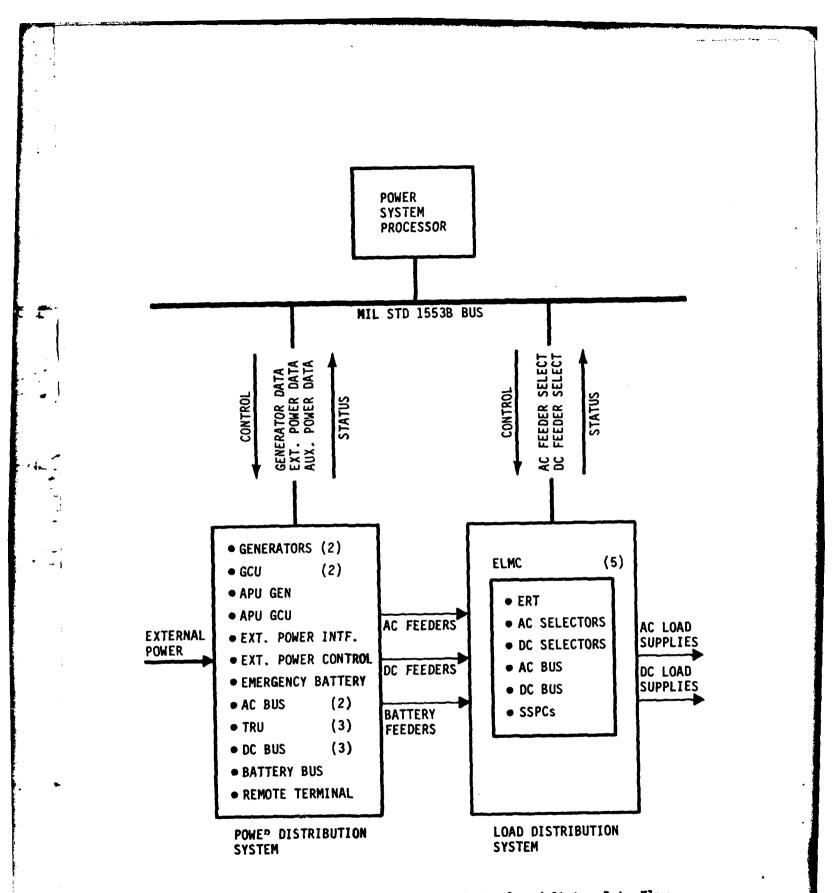

| 21 | Power System Processor Control and Status Data Flow |   | 66 |

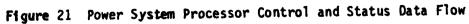

| 22 | Power System Processor Architecture with PSPE       |   | 69 |

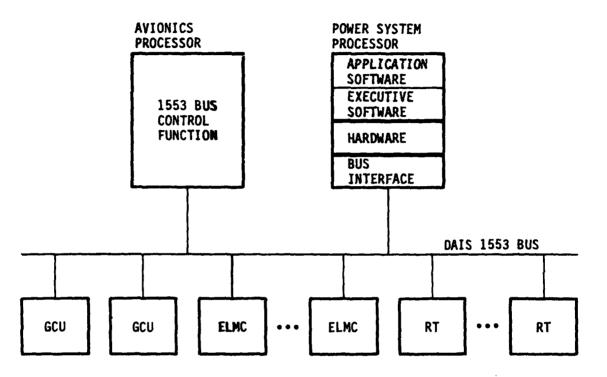

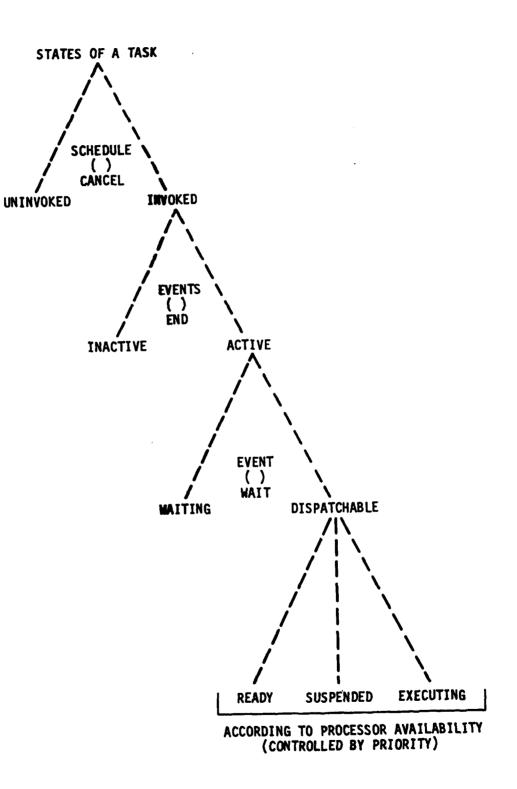

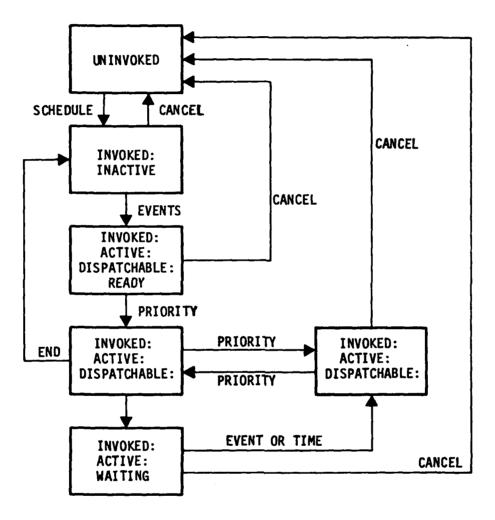

| 23 | Task States                                         |   | 71 |

| 24 | Task State Transition Diagram                       |   | 72 |

| 25 | PSP Applications Software Data Flow                 |   | 76 |

| 26 | Power Request Equation Example                      |   | 79 |

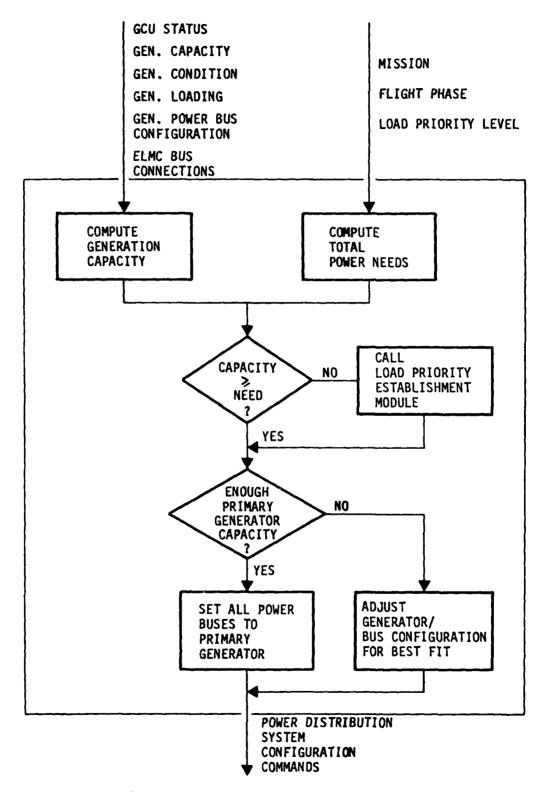

| 27 | Power Distribution System Configuration Control     |   | 81 |

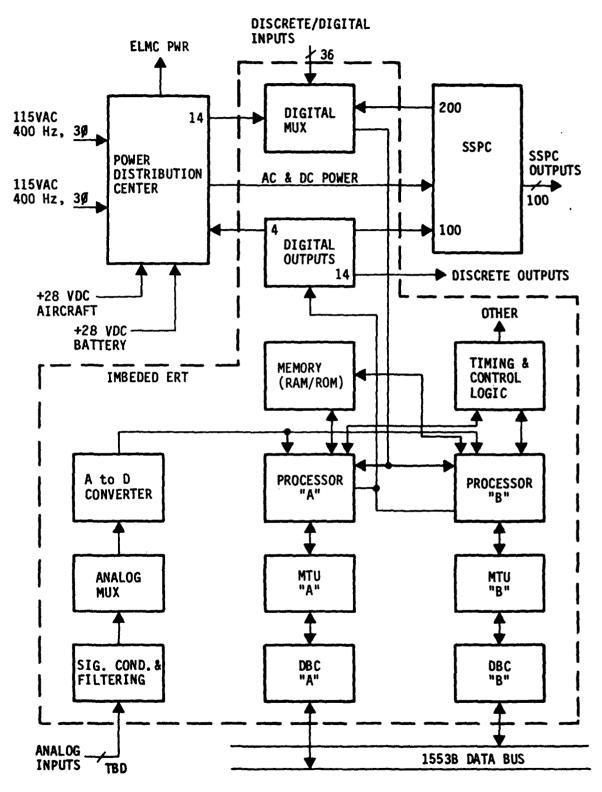

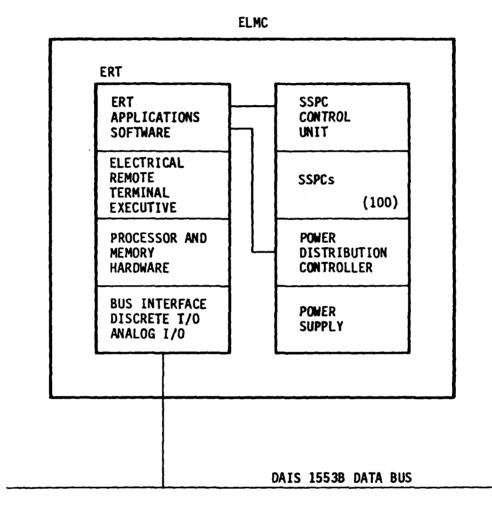

| 28 | ELMC Functional Diagram                             |   | 83 |

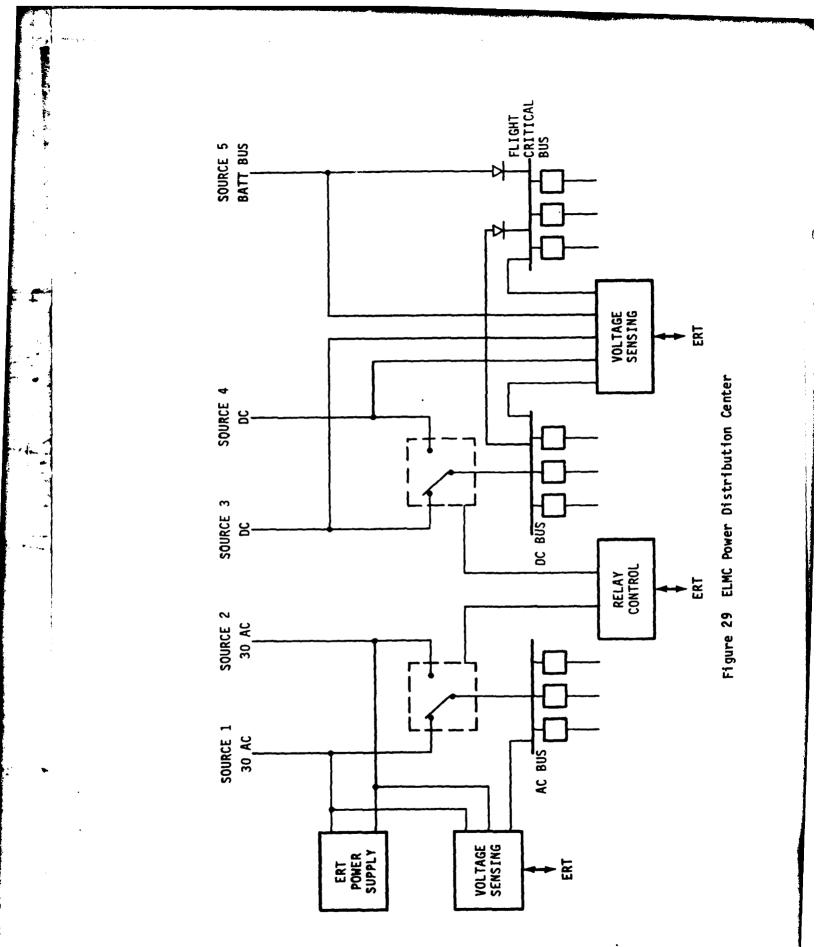

| 29 | ELMC Power Distribution Center                      |   | 85 |

## LIST OF FIGURES (continued)

## FIGURE

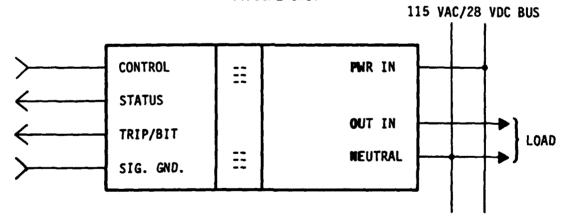

| 30 | SSPC Circuit Card and Configuration       | 88  |

|----|-------------------------------------------|-----|

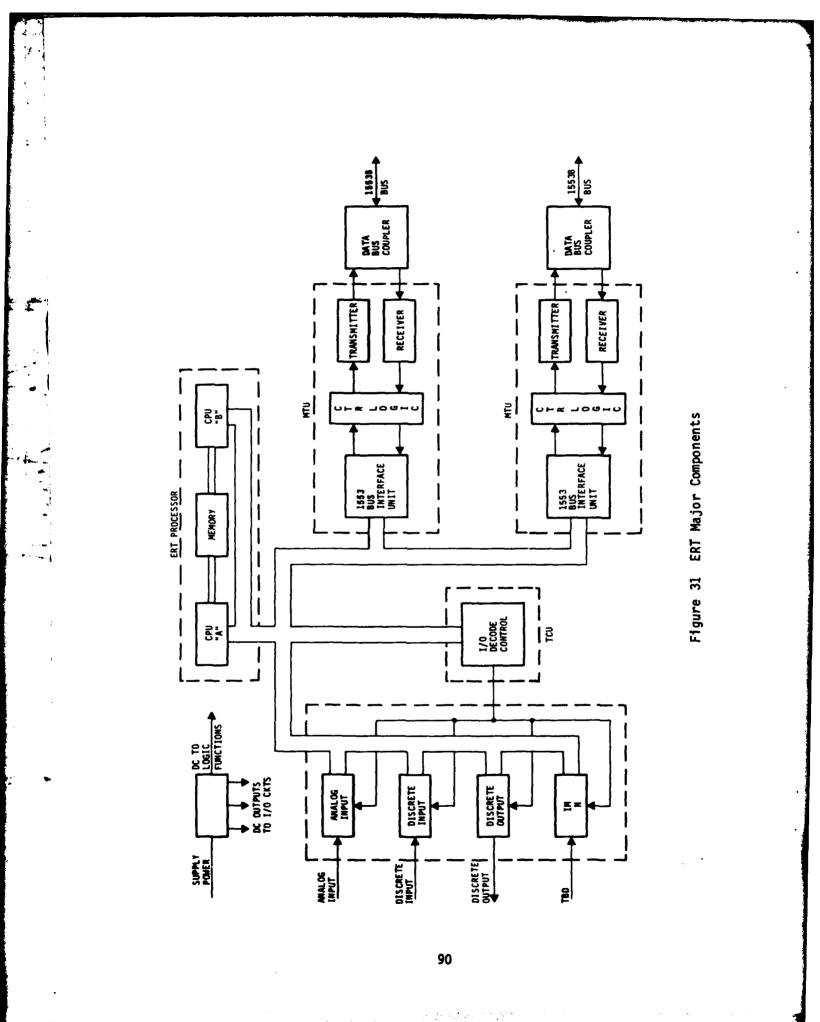

| 31 | ERT Major Components                      | 90  |

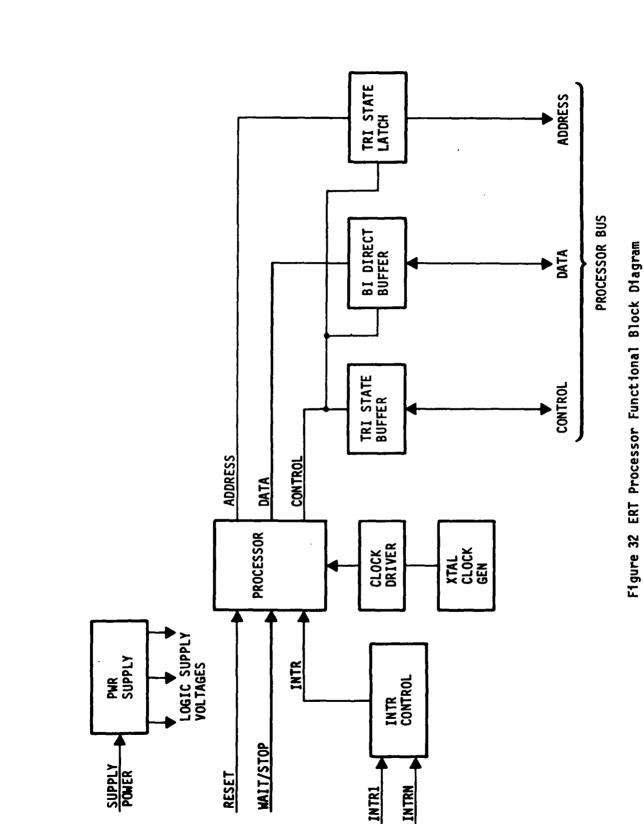

| 32 | ERT Processor Functional Block Diagram    | 92  |

| 33 | ELMC Architecture Including ERT Executive | 95  |

| 34 | BIT Word Format and Failure Codes         | 102 |

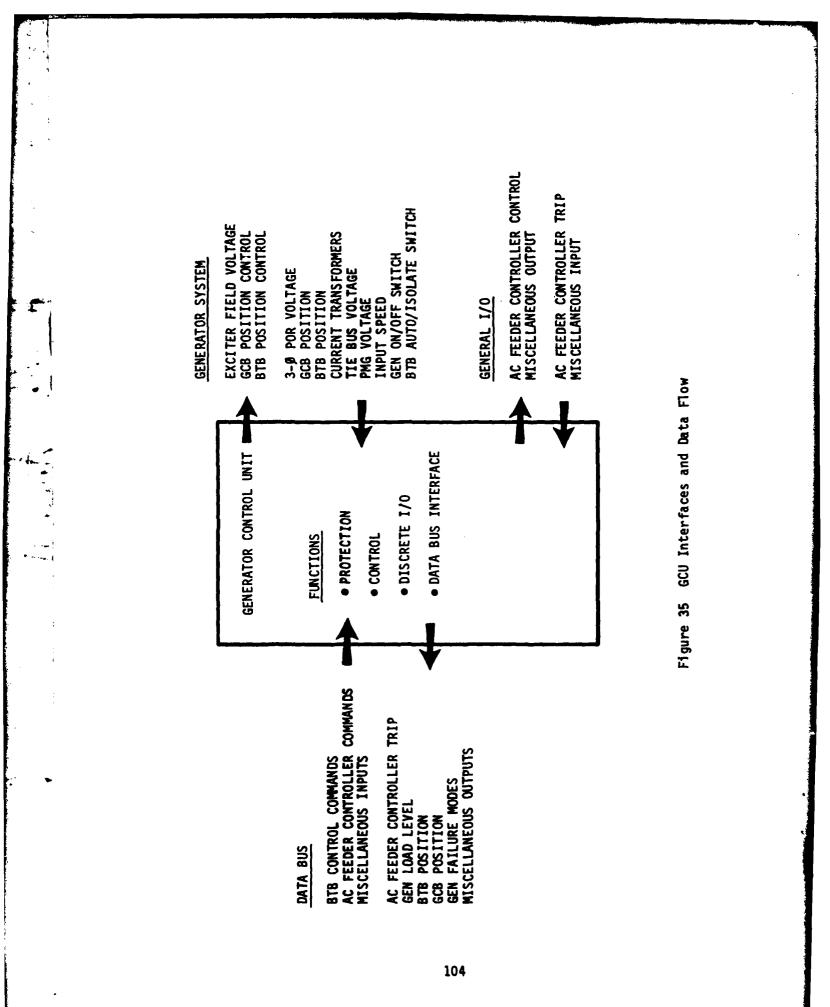

| 35 | GCU Interfaces and Data Flow              | 104 |

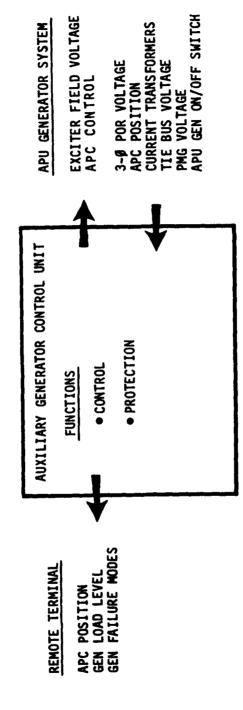

| 36 | AGCU Interfaces and Data Flow             | 105 |

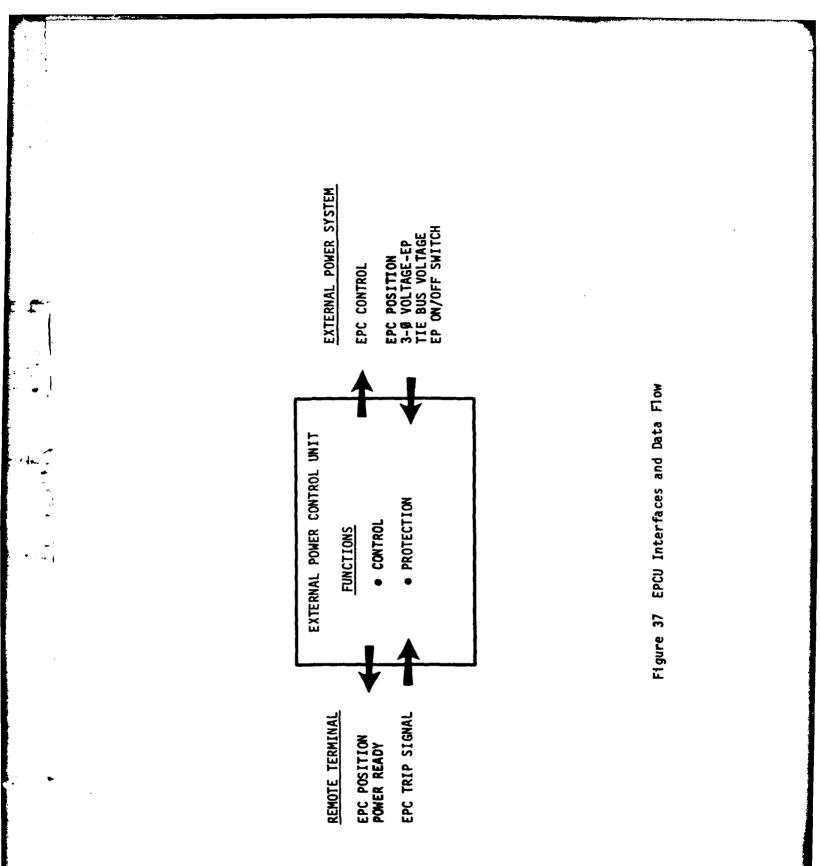

| 37 | EPCU Interfaces and Data Flow             | 107 |

| 38 | Laboratory Simulator Block Diagram        | 109 |

X

LIST OF TABLES

| TABLE |                                           | PAGE |

|-------|-------------------------------------------|------|

| 1     | ELECTRICAL LOAD ANALYSIS SUMMARY          | 7    |

| 2     | SOLID STATE POWER CONTROLLER DISTRIBUTION | 10   |

| 3     | BASELINE AVIONICS DATA BUS LOADING        | 25   |

| 4     | ELECTRICAL SYSTEM EQUIPMENT LIST          | 45   |

| 5     | SYSTEM STARTUP/RESTART                    | 56   |

| 6     | BUS MESSACE MODE CODES                    | 63   |

| 7     | CATEGORIES OF COMPOOL BLOCKS              | 74   |

x1

#### SUMMARY

This interim technical report presents the results of the preliminary design of an advanced aircraft electrical system (AAES). The AAES is designed to meet the requirements for a 1990 time frame two-engine tactical aircraft with multimission capability. The system performs the following major functions on the aircraft:

o Provide electrical power to meet all mission requirements.

o Distribute electrical power to the loads.

Provide electrical system protection.

o Control the distribution of electrical power and provide load management.

Electrical power generation consists of those functions necessary to assure that proper quality power is provided for distribution. Distribution of electrical power relates to the electrical bus structure, AC and DC, along with reliability and redundancy considerations to ensure that the generated electrical power is optimally delivered to the loads. Electrical system protection involves the automatic detection and isolation of system faults such as short circuits and generator failures. Finally, control of power distribution encompasses the on/off control of individual loads, load shedding and load sequencing.

The key characteristics of the AAES are:

- Integrated avionics and power data bus configuration consisting of Digital Avionics Information System (DAIS) standard elements (MIL-STD-1750 processor, MIL-STD-1553B data bus, controls and displays, and remote terminals (RT)).

- Intelligent Electrical Load Management Centers (ELMC) capable of controlling power to loads.

x11

- o Built-in-test (BIT) capability to isolate faults to the module level. BIT includes both circuit and data monitoring checks.

- o Solid State Power Controllers (SSPC) to replace circuit breakers and power control switches. SSPCs are turned on/off via computer control.

- Generator control, protection and status monitoring by a Generator Control

Unit (GCU) compatible with DAIS hardware and software.

- Multimission data information system through programmable system processors, ELMCs and standard DAIS elements.

- o Automatic load management for increased aircraft survivability and probability of mission completion.

#### SECTION I

#### INTRODUCTION

#### 1. Background

The Air Force Wright Aeronautical Laboratories (AFWAL) Aero Propulsion Laboratory has been sponsoring research and development programs directed toward applying advanced solid state power switching and computer control technology to aircraft electrical power systems. Development of components and subsystems utilizing solid state power switching and microprocessor based computer technology has progressed rapidly. Multiplexing techniques have been developed for transmission and processing of electrical system control data. This data usually consists of a large number of discrete (on/off) signals and information for solving control logic equations. Multiplex hardware and software designs have been optimized for electrical system control applications such as the B-1 E-Mux system. This, however, results in high initial development, integration and logistics costs. On large aircraft the amount of signal processing and data transfer may justify the use of a separate and optimized multiplex system for electrical system control; however, in the case of smaller aircraft this may not be the most cost effective solution.

For small aircraft, where the electrical system signal processing and data transfer may not be as large as for the B-1, it may be possible to integrate electrical system control with the avionics system in a single data bus system as developed in the DAIS program. Previous studies, such as AFAPL-TR-73-41, (Reference 1), examined this concept and concluded that integration was possible. Integration of the electrical power control was also examined in the DAIS program but was not implemented. Areas of concern with such integration are that the electrical power redundancy required for mission essential functions may not be adequate for flight critical functions. Another area of concern is that if the electrical power system is controlled by the multiplex system and in turn the multiplex system requires electrical power to operate, procedures must be devised to power-up the system. The

third area of concern is that growth of the data bus traffic may reach the roint where system complexity would negate the technical and cost advantages of an integrated system.

In order to permit evaluation of aircraft electrical power system design, laboratory simulators need to be designed and built. An A-7 electrical system simulator (Reference 2) was built by the Aero Propulsion Laboratory for demonstrating functional operation of the solid state distribution concept and to show that electromagnetic interference (EMI) presented no problem. This simulator was therefore built such that it would have the same ground planes and shielding that exists on the A-7 aircraft. This type of simulator has several disadvantages such as, difficulty in maintenance due to tight hardware locations and difficulty in making changes to the wiring harness, plus poor utilization of laboratory floor space.

Modular concepts of building a laboratory simulator (Reference 3) provide the advantages of lower cost, easy modification and more universal application, even though they do not allow for adequate EMI evaluation. To date no simulator has been developed to evaluate integrated power and avionics data bus control concepts.

#### 2. Program Objectives

The overall objective of this contract is to develop an aircraft electrical power distribution and control system that is integrated to the fullest practical extent with an aircraft digital avionics information management system (DAIS). Specifically this program has two distinct objectives. They are, first to define the requirements and conduct the design of a computer controlled, solid state electrical power distribution and control system for a small two engine aircraft, and second to develop the design of a laboratory simulator for evaluation of the aircraft electrical system.

#### 3. Approach

To achieve the objectives of this program, a two phase study with three tasks in Phase I and two tasks in Phase II has been undertaken. The tasks for each Phase are as follows:

- Phase I Analysis and Preliminary Design

- Task 1 Requirements Analysis

- Task 2 Conceptual Design

- Task 3 Preliminary Design

- Phase II Detailed Design

- Task 1 System Hardware and Software Design

- Task 2 Support Hardware and Software Design

The program flow chart for Phase I is shown in Figure 1. During this phase, in Task 1, the requirements are defined for the electrical power system and the integrated power system control for a small two engine tactical aircraft which will be capable of performing various missions (fighter, attack, reconnaissance, trainer, electronic warfare, fighter bomber). In addition, a data base of information regarding subsystems and component hardware and software of an Advanced Electrical Power Systems (AEPS) simulator is accumulated. The requirements definition and data base is developed with the primary objective of achieving the most cost effective designs for both the aircraft electrical system and electrical system laboratory simulator. To keep the system cost at a minimum, the program is tailored so the requirements meet as closely as possible the existing electrical and DAIS system requirements and applicable hardware and software available at the AFWAL Aero Propulsion and Avionics Laboratories. Also, during Task 1 an evaluation of the Aero Propulsion and Avionics Laboratories and equipment is made. This evaluation helps to arrive at a cost effective design of the laboratory simulator through utilization of existing hardware.

In Task 2 each of 3 data bus architectures (single integrated bus, hierarchical integrated bus, separate dedicated/non-integrated bus) are configured with options ranging from all computational capability residing in the digital processor (mission computer) to most of the processing relegated to remote terminals. Based on these options, AEPS conceptual designs are prepared. A tabulation of all the relevant parameters including processor/bus loading, reliability, memory, and cost is made. The baseline for the architectural studies is the separate dedicated/non-integrated data bus. Both the hierarchical integrated bus and the single integrated bus are evaluated

3

ſ

· · · · · · · · ·

--' --!

Figure 1 Phase I Program Flow Chart

against this baseline. Based on the architectural trade studies, one of the three control architectures is recommended for preliminary design.

In Task 3 a preliminary design of the electrical system with the selected architectures is conducted. System block diagrams, functional flow diagrams, data flow diagrams and key event/timing diagrams are prepared for the electrical system. Draft specifications for the hardware and software for the various components of the system are also prepared. A preliminary hazard analysis of the system is conducted and a detailed development plan for Phase II is prepared.

A report, AFWAL-TR-81-2058 (Reference 4), covering the results of Phase I, Tasks 1 and 2, has been published. This Interim Technical Report summarizes Tasks 1 and 2 and covers the results of Task 3.

## SECTION II REQUIREMENTS ANALYSIS AND CONCEPTUAL DESIGN

#### 1. Requirements Analysis

Design options were developed for an electrical power system for a small tactical two engine aircraft with advanced avionics and fly-by-wire (FBW) flight controls. The following assumptions were made to arrive at the electrical system requirements:

- o 2 Engine Driven Generators

- o 1 Flight Operable Auxiliary Generator

- o Mission Completion With 1 Main Generator

- o Safe Return With Auxiliary Generator

- o Triple Redundant Fly-By-Wire Flight Control System

- o FBW Electronics will be Powered by DC Power

- o Solid State Distribution

A primary generator is driven by each engine. The auxiliary generator is driven by a flight operable auxiliary power unit.

The electrical power system requirements include provisions to interface with the following subsystems:

Automatic Flight ControlHydraulic PowerAuxiliary PowerInstrumentsCommunicationsLanding GearCrew EscapeLife SupportEnginesLightningEnvironmental ControlNavigationFlight ControlsStores ManagementFuelFuel

The degree to which each subsystem is interfaced varies. For some subsystems

such as automatic flight controls, the interface will be only to provide power and caution and warning indication. For other subsystems such as environmental control, allocations were made for more extensive interfacing, such as on/off control of equipment and sensor data communication.

a. Load Analysis

Several aircraft with different missions were surveyed with the intent of determining the effect of the mission on the generation capacity (Reference 4). The survey showed that the fighter, electronic warfare, and fighter bomber missions required the most electrical power. The power requirements were also dependent on the number of crew members.

The trend for new aircraft is toward more electrical power generation capacity. This is the result of increased sophistication in avionics, weapons, and flight control systems. Aircraft dedicated to electronic warfare missions require greater amounts of power. Next to the electronic warfare mission, the fighter and fighter bomber aircraft have the highest power requirements.

A load analysis for a two engine tactical aircraft was developed. The analysis is based on the air-to-surface fighter which Boeing is studying. The load analysis encompasses the fighter and fighter-bomber missions and also has some ECM capability. A load profile developed from the analysis is shown in Figure 2. The load analysis is summarized in Table 1.

#### TABLE 1. ELECTRICAL LOAD ANALYSIS SUMMARY

|                     | MAXIMUM CONNECTED<br>LOAD | SUSTAINED PEAK EMERGENCY<br>LOAD |

|---------------------|---------------------------|----------------------------------|

| TOTAL AC POWER      | 58477 VA                  | 12577 VA                         |

| TOTAL DC POWER      | 7805 WATTS                | 2630 WATTS                       |

| TRU LOSSES          | 1377 WATTS                | 465 WATTS                        |

| TOTAL TRU INPUT POW | ER 9182 WATTS             | 3095 WATTS                       |

| TOTAL AC AND DC POW | ER 67659 VA               | 15672 VA                         |

#### b. Generation System

Using the load analysis and the mission effects analysis as a base, the generation and distribution system was sized. The generation system complement is shown below.

2-60 KVA 115/200 VAC Generators 1-20 KVA 115/200 VAC Auxiliary Generator 3-100 Amp 28 VDC Transformer Rectifier Units

Two 60 KVA main generators allow mission completion with one generator out. Three 100 amp transformer-rectifier units (TRU) provide the system's DC power. The TRUs are sized to provide power for all connected loads. Two TRUs will provide enough DC power for mission completion.

The circuit breaker counts of three aircraft were examined. The Reference 5 study estimated about 400 solid state power controllers (SSPCs) would be required for a single aircraft. Based on the above, the number of SSPCs selected for the aircraft under study was 500. A distribution of the 500 SSPCs was also developed (Table 2). Loads requiring SSPCs larger than 7.5A AC or 20A DC will be controlled by discretely packaged SSPCs or electromechanical power controllers (EMPCs) located outside the ELMCs.

#### TABLE 2 SOLID STATE POWER CONTROLLER DISTRIBUTION

115 VAC

| SIZE                                        |        | PERCENT TOTAL               |

|---------------------------------------------|--------|-----------------------------|

| 2A<br>3A<br>5A<br>7.5A                      |        | 31.5<br>8.5<br>7<br>3       |

|                                             | 28 VDC |                             |

| <u>SIZE</u>                                 |        | PERCENT TOTAL               |

| 2A<br>3A<br>5A<br>7.5A<br>10A<br>15A<br>20A |        | 37<br>6.5<br>2<br>1.5<br>.5 |

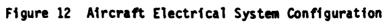

c. Distribution System

The distribution system consists of distributed load centers called ELMCs. Previous studies (References 5 and 6) have shown that this distributed concept lowers vulnerability to combat damage and in some cases lowers total system weight when compared to a single centralized distribution center. Individual loads are connected to the ELMCs rather than to the main electrical power buses as in conventional electrical systems. Power to the loads is controlled by SSPCs housed in the ELMC.

For a single engine fighter, (Reference 5) five ELMCs were recommended. The two engine tactical aircraft of this study is in the same size category. Five ELMCs provide coverage for the entire aircraft. These ELMCs would be located in the left and right forward avionics bay, left and right wing area and in the cockpit area.

The primary functions of the ELMC are to house the SSPCs and interface the SSPCs to the data bus. To maximize the utility of each box on the data bus, the ELMC will include additional functions such as those incorporated in RTs. This will minimize the number of boxes on the data bus. The additional

capabilities which will be included in the ELMCs are analog-to-digital (A/D) conversion and discrete input/output (I/O).

The ELMCs handle 15% of the system's discrete I/O data transfer. RTs handle 80% of the discrete I/O data transfer and the remaining 5% is allocated to the GCUs. Preliminary design of an RT indicates a capacity of approximately 250 inputs and 118 outputs can be packaged in a 4 MCU (1/2 ATR) size box. Based on such a design, three RTs are required to handle the I/O requirements of the system.

d. Flight Critical Power

Methods of providing power to flight critical equipment were investigated. In particular, ways of providing power to a triple redundant fly-by-wire flight control system were addressed. Two types of power are available, AC and DC. Both were evaluated for the application.

As a design philosophy, each channel of the flight control system must have its own independent power source. These sources may be cross tied for additional redundancy. For a triple redundant flight control system, three independent power sources are thus required. With DC, this provision is easily met by using three TRUS. With AC, the main generators provide two sources. A third source can be an inverter powered from a DC bus. A drawback to using AC power is the lack of a simple method for providing uninterruptible power to the flight critical equipment. With DC power, this is accomplished by diode paralleling the sources.

DC power is recommended for the flight critical systems. Two concepts were examined for providing power to flight critical equipment. In the selected concept (Figure 3), a flight critical bus is provided in the ELMC. Each bus is powered by its own TRU. Backup power is provided by a battery which is paralleled with the TRU. Any number of flight critical equipments can be connected to the bus; however, where redundancy is required, such as a triple redundant flight control system, only one channel of equipment is connected to each bus. Having a flight critical bus in the ELMC provides more versatility and reduces the number of load feeders. The vulnerability of the load due to the single feeder is minimized by short feeder lengths resulting from having 5 ELMCs distributed throughout the aircraft.

Figure 3 Flight Critical Bus in the ELMC

#### e. Power Bus Configuration

Two electrical power bus configurations were developed. Both configurations have provisions to support fly-by-wire flight control systems. The selected configuration is shown in Figure 4. Only three of the five ELMCs are shown.

Bus ties are incorporated in this configuration. In the AC system, the bus ties eliminate the need for separate power feeders for the auxiliary generator. The auxiliary generator supplies power to the ELMCs through the main generator buses. The DC bus ties allows the TRUs to be paralleled and to share power feeders. A disadvantage of this configuration is the additional protection required for the bus ties. Another disadvantage is the dependency of the auxiliary generator on the main generator buses for distributing power. For example, a fault on one of the two main generator buses prevents the use of the auxiliary generator if the unfaulted channel's generator is operating. This happens because the auxiliary and main generator cannot be paralleled. The simplicity of this configuration, however, translates to less wiring and, thus, less weight.

#### f. System Control and Protection

The system control and protection provides for automatic operation and coordinated fault isolation. Control and protection is sectionalized into the following areas: generator, distribution, and loads. The objectives of control and protection is to:

- o Reduce crew work load

- o Increase flexibility

- o Increase survivability

- o Increase probability of mission success

The reduced crew work load is achieved by automation. The use of digital processors and data bus communication lines link the various subsystems and allow coordination of most of the components of the electrical system with other aircraft subsystems.

Flexibility is achieved by programmable digital processors which control the system and the individual SSPCs. The capability to reconfigure the system greatly enhances system flexibility.

Increased survivability and probability of mission success are achieved by coordination of all electrical functions and a comprehensive load management program. Automatic switching provides for fast fault isolation, bus switching, and load shedding. Load management diverts power to flight and mission essential loads in the event of a dccrease in available power.

Generator control and protection functions have become fairly standardized, with only the threshold levels varying from program to program. The control and protection functions for the generator are shown below. The same functions will be applied to the APU generator.

#### Generator Protection

- o over/under frequency

- o over/under voltage

o open phase

- o input underspeed

- o differential protection o failed rotating rectifier

o overload

#### Generator Control

- o voltage regulation

- o frequency regulation

- o generator contactor

For advanced aircraft which depend on electrical power for mission completion and flight control, protection and control of the primary generating system is critical. To provide maximum fault isolation and to provide the necessary response time for the control of an aircraft generator, the control and protection of the generator is accomplished by the GCU and is not delegated to the system processors. The control and sensor lines to the generator are hardwired. The GCU is connected to the data bus. However, the generator control and protection functions operate independently of data bus service functions. This isolates the generator from data bus failures. The data bus

is used to carry data such as overload instructions, maintenance information, and fault indications, between the CCU and the system processors. Having the GCU hardwired to the generator also facilitates system startup from a "dead" airplane. In addition, loads necessary during startup are controlled by SSPCs which are in the closed state when no control signal is present.

The distribution system includes the main buses, external power receptacles and distribution feeders. The function of the distribution protection system is mainly to provide fault isolation. The protection and control functions associated with the distribution system are shown below.

#### Protection

o fault protection and isolationo abnormal external power protection

#### Control

o bus tie breaker control

o external power breaker control

o power distribution to ELMCs

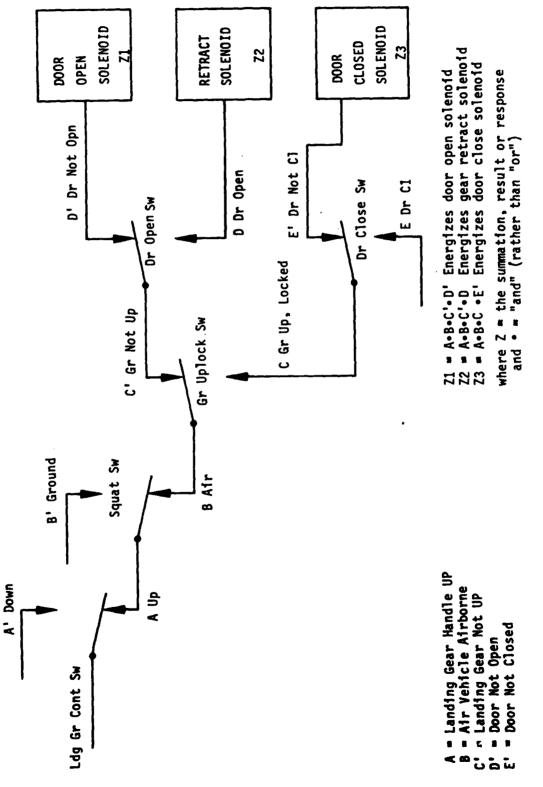

The versatility and survivability of the aircraft is enhanced with the multiplexed data bus control of the loads. All loads are under system control and status of the loads is constantly monitored. Load control is accomplished by the solution of Boolean control equations. There is one equation for each load. The equation takes the form shown below.

$$C = \overline{L} P (R + Q)$$

C = SSPC On/Off Control Signal

- L = Trip latch

- P = Priority Signal

- R = Request for Power (Solution of a Boolean Equation)

- Q = Test Request (Such as Ground Test)

The variable R is the output of a system equation consisting of inputs from the system's RTs and ELMCs. The priority signal, P, is used to implement load management. Sixteen load management levels are available. Each level represents a different set of priority signals for the SSPCs. At each level, each SSPC will have an assigned priority, P. A P set to "O" inhibits or commands the SSPC to turn off. A "1" allows the SSPC to turn on. The relationship of the P variable and the load management levels can be visualized as a 16 x 500 matrix (500 SSPCs in the system) of "1s" and "Os". Depending on the load management level implemented, a preselected combination of 500 "1s" and "Os" are substituted for the variable P in the SSPC control equations. The load management matrix is shown in Figure 5. Various system parameters are used to logically select one of the sixteen load management levels. The level can also be selected manually. Figure 6 shows parameters which are used in determining the load management level.

#### g. Applicability of J73/I (JOVIAL)

The evaluation of the applicability of JOVIAL higher order language to electrical systems was investigated. A literature search aimed at a comparison of the the efficiency of assembly and higher order languages was conducted. The actual coding of two typical power control routines in both JOVIAL and assembly language was done for comparison. The analyses were performed using J73/I; however, J73/I has since been superceded by J73. The changes made in the language have been in the area of syntax and data type conversion. Also, a few new functions have been added. The differences between J73/I and J73 are minor and do not affect the results of the analyses. Based on the results of the literature search and coding evaluation, it was concluded that J73 should be used as the programming language.

#### h. Controls and Displays

An analysis was done to establish the requirements for the controls and displays of the electrical system. The aim of the design is to minimize the controls, and only display that information which is essential for the pilot to maintain aircraft safety and to assure mission success.

£

· ·=- 1

CURRENT STATE OF THE SYSTEM ELMC BUS CONNECTION 1 Figure 6 Load Management Level Selection LOAD MANAGEMENT EQUATIONS GENERATOR CONDITION LOAD MANAGEMENT LEVEL GENERATOR CONFIGURATION MISSION AND FLIGHT PHASE 19

S. S. C. S.

وسترك والهوا

.....

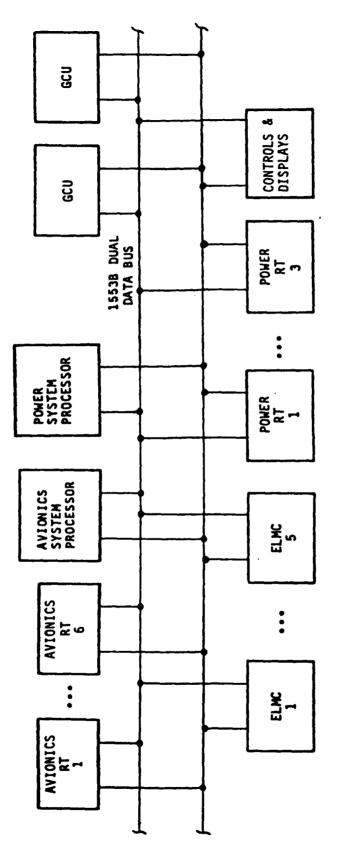

In keeping with this objective, no panel indicators are to be provided for individual SSPC status or trip indication and individual SSPC reset control. Indication of a failed or tripped SSPC appears on the appropriate subsystem warning panel or equipment warning panel. A control panel is required for the DAIS processors. It provides power to the appropriate processor during startup and restart control for any architecture.

A CRT display dedicated to the electrical system is not feasible in a two engine tactical aircraft; however, it is feasible to display electrical system data on the avionics display units. This integrated CRT display concept is possible with the integrated data bus architecture and the hierarchical data bus architecture. An example of this integrated controls/displays concept, which uses existing DAIS hardware, is shown in Figure 7. Only key system failures which affect the mission success will be displayed on the CRT.

#### 2. Control System Requirements

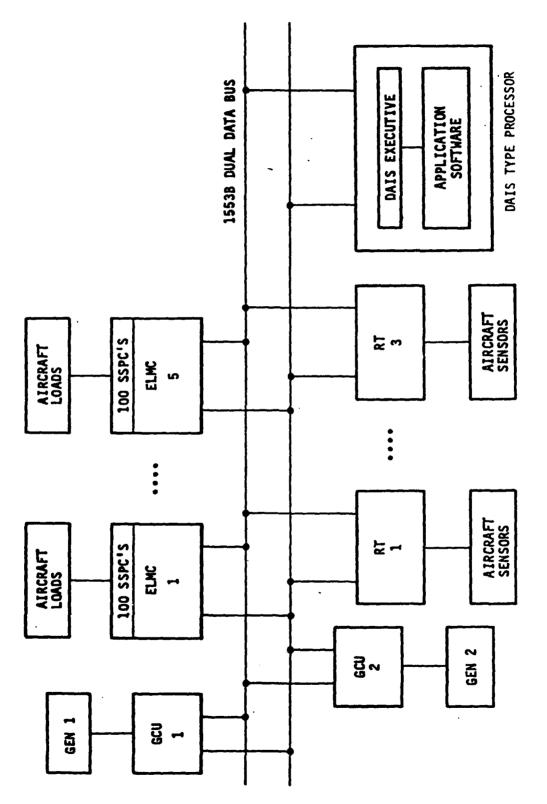

Processing, bus loading, and response time requirements are defined in this section. Following are the major assumptions for defining the requirements for the integrated power system control:

a) Maximum use of Digital Avionics Information System (DAIS) concepts (Reference 7)

- MIL-STD-1553B multiplexed data bus

- RTs per specification SA 321301

- DAIS executive with synchronous bus protocol

- Use of Jovial higher order language for power system application software

- b) Separate AN/AYK-15A processor for power system control.

- c) Hardware connected to the 1553B bus.

- 5 ELMCs with 100 SSPCs each

- 3 Power system RTs

- 2 GCUs

Figure 7 DAIS Integrated Controls/Displays

a. Processing Requirements

Processing requirements for the power system were based on the B-1 EMUX specification (Reference 8). Using the number of SSPCs as a complexity measure, the number and type of equations necessary for the power system in a tactical fighter was determined by scaling the equation count for the B-1 aircraft by the ratio of the SSPC\requirement for the fighter to that required in the case of the B-1 EMUX.

The processing requirements can be separated into three categories of equations as described below.

Category I: These are power request equations and are of the form Z=R where R may take one of the following forms:

- Form 1 One variable of the Form A or A, or the value "logic 1"

- Form 2 Five variables arranged in any valid Boolean expression with each variable used once only

- Form 3 Twenty variables arranged in any valid Boolean expression with each variable used once only

- Form 4 Two hundred variables arranged as the sum of products with each product term composed of no more than six variables with no variable repeated in the Boolean expression

There will be 208 form 1, 236 form 2, 45 form 3, and 8 form 4 equations for this aircraft.

Category II: There are 500 SSPC power control equations of the form:

$C = \overline{L}P (R + Q)$

Where R is a Boolean expression of Form 1, 2, 3, or 4 listed above; P is a single variable; L is the solution to the latch equation and Q is test request.

Category III: There are 500 power system status equations of the form:

I = (L + PX)

Where L is as defined in Category II above; P and X are single variables available to the system designer for definition.

b. Input/Output Requirements

In the power system, the input/output consists of the data and traffic transmitted between the power system processor and its ELMCs and RTs in order to accomplish the power system management and control functions. The I/O requirements were determined by scaling the B-1 EMUX requirements by the ratio of the SSPC count. The discretes transmitted on the bus consist of sensor, SSPC status, system control and status, RT sync, and mode control information.

The requirements for this study were 2096 discrete inputs and 1041 discrete outputs. It was assumed that the GCU interface with the power system processor would require approximately 50 discretes for either input or output. All remaining discretes were uniformly distributed among the ELMCs and RTs. That is, each device connected to the data bus with the exception of the GCUs, contributes equally to the total discrete input and output requirements.

c. Response Time

In order to compute the processor loading and data bus loading, the response time of the system must be known. Response time refers to the maximum time required to detect a change in an event, process the information and then send a response on the data bus. A bimodal response time was used in this study. For the power system, approximately 95% of the discrete data must be received by the power system processor (PSP), processed, and the results must be transmitted within 300 ms. The remaining 5% of the equations and discrete

data must be processed for a 50 ms response time. The 50 ms response time pertains to events which require power bus switching for power distribution reconfiguration.

d. Avionics Bus Loading

The avionics bus loading is necessary so the bus loading capacity for an integrated power and avionics data bus architecture could be sized. In order to determine realistic bus loading for the avionics system, the following aircraft missions were studied: fighter, attack, reconnaissance, trainer, electronic warfare, and fighter bomber.

In order to establish a representative avionics baseline bus loading model subsystems with average complexity were selected. Data for the weapons delivery function (fire control computer, stores management, fire control radar, and laser set), inertial navigation system, and air data computer were all taken from published data for the F-16. F-16 Control and Display data was used since no fighter-bomber control and display data was available. The baseline control and display subsystem therefore consists of a fire control and navigation panel, head-up-display (HUD), and radar display. Electronic counter measures (ECM), imaging, and communications data bus loading was based on data developed at Boeing for a multi-role bomber. The ECM subsystem function is assumed to consist of flare and chaff dispersal. The imaging subsystem baseline consists of a forward looking radar.

Perturbations from the baseline in the form of incrased complexity for the control and display, inertial navigation system, ECM, and imaging subsystems for the reconnaissance, trainer, and electronic warfare missions were examined. Significant complexity increases in the inertial navigation system and the imaging subsystem exist for the reconnaissance mission. Reconnaissance missions are assumed to require a very accurate inertial navigation system and the imaging subsystem would contain side looking radar, infra-red mapping equipment, high resolution cameras, and TV cameras as well as forward looking radar. The increases in data bus loading incurred by these more complicated subsystems is expected to be neutralized by the absence of a weapons delivery capability.

24

In the case of the trainer a more complicated control and display subsystem is anticipated because of the requirement for dual controls and displays, and an additional monitor function for one of the pilots. The expected increase in bus traffic is estimated to be less than 20% for this subsystem.

The electronics warfare mission represents perhaps the greatest potential for increased data bus traffic from the baseline due to the large amount of data needed to identify threats and jamming as appropriate. Data from the multi-role bomber study indicates that ECM can add 8000 words/sec to bus traffic. Again this is offset by a lack of weapon delivery capability for this mission. Using the F-16 data the weapons delivery capability would add 8975 words/sec to the data bus, more than offsetting the ECM traffic.

Based on the above analysis, the number of words/sec shown in Table 3 was selected as the baseline avionics data bus loading model. The percent bus loading, based on approximately 40,000 data words/sec maximum bus loading for the MIL-STD-1553B data bus, was 36%.

TABLE 3 BASELINE AVIONICS DATA BUS LOADING

| SUBSYSTEM                                                  | WORDS/SEC   |  |

|------------------------------------------------------------|-------------|--|

| Control and Display<br>Weapons Delivery                    | 661<br>8975 |  |

| Inertial Navigation<br>Air Data Computer<br>Communications | 3350<br>775 |  |

| ECM                                                        | 128<br>205  |  |

| Imaging Radar                                              | 128         |  |

#### 3. Technicial Analysis

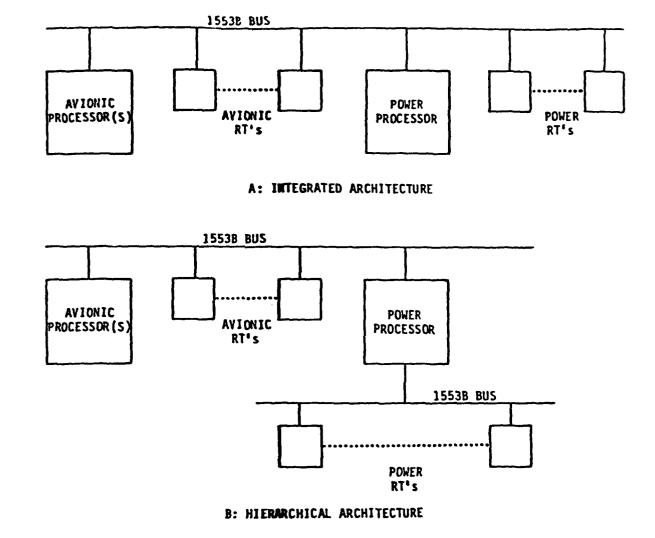

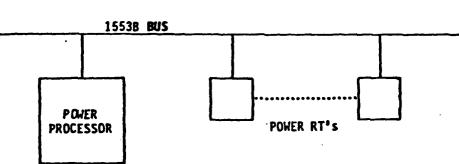

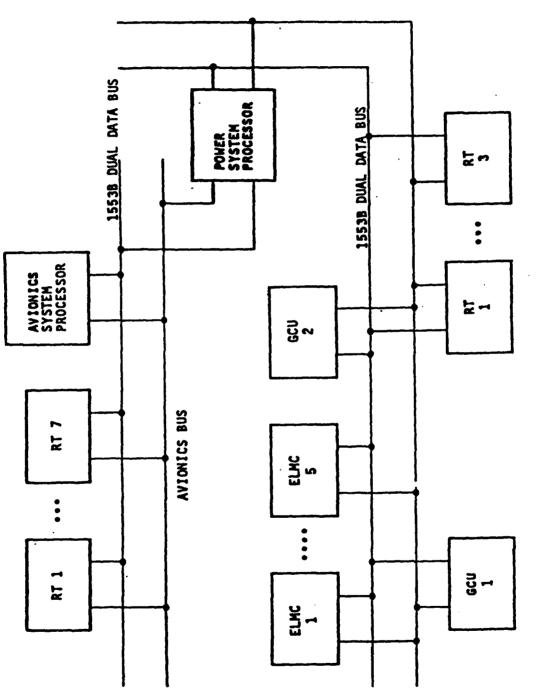

A technical analysis was performed on the three separate architectures considered for electrical control. These three architectures are shown in Figure 8 and are described below:

a) Integrated: The electrical control system is on the same bus as the avionics.

14,222

C: NON-INTEGRATED POWER BUS

Figure 8 Data Bus Architecture Configuration

- b) Hierarchical: The electrical control system is on a separate bus but is connected to the avionic bus through an interbus processor.

- c) Non-Integrated: The electrical control system is not connected to the avionic system by any multiplex data bus.

For each of these architectures the following analyses were performed:

- a) Processor loading: This is calculated as the total time required to calculate the necessary set of logic equations in a minor cycle divided by the time in a minor cycle. The accepted limit for processor loading is 50%.

- b) Bus Loading: This is calculated as the time required to transmit the necessary set of data, including overhead, in a minor cycle divided by the time in a minor cycle. The accepted limit for bus loading is 50%.

- c) Memory Requirements: The total memory requirements for the logic equations and the executive is calculated.

- d) Reliability: An architectural reliability for comparison of the integrated and hierarchical concepts is calculated.

- e) Number of Processors Required: An estimate of the total number of processors is given for each architecture.

- f) Smart RTs: The effect on processor loading and bus loading is analyzed using distributed processing with smart RTs.

- a. General Assumptions

The analysis of the three data bus architectures was made based on the assumptions listed below. The assumptions (a) through (j) apply to all of the three architectures studied, whereas (k) through (n) apply only to the integrated data bus architecture.