CARMEGIE-MELLON UNIV PITTSBURGH PA DEPT OF COMPUTER --ETC F/8 9/2 ON A MIGHT-PERFORMANCE VLSI SOLUTION TO DATABASE PROBLEMS.(U) AUG 81 S W SONG COLUM-CS-03-1492 NL AD-A112 542 UNCLASSIFIED

2549

On a High-Performance

VLSI Solution to Database Problems

Siang Wun Song

August 1981

DEPARTMENT of COMPUTER SCIENCE

Carnegie-Mellon University

# On a High-Performance VLSI Solution to Database Problems

Siang Wun Song

August 1981

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science at Carnegie-Mellon University

This research was supported in part by the Office of Naval Research under Contracts N00014-76-C-0370, NR 044-422, and N00014-80-C-0236, NR 048-659, in part by the National Science Foundation under Grant MCS 78-236-76, and in part by the Defense Advanced Research Projects Agency under Contract F33615-78-C-1551 (monitored by the Air Force Office of Scientific Research). The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the United States Government. The author was supported in part by FAPESP (1976-1980), Fundação de Amparo à Pesquisa do Estado de São Paulo, Brazil, under Contract No. 76-517, in part by CNPq (1980-1981), Conselho Nacional de Desenvolvimento Científico e Tecnológico, Brazil, under Contract 200.402-79-CC, in part by the Institute of Mathematics and Statistics of the University of São Paulo, Brazil, and in part by the Department of Computer Science, Carnegie-Mellon University.

# **Table of Contents**

| 1. Introduction                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>1.1 Goal and Motivation</li><li>1.2 Methodology and Evant</li><li>1.3 Organization of the T</li></ul>                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2. A Taxonomy and Appra                                                                                                                                                                                                                                                         | nisal of Database Machine Designs 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.1 Problem Characteriza 2.2 Dimensions of the Sp 2.3 Logic-enhanced Sec 2.3.1 Uni-Search-Pr 2.3.2 Multi-Search-F 2.3.3 Multi-Search-F 2.3.3.1 Comple 2.3.3.2 Partition 2.3.4 Appraisal 2.4 Logic-enhanced Prim 2.4.1 The Post-Proc 2.4.2 The Hierarchic 2.4.3 Systolic Priorit | ation  acc of Database Machine Designs  ondary Storage Designs  ocessor Scheme  Processor Scheme - Static Allocation  Processor Scheme - Dynamic Allocation  te-Bipartite-Graph Connection  ned-Storage-Units Connection  arry Storage Designs  essors of The DBC Design  cal Associative Architecture  ty Queues  rrays for Relational Operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.4.6 Appraisal                                                                                                                                                                                                                                                                 | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                 | of the Tree Machine Allocation Scheme  n 31  er Version Ints on the Algorithms Ints on the Restrictions Ints on the Restr |

| 3.3.2 Select                                                     | 39       |

|------------------------------------------------------------------|----------|

| 3.3.3 Sort                                                       | . 40     |

| 3.3.3.1 Handling Long Key Fields by Lexicographic Sort           | 42       |

| 3.3.4 Project                                                    | 43       |

| 3.3.4.1 Solution 1                                               | 43       |

| 3.3.4.2 Solution 2                                               | 43       |

| 3.3.4.3 Solution 3                                               | 45       |

| 3.3.5 Join                                                       | 46       |

| 3.3.6 Union and Intersection                                     | 46       |

| 3.4 Partitioning Strategies                                      | 47       |

| 3.4.1 Partitioning by Hashing                                    | . 49     |

| 3.4.2 Partitioning by Using the Distribution Function            | 49       |

| 3.4.3 Discussion of the Hardware Requirements                    | 51       |

| 3.5 Concluding Remarks                                           | 51       |

| 4. Implementation Considerations                                 | 53       |

| 4.1 Packaging Large Tree Structures                              | 53       |

| 4.1.1 The Linearized Tree                                        | 54       |

| 4.1.1.1 Threaded Tree Layout                                     | 55       |

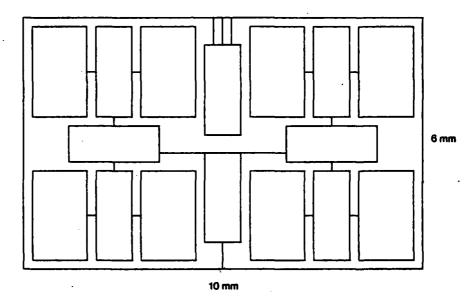

| 4.1.1.2 Packaging a Large Binary Tree                            | 57       |

| 4.1.1.3 Discussion                                               | 59       |

| 4.1.1.4 Packaging a Large Threaded Tree                          | 60       |

| 4.2 Design Considerations                                        | 60       |

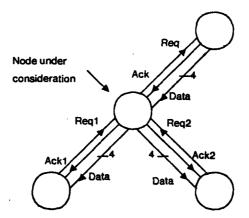

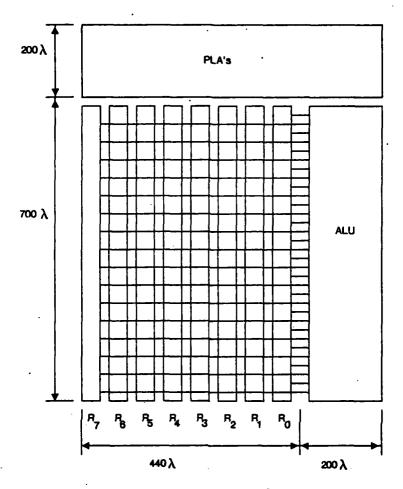

| 4.2.1 Circle Nodes                                               | 62       |

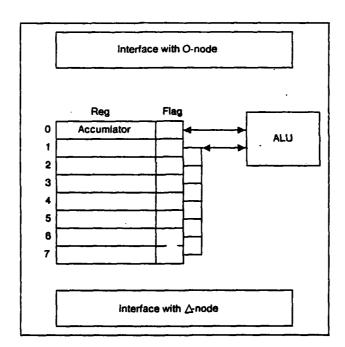

| 4.2.2 Square Nodes                                               | 64       |

| 4.2.3 Triangle Nodes                                             | 66       |

| 4.2.4 Pin Requirements                                           | 67       |

| 4.2.5 Timing and Area Estimates                                  | 67       |

| 4.2.6 Some Examples                                              | 69       |

| 4.2.6.1 Insertion                                                | 69       |

| 4.2.6.2 Deletion                                                 | 70       |

| 4.2.6.3 Selection                                                | 70       |

| 4.2.6.4 Join                                                     | 71       |

| 4.3 Concluding Remarks                                           | 71       |

| 5. Special-Purpose Hardware for Sorting                          | 73       |

| 5.1 I/O Complexity for Sorting                                   | 75       |

| 5.1.1 Model Definition and Notation                              | 75       |

| 5.1.2 A Lower Bound Result                                       | 76       |

| 5.2 Upper Bound Results                                          | 76<br>78 |

| 5.2.1 Straight Multiway Merge Sort                               | 78       |

| 5.2.2 The Linear Array Algorithm                                 | 80       |

| 5.2.3 The Cinedi Array Algorithm  5.2.3 The Systolic Tree Device | 82       |

| 5.2.4 The Systolic Tree Device 5.2.4 The Tree Algorithm          | 83       |

| 5.2.5 A More General Interpretation of the Parameter t           | 85       |

| 5.3 Considerations in the Design of the Interface Controller     | 86       |

| 5.3.1 Difficulty of Obtaining a Harmonious Flow                  |          |

| · · · · · · · · · · · · · · · · · · ·                            | 89<br>90 |

| 5.3.2 A Simple Solution                                          | 90<br>92 |

| 5.4 Numerical Speed-Up Values                                    | 92<br>93 |

| 5.4.1 Quicksort                                                  | 93       |

# PAGE III

| 5.4.2 Binsort                                                       | 95    |

|---------------------------------------------------------------------|-------|

| 5.5 Concluding Remarks                                              | 96    |

| 6. Applications                                                     | 99    |

| 6.1 Detection of Three-Dimensional Patterns of Points               | 100   |

| 6.1.1 Statement of the Problem                                      | 100   |

| 6.1.2 Description of a Previous Work                                | 101   |

| 6.1.3 Summary of New Complexity Results and Assumptions             | 101   |

| 6.1.4 A Worst-Case O(n <sup>2</sup> log m) Algorithm                | 103   |

| 6.1.4.1 The Matching Process                                        | 105   |

| 6.1.5 A Worst-Case min{O(n²), O(n m³)} Algorithm with Preprocessing | 107   |

| 6.1.5.1 Structure Preprocessing                                     | 107   |

| 6.1.5.2 Pattern Preprocessing                                       | 108   |

| 6.1.5.3 The Matching Process                                        | 109   |

| 6.1.5.4 Practical Considerations                                    | 116   |

| 6.2 Three-Dimensional Shape Matching                                | 117   |

| 6.2.1 Relation to the Previous Problem and New Assumptions          | 118   |

| 6.2.2 The Modified Algorithm                                        | 119   |

| 6.3 Reporting Pairwise Intersections of n Rectangles                | 122   |

| 6.3.1 Main Ideas                                                    | 123   |

| 6.3.2 A Partitioning Scheme                                         | 124   |

| 6.4 A Multidimensional Search Problem                               | 127   |

| 6.4.1 Related Work                                                  | 127   |

| 6.4.2 A Hardware-assisted Solution                                  | 128   |

| 6.5 The Containment Problem                                         | 129   |

| 6.6 Performance Estimates                                           | 131   |

| 6.7 Concluding Remarks                                              | 134   |

| 7. Conclusion                                                       | 135   |

| 7.1 Main Contributions and Results                                  | 136   |

| 7.2 Further Work                                                    | 138   |

| Appendix A. The Relational Data Model                               | 141   |

| A.1 Relations                                                       | 141   |

| A.2 Keys                                                            | 142   |

| A.3 Basic Relational Operations                                     | 142   |

| A.4 Implementation of Relational Database Systems                   | 144   |

| References                                                          | 147   |

| Index ·                                                             | . 157 |

# **List of Figures**

| Figure 2-1: Two kinds of bottlenecks.                                             | 11 |

|-----------------------------------------------------------------------------------|----|

| Figure 2-2: An overall framework.                                                 | 13 |

| Figure 2-3: Uni-search-processor model.                                           | 14 |

| Figure 2-4: Multi-search-processor (static allocation).                           | 15 |

| Figure 2-5: Complete-bipartite-graph connection.                                  | 18 |

| Figure 2-6: Partitioned-storage-units connection.                                 | 19 |

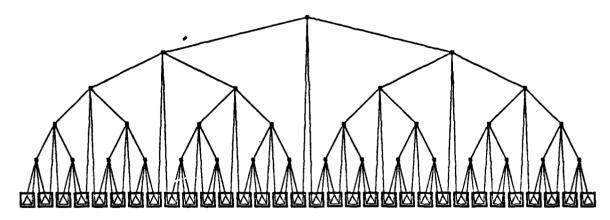

| Figure 3-1: System configuration.                                                 | 28 |

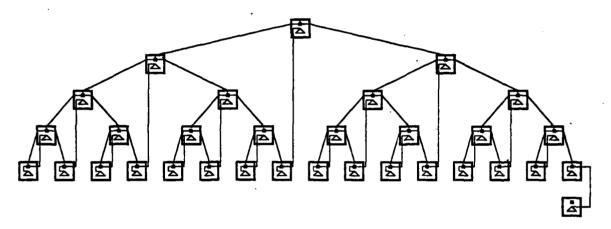

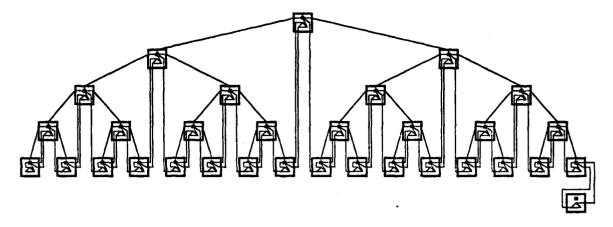

| Figure 3-2: The tree machine.                                                     | 29 |

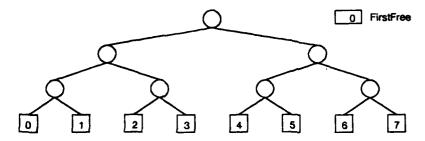

| Figure 3-3: An empty tree.                                                        | 31 |

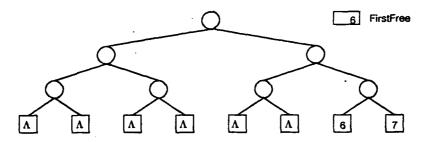

| Figure 3-4: After six insertions (Λ denotes an occupied node).                    | 32 |

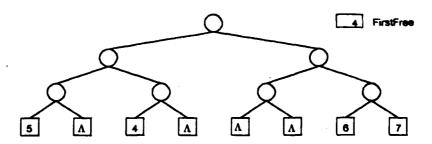

| Figure 3-5: After two deletions (Λ denotes an occupied node).                     | 33 |

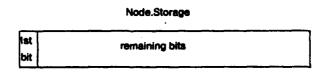

| Figure 3-6: A node storage.                                                       | 33 |

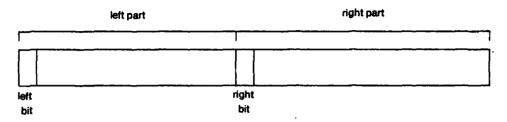

| Figure 3-7: Insert and delete instruction formats.                                | 34 |

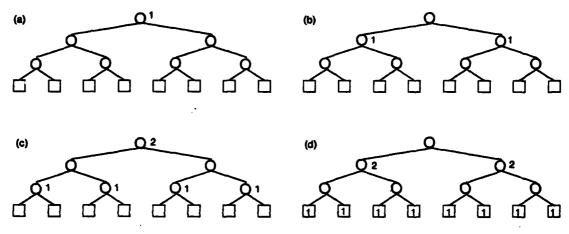

| Figure 3-8: Alternate empty layers of O-nodes.                                    | 37 |

| Figure 3-9: Blocking of flow.                                                     | 38 |

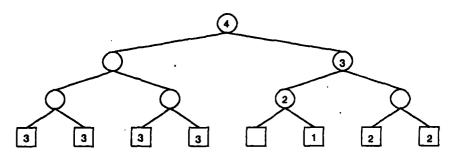

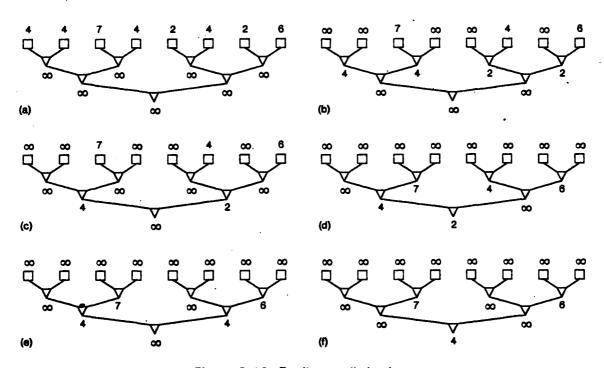

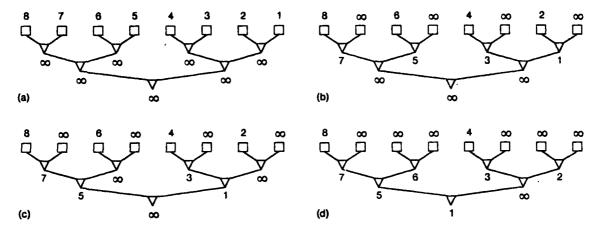

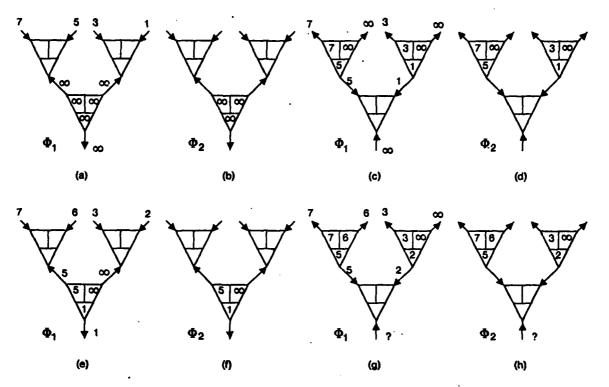

| Figure 3-10: A sorting example.                                                   | 41 |

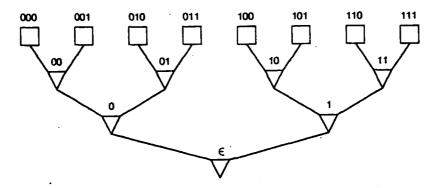

| Figure 3-11: Labeling the nodes of a binary tree.                                 | 42 |

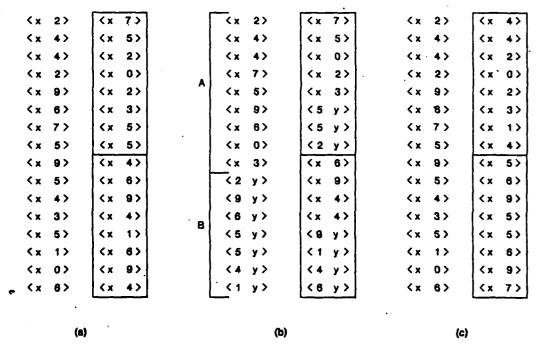

| Figure 3-12: Duplicates elimination.                                              | 44 |

| Figure 3-13: Examples of key-disjoint partitions                                  | 47 |

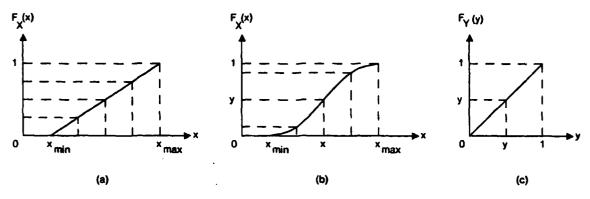

| Figure 3-14: Examples of distribution functions.                                  | 50 |

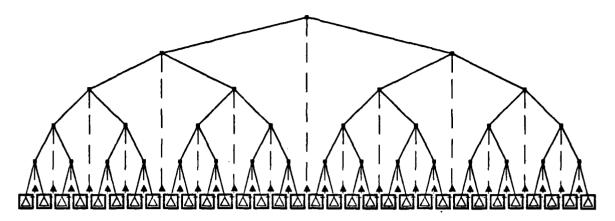

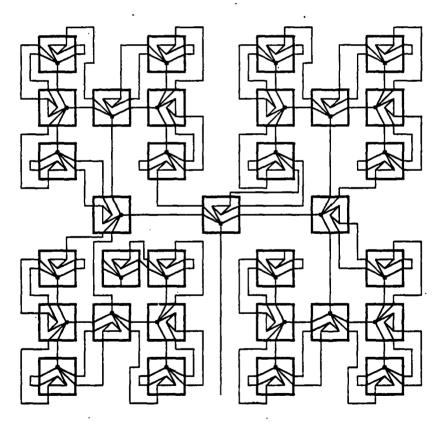

| Figure 4-1: The linearized tree and a special case.                               | 54 |

| Figure 4-2: The resulting structures after collapsing vertically connected nodes. | 55 |

| Figure 4-3: Laying out a threaded tree by a recursive procedure.                  | 56 |

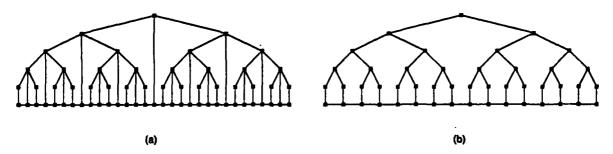

| Figure 4-4: Two packaging schemes.                                                | 57 |

| Figure 4-5: A new solution.                                                       | 58 |

| Figure 4-6: Chip layout after accommodating internal nodes.                       | 58 |

| Figure 4-7: Final binary tree chip layout.                                        | 59 |

| Figure 4-8: A large threaded tree.                                                | 60 |

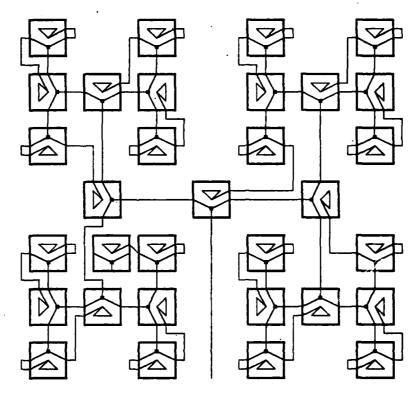

| Figure 4-9: Chip layout after accommodating internal nodes.                       | 61 |

| Figure 4-10: Final threaded tree chip layout.                                     | 61 |

| Figure 4-11: Data and signaling wires.                                            | 62 |

| Figure 4-12: Components of a Q-node.                                              | 64 |

| Figure 4-13: The unmirroring process and one component chip.                      | 67 |

| Figure 4-14: Layout of one 🗆-node.                                                | 68 |

| Figure 4-15: Layout of one component chip.                                        | 69 |

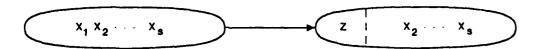

| Figure 5-1: A 1-move replacing x <sub>1</sub> by z.                               | 75 |

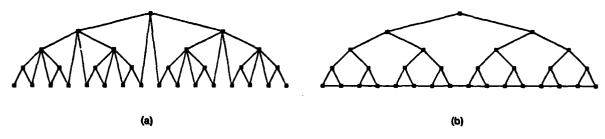

| Figure 5-2: An s <sup>t</sup> -ary t-move tree.                                   | 76 |

| Figure 5-3: Interpretation of the model.                                          | 77 |

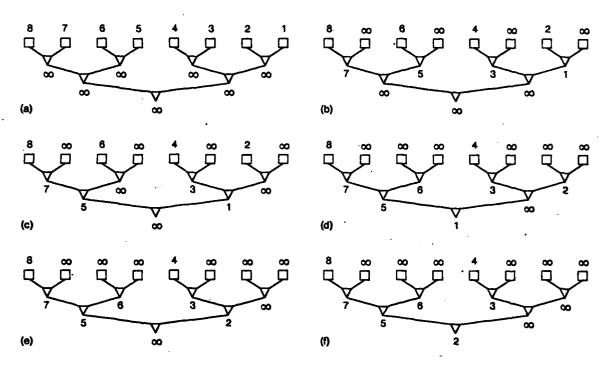

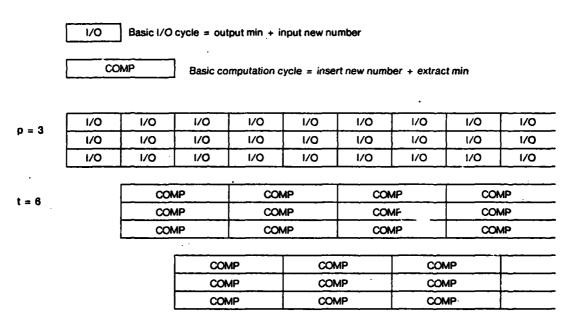

| Figure 5-4: An example of t = 6.                                                  | 88 |

| Figure 5-5: | Synchronization overheads and an ideal situation.                               | 87  |

|-------------|---------------------------------------------------------------------------------|-----|

| •           | Groups of three nodes are compared against each other.                          | 88  |

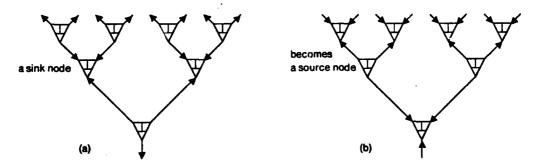

| Figure 5-7: | A sink node becomes a source node in the next time unit.                        | 88  |

| Figure 5-8: | The difficulty of obtaining a harmonious flow.                                  | 90  |

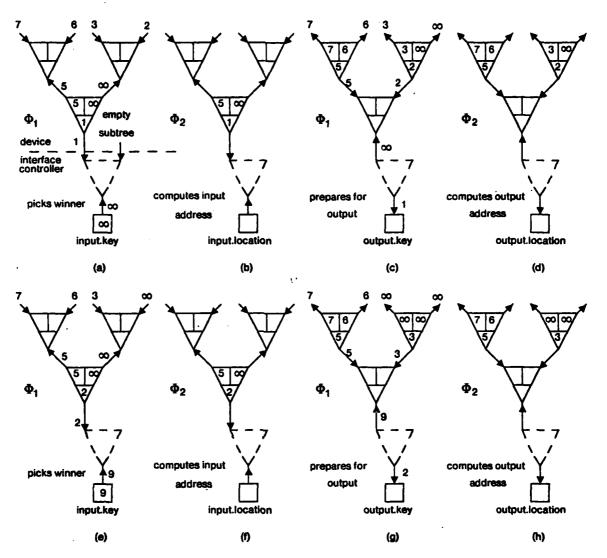

| Figure 5-9: | The interface controller acting as a new root node.                             | 91  |

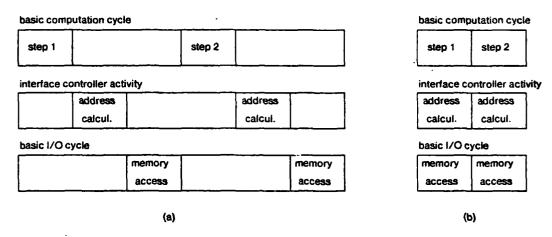

| Figure 5-10 | : Timing diagrams showing overlapping of three activities.                      | 92  |

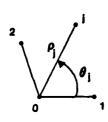

| Figure 6-1: | Polar coordinates in the new reference system.                                  | 104 |

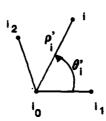

| Figure 6-2: | Polar coordinates in the 3-dimensional case.                                    | 106 |

| Figure 6-3: | An example showing the matching process.                                        | 111 |

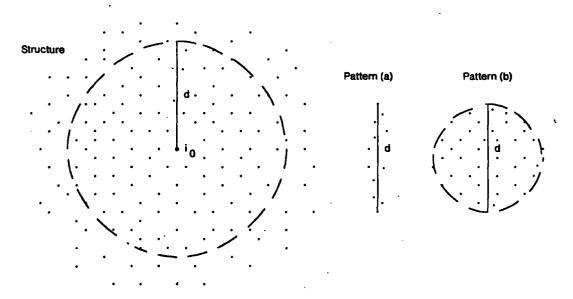

| Figure 6-4: | Two different patterns and a structure with a cloud of points around in         | 114 |

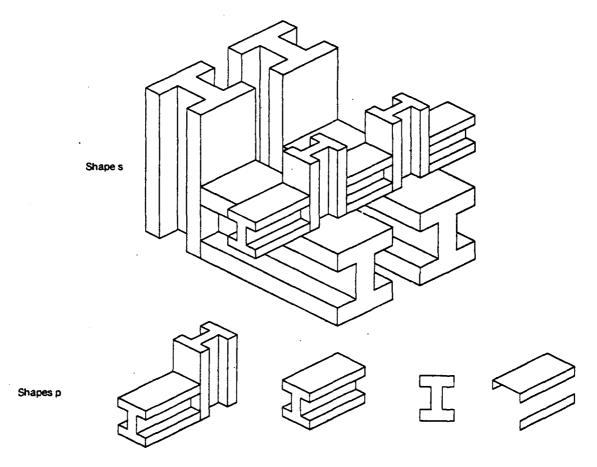

| Figure 6-5: | Shape matching examples in 3-space.                                             | 117 |

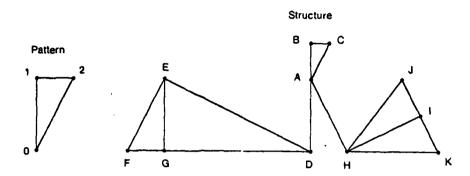

| Figure 6-6: | (0,1,2) matches (A,B,C), (D,E,F), (D,G,E), (E,G,F), (H,I,J), (H,I,K)            | 119 |

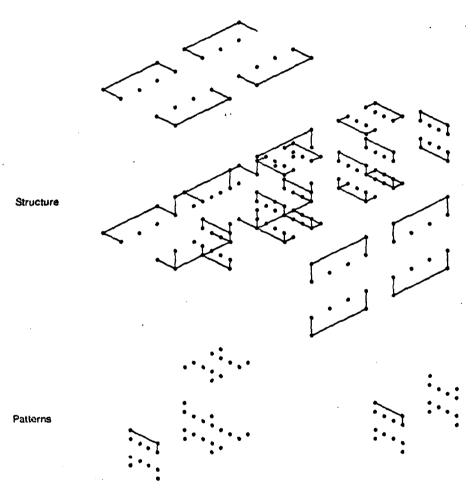

| Figure 6-7: | Patterns consisting mostly of points.                                           | 121 |

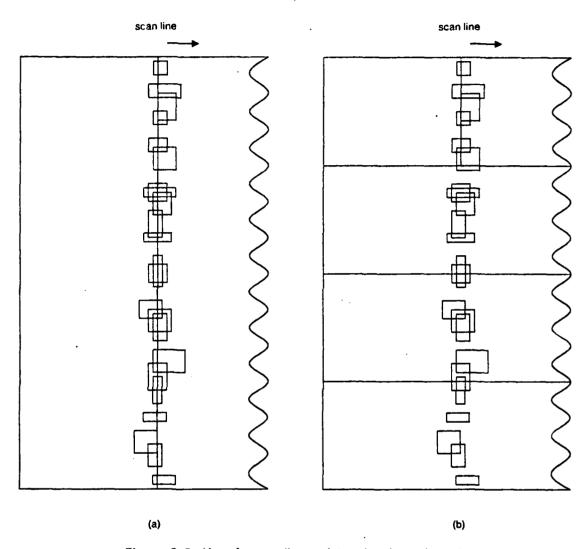

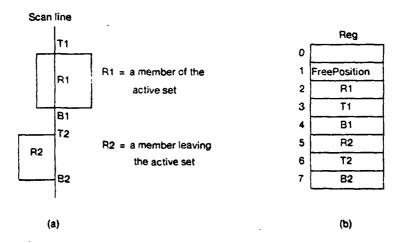

| Figure 6-8: | Use of a scan line to determine the active set.                                 | 123 |

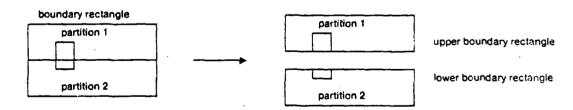

| Figure 6-9: | A boundary rectangle.                                                           | 125 |

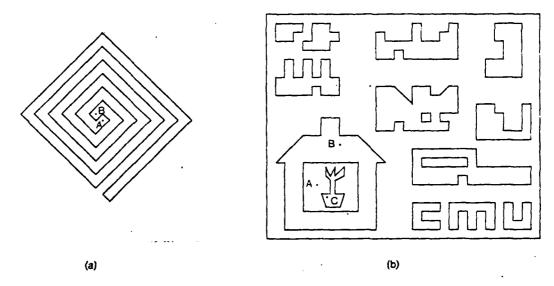

| Figure 6-10 | : The 2-D containment problem and one possible extension.                       | 129 |

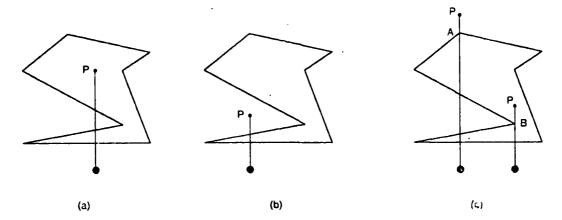

| Figure 6-11 | : Counting the number of edges above the query point; problem with singularity. | 130 |

| Figure 6-12 | : Nomenclature used and their respective assignment to register positions.      | 131 |

| Figure 7-1: | The relations FLIGHT and PILOT.                                                 | 141 |

| Figure 7-2: | A selection example.                                                            | 143 |

| Figure 7-3: | A projection example.                                                           | 144 |

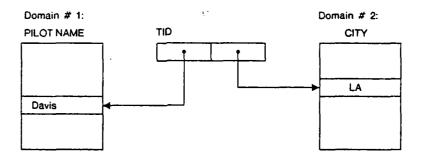

| Figure 7-4: | A join example.                                                                 | 145 |

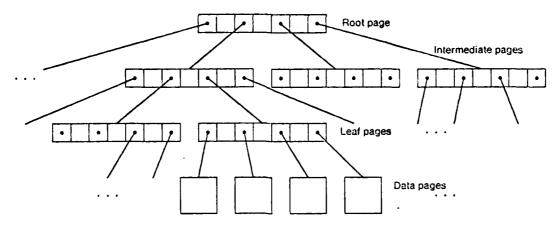

| Figure 7-5: | XRM storage structure.                                                          | 145 |

| Figure 7-6: | A B-tree index.                                                                 | 146 |

|             |                                                                                 |     |

# **List of Tables**

| <b>Table 2-1:</b> | Summary of demonstration results.                                | 21  |

|-------------------|------------------------------------------------------------------|-----|

| <b>Table 4-1:</b> | State transition table.                                          | 63  |

| <b>Table 4-2:</b> | Data movement instructions.                                      | 65  |

| <b>Table 4-3:</b> | Arithmetic and logical instructions.                             | 66  |

| <b>Table 5-1:</b> | Comparing systolic solutions with Quicksort.                     | 94  |

| Table 5-2:        | Comparing systolic solutions with Binsort.                       | 95  |

| Table 6-1:        | Polar coordinates for the m points of the pattern.               | 104 |

| Table 6-2:        | Polar coordinates for the n points of the structure.             | 105 |

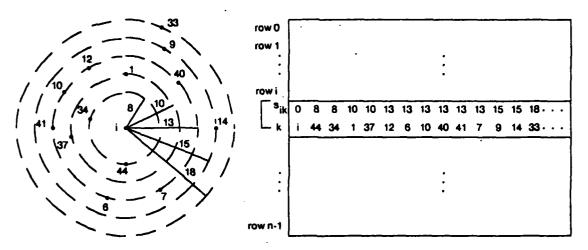

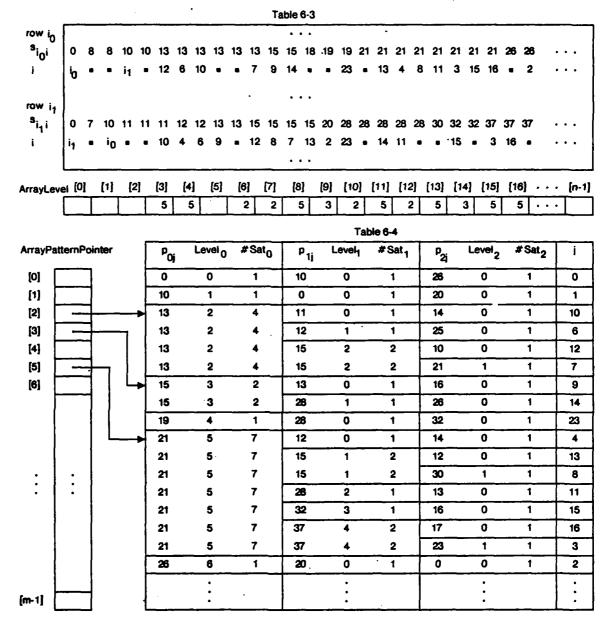

| Table 6-3:        | Each entry of row i contains a sorted distance value sit, and k. | 108 |

|                   | Distances to three selected points sorted lexicographically.     | 109 |

| <b>Table 6-5:</b> | Actions fired by a left edge.                                    | 132 |

| <b>Table 6-6:</b> | Actions fired by a right edge.                                   | 133 |

| Table 6-7:        | Performance estimates for the rectangle intersection problem.    | 134 |

to my wife Ping Ping

# **Acknowledgments**

I wish to thank my adviser H. T. Kung for his constant encouragement and advice throughout my entire study and research work. I would also like to thank Jon Bentley, Chuck Eastman, and Bob Sproull for serving on the thesis committee and for their valuable feedback and dedicated reading of the manuscript.

Special thanks are due to Mike Foster, Phil Lehman, Kemal Oflazer, Bob Whiteside, and Z. M. You for very helpful discussions and suggestions. Also, I thank the entire CSD community for building and maintaining an enjoyable environment for doing research.

l am grateful to the University of São Paulo, FAPESP (Fundação de Amparo à Pesquisa do Estado de São Paulo), and CNPq (Conselho Nacional de Desenvolvimento Científico e Tecnológico) for their financial support.

## **Abstract**

This thesis explores the design and use of custom-made VLSI hardware in the area of database problems. Our effort differs from most previous ones in that we search for structures and algorithms, directly implementable on silicon, for the solution of computationintensive database problems. The types of target database systems include the general database management systems and the design database systems. The thesis deals mainly with database systems of the relational model. One common view concerning specialpurpose hardware usage is that it performs a specific task. The proposed device is not a hardware solution to a specific problem, but provides a number of useful data structures and basic operations. It can be used to improve the performance of any sequential algorithm which makes extensive use of such data structures and basic operations. The design is based on a few basic cells, interconnected together in the form of a complete binary tree. The proposed device can handle all the basic relational operations: select, join, project, union, and intersection. With a special-purpose device of limited size attached to a host, the overall performance may ultimately be dictated by the I/O between the two sites. The ideal specialpurpose device design is one that achieves a balance between computation and I/O. We propose a model to study the I/O complexity for sorting n numbers with any special-purpose hardware device of size s, and show a lower bound result of  $\mathfrak{D}$  (n tog n/log s). We present an optimal design achieving this bound. An important finding is that for practical ranges on the quantity of data to be sorted, systolic sorting devices of small sizes can beat fast sequential sorting algorithms....To evaluate the theme that a data structure supporting a few basic operations can be useful, we examine a number of database problems all of which depend heavily on sort, join, and search operations. One problem is the detection of threedimensional patterns of m points in a large structure of n points, with application in chemical We present a sequential algorithm with worst-case time complexity of min{O(n<sup>2</sup>), O(n m<sup>3</sup>)}. With a uniform distribution of points in the pattern, the time complexity is at most O(m n). For the three-dimensional shape matching problem, where scale is also allowed, we give an O(n2) solution. We also propose a method of packaging certain large tree structures on chips. The packaging method requires only one type of fully utilized chip, which is not pin-bound. The wire lengths connecting component chips are shorter than those using the previously known layouts.

# Chapter 1 Introduction

With recent technological advances in the VLSI circuitry, the chip capacity, or component count on a chip, is increasing at an astonishing rate [66, 74]. Both the opportunities and challenges regarding effective use of VLSI are tremendous. Considerable interest has been aroused in employing special-purpose hardware systems in application areas that demand good response time and throughput. Examples of application areas already being considered include signal and image processing, and graphics. This thesis explores the design and use of custom-made VLSI hardware in the area of database problems. Search for hardwareoriented solutions to database problems, in the context of design and implementation of the so-called database machines, has been around for more than ten years. Our focus here, however, differs from most previous efforts in that we search for structures and algorithms, directly implementable on silicon, for the solution of computation-intensive database problems. The proposed design is based on a few basic cells, interconnected in a simple and regular way. By replicating the basic cells, whose design constitutes the main design effort, a powerful special-purpose device can be obtained. This means that design costs, which typically constitute the dominant cost in special-purpose VLSI hardware systems, can be greatly reduced. The size of the custom-made device can be varied accordingly to match various performance goals. The proposed device can be used in two ways. A device of "large" size (to be made precise later) can handle all basic relational operations with substantial performance improvement over conventional methods. It may constitute a viable solution when chip capacity continues to increase. Another way is to use a device of "small" size as a sorting engine. We shall show that such a device can provide significant speed-ups in relation to fast sequential sorting algorithms. This solution is attractive because it implements an operation used in many database problems, and it can be implemented with

current technology at a low cost. In either case the hardware is tailored to a specific application area and can thus be simpler in design than a general-purpose off-the-shelf computing device. The consequence is that we are likely to obtain a final product which is both compact in silicon area and able to provide good performance. Such a solution can thus be cost effective.

#### 1.1 Goal and Motivation

The goal of the present research work is to investigate the feasibility of employing special-purpose VLSI hardware to solve compute bound database problems. The types of target database systems include the general database management systems, as well as the so-called design database systems. The latter type of database system not only stores a model of some complex reality and provides primitive accesses to it, but also supports its design. Examples of design database systems include those used for architectural and mechanical designs. The thesis deals mainly with database systems of the relational model<sup>1</sup>.

By organizing information in database systems, integration is achieved. An integrated database reduces the redundancy in the stored data. One important advantage is the sharing of data and software for their manipulation and retrieval among different applications and new ones to be developed. Because of these advantages, use of database systems has become widespread. More recent database systems offer such attractive features as automatic verification and maintenance of semantic integrity, usage of views as abstraction and authorization mechanisms, etc. The price for such features is the performance penalty a user must often pay. What is allowed in a practical database system is often limited by performance concerns. Operations such as the relational join and sort are computationally expensive. An example of a costly query is the conjunctive query [16], shown to include a great number of queries actually asked in practice. For example, the language Query-by-Example [96] is based on a core of conjunctive queries. An optimal implementation of conjunctive queries utilizes a great number of expensive relational joins. In design databases

<sup>&</sup>lt;sup>1</sup>Appendix A contains a succinct introduction to the relational data model, as well as a brief discussion of the storage structures used in implementations of relational database systems.

such as those used for architectural and mechanical designs, costly spatial operations are often required. In masonry designs using object grammars [70], for example, the application of each production rule requires the complete solution of a complex three-dimensional shape matching problem. Details of this problem, as well as a number of other examples, will be examined in Chapter 6.

Semantic integrity verification and maintenance in design databases is discussed in [57, 58]. Integrity constraints in design databases may be very complex. Lafue [58] proposes delaying the maintenance of integrity until strictly necessary. As a consequence; violations of integrity are temporarily tolerated as long as they are known. Such measures reflect the performance concerns in design databases. Among the commercial database management systems, some kind of semantic integrity checking and maintenance has been implemented in System R [1, 2] and INGRESS [90]. Though some simple integrity constraints are negligible in cost, the user is warned against enforcing more complex controls unless he is willing to pay a considerable cost. GLIDE [27] is an example of a design database with data and control abstraction features of a high-level programming language. Some degree of semantic integrity verification is supported.

Another costly operation is the materialization of views. A view is a relation derived from existing relations, which may include base relations or derived relations. Nesting of views is therefore possible. Views constitute a powerful abstraction mechanism, as well as an authorization mechanism [29]. The creator of a view has the privileges to access, update (under certain conditions), and destroy it. It is also possible to *grant* some of these privileges to other users, and subsequently *revoke* the same privileges if desired. Views can also be used for another purpose. In order to enforce data independence and avoid redundancy, several kinds of normal forms have been proposed [20, 28]. In such normal forms, relations are broken into smaller parts which are then joined back together by the view mechanism. Materializing views may be costly when complex relational operations are involved [90]. In a recent report where System R is evaluated, Astrahan et al. [2] mention a performance penalty in executing very complex statements involving joins of several relations. They also point out that this performance degradation must be traded off against the advantages of normalization.

PAGE 8 CHAPTER 1 INTRODUCTION

These considerations serve as motivation for the development and usage of specialpurpose hardware to improve performance.

# 1.2 Methodology and Evaluation

A taxonomy and appraisal of database machine designs will be presented in Chapter 2. Such a study is related to the thesis in two ways. The appraisal will enable us to spot the strong and weak points of existing designs. For example, we will see that, with rare exceptions, previous works do not address the important issue of problem decomposition, that is, the partitioning of a large problem to be handled by a smaller piece of special-purpose hardware. The proposed taxonomy will provide us with the nomenclature needed to describe the context under which the proposed design stands. The taxonomy is based on several dimensions. One dimension is whether special-purpose logic is applied to secondary memory or primary memory, giving what we call *logic-enhanced secondary storage* or *primary storage* designs, respectively. Most previous designs belong to the first category, which is especially suitable for I/O-bound tasks. We shall focus mainly on designs that fall into the latter category, aimed at compute-bound tasks.

We shall consider a different view of special-purpose hardware usage. One common view is that a special-purpose device performs a well-defined and specific task such as filtering or two-dimensional convolution. The systolic architecture [56] was proposed as a solution to meet high-performance requirements for a compute-bound computational task that is regular, i. e., where repetitive computations are performed on a large set of data. Such is the case for example with respect to many signal and image processing computations. Nevertheless we would like to exploit usage of some kind of special-purpose hardware to handle computations that lack such regularity. The device we propose is not a hardware solution to a specific problem, but rather provides a number of useful data structures and basic operations. More specifically, it can be viewed as a hardware version of a heap, priority queue, or a data structure for searching in general. A sequential algorithm using complex data structures may spend a great amount of time in maintaining them. Overheads in book-keeping and control may be very expensive. This explains why certain asymptotically fast algorithms are not usable in practice, when the constant hidden in the O-notation makes the algorithm

inappropriate for the actual problem size. The same overheads in the hardware counterpart are usually small. The performance of any sequential algorithm which makes extensive use of such data structures and the supported basic operations will thus improve with the aid of such a device. The price of this flexibility is that the device is not self-contained in that it needs the supervision of some controller which may be part of the interface system or the host.

One focus of paramount importance is the study of decomposition procedures by which a large problem is partitioned into subproblems to be handled by a smaller special-purpose device. As a result, it may be necessary to store and retrieve intermediate results before a computation is complete. The overall performance may ultimately be dictated by the I/O between the device and the host. We emphasize the importance of study of I/O complexity to achieve the optimal design where computation and I/O are balanced.

As a means of evaluation, we will show that such a device is indeed useful in database problems and cost effective. We anticipate here a summary of conclusions. We show that the proposed device can handle all the basic relational operations: select, join, project, union, and intersection. Furthermore, we show that a variety of problems are reducible to this set of basic operations. These include two costly three-dimensional pattern or shape detection problems and some others involving spatial operations. These problems arise in design databases and some special database systems. One result that may be of practical significance is a new method for packaging certain tree structures among chips. With regard to sorting, an important finding is that for practical ranges on the quantity of data to be sorted, systolic sorting devices of small sizes can beat fast sequential sorting algorithms.

# 1.3 Organization of the Thesis

Chapter 2 contains a taxonomy and appraisal of existing database machine designs. Chapter 3 describes a tree-structured device to perform sorting and some basic relational operations as project, join, union, etc. Partitioning mechanisms for handling large problems whose size exceeds that of the primary memory are discussed. Chapter 4 contains some implementation considerations. We present results on the packaging of large tree structures

PAGE 10 CHAPTER 1 INTRODUCTION

among chips, based on a layout result for a new structure called a *linearized tree*. We also discuss the design of the basic cells of the device, and propose a simple instruction set. Chapter 5 focuses on the importance of I/O on the overall system performance where a special-purpose device of limited size is used. Lower bound results on the I/O complexity for sorting are derived and an optimal design achieving this bound is shown. Chapter 6 examines five different problems that arise in special database systems, including detection of patterns of points and lines in three-space. The solutions are found to depend heavily on sort, join and search. Finally, concluding remarks, a summary of main results and contributions, and further works are presented in Chapter 7.

# Chapter 2

# A Taxonomy and Appraisal of Database Machine Designs

The purpose of this chapter is twofold. We survey existing database machine designs to identify their strengths and weaknesses, and propose a taxonomy which will then be used as a context for our research. This chapter is organized as follows. First we characterize the problem by identifying two bottlenecks. Then we describe the several dimensions the taxonomy is based on. At the risk of oversimplification, the proposed taxonomy attempts to group many seemingly different designs into a few categories by concentrating on their similarities. The remainder of the chapter can then be viewed as a detailed presentation of these categories, with a brief survey of previous database machine designs that fall into each category. Part of the appraisal of database machines is based on a paper by Langdon [60].

# 2.1 Problem Characterization

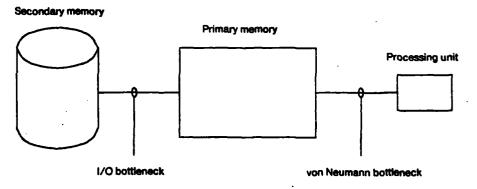

Figure 2-1: Two kinds of bottlenecks.

As shown in Figure 2-1, we can identify two potential bottlenecks, namely the I/O bottleneck and the so-called von Neumann bottleneck. Memory hierarchies exist because of

economic reasons. If primary memory were inexpensive, there would be no need for secondary storage devices. Database files typically reside in the less expensive secondary memory and only needed portions are brought into primary memory for processing. Among the secondary storage devices, the magnetic disks have come into wide use. In moving-head disks, a comb-like assembly contains the read/write heads. All tracks under the read/write heads form a cylinder. To access data in a sector, the assembly first positions the read/write heads over the cylinder containing the desired track and sector. The time to do this is called the seek time. Having located the desired track, there is rotation delay for the needed sector to come under the read/write head. This time is the latency time. Finally there is the transmission time required to read or write a series of sectors. In fixed-head disks, every track has its own read/write head. No mechanical movement of the head assembly is involved and the seek time is essentially zero. Careful design of access paths and maintenance of appropriate indices help in reducing the number of disk accesses. To eliminate the need for access paths and indices, database machines with fast retrieval times have been proposed. Most database machine designs use the logic-per-track approach [84], allocating a read head, some search logic, and write head to each data track of rotating storage devices. Data read by the read head can be compared against some stored constant and modified, and subsequently written back to the track during the same revolution. Such designs have content addressability as their basic characteristic and can provide fast on-the-fly retrieval.

In a compute-bound task a data element participates in many operations. The best place to carry out such a task is inside the primary memory, because of its faster access speed. It was observed in [56] that in a conventional von Neumann machine, each operation typically fetches one or more operands from memory. Hence the amount of I/O (between the memory and the central processing unit) is proportional to the number of operations to be performed rather than the number of inputs required for the computation. The von Neumann bottleneck is in fact an I/O bottleneck in lesser scale. To reduce traffic through this bottleneck, many works have been done in the context of optimal register allocation or usage of cache memory. Studies of such solutions abound in the literature and fall outside the scope of the present work.

# 2.2 Dimensions of the Space of Database Machine Designs

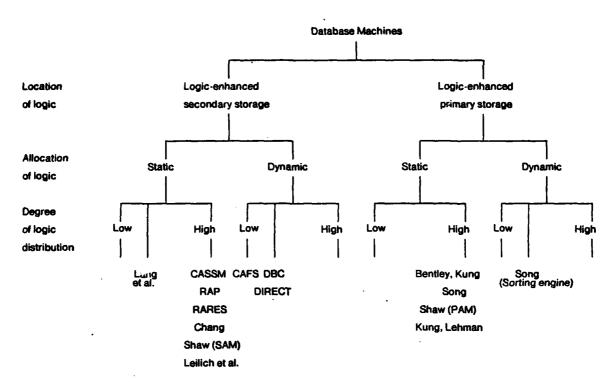

Figure 2-2: An overall framework.

The taxonomy is based on several dimensions. Depending on where special-purpose logic is applied, we have *logic-enhanced secondary* or *primary storage* designs. Most previous designs are variations of the first type. Another dimension along which designs can be classified is the way logic is allocated to storage units, whether *statically* or *dynamically*. A third dimension is the degree of distribution of logic among memory elements, defined in [83] as the number of storage elements associated with each processing unit. Along this dimension, we may have a wide spectrum of designs. High degree of logic distribution signifies faster computation rate, and this should be such that a balance between computation and data access rate is achieved. Classification of designs along this dimension is also important since it is related to the cost of a physical implementation. As an example, we can view a conventional von Neumann machine as a logic-enhanced primary storage device occupying the lowest end of the logic distribution spectrum. The allocation of logic is

dynamic since one processing unit serves the entire memory. Figure 2-2 shows an overall framework, illustrated with a few particular designs. The reader can refer to this figure when reading the rest of this chapter. Its purpose is to illustrate the several categories and not to show the exact positions of the various designs. No attempt should therefore be made to derive quantitative conclusions. Only with a more specific definition of degree of logic distribution and a more detailed analysis of the implementations involved can such positions be made more precise.

# 2.3 Logic-enhanced Secondary Storage Designs

#### 2.3.1 Uni-Search-Processor Scheme

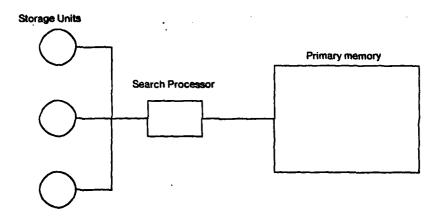

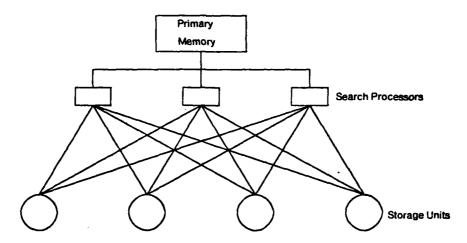

Figure 2-3: Uni-search-processor model.

One search processor is attached between the secondary storage devices and the primary memory (Figure 2-3). Irrelevant data can be filtered out before they reach the primary memory, and thereby reducing I/O traffic. Some early examples of database machines are of this kind. This scheme occupies the low end of the logic distribution spectrum. The allocation of logic is dynamic since one search processor serves the entire secondary memory. An example is the Content Addressed File System, or CAFS [3, 23].

#### 2.3.2 Multi-Search-Processor Scheme - Static Allocation

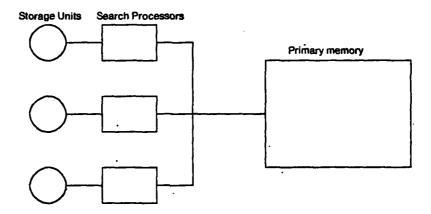

A storage unit considered in the following is usually a disk track, bubble memory, or charge-coupled device. The static allocation scheme pre-allocates one search processor to each storage unit, requiring as many search processors as there are storage units (see Figure 2-4). With such designs, the search time is typically tens of milliseconds. They occupy the high end of the logic distribution spectrum.

Figure 2-4: Multi-search-processor (static allocation).

Among the designs which fall into this category, we cite the following. (Some of these designs, conceived with static allocation in mind, are now shifting to the dynamic allocation scheme, to be discussed shortly afterwards.) CASSM [91], or Content Addressed Segment Sequential Memory, designed and with a prototype built at the University of Florida, is one of the earliest design efforts and thus has exercised considerable influence over other designs. It is designed mainly to support the hierarchical database model. The CASSM system consists of an array of cells each of which contains a processing element and a circular memory element (a disk track). The processing element consists of a read head, comparison and modify logic, and a write head. One difficulty of implementing logic per-track devices is the mechanical tolerance problem [60]. As bit densities achievable on the magnetic media increases, the spacing between the read and write heads becomes tighter by the same amount. CASSM has a read/modify/write capability using two physical disk tracks (A and B) per logical track of storage. Data read from track A passes through the cell and is then written

on track B. Next, data from track B is passed to track A, which permits any bit to be modified yet employs a single head per track. Data sensed by the read head can be compared against a constant value stored in the cell. CASSM has one comparator for data search. Intermediate results are recorded as mark bits which can subsequently be used. A hardware prototype with two cells was originally planned. What actually was built was a single-cell prototype system. A fixed-head floppy disk was used. The system was built using 220 SSI circuits and interfaced to a NOVA 800 computer.

RAP [79], or Relational Associative Processor, was designed and implemented at the University of Toronto. It supports the relational data model. Like CASSM, an RAP cell has a processing element and a rotating memory, which is a CCD track built from Intel's 16 Kbit 2416 components. One problem of using charge-coupled devices is their volatility. Since they are susceptible to power disturbances, appropriate measures (such as stand-by power sources) must be taken. In an RAP cell, three comparators are used. (Recall that a CASSM cell has one.) The comparators are used in two instances. The first instance is the qualification or selection of tuples. Up to three domains may be compared against constant values stored in the cell. Each tuple has also a mark bit field to record temporary results which can subsequently be used. A second instance is to compare single domain values against three comparands. It may thus require less number of revolutions as compared to CASSM. A prototype system, called RAP.2, of two cells was built in 1977. In this prototype system, each record was limited to 255 items whose length could only be 1, 2, or 4 bytes of data. In the planned RAP.3 this length will be arbitrary. In RAP.2 each cell can store data (or part of the data) belonging to a single relation. This means that while a large relation can be allocated to several cells, an entire cell is needed to store a small relation. This restriction will be removed in RAP.3. Regarding the performance of RAP.2, it is reported that gains range from one to three orders of magnitude in query execution speed over conventional systems.

Chang [17] proposes slightly modified major/minor loop bubble chips to accommodate storage and access for relational databases. While the data tracks of the logic-per-track disk files are difficult to synchronize, an important advantage of bubble-like devices is the bit-by-bit synchronization. Bubble technology, however, suffers from a bit rate problem, that is, the data transfer rate may be too slow to be competitive with other rotating storage devices.

RARES [68], also designed to support the relational model, differs from others mainly in that tuples are stored across the tracks of the head-per-track disk storage. A system of up to 14 search processors has been designed and implemented by Leilich et al. [63]. With considerably less logic distribution than the other designs in the static allocation category is the design by Lang et al. [59], in which a processor is associated with each direct access storage device, instead of with each storage track. A very recent effort is the investigation of tools for generating language transducers [32]. The research involves the construction and evaluation of VLSI circuits using language transducers for several problems. One of the problems is the construction of a data filter for logic-per-track database machines.

In the static allocation scheme, each storage unit has its own private search processor and it does not matter in which storage units a file should reside. Therefore storage organization is quite simple. The main problem, of course, is the waste of too much potential resource. The global database may contain information for many different users and applications. In processing one specific query, however, the actual load (i.e., the amount of data needed for the processing) may well constitute a tiny fraction of the whole database. Providing logic to all disk tracks of the entire database is analogous to a memory management system in which enough physical memory is provided to hold all programs ever written by all the users of a given installation.

## 2.3.3 Multi-Search-Processor Scheme - Dynamic Allocation

Still using our analogy with a memory management system, a virtual memory system allocates physical memory dynamically to segments of programs only when their presence in the main store is required for execution. The amount of physical memory can thus be significantly less than the total program space. Similarly, in the dynamic allocation scheme, a number of search processors are allocated dynamically to those storage units containing information to be processed. The amount of search logic is therefore distributed to the entire database and hence will occupy the lesser end of the logic distribution spectrum as compared to those with static allocation. Depending on how search processors are connected to storage units, we have many variations of this scheme. Two of these, which correspond to real database machine designs, will be examined.

## 2.3.3.1 Complete-Bipartite-Graph Connection

Figure 2-5: Complete-bipartite-graph connection.

In this scheme each search processor is connected to every storage unit of the database, as depicted in Figure 2-5. It works in the following manner. Each storage unit keeps broadcasting its contents to all the search processors. An individual search processor can choose to listen to one of the storage units and ignore the others. We have thus a very flexible connection. Any search processor can operate on any storage unit. Furthermore, several search processors can operate independently on the same storage unit, as long as they do not contend (for instance, they should not all try to update at the same time). This connection also allows a multi-user system in which some search processors may be operating to answer one user's queries, while some other search processors are working on another user's queries. Flexibility is of course obtained at the cost of the number of connections and the more complex control mechanism of the search processors. DeWitt [25], at the University of Wisconsin, Madison, proposes a design of a system called DIRECT which uses essentially this connection. In the proposed configuration, it will have eight LSI-11/03 search processors and 32 storage units each composed of a 16K byte CCD memory.

## 2.3.3.2 Partitioned-Storage-Units Connection

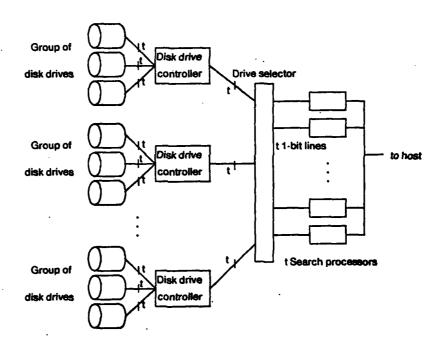

In this connection scheme, if we have t search processors and n storage units (typically, t < n), then all the storage units will be divided into n/t partitions, each with t storage units. The t search processors can be connected to the storage units of one partition, but not to storage units of different partitions. Data residing in one partition can be examined by the search processors in essentially one disk revolution time (assuming a storage unit to be a disk track). Therefore, if related data are clustered into the same partition, they can be searched very quickly. We thus see that this scheme can provide the same performance as the static allocation scheme, given that we have enough search processors (t is sufficiently large) and related data are properly clustered.

Figure 2-6: Partitioned-storage-units connection.

The Data Base Computer [5], or DBC, designed by a group headed by D. Hsiao at Ohio State University, fits into this model. The DBC design uses moving-head disks as storage devices, the only requirement being the parallel read-out capability of the t tracks of one disk cylinder. The set of disk drives is divided into 8 - 16 drives for access and control purposes

(Figure 2-6). Each group is controlled by a disk drive controller. A drive selector determines a particular disk drive controller which, in turn, determines the disk drive whose data are to be transferred. Data read out from one cylinder are then fed into t search processors. The DBC design was conceived with dynamic allocation approach in mind, and has provided extensive literature on such issues as data clustering and security checks [6].

#### 2.3.4 Appraisal

Logic-enhanced secondary storage designs are based on the logic-per-track philosophy. and have one common goal: that of providing efficient on-the-fly search of massive amounts of data in one or a few disk rotations. They constitute promising approaches to the important selection operation. Some other frequently used database operations, however, require not only knowledge of the values of individual data items, but depend on some kind of interaction among data items. The relational join between two relations of size n each, for example, requires O(n2) comparisons in its straightforward implementation. With a secondary associative storage device, it can be implemented as follows. For each tuple of one relation, we extract the specific field over which the join is being performed. Then in one revolution time we compare it with the corresponding field of all the tuples of the second relation. Therefore the join operation can in principle be obtained in approximately O(n) revolutions, where n is the number of tuples of the first relation. While this linear performance result might seem quite acceptable at a first sight, we have to keep in mind that one revolution time is on the order of tens of milliseconds. Therefore this mechanism is acceptable as long as we have a small number of argument tuples. For a concrete example, we cite the design of RAP in which the join is performed in a way very similar to the one described. Table 2-1 reproduces a summary of some results of a live demonstration of the RAP.2 prototype hardware [79]. The execution time for the third query, containing a join operation, is considerably greater than those of the other two.

Some recent designs combine the secondary associative storage devices with a logicenhanced primary memory. In such designs, the secondary associative memory plays an important role in the case when the problem size is too large to be handled entirely in the primary memory. Appropriate partitions can be retrieved by the logic-enhanced secondary

| # rotations  | Time                        | Tuples retrieved                           |

|--------------|-----------------------------|--------------------------------------------|

| 13 rotations | 18/60 s                     | 11 tuples                                  |

| 5 rotations  | 8/60 s                      | 0 tuples                                   |

| 63 rotations | 82/60 s                     | 7 tuples                                   |

|              | 13 rotations<br>5 rotations | 13 rotations 18/60 s<br>5 rotations 8/60 s |

Table 2-1: Summary of demonstration results.

storage devices and delivered to the primary store. For example, Lin [69] discusses the usage of associative secondary storage to aid in external sorting. Sorting is also discussed in the article on RARES [68]. The method is based on the knowledge of a histogram concerning the key values. By using content addressability of the secondary store, the appropriate partition is brought into the main memory which is assumed to be fast enough to produce sorted sequences in a pipelined fashion as a new partition is being retrieved. A more detailed discussion on these ideas is found at the end of Chapter 3.

# 2.4 Logic-enhanced Primary Storage Designs

Depending on the degree of logic distribution, several kinds of logic-enhanced primary storage designs can be considered. At the low end of the spectrum is the attachment of special-purpose hardware of limited size to a conventional passive memory. In such designs, logic is allocated dynamically to the entire memory. At the other end of the spectrum are the designs using the so-called smart memory (which we will refer to as *logic-per-datum* designs), in which there is a commingling of logic and memory elements in a fine grain. Such designs are of very high performance and constitute a departure from the von Neumann architecture. The remainder of this section will survey the various logic-enhanced primary storage designs.

## 2.4.1 The Post-Processors of The DBC Design

In the DBC design mentioned earlier, functions such as sorting of retrieved records, relational join operations on two sets of records retrieved from secondary memory, and the set functions as maxima and average, are all handled by what is known as the postprocessors. Recall that search logic is allocated dynamically to the secondary memory so that a cylinder of data can be content searched in essentially one disk rotation. The retrieved data are fed, in a pipelined fashion, to the post-processors. The post-processing functions are presented in a number of reports describing the sort operation [40] and the join operation [39, 41]. In particular the last report also contains a comparison of the DBC join method with other proposed methods. The post-processing functions are performed by a multiprocessor system consisting of a number of linearly connected processors each with private memory. In an earlier description [39] they share an associative memory for storage and fast retrieval of join attribute values. For each unique join attribute value, the associative memory provides an integer index, which is then used by the processors to obtain a memory location by means of hashing. This first design has the drawback of not being easily hardware-extensible. All processors share the same associative memory which will become a bottleneck when the number of processors increases. A new design described in [41] distributes the associative memory among all the processors, such that each will contain a fraction of the original associative memory. In either design, a very strong assumption is that all the required tuples can fit into the memories of the multiprocessor system. Its practical use may depend on the ease of partitioning large problems.

#### 2.4.2 The Hierarchical Associative Architecture

A hierarchical associative architecture has been proposed by Shaw [83] for the efficient evaluation of relational primitives such as join, project, and select. It consists of a hierarchy of associative storage devices under the control of a general-purpose processor. At the bottom of the hierarchy is a secondary associative memory (SAM), which may be implemented using parallel logic-per-track disks, as in CASSM, RAP or RARES. At the top of the hierarchy is a primary associative memory (PAM), capable of fast content-based searches. Complex relational primitives such as the join operation on two relations are evaluated in the primary

associative memory, with the assistance of the secondary associative memory. Shaw considers the important case of handling large problems whose size exceeds that of the primary associative memory. He distinguishes two kinds of evaluations, namely, internal evaluation where the argument relations can be fit entirely into the primary associative memory, and external evaluation where the relations exceed its capacity. Shaw shows that when argument relations are large, the time required for evaluation of complex primitives with the hierarchical associative architecture represents a substantial improvement over the results attainable using only secondary associative storage devices.

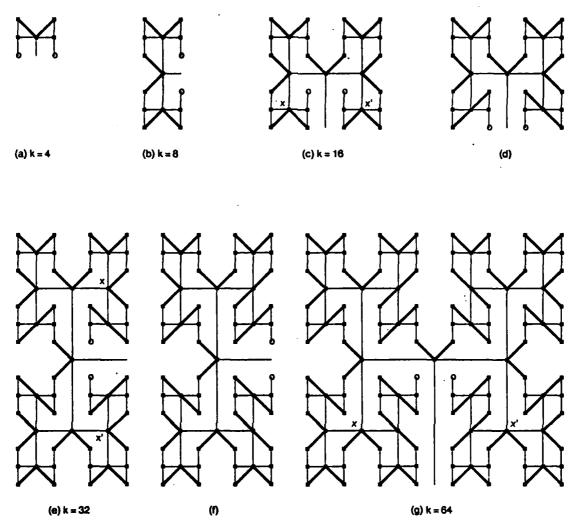

#### 2.4.3 Systolic Priority Queues

The systolic array approach has been proposed as a solution to offload costly computations. Systolic algorithms have been presented for matrix computations [51], signal and image processing [52, 53, 55], pattern matching [31], transitive closure and dynamic programming [49], and many others. (For a more complete list of systolic algorithms, see [54]; for a discussion on the philosophy of the systolic architecture, see [56].) One systolic design especially useful in database applications is the priority queue proposed by Kung and Leiserson [64]. A linear array of cells is used to store a collection of elements with the possible operations of insertion, deletion and minimum extraction. (Fisher [30] presents designs of systolic arrays for computing running order statistics where ranks other than the minimum and input spaces of higher dimensions are considered.) In addition to storage, some comparison logic is provided at each cell. A sequence of the above operations can be executed concurrently in a pipelined fashion, in such a way that the response time is a constant, independent of the length of the array. A priority queue can also be implemented with a hardware heap in a straightforward way as we will show in Section 3.3.3. Notice that a systolic priority queue, whether implemented as a linear array or a heap, is a logic-per-datum device and, as such, occupies the high end of the logic distribution spectrum. However, if such a device of limited size is used to aid in the internal sorting of a much larger collection of numbers, then the degree of logic distribution will be considerably less. Hence, depending on the size of a systolic device and the problem size it is able to handle, its usage may be economically infeasible, or perfectly viable and justifiable. (Internal sorting with the aid of systolic devices will be treated in more detail in Chapter 5.)

# 2.4.4 The Systolic Arrays for Relational Operators

Kung and Lehman [50] consider the use of a large number of simple processors connected in a linear array for the handling of relational operators. They describe, among others, arrays for performing intersection (which can also be used for projection with duplicate removal) and join of two relations. A single database transaction may consist of a number of relational operations. Therefore to process all the operations required in one or more transactions, an integrated system containing several systolic arrays is needed. A crossbar scheme connecting the memories holding required data and the special-purpose systolic arrays is proposed.

In a recent work by Kim, Kuck, and Gajski [43], a bit-serial/tuple-parallel relational query processor is proposed. The scope of the study is limited to designing a query processor that will efficiently process data already loaded into the primary memory. As in the case of the systolic arrays of Kung and Lehman, the proposed query processor is designed with the view toward VLSI implementation.

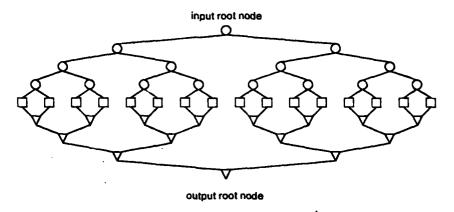

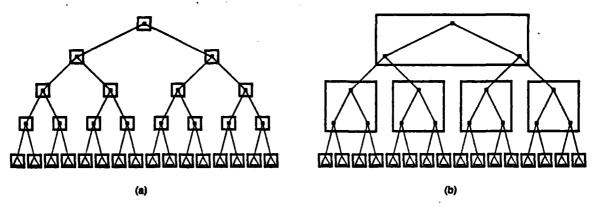

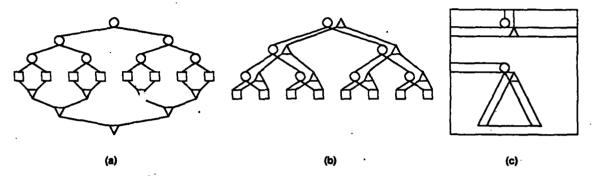

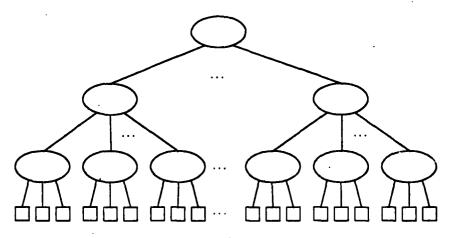

#### 2.4.5 The Tree Machine

A logic-per-datum design consisting of a binary tree of cells has been proposed by Bentley and Kung [9] (and independently by Browning [14, 15]). The internal cells of the binary tree can propagate information to, as well as combine the information of the descendant cells (such as taking the logical and, or select the minimum, etc.). Data elements reside in the leaf cells which are provided with logic to carry out a limited repertoire of instructions. Such a structure is especially suitable for different kinds of searching problems, because of the logarithmic path between the root cell and any leaf cell. It has been extended [85] to handle the sort operation, and relational operations as project, join, union, etc. Details are found in Chapter 3. Such a design is of high performance and occupies the high end of the logic distribution spectrum (see Figure 2-2 under the branch of static allocation). The same device, of a small capacity, can be allocated to serve a much larger memory, thereby occupying the lesser end of the spectrum (Figure 2-2 under the branch of dynamic allocation). Such a device will be discussed in Chapter 5.

### 2.4.6 Appraisal

Logic-enhanced primary memory designs are useful for compute-bound tasks where a same datum participates in many operations. On the other hand, I/O-bound tasks such as selection are better handled by logic-enhanced secondary storage devices, before the data even get to the primary memory. The best architecture is perhaps a hierarchy containing both kinds of devices. Logic-enhanced secondary devices may be used to filter out the irrelevant data, and more complex operations on the selected ones are processed in the logic-enhanced primary memory. Designs where logic is allocated dynamically to the entire memory is usually economical to implement but require careful study of the issue of problem partitioning, that is, how to decompose a large problem such that it can be handled by a special-purpose device of smaller size. The logic-per-datum designs can provide very high performance and constitute a departure from the von Neumann architecture. Their implementation cost may however limit their usage to very specialized applications, where fast response time and throughput are required, e.g. on-line bank-teller systems that support a huge number of simultaneous transactions [62].

# Chapter 3

## The Tree Machine

In this chapter we describe a tree-structured machine for the handling of relational operations, as well as the important sorting operation. A novel space allocation scheme for the tree machine, as well as insertion and deletion procedures, will be described. Many of the sections presented here are contained in [85], which however does not consider problem partitioning.

In database applications, queries typically require the execution of a sequence of database operations before the answer is obtained. One such sequence might be the selection of the required tuples, the joining of the selected tuples of two relations over some attribute, followed by the projection of the result relation to extract the desired columns and the final output of the result with duplicate-removal. It is therefore desirable to have a single special-purpose device which can provide efficient solution to all basic database operations. For this purpose we have chosen the tree machine of Bentley and Kung [9] and attempted to extend it to handle other basic database operations. Tree-structured machines have been proposed as general-purpose computing devices by Berkling [11], Browning [14, 15], Mago [72], Sequin, Despain, and Patterson [80] and Wilner [95]. Hollaar [35] presents a tree-structured design for merging sorted lists.

This chapter is organized as follows. First we characterize the system configuration and present a general description of the tree machine. We shall present a new space allocation scheme and comment on its practical usage. We then consider some basic database operations, including select, sort, project, join, union, and intersection. Finally we discuss decomposition strategies to retrieve to primary memory appropriate partitions of a large argument set stored in secondary memory.

# 3.1 System Configuration

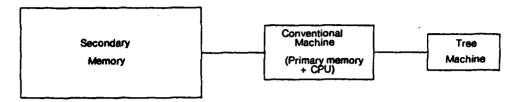

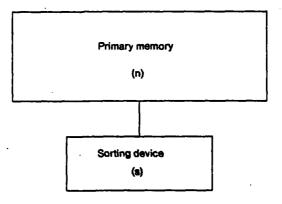

Figure 3-1: System configuration.

We distinguish the following hierarchy of memories (Figure 3-1): secondary memory, primary memory, and the special-purpose device. Under this hierarchy, two levels of problem decomposition need to be considered. On the first level a large problem exceeding the primary memory capacity has to be decomposed and appropriate partitions brought to the primary memory to be processed. Two decomposition schemes will be discussed at the end of this chapter. This level of decomposition can be carried out with the aid of some kind of secondary associative storage devices, as discussed in the previous chapter. A second level of decomposition is the partitioning of data elements inside the primary memory to be handled by a tree machine of smaller size. This will be discussed in Chapter 5. Throughout this chapter, however, we assume a "large" tree machine in the sense that every tuple stored in the primary memory has an alternate representation (such as its memory location and part of the complete tuple) stored in a node of the tree machine.

# 3.2 General Description of the Tree Machine