AD-A090 178 HONEYWELL SYSTEMS AND RESEARCH CENTER MINNEAPOLIS MN UNIT UNDER TEST SIMULATOR FEASIBILITY STUDY.(U) JUN 80 S J NUSPL, D T LEE, JP HUDSON F3361 UNCLASSIFIED 805RC46 AFWAL-TR-80-1091 F/G 14/2 F33615-79-C-1811 NL 10:3 40901 H

LEVE

0

; ; ;

AFWAL-TR-80-1091 /

# UNIT UNDER TEST SIMULATOR FEASIBILITY STUDY

AD A 0 9 0 1 7 8

Honeywell

SYSTEMS & RESEARCH CENTER

2600 RIDGWAY PARKWAY MINNEAPOLIS, MINNESOTA 55413

June 1980

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

AVIONICS LABORATORY AIR FORCE WRIGHT AERONAUTICAL LABORATORIES AIR FORCE SYSTEMS COMMAND WRIGHT-PATTERSON AIR FORCE BASE, OHIO 45433

#### NOTICE

When Government drawings, specifications, or other data are used for any purpose other than in connection with a definitely related Government procurement operation, the United States Government thereby incurs no responsibility nor any obligation whatsoever; and the fact that the government may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data, is not to be regarded by implication or otherwise as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture use, or sell any patented invention that may in any way be related thereto.

This report has been reviewed by the Office of Public Affairs (ASD/PA) and is releasable to the National Technical Information Service (NTIS). At NTIS, it will be available to the general public, including foreign nations.

This technical report has been reviewed and is approved for publication.

NELSON N. ESTES Project Engineer

FOR THE COMMANDER

RAYMOND E. SIFERD, Col, USAF Chief, System Avionics Division Avionics Laboratory RAYHOND D. BELLEM, Lt Col, USAF Chief, Support Systems Branch Avionics Laboratory

"If your address has changed, if you wish to be removed from our mailing list, or if the addressee is no longer employed by your organization please notify AFWAL/AAAF, W-PAFB, OH 45433 to help us maintain a current mailing list".

Copies of this report should not be returned unless return is required by security considerations, contractual obligations, or notice on a specific document.

AIR FORCE/56780/24 September 1980 - 80

|          | UNGLASSIFIED                                                                                                    | <u> </u>                                                         |                                                           |                                                                                                                                                       |        |

|----------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| SECU     | RIT LASSIFICATION OF THE                                                                                        | S PAGE (When Data Entered)                                       |                                                           |                                                                                                                                                       |        |

|          | ( 14 PEPORT DOC                                                                                                 | UMENTATION PAGE                                                  |                                                           | READ INSTRUCTIONS BEFORE COMPLETING FORM                                                                                                              |        |

| 1 1 1 1  | AFWAL TR-80-1091                                                                                                |                                                                  | 1901                                                      | 3 RECIPIENT'S CATALOG NUMBER                                                                                                                          |        |

| ( F In   | NIT UNDER TEST                                                                                                  |                                                                  | 9                                                         | Final Technical Repert                                                                                                                                | ,      |

| SI<br>FI | MULATOR FEASIB<br>NAL TECHNICAL I                                                                               | ILITY STUDY .                                                    | (14)                                                      | 6 PERFORMING ORG. REPORT NUMBER 89SRC46                                                                                                               | _      |

|          | ITHOR.                                                                                                          |                                                                  |                                                           | B. CONTRACT OR GRANT NUMBER(S)                                                                                                                        | $\neg$ |

|          | ephen J./Nuspl<br>avid T./Lee                                                                                   | John P./Hudson<br>Todd C./Steeves                                | (15)                                                      | WPAFB Contract No.<br>F33615-79-C-1811 NEW                                                                                                            |        |

|          | RECEMING ORGANIZATION NA                                                                                        |                                                                  |                                                           | 10 PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS                                                                                         | ヿ      |

| 26       | 00 Ridgway Parkwa<br>inneapolis, Minnesc                                                                        |                                                                  | rei (1/                                                   | 2003-02-50                                                                                                                                            |        |

| ប        | ontrolling office NAME Anited States Air For                                                                    | ND ADDRESS<br>CE                                                 |                                                           | June 80                                                                                                                                               |        |

|          | r Force Avionics L<br>right-Patterson AF                                                                        | <u> </u>                                                         |                                                           | 19: NUMBER OF PAGES 276 pages                                                                                                                         | 1      |

|          |                                                                                                                 | ADDRESS(if different from Contro.                                | ling Office)                                              | 15. SECURITY CLASS. (of this report,                                                                                                                  | ヿ      |

| ,        |                                                                                                                 |                                                                  | . /                                                       | Unclassified                                                                                                                                          | ١      |

| ;        | (                                                                                                               | 12/- 14                                                          |                                                           | 15# DECLASSIFICATION DOWNGRADING SCHEDULE                                                                                                             | 1      |

| je       |                                                                                                                 | ed for public releas                                             |                                                           |                                                                                                                                                       | _      |

|          | OPPLEMENTARY & TES                                                                                              |                                                                  |                                                           |                                                                                                                                                       |        |

|          |                                                                                                                 |                                                                  |                                                           |                                                                                                                                                       |        |

|          |                                                                                                                 | vide it becomes and electric by MATE                             | block number)                                             |                                                                                                                                                       | -[     |

| Ui<br>Si | UT<br>nit Under Test<br>mulator<br>utomatic Test Equip                                                          | Verific                                                          | ation and                                                 | d Validation                                                                                                                                          |        |

| pr<br>in | nis report addresse<br>stential solution for<br>cograms for automa<br>crease the effective<br>evelopment costs. | s the use of a Unit U<br>supporting the verific test equipment ( | Inder Te<br>lication a<br>ATE). T<br>tion and<br>involved | st (UUT) simulator as a and validation (V&V) of test the objectives are to validation and to reduce a top-down look at the techniques and (continued) |        |

DD FORM 1473 LEDITION OF 1 NOV 45 IS OBSOLETE

402349

CANCELL ASSISTICATION OF THIS PAGE: When Dain Entered,

#### 20. (continued)

stechnologies that could be applied to realize a UUT simulator. The recommended solution is based on multiple levels of simulation and uses either an instrument bus interface to the test equipment or a software-only-based interface to the test-program interpreter. Further issues of cost effectiveness must be addressed for the Modular Automatic Test Equipment (MATE) context.

# CONTENTS

| Section |                                          | Page |

|---------|------------------------------------------|------|

| 1       | INTRODUCTION AND SUMMARY                 | 1    |

| 2       | PROBLEM DEFINITION                       | 5    |

|         | Validation and Verification (V&V)        | 5    |

|         | Problem is Real and Costly               | 6    |

|         | UUT Availability Problem Examples        | 8    |

|         | UUT Damage/Refurbishment Problems        | 9    |

|         | Elements of a UUT Simulator              | 9    |

|         | Classes of UUTs                          | 9    |

|         | The ATE Itself                           | 11   |

|         | Limited Data                             | 12   |

|         | Can the UUT Be Eliminated?               | 12   |

| 3       | UUT SIMULATOR REQUIREMENTS               | 15   |

|         | Requirements Collection Methods          | 16   |

|         | UUT Simulator Start Time (R.1)           | 17   |

|         | Modeling Levels (R. 2)                   | 18   |

|         | Physical Requirements (R. 3)             | 19   |

|         | Time Requirements (R. 4)                 | 20   |

|         | V&V Session Functionality (R.5)          | 20   |

|         | Simulation System Control Support (R. 6) | 25   |

# CONTENTS (continued)

| Section |                                                                                                  | Page |

|---------|--------------------------------------------------------------------------------------------------|------|

|         | Baseline Requirements Definition                                                                 | 39   |

|         | UUT Simulator Start Time (R.1)                                                                   | 39   |

|         | Modeling Levels (R. 2)                                                                           | 40   |

|         | Physical Requirements (R. 3)                                                                     | 42   |

|         | Time Requirements (R. 4)                                                                         | 43   |

|         | V&V Session Functionality (R.5)                                                                  | 43   |

|         | Simulation System Control Support (R. 6)                                                         | 51   |

|         | Enhancements                                                                                     | 52   |

|         | UUT Simulator Start Time (R.1)                                                                   | 52   |

|         | Modeling Levels (R.2)                                                                            | 53   |

|         | Physical Requirements (R. 3)                                                                     | 57   |

|         | Time Requirements (R. 4)                                                                         | 58   |

|         | V&V Session Functionality (R. 5)                                                                 | 60   |

|         | Simulation System Control Support (R. 6)                                                         | 60   |

|         | Requirements Information From Literature                                                         | 62   |

|         | Questionnaire Results                                                                            | 64   |

| •       | As a Test Program Validator                                                                      | 64   |

|         | What Were the Problems and How Would You Rank Them in Severity?                                  | 67   |

|         | How Would You Validate a TPS if its UUT Was Difficult to Obtain or its Availability Was Limited? | 71   |

|         | TRD and ATLAS Program Analyses                                                                   | 76   |

|         | TRD Analysis                                                                                     | 76   |

# CONTENTS (continued)

| Section |                                        | Page |

|---------|----------------------------------------|------|

|         | ATLAS Program Analysis                 | 85   |

| 4       | SOLUTION ALTERNATIVES                  | 89   |

|         | Simulation Techniques                  | 90   |

|         | Circuit Level Analog Simulation        | 91   |

|         | Digital Circuit Gate-Level Simulation  | 100  |

|         | Functional Simulation                  | 111  |

|         | Interface-Level Simulation             | 142  |

|         | Mixed-Level Simulation                 | 143  |

|         | Additional Information From Literature | 146  |

|         | Applicable Technologies                | 155  |

|         | Computer Hardware                      | 156  |

|         | Solution Categories                    | 160  |

|         | Solution Components                    | 167  |

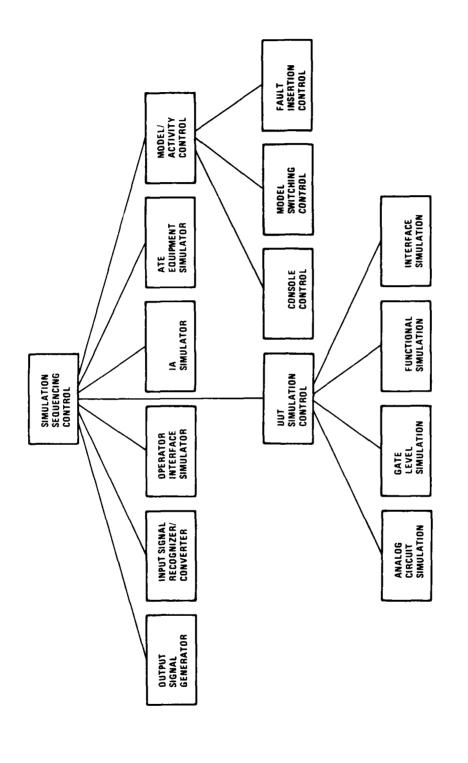

|         | Simulation Sequencing Control          | 171  |

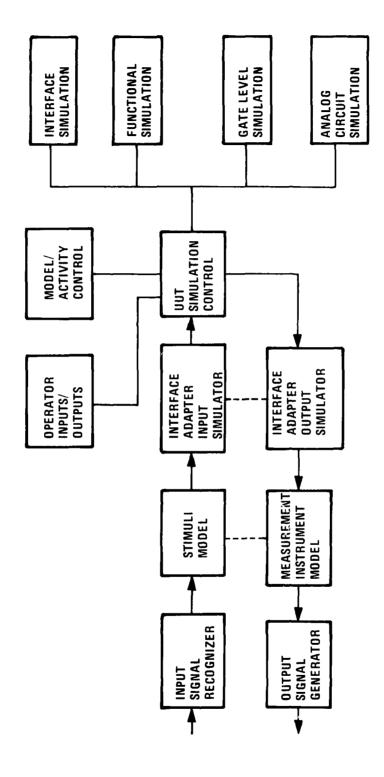

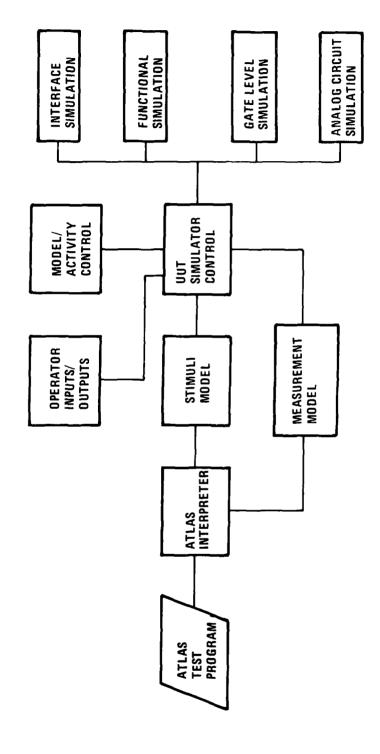

|         | UUT Simulation Control                 | 174  |

|         | Analog Circuit Simulation              | 175  |

|         | Gate-Level Simulation                  | 176  |

|         | Functional Simulations                 | 177  |

|         | Interface Level Simulation             | 178  |

|         | Output Signal Generator                | 178  |

|         | Input Signal Recognizer/Converter      | 179  |

# CONTENTS (continued)

| Section |                                                      | Page |

|---------|------------------------------------------------------|------|

|         | Operator Interface Simulator                         | 180  |

|         | Interface Adapter Simulator                          | 180  |

|         | ATE Equipment Simulator                              | 181  |

|         | Model/Activity Control                               | 181  |

|         | Common Support Modules                               | 183  |

|         | Model Data Base Support                              | 183  |

|         | Other Support Components                             | 184  |

|         | Solution Selection                                   | 187  |

| 5       | SOLUTION DISCUSSION                                  | 196  |

|         | Solution Recommendations and Comments                | 196  |

|         | Usage Scenarios                                      | 200  |

|         | Minimal Baseline Scenario                            | 201  |

|         | Interactive Scenario                                 | 202  |

|         | Batch Mode Scenario                                  | 204  |

|         | Model Changing Scenario                              | 205  |

|         | Additional Usages                                    | 206  |

|         | Semiautomated Support for Test<br>Program Generation | 206  |

|         | Training Support                                     | 206  |

|         | UUT Specification in TRD                             | 207  |

|         | Integrated Repository of UUT  Behavior in Field      | 207  |

# CONTENTS (concluded)

| Section    |                                                                       | Page        |

|------------|-----------------------------------------------------------------------|-------------|

|            | Support for Post Mortem of Catastrophic Failures                      | 208         |

|            | Interface Adapter Verification                                        | 208         |

| 6 CC       | DNCLUSIONS                                                            | 211         |

| REFERENCE  | es es                                                                 | 217         |

| APPENDIX A | A. REFERENCE CONTENT CLASSIFICATION                                   | 237         |

| APPENDIX I | S. SPECIFIC EXAMPLES OF STIMULI AND RESPONSE CLASSIFICATIONS FOR TRDs | <b>24</b> 5 |

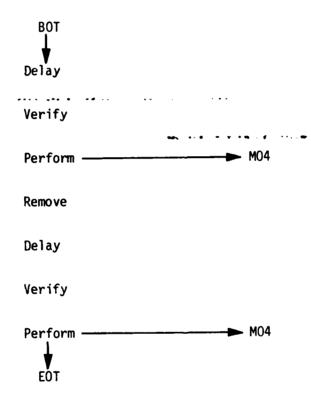

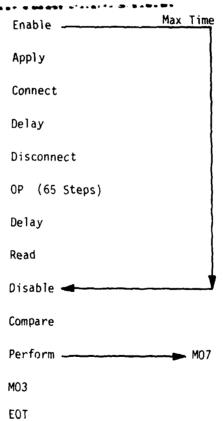

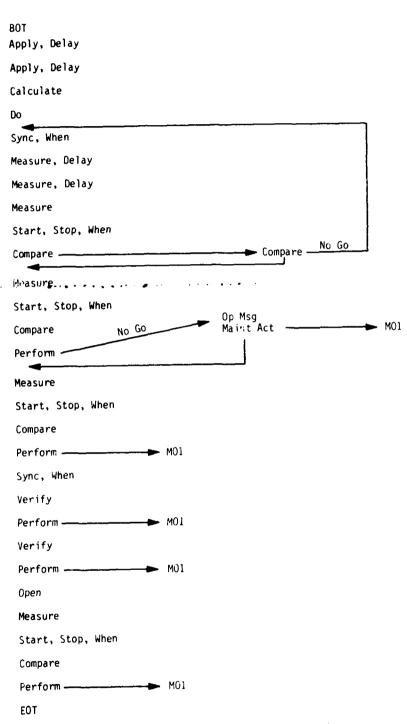

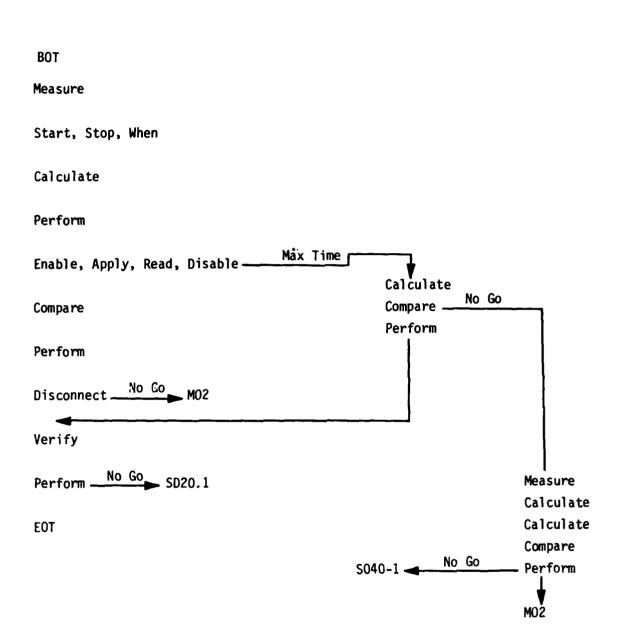

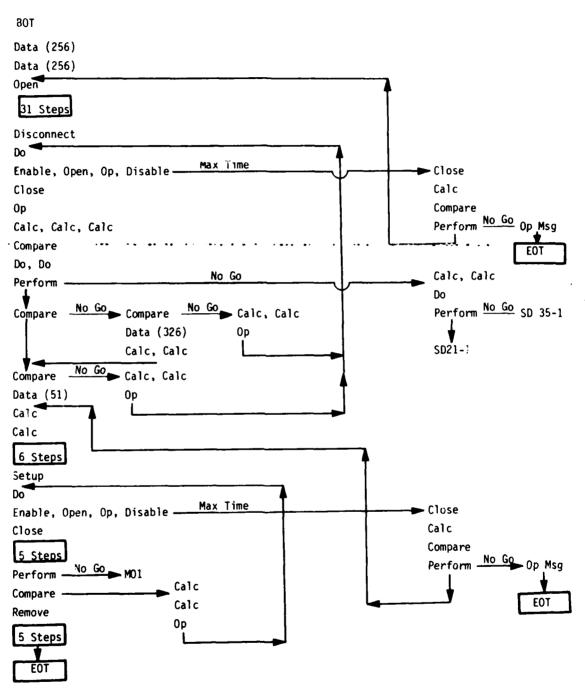

| APPENDIX ( | C. ATLAS TEST PROGRAM FLOW DIAGRAM EXAMPLES                           | <b>2</b> 55 |

# LIST OF ILLUSTRATIONS

| Figure | ·                                       | Page |

|--------|-----------------------------------------|------|

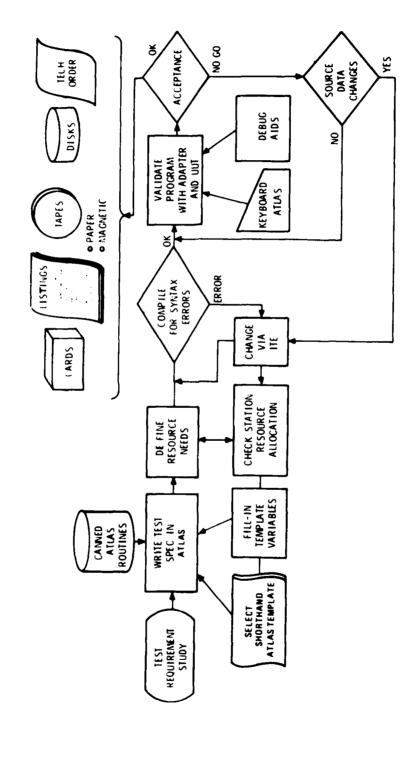

| 1      | ATLAS Test Program Development Process  | 7    |

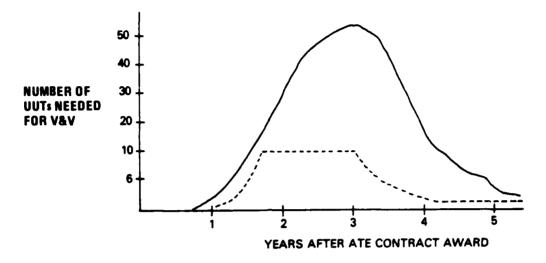

| 2      | UUT Requirements at V&V Efforts         | 10   |

| 3      | Functional Simulation Representation    | 114  |

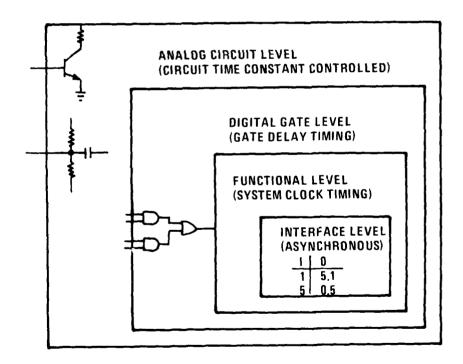

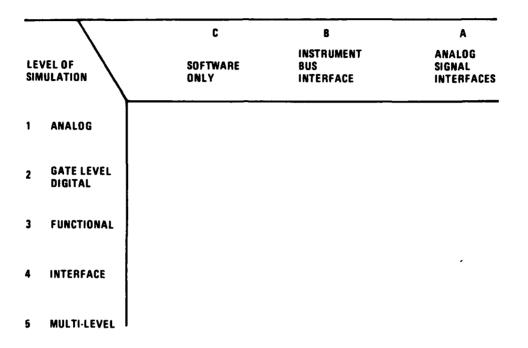

| 4      | Levels of Simulation                    | 161  |

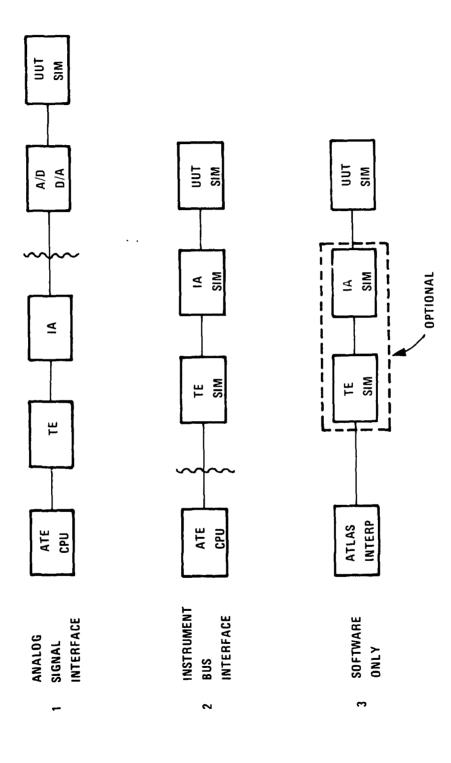

| 5      | UUT Simulator Interface Methods         | 164  |

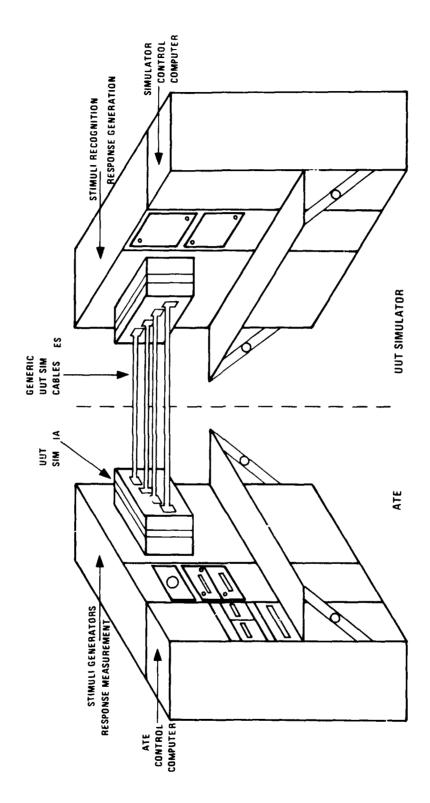

| 6      | Drawing of UUT Simulator (Analog Level) | 165  |

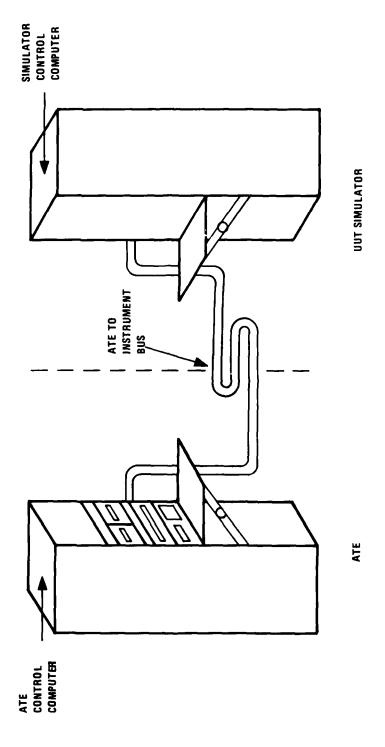

| 7      | Drawing of Interface-Bus Visualization  | 168  |

| 8      | UUT Simulator Signal Flow Model         | 170  |

| 9      | Software-Only Form of UUT Simulator     | 172  |

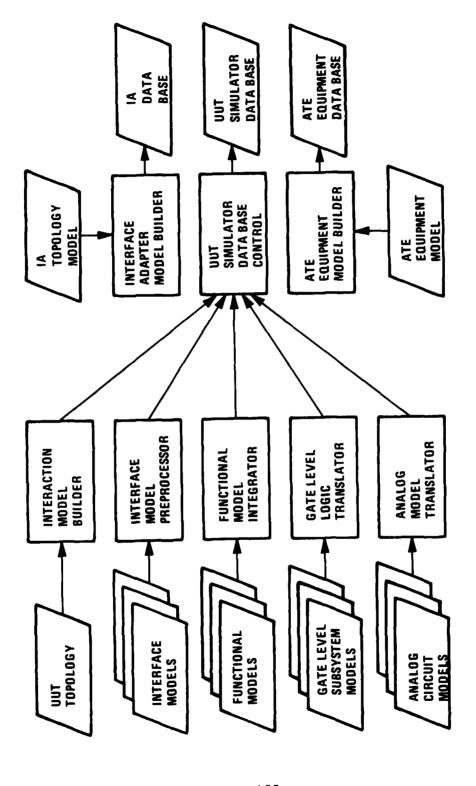

| 10     | UUT Simulator Components                | 173  |

| 11     | UUT Simulator Support Functionality     | 185  |

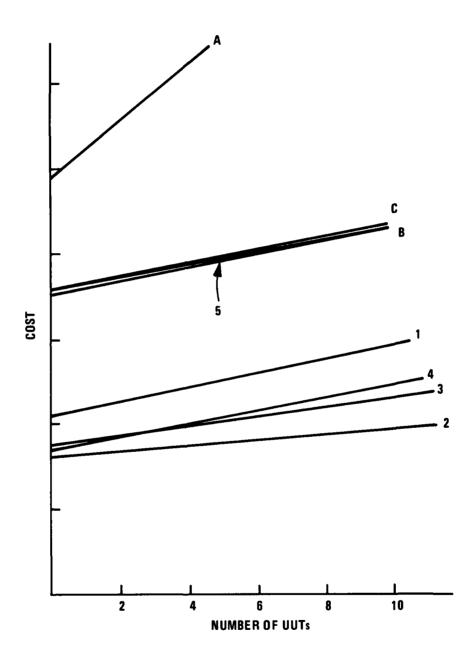

| 12     | Initial Trade-off Matrix Format         | 188  |

| 13     | Summary Costs for UUT Simulator         | 194  |

# LIST OF TABLES

| Table |                                                 | Page |

|-------|-------------------------------------------------|------|

| 1     | UUT Simulator Requirements Categories           | 18   |

| 2     | A Summary of UUT Simulator Requirements Results | 27   |

| 3     | TRD Analysis Results                            | 82   |

| 4     | ATLAS Test Program Logic Flow Diagrams          | 86   |

| 5     | Major Computer-Aided Circuit Design Programs    | 93   |

| 6     | Program Features                                | 94   |

| 7     | Analysis Details                                | 95   |

| 8     | Output Details                                  | 96   |

| 9     | System Capability (Gate level)                  | 105  |

| 10    | General Considerations (Gate level)             | 106  |

| 11    | IC Modeling (Gate level)                        | 107  |

| 12    | Circuit Modeling (Gate level)                   | 108  |

| 13    | Good-Circuit Simulation (Gate level)            | 109  |

| 14    | Fault Simulation (Gate level)                   | 110  |

| 15    | System Capability (Functional)                  | 118  |

| 16    | General Considerations (Functional)             | 121  |

| 17    | IC Modeling (Functional)                        | 126  |

# LIST OF TABLES (concluded)

| Table |                                      | Page |

|-------|--------------------------------------|------|

| 18    | Circuit Modeling (Functional)        | 130  |

| 19    | Good-Circuit Simulation (Functional) | 133  |

| 20    | Fault Simulation (Functional)        | 137  |

| 21    | Reference Literature Summary         | 147  |

| 22    | Component Development Costs          | 190  |

| 23    | Incremental Usage Cost Factors       | 192  |

## LIST OF ACRONYMS

AATPG Analog Automatic Test Program Generation

AIS Avionics Intermediate Shop

ATE Automatic Test Equipment

ATG Automatic Test Generation

ATLAS Abbreviated Test Language for Avionic Systems

ATPG Automatic Test Program Generation

ATS Automatic Testing System

CAD Computer Aided Design

CAP Circuit Analysis Program

COMPSIG Complementary Signals

CUT Circuit Under Test

DATPG Digital Automatic Test Program Generation

DoD Department of Defense

FI Fault Isolation

HATS Hybrid Automatic Test System

HDL Hardware Discription Language

HOL High Order Language

IA Interface Adapter

ID Interface Device (Interface Adapter)

ILASS Intermediate Level Avionic Support System

ITA Interface Test Adapter

LRU Line Replaceable Unit

MATE Modular Automatic Test Equipment

OIT Operator Interface Terminal

## LIST OF ACRONYMS (concluded)

OPAL Operational Performance Analysis Language

PIU Programmable Interface Unit

RATEL Raytheon Automatic Test Equipment Language

RTL Register Transfer Language

SIP Standard Interface Package

SPICE Simulation Program with Integrated Circuit Emphasis

SRA Shop Replaceable Assembly

SRU Shop Replaceable Unit

TEEM Test Equipment Effectiveness Model

TPS Test Package Set (also Test Program Set)

TRD Test Requirement Document

UUT Unit Under Test

V&V Verification and Validation

VAST Versatile Avionics Shop Test

VCOMP VAST Compatibility Program

WRA Weapon Replaceable Assembly

#### SECTION 1

#### INTRODUCTION AND SUMMARY

The development and maintenance of test programs have become one of the main cost factors in Air Force weapons systems. One of the major components of these development costs is Verification and Validation (V&V). This report addresses the use of a Unit Under Test (UUT) simulator as a potential solution in reducing V&V costs and in increasing the effectiveness of the V&V.

The typical approach during test program V&V is to execute the manually-generated test programs on the Automatic Test Equipment (ATE), using a real UUT to verify that the programs operate as intended. The following are some typical problems which are encountered:

- UUT unavailability during the V&V phase

- Delay of test program verification because the spare UUTs being used are pulled back for higher priority needs

- Delays because of UUT damage due to errors in the test programs

- Uncertainty of test-program coverage because fault paths cannot be forced in the UUT being used for V&V.

It was determined by the Air Force that one potential solution to the above problems is to use a UUT simulator rather than a real UUT during

as much of the V&V activity as possible. To assess the merit of this approach, the Air Force initiated the UUT Simulator Feasibility Investigation Study Program. This report covers the findings in the performance of this program.

The study approach basically involved a top-down look at the problem to be solved and a bottom-up look at the techniques and technologies that could be applied to realize a UUT simulator. During the first part of the program the following top-down activities were performed:

- Requirements were collected from the literature, from a validator survey, from analyzing Test Requirement Documents (TRDs), and from analyzing representative ATLAS test programs.

- A baseline set of requirements was established.

- A set of enhancement features was defined and prioritized.

- UUT simulator usage scenarios were postulated.

- Potential Interface Adapter (IA) verification usage was defined.

The specifics of the above are covered in Sections 2 and 3 of this report.

As a part of the bottom-up activities, the following were performed:

- The literature was searched for potentially applicable simulation techniques.

- Extensions of the techniques and specific sets of UUT simulator solutions were postulated.

- Trade-off information was derived for the classes of UUT simulators.

- Based on this information, recommended solutions were derived.

- Additional uses for a UUT simulator aside from supporting V&V were considered.

The results of the above are covered in Sections 4 and 5 of this report.

The following set of conclusions summarizes the outcome of the UUT simulator feasibility study program:

- The feasibility of simulators for classes of UUTs in the digital, analog, and hybrid area is clear; their cost-effectiveness in V&V must still be validated.

- To be most effective the UUT simulator development must start early in the development cycle of a Line Replaceable Unit (LRU), and the simulator must be based on the UUT design or schematics. From Modular Automatic Test Equipment (MATE) program inputs, it was found that the UUT simulator should be oriented more toward ensuring that the V&V provides better checks on the TRD and on the test programs than toward minimizing the cost of developing test programs.

- The UUT simulator should be used as an orthogonal check on the validity and completeness of the testing as embodied in the TRD and in the test programs. Assessment of fault coverage completeness to minimize LRU down-time when in the field is a key payoff factor.

- The UUT simulator should be based on multiple levels of simulation and on either a software-only or an instrument bus

interface with the ATE system on which the test programs are executed. Solutions based on analog signal interfaces are not recommended.

- In using the UUT simulator as recommended above, the Test

Package Set (TPS) development costs may actually increase. However, the resulting increase in test program quality (and

consequently improved UUT uptime) should more than offset this

increase.

- A UUT simulator is not a total or the only solution in supporting V&V and in decreasing test program development and maintenance costs. A real UUT must still be used during a part of the validation. Automatic test program generation, if realizable and cost-effective, reduces the need for a UUT simulator.

- Test program developers and validators must be convinced of the merits of a UUT simulator. A demonstration program addressing further issues and supporting the validation of the UUT simulator concept is necessary before large scale usage of UUT simulators.

- Additional UUT simulator cost-effectiveness issues must be resolved. It is not clear yet whether it is most cost-effective to develop a generic UUT simulator system, whether families of such systems should be developed, or whether it will suffice to simply develop a set of guidelines to support the construction of unique UUT simulators based on specific weapon program requirements.

#### SECTION 2

#### PROBLEM DEFINITION

This section presents a more detailed picture of the problem that the UUT simulator is addressing. Specific examples are used to demonstrate to the reader the reality of the problem. Experiences with a very low fidelity form of simulator are also described.

# VALIDATION AND VERIFICATION (V&V)

Verification and validation of UUT test programs involve a complex set of disciplines. When the validator encounters a problem implementing a test, he must discriminate where the problem originates:

- Is it the test program software?

- Is the test program stepping outside the ATE capabilities?

- Is the ATE itself at fault? If so, is it by design deficiency or malfunction?

- Is the interface test adapter mating the UUT to the ATE at fault?

If so, is it be design deficiency or malfunction?

- Is the UUT failing? If so, how can this be verified?

- Is the Test Requirement Document (TRD) for the UUT accurate, up-to-date, and correct?

Figure 1 depicts one version of an ATLAS test program development process. Though greatly affected by prior elements, V&V begins at the step "Validate Program with Adapter and UUT" and continues beyond acceptance of the first Test Package Set (TPS). The reason V&V actually continues beyond "sell off" is perceivable when considering multiple test systems deployment. Each ATE system must "play" with each of its TPSs to be operational. Experience at Warner Robins Air Logistic Command (WRALC) has shown that because of UUT variability, there is only 25 percent confidence that a TPS, when validated with only one UUT, will work with all UUTs. This confidence jumps to 75 percent for a TPS validated against two UUTs and 90 percent for three UUTs.

Typically, however, V&V is thought of as just through sell off of the first TPS. When used in this context, V&V usually accounts for about 40 percent of the TPS development process.

#### PROBLEM IS REAL AND COSTLY

To characterize the problem, let us look at an example derived from Honeywell experience. As an ATE supplier of the F-15 ADTS and F-15 TITE systems, Honeywell has total ATE and TPS development, integration, and V&V responsibility. This V&V activity has produced over 500 Avionics LRU and module TPSs during the last five years. Because each TPS effort involved usage of at least one UUT, at a few thousand dollars value each, many millions of dollars worth of UUTs have been tied up during this V&V effort. In the case of LRUs, the problem can sometimes be more

Figure 1. ATLAS Test Program Development Process

noticeable because the V&V cycle is usually longer and the LRU cycle is more costly. For example, on F-15 TITE, LRU No. 3 (Countermeasures Computer) required availability of three LRUs for one and one-half years during V&V.

#### UUT AVAILABILITY PROBLEM EXAMPLES

At Honeywell we have found that more typically LRU V&V requires an availability of one and one-half LRUs. The extra one-half LRU would generally be for card/plug-in module replacements for trouble-shooting and repair of the LRU in V&V. While this is possible with LRUs, it is not always practical, and it will not suit module level V&V at all.

These practical limitations on V&V activities were very clearly illustrated in the minutes of two recent F-15 TITE Technical Meetings:

- "There is a shortage of Band 1 UUTs. There is a total of four Band 1 UUTs; three of these four UUTs are defective. The only good UUT is being used in RF amplifier testing. Two of the other UUTs are being returned to St. Charles for repair. The other defective UUT will be kept at the site (V&V) for limited use during validation. The diodes required for repair of these UUTs have arrived from Northrop."

- "Verification of ATE Stations 10 through 15 at Honeywell, Minneapolis, presents no problems for the ICS UUTs; however, TITE does not have available enough EWWS and RWR UUTs for verification at Honeywell, Minneapolis, while maintaining UUTs at the St. Louis site for sustaining work."

## UUT DAMAGE/REFURBISHMENT PROBLEMS

Going beyond availability of good UUTs, V&V faces the inevitable damage of a UUT during V&V. Typical causes for such UUT damage are as follows:

- Oscilloscope probe damage to Avionics module protective coating of components

- Inadvertent electrical damage to the UUT by grounding with probes

- Incorrect application of UUT power

While the first cause may be understandable in a validation environment and not too expensive to repair, the second and third causes can be very costly because damage to both the UUT and ATE can be extensive. But even if damage is minimal, a defective (damaged) UUT will usually shut down V&V effort because a second UUT is not available. Honeywell experience on F-15 shows the average time to repair a UUT is one to two weeks, and a minimum of 3 days is required. This discontinuity in the V&V effort has a very adverse effect on cost and schedules for ATE projects.

#### ELEMENTS OF A UUT SIMULATOR

## Classes of UUTs

The typical requirements for UUT availability in a TPS development project are portrayed in Figure 2 (solid line). The dashed lines in this

Typical requirements for UUT availability in a TPS development project

Goal of reducing need for UUT

Figure 2. UUT Requirements at V&V Efforts

figure illustrate the goal of driving down the need for UUTs and reducing the time they are involved in V&V. If a universal UUT simulator were available that could stand up to V&V in place of any UUT, this could indeed drive the dashed line near zero. This problem is bounded somewhat by requiring coverage of only analog, digital, and hybrid UUTs. However, all classes of UUTs are encountered in TPS development and as such these "classes"--

- Analog

- Digital

- Hybrid

- High Power

- RF

- Microwave

- Video

- Pneumatic

- Inertial

- Communication

should also be considered as worthy targets of the solution.

# The ATE Itself

The ATE where TPS development is conducted should also be considered an element in any simulation approach. Modularization of ATE promised by the MATE program could have a dramatic impact on a UUT simulator solution. If interfaces in MATE are standard and accessible, a simulator may be able to intercept native ATE functions rather than be a slave to the general ATE I/O ports.

Perhaps, though, the ideal simulator would not concern itself with the ATE, but rather conduct itself as the UUT would-responding to ATE stimuli with an expected UUT response. In this way, the UUT simulator could be used on any ATE, not just those with MATE-defined interfaces. Besides, it may not be practical to allow a V&V effort to have access to internal ATE functions.

## Limited Data

Any UUT simulator must also address the problems of attaining information about the UUT. UUT Test Requirements Documents (TRD) misinformation has been proven, time and time again, to be a back breaker of TPS development programs. Acquiring information necessary for UUT simulation could be an equally frustrating experience. For a simulator to conduct itself as the UUT would perform, it may be necessary to obtain UUT design information as well as UUT performance information as contained in the TRD. This may be another practical limit to simulation, considering the consequences of vendor proprietary design information.

Consideration should be given to approaches to simulation that minimize the need for design information about the UUT. Perhaps the simulator should concern itself with only the UUT I/O interfaces—the signal types, ranges of stimulus and response constraints, data envelop formats, etc. Such information, because it may be more readily attainable and be fairly correct (because a companion LRU or module depends on this interface), may be a viable data base for construction of a UUT simulator.

## Can the UUT Be Eliminated?

Unless one narrows and descopes the classes of UUTs and the types of tests validated on these UUTs (i.e., simple, moderate, or complex synchronized tests), it would be difficult, if not impossible, to totally eliminate the UUT from V&V. A UUT simulator approach that could eliminate the need for a UUT during 99 percent of the V&V effort, but was effective only for digital card UUTs, might be easy to achieve. But

another approach, which would eliminate the need for a UUT 80 to 90 percent of the time and which would cover a broader class of digital, analog, and hybrid LRUs or modules may, indeed, provide a better ratio of performance to development cost.

A relatively simple but effective simulation approach was recently developed by Honeywell for the F-16 Depot TPS development. For F-16 Depot, Honeywell was chosen to supply analog test stations. General Dynamics/Fort Worth (GD/FW) had TPS development responsibility. Because of schedule constraints, GD/FW needed a mechanism that would allow them to begin TPS development prior to delivery of analog test stations. As a result, Honeywell delivered the F-16 Depot Mini-Disc Expanded Memory System (UG26000GD01) in August 1978. As in many ATE program development stations, this system allowed test program generation to proceed in a very effective manner. But because this system, called Mini-DEMS, was implemented with a set of computer and peripheral devices identical to the analog test station, TPS V&V, as well as test system training capabilities, were added. This was accomplished by adding software and a circuit card to the computer I/O bus extension that would act as a null interface, "simulating" any analog test station ATE instrumentation. The Mini-DEMS has allowed GD/FW to actually execute the ATLAS test programs they develop. This Mini-DEMS has allowed the V&V process to proceed, eliminating not only the need for a UUT, but also the ATE itself and the interface test adapter. In addition, because the Mini-DEMS reacts just like the analog test station, it has served as a very effective ATE operation trainer also. Two Mini-DEMS were delivered to GD/FW, one in August 1978, the other in September 1978 (one will be delivered to USAF later).

TPS development and V&V have proceeded on a multishift basis at GD/FW since this delivery. Those test programs that had completed V&V testing on a Mini-DEMS were ready for final integration with the ATE which arrived in January 1979. Using this approach, 30 to 40 percent of the V&V effort was possible without the UUT.

#### SECTION 3

### **UUT SIMULATOR REQUIREMENTS**

This chapter contains the definitions of the requirements which must be satisfied in order for the UUT simulator to realize the projected benefits. The first section contains a brief description of the methods used to collect the requirements. It shows that a comprehensive multi-faceted approach was used to arrive at the requirements. Reaching the same conclusions with different approaches lends credibility to the requirements.

The second section contains a definition of the baseline requirements for the UUT simulator. This set of requirements is fundamental to the operation of the simulator in the anticipated scenarios. If these requirements are not met, we project that the expected benefits of the UUT simulator will be lessened.

The third section contains a definition of the UUT simulator enhancements, prioritized according to their expected value. The features described here are expected to provide some payoff if included in the simulator, but they are "wants" rather than "musts." The prioritization was performed on a basis of payoff rather than on a basis of expected additional cost of the feature.

The remaining sections of this chapter contain additional documentation supporting the baseline requirements and enhancements. The topics discussed are requirements information from the literature, questionnaire results, and TRD/ATLAS program analyses.

# REQUIREMENTS COLLECTION METHODS

A properly scoped activity to collect information, which impacts the requirements definition, is the key first step in arriving at a good UUT simulator definition. The collection must be performed from different angles of attack to ensure a good composite picture of what the problem is and what is needed. This was accomplished on our program by performing the following activities:

• A Literature Survey—A number of approaches was used to search for relevant information in the literature, which would help to clarify the nature and extent of the problem being addressed, which would describe relevant experience with simulation techniques or other methods for overcoming the problems, and which would possibly identify solutions that have already been used. During the literature search we did not concentrate as much on solutions as on trying to identify the problem. We were more interested during this stage of the program in information that would lead to requirements rather than solutions.

The results of the literature survey are discussed in more detail in this section. These results and further observations from papers which we reviewed but did not document had a strong influence on the UUT simulator requirements defined in this chapter.

A Survey Questionnaire—Based on preliminary discussions with test program developers and validators, a survey questionnaire was developed and distributed both within Honeywell and to outside experts. The results from the responses and in some cases verbal discussions helped to formulate requirements constraints. By using the questionnaire we were able to find information which typically would not appear in formal papers in conferences.

• TRD/ATLAS Program Analysis—A representative set of test requirements documents and ATLAS test programs was chosen from the F-15 TITE program. These were then analyzed for complexity and for characteristics which would influence the requirements for a UUT simulator. The detailed results of this analysis are found in this section. Again, the UUT simulator requirements presented in this chapter reflect what was learned in the analysis.

When all the information had been collected, we looked at a number of alternative ways of coalescing it and presenting it. We finally decided to use the form of categorization of the requirements as shown in Table 1. This method allows a reasonably orthogonal presentation of the UUT simulator features and supports a structured presentation which will make it easier for the reader to keep the requirements separated. The following briefly discuss the categories which are used.

# UUT Simulator Start Time (R.1)

This requirement has to do with the relative phasing of the UUT development, the development of the test program set for the UUT, and the development of the UUT simulator. In the ideal case, the UUT simulator could be started when the UUT is still in design. In some cases the UUT simulator must be

TABLE 1. UUT SIMULATOR REQUIREMENTS CATEGORIES

- R. 1 UUT Simulator Start Time

- R. 2 Modeling Levels

- R.3 Physical Requirements

- R. 4 Time Requirements

- R. 5 V&V Session Functionality

- 5.1 Initialization

- 5.2 Interactive Simulation Session

- 5.3 Interactive Session Control

- 5.4 Performance Constraints

- 5.5 Simulation Session Preparation

- 5.6 Post-Simulation Evaluation

- R. 6 Simulation System Control Support

developed after the UUT has already been fully developed. It is still important to have adequate design and interface information to be able to develop an adequate simulator.

# Modeling Levels (R. 2)

The level of modeling of the UUT determines the level of fidelity at which the UUT simulator mimics the actual UUT. At one extreme, digital and analog UUTs are simulated with precise circuit models. At the other extreme, only the interfaces which interact with the ATE equipment are sufficiently modeled to produce representative responses. The two extremes can also be considered analogous to models used in electronic maintenance training simulators:

- A "simulation based" maintenance trainer is one in which the

interaction is based on simulation models of the device being

trained. Internal states are maintained so that the simulation is

reasonably realistic.

- A "procedural" trainer is one in which only the interface is simulated to a sufficient degree to allow a student to follow a sequence of steps in a Technical Order.

The "procedural" form of trainer corresponds to a UUT simulator based on interface characteristics only. This form of a simulation tends to be less expensive, but adequancy of fidelity is an issue.

For automatic test program verification there are additional modeling requirements beyond the UUT: the interface adapter, any operator interfaces (such as pots or switches), and the ATE equipment (depending on the simulation approach).

# Physical Requirements (R. 3)

These requirements have to do with the required level of ruggedness of the equipment performing the UUT simulation, the location of the equipment relative to the ATE to which the UUT is connected, and the fidelity of the electrical signals at the interface. Physical portability is also a requirement to be considered in this category.

# Time Requirements (R. 4)

There are a number of different aspects of time which may be required by the UUT simulator:

- Operation speed as compared to real time

- Block allocation time which may constrain the user access to the simulator

- Immediacy of access

- Response time to activities requested by the user

- Familiarization time for a user to become proficient in the use of the simulator

# V&V Session Functionality (R. 5)

The requirements in this category have to do with the use of the UUT simulator during a session in which an automatic test program is being verified. To help partition the requirements into a more structured format, the following subsections are used:

- Initialization (R. 5.1)

- Interactive Simulation Session (R. 5.2)

- Interactive Session Control (R. 5. 3)

- Performance Constraints (R. 5. 4)

- Simulation Session Preparation (R. 5. 5)

- Post-Simulation Evaluation (R. 5. 6)

Each of these subsections is briefly discussed below.

<u>Initialization (R. 5.1)</u>—Initialization includes activities required to start the system, to activate the desired UUT simulation model, to start the operator interface, and to activate auxiliary models such as the Interface Adapter model if present.

Interactive Simulation Session (R. 5.2)—Requirements in this subsection are key in making the UUT simulator achieve the expected benefits. The user must be able to adequately control the interaction of the simulation with the ATE and the external environment. Furthermore, the simulation must provide him with feedback and must be adequately responsive so that he uses his time in debugging and verifying test programs efficiently. The requirements are further divided into the following categories:

Input Requirements (R. 5.2.1)—All inputs which must be sensed by the UUT simulator from the operator, from the ATE, and from the simulated environment are included. These inputs are simulations of equivalent inputs which must be sensed by the real UUT.

Output Requirements (R. 5. 2. 2)—All the outputs which must be generated by the UUT simulator are included. Also specified in this section are the means by which the outputs are calculated.

Simulation Status Outputs (R. 5.2.3)—In addition to the outputs which mimic the real UUT outputs, the UUT simulator can have additional internal states which can help in the process of debugging and verifying the test programs. This section contains the requirements for outputting such information.

Performance Monitoring (R. 5, 2, 4)—During the process of simulating a UUT being exercised by a specific test program, information can be collected on the performance of the test program and on the performance of the UUT. This information can then be used in evaluating how well the test program is exercising the UUT.

On-Line Performance Evaluation (R. 5. 2. 5)—Functional requirements in this category determine what performance information can be extracted while the simulation is still in progress. As a result of getting such information, the user makes changes in the test program or in the method of simulation to improve the performance indicators which he is watching.

Procedural Branching Control (R. 5. 2. 6)—An important aspect of a UUT simulator is the ability to force the test program into exercising all of the test branches. The requirements determine the different types of procedural control needed.

Patch and Retain Temporary Changes (R. 5. 2. 7)—During the debug phase of test program development it is necessary to allow the programmer to make incremental modifications so that he can gauge their effect on the simulation and on how the test program responds.

Interactive Session Control (R. 5.3)—This set of requirements characterizes how the user can control the progress of his session on the UUT simulator. The requirements are further classified into the following categories:

Freeze/Run/Replay (R. 5.3.1)—Capabilities are specified here as to the extent of control of the simulation in terms of stopping it, allowing it to continue, and restarting it at a previous point.

Monitoring Level Control (R. 5. 3. 2)—The requirements in this section determine the amount of control over tracing of simulator variables.

Utility Functions (R. 5. 3. 3)—This section includes requirements for special utility functions which are needed to support control of the simulation.

<u>UUT Simulator Messages (R. 5. 3. 4)</u>—The requirements in this section include the types of messages which must be provided to indicate to the user that the simulator has encountered error conditions or that capacities of the system are close to being exceeded.

<u>Performance Constraints (R. 5.4)</u>—This section contains requirements on the performance of the UUT simulator during a V&V Session. The two areas covered are performance, when used in a batch mode, and responsiveness, when used in an on-line mode.

Simulation Session Preparation (R. 5.5)—Requirements in this category are concerned with the features in the UUT simulator, which are oriented to helping the user plan and prepare for a simulation session. The following are the subsections:

<u>Function Selection (R. 5. 5.1)</u>—The requirements are included for selecting specific cases from a set of alternatives available. For example, selection of a specific UUT and selection of specific operating modes may have to be supported.

Malfunction Selection (R. 5. 5. 2)—The requirements in this section include the ability to force the simulator to mimic specified malfunctions which will, in turn, force the test program into specific procedures.

<u>Procedure Selection (R. 5. 5. 3)</u>—If response in the simulation can be determined by procedures, this section contains requirements on the selection and modification of these procedures.

Simulation Preparation/Selection (R. 5. 5. 4)—This section includes requirements on the ability to prepare specifics of the simulation such as amount of detail and values for specific parameters.

<u>Trace Level Selection (R. 5. 5. 5)</u>—The requirements included determine the ability to preset trace levels and detail before the simulation is started.

<u>Post-Simulation Evaluation (R. 5.6)</u>—The requirements in this section include capabilities of the system to support evaluation of results after the simulation has been completed. The following are the subsections included:

Test Program Evaluation (R. 5. 6. 1)

Save Performance Reports (R. 5. 6. 2)

Display Specific Reports (R. 5. 6. 3)

#### Simulation System Control Support (R. 6)

Requirements in this section include those features of a computer system required to keep the system operational and to keep the system updated with the latest information on the simulation components. The following subsections are included:

Initialization (R. 6.1)

Operational Assurance (R. 6.2)

Subsystem Switching Control (R. 6.3)

Off-Line Activity Control (R. 6.4)

System Instrumentation (R. 6. 5)

System Recovery (R. 6. 6)

Configuration Management Support (R. 6.7)

Performance Data Reduction Support (R. 6.8)

Load Projection/Enhancement Support (R. 6.9)

Data Base Support (R. 6. 10)

Off-Line Preparation/Maintenance (R. 6.11)

A summary of the UUT simulator requirements results is presented in the matrix in Table 2. The requirements categories discussed above appear with two columns. The first column contains an "x" if the corresponding requirement is in the baseline. If there is no "x" in the first column, the feature is classified as an enhancement. In this case there is a number from 1 to 3 in column 2. A "3" indicates high value of the feature and a "1" indicates a low value. The individual requirements are further explained in the following two sections of this chapter.

| 1 |   | 1       | 2     | ì     |

|---|---|---------|-------|-------|

| 1 | X | 1       |       | 1     |

|   |   |         |       |       |

| ! |   | 1 1 1 1 | 2 2 1 | 1 1 1 |

| ; |   |         |       |       |

|   |   |         |       |       |

| ; | x | 1       | 1     | ;     |

| 1 | x | 1       |       | 1     |

| ł |   | ŀ       | 3     | ¦     |

|   |   | ; x     | x     |       |

|    | Modeling Language                                              |        |   |   |             |             |

|----|----------------------------------------------------------------|--------|---|---|-------------|-------------|

|    | English Language Based (ATLAS-like)                            | 1      | x | 1 |             | 1           |

|    | Graphical                                                      | 1      |   | 1 | 2           | ;           |

|    |                                                                |        |   |   |             |             |

|    | Fault Simulation Capability                                    |        |   |   |             |             |

|    | Interface Level<br>Functional Module Level                     | 1      | X | 1 | 2           | 1<br>1<br>1 |

|    | Circuit Level                                                  | 1      |   | 1 | 1           | 1           |

|    |                                                                |        |   |   |             |             |

| 3. | Physical Requirements                                          |        |   |   |             |             |

|    | Hardware Reliability                                           |        |   |   |             |             |

|    | Militarized                                                    | 1      |   | 1 | 1           | 1           |

|    | Ruggedized<br>Commercial                                       | i<br>! | X | i | 1 2         | 1           |

|    | Location                                                       |        |   |   |             |             |

|    | Adjacent ATE<br>Remote and Real Time Access                    | -      |   | 1 | 3<br>1<br>1 | ;           |

|    | Remote Only                                                    | į      |   | 1 | 1           | ;           |

|    | Physical Portability                                           |        |   |   | 2           |             |

|    | Movable among ATE Stations<br>Transportable to Different Sites | 1      |   | 1 | 3           | 1           |

|    | Electrical Signals                                             |        |   |   |             |             |

|    | Bypassed (via bus interface)                                   | i      | Х | ì |             | i           |

|    | Nominal Values<br>(not accurate)                               | ł      |   | 1 | 1           | 1           |

|    | Accurate Values                                                | 1      |   | ! | 2           | 1           |

|    | Accurate Signals + noise effects                               | 1      |   | 1 | 3           | ì           |

|    |                                                                |        |   |   |             |             |

### 4. Time Requirements

| Real Time (UUT Operation) Full Real Time Scaled, Reduced time Asynchronous                                              |             | x |       | 1   | 1 1 1     |

|-------------------------------------------------------------------------------------------------------------------------|-------------|---|-------|-----|-----------|

| Block Time (How Quickly<br>How Long)<br>Continuous Usage<br>Allocatable by Block<br>Time                                | ;<br>;<br>; |   | 1 1 1 | 1 3 | !         |

| Access Requirements On Demand Flexible Schedule Fixed Schedule                                                          | †<br>†<br>† | x | :     | 3   | 1 1 1 1 1 |

| Response Time (Validators Perspective) No Perceptible delays from real UUT operation Up to 2 Min delays (or 5 sec/step) |             |   |       | 2   |           |

| Familiarization Time No Training Required (Built in Aids) 2 Day Training +                                              | ;<br>;      |   |       | 3   |           |

| Month Familiarization<br>About as long as<br>learning ATE Use                                                           | ;           |   |       | 2   |           |

| 5. V and V Session Functional Requirements                                                                |                       |             |        |     |        |

|-----------------------------------------------------------------------------------------------------------|-----------------------|-------------|--------|-----|--------|

| 5.1 Initialization                                                                                        |                       |             |        |     |        |

| System Initialization Display Panel Switches Restart at Saved State                                       |                       | x<br>x<br>x |        |     | 1 1    |

| UUT Model Identification<br>Verify Proper Model<br>Provide Parameter<br>input for model                   | !                     | x<br>x      | :      |     | :      |

| ATE Interface Model Identification<br>Verify Proper Model<br>Provide Parameter<br>Input for Model         | ;<br>;<br>;           | x<br>x      | !<br>! |     | 1      |

| Operator Interface<br>Initialize Simulator<br>Unique Functions                                            | }                     | х           | ;      |     | ;      |

| (eg. Starting Collection) Select Operation Mode                                                           | ;                     | х           | !      |     | 1<br>t |

| 5.2 Interactive Simulation Session                                                                        |                       |             |        |     |        |

| 5.2.1 Input Requirements                                                                                  |                       |             |        |     |        |

| Input Sensing Requirements                                                                                |                       |             |        |     |        |

| UUT Panel / Manual Inputs<br>Soft Keys<br>Test Points<br>Dynamic (Manually<br>Controlled) Model Parameter | t<br>1<br>1<br>1<br>1 | X           | 1 1 1  | 3 2 | 1 1 1  |

| ATE Signal Routing                                                  | ; | X      | 1 |   | ; |

|---------------------------------------------------------------------|---|--------|---|---|---|

| Interface Signals  ATE Inputs  Recognize Valid  Signal Gen. Command | 1 | x      | 1 | 2 | 1 |

| UUT Environment Simulator<br>Cooling Monitor                        | ļ |        | 1 | 2 | 1 |

| 5.2.2 Output Requirements                                           |   |        |   |   |   |

| 5.2.2.1 Calculate Outputs Based on                                  |   |        |   |   |   |

| ATE Inputs Operator Inputs on Simulated Panel/Controls              | ; | x<br>x | 1 |   | ! |

| Sequence of Input States Functional Simulation Model (Digital)      | ; |        | 1 | 1 | 1 |

| Functional Simulation Model (Analog)                                | 1 |        | 4 | 1 | } |

| Logic Model (Digital) Detailed Circuit Model                        | } |        | } | 2 | } |

| 5.2.2.2 Calculate Responses based on Malfunction Simulation         |   |        |   |   |   |

| Single Malfunction Multiple Sequential                              | ; | X      | 1 | 3 | 1 |

| Malfunctions<br>Multiple Concurrent<br>Malfunctions                 | i |        | 1 | 1 | ; |

| 5.2.2.3 Generate Outputs                                                                                                     |   |   |                                         |                       |           |

|------------------------------------------------------------------------------------------------------------------------------|---|---|-----------------------------------------|-----------------------|-----------|

| UUT Simulated Indicators Alphanumeric Representation Graphic Representation                                                  | 1 | x | ;                                       | 1                     | 1         |

| Outputs to ATE Interface<br>Emit Realistic Responses<br>Check validity of Measurement<br>Command                             | 1 | x | ;                                       | 2                     | 1         |

| 5.2.3 Simulation Status Outputs                                                                                              |   |   |                                         |                       |           |

| 5.2.3.1 Information Output                                                                                                   |   |   |                                         |                       |           |

| Input State from ATE Output State to ATE UUT Indicator States Selected Computed Values Internal UUT States History of States |   |   |                                         | 2<br>2<br>2<br>1<br>3 |           |

| 5.2.3.2 Output Method                                                                                                        |   |   |                                         |                       |           |

| Console CRT<br>Printer<br>On Mass Storage                                                                                    | 1 |   | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | 3<br>3<br>3           | 1 1 1 1 1 |

| 5.2.4 Performance Monitoring                                                                                                 |   |   |                                         |                       |           |

| Active Interface Pins Signal Ranges on Interfaces Closeness of signal limits to bounds limits                                | 1 |   | 1                                       | 2 2 2                 | 1 1 1     |

| 5.2.5 On-line Performance Evaluation                                     |   |        |   |   |        |

|--------------------------------------------------------------------------|---|--------|---|---|--------|

| Unused Interface Pins Average Closeness of Signal to bounds Values       | 1 |        | : | 2 | !      |

| Fault Coverage                                                           | ł |        | ! | 3 | !      |

| 5.2.6 Procedural Branching Control                                       |   |        |   |   |        |

| Manual Control of Response                                               | ; | x      | ! |   | 1      |

| to Force Test Branching<br>Control of Branching via                      | ţ | x      | ! |   | !<br>} |

| Stored Sequences Control of Branching via UUT                            | 1 | x      | ; |   | {      |

| Parameter Selection<br>Control of Branching via<br>Malfunction Selection | i | x      | ; |   | 1      |

| 5.2.7 Patch and Retain Temporary Changes                                 |   |        |   |   |        |

| Change Parameters<br>Change UUT Response<br>Procedure                    | 1 | X<br>X | 1 |   | 1      |

| Change UUT Model                                                         | ; | X      | ì |   | ì      |

| Incrementally<br>Substitute UUT Model                                    | 1 |        | 1 | 3 | 1      |

| Components<br>Store Model for Later<br>Recall                            | } | x      | } |   | ł      |

5.3 Interactive Session Control

#### 5.3.1 Freeze/Run/Replay Freeze State from | x | | Simulator Console Freeze State From 1 1 1 ATE Command Automatically Trigger Freeze on UUT Simulator Bounds Error Expected Signal Error 1 3 After Specified no. actions Programmed Condition Freeze and Restart After Fixed Delay On Operator Initiation Save Frozen State on | x | | Command from Console Save Frozen State on 1 121 Command from ATE Restore Previous State | x | | 5.3.2 Monitoring Level Control Trace Control Based on Console Level | | 2 | and Coded Threshold Based on Programmed 1 1 1 Conditions 5.3.3 Utility Functions | x | | Soft Keys for UUT Simulator Control

| 5.3.4 UUT Simulator System Messages                                    |   |             |       |   |   |  |

|------------------------------------------------------------------------|---|-------------|-------|---|---|--|

| Simulator Error Conditions<br>System Status<br>System Error Conditions | ! | x<br>x      | ;     | 3 | ! |  |

| 5.4 Performance Constraints                                            |   |             |       |   |   |  |

| 5.4.1 Batch Performance                                                |   |             |       |   |   |  |

| Less than 1 hour turnaround                                            | 1 |             | ;     | 3 | 1 |  |

| 5.4.2 Response Time Constraints                                        |   |             |       |   |   |  |

| Less than 2 seconds in<br>Single Step Mode                             | ; |             | 1     | 3 | 1 |  |

| 5.5 Simulation Session Preparation                                     |   |             |       |   |   |  |

| 5.5.1 Function Selection                                               |   |             |       |   |   |  |

| Select Function from a Function                                        |   |             |       |   |   |  |

| Menu<br>UUT to be Simulated<br>Monitoring Modes<br>Interaction Modes   |   | x<br>x<br>x | 1 1 1 |   |   |  |

| 5.5.2 Malfunction Selection                                            |   |             |       |   |   |  |

| Select Specific Malfunction                                            | 1 | x           | ;     |   | 1 |  |

| Procedures Select Parameters Inducing Malfunctions                     | 1 | x           | {     |   | 1 |  |

| 5.5.3 Procedure Selection                                              |   |             |       |   |   |  |

| Select Response Procedures Build New Response Procedures and Chain     | : | X<br>X      | 1     |   | ; |  |

| 5.5.4 Simulation Preparation/Selection                                                  |                  |        |       |             |             |

|-----------------------------------------------------------------------------------------|------------------|--------|-------|-------------|-------------|

| Select Simulation Detail<br>Level                                                       | ł                | x      | 1     |             | 1           |

| Select Specific Simulation Select Simulation Parameters                                 | 1                | X<br>X | 1     |             | 1           |

| 5.5.5 Trace Level Selection                                                             |                  |        |       |             |             |

| Based on Preset Level<br>Based on Programmed Conditions                                 | 1                |        | 1 1 1 | 3           | 1           |

| o.o Post-Simulation Evaluation                                                          |                  |        |       |             |             |

| o.o.1 Test Program Evaluation                                                           |                  |        |       |             |             |

| Generate Statistics on Coverage(Steps, Pin Usage etc.) Tolerance Limits Error Summaries | 1<br>1<br>1<br>( |        | 1 1 2 | 3<br>2<br>3 | 1 1         |

| Jenerated Simulated UUT                                                                 | 1                |        | ŀ     | 3           | i           |

| Statistics<br>Generate Simulator System<br>Statistics                                   | 1                |        | 1     | 2           | į           |

| 5.6.2 Save Performance Reports                                                          |                  |        |       |             |             |

| On Mass-storage<br>Changes from stored reports                                          | 1                |        | 1     | 3           | 1<br>1<br>1 |

| 5.6.3 Display Specific Reports                                                          |                  |        |       |             |             |

| On Display<br>On Printer<br>Compared to Saved Reports                                   | 1 1 1            |        | 1     | 3<br>3<br>2 | 1 1 1 1 1   |

| 6. Simulation System Control Support                            |        |        |        |     |   |

|-----------------------------------------------------------------|--------|--------|--------|-----|---|

| 6.1 Initialization                                              | 1      | x      | t<br>t |     | 1 |

| 6.2 Operational Assurance                                       | ;      | x      | ;      |     | 1 |

| 6.3 Subsystem Switching Control                                 | !      |        | ł      | 1   | ; |

| 6.4 Off-line Activity Control                                   | ;      |        | 1      | 2   | 1 |

| 6.5 System Instrumentation                                      | ŧ      |        | 1      | 1   | ì |

| 6.6 System Recovery                                             | 1      |        | ;      | 1   | ļ |

| 6.7 Configuration Management Support                            | 1      | x      | ;      |     | 1 |

| 6.8 Performance Data Reduction Support                          | ;      |        | ł      | 1   | ŀ |

| 6.9 Load Projection/Enhancement Support                         | i<br>i |        | 1      | 1   | ! |

| 6.10 Data Base Support                                          |        |        |        |     |   |

| UUT Models<br>ID Characteristics<br>ATE Interface Configuration | 1      | x      | 1 1 1  | 3 2 | : |

| 6.11 Off-Line Preparation/Maintenance                           |        |        |        |     |   |

| 6.11.1 Model and Procedure Preparation Support                  |        |        |        |     |   |

| Interactive<br>English-Language Based                           | :      | X<br>X | !<br>! |     | ! |

| 6.11.2 Model and Procedure Code Modification: | S |   |   |   |  |

|-----------------------------------------------|---|---|---|---|--|

| Incremental Modifications                     | 1 | x | 1 |   |  |

| 6.11.2 Interface Model Modifications          | i | Х | 1 |   |  |

| 6.11.4 UUT Simulator Verification             |   |   |   |   |  |

| Syntax Checks                                 | i |   | 1 | 3 |  |

| Inconsistency Analysis                        | ; |   | 1 | 1 |  |

#### BASELINE REQUIREMENTS DEFINITION

This section contains a discussion of the set of UUT simulator requirements which are in the baseline. This set of requirements was determined to be needed in order to realize the benefits expected of a UUT simulator for use in support of the V&V of test programs.

The requirements discussions follow the structure as defined in Section 3, Requirements Collection Methods. Only those items in Table 2 which contain an "x" in column 1 are discussed here.

#### UUT Simulator Start Time (R.1)

After the UUT Has Been Built--Based on comments from papers in the literature and from responses to our questionnaire, it can only be assumed that the UUT simulator is started after the UUT has already been built. It would be desirable to start the development of the UUT simulator during the UUT development to use as much of the available design information as possible, particularly when the test programs are developed by an organization other than the developers of the UUT; this has not been done. One of the major problems in test program development is that not enough information is generally available on the UUT to expeditiously develop the test programs. Usually a sequence of iterations of information collection is needed before the test program development can be completed.

To maximize the utility of the simulator as an independent check of the test programs during V&V, it is highly desirable that the simulator simulate the UUT as closely as possible. The UUT simulator should

therefore be based on UUT design information such as that contained in a Part II specification and a schematic. For an independent check, it is particularly important that the UUT simulator not be based on the requirements in the TRD or the code in the ATLAS test program developed to test the UUT.

Development of the UUT simulator independently of the test program development can serve as a secondary check on the adequacy of the information about the UUT. The developers can cross-check their understanding of the UUT when the test programs are finally run against the UUT simulator.

#### Modeling Levels (R.2)

#### Interface Level--

Recognize Stimuli and Generate Response (From Bus)--This level of modeling would recognize that a specific stimuli is being applied (via the ATE equipment command and the routing which is in effect). The recognition assumes the ATE is based on a bus structure architecture and that the UUT simulator can intercept and respond on the bus to mimic the stimuli generators and instruments.

. Depending on the ATE approach, this level of modeling appears to provide most of the expected benefits and is reasonably feasible.

#### Additional External Models--

Interface Adapter Model: Topology--The topology of the interface adapter must be capable of being simulated to support checking of proper signal routing during the simulation.

Operator Interface Model--Any interface between the UUT and the operator (such as switches and indicators) which the operator must observe or set, must also be capable of being simulated. See the requirement below on "soft keys" ("Utility Functions").

#### Modeling Language --

English Language Based (ATLAS-like)--If any form of UUT simulator modeling language is required (even if only very simple), it must be English Language based and similar in intent to ATLAS. The primary objective is to make the resulting models easy to read and easy to alter for an appropriately skilled model developer.

#### Fault Simulation Level--

Interface Level--Faults must be capable of being simulated in order to force the test programs into their no-go and diagnostic paths. However, as a baseline requirement it is necessary that only the faults be simulated at the interface level with interface characteristics which trigger the fault detection tests in the test programs.

#### Physical Requirements (R.3)

#### Hardware Reliability--