FAMILY OF RAYTHEON DGM DIGITAL GROUP MULTIPLEXERS 1084887.

FINAL

CORADCOM-75-0036-F2

TECHNICAL REPORT

FINAL TYPE

(Volume 2 of 2: Section 3.0, 5.0, 7.0, 15.4)

# **DGM PROGRAM** CONTRACT NO. DAAB07-75-C-0036 🗸

FEBRUARY 1980

CDRL SEQ. NO. G037

8 20 116

**PREPARED FOR:** UNITED STATES ARMY ELECTRONICS COMMAND FORT MONMOUTH, NEW JERSEY

PREPARED BY: RAYTHEON COMPANY EQUIPMENT DIVISION COMMUNICATIONS SYSTEM LABORATORY SUDBURY, MASSACHUSETTS 01776

Approved for Public Release:

Distribution Unlimited

# Best Available Copy

FAMILY OF RAYTHEON DGM 3 DIGITAL GROUP MULTIPLEXERS(DGM) Volumie FINAL FINAL TYPE TECHNICAL REPORT (Volume 2 of 2: / Section 3.0, 5.0, 7.0, 15.4) Kal rept. May 75-Feb 89 DGM PROGRAM CONTRACT NO. (DAABØ7-75-C-Ø036) 15 143 FEBRUARY 1980 2. CDRL SEQ. NO. G037 William /Hatton harles / Shthank aves PREPARED FOR: UNITED STATES ARMY ELECTRONICS COMMAND 129280100 FORT MONMOUTH, NEW JERSEY CORADCOM PREPARED BY: RAYTHEON COMPANY EQUIPMENT DIVISION COMMUNICATIONS SYSTEM LABORATORY SUDBURY, MASSACHUSETTS 01776 75-0036-FZ This document has been approved for public release and sale; its distribution is unlimited.

# TABLE OF CONTENTS

arniar daelen seri disentakun terdina

1.14

:

and the second second

|                           | Section |      |          |                                                  | Page |

|---------------------------|---------|------|----------|--------------------------------------------------|------|

|                           | 3       | LGM  |          |                                                  | 3-1  |

|                           |         | 3.1  | Design ( | Goals and Requirements                           | 3-2  |

|                           |         | 3.2  | Design A | Approach                                         | 3-2  |

|                           |         |      | 3.2.1    | Summary                                          | 3-2  |

|                           |         |      | 3.2.2    | Detailed Electrical Design for the LGM           | 3-4  |

|                           |         |      | 3.2.3    | Interface Description                            | 3-7  |

|                           |         | 3.3  | Detail F | Electrical Design                                | 3-11 |

|                           |         |      | 3.3.1    | Introduction                                     | 3-11 |

|                           |         |      | 3.3.2    | MUX/DEMUX                                        | 3-11 |

|                           |         |      | 3.3.3    | Group Framing Unit                               | 3-21 |

|                           |         |      | 3.3.4    | Timing Generator/Telemetry - LGM                 | 3-34 |

|                           |         |      | 3.3.5    | Loop Modem                                       | 3-34 |

| jath - oldfathi - 🥆<br>Na |         |      | 3.3.6    | Interface P.C.B./Interface Drivers and Receivers | 3-46 |

|                           |         |      | 3.3.7    | BITE LGM                                         | 3-56 |

|                           |         |      | 3.3.8    | Power Supply                                     | 3-57 |

|                           |         |      | 3.3.9    | Human Factors Engineering                        | 3-71 |

|                           |         |      | 3.3.10   | Reliability Design                               | 3-73 |

|                           |         |      | 3.3.11   | Summary of PQT Results                           | 3-73 |

|                           | 5       | RLGM | I        |                                                  | 5-1  |

|                           | Ū       | 5.1  |          | Goals and Requirements                           | 5-2  |

|                           |         | 5.2  | Ť        | Approach                                         | 5-4  |

|                           |         |      | 5.2.1    | Summary                                          | 5-4  |

|                           |         |      | 5.2.2    | Detailed Electrical Design of the RLGM           | 5-5  |

|                           |         |      | 5.2.3    |                                                  | 5-8  |

| <b>A</b>                  |         |      |          | _                                                |      |

ii

Stor of the states of the states

# TABLE OF CONTENTS (Cont.)

A SUMMAN IN A SUM IN THE REAL

| Section |     |                 |                                        | Page              |

|---------|-----|-----------------|----------------------------------------|-------------------|

|         | 5.3 | Detail E        | lectrical Design                       | 5-11              |

|         |     | 5.3.1           | Introduction                           | 5 <b>-</b> 11     |

|         |     | 5.3.2           | Loop Modem                             | 5-12              |

|         |     | 5.3.3           | MUX/DEMUX                              | 5-12              |

|         |     | 5.3.4           | RLGM: Framing/Synchronizer Unit        | 5-16              |

|         |     | 5.3.5           | Group Modem - RLGM                     | 5-19              |

|         |     | 5.3.6           | Timing for the RLGM                    | 5-26              |

|         |     | 5.3.7           | BITE                                   | 5-26              |

|         |     | 5.3.8           | Power Supply                           | 5-41              |

|         |     | 5.3.9           | Signal Entry Panel                     | 5-47              |

|         |     | 5.3.10          | Human Factor Engineering               | 5-52              |

|         |     | 5.3.11          | Reliability                            | 5-53              |

|         |     | 5.3.12          | Summary of PQT Results                 | 5 <del>~</del> 53 |

|         |     |                 |                                        |                   |

| 7       | RMC |                 |                                        | 7-1               |

|         | 7.1 | Design (        | Goals and Requirements                 | 7-2               |

|         | 7.2 | Design Approach |                                        | 7-5               |

|         |     | 7.2.1           | Summary                                | 7-5               |

|         |     | 7.2.2           | Detailed Electrical Design for the RMC | 7-5               |

|         |     | 7.2.3           | Interface Description                  | 7-9               |

|         | 7.3 | Detail E        | lectrical Design                       | 7-12              |

|         |     | 7.3.1           | Introduction                           | 7-12              |

|         |     | 7.3.2           | Loop Modem                             | 7-13              |

|         |     | 7.3.3           | Mux Demux (RMC)                        | 7 <del>-</del> 13 |

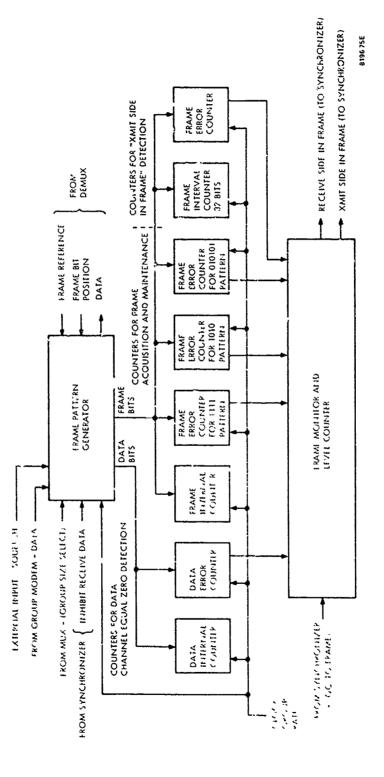

|         |     | 7.3.4           | RMC: Framing/Synchronizer Unit         | 7-23              |

|         |     | 7.3.5           | Group Modem - RMC                      | 7 <b>-</b> 27     |

|         |     | 7.3.6           | Clock and Timing for the RMC           | 7-27              |

iii

- 20

重

# TABLE OF CONTENTS (Cont.)

1

| Section |          |                                  | Page  |

|---------|----------|----------------------------------|-------|

|         | 7.3.7    | Balanced Interface               | 7-37  |

|         | 7.3.8    | BITE                             | 7-37  |

|         | 7.3.9    | Power Supply                     | 7-38  |

|         | 7.3.10   | Signal Entry Panel               | 7-44  |

|         | 7.3.11   | Human Factor Engineering         | 7-44  |

|         | 7.3.12   | Reliability                      | 7-45  |

|         | 7.3.13   | Summary of PQT Results           | 7-46  |

| 15.4    | l Mechan | ical Design - GTE Sylvania Units | 15-1  |

|         | 15.4.1   | Shelter Mounted Units            | 15-1  |

|         | 15 1 9   | Remote Units                     | 15-20 |

| Access                             | ion For                    |      | Z |

|------------------------------------|----------------------------|------|---|

| NTIS<br>DDC TA<br>Unanno<br>Justif | в                          | )[   |   |

|                                    | bution.                    |      |   |

| Avail<br>Dist.                     | ability<br>Availe<br>spect | mā/o |   |

| Ŕ                                  |                            |      |   |

iv

# LIST OF ILLUSTRATIONS

|                   | Figure |                                                    | Page   |

|-------------------|--------|----------------------------------------------------|--------|

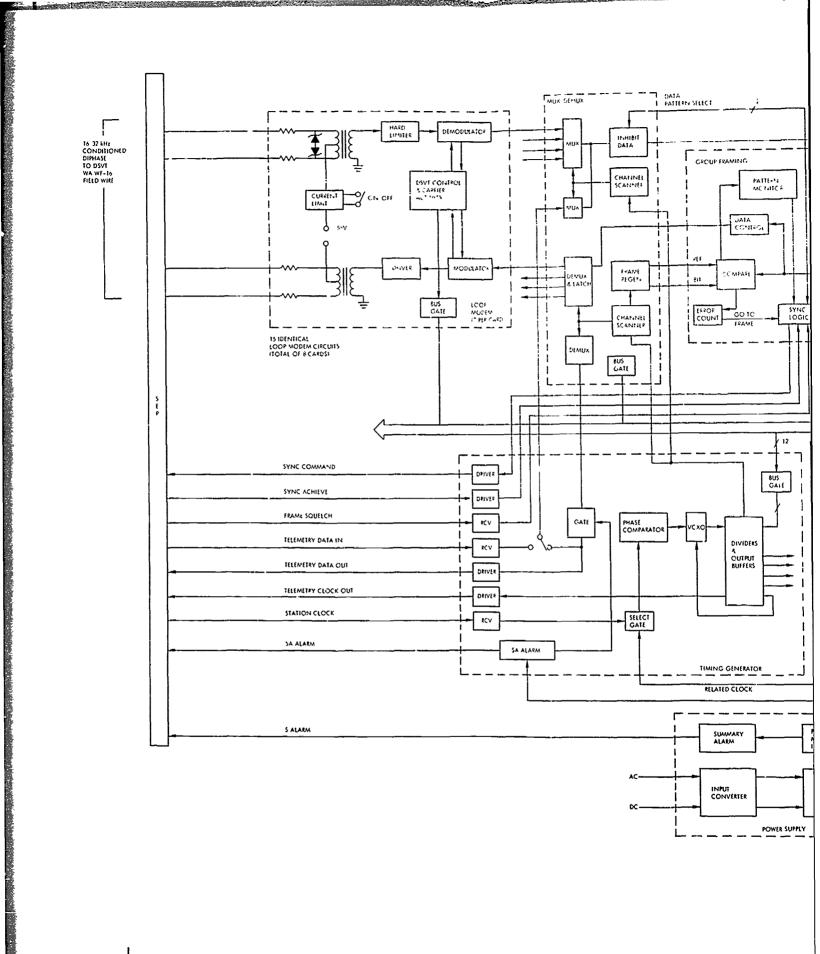

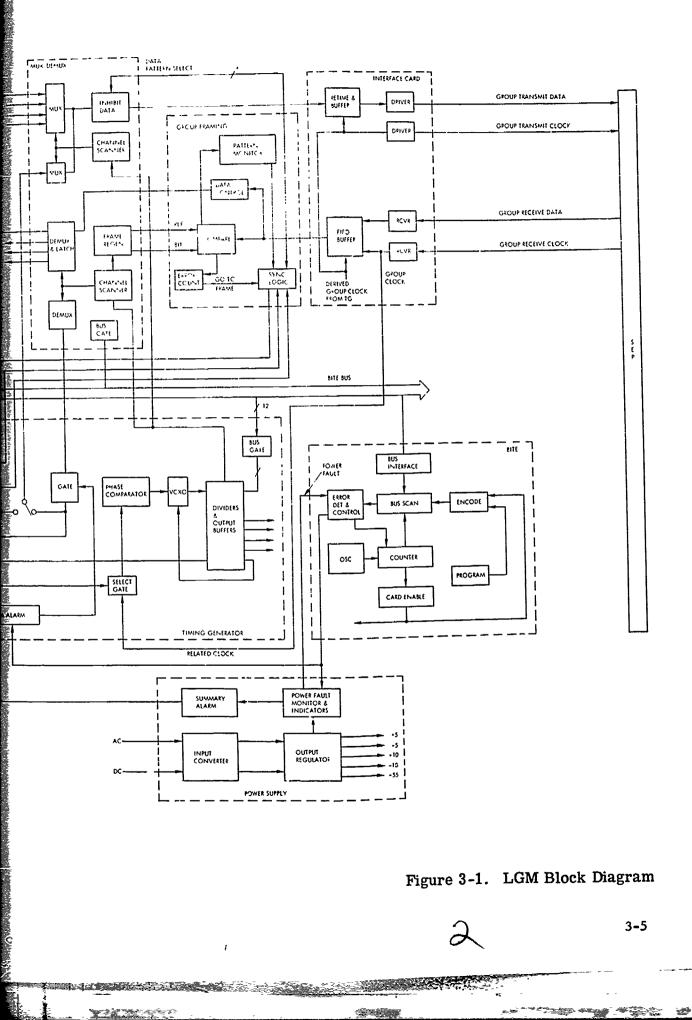

|                   | 3-1    | LGM Block Diagram                                  | 3-5    |

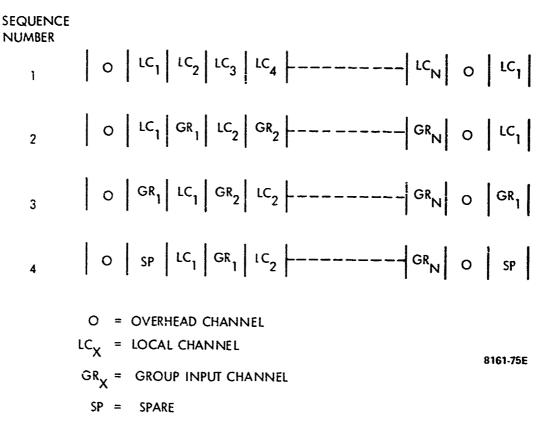

|                   | 3-2    | MUX/DEMUX Pattern Sequences                        | 3-13   |

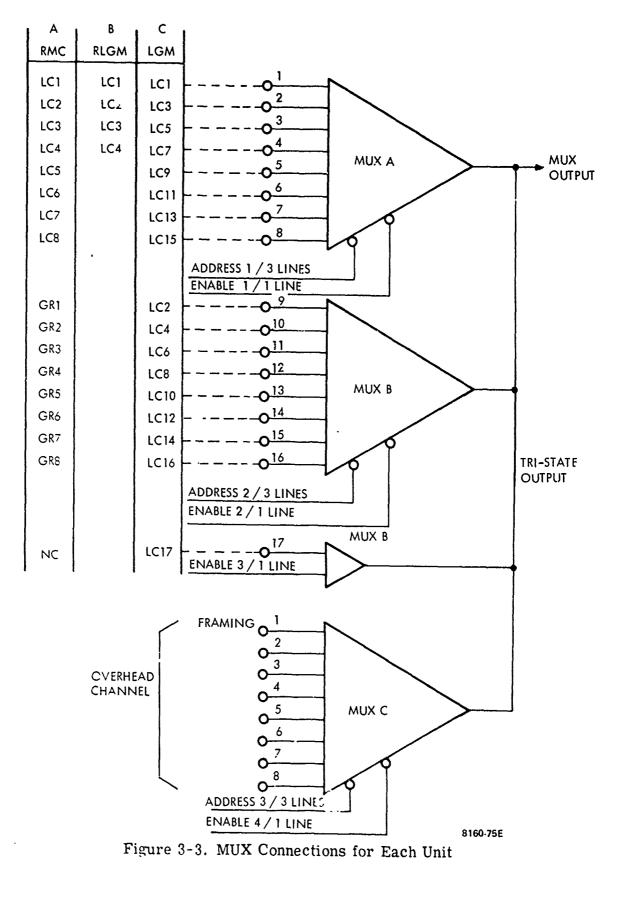

|                   | 3-3    | MUX Connections for Each Unit                      | 3-15   |

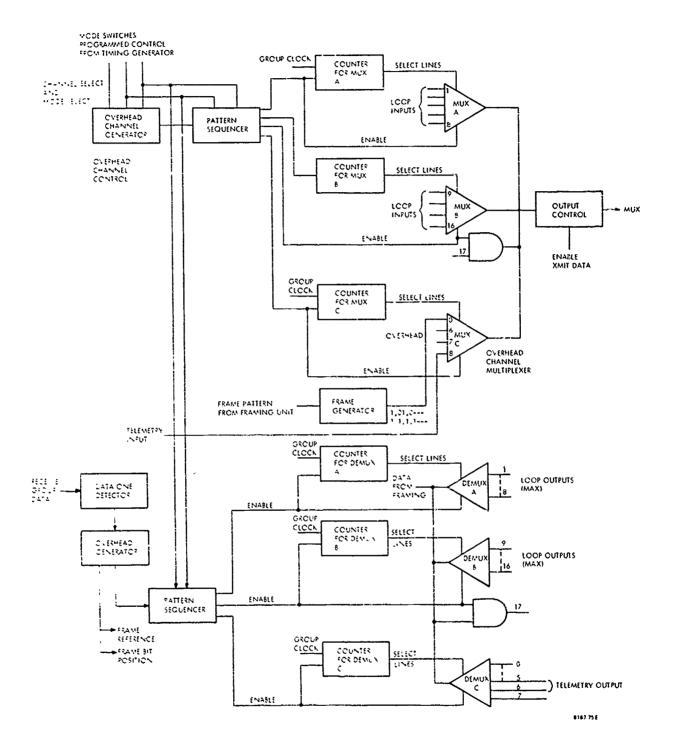

|                   | 3-4    | MUX/DEMUX Block Diagram                            | 3-18   |

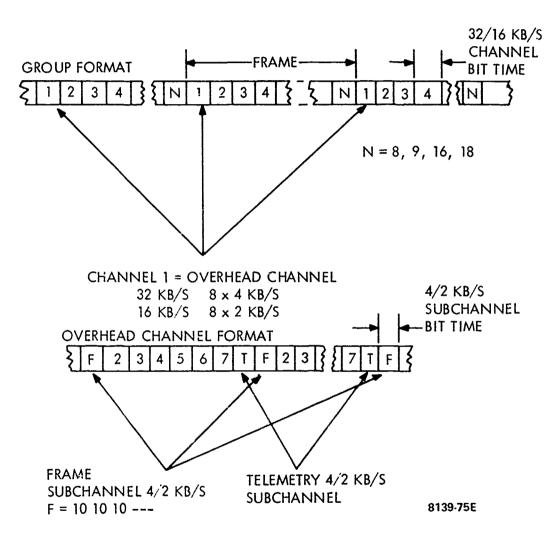

|                   | 3-5    | LGM Output Group Patterns and Overhead Channels    | 3-20   |

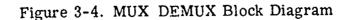

|                   | 3-6    | Framing Block Diagram                              | 3-22   |

|                   | 3-7    | LGM Group and Overhead Channel Formats             | 3-23   |

|                   | 3-8    | Frame Acquisition and Maintenance Flow Chart       | 3-27   |

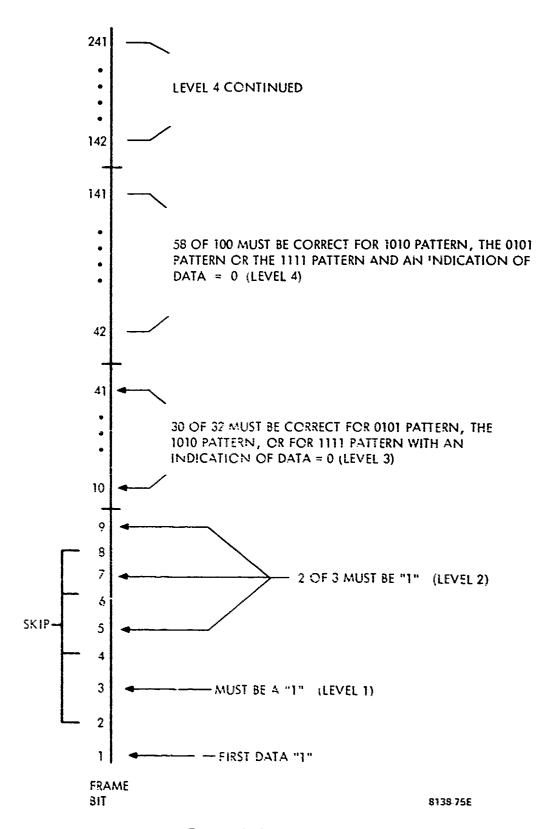

|                   | 39     | Framing Sequence                                   | 3-28   |

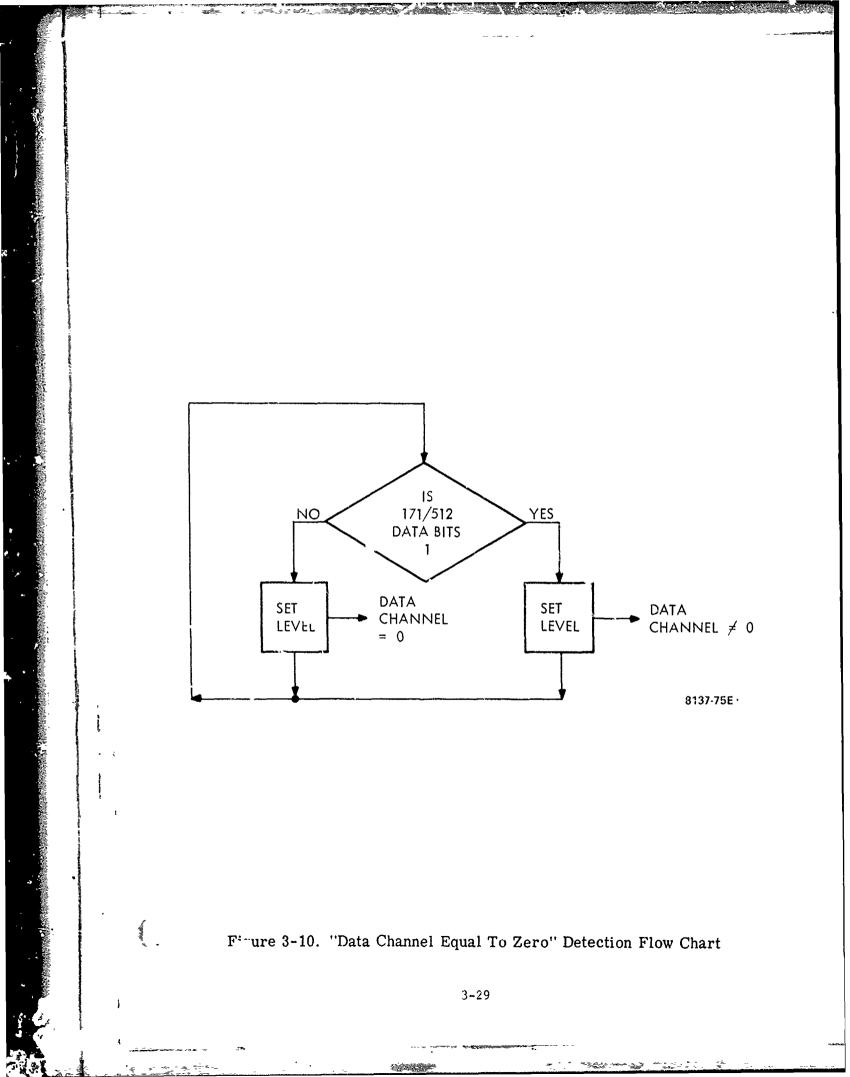

|                   | 3-10   | 'Data Channel Equal To Zerc'' Detection Flow Chart | 3 - 29 |

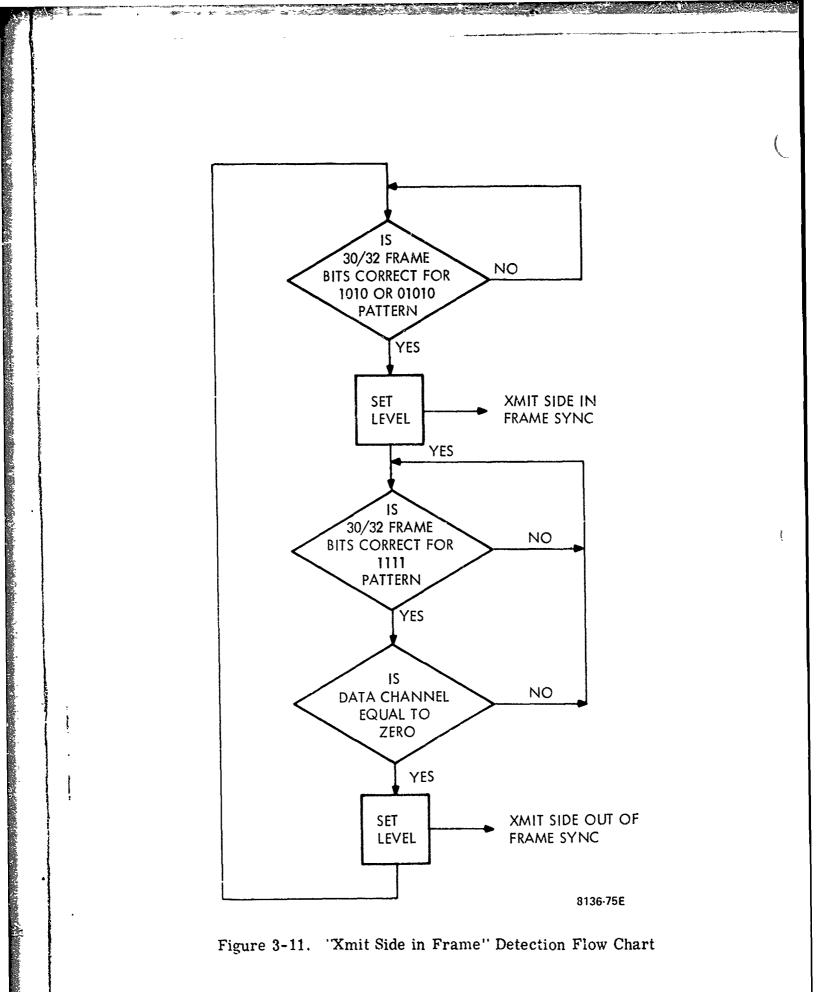

|                   | 3-11   | "Xmit Side in Frame" Detection Flow Chart          | 3-30   |

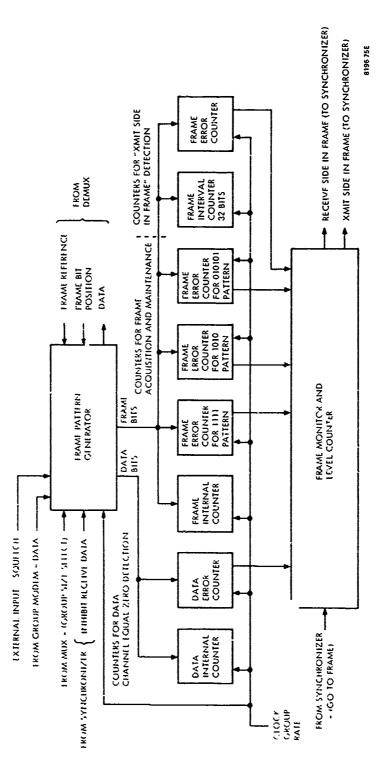

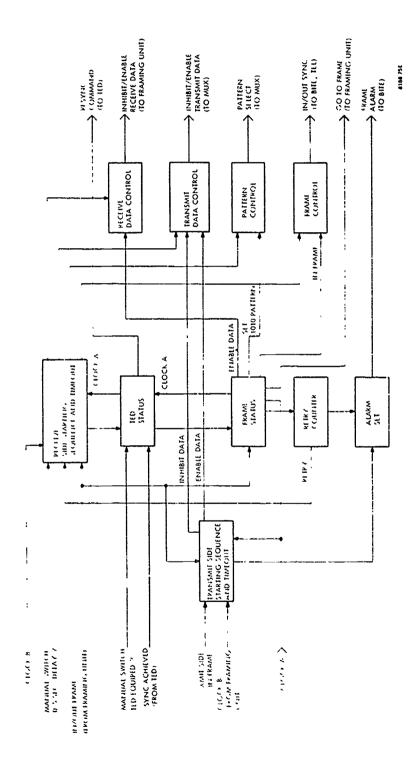

| <sup>Addale</sup> | 3-12   | Frame Synchronizer Block Diagram                   | 3-32   |

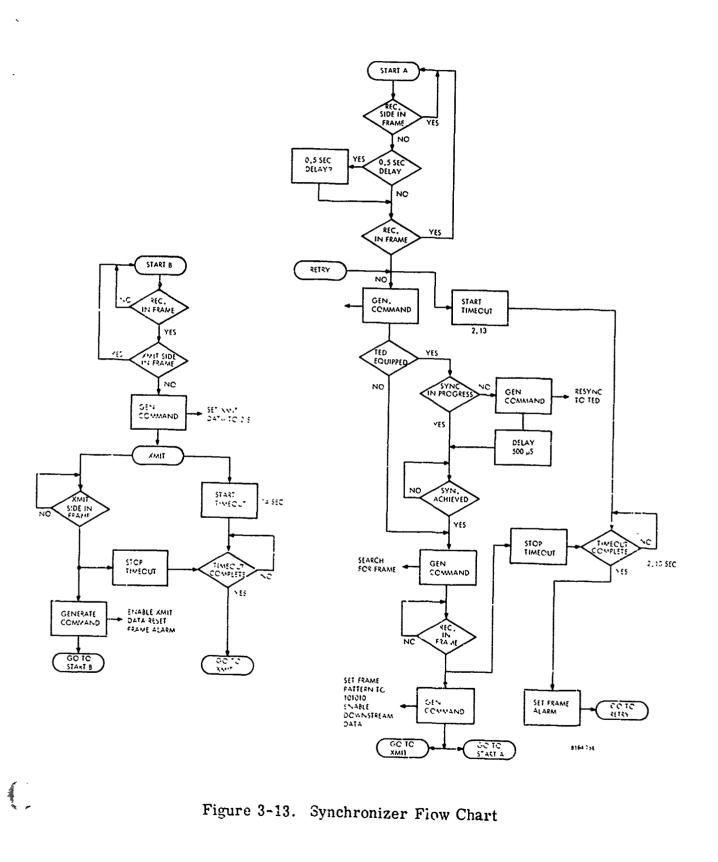

| š<br><b>N</b> 7   | 3-13   | Synchronizer Flow Chart                            | 3-33   |

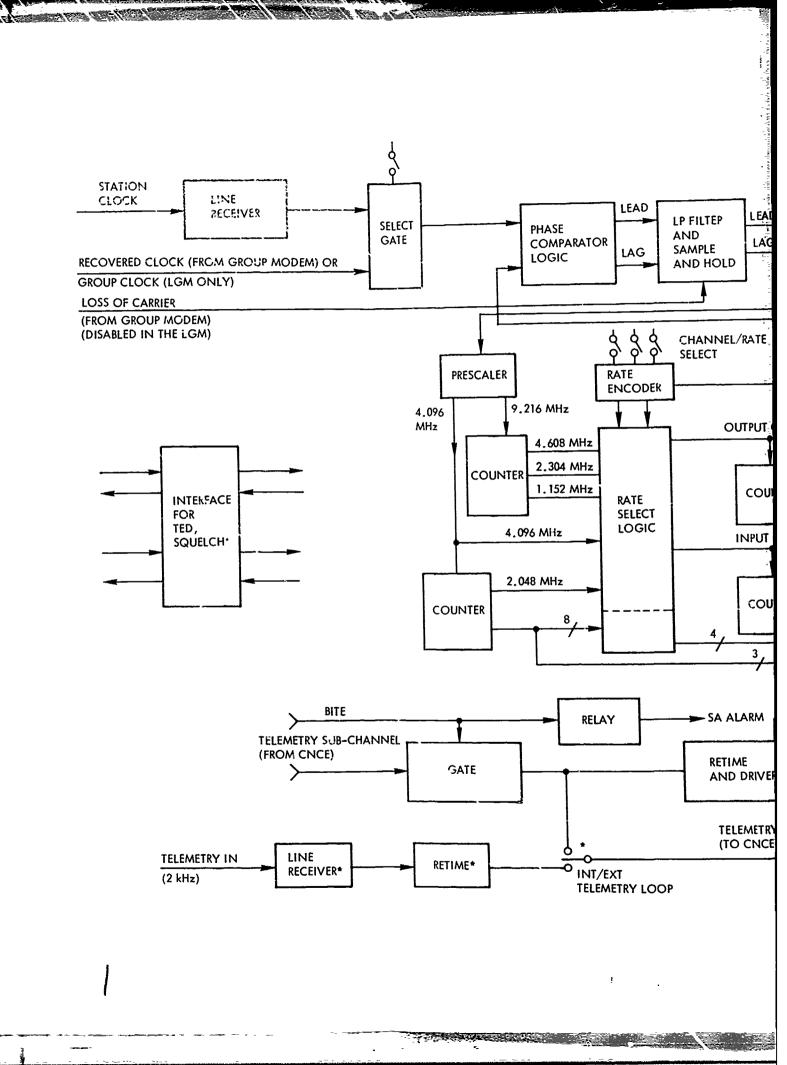

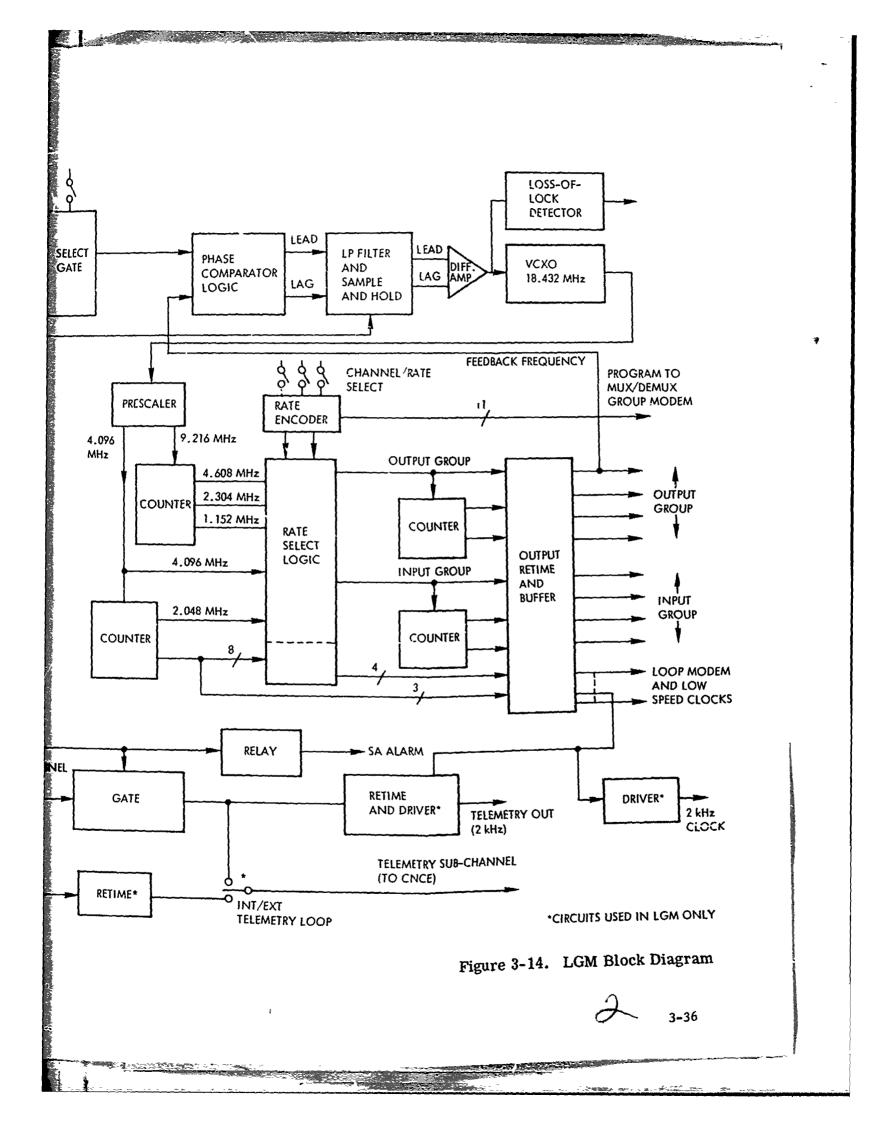

|                   | 3-14   | LGM Block Diagram                                  | 3-36   |

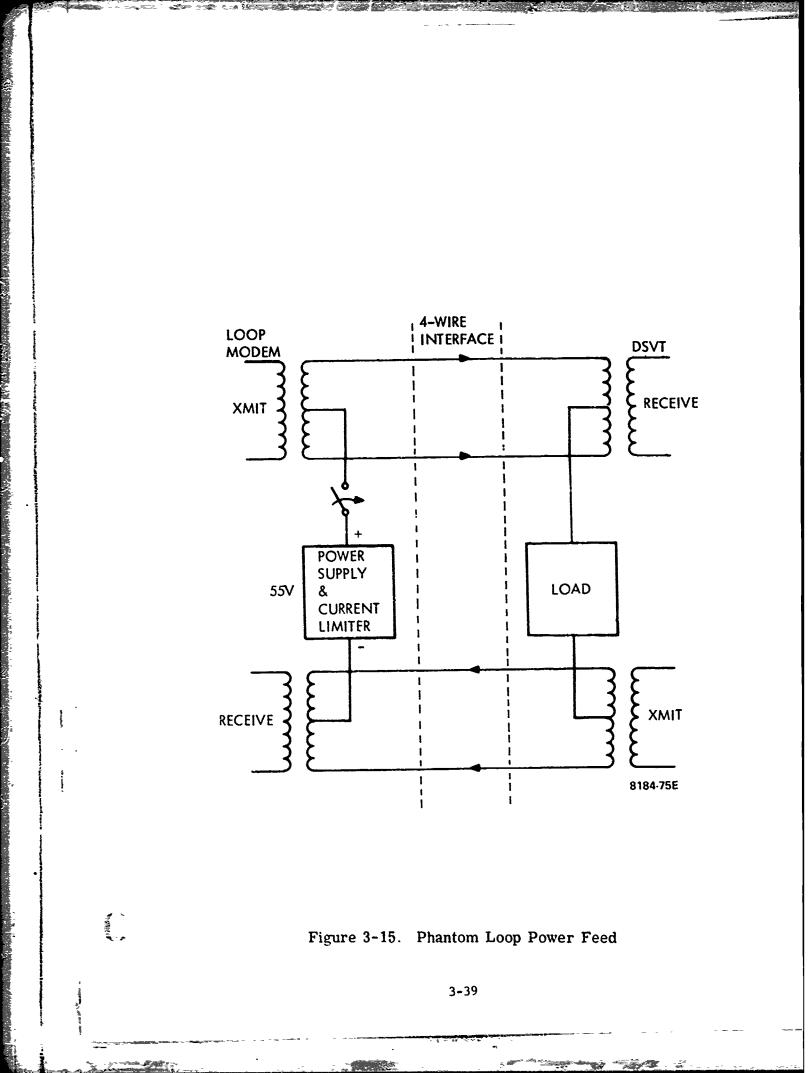

|                   | 3-15   | Phantom Loop Power Feed                            | 3-39   |

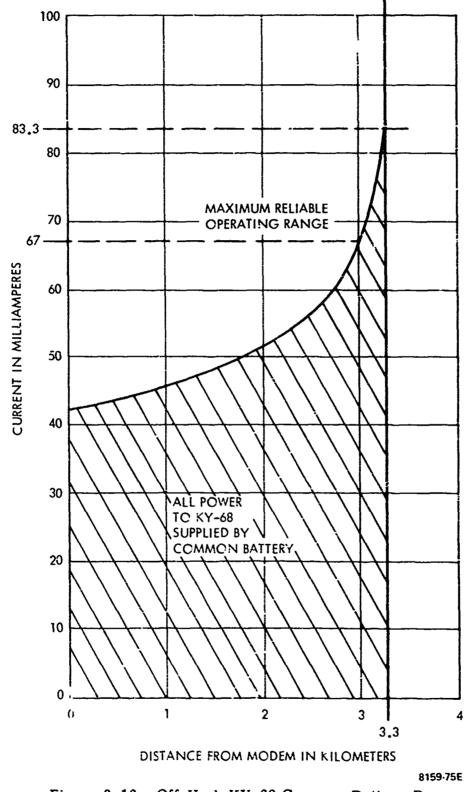

|                   | 3-16   | Off-Hook KY-68 Common Battery Power                | 3-40   |

|                   | 3-17   | Loop Modem Modulator Section                       | 3-41   |

|                   | 3-18   | Generation of Conditioned Diphase Data             | 3-42   |

|                   | 3-19   | Loop Modem Demodulator Section                     | 3-44   |

|                   | 3-20   | Interface Card Block Diagram                       | 3-47   |

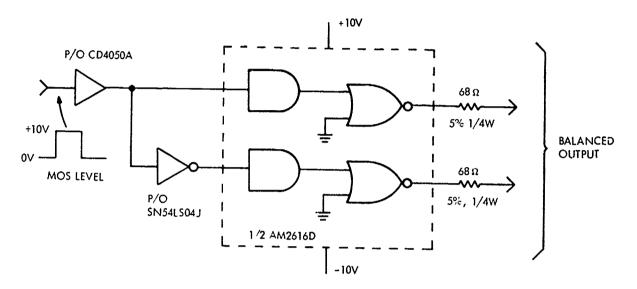

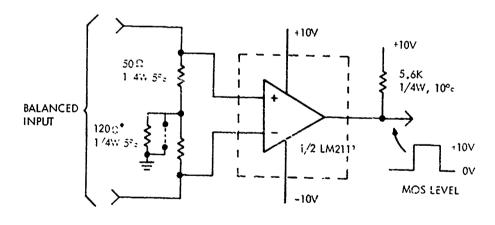

|                   | 3-21   | Balanced Interface Circuit                         | 3-48   |

|                   | 3-22   | Interface Circuit                                  | 3-51   |

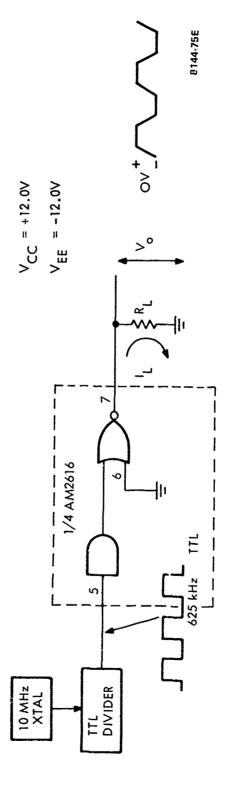

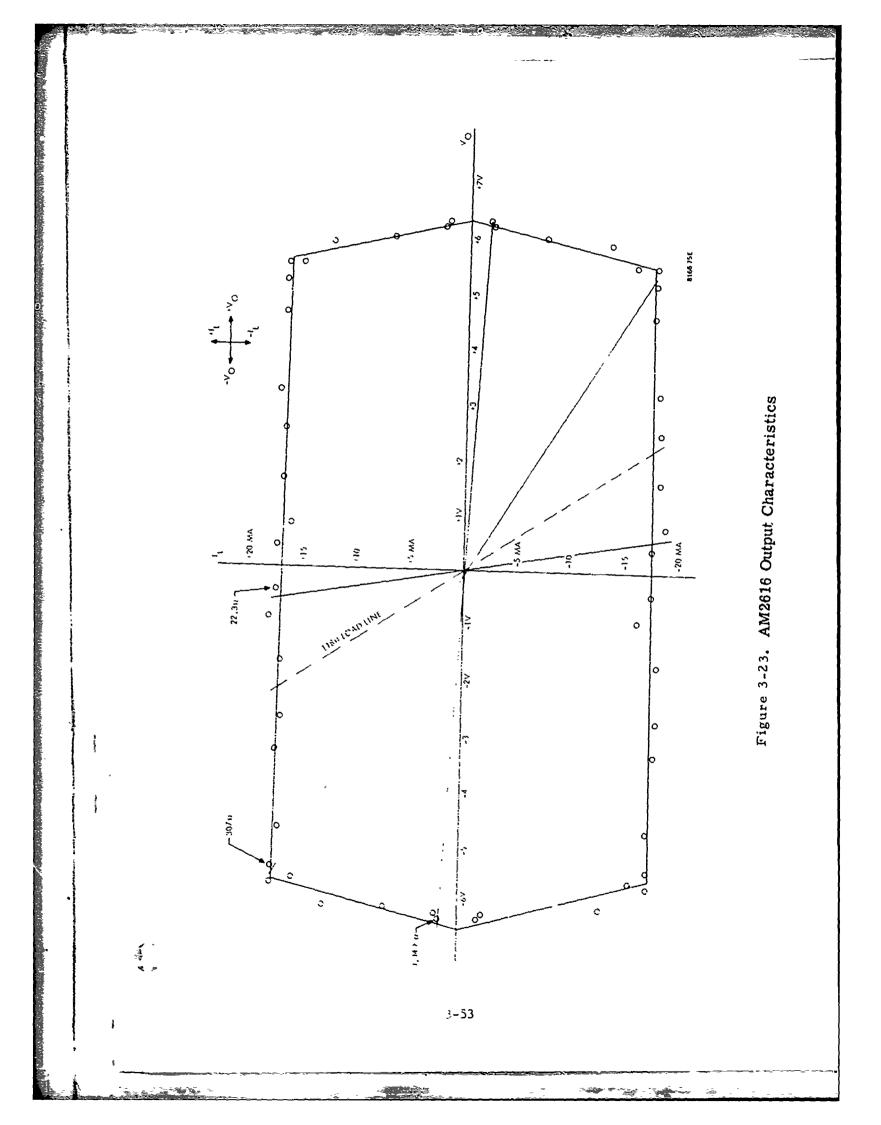

|                   | 3-23   | AM2616 Output Characteristics                      | 3-53   |

v

-e <u>-</u>

, solitor 🖌

ŝ

- 1<sup>0</sup>-10

· .

# LIST OF ILLUSTRATIONS (Cont.)

| Figure |                                                                | Page |

|--------|----------------------------------------------------------------|------|

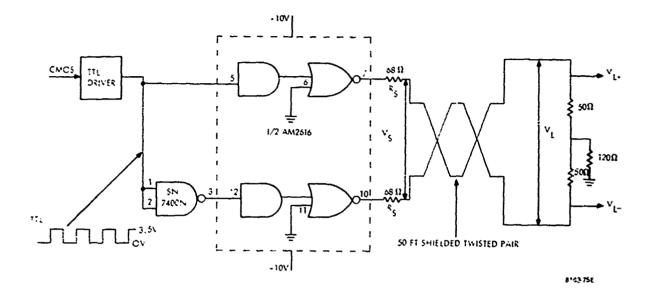

| 3-24   | Driver Circuit Employing AM2616                                | 3-54 |

| 3-25   | AM1500 Receiver Circuit                                        | 3-55 |

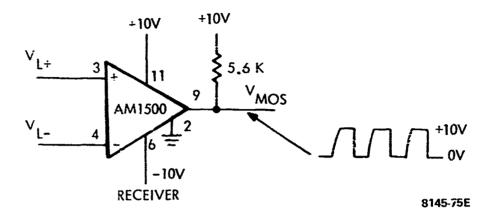

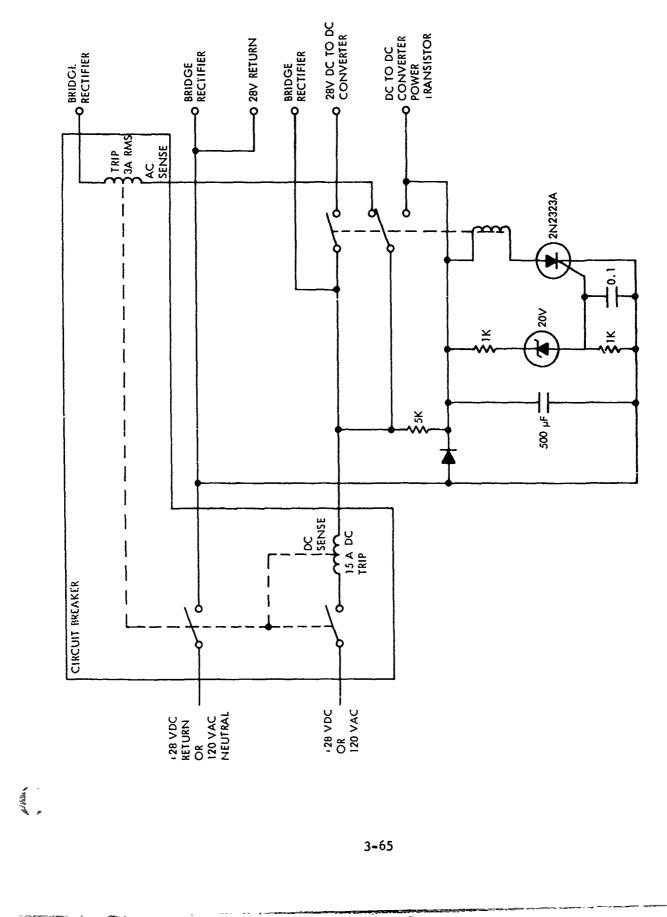

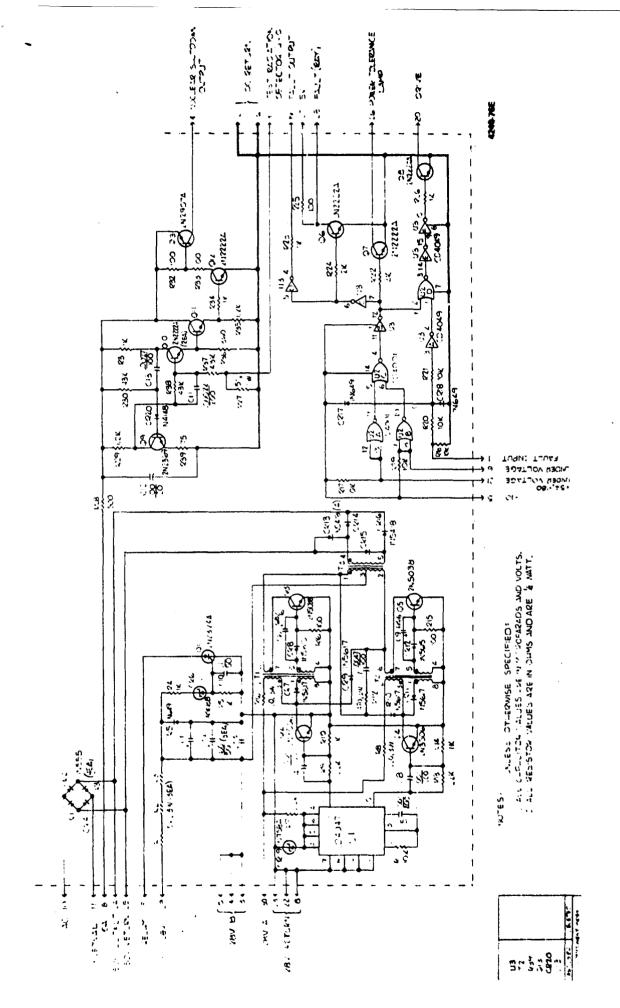

| 3-26   | Flyback Converter                                              | 3-62 |

| 3-27   | LGM Power Supply Block Diagram                                 | 3-64 |

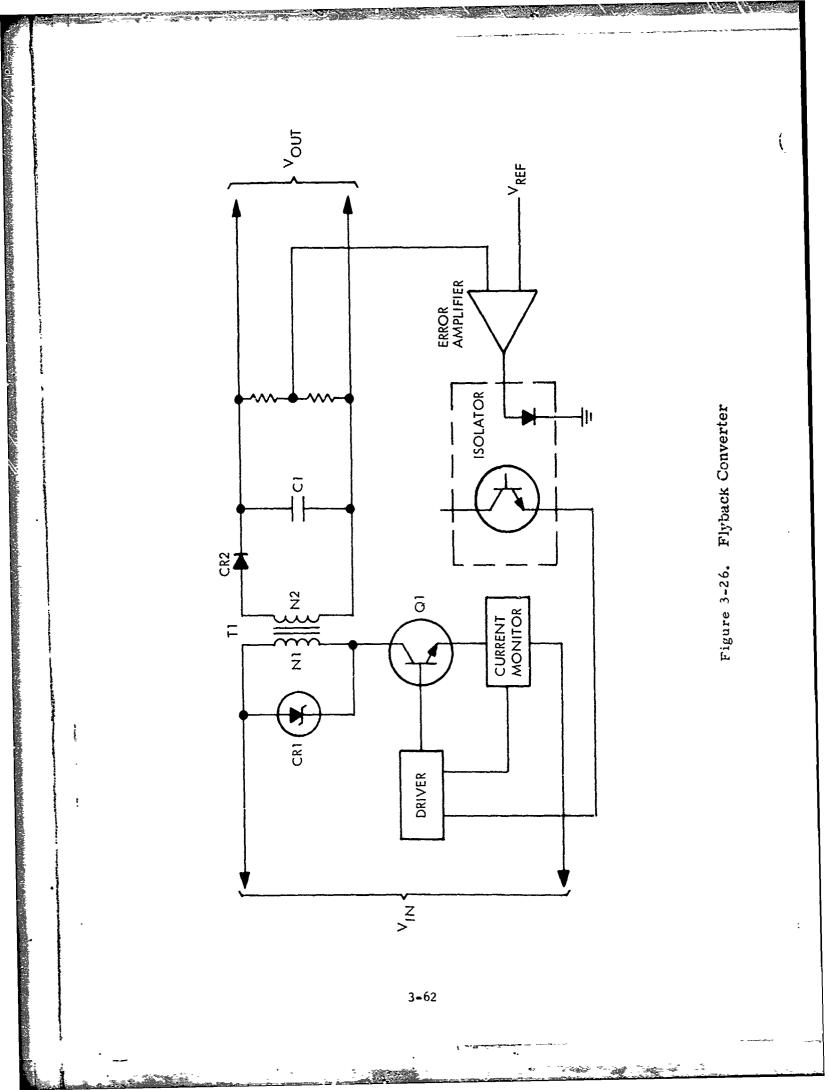

| 3-28   | Prime Power Detector and Circuit Breaker Diagram               | 3-65 |

| 3-29   | Power Supply, Module C                                         | 3-67 |

| 3-30   | Power Supply, Module 'B''                                      | 3-69 |

| 3-31   | Power Supply, Module "A"                                       | 3-70 |

| 3-32   | Power Supply, Module 'H''                                      | 3-72 |

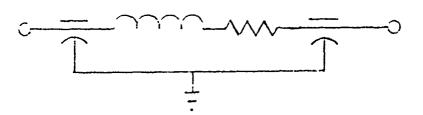

| 3-33   | Filter Pin-Amphenol 482-22                                     | 3-78 |

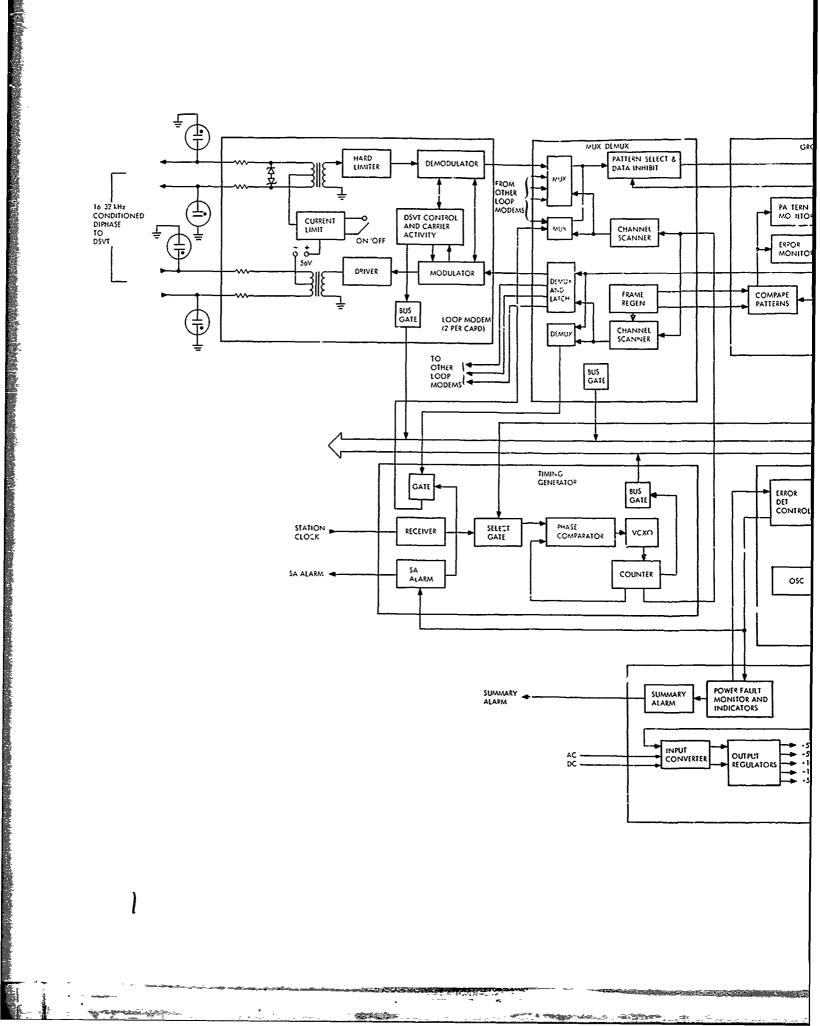

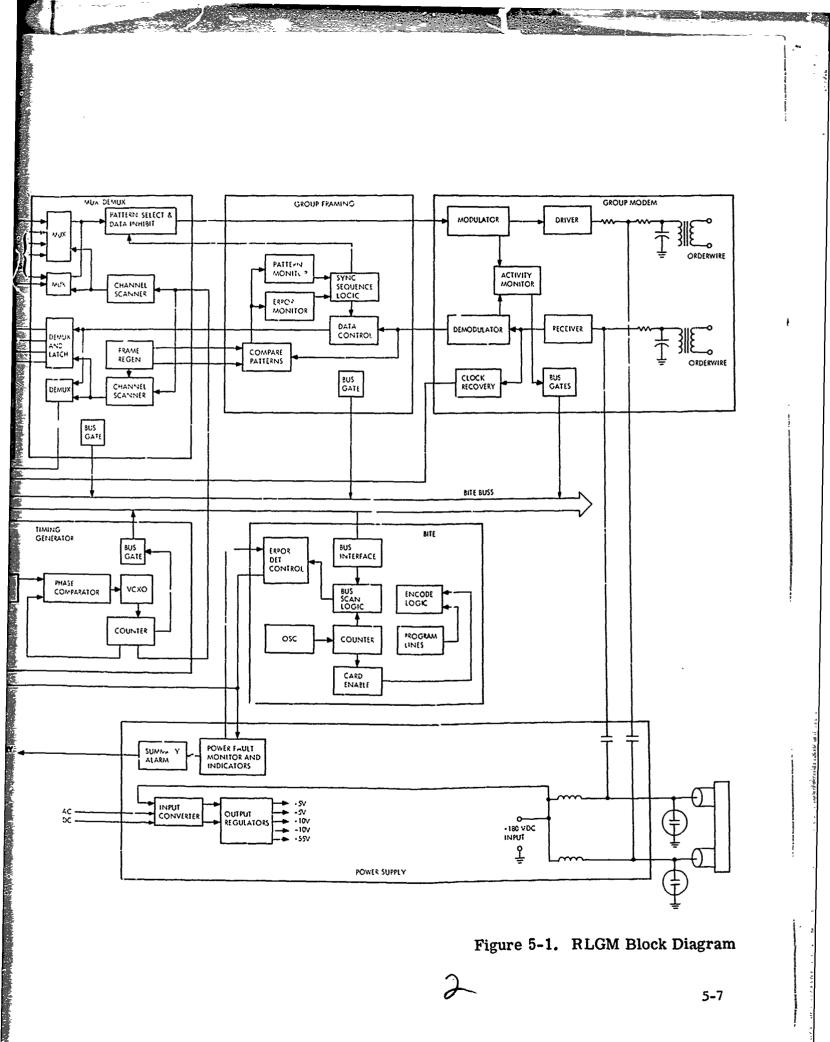

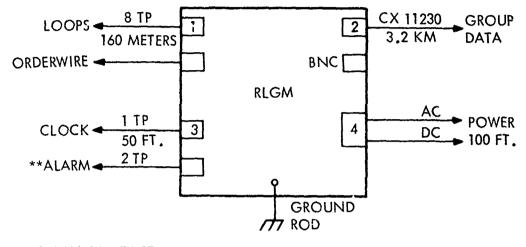

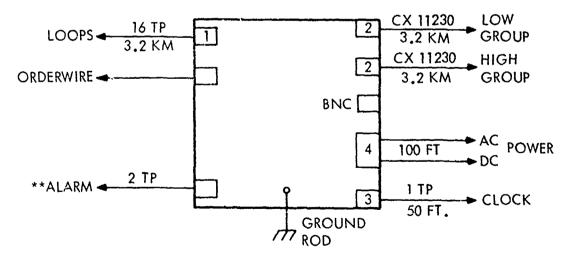

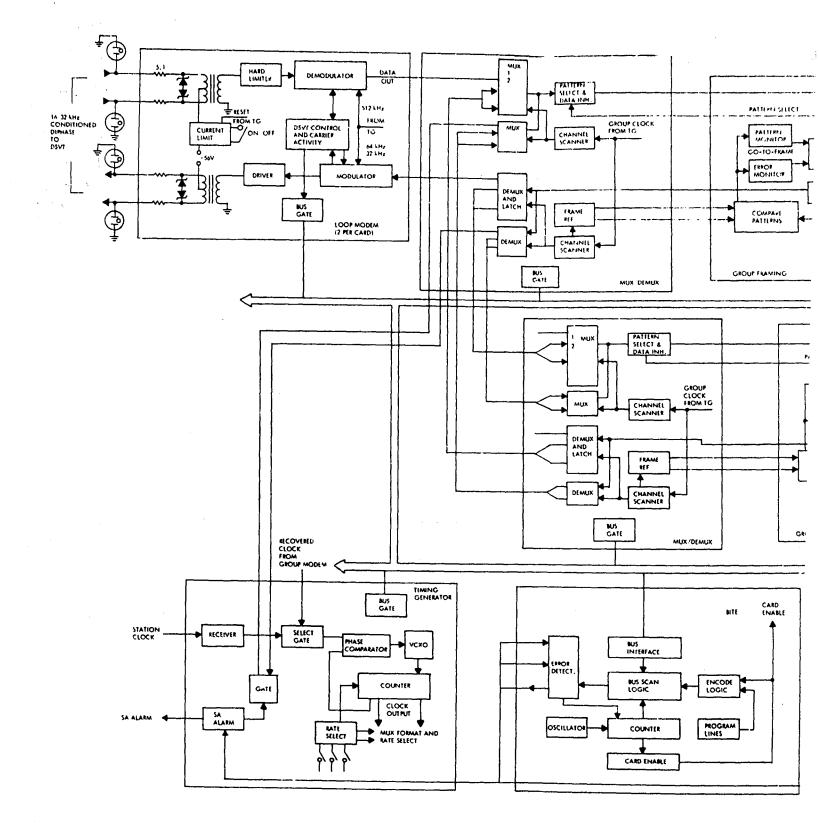

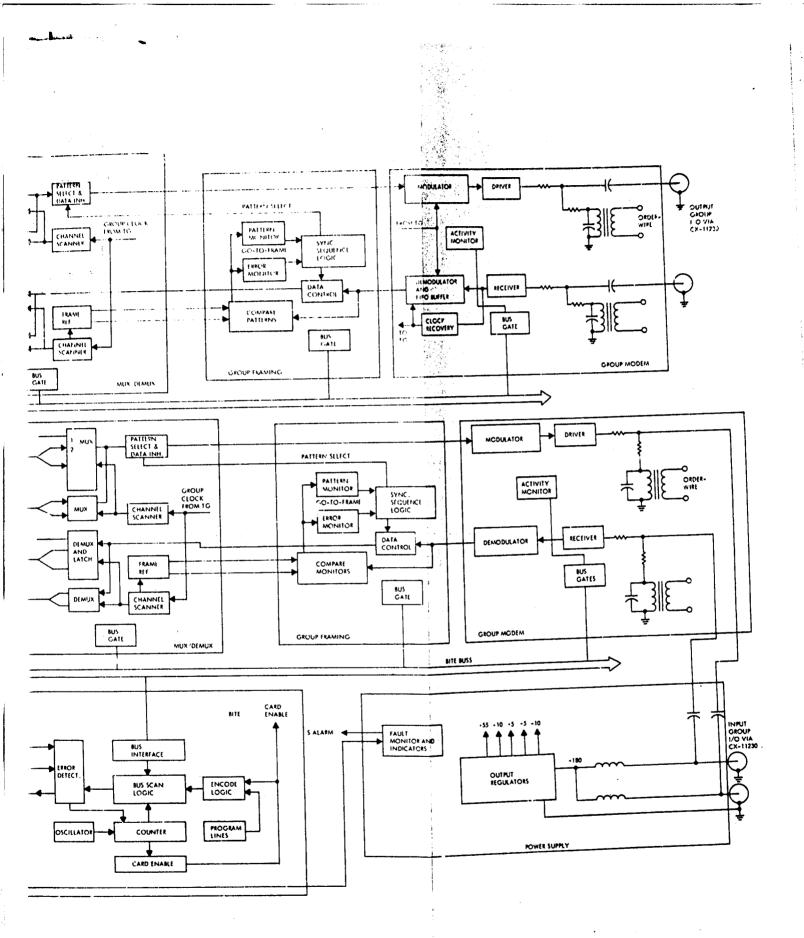

| 5-1    | RLGM Block Diagram                                             | 5-7  |

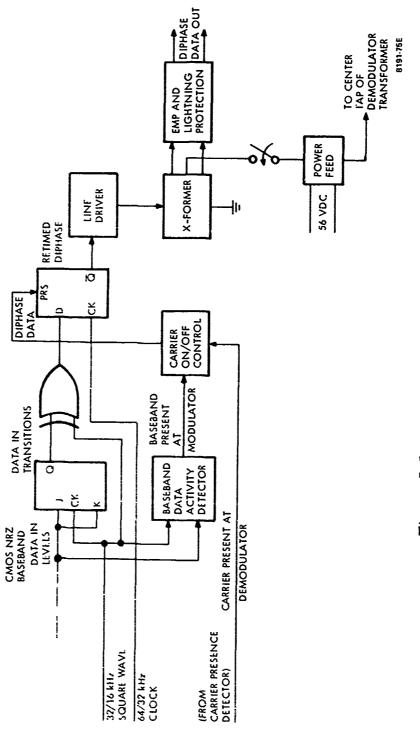

| 5-2    | Loop Modem Modulator Section                                   | 5-13 |

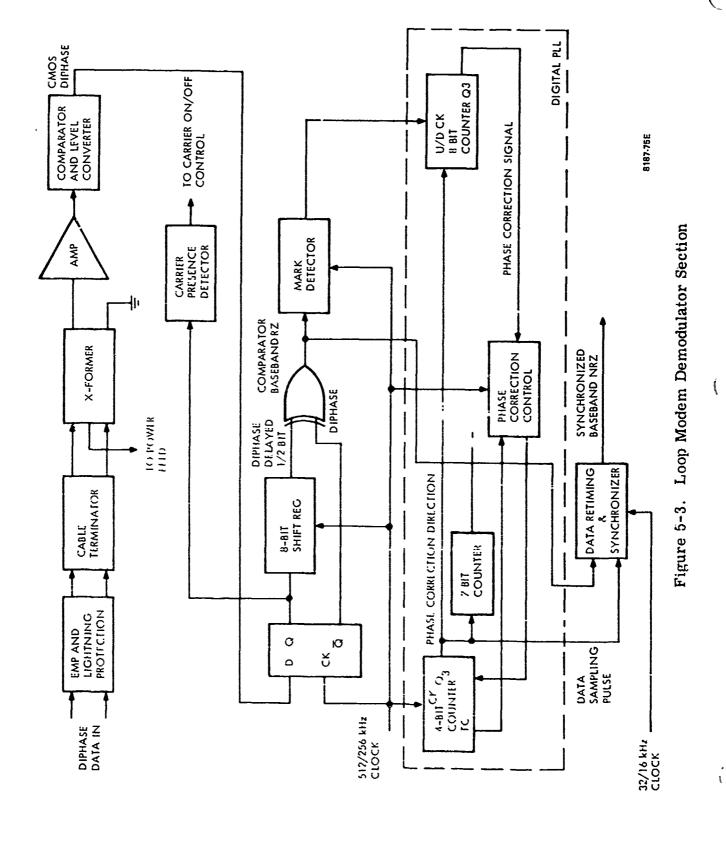

| 5-3    | Loop Modem Demodulator Section                                 | 5-14 |

| 5-4    | RLGM Output Format                                             | 5-15 |

| 5-5    | Overhead Channel Format                                        | 5-15 |

| 5-6    | Framing Block Diagram                                          | 5-17 |

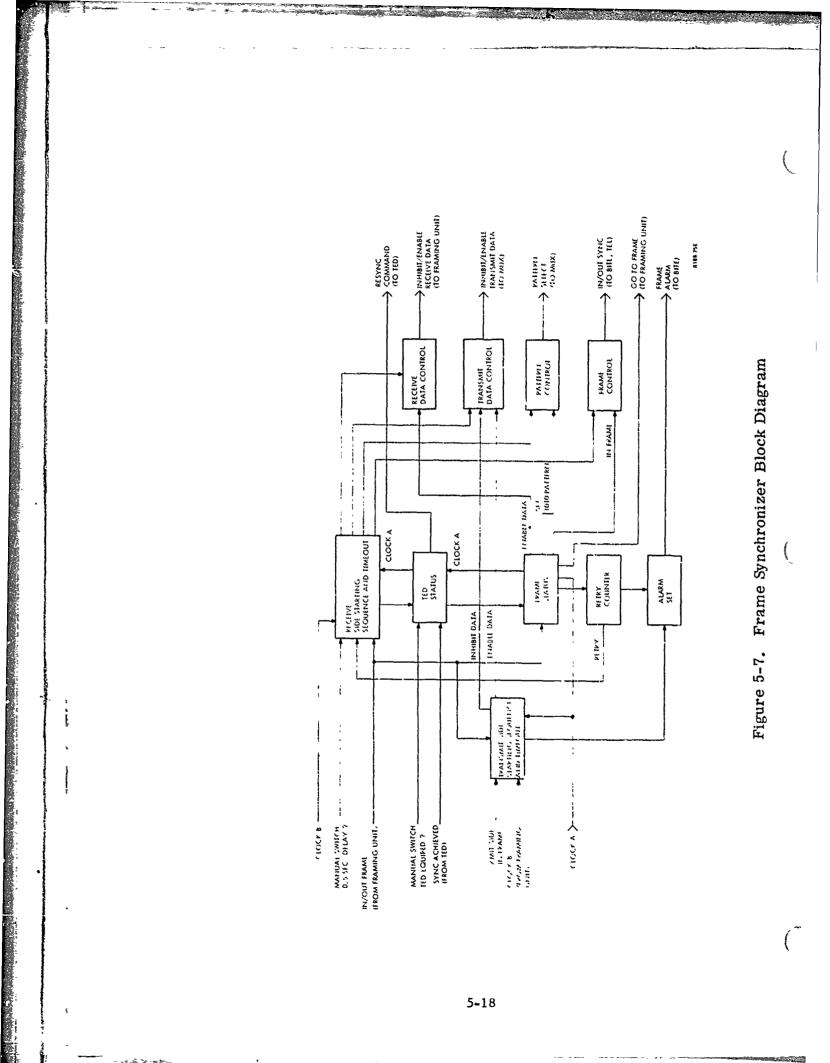

| 5-7    | Frame Synchronizer Block Diagram                               | 5-18 |

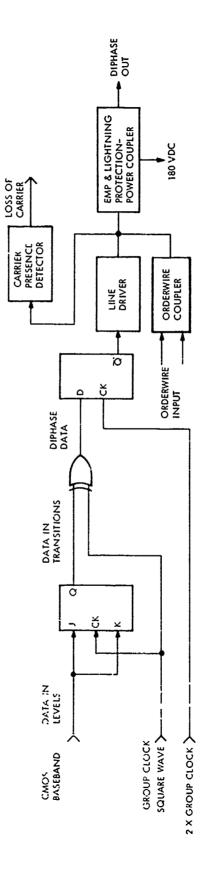

| 5-8    | Group Modem Modulator Section                                  | 5-20 |

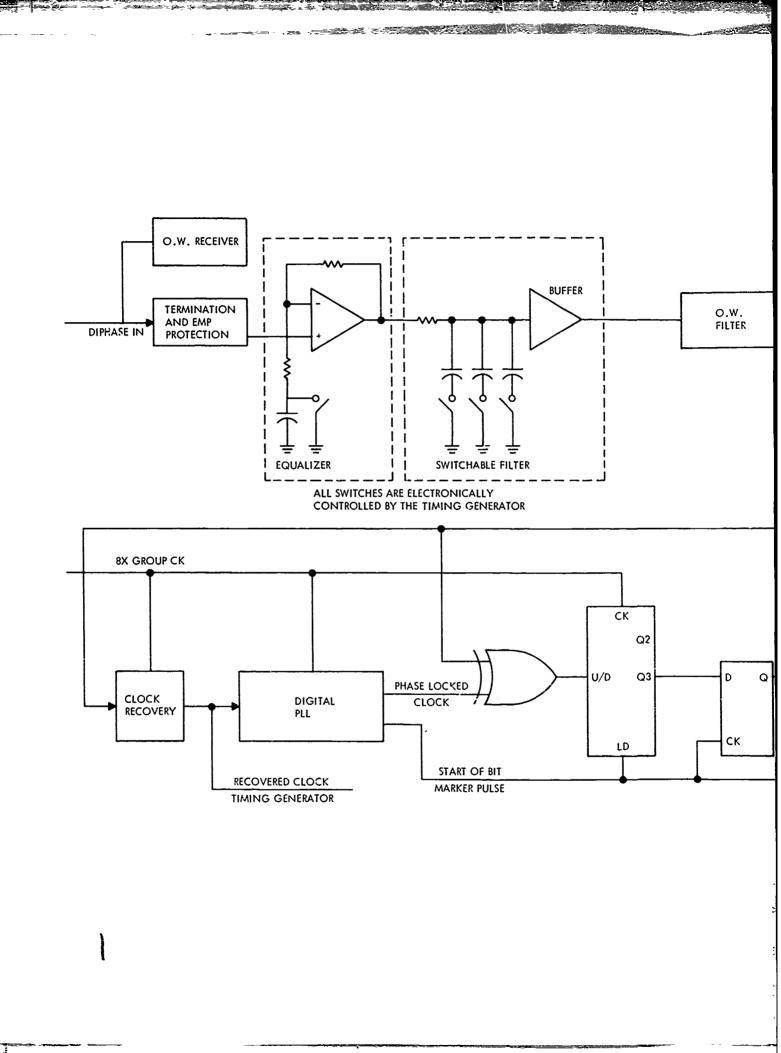

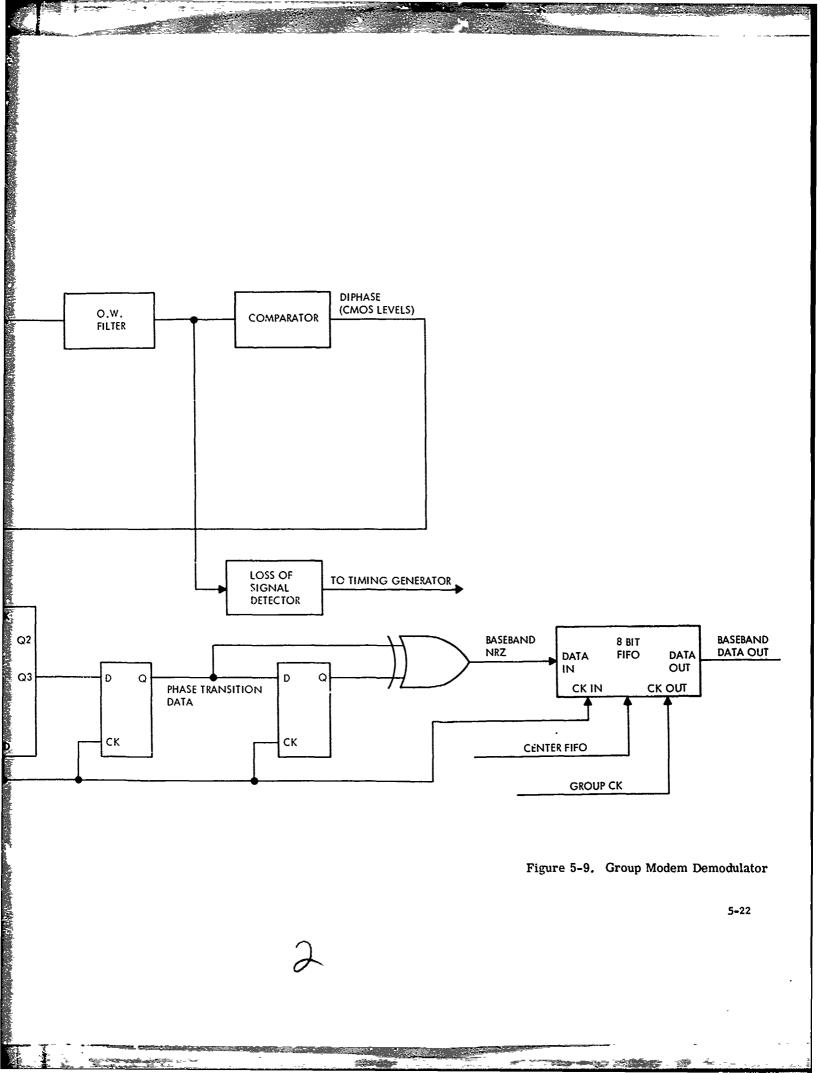

| 5-9    | Group Modem Demodulator                                        | 5-22 |

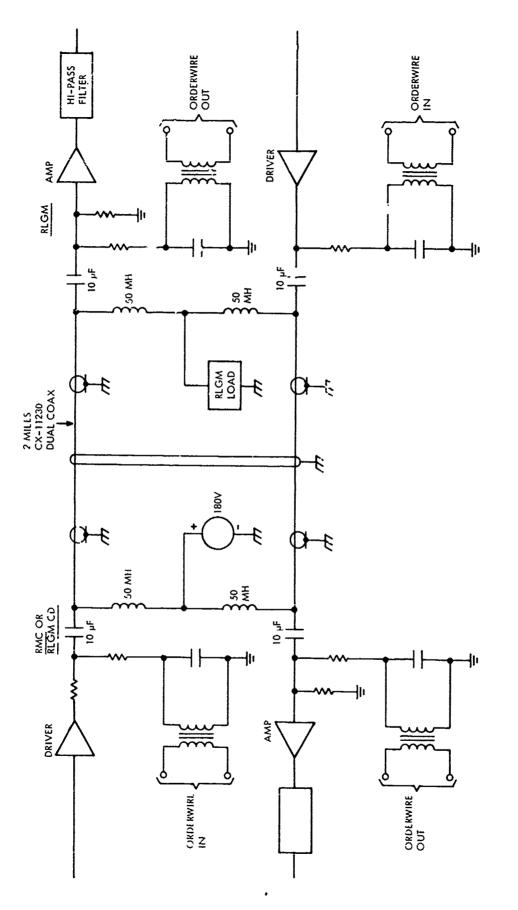

| 5-10   | Power Feed and Orderwire Circuits for RLGM and RMC Group Modem | 5-24 |

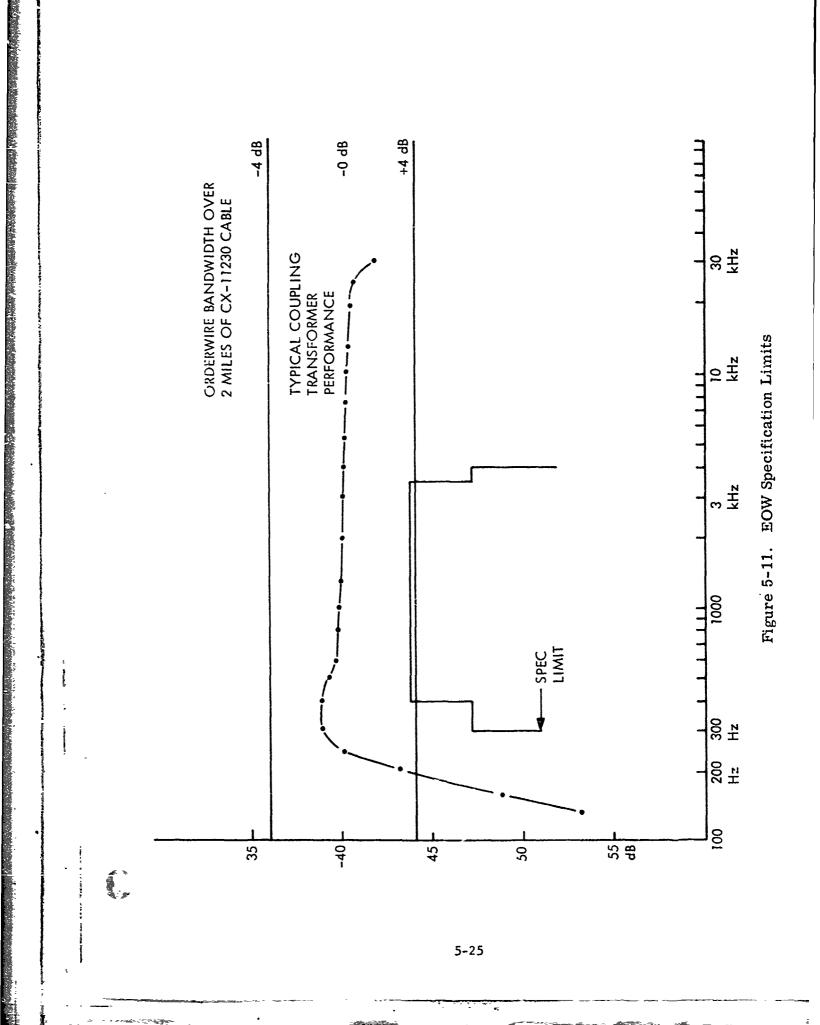

| 5-11   | EOW Specification Limits                                       | 5-25 |

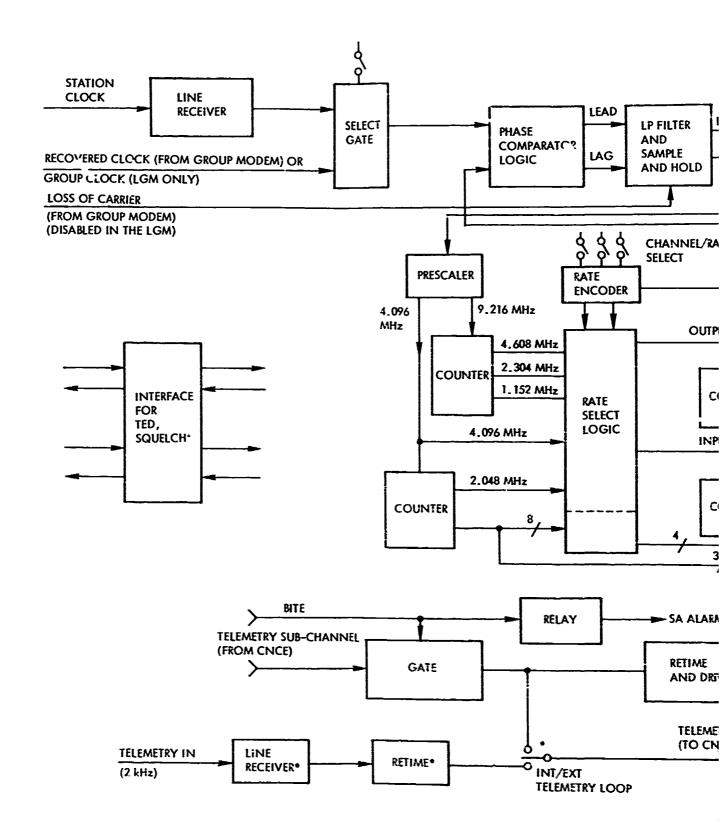

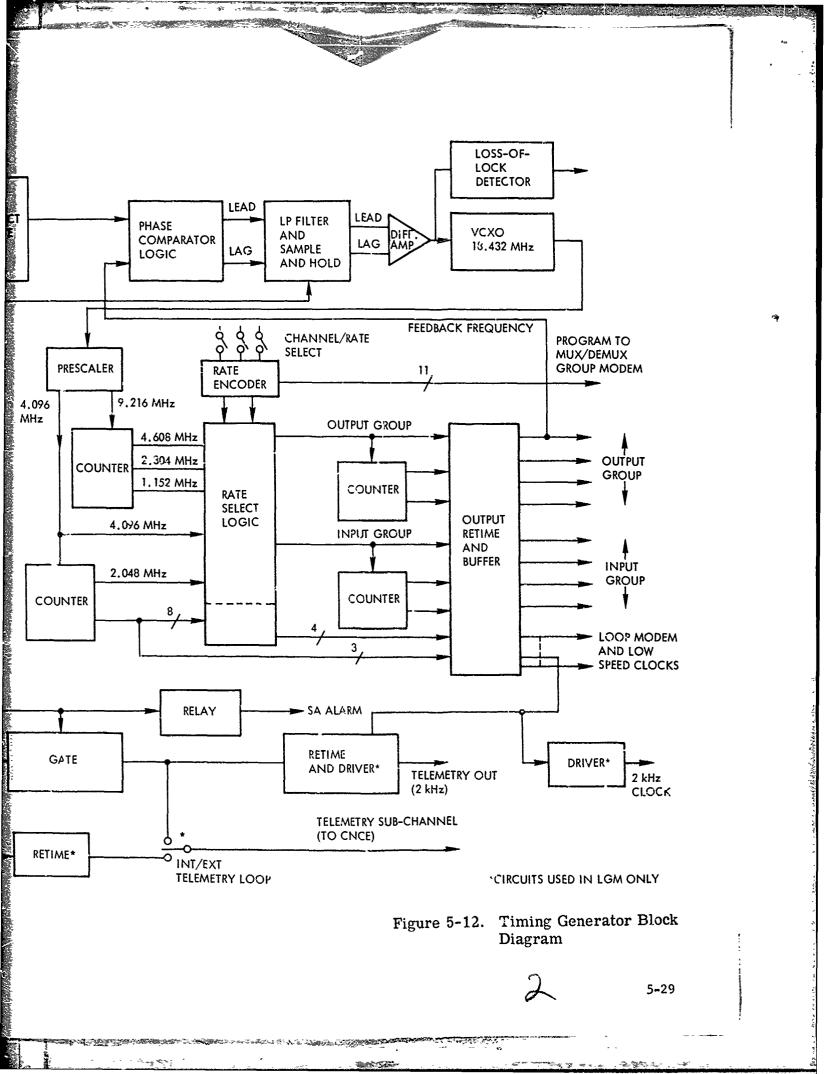

| 5-12   | Timing Generator Block Diagram                                 | 5-29 |

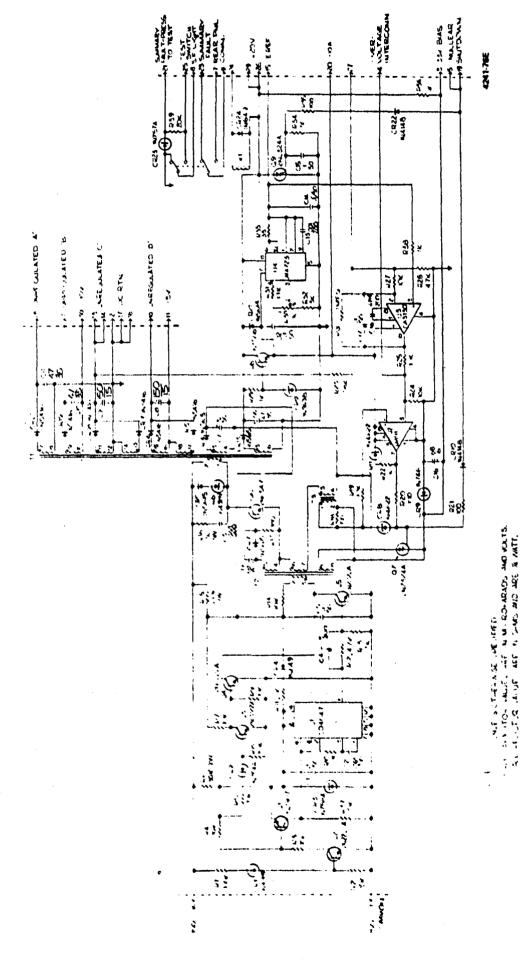

| 5-13   | Block Diagram of BITE Card                                     | 5-30 |

| 5-14   | LGM Alarm Implementation Block Diagram                         | 5-39 |

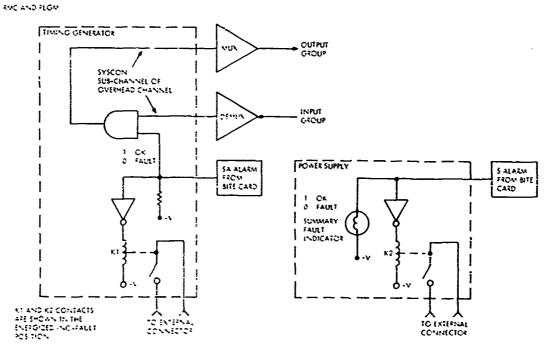

| 5-15   | RMC Alarm Implementation Block Diagram                         | 5-39 |

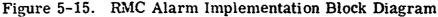

| 5-16   | RGLM Power Supply Block Diagram                                | 5-43 |

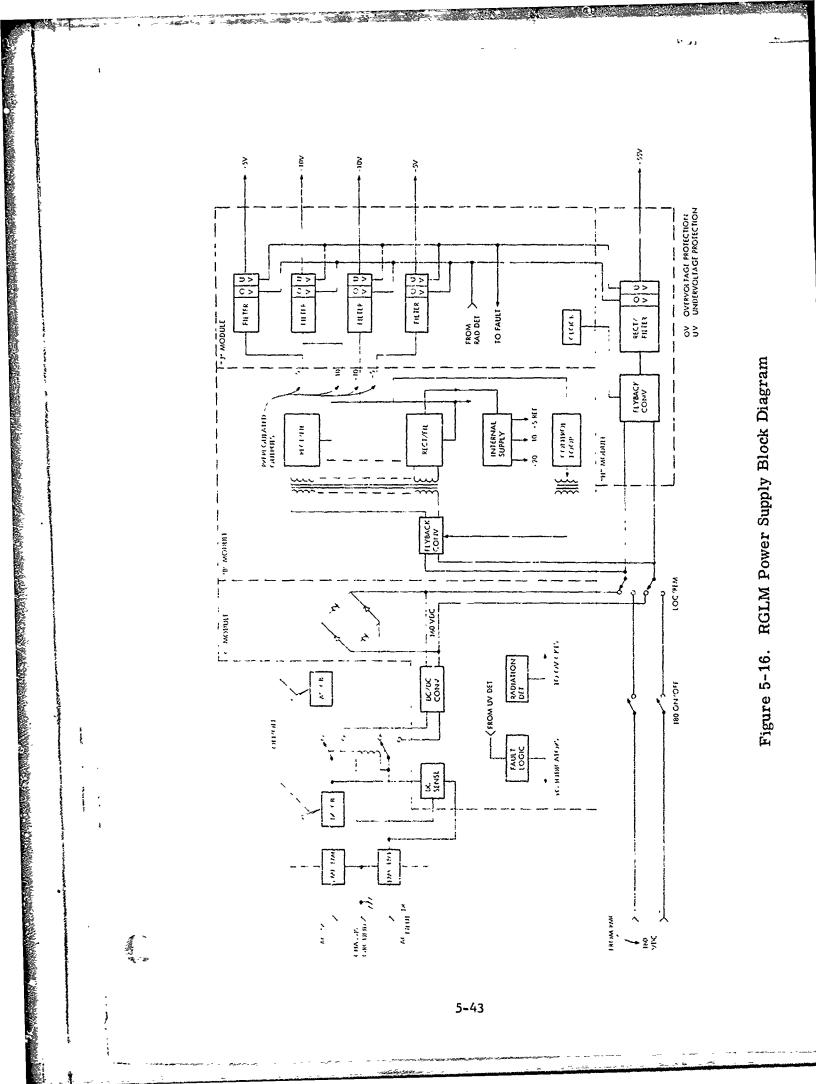

| 5-17   | Power Supply - Module "J"                                      | 5-46 |

vi

2ès -

# LIST OF ILLUSTRATIONS (Cont.)

警(27)?

|            | Figure |                                                                  | Page |

|------------|--------|------------------------------------------------------------------|------|

|            | 5-18   | Remote Loop Croup Multiplexer and Remote<br>Multiplexer Combiner | 5-48 |

|            | 5-19   | Receiver Diphase and Transmitter Diphase Loops                   | 5-50 |

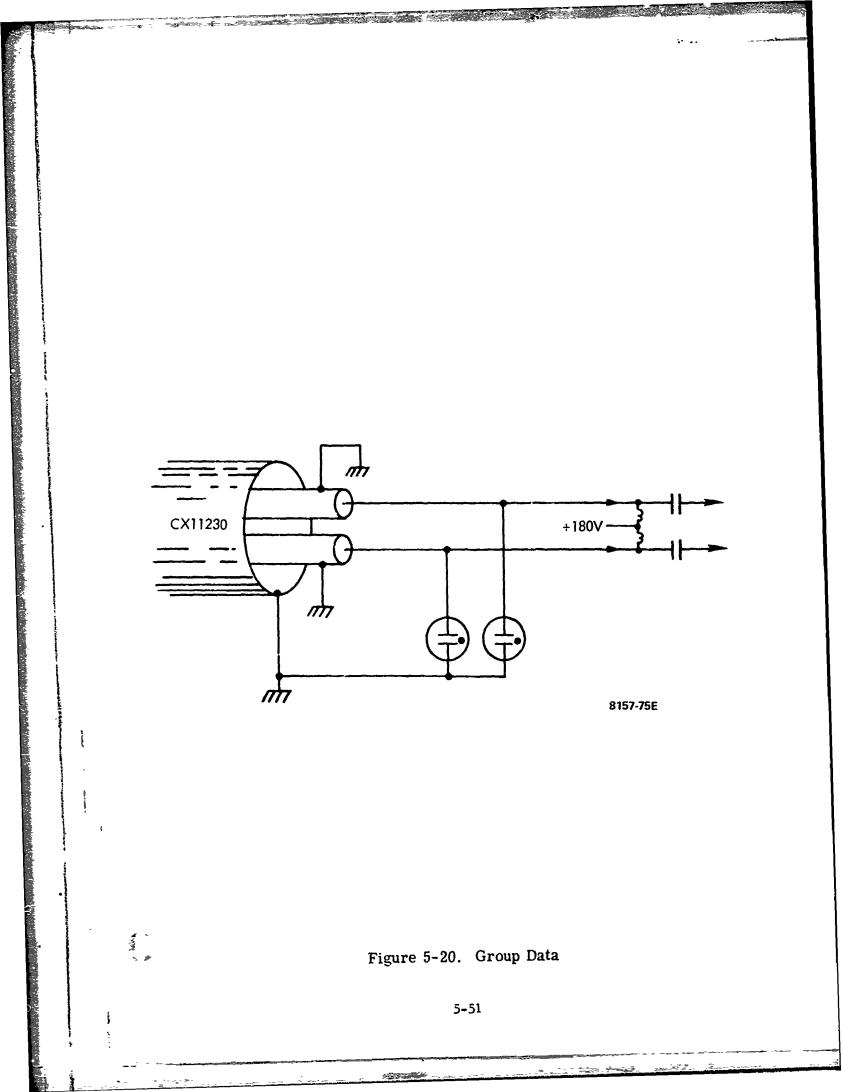

|            | 5-20   | Group Data                                                       | 5-51 |

|            | 7-1    | RMC Block Diagram                                                | 7-7  |

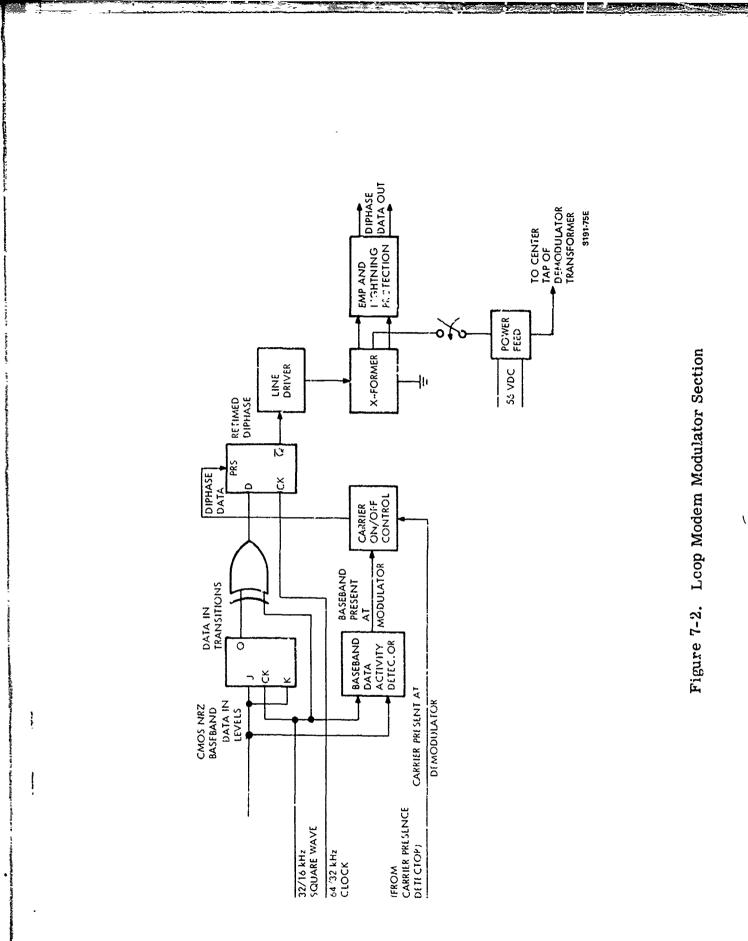

|            | 7-2    | Loop Modem Modulator Section                                     | 7-14 |

|            | 7-3    | Loop Modem Demodulator Section                                   | 7-15 |

|            | 7-4    | RMC Formats                                                      | 7-16 |

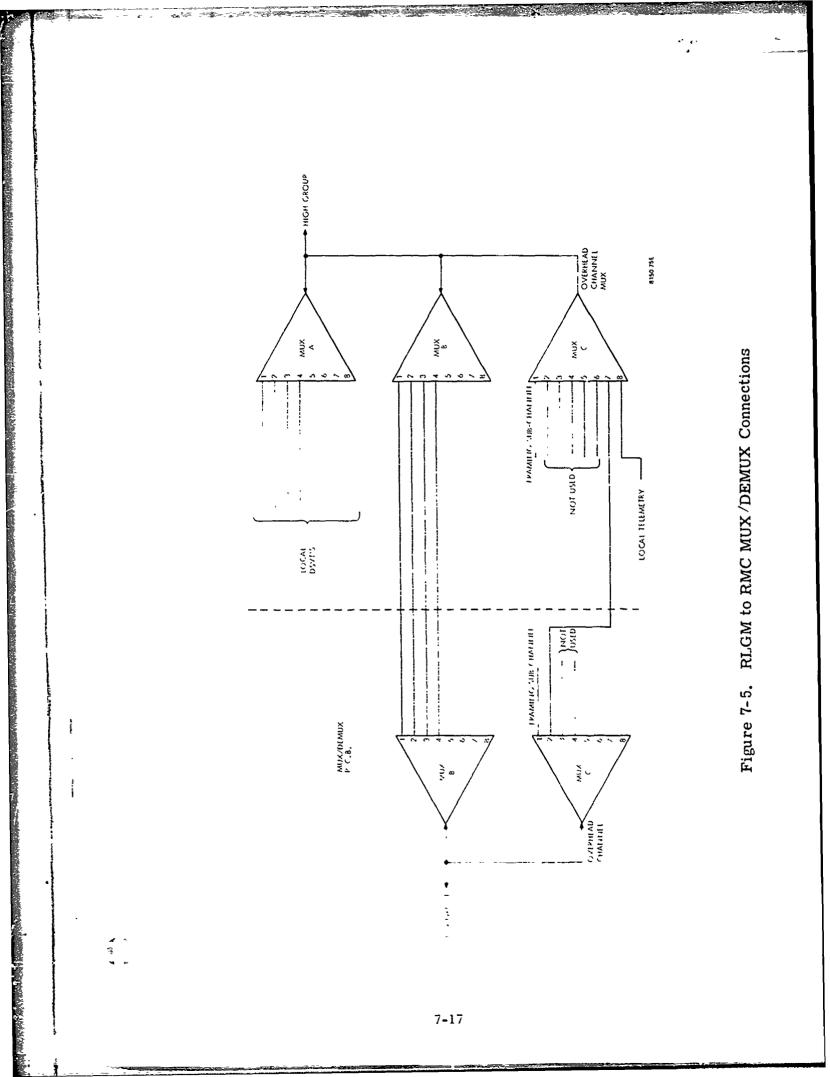

|            | 7-5    | RLGM to RMC MUX/DEMUX Connections                                | 7-17 |

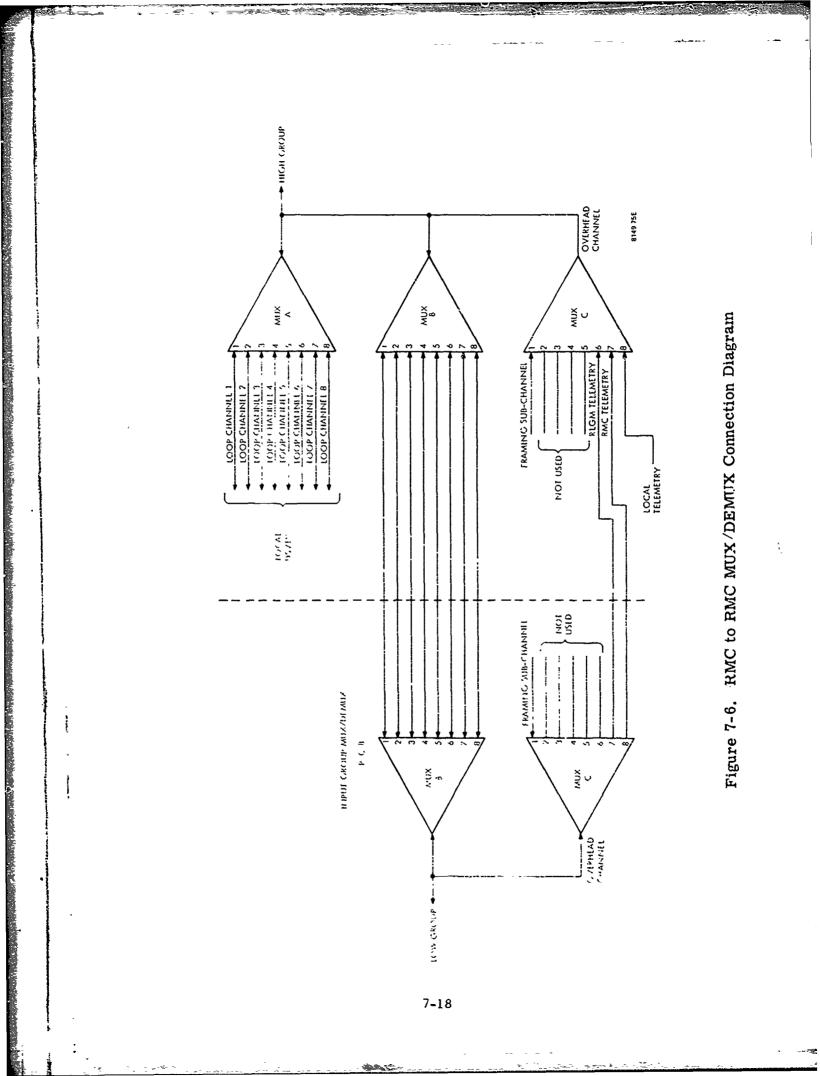

|            | 7-6    | RMC to RMC MUX/DEMUX Connections Diagram                         | 7-18 |

|            | 7-7    | RMC Output Configurations                                        | 7-19 |

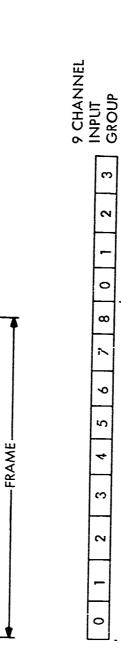

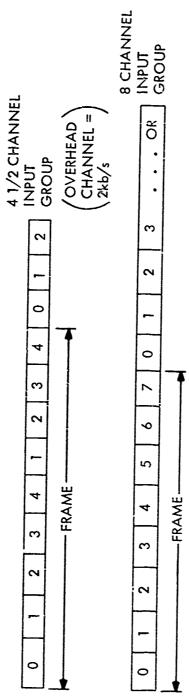

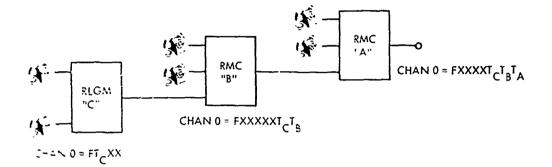

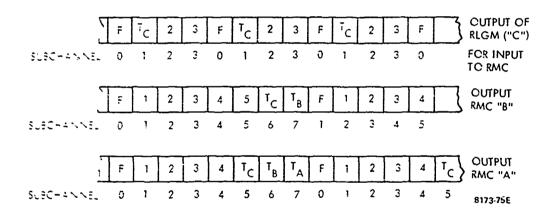

| (Trafferer | 7-8    | Input Group Formats                                              | 7-21 |

| • -        | 7-9    | RMC Overhead Channel Formats                                     | 7-22 |

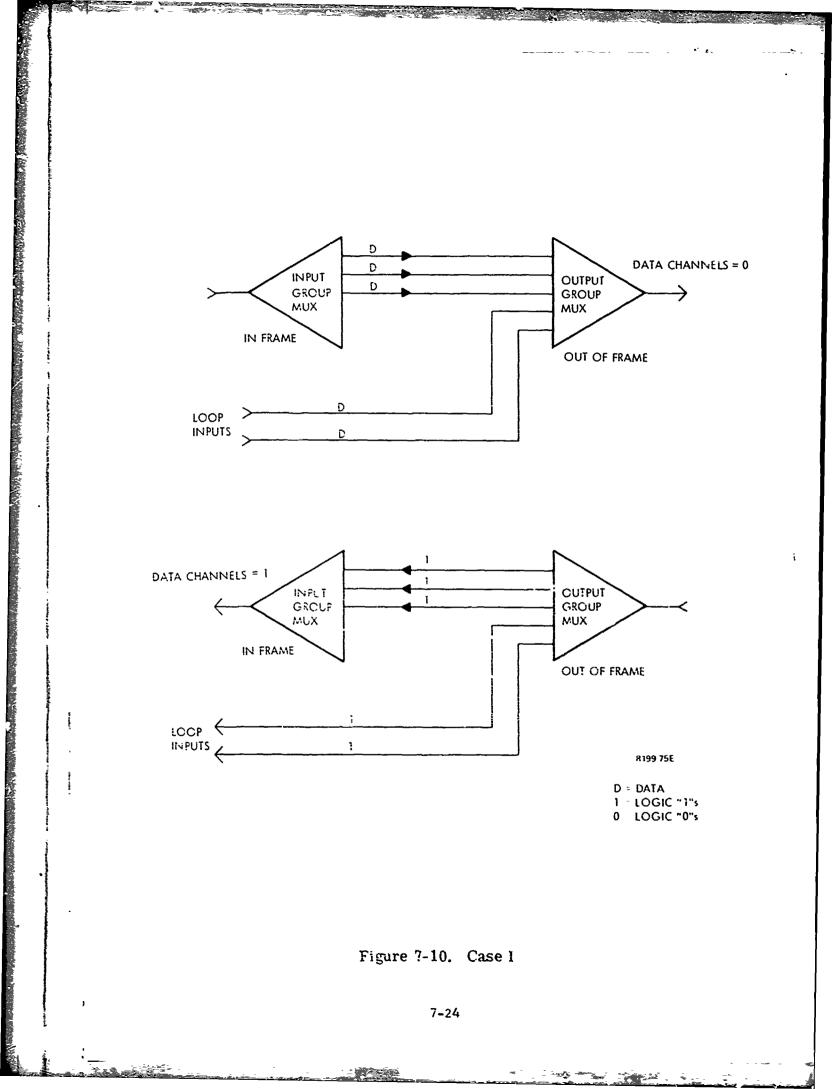

|            | 7-10   | Case I                                                           | 7-24 |

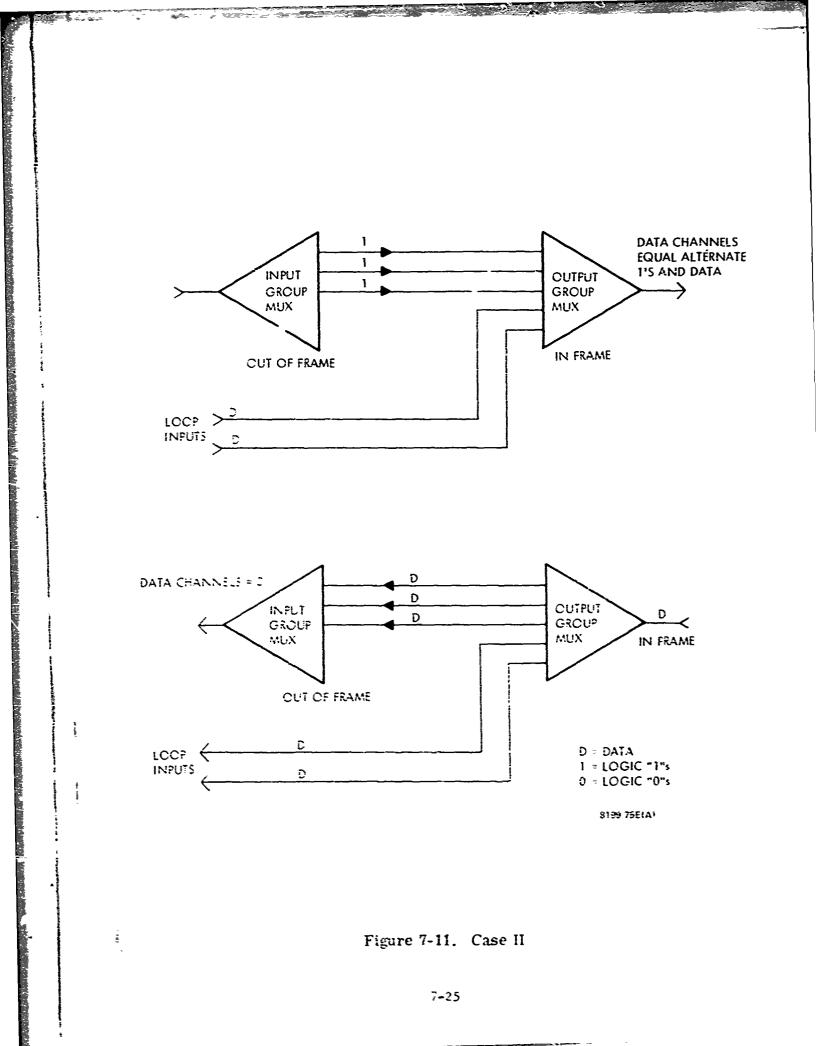

|            | 7-11   | Case II                                                          | 7-25 |

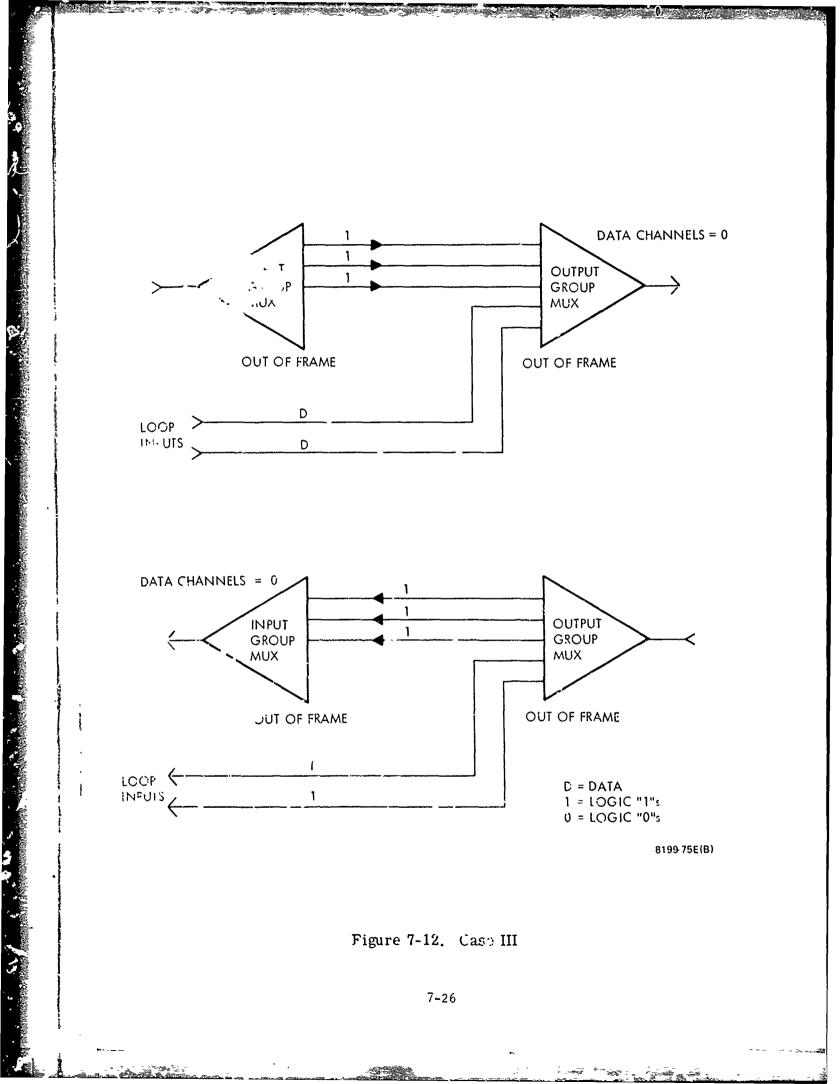

|            | 7-12   | Case III                                                         | 7-26 |

|            | 7-13   | Framing Block Diagram                                            | 7-28 |

|            | 7-14   | Frame Synchronizer Block Diagram                                 | 7-29 |

|            | 7-15   | Group Modem Modulator Section                                    | 7-30 |

|            | 7-16   | Group Modem Demodulator                                          | 7-32 |

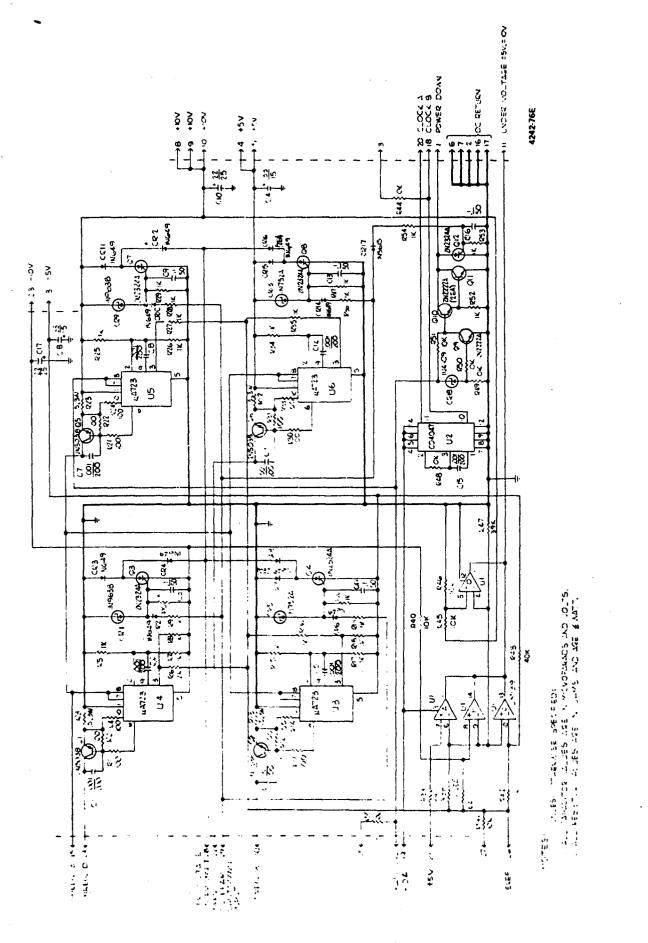

|            | 7-17   | RMC Clock and Timing Circuitry                                   | 7-33 |

|            | 7-18   | Timing Generator Phase-Locked-Loop                               | 7-36 |

|            | 7-19   | RMC Power Supply Block Diagram                                   | 7-40 |

|            | 7-20   | Power Supply - Module D                                          | 7-43 |

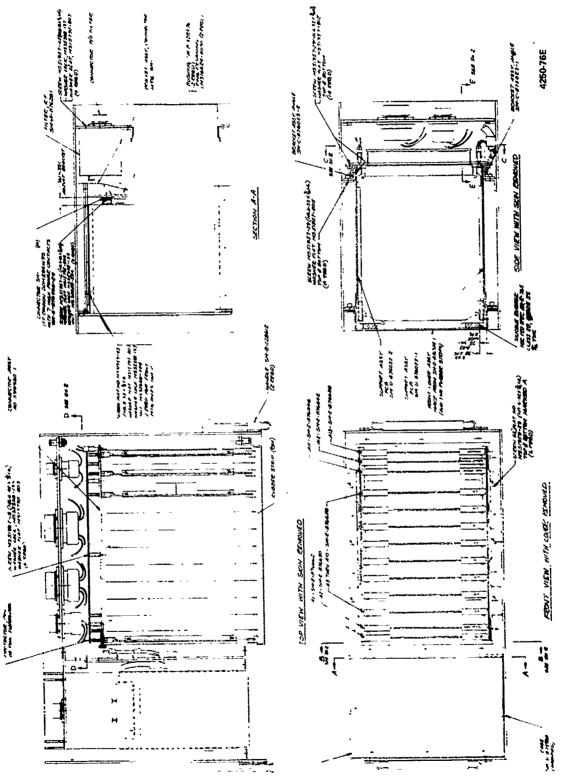

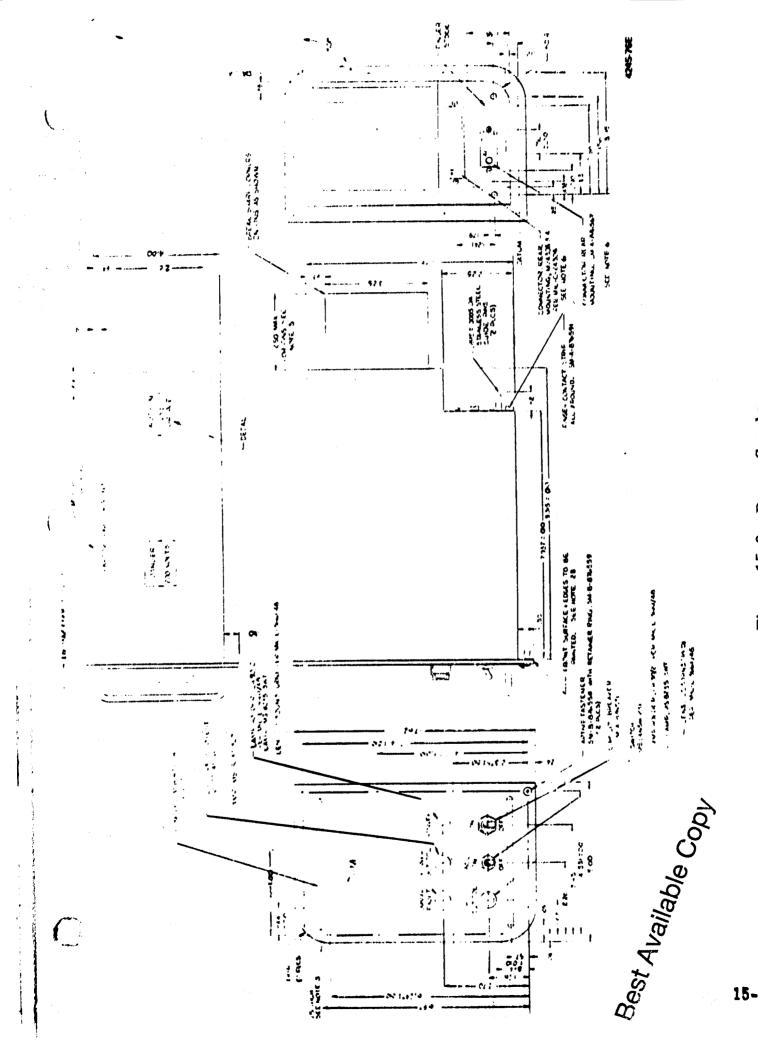

|            | 15-1   | Loop Group Modem (LGM)                                           | 15-2 |

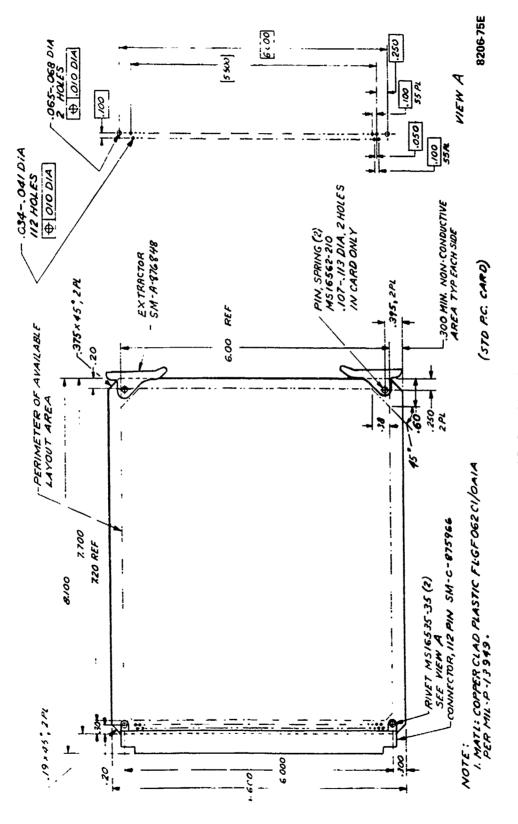

|            | 15-2   | Standard Panel                                                   | 15-4 |

, на**к** 16

vii

2

> 9400.-,a∰.,

# LIST OF ILLUSTRATIONS (Cont.)

| Figure |                                                                    | Page  |

|--------|--------------------------------------------------------------------|-------|

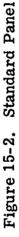

| 15-3   | Shielding Effectiveness vs. Screw Spacing<br>(Frequency = 200 MHz) | 15-16 |

| 15-4   | Power Supply - LGM                                                 | 15-18 |

| 15-5   | Remote Multiplexer Combiner                                        | 15-21 |

| 15-6   | Remote Loop Group Multiplexer                                      | 15-22 |

| 15-7   | Equipment Case                                                     | 15-23 |

| 15-8   | Standard Panel                                                     | 15-25 |

| 15-9   | Power Supply                                                       | 15-39 |

t and

(

# LIST OF TABLES

Science.

| Table |                                                                | Page  |

|-------|----------------------------------------------------------------|-------|

| 3-1   | Functional Requirements - Loop Group Multiplexer (LGM)         | 3-3   |

| 3-2   | LGM Interface Specification Summary                            | 3-8   |

| 3-3   | Number of Channels per Group                                   | 3-12  |

| 3-4   | Framing Unit Interface                                         | 3-24  |

| 3-5   | Interface Levels to Synchronizer                               | 3-35  |

| 3-6   | Timing Generator Outputs                                       | 3-37  |

| 3-7   | NRZ Balanced Interfaces by Circuit Card                        | 3-49  |

| 3-8   | NRZ Balanced Interfaces by Equipment                           | 3-50  |

| 3-9   | R <sub>L</sub> Positive and Negative Peak Values               | 3-52  |

| 3-10  | AM2616 and LM2111D Features                                    | 3-56  |

| 3-11  | GTE Sylvania Power Supply P.C.B. Complement                    | 3-58  |

| 3-12  | Major Performance Requirements of Power Supply                 | 3-59  |

| 3-13  | LGM Reliability                                                | 3- 73 |

| 5-1   | Multiplexer (RLGM) ر Functional Requirements - Remot           | 5-3   |

| 5-2   | RLGM Interface Specification Summa y                           | 5-10  |

| 5-3   | Timing Generator Outputs                                       | 5-27  |

| 5-4   | Timing Generator Bus Assignment                                | 5-31  |

| 5-5   | Group Modem Bus Assignment                                     | 5-32  |

| 5-6   | Loop Modem Bus Assignment                                      | 5-33  |

| 5-7   | MUX DEMUX Bus Assignment                                       | 5-34  |

| 5-8   | Group Framing Bus Assignment                                   | 5-35  |

| 5-9   | Interface Card Bus Assignment                                  | 5-36  |

| 5-10  | Order in Which the P.C. Cards are Scanned                      | 5-40  |

| 5-11  | RLGM Reliability                                               | 5-53  |

| 7-1   | Functional Requirements - Remote Multiplexer<br>Combiner (RMC) | 7-3   |

| 7-2   | RMC Interface Specification Summary                            | 7-10  |

| 7-3   | Timing Generator Outputs                                       | 7-31  |

| 7-4   | Timing Generator Decoder Outputs                               | 7-34  |

ix

<u> (\* 187</u>

- *a*ć

# LIST OF TABLES (Cont.)

| Table |                                                      | Page  |

|-------|------------------------------------------------------|-------|

| 7-5   | RMC Reliability                                      | 7-45  |

| 15-1  | LGM Weights                                          | 15-5  |

| 15-2  | Power Dissipation                                    | 15-6  |

| 15-3  | Worst Case Thermal Analysis Results                  | 15-7  |

| 15-4  | LGM Power Supply Assemblies and Allocations          | 15-19 |

| 15-5  | RLGM and RMC Weights                                 | 15-26 |

| 15-6  | Power Dissipations                                   | 15-28 |

| 15-7  | Worst Case Thermal Analysis Results                  | 15-29 |

| 15-8  | Environmental Design Requirements                    | 15-31 |

| 15-9  | RMC and RLGM Power Supply Assemblies and Allocations | 15-40 |

# SECTION 3 LGM

The Loop Group Multiplexer (LGM) is used in tactical communications shelters and vans. Its primary function is the time division multiplexing of up to sixteen (16) conditioned diphase loops into a loop group and the time division demultiplexing of a digital group into its constituent channels. One channel of the loop group is allocated for overhead (non-traffic) functions, such as the framing pattern and telemetering data for SYSCON. Local access to the overhead channel's SYSCON telemetry subchannel is provided at the LGM.

The conditioned diphase interface at the loopside is provided by a Loop Modem element which operates at a 32 or 16 kb's rates. The Loop Modem elements primary function is to transmit and receive conditioned diphase signals on the cable connecting it to a DSVT or another digital subscriber set which has the same functional and interface requirements of a DSVT. In addition, the Loop Modem element provides DC power to the DS<sup>17</sup>T for common battery operation. Two Loop Modem elements are packaged on a single P.C.B.

The Group Framing and Synchronization element generates and detects the frame synchronization patterns required to maintain link synchronization. Frame sync acquisition is initiated when the out of sync condition is detected. In addition, the Group Framing and Synchronization element commands the Trunk Encryption Device (TED) to resynchronize when required during frame synchronization acquisition when a TED is used.

The group interface provides a full duplex digital group consisting of balanced NRZ data which may be connected to a TED. GM, TGM, MGM or Low Speed CDM.

Generation of the internal timing signals required by the LGM is performed by the Clock and Timing Generator element. The LGM operates on reference timing at the group rate from either an external source or from the received group clock.

The LGM design also includes BITE, for O&M support.

The LGM DC power is obtained from its Power Supply element which operates from AC or DC primary power sources.

#### 3.1 DESIGN GOALS AND REQUIREMENTS

The LGM function requirements are summarized in Table 3-1.

A major design objective in the LGM was directed toward reducing the number of printed circuit boards (P.C.B.'s) required to meet the functional requirements for the LGM and to minimize the input power required.

This objective was of major importance in view of the savings in combining the Loop Modern (LM) unit with the Loop Group Multiplexer (LGM) unit.

To this end, by optimizing the design and partitioning of circuits, a design has been achieved which significantly reduces the P.C.B. card types and thus, permitted the Loop Group Multiplexer (LGM) and the Loop Modem (LM) to be combined into a single unit.

3.2 DESIG. TAPPROACH

3.2.1 Summary

I here are a number of basic design approaches which the subcontractor used throughout the design to optimize commonality with the Raytheon units. Basic design approaches were as follows.

# TABLE 3-1.FUNCTIONAL REQUIREMENTS - LOOP GROUP<br/>MULTIPLEXER (LGM)

Definition: The LGM shall multiplex up to 16 conditioned diphase channels into a single digital time division multiplexed loop group. One of the channels shall be an overhead channel for framing and telemetry. Loop Side Group Side

|                                   | Loop Side                                             |                   | Group Side                                                                                                    |

|-----------------------------------|-------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------|

| Type of Channels:                 | 4 wire full dup                                       | lex               | Same                                                                                                          |

| Number of Channels:               | 7, 8, 15, or 16                                       | 5                 | 8, 9, 16, or 18                                                                                               |

| Bit Rate:                         | 32/16/kb/s                                            |                   | 128, 144, 256 or<br>288 kb/s at 16 kb/s<br>Loop Rate<br>256, 288, 512, or<br>576 kb/s at 32 kb/s<br>Loop Rate |

| Modulation:                       | Conditioned Dip                                       | phase             | NRZ, balanced                                                                                                 |

| Used With:                        | DSVT                                                  |                   | TED or GM                                                                                                     |

| Power Feed:                       | DSVT per TT-                                          | A3-9002-0017      |                                                                                                               |

| Impedance:                        | 125 +10 $\%$ Return<br>26 dB in the ba<br>8 to 56 KHz |                   |                                                                                                               |

| Crypto Interface:                 |                                                       |                   | TED                                                                                                           |

| Timing:                           |                                                       |                   | Station Clock/Receive<br>Group Clock                                                                          |

| Modularity:                       | Loops                                                 | 16 kb/s Loops     | 32 kb/s Loops                                                                                                 |

|                                   | 7<br>8                                                | 128<br>144        | 256<br>288                                                                                                    |

|                                   | 15                                                    | 256               | 512                                                                                                           |

|                                   | 16                                                    | 288               | 576                                                                                                           |

| Overhead Channel<br>Structure:    | Eight subchann<br>is telemetry                        | els, one channe   | l is framing, a second                                                                                        |

| Telemetry Sub-<br>channel Access: | Access shall be<br>subchannel                         | e provided to the | e LGM 2 kb 's telemetry                                                                                       |

| Size:                             | 8.5"H x 12"D                                          | x 19" - Rack M    | lount                                                                                                         |

| Input Power:                      | 190 watts maxis                                       | mum               |                                                                                                               |

| Type of Power:                    | 115 VAC ±10%                                          | 50 to 400 Hz      |                                                                                                               |

| Weight:                           | 17 KG                                                 |                   |                                                                                                               |

| BITE:                             | Power Monitor<br>Failure                              | /Fault Isolation  | Loss of Sync Channel                                                                                          |

| Reliability:                      | 3.000 HR-MTB                                          | F                 |                                                                                                               |

i

Ì,

-\*\*\*\*\*\*\*\* 3-3

-

----

\*\*\*\*\*\*

1

- a. The extensive use of C-MOS devices. An extensive trade off study was performed on the use of Low Power Schottky devices versus C-MOS. The results of this study showed that, on the average, a five to one power savings could be achieved by using C-MOS. This significant power savings was achievable since the speeds at which most of the circuits operated were below 1 MHz. Low Power Schottky devices are used when operating at higher frequencies.

- b. Common printed circuit boards are used in the field and shelter units. Since these are identical function; i.e., framing and synchronization, to be performed in both the shelter and field units, identical cards are used to perform these common functions. Variations in specific requirements; i.e., group output rates, MUX/DEMUX sequences are selectable by toggle switches mounted to the P.C.B.'s. Back plane wiring is used to insure that illegal sequences cannot be selected when a common card is placed in a unit.

- c. Minimized the design of the loop modem circuit so that two loop modems were packaged on a single P.C.B.

- d. Designed the Power Supply so that common circuit designs are used in the field and shelter units.

- e. Designed the loop modem P. C. B. 's so that they are completely interchangeable with the loop modem P. C. B. 's used in the field units.

- f. Designed a Clock and Timing P.C.B. which is interchangeable with the Clock and Timing P.C.B.'s located in the RMC and RLGM units.

- g. Mechanical design approaches are discussed in Paragraph 15.4 of this volume.

#### 3.2.2 Detailed Electrical Design for the LGM

A detailed block diagram of the LGM is shown in Figure 3-1. The LGM time division multiplexes up to eighteen (18) digital channels into a single digital time division multiplexed loop group. One of the eighteen (18) channels is an overhead channel which transmits framing and SYSCON telemetry data. The LGM contains sixteen (16) conditioned diphase loop modems. Two modems are packaged on a single P.C.B. The loop modems accept baseband digital loop

-

٢.

signals from the MUX/DEMUX P.C.B. and modulate/demodulate the loop data for transmission to digital voice subscriber terminals via telephone (WF-16) cable. The modems also provide phantom loop power over this same cable to power the DSVT operating in a common battery mode. A switch is provided on each loop modem to control the power (on/off) to each DSVT. Second level EMP protection circuits are located on each loop modem.

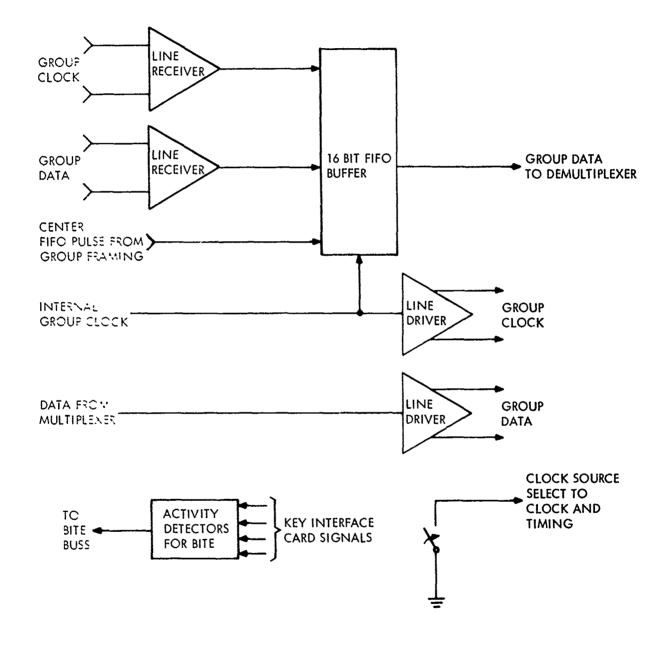

The Loop Modems NRZ baseband data is passed to the MUX/DEMUX card where it is multiplexed with the overhead channel containing the SYSCON subchannel. The resulting bit interlaced data stream is sent to the Group Framing Unit where the data is gated to the output group data interface under control of the Synchronizer section of the Group Framing Unit. The output data stream is buffered and converted to a balanced interface on the interface card before appearing at the external connector interface.

The group data input is converted from a balanced signal to C-MOS (Interface Card) and inputted to  $a \pm 8$  bit FIFO. The re-timed data is then connected to the frame regenerator portion of the Group Framing Unit. The frame regenerator is a counter whose output (frame pattern) is aligned in phase with the incoming frame pattern in the data. The frame reference is used to properly phase the MUX DEMUX circuitry. The demultiplexed data channels are buffered, and applied to each loop via the Loop Modems. A multi-pin connector is used at the rear of the LGM unit for the loop signals.

The Timing Generator locks an internal oscillator to an external station clock which is applied as a balanced line input at the group bit rate. Toggle switches located on the Timing Generator P.C.B. are used to program the proper output clock rate: the switch outputs are also used to program the MUX'DEMUX card.

A switch is also provided on the Timing Generator P.C.B. to provide a loop-back capability for the SYSCON telemetry sub-channel. This sub-channel may be looped back either internally - output of the demultiplexer connected directly to the multiplexer or externally via the SYSCON external connections.

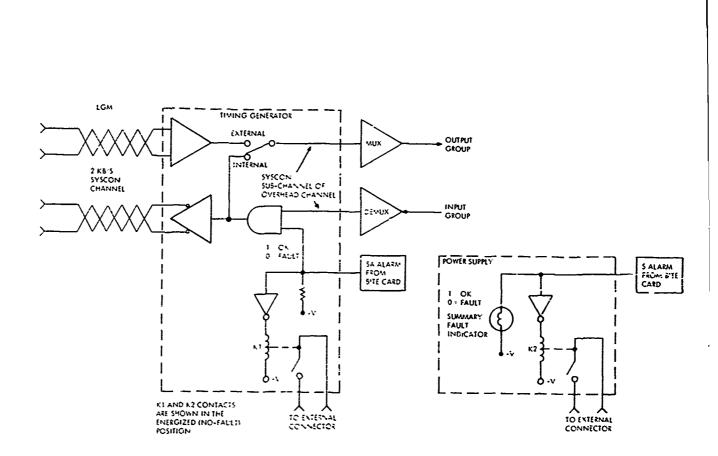

n addition, a summary BITE alarm (SA) will cause ZERO's to be inserted on the receive side of the telemetry subchannel.

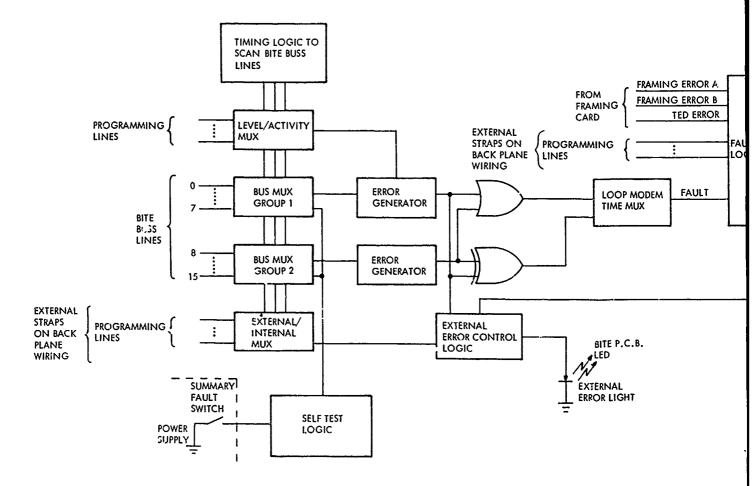

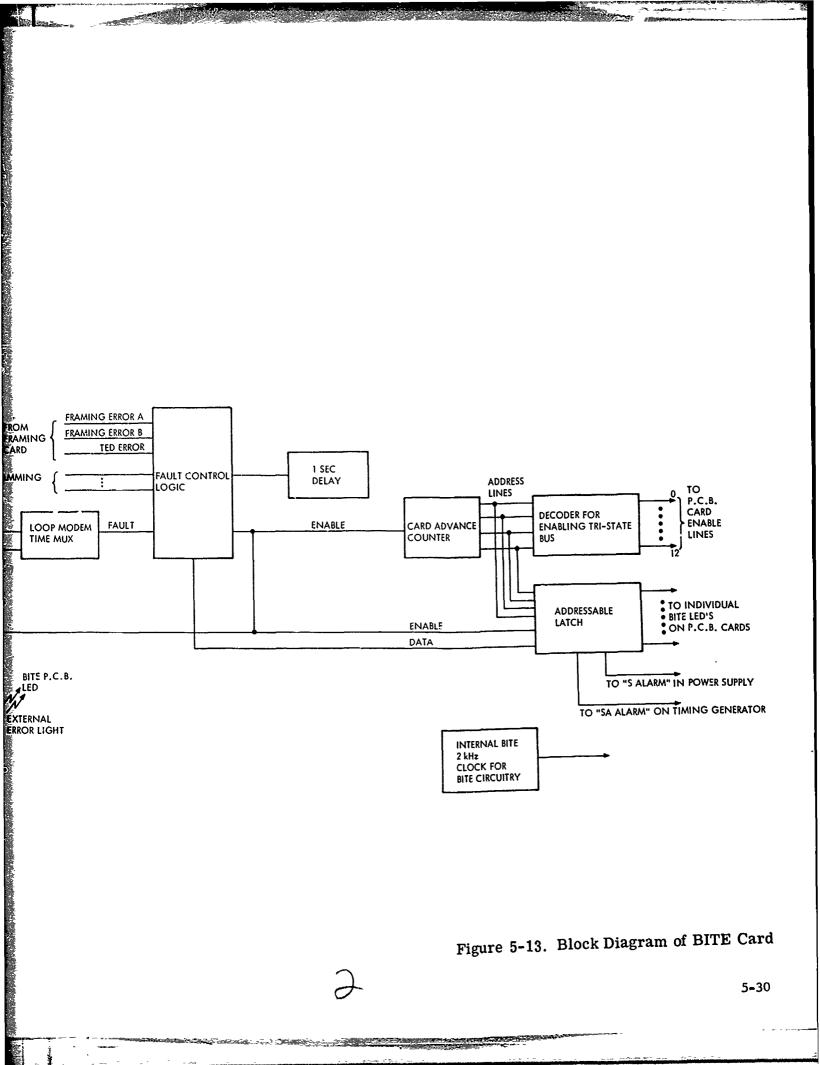

The BITE card monitors key signal status on each P.C.B. within the LGM. These signals are transmitted to the BITE P.C.B. over a sixteen (16) bit buss. The BITE P.C.B. sequentially addresses each P.C.B. within the unit and determines whether all the "key" signals are present. If not, a one second delay is started and the signals tested again. If after the one second delay, the fault persists, a summary error flag is raised. This flag causes the S and the SA (depending upon the fault) alarm to be energized. An LED located on the defective P.C.B. will then be illuminated along with the Summary Error indicator located on the front panel of the power supply. In the event that the BITE has detected a fault which could be caused by an external error (interface unit), the LED located on the BITE P.C.B. will illuminate. The fault LED located on the BITE P.C.B. is used to indicate external errors only.

The LGM power supply operates from 120 VAC, 50 to 400 HZ single phase power. The power supply outputs are  $\pm 10$  VDC,  $\pm 5$  VDC, and  $\pm 55$  VDC. The 5 and 10 VDC voltages are used internally to power the LGM P.C.B.'s. The  $\pm 55$  Volt output is used for powering the DSVT's via phantom loops. The Power Supply contains fault monitoring circuits which monitor the status of each output voltage. When an out-of-tolerance indication is detected, the Power-out-of Tolerance and Summary Fault indicators are illuminated.

#### 3.2.3 Interface Description

The LGM interface requirements are summarized in Table 3-2 and are described in the following sections.

## 3.2.3.1 Loop Interface (J1 and J2)

The LGM loop interface provides connections for 7, 8, 15 or 16 full duplex digital loops. Each loop interface shall consist of transmit loop data and receive loop data. The signals are conditioned diphase modulated signals. he signal rates are 16 kb/s or 32 kb/s. The signal lines are balanced.

Planne

TABLE 3-2. LGM INTERFACE SPECIFICATION SUMMARY

| Connector | Function                                                                                                                                                            | Signal Rate/<br>Frequency                                                                                     | Signal/Line<br>Characteristics                                                                                            | Type of Cable<br>Connection<br>Required                 | Number of<br>Wires in<br>Connector |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------|

| If        | <ul> <li>Transmit and Recei e<br/>Loop Data (Line Sid. ) -<br/>Channels 1 through 8</li> </ul>                                                                      | 16 or 32 kb/s                                                                                                 | Conditioned<br>Diphase                                                                                                    | 8 individual<br>quads - each<br>quad shielded           | 40                                 |

| .J2       | <ul> <li>Transmit and Receive<br/>Loop Data (Line Side) -<br/>Channels 9 through 16</li> </ul>                                                                      | 16 or 32 kb/s                                                                                                 | Conditioned<br>Diphase                                                                                                    | 8 individual<br>quads - each<br>quad shielded           | 40                                 |

| J3        | <ul> <li>Transmit group data</li> <li>Receive group data</li> <li>Transmit group clock</li> <li>Receive group clock</li> </ul>                                      | 256, 288, 512 or<br>576 kb/s @ 32 kb/s<br>loop rate or 128,<br>144, 256 or 288<br>kb/s @ 16 kb/s<br>loop rate | NRZ, Balarced                                                                                                             | 4 individual<br>shielded twister<br>pairs               | 12                                 |

| J4        | <ul> <li>Sync command</li> <li>Sync achieve</li> </ul>                                                                                                              | $\sim 10 \ \mu s$ DC level DC level                                                                           | Balanced<br>Unbalanced                                                                                                    | 2 individual<br>shielded twisted<br>pairs               | 9                                  |

| J5        | <ul> <li>Station clock</li> </ul>                                                                                                                                   | Group Rate                                                                                                    | Balanced square<br>wave                                                                                                   | 1 shielded<br>twisted pair                              | 3                                  |

| J6        | <ul> <li>Telemetry data out</li> <li>Telemetry data in</li> <li>Telemetry clock out</li> <li>Frame squelch (in)</li> <li>SA Alarm</li> <li>Summary Alarm</li> </ul> | 2 kb/s<br>2 kb/s<br>2 kb/s<br>DC<br>Contact Closure<br>Contact Closure                                        | NRZ, Balanced<br>NRZ. Balanced<br>Balanced<br>Square wave<br>TTL compatible<br>ALM = Close Contact<br>ALM = Close Contact | 6 individual<br>twisted pairs<br>with overall<br>shield | 13                                 |

| LI        | • Prime power                                                                                                                                                       | AC 50, 60, or<br>400 Hz                                                                                       |                                                                                                                           | 3 conductors                                            | က                                  |

5 M -

ĺ

Ċ

# 3-8

•5

÷

DSVT power feed is provided on each line via a phantom loop. Two multi-pin connectors are used for these signals.

#### 3.2.3.2 Group Interface (J3)

The group interface interfaces with a full duplex digital group which connects to a Group Modem or TED. The group interface consists of transmit group data and receive group data; transmit group clock and receive group clock. The signals will be NRZ. The line is balanced. The signal bit rates are 256, 288, 512 or 576 kb/s for loop data rates of 32 kb/s and 128, 144, 256, or 288 for loop data rates of 16 kb/s. A single connector is provided for these signals. When connecting to this interface, a cable consisting of shielded twisted pair should be used.

Cabling between the LGM and GM and between the LGM and the TED will be made from this common connector located on the LGM. It should be noted that when the LGM is connected to the TED, the TED control signals, Resync Command and Resync Achieved, are terminated in a separate LGM connector. Since these signals must be combined with other TED signals, a junction box of some kind must be provided outside the LGM unit. This junction box is not supplied.

3.2.3.3 TED Control Lines (J4)

A common connector is provided to carry the two black TED control signals required for TED synchronization. These signals are SYNC ACHIEVE and SYNC COMMAND. The interface cable connecting to this connector must be shielded twisted pair.

3.2.3.4 Station Clock (J5)

The LGM will accept a station clock input. The frequency of the clock is at the group bit rate.

#### 3.2.3.5 TELEMETRY/SQUELCH/ALARM Signals (J6)

A common connector is provided to carry the SYSCON TELEMETRY signals (2 kb/s), the FRAME SQUELCH signal and contact closures for the ALARM outputs. A switch is provided in the LGM which will internally connect the SYSCON Telemetry output to the SYSCON TELEMETRY source. The frame squelch (inhibit) is a DC input. When active, this signal inhibits frame search within the LGM.

#### 3.2.2.6 Prime Power (J7)

A common connector is provided to accept the Prime Power to the LGM. The input power will be 115 VAC  $\pm$  10% to 400 Hz. The power cable must have an overall cable shield.

5

#### 3.3 DETAIL ELECTRICAL DESIGN

## 3.3.1 Introduction

Common logic elements were designed into P.C.B.'s which were used in more than one unit. This was possible since there are many functions which are similar in these units. Consequently, it was decided to design these cards with emphasis on commonality. Variations in specific unit functions were taken care of by either toggle switches mounted on the P.C.B. or by back-plane wiring. For purposes of this technical report, we will describe the card in detail only once in the first section covering that material; variations of how it will be used in each unit will be covered under that unit.

#### 3.3.2 MUX/DEMUX

#### 3.3.2.1 Common Design

A common P.C.B. is used to perform the multiplexing and demultiplexing function in the LGM, RLGM, and RMC. Evaluations of the variations required by each unit as well as the multiple variations within each unit indicated that a common P.C.B. could be implemented.

The design of the MUX/DEMUX P.C.B. was implemented without the use of ROM's or PROM's. Consequently, the design was implemented using a logic topology which can produce all of the MUX/DEMUX variations by simple toggle switch selection.

## 3.3.2.2 MUX/DEMUX Requirements

Before a discussion on the operation of the MUX/DEMUX P.C.B. certain system requirements, in terms of the MUX/DEMUX function will be explained.

An examination of the MUX/DEMUX Pattern sequences for the RLG<sub>1</sub> LGM and RMC reveal that there are only four possible combinations. that is, the sequence of multiplexing or demultiplexing local channels and/or another group input, as in the case of RMC, must be one of four patterns as shown in Figure 3-2. Keep in mind that we are speaking of pattern sequences only, regardless of the number of channels within the group. N in Figure 3-2 could be any number, what is important is the sequence. Associating each MUX/DEMUX pattern sequence (Figure 3-2) with each unit (LGM, RMC, and RLGM) reveals that each pattern is used in the unit indicated.

|          | Unit |      |     |  |

|----------|------|------|-----|--|

| Sequence | RMC  | RLGM | LGM |  |

| 1        | X    | X    | X   |  |

| 2        | x    |      |     |  |

| 3        | x    |      |     |  |

| 4        | x    |      |     |  |

As can be seen the RLGM and LGM will always use pattern sequence 1 but the RMC can be operated in any of the four pattern sequences shown.

Now that the pattern sequence has been established, the last piece of information required is the number of channels within the group - the N of Figure 3-2. This is determined by the specification requirement and is summarized in Table 3-3.

|          | Channels Per Group |      |                    |

|----------|--------------------|------|--------------------|

| Sequence | RMC                | RLGM | LGM                |

| 1        | 8 or 9             | 9    | 8 or 9 or 16 or 18 |

| 2        | 9 or 16            |      |                    |

| 3        | 8                  |      |                    |

| 4        | 18                 |      |                    |

TABLE 3-3. NUMBER OF CHANNELS PER GROUP

Figure 3-2. MUX/DEMUX Pattern Sequences

Table 3-3 shows that in the RMC pattern 1 can only be select of for either an 8 or 9 channel group; that the LGM can MUX/DEMUX a pattern 1 sequence for an 8 or 9 or 16 or 18 channel group, and that only the channel groups associated with each pattern sequence need be selected on a per unit basis. There is a maximum of six MUA./DEMUX combinations involved. For example, the RMC can be operated in one of four patterns with one of four channel-per-group combinations. The LGM has only four combinations, the number of channels per group. The RLGM is fixed with pattern 1 and nine channels per group.

È

As an example of how this would work in an RMC let us look at the multiplexer circuit shown in Figure 3-3. If the local channels are always connected to MUX A and the group input channels are always connected to MUX B the connections to the multiplexer will be as shown in column A, which is all of the combinations for the RMC, that is up to eight local channels multiplexed with eight channels of an incoming group. To multiplex these inputs the pattern and the number of channels in the group must be known. This information will be supplied to the MUX DEMUX card by three toggle switches located on the Timing Generator. Only three switches are required since there are only six combinations as was previously explained. Let us assume that pattern 3 is selected. This means that the pattern sequence for multiplexing is as shown in Figure 3-2 and repeated here.

Seal of the Seal o

3-15

•

Since pattern 3 in the RMC must be an eight channel group (refer to Table 3-3), and the pattern sequence starts with the first GROUP INPUT channel, only three local phones will be connected. These inputs will be connected to MUX A, inputs 1 through 3 of Figure 3 3.

The MUX/DEMUX logic will cause the address 1, 2, and 3 counters of Figure 3-3 to clear such that each address line is zero. When each MUX is enabled line 1 of MUX A, line 9 of MUX B or line 1 of MUX C will be selected.

The following multiplexer sequence will then be followed:

- ENABLE 4 line will become active gating the framing subchannel into the MUX OUTPUT line.

- At the next group clock ENABLE 2 will be active, ENABLE 3 will be inactive and the address 3 counter will advance by one.

- With ENABLE 2 active, line nine (9) will be enabled gating the group input line 1 into the MUX OUTPUT line.

- At the next group clock ~ ENABLE 1 will become active, ENABLE 2 will be inactive and the address 2 counter will advance by one.

- With ENABLE 1 active, line one (1) will be enabled gating the local channel 1 line into the MUX OUTPUT line.

- At the next group clock ENABLE 2 will be come active, ENABLE 1 will be inactive and the address 1 counter will advance by one.

- With ENABLE 2 active, line ten (10) will be enabled gating the group input line 2 into the MUX OUTPUT line.

- This sequence continues for eight group clock pulses, whereupon the address 1 and address 2 counters are cleared and the ENABLE 4 line becomes active gating the second overhead sub-channel into the bus.

- At the next group clock ENABLE 2 line becomes active and the sequence just described is repeated.

If pattern 2 were to be selected by the toggle switches, the sequence just described would repeat except that the ENABLE 1 line would be active before ENABLE 2. This would multiplex the output with local channel 1 in the first channel following the overhead and the first group input line in the third channel slot.

# 3.3.2.3 MUX/DEMUX Variations for RLGM and LGM

The above discussions demonstrated how the MUX/DEMUX function would operate in the RMC. Operation of the card in the RLGM is modified, since the RLG output pattern sequence is fixed. Column B of Figure 3-3 shows how the RLGM connections are made. The most significant bit of the address lines to MUX A is grounded in the backplane wiring. The overhead channel is gated onto the output bus followed by inputs 1 through 4 scanned twice. The result is a 4-1/2 channel group which will be:

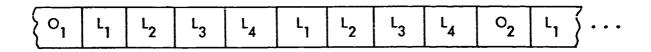

0 | LC1 | LC2 | LC3 | LC4 | LC1 | LC2 | LC3 | LC4 | 0 | LC1 | ---

This, MUX A is scanned in the RLGM using the same control logic of sequence 1 (nine channels) in the RMC. Because of the wiring variation in the backplane and the assignment of local channels, the same card may be used in the RLGM.

Column C of Figure 3-3 shows the connections for an LGM. As may be seen from Figure 3-3, the local channels are assigned alternately to MUX A and MUX B. The pattern sequence logic used to generate the group output is sequence 2 but, because of the assignment of alternating channels, the pattern generated is sequence number 1. When an 18 channel output is desired from the LGM, the logic for sequence 4 is employed to generate an output with a spare channel in the first position after the overhead channel. The appearance of an 18 channel output from an LGM would be:

0 | SP | LC1 | LC2 | LC3 | --- | LC16 | 0 | SP

Again, due to the alternate assignments of channels to MUX A and MUX B, the proper sequence of output channels is generated.

# 3.3.2.4 MUX/DEMUX Card

diriz a a desta di dua, histo 2000 estimato serio

A block diagram of the MUX/DEMUX P.C.B. is shown in Figure 3-4.

Programming is accomplished by the use of three switches located on the edge of the Timing Generator. The switch outputs are encoded on the Timing Generator and transferred to the MUX, DEMUX card to control the output

34-1-1-1

No. - 10

1.4.1.1

10.7

\_ \_ \_ \_ \_ \_

. С

-

÷.

#### 3-18

.

STATES IN

<u>Cardena</u>

35.

È.

Pattern Sequencer. In addition, a counter (Overhead Channel Generator) is preset to the proper value to divide the group rate clock (controlled by the same switches) by 8, 9, 16 or 18. This establishes where in the pattern of the group output to insert the data from the overhead channel and data from the Loop modems.

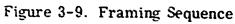

The multiplexer function contains three 8 bit multiplexers (A, B and C) and one additional input for the 17 Loop inputs and 8 overhead sub-channels. The Pattern Sequence provides the enable inputs to the multiplexers and produces one of the pre-selected output patterns of Figure 3-5, LGM Output Group Patterns.

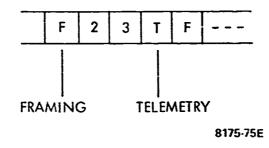

Multiplexer C. is dedicated to the 8 sub-channels that together make up the overhead channel. (See Figure 3-5 Overhead channel.) The first of these subchannels contains the Frame information from the Frame Generator, and will be alternating 1 - 0 or all 1's as selected by the Frame Pattern signal from the Group Framing card. Channel 8 of the sub-channels (subchannel before the framing subchannel) is for local telemetry. The remaining subchannels are set to logic level "1."

The output control circuitry inhibits the data channels from the MUX output upon command from the Group Framing card. The Enable Xmit Data signal causes the output of either normal data or all 0's. In either case, the frame pattern is passed through unaltered by the Output Control Logic.

The programmable DEMUX receives reframed data and a frame reference from the framing card and demultiplexes the data into loop channels and overhead subchannels in a preselected manner similar to the multiplexer. The eighth subchannel (subchannel just before the framing subchannel) containing SYSCON Telemetry is demultiplexed and routed to a card output.

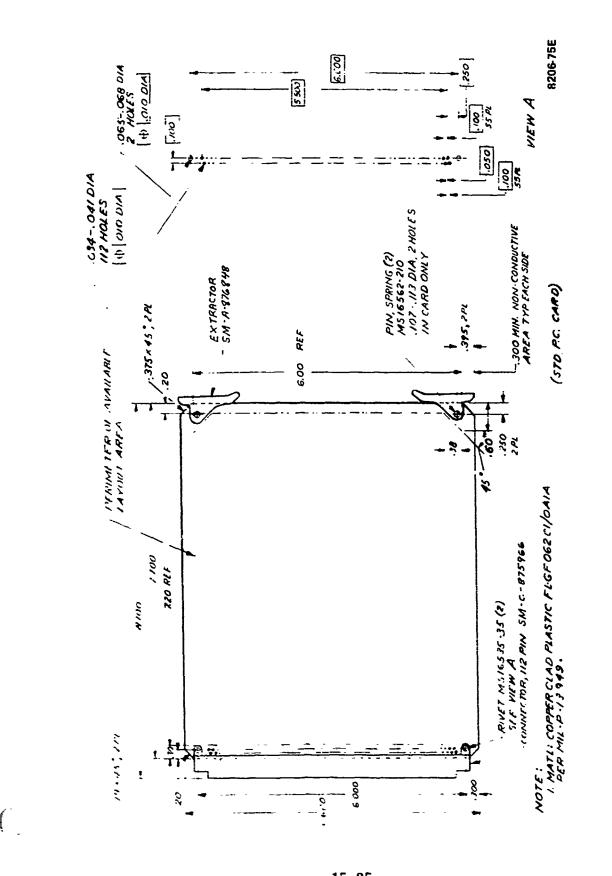

Figure 3-5. LGM Output Group Patterns and Overhead Channels

8133-75£

• • • • • • • • • • • • • O L1 L2 L3 L4 L5 L6 L7 L8 O L1 L2 L3 ..... O SP L1 L2 L3 L4 L5 L6 L7 L8 L9 L10 L11 L12 L13 L14 L15 L16 O SP L1 L2 L3 . O L1 L2 L3 L4 L5 L6 L7 L8 L9 L10 L11 L12 L13 L14 L15 O L1 L2 L3 . . . . 0 L] L2 L3 L4 L5 L6 L7 O L] L2 L3 . . . . . . . PATTERN NO. OF CHAN. NO. OF LOOPS 15 2 1 α ω ¢ 16 18

ہ (\_

u,

5 6 7

5 P

ო

2 0

----

1 2

TO/FROM SUB CH,

OVERHEAD CHANNEL

**⊢** ∞

F = FRAME BIT FROM FRAME SUBCHANNEL

[. 1,1,1 . . . OR . 1,0,1,0, . . . }

1. A.

3-20

一种经济分子

#### 3.3.3 Group Framing Unit

The original framing procedure was to occupy two printed circuit cards the framing card and the synch-onizer card. Because of design simplification, both these functions eventually required only one printed circuit card referred to as the Group Framing card.

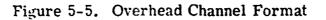

The framing portion of the card consists mainly of counters that monitor the incoming data and count errors in the framing patterns to determine frame status. The primary outputs from the framing portion of the card are "received side in/out of frame" and "remote side in/out frame."

The function of the synchronizer portion of the card is to interpret the frame status information and control the received data, the transmit data, frame output pattern and resync information to the TED.

# 3.3.3.1 Framing

The group framing unit is used in the receive side of all group data streams and controls the acquisition and maintenance of frame synchronization and generates frame error counts. The frame generator, in the block diagram of Figure 3-6 aligns itself with the framing pattern contained within the overhead channel of the data stream.

During the framing process, all the data transmitted by the remote unit has been set to zero with the exception of the first subchannel of the overhead channel (location of the framing sub-channel). Figure 3-7 illustrates the group and overhead channel formats. This channel contains a framing pattern of all "1's" or alternate "1's" and "0's." The framing unit interface is shown in Table 3-4.

í

4

Ĺ

1911 - 1920

27.3

101057

-----

Figure 3-7. LGM Group and Overhead Channel Formats

| Inputs:  |                       |                                                                                                                                    |

|----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1.       | "Go to Frame"         | Command from the synchronizer<br>logic 0 pulse of a period of 1/group<br>rate.                                                     |

| 2.       | Inhibit Receive Data  | Level from the synchronizer<br>0 = sets downstream data to one's<br>1 = enables downstream data                                    |

| 3.       | Group Size Select     | Line input for 4, 5, 9, 16 or 18<br>channels, level "1" on any one line<br>select group size. All lines logic 0<br>for 8 channels. |

| 4.       | Data                  | Baseband data from demodulator,<br>levels compatible with CMOS circuitry.                                                          |

| 5.       | Clock                 | At group bit rate, 50% duty cycle.                                                                                                 |

| 6.       | Squelch               | Input level 0 = inhibit frame search<br>1 = enable frame search                                                                    |

| 7.       | Frame Reference       | Logic "1" pulse of width $1/group$ rate<br>at a frequency of 4 kHz, in phase with<br>internally generated frame pattern.           |

| Outputs: |                       |                                                                                                                                    |

| 1.       | Data                  | Baseband data out                                                                                                                  |

| 2.       | Error Out             | Single output line, level is active high indicating an error in the frame pattern                                                  |

| 3.       | Receive Side in Frame | Level to synchronizer<br>"1" = in frame<br>"0" = out of frame                                                                      |

| 4.       | Xmit Side in Frame    | Level to synchronizer<br>"1" = in frame<br>"0" = out of frame                                                                      |

## TABLE 3-4. FRAMING UNIT INTERFACE

Note: All levels compatible with CMOS Logic.

Upon a command of the synchronizer to "go to frame" the framing unit sends a command to the demultiplexer to search for a data "one". When the demultiplexer detects a "one" it begins generating a frame reference signal, a 2K/1k Hz square wave aligned with the "1-0-1-0" pattern, and a "frame bit" pulse indicating the position of the first subchannel. The framing unit uses this information to generate an internal "1-1-1-1", "0-1-0-1" and "1-0-1-0" framing patterns. At the proper bit intervals, the interval framing patterns are compared to the received data and, if different, error pulses are generated and counted over predetermined intervals.

Because the framing unit does not know which pattern is being received, errors for both the all 1's pattern and the alternate "1 - 0" pattern must be counted, and in addition, because there might be a phase error in the received "1 - 0" pattern and the internally generated "1 - 0" pattern errors must be counted for an alternating "0 - 1" pattern. This phase error can occur when the generator. which is a counter that locates the position of the framing bit, locks onto an all "1's" pattern and then the pattern is switched to an alternating pattern

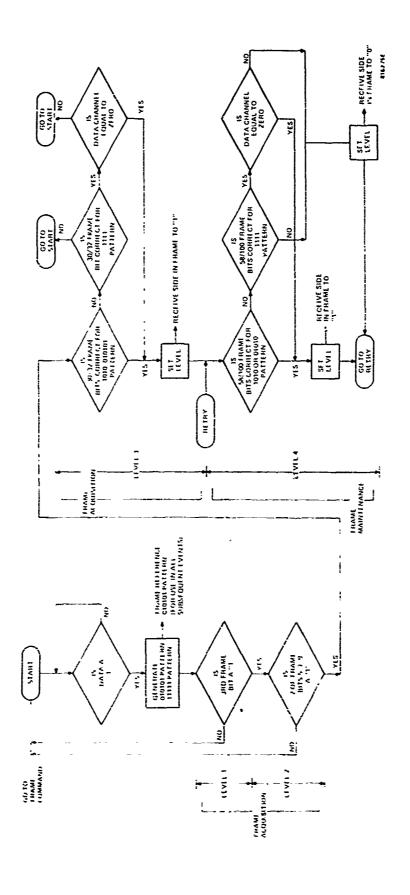

Frame acquisition is a three level process controlled by the frame monitor, in which, during each level, the outputs of the counters are examined at the completion of a predetermined interval and, if the number of errors are below thresholds, the acquisition level is advanced. The acquisition process is shown in flow chart form in Figure 3-8 and the criteria that must be met to advance from one level to the next is diagrammed in Figure 3-9.

The frame monitor begins the four level process upon a "go to frame" command from the synchronizer; level 1 is achieved upon the detection of the first data "one". In level 1, the 3rd framing bit is examined and must be a data "1" to advance to level 2 where two of the three bits 5, 6, and 9 must be data "1's". In level 3, frame bits 10 through 41 are examined. If 30 of the 32 bits are correct for the 0101 pattern, the 1010 pattern or the 1111 pattern, with an indication of zero data on the channels, "in frame" is declared and the system advanced to mainter.ance mode (level four). If, at any time, in levels one, two, or three, the criteria cannot be met, a search command is initiated and the system awaits another data "1", restarting the acquisition process.

The detection of the condition that data in the channels is equal to logic 0's is accomplished by 2 counters. One counts the position of data bits and one counts the data "1's" in these positions. If there are fewer than 171 data "1's" out of a 512 bit sample, a level is set indicating that data in the channels is equal to zero. The detection circuit runs continuously and is independent of the circuits used for acquisition and maintenance. A flow chart of this detection sequence is shown in Figure 3-10.

In the maintenance mode (level four) the frame bits are examined over 100 bit intervals: errors are counted for the 010101, 101010, and 1111 pattern and if 58 of these 100 bits are correct for the 010101 or 101010 patterns or for the 1111 pattern with an indication of zero data on the channels, an indication of "inframe" is maintained.

If, at any time, the criteria cannot be met, the next 100 bits are examined and if the test fails a second time "out of frame" is indicated to the synchronizer. The system continues to test 100 bit samples.

Another detection circuit that runs independent of the acquisition and maintenance circuitry monitors the frame bits over 32 bit intervals to determine which framing pattern is being received. Once 30 out of 32 frame bits are correct for the 1010 frame pattern or the 0101 pattern, a level is set indicating that the "transmit side is in frame sync." The 1111 frame pattern is then monitored and when 30 out of 32 frame bits are correct for this pattern and there is an indication of zero data on the channels, a level is set indicating that the "transmit side is not in frame sync." The flow chart of this sequence is shown in Figure 3-11.

The "squelch" input to framing unit is a DC level from an external input. A logic 0 forces an inframe condition on the receive side and enables data and the 1010 frame pattern to be transmitted. Refer to Table 3-4.

- annual

sidiulium,

Figure 3-8. Frame Acquisition and Maintenance Flow Chart

.₩

ŝ.,

3-28

Ĩ

3-30

The 'Inhibit Receive Data'' input from the synchronizer controls the received data. A logic 0 sets all received data to ''1's.'' Refer to Table 3-4.

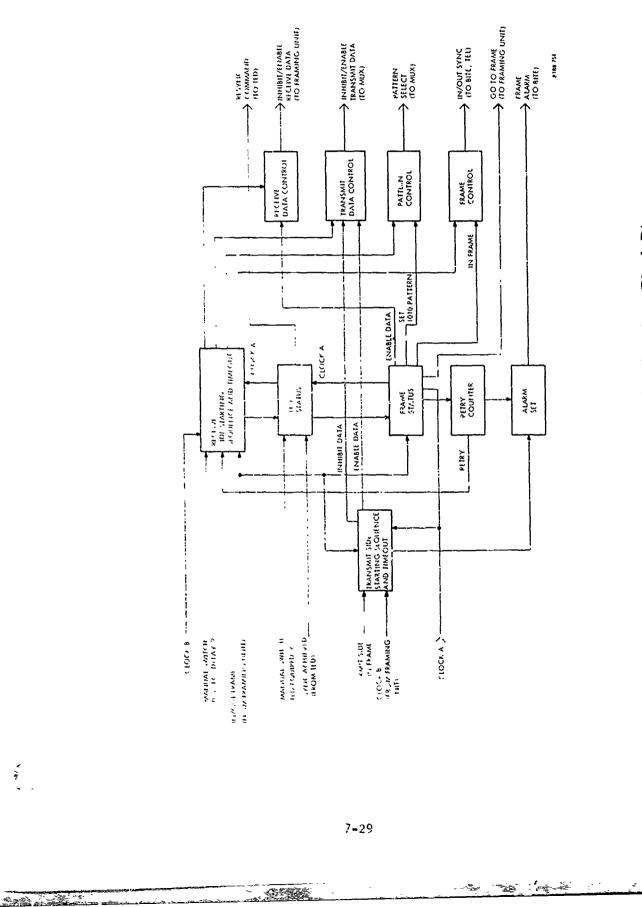

## 3.3.3.2 Synchronizer

Control of the sequence of operations necessary to obtain link synchronization is the main task of the synchronizer unit, shown in the block diagram of Figure 3-12. The setps in the logic sequence are shown in the flow chart of Figure 3-13. In that figure, signals from the framing unit are monitored for change of state: when the framing unit declares the receive group signal "Out of Frame", the chain of events down the right side of the chart occurs.

After a 0.5 second delay (which may be switched out) traffic flowing to downstream loops is set to all "1's", the frame pattern set to all "1's", and the transmitted data set to all "0's." Next, a timeout of 2.13 seconds is started and the TED checked for sync in progress; if sync is not in progress, a command is sent to the TED to begin synchronization. After a 500  $\mu$ second delay, in-sync status is checked and, when received, a "go to frame con.mand" is sent to the framing unit commanding it to search for frame. In-frame status is awaited and when received, the transmitted framing pattern is changed to alternate "1's" and "0's and the downstream data enabled. The received frame pattern is checked: if the pattern indicates the transmit side is in frame-sync the transmitted data is enabled and the sequence returned to the starting point. If frame sync cannot be achieved within approximately 2.13 seconds, the sequence is returned to the entry point labeled RETRY on the flow chart. If frame cannot be achieved, an alarm is set and not cleared until the receive side is declared in-frame sync.

If the framing unit detects a frame pattern change to all "1's", but the received side is still in sync, the sequence down the left side of the flow chart is followed. The transmit data, except for the framing sub-channel, is set to all "0's" until 1010 framing pattern is received. Failure to receive in-sync status within approximatelv 14 seconds causes the circuit to try again until the 1010 framing pattern is received. Frame status and frame alarm are supplied to the

ĵ-3]

Figure 3-12. Frame Synchronizer Block Diagram

ĺ

Ć

4.,

(

· ..

3-32

- 29 ¥273

地位沿达的图曲器的东部东

No. 6 9 9

## 3-33

÷ .

u - Cri Han in El BITE card. Three LED's are supplied on the Group Framing card and their functions are as follows:

a. BITE indicator

b. Frame Alarm

c. TED alarm - illuminated when the TED is not in synchronism Table 3-5 is a list of the interface levels to the synchronizer.

#### 3.3.4 Timing Generator/Telemetry - LGM

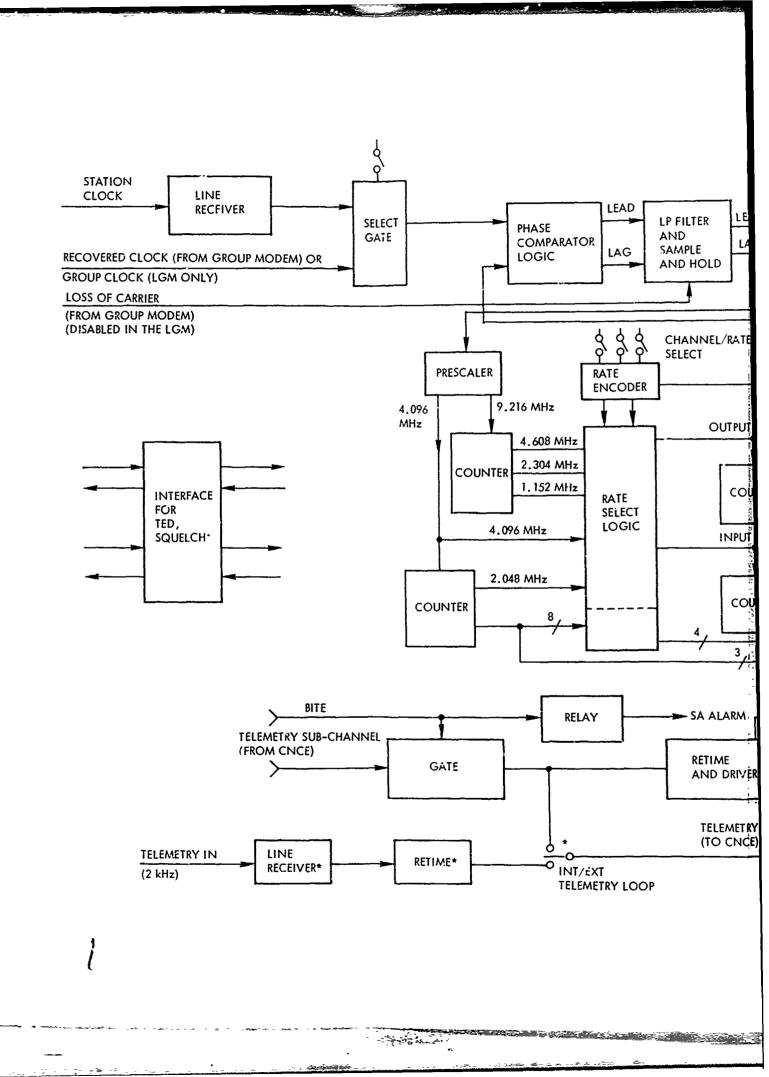

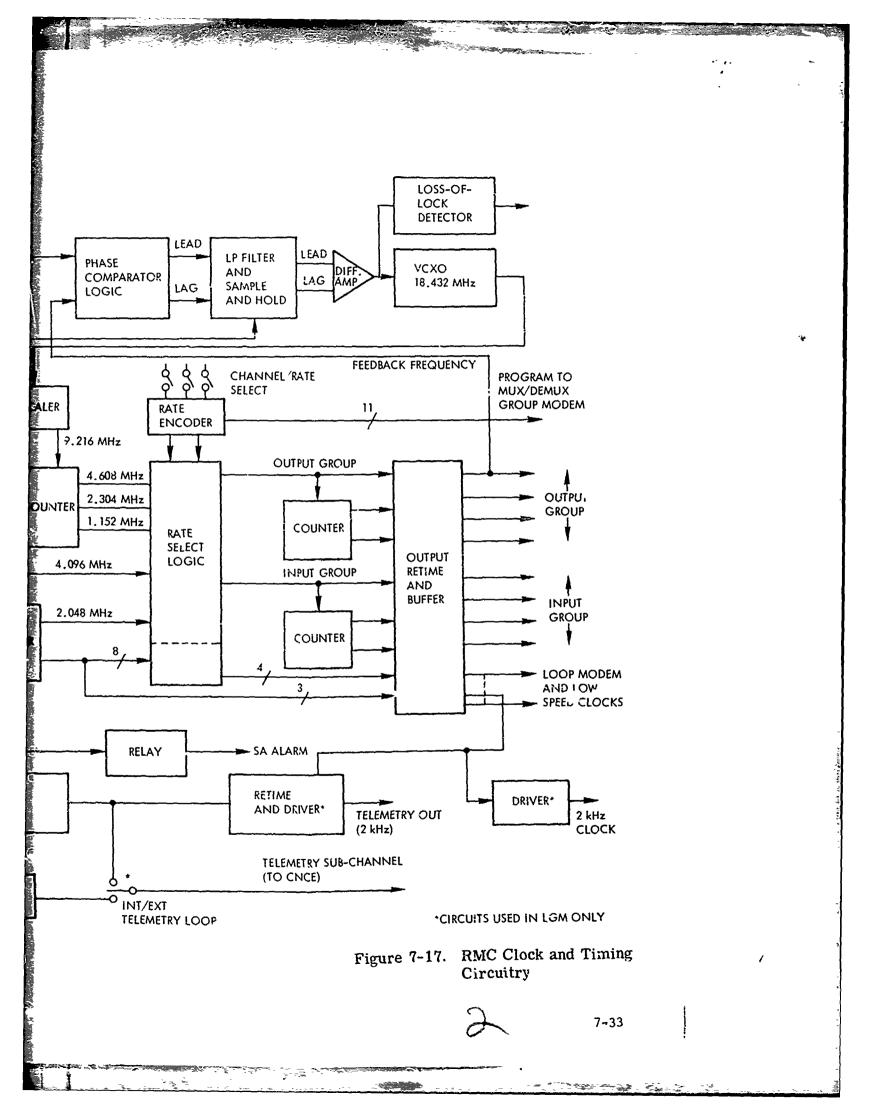

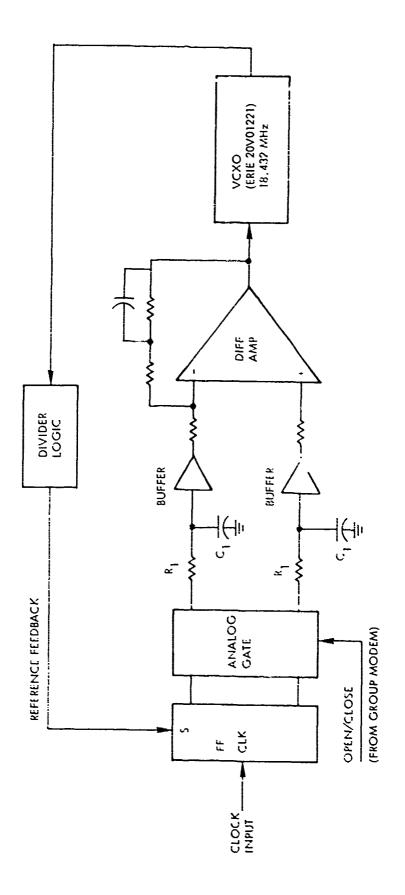

The same Timing Generator is used in the RMC, RLGM and LGM. Various combinations of rates are used in the units; the rate combinations required in the LGM are generated by the circuitry shown in block diagram form in Figure 3-14. Table 3-6 shows the clock rate required, the rate switch codes, and the configurations where the rates are required.

In the LGM, the Timing Generator is locked to either the Station Clock input or the clock associated with the NRZ Group Data input; they are both the same frequency and differ only in phase.

Line drivers and receivers for SYSCON Telemetry access are placed on the Timing Generator, as is the switch to route Telemetry loop-back internally or externally, the relay for the SA Alarm and the gate which breaks the Telemetry loop if the BITE indicates a fault. Interface drivers and receivers for the TED and Frame Squelch inputs (used only in the LGM) and the receiver for the Station Clock input are also placed on the Timing Generator card. Details of the circuit implementation for the interface drivers and receivers are given in Section 3.3.6. Details of the Timing Generator implementation are covered in Section 7.3.6.

#### 3.3.5 Loop Modem

The Loop Modem is a WF-16 field wire carrier terminal which provides full duplex transmission of binary data signals at 32, 16 kb/s between DSVT terminals and the LGM. A phantom power loop is provided in the diphase output

#### 3**-**34

- Frank have to

| Input:                       |                                                                                                      |

|------------------------------|------------------------------------------------------------------------------------------------------|

| Xmit side in frame           | Level from framing unit<br>0 = receiving 1111 pattern<br>1 = receiving 1010 pattern                  |

| Receive side in frame        | Level from framing unit<br>0 = out of frame<br>1 = in frame                                          |

| Sync achieved                | Level from TED, balanced signal<br>0 = sync in progress<br>1 = sync achieved                         |

| 0.5 sec delay                | Level set by manual switch<br>0 = No delay (switch closed)<br>1 = Delay enabled (switch open)        |

| TED Equipped                 | Level set by manual switch<br>0 = TED Equipped (switch closed)<br>1 = Not TED Equipped (switch open) |

| Clock A                      | 32 kHz, 50% duty cycle                                                                               |

| Clock B                      | 150 Hz, 10 - 90% duty cycle                                                                          |

| Output:                      |                                                                                                      |

| Inhibit/enable receive data  | Output level to framing unit<br>0 = inhibit receive data<br>1 = enable receive data                  |

| Inhibit/enable transmit data | Output level to multiplexer<br>0 = inhibit data<br>1 = enable data                                   |

| Pattern select               | Output level to multiplexer<br>0 = 1111 pattern<br>1 = 1010 pattern                                  |

| In/out frame sync            | Output level to BITE<br>0 = out of sync<br>1 = in sync                                               |

| Frame alarm                  | Output level to BITE<br>0 = frame alarm<br>1 = no alarm                                              |

| Resync command               | Balanced output to TED 32 $\mu$ s positive pulse                                                     |

| Go to frame                  | Command to framing unit of period 1/32K                                                              |

## TABLE 3-5. INTERFACE LEVELS TO SYNCHRONIZER

٤-

Note: All levels are C-MOS compatible.

-

- sugare

=

1 440 MAL

abidena bereken der barbahlich

| RLGM Configuration                                                              | -          | 4 1 '2 Chan | -      | -      | -       | -       |

|---------------------------------------------------------------------------------|------------|-------------|--------|--------|---------|---------|

| LGM Configuration                                                               | 8 Chan     | 9 Chan      | -      | -      | 16 Chan | 18 Chan |

| Input<br>RMC Configuration                                                      | 4 1/2 Chan | 4 1 '2 Chan | -      | -      | 8 Chan  | 9 Chan  |

| Output                                                                          | 8 Chan     | 9 Chan      | 8 Chan | 9 Chan | 16 Chan | 18 Chan |

| Switch 1                                                                        | 1          | 1           | 0      | 0      | 1       | 1       |

| Switch 2                                                                        | 0          | 1           | 0      | 1      | 0       | 1       |

| Switch 3                                                                        | 1          | 0           | 1      | 0      | 0       | 1       |

| CLOCKS                                                                          |            |             |        |        |         |         |

| <ul> <li>Station Clock.<br/>Recovered Clock, or<br/>Data Clock Input</li> </ul> | 256        | 288         | 256    | 288    | 512     | 576     |

| <ul> <li>Output Group</li> </ul>                                                | 256        | 238         | 256    | 288    | 512     | 576     |

| * 2X Output Group                                                               | 512        | 576         | 512    | 576    | 1024    | 1152    |

| * 8X Output Group                                                               | 2048       | 2364        | 2048   | 2304   | 4096    | 4608    |

| * Input Group                                                                   | 144        | 144         | 144    | 144    | 256     | 268     |

| • 2X Input Group                                                                | 288        | 288         | 288    | 288    | 512     | 576     |

| * 8X Input Group                                                                | 1152       | 1152        | 1152   | 1152   | 2048    | 2304    |

| * Loop Modem Clock 1                                                            | 512        | 512         | 512    | 512    | 512     | 512     |

| Loop Modem Clock 2                                                              | 64         | 64          | 64     | 64     | 64      | 54      |

| Loop Modem Clock 3                                                              | 32         | 32          | 32     | 32     | 32      | 32      |

| Group Framing Clock                                                             | 32         | 32          | 32     | 32     | 32      | 32      |

| <b>Telemetry Clock</b>                                                          | 2          | 2           | 2      | 2      | 2       | z       |

|                                                                                 | 0.15       | 0.15        | 0.15   | 0.15   | 0.15    | 0.15    |

## TABLE 3-6. TIMING GENERATOR OUTPUTS

10 - E

and the good of the second s

-992) 1 ž

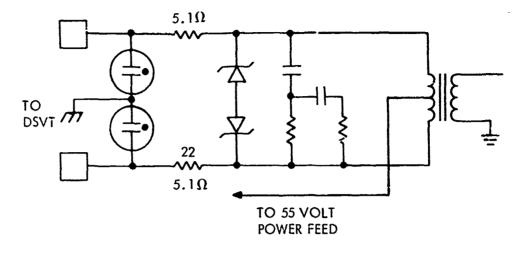

loop to power the DSVT. The phantom loop power feed is illustrated in Figure 3-15. The maximum current drawn by the off-hook DSVT is 83.3 mA with no battery charging current. The corresponding maximum reliable operating range is 3.0 Km (refer to Figure 3-16). The current limiter is set to trip at 250 mA for short circuit protection. The open circuit threshold is set at 3 mA, that is, if the loop current is ever less than 3 mA, the power feed open circuit detector will cause an alarm to be generated. A manual switch provides for disconnecting power from the loop for maintenance purposes. This switch is also be used to disable the summary status alarm signal when a loop modem is not connected to a DSVT.

The current limiter is designed to pass a transient current of up to 180 mA peak for 45 milliseconds without shutdown. The DSVT creates a transient which was discovered during interface testing with the V2-model DSVT.

#### 3.3.5.1 Diphase Modulator

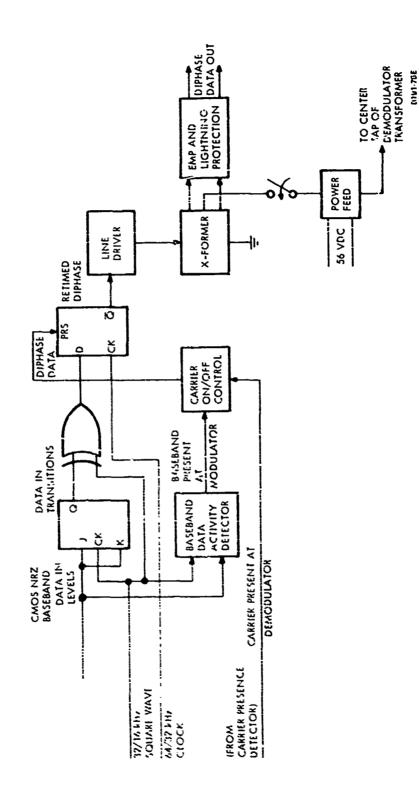

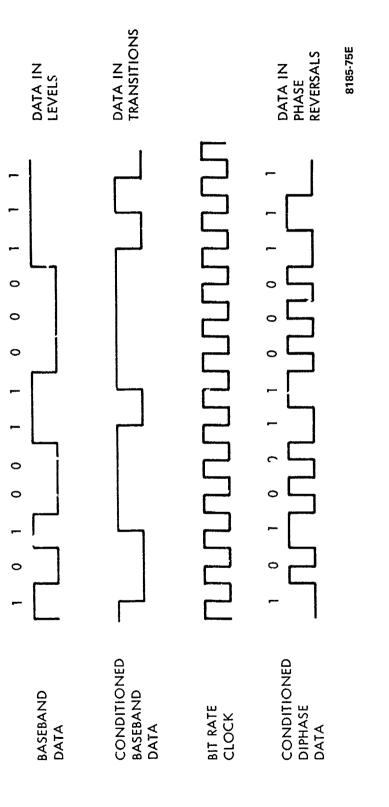

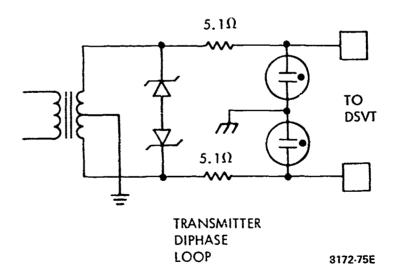

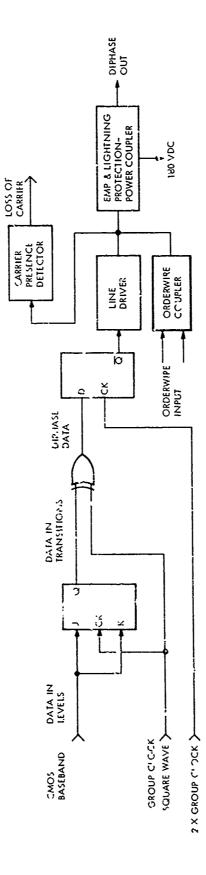

Figure 3-17 is a block diagram of the Diphase Modulator. The line receiver converts the balanced NRZ baseband to CMOS logic levels. Figure 3-18 shows how diphase data is generated. When the data is a mark (one) the J-K flip-flop toggles. The output of the J-K flip-flop is conditioned baseband. A transition in the conditioned baseband represents a mark (one).

The conditioned baseband is modulo two added to the bit rate clock (square wave). The resulting output is a conditioned diphase modulated version of the input baseband data. The diphase is retimed by the D flip-flop to remove glitches. The data activity detector generates a control signal indicating the presence of data activity at the baseband input. The modulator output is controlled by the baseband data activity line and the carrier presence detector line. If these signals indicate input data activity and/or carrier presence for a period of approximately 50 ms, the modulator output is enabled. The low-pass filter attenuates diphase signal out-of-band frequency components which might generate

Figure 3-16. Off-Hook KY-68 Common Battery Power

สมารรณการ

Manager and

ŝ.

1

Figure 3-17, Loop Modem Modulator Section

<u>]-41</u>

Figure 3-18. Generation of Conditioned Diphase Data

ł

crosstalk and provide FMP protection to the line driver by filtering out hf, high level EMP transients. The transformer couples the line driver to the line. The signal level on the loop side of the transformer shall be 3.0 Vp-p  $\pm$  10%. The rise and fall times are nominally 5% of the bit period at 32 kb/s or 1.56  $\mu$ sec. The rise and fall time remains 1.56  $\mu$ s (10-90% nominal) when the bit rate is changed to 16 kb/s. The transformer provides 600V isolation between the line driver and line. The transmitted waveform is square with less than 5% droop.

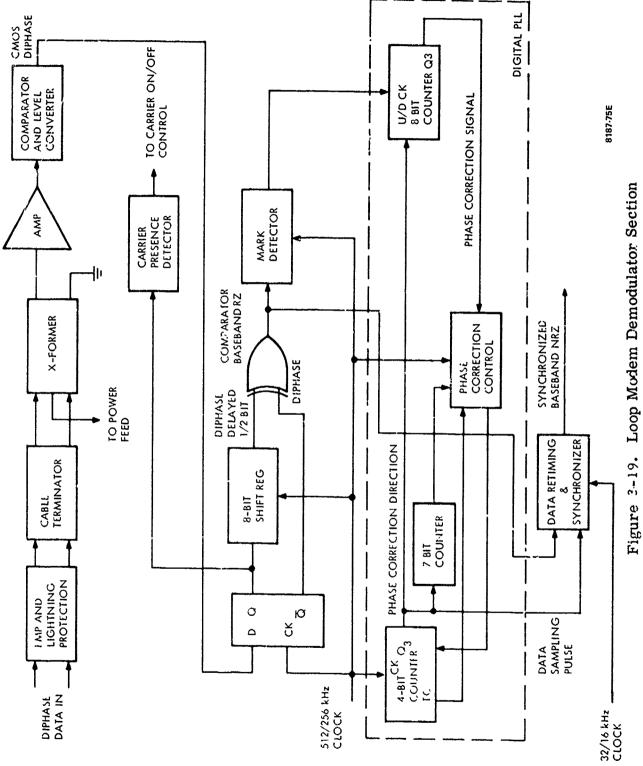

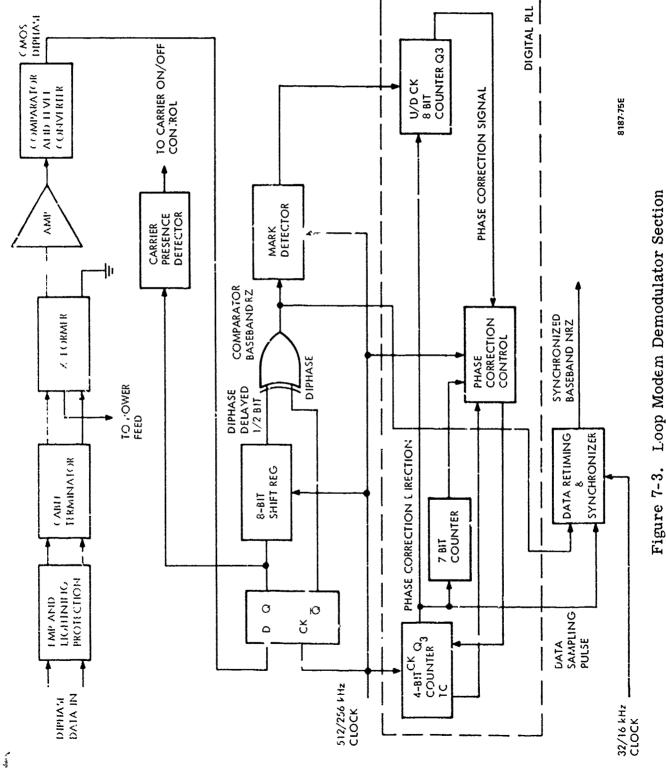

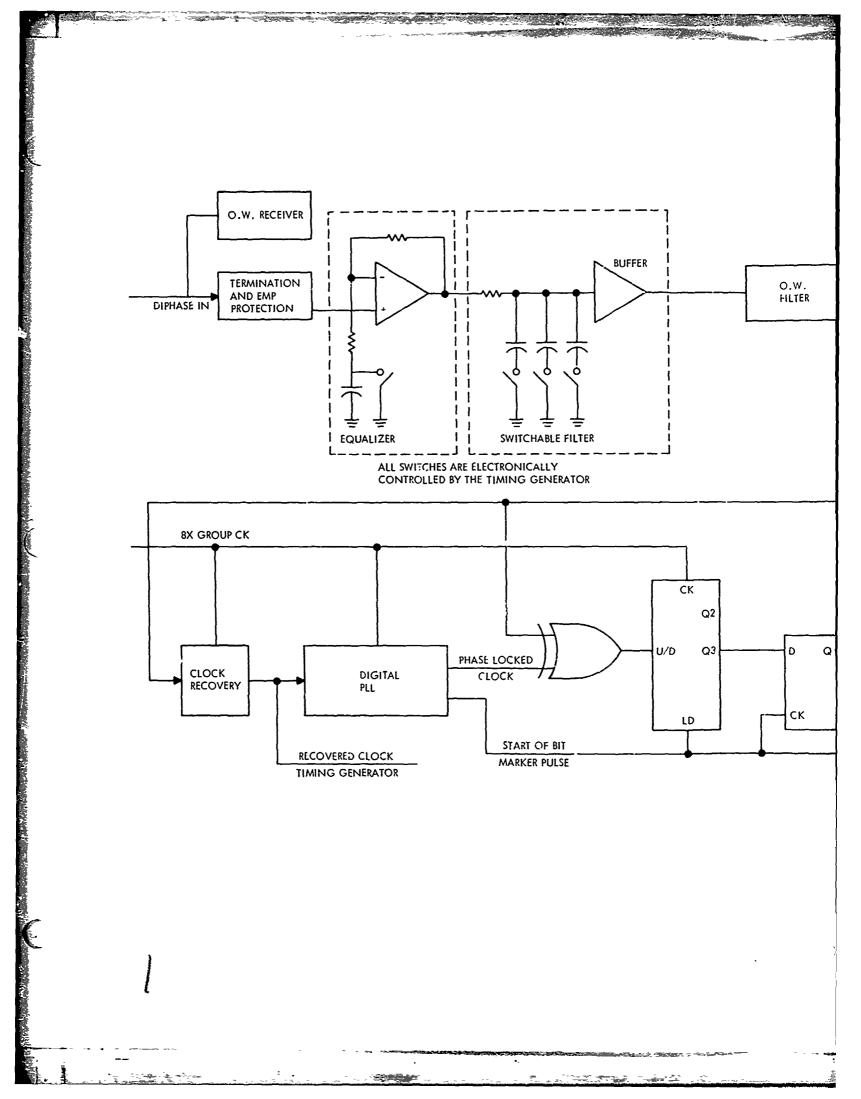

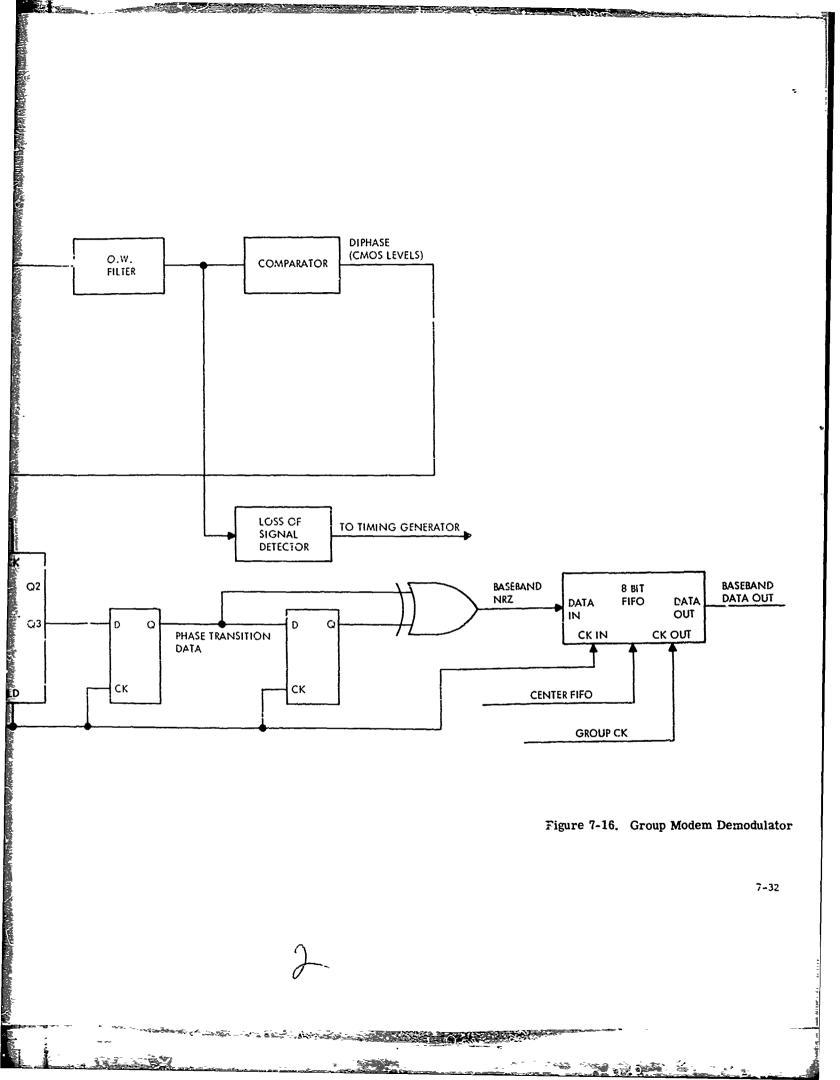

## 3.3.5.2 Diphase Demodulator

Refer to Figure 3-19 for a block diagram of the diphase demodulator. The input transformer AC-couples the input diphase signal to the band limited amplifier. The minimum detectable signal level is 150 mV to prevent nearend crosstalk from interfering with receive operation. The comparator and level converter transform the received diphase to CMOS logic levels. The diphase is delayed by one half bit, by shifting it through an eight bit shift register. The delayed diphase is compared with the undelayed diphase, the resulting output is baseband return to zero data. The mark detector generates a pulse for each mark (one) in the baseband return to zero. When in sync the data sampling pulse from the 4-bit counter occurs at the same time as the pulses from the mark detector. If the pulses from the mark detector consistently occur at the wrong time, the starting count of the 4-bit counter is altered by one in the appropriate direction. This action will synchronize the data sampling pulse to the pulses from the mark detector. The data sampling pulses sample the baseband return to zero data. The data is converted to baseband NRZ and synchronized to the bit rate clock in the DATA retiming and synchronizer block.

39 - -

t\_okr≣\_

**600** ÷.

-94.

÷

anteresti ere sere de la sere de l

terretaria da susception estatucionen estatucionen presentationen estatucionen estatucionen estatucionen estat A susceptionen estatucionen estatucionen estatucionen estatucionen estatucionen estatucionen estatucionen estatu

sianda in a

100001MIN\*\*

3-44

1997 - E. B.

749746.0777

2.336

3.3.5.3 Phone Wake-up and Shutdown

|    |                                                                           | Local   | Phone Initiating Call                                                                                                           |    |                                                         |

|----|---------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------|----|---------------------------------------------------------|