AD-A077 428 STANFORD UNIV CALIF STANFORD ELECTRONICS LABS

ADLIB USER'S MANUAL.(U)

AUG 79 0 D HILL

SEL-79-027

UNCLASSIFIED

SEL-79-027

AD77428

AD7

### COMPUTER SYSTEMS LABORATORY

(12)

STANFORD ELECTRONICS LABORATORIES

DEPARTMENT OF ELECTRICAL ENGINEERING

STANFORD UNIVERSITY - STANFORD, CA 94305

ADLIB USER'S MANUAL

by Dwight D. Hill

Technical Report No. 177

DDC FILE COPY

August 1979

This work was supported by the Joint Services Electronics Program under Contract DAAG29-79-C-0047.

79 10 22 153

SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered) READ INSTRUCTIONS REPORT DOCUMENTATION PAGE BEFORE COMPLETING FORM REPORT NUMBER 2. GOVT ACCESSION NO. 3. RECIPIENT'S CATALOG NUMBER Rechnical Report No. 177 5. TYPE OF REPORT & PERIOD COVERED 4. TITLE (and Subtitie) Technical Report ADLIB User's Manual PERFORMING ORG. REPORT NUMBER SEL-79-027, 78-17 AUTHORIS B. CONTRACT OR GRANT NUMBER(s) Dwight D./Hill JSEP DAAG29-79-C-0047 10 PROGRAM ELEMENT, PROJECT, TASK 9 PERFORMING ORGANIZATION NAME AND ADDRESS Computer Systems Laboratory N-921 66 (12)86 Stanford University Stanford, CA 94305 12 REPORT DATE 13. NO. OF PAGES 11. CONTROLLING OFFICE NAME AND ADDRESS August 1979 76 Army Research Office P.O. Box 12211 Research Triangle Park, NC 27709 15. SECURITY CLASS. (of this report) Dr. J. R. Suttle Unclassified 15. DECLASSIFICATION/DOWNGRADING 16. DISTRIBUTION STATEMENT (of this report) Reproduction in whole or in part is permitted for any purpose of the U.S. Government. 17. DISTRIBUTION STATEMENT (of the abstract entered in Block 20, if different from report) 18 SUPPLEMENTARY NOTES 19. KEY WORDS (Continue on reverse side if necessary and identify by block number) simulation, PASCAL, hardware description languages, SABLE, SDL 20 ABSTRACT (Continue on reverse side if necessary and identify by block number) ADLIB (A Design Language for Indicating Behavior) is a new computer design language recently developed at Stanford. ADLIB is a superset of PASCAL with special facilities for concurrency and interprocess communication. It is normally used under the SABLE simulation system.

DD 1 JAN 73 1473 EDITION OF 1 NOV 65 IS OBSOLETE

SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered)

332 400

TOP

ADLIB USER'S MANUAL

Dwight D. Hill

Technical Report No. 177

August 1979

Computer Systems Laboratory

Departments of

Electrical Engineering and Computer Science

Stanford University

Stanford, California 94305

<sup>\*</sup>This work was supported by the Joint Services Electronics Program under Contract DAAGZ9-79-C-0047

ADLIB USER'S MANUAL

Dwight D. Hill

Technical Report No. 177

August 1979

Computer Systems Laboratory

Departments of

Electrical Engineering and Computer Science

Stanford University

Stanford, California 94305

ABSTRACT

ADLIB (A Design Language for Indicating Behavior) is a new computer design language recently developed at Stanford. ADLIB is a superset of PASCAL with special facilities for concurrency and interprocess communication. It is normally used under the SABLE simulation system.

INDEX TERMS : simulation, PASCAL, hardware description languages, SABLE, SDL

#### Introduction

SABLE is a design automation system currently being developed at Stanford University to support structured, multi-level simulation of computer designs. SABLE stands for Structure And Behavior Linking Environment, because it joins information about the interconnectivity of components with algorithmetic specifications of their behavior. The user expresses interconnectivity via SDL (Structural Design Language ) [VCW77], which has facilities for defining multiple levels of physical hierarchy. Component behavior is specified in ADLIB (A Design Language for Indicating Behavior), which is a superset of the language PASCAL [JK74]. ADLIB was designed to simplify the description of commonly used computer components and to be compatible with SDL and SABLE. ADLIB was never intended to be a programming language completely by itself.

This manual is divided into three parts: an introduction to ADLIB with a informal description of the basic features; a more detailed discussion of the structure of an ADLIB program, including scoping rule and contour models; and a summary of the keywords and syntax of the language. Because documentation is widely available, this manual will not repeat the detailed features of PASCAL. However, the basic aspects of PASCAL will be described briefly, so that readers familiar with other high level languages should be able to follow the discussion without too much difficulty.

The author would like to express his thanks to William vanCleemput, Warren Cory, Eric Slutz, Tom Blank, Ann Beetem, Bob Dutton, John Hennessey, and all the other, people who have contributed to ADLIB.

# TABLE OF CONTENTS TO STANFORM THE STANFORM T

| BAS |     |     |            | AD      | . 1  |     |    |        |     |       |      |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   |      |

|-----|-----|-----|------------|---------|------|-----|----|--------|-----|-------|------|-------|-------|-----|------|-----|-----|---|------|-------|---|------|---|-----|---|-----|-----|---|-----|-----|-----|---|---|------|

| 1   | P   | HP  | ns         | F       | n    |     |    | 11     | *   |       |      |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | •    |

| ,   | ,   | URF | OD         | iic     | 71   | n   | S. | 7      | 'n  | *     | ù    |       | NE    | u'  |      | 'n  | · · |   | -    | 20    |   | ici  | ė | *   |   | *   | *   | * |     | *   | *   | * | * |      |

|     | 1   |     | VI         | FW      |      | F   |    |        | S   | - 4   | "    | -     | UN    | S 1 | 0    | ic  | Ť   |   | CUI  | 13    |   | 00   | 3 |     | * |     | *   | * | *   |     |     | * | * |      |

|     | 2   | AT  | VI         | TI      | ni   | Ä   | 1  | A      | DI  | 1     | À    | č     | ON    | 51  | P    | iic | TS  |   |      | *     |   |      | * |     |   | *   | *   |   | *   |     |     | * | * |      |

| 3   |     | ESI | GN         | IN      | G    | A   | Ñ  | A      | DI  | i     | B    | P     | RO    | GF  | A    | Ä   |     |   |      |       |   | *    |   | *   | * |     |     |   | *   |     |     |   |   | 1.   |

|     |     |     |            |         |      | -   |    |        |     |       | -    |       |       | -   |      |     |     |   |      |       |   | •    |   | •   |   |     |     |   | *   |     |     |   |   | •    |

| CHA |     |     |            |         |      |     |    |        |     |       |      |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   |      |

| TYP | ES, | NE  | TT         | YP      | ES   | ;   | AN | ID     |     | TY    | PI   |       | CH    | EC  | K    | IN  | G   |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   |      |

| 1   | W   | HAT | D          | OE      | 5    | **  | 51 | FR     | 01  | NG    | L    | 1     | TY    | PE  | D    | *   | ME  | A | N?   |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 2    |

| 2   | T   | YPE | C          | HE      | CH   | I   | NO | 3      | Q!  | F     | N    | Ŧ     | S     |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   |      |

| 3   | D   | AIA | 1          | YF      | E    | •   | A  | Y A    | 1   | LA    | BI   | . Е   | 1     | N   | A    | Dι  | 11  | , |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 2    |

|     | 1   | B   | OL         | EA      | N    |     |    |        |     |       |      |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 2    |

|     | 2   | 11  | ITE        | GE      | R    |     |    |        | 3   |       |      |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 2    |

|     | 3   | R   | AL         |         |      |     |    |        |     |       |      |       |       |     |      |     |     | - | 14.4 | CLUY. |   | - 20 | 1 | 100 |   | 100 | 102 | 1 | 900 |     |     |   |   | 2    |

|     | 4   | EN  | UM         | ER      | A    | E   | D  | T      | YI  | B     | S    |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 2    |

|     | 5   | 51  | IBR        | AN      | G    | : 5 |    |        |     |       |      | *     |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 2    |

|     | 6   | AF  | (RA        | Y 5     |      |     |    |        |     |       |      |       |       |     | 1013 |     |     |   | 1    | 1     | 1 |      |   | -   |   |     |     |   | 144 | 744 |     |   |   | 2    |

|     | 7   | RE  | CO         | RD      | 5    |     | *  | *      |     |       |      | *     |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 2    |

|     | 8   | 58  | 15         |         |      |     |    | *      |     |       |      |       |       |     | . ,  |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 2    |

|     | ?_  | F   | LE         | 5       | -    |     |    |        |     |       | *    |       |       |     |      |     |     | * |      | *     | * | *    |   |     |   |     |     |   |     |     |     |   |   | 2    |

|     | 10  | !   | OI         | NI      | ER   | (2  |    | *      |     |       | *    | *     | *     |     |      |     |     |   | *    |       | * |      |   | *   |   |     |     |   |     |     |     |   |   | 2    |

|     | 11  |     | II         |         |      |     | *  | *      |     |       | *    | *     | *     |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   | *   |     |     |   | * | 2    |

|     | 13  |     | EG         | 15      | 11   | K   | -  | .:     |     |       | :    |       | _:    | _ : | _    | ٠.  |     |   |      |       |   |      | * | *   |   |     |     |   |     | *   |     |   | * |      |

| A C | ONT | ONT | OU         | OD<br>R | EL M | ספ  | FC | R      |     | A D   | L    | B     |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | ,    |

| 2   | 5   | TRU | CT         | UR      | E    | 0   | F  | A      | N   |       | DI   | I     |       | PF  | 105  | GR  | AF  | 1 |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 3    |

|     | 1   | GE  | . UB       | AL      |      | U   | C. | 41     | 1   | ۲1    | E    | t S   |       |     |      |     |     |   |      |       |   |      | - | -   |   | -   |     | 1 | 120 | 1   | -   |   | 1 | -0.0 |

|     | 2   | NE  | 15<br>0C   | A       | NI   | )   | NI | ET     | T'  | YP    | E    | 5     |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   |      |

|     | 3   | CI  | OC         | K S     |      |     |    | *      |     |       |      |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 1    |

|     | 4   | 1.  | THE L      | NU      |      | ٦,  | A  | JS     |     | 5     |      |       |       |     |      |     |     |   |      |       |   |      |   | -   |   |     |     |   |     |     |     |   |   |      |

|     | 5   | R   | MP         | IN      | ES   | ,   |    |        |     |       |      |       |       |     |      |     |     |   |      |       |   |      |   |     | * |     |     |   |     |     |     |   |   | 1    |

|     | 6   | C   | MP         | IX      | P    |     | DE | F      | L   | NI    | T    | 0     | NS    |     |      |     | *   | * |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 1    |

| CHA |     |     |            |         |      |     |    |        |     |       |      |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   |      |

| ADL | IB  | SY  | ITA        | X       |      | -   |    |        |     |       |      |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   |      |

| 1   | ı   | OM  | LE         | VE      | L    | 5   | Y  | IT     | A   | X     |      |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   |      |

| 2   | 5   | UM  | TAR        | Y       | 01   | -   | OF | E      | R   | AT    | 01   | 25    |       |     |      |     |     | * |      |       |   |      |   | *   |   |     |     |   |     |     |     |   |   |      |

| 3   | 3   | IA  | <b>TUA</b> | K U     |      | ιυ  |    | 1      | 1   | - 1   |      | (5    |       | -   |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     | 100 |   |   |      |

| 4   | 8   | ESI | RV         | ED      |      | 40  | RI | 25     |     |       |      | *     |       |     |      |     |     | * | *    |       |   |      |   |     | * |     |     |   |     |     |     |   |   | 4    |

| 5   | 5   | YH  | AX         | C       | H    | AR  | 1  | ,      |     | *     |      |       | *     |     |      |     |     |   |      | *     |   |      |   |     |   |     |     |   | *   | *   |     |   |   | *    |

| APP | END | IX  | 1          | :       | R    | JU  | T  | IN     | E   | P     | A    | ck    | AG    | E   | ,    |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   |      |

| 1   |     | GP  |            |         |      |     |    | 700750 | 200 | 10.71 | 0.70 | 40.00 | T-100 | -   |      |     |     |   |      |       |   |      |   | 4.5 |   |     |     |   |     |     |     |   |   |      |

|     | 1   |     | IT         |         | L    | 12  | A  | T      | 0   | N     |      |       |       |     |      | •   |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 1    |

|     | 2   | CI  | NV         | ER      | 5    | 10  | N  | -      | -   |       |      |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 1    |

|     | 3   | A   | H          | H       | E    | П   | C  |        |     |       |      |       |       |     |      |     |     |   |      |       | - |      |   |     |   |     |     |   |     | 18  |     |   |   | 1    |

|     | 4   | 51  | HIF        | TS      |      |     |    |        |     |       |      |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     | -   |   |     |     |     |   |   | 1    |

|     | 5   | 8   | IT.        | AC      | CI   | ES  | 5  | IN     | G   |       |      |       |       |     |      |     |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 1    |

|     | 6   | L   | OGI        | CA      | L    | 140 |    |        | 1   | TO S  | -    |       |       |     |      | 618 |     |   |      |       |   |      |   |     |   |     |     |   |     |     |     |   |   | 1    |

|     | 7 FORMATTED I/O   |     |     |     |     |  |   |  |   |   |   |   |   |   |   |   |   | . A-7  |

|-----|-------------------|-----|-----|-----|-----|--|---|--|---|---|---|---|---|---|---|---|---|--------|

| 2   | RNDPACK           | -:- | :   |     |     |  |   |  |   |   |   |   |   |   |   | * |   | . A-8  |

|     | 1 SETTING A NEW   | "SE | ED" |     | : . |  |   |  | * |   |   |   |   |   | * |   |   | . A-8  |

|     | 2 RANDOM DRAWING  | FAC | NCI | TOM | 3 . |  |   |  |   |   | * |   |   |   |   |   |   | . 4-9  |

|     | 3 DATA ANALYSIS   | FAC | 111 |     |     |  | * |  |   | * | * | * | * | * | * | * | * | . A-10 |

| PPE | ENDIX 2: REFERENC | ES  |     |     |     |  |   |  |   |   |   |   |   |   |   |   |   |        |

APPENDIX 3: INDEX

#### CHAPTER 1 BASICS OF ADLIB

#### 1.1 PURPOSE OF ADLIB

The purpose of an ADLIB description is to define the behavior of one or more types of computer components. The SABLE system then combines these with information that specifies the number of components used, and the way they are connected. This topological information is expressed in SDL. For convenience the user may generate the SDL automatically via an interactive graphical structure editor called SUDS2 [US79].

In ADLIB, the code that defines the behavior of one type of component is called a <u>comptype</u>. There is no way of telling from an ADLIB source how many components of each comptype, if any, will be used in a design. Each comptype written in ADLIB is a specification of the input to output function of one type of component. Essentially all information that passes through a component must go through well defined I/O interfaces called "nets." SABLE later connects these nets to the nets of other components as directed by the user via SDL.

Before we enter into any explanations of ADLIB and SABLE, it might be helpful to give a small, useless but complete example. We will define a tiny system consisting of a dealer and a player. the dealer sends random integers to the player, who just receives them and writes the results on the terminal. The ADLIB code for this looks like:

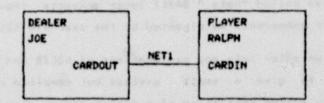

The structure of this system is shown below:

The SDL code to used describe the interconnectivity of this system is:

NAME: TEST;

TYPES :dealer.player;

dealer : joe;

player : ralph;

END;

NETSEGMENT;

net1 = joe.cardout,ralph.cardin;

ENDNETS;

ENDNETS;

ENDC;

CEND;

When this code is compiled and executed, the result is a never ending stream of random integers between 1 and 13 (inclusive) directed to the terminal. If the example makes sense, fine. If not, don't worry. The remander of this paper will explain and elaborate everything.

#### 1.2 INTRODUCTION TO THE NEW ADLIB CONSTRUCTS

Because ADLIB is a superset of PASCAL, it includes all of the PASCAL control statements. For readers not familiar with these statements they are summarized here.

#### 1.2.1 Review Of PASCAL Constructs

- IF <boolean expr> THEN <stmt1> ELSE <stmt2>

which chooses between two alternative statements;

- 2. CASE <expr> OF <value1>:<stmt1> <value2>:<stmt2>

which selects one of an arbitrary number of statements. (similar to, but more powerful than a "switch" or "computed goto");

- WHILE (boolean expr) DO (stmt)

which iterates a statement zero or more times;

- REPEAT (stmt) UNTIL (boolean expr)

which iterates a statement one or more times;

- GOTO <label>

which transfers control to <label> unconditionally\*.

#### 1.2.2 Additional ADLIB Constructs

The above six constructs are useful for defining the algorithm incorporated within a component, but are not adequate for describing inter-component control and data flow. Therefore, the following new constructs have been added to ADLIB:

#### 1.2.2.1 ASSIGN (expr) TO (net name) (timing clause)

Assign evaluates (expr) and stores the result away in a hidden area. At a later time, this value is retrieved and assigned to the specified net. Time delays may be specified in several ways depending on the nature of the circuit (synchronous or asynchronous) and the objectives of its designer. The simplest way is to define a delay directly, as for example:

#### ASSIGN true TO out DELAY 15.3;

Fifteen and three tenths simulated time units after this statement is executed, the net "out" will be updated to the value "true". Time delays need not be constants, any real expression may be used. For example, if two parallel paths exist to the same outward connection, and either one is sufficient to drive it, then we could define the component's behavior as:

\*This construct is currently out of fashion.

ASSIGN result TO out DELAY min(delay\_1,delay\_2)

("Min" is a function that returns the minimum of its arguments.)

The expression in an ASSIGN statement may contain function calls. For example, in order to describe a signal generator, it is convenient to write:

#### ASSIGN sin(time\*frequency) TO signalout

This statement illustrates two other points as well. In ADLIB, the variable "time" always contains the current value of the simulation time. When the simulation begins, it is equal to 0.0. User assignment to "time" results in a compilation error message. Also, this statement does not contain an explicit DELAY clause. The ADLIB compiler therefore treats it as if DELAY 0.0 were specified. At first glance, zero propagation delay times may seen confusing, unrealistic, and potentially hazardous. However, because of the runtime organization of SABLE, this operation is unambiguous and useful. During simulation, SABLE cycles between the execution of component's behavior descriptions and the updating of the nets connecting them. First, all components are allowed to execute, then all nets are updated, then all components are allowed to execute again, etc. One iteration of this cycle constitutes one event. It may happen that several events occur sequentially, but at the same simulated time. If one or more components assign to a set of nets with a DELAY of 0.0, then all these updates will appear to occur simultaneously.

No hazards or races are introduced by allowing zero propagation delay, and there are several applications where it is in fact, necessary and appropriate. For example, a designer may prefer to treat combinational logic as operating with zero time delay, to contrast it with the sequential circuitry. As an extreme example of this, consider

a system implemented with relays. We wish to express the idea that a voltage propagates through the contacts of a relay immeasurably faster (measured in nano-seconds) than the speed at which the armature moves (measured in milli-seconds). To describe a relay which operates as a single pole, double throw switch (like a one bit multiplexor), we could write:

#### IF armature\_position = up THEN ASSIGN input1 TO out ELSE ASSIGN input2 TO out

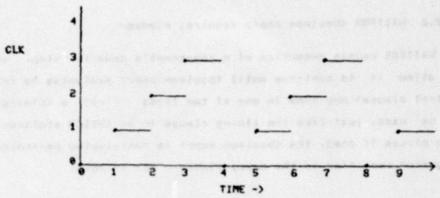

In the above example, the exact speed of propagation incalculable and irrelevant (in fact, it would probably be lost to round-off error). On the opposite extreme are circuits whose output values must be available at precisely controlled instants, i.e. synchronous circuits. For example, most micro-controllers operate at a precisely constant speed independent of the micro-instruction mix (this is not generally true of macro-instructions). Such controllers and any circuitry directly connected with them are most conveniently defined in ADLIB with the use of a CLOCK and the SYNC primitive. An ADLIB clock may be thought of as a function that maps simulation time into positive integers. At time 0 all clocks have value 0. As simulation time the clocks run through their phases repetitively: 0,1,2,3,0,1,2,3,0,1,2,3... etc. for a four phase clock. The period of repetition is the parameter value specified by the user in the clock definition statement. The value of clock "clk." defined as:

CLOCK clk(4.0.4);

is shown in figure 1.

By use of the SYNC operator, the user can synchronize an operation with a particular leading edge of a clock. For example, a micro-controller might have to have several control lines ready at precisely the leading edge of the number one phase of clock "micro\_clk". This could be written as:

FIGURE 1: VALUE OF CLK(4.0,4)

```

r := microstore[micro_ip];

micro_ip := micro_ip + 1;

ASSIGN r.carry TO line1 SYNC micro_clk PHASE 1;

ASSIGN r.shift0 TO line2 SYNC micro_clk PHASE 1;

ASSIGN r.shift1 TO line3 SYNC micro_clk PHASE 1;

ASSIGN r.shift2 TO line4 SYNC micro_clk PHASE 1;

ASSIGN r.clear TO line5 SYNC micro_clk PHASE 1;

(*etc.*)

```

All of the above ASSIGN statements will be effected at precisely the seme simulated time.

The user may specify any number of independent CLOCKs, each with their own periods and numbers of phases. Unlike some other simulation environments, clocks do not consume any computation resources themselves: only when and if a component accesses them is any calculation performed. The user may mark one of the clocks as being the This saves him or her from writing the clock's name in every sync clause. Also, if no phase is specified, the compiler assumes that phase 0 is intended. It is therefore quite convenient to describe systems that maintain a single universal clock, such as a pipelined multiplier that keeps each stage in lock step with the others.

#### 1.2.2.2 WAITFOR (boolean expr) (control clause)

WAITFOR causes execution of a component's code to stop, and does not allow it to continue until content clause may come in one of two forms. First, a ctiming clause

may be used, just like the timing clause in an ASSIGN statement. If a delay clause if used, the cboolean expr is reevaluated periodically at the period specified in the delay clause. For example:

WAITFOR current>0.001 DELAY sample\_period;

This statement would check the value of "current" every "sample\_period" time units, until it exceeded one milliamp.

If SYNC is specified, the <boolean expr> is reevaluated each time the specified clock goes through the specified phase. For example:

WAITFOR acknowledge=1 SYNC bus\_clock PHASE 4;

This statement would not allow execution to continue until the net "acknowledge" was equal to 1 on the leading edge of the fourth phase of clock "bus\_clock".

Alternatively, a control clause may take the form of a list of nets that the component is to be sensitized to. This format is called a "check list", because whenever one of the nets mentioned in it is updated, the boolean expression is rechecked. By this means, it is easy and efficient to describe asynchronous machines driven by the the nets to which they are connected. For example:

WAITFOR data\_rdy = 1 CHECK data\_rdy

This statement would put the component into a passive state until the

net "data\_rdy" was updated to the value 1. No simulation resources are consumed while the component is idle (there is no "busy waiting"). In particular, if other components ASSIGN to data\_rdy whatever value that it already contains, the expression "data\_rdy = 1" is not reevaluated. This is because SABLE automatically deletes all such null updates.

#### 1.2.2.3 Sensitize, Desensitize, and Detach

Taken collectively, these provide a facility for direct control of the operation of a component. They operate in a way that is similar to WAITFOR, but at a lower level and somewhat more efficiently. Sensitize and desensitize are predefined procedures make a component receptive or immune to changes on its inward nets. These procedures are always used in conjunction with the DETACH operator, which causes execution of a component to stop until one or more of the nets to which it is sensitive is updated. When an update on a sensitized net occurs, the component will be awakened.

Because of the flexibility of the WAITFOR construct, it is difficult to think of an application where DETACH is really more convenient, and not merely more efficient. However, to illustrate its use, we shall use it to describe a finite state machine that recognizes the bit strings consisting of 1's and 6's. The strings must match a regular expression that begins and ends with 1, and where any 0 must be preceded and followed by at least one 1 (example taken from [KZ70]). This machine is stimulated by a net called "input\_line", which contains a data element "d" and a strobe field "s". (In order to drive this machine, it is necessary to put the data value in the "d" field, and to update the "s" field.) In ADLIB, one way to define the automaton is:

sensitize(input\_line);

- 1: detach; (\*initial state\*)

if input\_line.d = 0 then goto 3;

- 3: detach: (\* terminal state\*) goto 3;

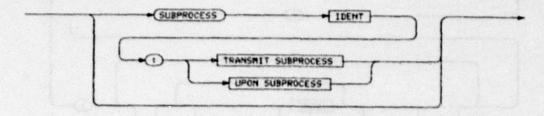

When combined with the facilities available in PASCAL, the above primitives are adequate to encode almost any conceivable function among a component's nets. However, before a design language will be used, it must be more than adequate, it must be convenient. Therefore ADLIB also incorporates the concept of "subprocesses" to facilitate encoding the behavior of many common computer activities. Each subprocess performs a single function and runs independently of the main body of the comptype. There are two types of subprocesses, upon and transmit.

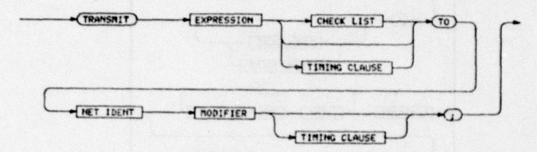

#### 1.2.2.4 UPON (boolean expr) (check list) DO (stmt)

Upon is used to define a set of activities to be performed independently of the main activities of the component. Whenever a net in <check list> is updated, <boolean expr> is reevaluated. If it is true, then <stmt> is executed. For example:

This code would check the priority level whenever the interrupt net was updated, and service the interrupt when necessary.

#### 1.2.2.5 TRANSMIT (expr) TO (net) (timing clause)

TRANSMIT is more specialized than UPON. A transmit subprocess reevaluates (expr) whenever one or more of the nets in (net list) is changed. The result is then assigned to (net name) at the time specified by (timing clause). Transmit is very convenient for describing combinational circuitry. For example, a simple NAND gate can be described with:

nand: TRANSMIT NOT(a AND b) TO c CHECK a.b DELAY 15.0;

#### 1.2.2.6 Inhibit And Permit

The name given to a subprocess may be used to control it by means of the procedures "permit" and "inhibit". All subprocesses are initially inhibited, which means that no external stimulus can activate them. The main body of a component may then permit some or all of the subprocesses to run, at which point they are ready to respond to stimuli. Subprocesses may be inhibited at any time, which returns them to their initial, inactive state. For example, a computer may protect a critical region with:

inhibit(interrupt);

write\_to(shared\_data);

permit(interrupt);

#### 1.3 DESIGNING AN ADLIB PROGRAM

To illustrate how ADLIB is used, we shall "design" a small system that plays Blackjack with itself. This was inspired by a DDL design found in IDDL751, but is somewhat more complex and complete. The ADLIB system consists of one or more dealers and one or more players. Nets shall be used to represent the flow of cards from the dealers to the players, and to coordinate their activities. To begin our design

process, we first consider what data must be transmitted (suit and rank) and what control information is needed (player is waiting for card. dealer is waiting for player, etc.) We develop three types of nets (nettype's) that define the structure of the nets which carry information between components, and associate an interpretation with The design at this point might be encoded as shown in figure 2. The nettypes shown fall into two categories: structured nettypes, such "card\_bus" and simple ones. such as "display\_lights" and "control\_line". Structured nettypes are most useful when several pieces of information are logically affiliated but need to be updated and examined independently.

```

PROGRAM cardgame:

TYPE

card_bus = RECORD

suit : suit_type;

rank : rank_type;

END:

display_lights = (hit, stand, broke);

control_line = (card_rdy, card_accepted);

COMPTYPE dealer: (* deals out cards*)

BEGIN

(* not yet designed*)

END:

COMPTYPE player; (*accepts cards, stands or goes broke*)

BEGIN

(* not yet designed*)

END:

BEGIN

END.

```

Figure 2 - Outline of Blackjack System

The code in figure 2 specifies three nettypes but no control protocol. We decide to use one control line between each player and the dealer that serves it, and to alternate the value of this net between "card\_rdy" and "card\_accepted". The synchronization mechanism can then be expressed by the code fragments shown in figure 3. The first waitfor statement shown causes the player to wait until the card is ready, and

the second causes the dealer to wait until the player has decided what to do.

(\* player's code \*)

WAITFOR cntrl = cardrdy CHECK cntrl;

(\* accept card\*)

ASSIGN card\_accepted TO cntrl;

(\* process card, go broke, hit or stand\*)

(\* dealer's code \*)

(\* generate next card \*)

(\* assign nextcard to cardbus \*)

ASSIGN card\_rdy TO;

WAITFOR cntrl = cardaccepted CHECK cntrl;

Figure 3 Code fragments for Coordination

We are now ready to specify the algorithms used by the players and dealers. For the purpose of this discussion, the player just accepts cards until it reaches its limit, treating aces as 1 or 11 points as needed. The ADLIB code for the player is shown in figure 4, and will be referred to later.

END:

COMPTYPE player; (\* declare the "terminals" of this component\*) INWARD card : card\_bus; DUTWARD lights : display\_lights; EXTERNAL cntrl : control\_line; (\*declare the storage needed by this component\*) score : 0..27; holding\_ace : boolean; BEGIN WHILE true DO BEGIN holding ace := false; score := 0; REPEAT REPEAT ASSIGN hit TO lights: IF (card.rank=ace) AND (NOT holding\_ace) THEN BEGIN holding\_ace: true END; UNTIL score >= upper\_limit;

IF (score > 21) AND holding\_ace THEN BEGIN score := score - 10;

holding\_ace := false END;

UNTIL score >= upper\_limit;

IF score <= 21 THEN ASSIGN stand TO lights ELSE ASSIGN broke TO lights; END:

Figure 4: Definition of Comptype "Player"

In order to see if comptype "player" works properly, it is necessary to develop a "dealer" comptype to drive it. There are several possible ways to do this, just as there are several ways to test a new piece of hardware. In ADLIB, it is easy to write a comptype that talks with the terminal for interactive testing. Another possibility is to use a pseudo-random number generator that will choose cards from an infinite deck. A package of such generator routines called RNDPAK is available to ADLIB users. Finally, the designer can write a comptype that reads the test data from a file. Each of these approaches have

their own merits at different phases in the design process. Normally, interactive testing would be used for initial debugging, large numbers of random inputs for extensive testing, and prerecorded, specially selected values for production.

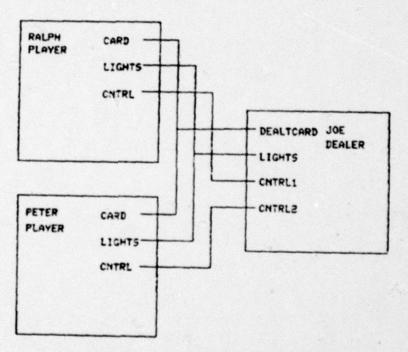

Having specified the behavior of comptype "player" and "dealer", we are free to use as many of each as we wish in our design. The structure of one possible cardgame is shown in figure 5.

FIGURE 5 : STRUCTURE OF A SIMPLE CARDGAME

## CHAPTER 2 TYPES, NETTYPES AND TYPE CHECKING

## 2.1 WHAT DOES "STRONGLY TYPED" MEAN?

Like its base language PASCAL, ADLIB is said to be a "strongly typed" language [OEI78]. This means that each piece of data, each function and all parameters must each be declared with exactly one type. Whenever a variable or net is used, its use must be type compatible with its declaration. In a well-written program, the type of a variable defines the narrowest possible range of values that it may attain. While beginning programmers may think that type checking is an arbitrary restriction on their programming style, more experienced designers can usually put it to very good use. Typing is essentially a way for the designer to express his or her intentions about the way in which a piece of data should be used. The compiler can then automatically detect when those intentions are violated, which usually implies an error. In languages that are not typeful, it is often easy to treat character strings as reals, or integers as pointers. Even when this is done intentionally, it is very difficult to read, understand and maintain the resulting program. And when it is done unintentionally, chaos can result. For a discussion of PASCAL typing and program reliability the reader is referred to [WN75].

#### 2.2 TYPE CHECKING OF NETS

The primary type checking mechanism in ADLIB is the use of nettypes for defining the intended interconnection mechanism between components.

In SABLE, the nets that connect components must be declared with identical nettypes at each end. If this is not so, an error message is printed\*. This nettype checking is considerably more thorough than checks found in most register transfer language's (RTL's), where it is only necessary that the number of bits must match. To illustrate this difference, consider a component that produces two BCD (binary coded decimal) digits and another that accepts eight bits of binary data. Most RTL's would allow them to be directly connected, since 8 bits = 8 bits. Even simulation might not detect this error if the test set did not happen to include any values greater than 9. But the ADLIB - SABLE environment would detect the mismatch, since "BCD" is not type compatible with "binary". Further examples of type checks will be given later in this section.

But types should not be viewed just as a restriction. Compared with other languages, ADLIB (like PASCAL) offers a wealth of useful new types to choose from. The next section illustrates a few of the ways that a designer can take advantage of them to reduce errors and improve readability.

#### 2.3 DATA TYPES AVAILABLE IN ADLIB

Because ADLIB is a superset of PASCAL, it inherits all of the PASCAL type construction mechanisms. For the benefit of readers not familiar with PASCAL, these are listed here:

\*Unless a special TRANSLATOR has been provided. TRANSLATORS provide the ability to do multi-level simulation at the expense of some type-checking security and some loss of data precision. For a discussion of their use, see [HDD79-1].

#### 2.3.1 Boolean

Boolean variables can attain the values true or false. (Similar to FORTRAN's LOGICAL.) For example if "strobe" were declared to be of type boolean we could write:

strobe := data\_rdy AND (bus\_clock = 3)

#### 2.3.2 Integer

I.e. -15, or 1024.

#### 2.3.3 Real

I.e. 3.14159 or 6.023e24

#### 2.3.4 Enumerated Types

These allow a user to enumerate (list out) all the possible values of a piece of data. For example:

logic\_level = (low, high, unknown, high\_impedance)

We have already seen several examples of enumerated types in the cardgame program. Enumerated types are also useful for describing the instruction sets of machines, such as the INTEL 8008 [173]:

TYPE

instruct\_kind = (lrr,lrm,lmr,lri,lmi,

inr,dcr,adr,adm, (\*etc\*));

In ADLIB, one can use a CASE statement to describe the execution of a machine instruction in a format very similar to ISP [BCG71]. For example:

TYPES, NETTYPES AND TYPE CHECKING DATA TYPES AVAILABLE IN ADLIB

FUNCTION decode : instruct\_kind; (\* code omitted for brevity\*)

BEGIN (\*main body of program\*)

CASE decode OF

1rr : (\* load reg to reg\*)

BEGIN (\* code omitted \*) END;

ret : (\* return from subroutine\*)

BEGIN (\* code omitted\*) END;

(\*etc\*)

END;

#### 2.3.5 Subranges

These specify that only part of a range of values is acceptable, for example:

#### register\_number = 0..7

specifies not only that variables of type register\_number are integers, but also that they must lie between 0 and 7 (inclusive). Assigning a value to a subrange variable that is outside its range is automatically detected. For example, in the ADLIB blackjack machine the variable "score" was declared to range over the values 0 to 27, the high value being equal to 16 (the highest possible score before standing) + 11 (value of an ace). By contrast, the DDL version merely declared the score to be a five bit register. The ADLIB approach has two advantages. First, it allows the designer to defer any decision on the representation of data in the early stages of design. Second, and more importantly, it encodes more information: e.g. the fact that the score can never exceed 27. Although this is not too critical here, it is easy to visualize applications where the range of data that a register holds, if known, can be used to improve the design. For example, nine ADLIB blackjack scores could safely be added in an 8-bit alu, since we know the total cannot exceed 243. On a more practical level, it might be useful to know not only that memory addresses in a DEC 10 are 18 bits

long, but also that they range from 16 to 262144, (since the first 16 addresses refer to registers).

2.3.6 Arrays

ARRAY is similar to DIMENSION in FORTRAN. For example: memory = ARRAY(0...1023) OF integer

#### 2.3.7 Records

Records are useful for grouping related data, as for example:

complex = RECORD

real\_part,imag\_part : real;

END:

Most register transfer languages, including DDL, provide mechanisms for making several names equivalent references to the same piece of data. The usual example of this is an instruction register, where one of the bits is given a mnemonic name such as "I" (for Indirect) in addition to being 1R101. This can make parts of a program more readable, but can also lead to confusion when a mnemonic is referenced for the first time several pages away from its declaration. The strategy adopted by ADLIB is to use "variant" records for this purpose. A variant record is essentially a single data area that may have several different data structure "templates" applied to it. As an example of this, consider the four ways that one can look at an HP 2116 instruction, as discussed in the machine manual [HP]. In ADLIB, these alternative views would be encoded as:

TYPE instr\_variant = (whole, memory\_ref, register\_ref, i\_o); VAR ir : RECORD CASE instr\_variant OF

whole : (ARRAY[0..15] OF bit);

memory\_ref : (indirect : bit;

mem\_instr : ARRAY[0..4] OF bit; zero : bit; mem\_addr : ARRAY[0..9] OF bit); reg\_ref : (group : ARRAY(0..3) OF bit; micro : ARRAY(0..11) OF bit); i\_o : (io\_group : ARRAY[0..3] OF bit; io\_instr : ARRAY[0..5] OF bit; select : ARRAY[0..5] OF bit; END:

This record informs the reader (and the compiler) that the instruction register "ir" may be viewed in four different ways, but is still in fact just one register 16 bits long. (Note that the total number of bits in each variant is 16.) Access to ir can then be performed using the mnemonic fields, as for example:

ir.whole := data\_bus;

IF ir. indirect = 1 THEN cycle := fetch;

Now the fields are closely associated with the register, and the reader is (hopefully) less likely to misinterpret them.

#### 2.3.8 Sets

A SET is an area of storage that may contain from 0 to all of its members i.e. a powerset. Textually, sets are delimited by "[" and "]", and facilties are provided for set intersection (AND), union (OR), difference (-) membership (IN), equality ("="), size comparison ("(" and ">"). Since sets are normally packed into machine words, these operations usually run very quickly. Sets are convenient for grouping related symbols, both visually for the reader and logically for simulation. For example, in the 8008 we can express certain facts in machine readable form that are normally only shown on the data sheets.

such as:

index\_instructs:=[lrr,lrm,lmr,lri,lmi,inr,dcr];

one\_cycle\_alu:=[adr,acr,sur,sbr,ndr,xrr,orr,cpr];

As an example of the use of set operators, consider the code that describes the timing of part of the execution cycle. It might contain:

IF instruction IN one\_cycle\_alu THEN WAITFOR SYNC PHASE 1;

#### 2.3.9 Files

The ADLIB user may declare various types of FILEs to match the data to be stored in them. Storing and retrieving that data can then be accomplished very efficiently. For example, it is easy to describe a core image as:

core\_image : FILE OF integer;

For convenience, special facilties are provided for reading and writing files of text.

#### 2.3.10 Pointers

PASCAL, (and therefore ADLIB) provides two independent areas for storing data, the ordinary stack and a heap. The heap is accessed only via special pointer variables, which may in turn point to other pointers, etc. This makes it convenient and efficient to develop complex data structures. Pointers are denoted by the up arrow "f". For example, the data structures for describing a virtual memory system might look like:

TYPE

page = ARRAY[0..511) OF integer;

page\_ptr = \( \gamma\) means "pointer to"\*)

page\_table = ARRAY [0..255] OF RECORD

logical\_address : 0..64255;

is\_incore : boolean;

memory\_ref : page\_ptr;

END:

New elements are added to the heap by means of the "new" procedure.

Using this, part of the code to describe memory management might be written:

VAR pm : pagemap;

IF NOT pm[high\_bits].is\_incore THEN new(pm.memory\_ref);

This would allocate a new page of memory from the heap if the "is\_incore" flag of page\_map "pm" were false.

Whereas the above types are part of both PASCAL and ADLIB, the following two are available only in ADLIB.

#### 2.3.11 Bit

This is a predeclared subrange of integer. It may range over the values 0..1.

#### 2.3.12 Register

This is a predeclared type that is useful for RTL descriptions. Many special routines are provided for manipulating variables of type register, such as exclusive or, rotate, etc. Arithmetic may be performed on registers in one's complement, two's complement, sign magnitude, and unsigned formats.

#### 2.3.13 Another Example: R5232 Interface

One can combine enumerated types with records to create a very strong, specific definition of an interface. For example, consider the R5232 connection standard. Most RTL's would merely specify it as a 25 bit connection, which could be written in ADLIB as:

RS232 = ARRAY [1..25] OF bit:

However, this would not make best use of the facilities evailable. In ADLIB, it would be better to write:

```

TYPE

widerange = (neg_12V,pos_12V);

grounded = (zero);

NETTYPE

RS232 = RECORD

fg : grounded; (*frame ground*)

td : widerange; (*transmit data*)

rd : widerange; (*received data*)

rts : widerange; (* request to send*)

(* etc.*)

END;

```

If the net "tty1\_line" were declared to be of nettype RS232, then the compiler would accept

ASSIGN neg\_12V TO tty1\_line.td;

but would flag as an error:

ASSIGN 0 TO tty1\_line.terminel\_rdy;

TYPES, NETTYPES AND TYPE CHECKING DATA TYPES AVAILABLE IN ADLIB

Page 2-10

because of type incompatibility.

et dahirrint ka

elpos of chartelps

L ANGLE US (STREAMS BELLIO

e e 1.12% from thresholds to

nn 126 1 12884 1 198

to see here admit the ti

194 Standard 1989 december 2

na wa tenden ita espektokoa (h. 1878). 1872).

this was a light diff that gave the less

sty testers; part full by a WESSE

## CHAPTER 3 A CONTOUR MODEL FOR ADLIB

The chapter is intended to be an informal but unambiguous definition of the behavior of systems specified in ADLIB and SDL, and simulated under SABLE. The definition consists of three parts: a static contour model for ADLIB programs, a dynamic contour model for their execution under SABLE, and a simulation structure that defines the the various ADLIB primitives. For readers unfamiliar with contour models, an introductory tutorial is available in [JBJ71]. Also of interest is SIMULA Begin [BGM73] which is tuned to SIMULA67, and OREGANO [BD71]. However, the basic principles of contour models are fairly simple, and this description will avoid the more complex issues.

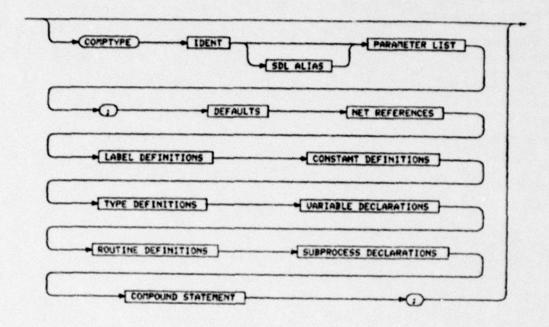

#### 3.1 CONTOUR MODELS

A contour model uses rectangles to represent scopes of program identifiers as defined by the user. A static contour model represents the way in which these scopes are nested in the source program, e.g. procedures within procedures, global and local variables etc. Such a drawing can be used to answer questions about identifier visibility, naming conflicts, and data hiding. The set of identifiers visible at any point in the model is determined by examining each enclosing contour in turn. Identifiers inside of non-nested contours can be accessed only through "access pointers" (ap's) that link one scope with another. Access pointers are used extensively in SIMULA 67 to perform a "remote

| KPK51712E   | LATELS CONSTANTS TYPES WRITYPES UNRIABLES CLOCK1        | ROUTINES | COMPTYPEL  | CHAIN BODY OF PROGRAM |

|-------------|---------------------------------------------------------|----------|------------|-----------------------|

| DESENSITIZE | CLOCKE                                                  | ROUTINEZ | COMPTYPE2  | PROGRAMI              |

| PERMIT      | C10013                                                  | ROUTINES | COMPTYPE3  | 2 13 (CO.P.)          |

| Inecisit    | COLUMN AND AND AND AND AND AND AND AND AND AN           |          |            |                       |

| STOPSIM     | end to distant<br>the strength of a<br>of the treatment |          |            |                       |

|             | sud isamptois                                           |          | er asmerni |                       |

FIGURE 1: STATIC CONTOUR HODEL OF AN ABLIS PROGRAM

access," which is where one process reaches into another and may directly alter internal attributes of it. This facility is not available to the ADLIB user directly because it invites hard-to-detect side effects and bad code structuring.

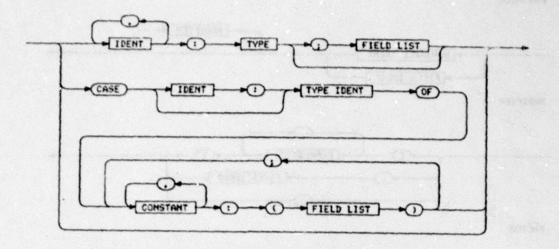

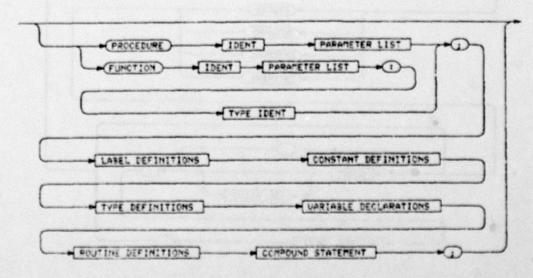

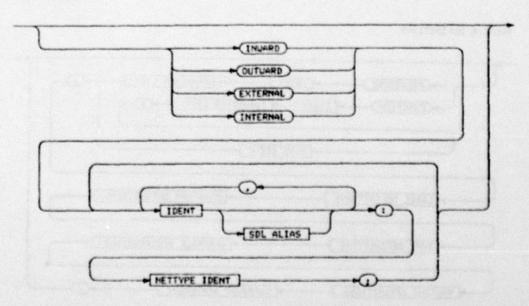

#### 3.2 STRUCTURE OF AN ADLIB PROGRAM

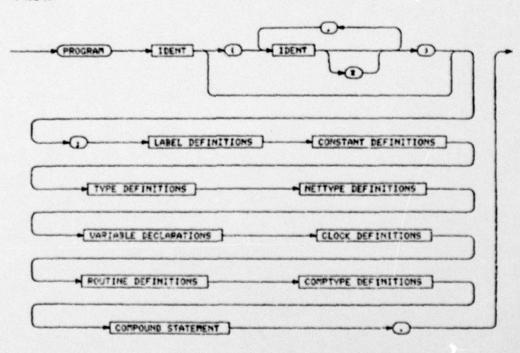

The static contour model for an ADLIB program is illustrated in figure 1.

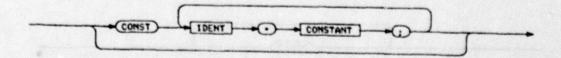

# 3.2.1 Global Identifiers

The model shown in figure 1 is not much different from the contour model of a PASCAL program. In the upper left hand corner of each rectangle appear the user defined labels, constants, and types and also the user declared variables\*. In addition, more rectangles may appear within a rectangle representing nested scopes.

In the outermost contour is the predeclared variable "time" which represents the simulation time. User assignment to this variable is illegal and is detected at during compilation. Contour 2 in figure 1 is the global level for the user. In it are found the user's global labels, constants, types, nettypes clocks, variables, routines\*\* and comptypes. The meanings of labels, constant and type definitions, are unchanged from PASCAL. There is also an algorithm associated with this

\*In this report, items that do not consume storage at runtime are said to be "defined", and items that do are said to be "declared". In particular, items that are defined do not appear inside of contours in the dynamic models.

\*\*Throughout this paper, the word "routine" is taken to mean procedure or function.

contour that could be called the "main body" of the program which can be used for initialization of the global variables, resetting files and such. This main body may not contain any ADLIB control primitives such as detach or waitfor, and may not access any component or net. During the execution of the program's main body, time and all clocks are identically zero. This code block may call global routines that call further routines recursively, just like the main body of an ordinary PASCAL program.

The inclusion of global variables into ADLIB is a concession to practicality and user convenience. Ideally, a design should not have any, since they might represent inter- component connections that have no physical correspondence. However, there are also many applications for global variables that do not violate the intended structure of For example, data collection and interpretation can be simplified if each component calls a routine that accepts intermediate results and stores them away in a global area for later analysis. On the other hand, global variables should not be used for intercomponent communication. This is what nets are intended for, just as parameters are intended for communicating with routines. It may be possible to detect such clandestine component interaction during compilation and prohibit it, just as there have been proposals to ensure that routines have no side effects. However, such mechanisms can generally be defeated and are invariably unpopular with programmers. The decision of how to use global variables is therefore left to the user.

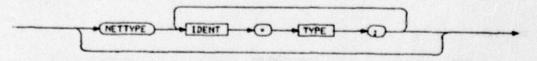

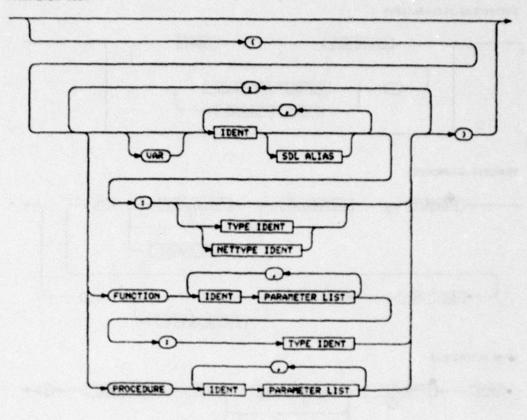

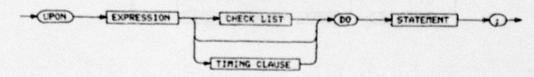

# 3.2.2 Nets And Nettypes

Nettype definitions are similiar to type definitions, except that they inform the compiler that it must be prepared to handle nets of this type. Nets are a concept that is unique to ADLIB, similiar to but not the same as ordinary program variables. Nets are allocated in a

different way from variables, and are interconnected with components and with the simulation support system. The various nettypes thus define the ways that the components are able to interact. importance of this for error detection and verification is discussed in [HDD79-1]. During simulation, the support system generates new data items of the various nettypes, compares them, does assignments to them, and dynamically regenerates the storage alloted to them. Nettypes (as opposed to ordinary types) must be used whenever nets are declared inside comptypes or are used as parameters to routines. Functions may not return nets, and nets may not appear on the left side of assignment (":=") statements. To update a net, the ASSIGN statement and the TRANSMIT subprocess facilities are provided. (This is somewhat like SIMULA 67, where updating a pointer requires a special syntax.) Any expression assigned to or compared with a net must be type compatible with the nettype of the net. Within a comptype, two types or nettypes are compatible if they are subranges of the same base type\*\*\*\*.

Whenever a net appears where an expression is called for, the current value of the net is used, in the same way that a program variable normally refects its value. When a net is used as the subject of an assign or transmit statement, its reference value is used. When a net is declared as a <u>var</u> parameter to a routine (i.e. the keyword var is used in the parameter declaration), the routine may <u>assign</u> to it. If the net is not marked as <u>var</u>, then the routine may access, but not update the value of the net.

<sup>\*\*\*\*</sup> This is not true in connections between components, because SABLE considers each nettype to be incompatible with all the other nettypes.

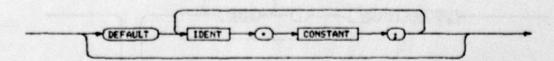

#### 3.2.3 Clocks

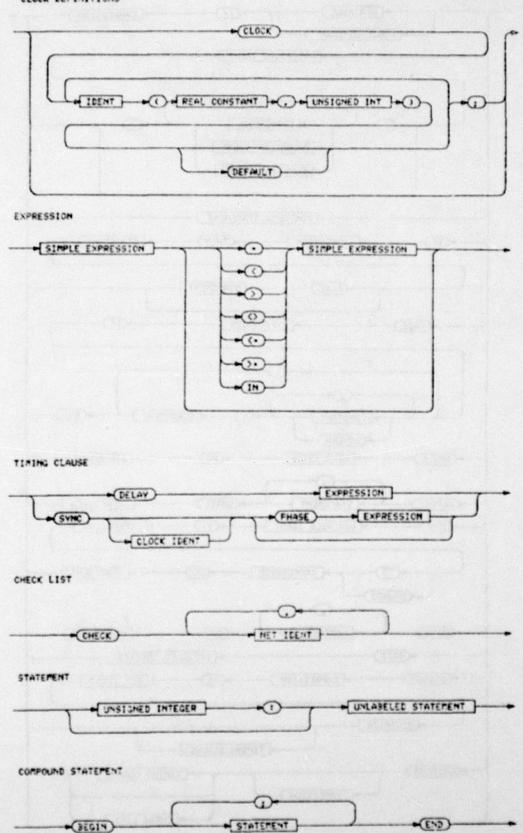

Following the nettype definitions, an ADLIB program may contain one or more clock definitions. These create functions that map the simulation time to an unsigned integer. Their syntax is:

CLOCK (clockname) ( (period) , (numphases) ) [ DEFAULT] ;

Symbolically, the function is:

<clkname> ==

(time/(<period>/<numphases>) ) MOD <numphases>

A clock function may be invoked anywhere that a variable integer expression is allowed. Clocks may also be used in timing clauses, which are explained in the next section.

# 3.2.4 Timing Clauses

Timing clauses may be used in assign, transmit and waitfor statements throughout an ADLIB program. A timing clause yields a time value at each evaluation. This time value is used in various ways as described later. There are two forms of timing clause: sync and delay.

#### 3.2.4.1 SYNC

The syntax for a sync timing clause is:

SYNC [ <clock name> [PHASE <integer phase number>]]

If <clock name> is omitted the clock marked "default" is used. If phase is omitted, phase 0 is assumed. The value returned by this sync timing clause is the next time when the specified clock will go through the

A CONTOUR MODEL FOR ADLIB STRUCTURE OF AN ADLIB PROGRAM

specified phase. Symbolically, this can be written as:

SYNC (cleck name) PHASE (integer phase number) ==

min ( (t' : real | (t' > time) AND <clockname>(t') = <integer phase number>)

#### 3.2.4.2 DELAY

The other timing expression used in ADLIB is the delay clause which has the syntax:

DELAY (real delay time)

This evaluates as:

time + <real delay time>

#### 3.2.5 Routines

Global routines are represented as in PASCAL and may include more routines nested within themselves. These routines may be freely called from inside any comptype, and may contain assign statements to net However, routines may not contain waitfor or detach statements. This restriction allows an enormous simplification and acceleration of the runtime support, because it sharply reduces the need for dynamic storage reclamation ("garbage collection") found in some simulation languages, (for example SIMULA 67). Since ADLIB provides other facilities such as subprocesses and better interprocess communication, it is hoped this restriction will not be overly constraining.

#### 3.2.6 Comptype Definitions

Following the global routine definition section is the "raison d'etre" for the whole ADLIB program, the component type definitions (comptypes). These are the only part of an ADLIB program visible to SABLE. Comptypes are similiar to routine definitions in that they

| PARAMETERS      |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NETS            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LABELS          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CONSTANTS       |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TYPES           |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| UARS            |                  | The State of the S |

| ROUTINES        | SOUTINES         | ROUTINES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |                  | 1000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 | Land to the same |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

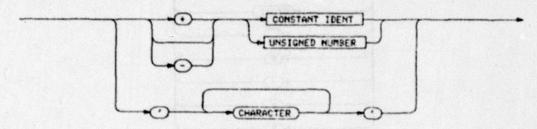

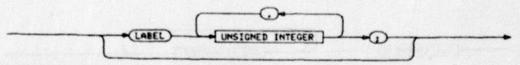

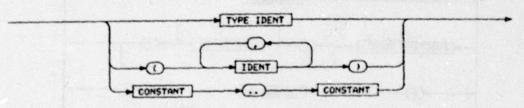

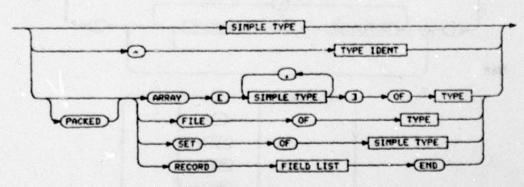

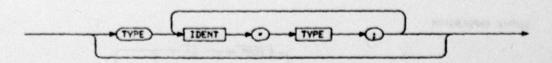

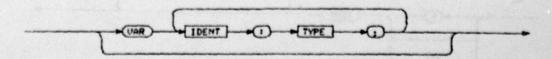

|                 |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |