Research and Development Technical Report **DELET-TR-78-2991-1**

# NANOSECOND PULSERS FOR MM WAVE TUBES

J. STOVER, N. KOMATSU HUGHES AIRCRAFT COMPANY GROUND SYSTEMS GROUP FULLERTON, CA 92634

**July 1979**

First Interim Report for Period September 1978

**Through January 1979**

DISTRIBUTION STATEMENT APPROVED FOR PUBLIC RELEASE: DISTRIBUTION UNLIMITED

Prepared for

**U.S. Army Electronics Technology & Devices Laboratory**

ERADCOM

US ARMY ELECTRONICS RESEARCH AND DEVELOPMENT COMMAND FORT MONMOUTH, NEW JERSEY 07703

79 07 16 034

COPY

# NOTICES

### Disclaimers

The citation of trade names and names of manufacturers in this report is not to be construed as official Government indorsement or approval of commercial products or services referenced herein.

### Disposition

Destroy this report when it is no longer needed. Do not return it to the originator.

1

a land the set of the set

UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE (Then Date Entered) READ INSTRUCTIONS BEFORE COMPLETING FORM PORT DOCUMENTATION PAGE 2. GOVT ACCESSION N RECIPIENT'S CATALOG NUMBER DELET TR-78-2991-1 - Selle First Interim Sep 78u Jan 79 NANOSECOND PULSERS FOR MM WAVE 0 -TUBES . FR79-14-353 . AUTHOR(.) DAAB97-78-C-2991 J. STOVER N. KOMATSU 10 .5 . PERFORMING ORGANIZATION NAME AND ADDRESS PROGRAM ELEMENT, PROJECT, TASK Hughes Aircraft Co., Ground System Group 62705 1901 W. Malvern 1L162705 AH 94 02 G1 Fullerton, CA 92634 16 PERONT DATE USA Electronics Technology & Devices Lab Jul 979 ATTN: DELET-BG 17 0 Fort Monmouth, N.I 07703 olling Office) IS. SECURITY CLASS. (of this n UNCLASSIFIED IS. DECLASSIFICATION/DOWNGRADING 16. DISTRIBUTION STATEMENT (of this Report) Approved for Public Release; Distribution Unlimited 17. DISTRIBUTION STATEMENT (of the abstract antored in Black 20, if different from Report) 18. SUPPLEMENTARY NOTES 19. KEY WORDS (Continue on reverse side if necessary and identify by block number) Avalanche Transistor VMOS FET Marx Modulator **Bipolar Junction Transistor (BJT)** ABSTRACT (Continue on reverse side if necessary and identify by block number) No decision has been reached as to the semiconductor device that will be used as the switching element for the nanosecond pulsers. The evaluation of avalanche transistors, VMOS FET, and LASS devices is continuing. A contributing factor to the lack of progress during the early months of the contract was program staffing problems and late arrival of critical test equipment. . DD , JAN 73 1473 EDITION OF I NOV 68 IS OBSOLETE UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE (Then Date Ent 172 370 Ju

# CONTENTS

| ABSTRACT                             | 2  |

|--------------------------------------|----|

| SUMMARY                              | 2  |

| PROGRAM OBJECTIVES                   | 2  |

| PROGRAM ORGANIZATION                 | 3  |

| NANOSECOND PULSER DESIGN ,           | 4  |

| COMPARISON OF SWITCH DEVICES TO DATE | 4  |

| DISTRIBUTION                         | 15 |

# List of Tables

| Table I  | Program Requirements            | 8 |

|----------|---------------------------------|---|

| Table II | Pulse Transformer Specification | 9 |

# List of Figures

100

| Figure 1 | Marx Modulator Configuration                                       | 10 |

|----------|--------------------------------------------------------------------|----|

| Figure 2 | Organization of the Nanosecond Pulser for MM Wave Tubes<br>Program | 11 |

| Figure 3 | Avalanche Transistor Test Setup                                    | 12 |

| Figure 4 | VMOS FET Test Setup                                                | 12 |

| Figure 5 | Marx Modulator                                                     | 13 |

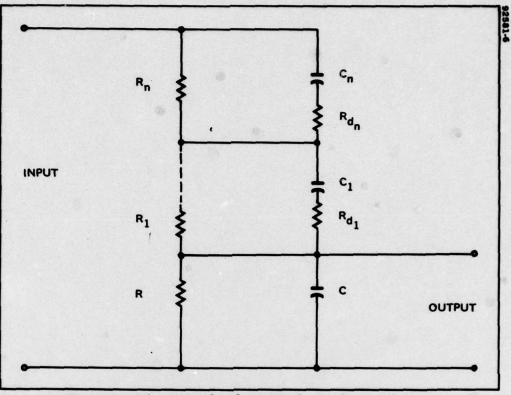

| Figure 6 | Schematic of Voltage Divider Under Development                     | 14 |

1

| Acce. | ssion For         |     |

|-------|-------------------|-----|

| NTIS  | GadacaI           | 1   |

| DDC 1 |                   |     |

| Unann | cunced            | HI  |

|       | lication          | ų   |

| By    |                   |     |

| Distr | ibution/          |     |

| Avai  | lability Cod      | les |

|       | Avail and/o       | r : |

| Dist. | special           |     |

| Λ.    |                   | 2.  |

| Ħ     | Section 2 Section |     |

| 1     |                   |     |

-

#### ABSTRACT

and the second of the second

No decision has been reached as to the semiconductor device that will be used as the switching element for the nanosecond pulsers. The evaluation of avalanche transistors, VMOS FET, and LASS devices is continuing. A contributing factor to the lack of progress during the early months of the contract was program staffing problems and late arrival of critical test equipment.

#### SUMMARY

Extensive time is being expended on the selection of the switching device as the selected switching device will probably be used on all three tasks (Task A, B, and C of the technical guidelines).

Initial consideration was given to the avalanche switching transistors because of their original success in obtaining fractional nanosecond rise and fall times in the 500-600 volt region in the 1963-65 era.

Next consideration was given to the VMOS FET operating in the avalanche mode. Only the avalanche mode of operation has been considered, since fractional nanosecond rise and fall times are desired. Normal operation of these devices yields rise and fall times in the 2-5 nanosecond region.

Lastly, consideration has been given to the LASS (Light Activated Silicon Switch), but this device still exists pretty much as a laboratory curiosity and it is doubtful that hardware deliveries could be predicted based upon this device.

Through this reporting period the only switching circuitry under consideration has been the Marx modulator circuit. This circuitry has been investigated using avalanche transistors as switching devices. Up to six series cascaded stages have been investigated.

#### PROGRAM OBJECTIVES

The efforts of this program are directed towards the development of three separate nanosecond pulsers for MM Wave Tubes. The performance requirements for the three tasks are listed in Table 1.

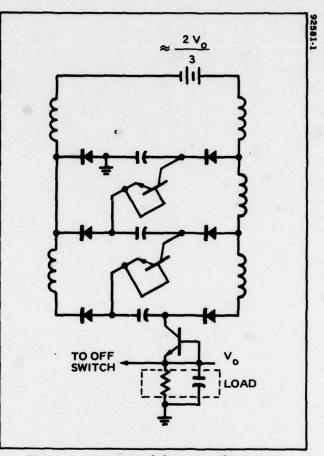

The basic configuration of the pulser will be that of a Marx modulator. This is shown in Figure 1. In this modulator configuration the capacitors are all charged in parallel from d-c charging power supply represented in Figure 1 by a battery through isolating impedances (here represented by inductors) and isolating diodes. The capacitors, upon reaching a certain preselected voltage level determined by the breakdown voltage of the switching device used, are effectively connected in series across the output load when the switching device is caused to move from a nonconducting to a conducting state. The switching device is represented in Figure 1 by an avalanche transistor. However the Marx circuit is not limited to the use of avalanche transistors, but can be used with avalanche diodes, LASS, conventional switching transistors, spark gaps and electron tube switches. The selection of the Marx circuit is primarily based upon the low voltage switching levels of existing semiconductor devices, and the modulator requirements of switching 2 to 13 kilovolt pulses into the load. Thus, the features of the Marx Circuit (that of charging in parallel and discharging in series) naturally lend themselves to semiconductor switching devices. Another consideration for selecting the Marx circuit was the fractional nanosecond rise and fall times achieved at the 7 kilowatt peak power level in 1963-65 era.

As presently envisioned, the Marx circuit would be utilized for the high speed sub-nanosecond switching portions of all three tasks.

#### PROGRAM ORGANIZATION

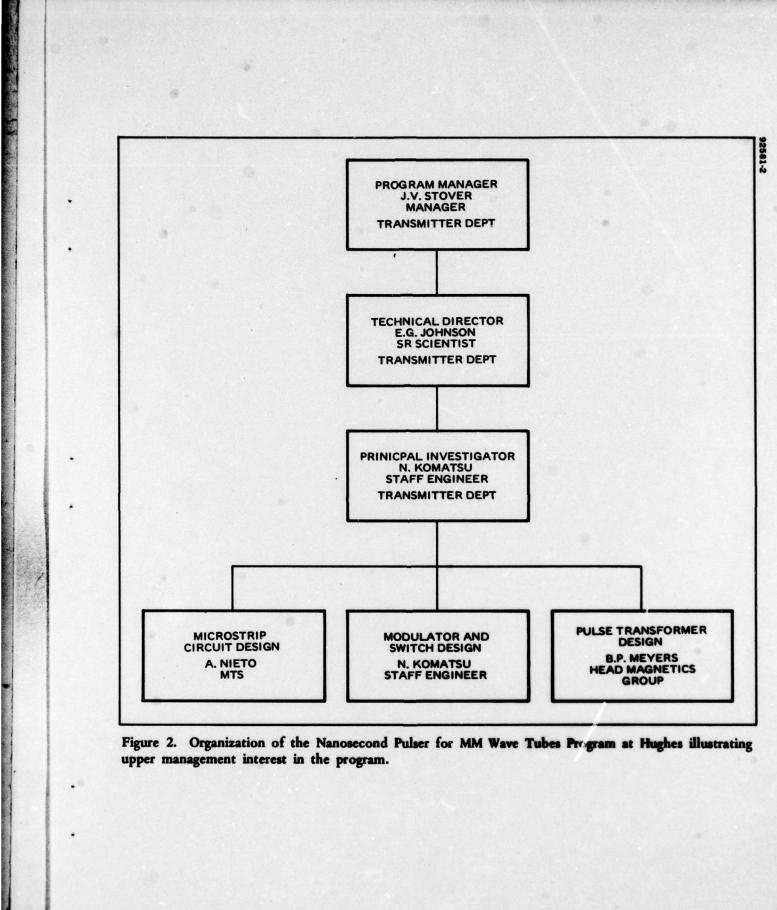

The importance of meeting the program requirements as contained in the contract technical guide lines, and the extreme technical challenge anticipated is mirrored in the project organization shown in Figure 2 where the top technical and managerial skills are brought to bear on this program.

Technically, the three major pulser tasks will be accomplished in three seperate, but serial developments. Initially, our technical assault will be focused upon the Task A requirements (the easiest of the three tasks) and the move into the more technically difficult tasks of Task B and lastly, Task C.

Our technical approach to each task will be first to select the switching device based upon switching speed, peak current per switching device, and peak voltage switched per device. Next, we will optimize the switching device performance in a switch element (a switch element being defined as that circuitry using one switching device). Then we will optimize the switch element performance in a switch module (a switch module being defined as the maximum number of series connected switch elements that can achieve the switching speeds required). This will be followed by the parallel connection of switch modules (if required) to obtain the peak switching power required. Lastly we will develop the matching network to match the modulator to the load.

With the nanosecond pulser development completed for a given task, we will then develop the power supplies, trigger circuitry, and other ancillary circuitry required.

Continually throughout this program efforts will be expended to develop the instrumentation and magnetic components required for this program.

A detailed organizational outline of this program is shown in Figure 2.

#### NANOSECOND PULSER DESIGN

#### Switching Device Selection

Three different types of switching devices are being considered for this program. These devices are the bipolar junction transistor (BJT) operating in the avalanche mode, the VMOS FET, and the LASS (Light Activated Silicon Switch).

Both BJTs and transistors specifically made to operate in the avalanche mode have been tested. The two BJTs which have been tested were the 2N3020 and 2N2219A. The slower switching speed of the 2N3020 eliminated that device from consideration. The 2N2219A transistors tested were manufactured by Raytheon, National, and Fairchild with the highest yield of acceptable devices (25%) coming from those manufactured by Fairchild. VMOS FETs presently manufactured by Siliconix have been tested to determine if the device exhibits an avalanche mode of operation. Contrary to Siliconix technical representatives opinions that their VMOS FETs would not operate in the avalanche mode, three FETs (the VMP1, the 2N6661, and the 2N6658) operated in the avalanche mode by applying a trigger to the gate with drain to source voltage beyond the absolute maximum ratings. Rise times from 1.5 to 2.0 nanoseconds have been achieved. Further evaluation of the rise time must be made using an improved gate driving source and triggering of the drains of the devices must be investigated. A fourth unit, the VMP4 VMOS FET which incorporates r-f type construction features failed to avalanche. The reasons why the first three types of VMOS FETs avalanched successfully while the VMP4 did not, has not been determined. When sufficient data is accumulated a Siliconix technical representative will be contacted to discuss this application and resolve the outstanding questions.

Contact with the Westinghouse representative indicates the LASS is, as of now, a laboratory device and not a production item. Use of other devices such as the RBDT was suggested but these units will not operate at the nanosecond turn on region nor at the pulse repetition rate of 20 KHz. Periodic checks on the LASS will be made during the program to see if there is any change in the status of the device.

#### COMPARISON OF SWITCH DEVICES TO DATE

Present indication is that the Raytheon avalanche transistors, the AVK and possibly the AVG will be a suitable choice for the switching element. With all performance characteristics near equal, the advantages of utilizing transistors in the avalanche mode with avalanche parameter specified far outweighs the use of BJTs that may show favorable avalanche parameters today, and uncertain device parameters in the future.

Further evaluation of the VMOS FET must be performed on the device itself as well as the device implemented in a Marx configuration before the choice between the avalanche transistor and VMOS FET is finalized.

#### A. Switch Element Development

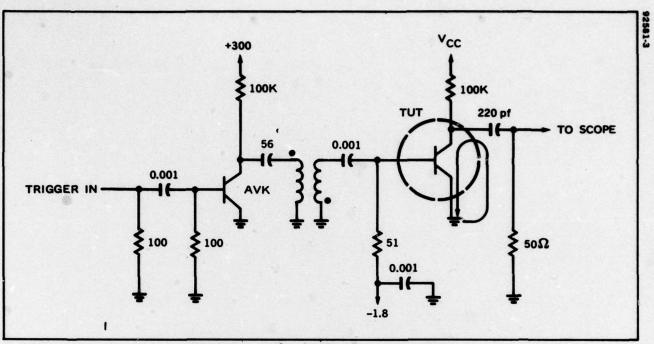

The individual switching devices were tested in the circuitry shown in Figure 3. Initially, with no trigger applied, Vcc was raised to the voltage where self sustained switching of the transistor under test (TUT) occurred, thereby determining the avalanche breakdown voltage of the device. Setting Vcc below the avalanche breakdown voltage by approximately 10 volts yields a stable quiecent operating point. The triggers are then applied and the dI/dT or the rise time of the transistor output current is measured across a 50 ohm load.

Caution is exercised in the layout of the loop containing the TUT, discharge capacitor, and the load resistor to minimize stray circuit inductance that will effectively increase the current rise time of the device.

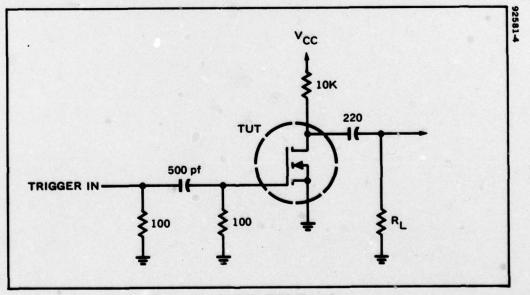

The test of the VMOS FETs thus far has been to determine whether the device exhibits some form of avalanche characteristics. Three out of the four types of FETs tested in the configuration shown in Figure 4 exhibited avalanching.

The avalanche voltage of the device was determined in the same manner used on the BJTs. The triggering of the device into avalanche was far more critical on the FETs than the BJTs. The current rate of rise of the FET devices ranged near the 2ns region. Additional investigation is required to determine the avalanche mechanism, the turn on problem encountered, and the possible rise time improvement with a faster trigger pulse applied to the gate.

Nothing has been done regarding the LASS device other than contacting Westinghouse. The response from the vendor indicated this switching device is a laboratory device, not ready yet for circuitry development.

#### B. Switch Module Development

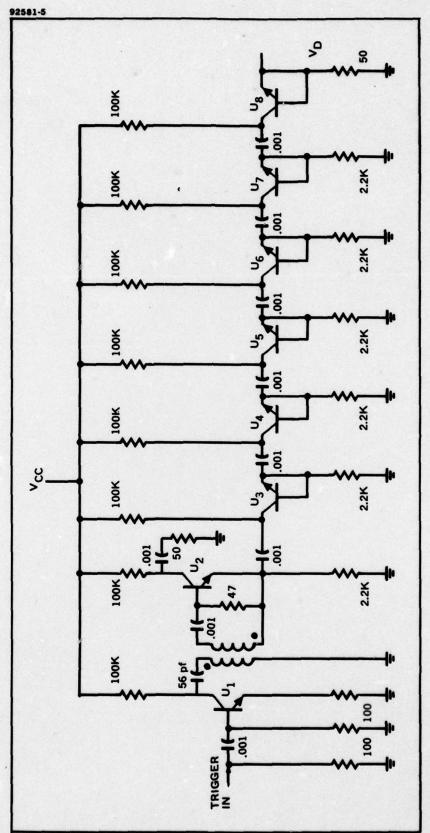

The Marx modulator configuration shown in Figure 5 was fabricated and tested. The output voltage (Vo) of the unit was approximately one half of that specified (600V) for the unit illustrated in the proposal. The decreased voltage output is attributed to the impedance matching required between the output load and series switch arrangement. Reflections caused by a mismatch affects the rise time of the output voltage.

Operation of the Marx modulator switch was achieved with a set (U1 - U8) of 2N2219A BJTs as well as a set of Raytheon's line of avalanche transistors, the AVKs. Aside from a slight change in Vcc, no noticeable difference of the output was noted.

As soon as more tests are performed on the individual VMOS FET devices, they will be incorporated into the above described Marx modulator configuration.

#### C. Pulse Transformer Development

The preliminary requirements for the pulse transformer needed for the Task C requirement are shown in Table III.

The following types of designs have been considered:

1) Bifilar

- a) Twisted Pair

- b) Coaxial

- 2) Coaxial Line

- 3) Tapered Transmission Line

- 4) Helical Transmission Line

Initially work was begun by considering a simple 1:1 turns ratio pulse transformer. First, pulse transformers were wound using a Ferroxcube 1FI9 ferrite U core with a 0.5 inch outside diameter wound with approximately 18 inches of bifilar winding length driving a 50 ohm load. This gave a very poor rise time.

Next this was compared to the rise time degradation obtained by pulsing 30 inches of RG188U coaxial cable where a rise time of 27 nanoseconds was measured. There it was found that the coaxial cable approach gave improved performance. Tapered Transmission Line and Helical Transmission Line pulse transformers as well as the Coaxial Bifilar (also called a Balun) look promising.

An extensive literature search is still underway to determine the present state of the art. Present thoughts point to the use of a coaxial line pulse transformer using air as the dielectric. Recent literature states that faster rise times are achieved with this type of line.

#### D. Voltage Divider for Nanosecond Pulser Program

During this initial program period, requirements for a voltage divider test probe were generated. The following is a list of these requirements:

| 5000:1                 |

|------------------------|

| 2000 Volts, 100 K ohms |

| ±1 Volt, 50 ohms       |

| 100 picosec.           |

|                        |

A commercially available probe with these specifications has not been found. It was, therefore, decided to begin an in-house design of the required voltage divider probe. Conversations with probe manufacturers revealed a pessimism toward the success of our planned effort. A literature search revealed a lack of practical design information applicable to our needs. With this in mind, it became clear that a novel and yet basic approach to the probe design must be attempted; an approach which would be flexible enough to allow design changes dictated by changing pulser circuit monitoring needs. The following is a list of design criterion with which we began our basic design:

- The circuit should be as small as practical to reduce stray and dimensional capacitance and inductance effects.

- The circuit should be assembled using microwave transmission line to ease impedance matching.

- Microwave circuit components should be used in keeping with a high frequency design approach.

- Lead length from test point to probe and ground to ground should be minimized to reduce loop inductance.

- A 50 ohm output impedance compatible with various transmission lines and test equipments, is recommended.

- Input impedance must be high enough to prevent pulser circuit loading.

With the above in mind, it was decided to build a stripline voltage divider utilizing microwave chip components on a 50 ohm line. The initial divider circuit to be investigated is shown in Figure 6.

**Eiven;**

$$R_d$$

$R_1 = R_2 = R_n$

$C_1 = C_2 = C_n$

Resistor R<sub>d</sub> is an optional overshoot damping resistor. The divider ratio is

$$\frac{\frac{C_n}{n}}{\frac{C_n + C}{n}} = \frac{R}{nR_n + R}$$

The frequency compensation criterion is  $R_n C_n = RC$

Also  $C_n$  must be small compared to the 30 pf pulser load requirement.

Component samples have been requested for evaluation in divider type circuits.

During the next reporting period the following is planned:

- 1. Investigate the characteristics of the three basic divider circuits; resistive, capacitive, and mixed, in relation to our proposed design.

- 2. Investigate the causes and effects of stray and residual inductance and capacitance in our divider circuit.

- 3. Determine optimum values for  $R_d$ ,  $R_n$ , and  $C_n$ .

- 4. Order divider and probe components.

- 5. Assemble prototype probe for performance evaluation.

- 6. Optimize probe design and utilize in support of Nanosecond Pulser Program.

|                                       | Task A | Task B   | Task C |

|---------------------------------------|--------|----------|--------|

| Output Voltage (kilovolts)            | 1.2    | 2        | 12     |

| Peak Output Current,<br>min (amperes) | 60     | 108      | 600    |

| Rise and Fall Times<br>(nanoseconds)  |        | 0.5      |        |

| Load Capacity<br>(picofarads)         |        | 30       |        |

| Pulse Width<br>(nanoseconds)          |        | 4 to 100 | -      |

| Jitter, max<br>(nanoseconds)          |        | 0.5      |        |

| PRR                                   |        | 20 kHz   |        |

| Isolation From Ground<br>(kilovolts)  | ii     | 15       | 25     |

| Input Voltage (volts dc)              |        | 28       |        |

| TABLE | L | PROGRAM | REQUIREMENTS |

|-------|---|---------|--------------|

|       |   |         |              |

| Turns Ratio        | 1:6                               |

|--------------------|-----------------------------------|

| Output .           | 12 Kv into 12 KΩ Shunted by 30 pf |

| Input              | 2 Kv                              |

| Rise Time (10-90%) | 0.1 nsec                          |

| Fall Time (90-10%) | 0.2 nsec                          |

| PRR                | 20 kHz                            |

| Pulse Width        | 2, 4, 10, 20, 50, 100 nsec        |

## TABLE II. PULSE TRANSFORMER SPECIFICATION

State State State State

W - W

2.

Figure 1. Marx Modulator Configuration

Figure 2. Organization of the Nanosecond Pulser for MM Wave Tubes Program at Hughes illustrating upper management interest in the program.

Figure 3. Avalanche Transistor Test Setup

Figure 4. VMOS FET Test Setup

12

and the second se

· ·

Figure 5. Marx Modulator

Figure 6. Schematic of Voltage Divider Under Development

#### DISTRIBUTION

Copies 12 1

1

1

1

1

1

1

2

Defense Documentation Center ATTN: DDC-TCA Cameron Station (Bldg 5) Alexandria, VA 22314

Code R123, Tech Library DCA Defense Comm Engrg Ctr 1800 Wiehle Ave Reston, VA 22090

Office of Naval Research Code 427 Arlington, VA 22217

Director Naval Research Laboratory ATTN: Code 2627 Washington, DC 20375

Cdr, Naval Surface Weapons Center White Oak Laboratory ATTN: Library Code WX-21 Silver Spring, MD 20910

Rome Air Development Center ATTN: Documents Library (TILD) Griffiss AFB, NY 13441

Hq, Air Force Systems Command ATTN: DLCA Andrews AFB Washington, DC 20331

Commander, MIRADCOM Redstone Scientific Info Center ATTN: Chief, Document Section Redstone Arsenal, AL 35809

Director, Ballistic Missile Defense Advanced Technology Center ATTN: ATC-R, PO Box 1500 Huntsville, AL 35807

Commander US Army Intelligence Center & School ATTN: ATSI-CD-MD Fort Huachuca, AZ 85613

Copies

1

2

1

1

2

1

1

1

1

Commander HQ, Fort Huachuca ATTN: Technical Reference Div Fort Huachuca, AZ 85613

Commander US Army Electronic Proving Ground ATTN: STEEP-MT Fort Huachuca, AZ 85613

Deputy for Science & Technology Office, Assist Sec Army (R&D) Washington, DC 20310

Commandant US Army Signal School ATTN: ATZ-HET-L Fort Gordon, GA 30905

Director of Combat Developments US Army Armor Center ATTN: ATZK-CD-MS Fort Knox, KY 40121

> Cdr, Harry Diamond Laboratories ATTN: Library 2800 Powder Mill Road Adelphi, MD 20783

Director US Army Ballistic Research Labs ATTN: DRXBR-LB Aberdeen Proving Ground, MD 21005

Harry Diamond Laboratories, DA ATTN: DELHD-RCB (Dr. J. Nemarich) 2800 Powder Mill Road Adelphia, MD 20783

Director US Army Materiel Systems Analysis Acty ATTN: DRXSY-T Aberdeen Proving Ground, MD 21005

Copies

1

1

2

1

1

1

Director US Army Materiel Systems Analysis Actv ATTN: DRXSY-MP Aberdeen Proving Ground, MD 21005

- Cdr, AVRADCOM ATTN: DRSAV-E PO Box 209 St. Louis, MO 63166

- Commander, ARRADCOM ATTN: DRDAR-LCA-PD Dover, NJ 07801

- 1 TRI-TAC Office ATTN: TT-SE Fort Monmouth, NJ 07703

- 1 Cdr, US Army Avionics Lab AVRADCOM ATTN: DAVAA-D Fort Monmouth, NJ 07703

1 Project Manager, FIREFINDER ATTN: DRCPM-FF Forth Monmouth, NJ 07703

- 1 Commander Project Manager, SOTAS DRCPM-STA Fort Monmouth, NJ 07703

- Cdr, US Army Research Office ATTN: DRXRO-IP PO Box 12211 Research Triangle Park, NC 27709

- Cdr, US Army Research Office ATTN: DRXRO-PH (Dr. R.J. Lontz) PO Box 12211 Research Triangle Park, NC 27709

- Cdr, US Army Signals Warfare Lab ATTN: DELSW-OS Vint Hill Farms Station Warrenton, VA 22186

#### Copies

1

1

1

1

1

1

1

1

1

Commander US Army Mobility Eqp R&D Cmd ATTN: DRDME-R

ATTN: DRDME-R Fort Belvoir, VA 22060 CDR, PM Concept Analysis Centers

ATTN: DRCPM-CAC Arlington Hall Station Arlington, VA 22212

Cdr, Night Vision & Electro-Optics Lab ERADCOM ATTN: DELNV-D Fort Belvoir, VA 22060

Chief Office of Missile Electronic Warfare Electronic Warfare Lab, ERADCOM White Sands Missile Range, NM 88002

Cdr, Harry Diamond Laboratories ATTN: DELHD-CO 2800 Powder Mill Road Adelphi, MD 20783

Commander ARRADCOM DRDAR-TSB-S Aberdeen Proving Ground, MD 21005

Cdr, ERADCOM ATTN: DRDEL-CG: -CD; -CS (IN TURN) 2800 Powder Mill Road Adelphi, MD 20783

Cdr, ERADCOM ATTN: DRDEL-CT 2800 Powder Mill Road Adelphi, MD 20783

Cdr, ERADCOM ATTN: DRDEL-PAO 2800 Powder Mill Road Adelphi, MD 20783

Copies

1

1

1

Cdr, ERADCOM ATTN: DRDEL-SB; -AP (IN TURN) 2800 Powder Mill Road Adelphi, MD 20783

CDR, ERADCOM ATTN: DRDEL-PA; -ILS; -ED (IN TURN) 2800 Powder Mill Road Adelphia, MD 20783

HQS, Harry Diamond Laboratories ATTN: DELHD-TD (DR. W.W. CARTER) 2800 Powder Mill Road Adelphi, MD 20783

Commander US Army Electronics R&D Command Fort Monmouth, NJ 07703

1 DRDEL-SA 1 DELEW-D 3 DELCS-D 1 DELET-D 1 DELET-DD 2 DELET-DT 5 DELET-BG 1 DELSD-D 1 DELSD-AS 1 DELSD-L (Tech Library) 2 DELSD-L-S (Stinfo) 25 **Originating Office**

> Commander US Army Communications R&D Command Fort Monmouth, NJ 07703

1 DRDCO-COM-RO 1 USMC-LNO 1 ATFE-LO-EC

RALICE

Copies

112

2

1

2

2

1

1

Commander US Army Communications & Electronics Materiel Readiness Command Fort Monmouth, NJ 07703

| DRSEL-PL-ST |

|-------------|

| DRSEL-MA-ME |

| DRSEL-PA    |

MIT - Lincoln Laboratory ATTN: Library (RM A-082) PO Box 73 Lexington, MA 02173

NASA Scientific & Tech Info Facility Baltimore/Washington Intl Airport PO Box 8757, MD 21240

Advisory Group on Electron Devices 201 Varick Street, 9th Floor New York, NY 10014

Advisory Group on Electron Devices ATTN: SECY, Working Group D (Lasers) 201 Varick Street New York, NY 10014

TACTEC Batelle Memorial Institute 505 King Avenue Columbus, OH 43201

EG&G Inc 35 Congress Street Salem, MA 01970