GENERAL ELECTRIC CORPORATE RESEARCH AND DEVELOPMENT --ETC F/G 20/12

INTERFACE DOPING OF MNOS TRANSISTORS.(U)

JUN 77 C A NEUGEBAUER, M M BARNICLE

SRD-77-108

AFAL-TR-77-111

NL AD-A067 857 UNCLASSIFIED OF2 AD A067 57 E F 接触

DOC FILE COPY

M'agina a

SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered) **READ INSTRUCTIONS** REPORT DOCUMENTATION PAGE BEFORE COMPLETING FORM 2. GOVT ACCESSION NO. 3. RECIPIENT'S CATALOG NUMBER AFAL TR-77-111 TITLE (and Subtitle) Interim Technical Report 1 Apr 2 1076 - 31 Mar 2077 INTERFACE DOPING OF MNOS TRANSISTORS hase C.A. Neugebauer M.M. Barnicle F33615-76-C-1035 PROGRAM ELEMENT, PROJECT, TASK AREA STORK UNIT TEMBERS PERFORMING ORGANIZATION NAME AND ADDRESS General Electric Company Corporate Research and Development Project 230 Schenectady, NY 12345 11. CONTROLLING OFFICE NAME AND ADDRESS 12. REPORT DAT Air Force Avionics Laboratory (AFAL/DHR) June 1077 Air Force Wright Aeronautical Laboratories 111 Wright Patterson AFB, Ohio 45433 ntealling Office) 15. SECURITY CLASS. (of this report) 14. MONITORING AGENCY NAME & ADDRESS(If different to Unclassified 15a, DECLASSIFICATION/DOWNGRADING 16. DISTRIBUTION STATEMENT ( This Report) Approved for public release; distribution unlimited. 17. DISTRIBUTION STATEMENT (of the abstract entered in Block 20, if different from Repo 18. SUPPLEMENTARY NOTES 19. KEY WORDS (Continue on reverse side if necessary and identify by block number) Interface Doping, MNOS, Semiconductor Memory, Write Characteristics, Retention, Endurance, Nitride, Fowler-Nordheim Tunneling, Memory Window. 20. ABSTRACT (Continue on reverse side if necessary and identify by block number) This Interim Technical Report describes the progress for the 1 April 1976 to March 1977 period of Phase I of the Interface Doping of MNOS program. Use of Cr, W, Pt, Ni, Pd and Ir as interface dopant in monolayer quantities between an oxide layer of Fowler-Nordheim tunneling thickness and 300-500A of Si3N4 gives MNOS memory retention of electrons of many centuries even at elevated temperatures, while retaining high write speed. Endurance is limited to 103 write/erase cycles. DD 1 JAN 73 1473 EDITION OF I NOV & IS OBSOLETE

406617

SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered)

1000

|         | TABLE OF CONTENTS                        | ACCESSION for                                       |  |

|---------|------------------------------------------|-----------------------------------------------------|--|

| SECTION |                                          | NTIS White Section D DDC Buff Section D UNANNOUNCED |  |

| I       | INTRODUCTION                             | JUST FICATION                                       |  |

| II      | APPROACH                                 | BY                                                  |  |

| III     | INTERFACE-DOPED MNOS DEVICE FABRICATION  | DISTRIBUTION/AVAILABILITY CODES  DI SP. CIAL        |  |

| IV      | INTERFACE DOPING                         | A                                                   |  |

|         | Selection of Dopants                     | 01                                                  |  |

|         | Dopant Concentration                     | 3 90237 3983308                                     |  |

|         | Doping Conditions                        |                                                     |  |

|         | Vacuum Deposition of Metal Dopants       | by Evaporation                                      |  |

|         | Tungsten Oxide Evaporation               | Departments of E                                    |  |

|         | Dopant Deposition by Sputtering          |                                                     |  |

|         | Dopant Deposition by Solution Dopin      | ng                                                  |  |

|         | Analytical Procedures                    | upi osvienduma/                                     |  |

| v       | WRITE CHARACTERISTICS                    |                                                     |  |

| 98      | Write Mechanisms and Write Curves        |                                                     |  |

|         | Comparison with Undoped Devices          |                                                     |  |

|         | Dependence of Write Speed on Dopani      | Concentration                                       |  |

|         | Dependence of Write Speed on Oxide       |                                                     |  |

|         |                                          | Inickness                                           |  |

|         | Temperature Dependence                   |                                                     |  |

|         | Write Characteristics of Devices Do      | oped by Sputtering                                  |  |

|         | Summary of Write Characteristics         |                                                     |  |

| VI      | DOPANT CONCENTRATION DEPENDENCE OF MEMOI | RY WINDOW                                           |  |

| VII     | MEMORY RETENTION                         |                                                     |  |

|         | Stored Charge Decay as a Function of     | of Time                                             |  |

|         | The Effect of Oxide Thickness            |                                                     |  |

## TABLE OF CONTENTS (Cont'd)

| SECTION  |                                                     | PAGE |

|----------|-----------------------------------------------------|------|

|          | The Effect of Dopant Concentration                  | 66   |

|          | Temperature Dependence                              | 70   |

|          | The Effect of High Positive Applied Bias            | 74   |

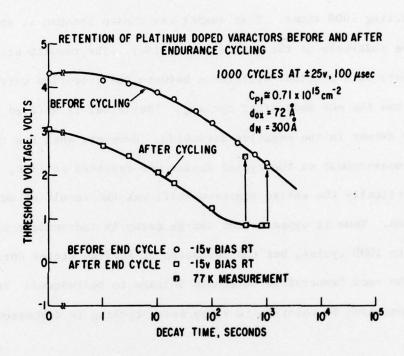

|          | The Effect of Endurance Cycling                     | 77   |

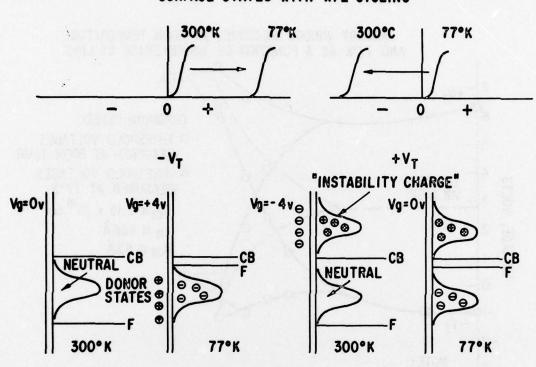

| VIII     | FAST SURFACE STATE GENERATION                       | 79   |

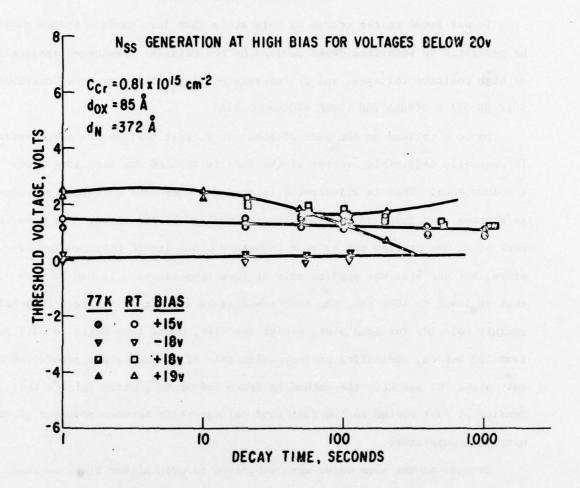

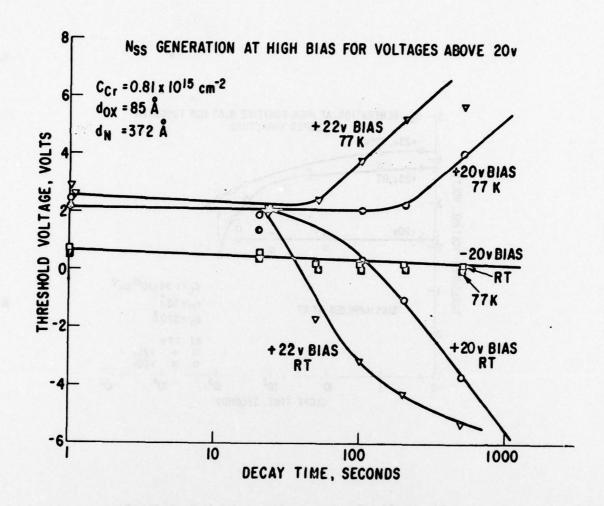

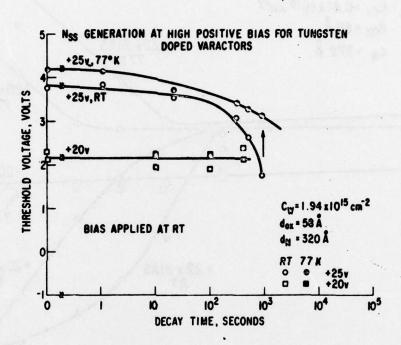

|          | Surface State Generation Under Prolonged Bias       | 79   |

|          | Surface State Generation Due to Write/Erase Cycling | 83   |

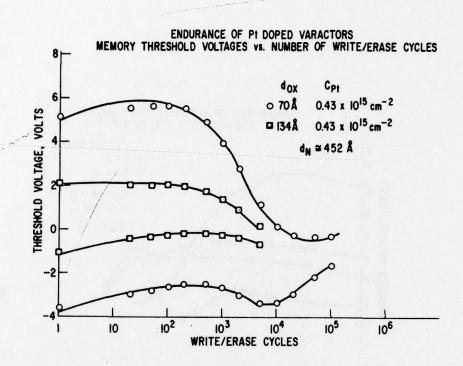

| IX       | ENDURANCE                                           | 88   |

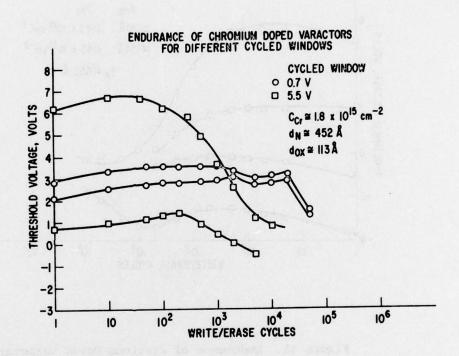

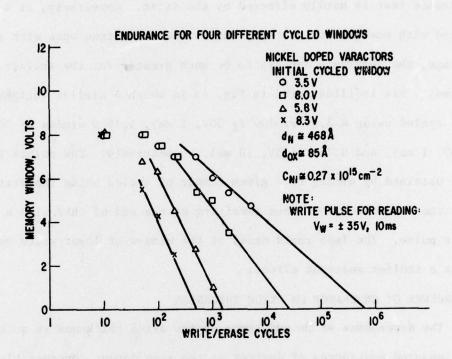

|          | Dependence of Endurance on Window Being Cycled      | 88   |

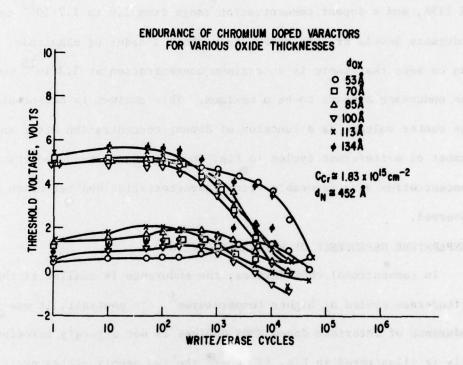

|          | Dependence on Endurance on Oxide Thickness          | 91   |

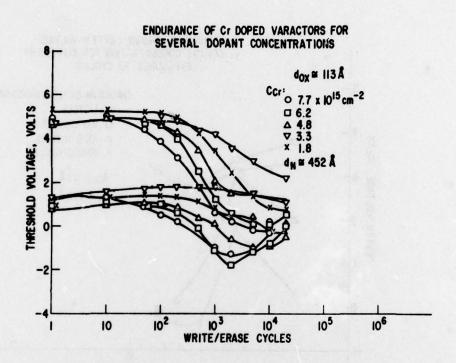

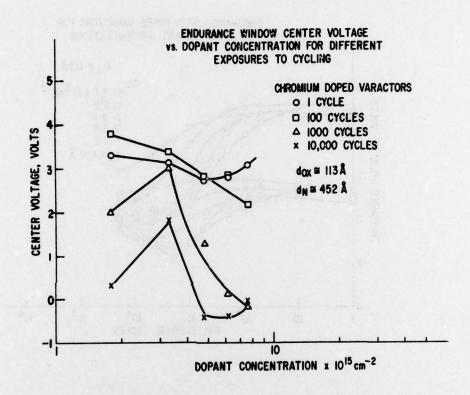

|          | Dependence of Endurance on Dopant Concentration     | 94   |

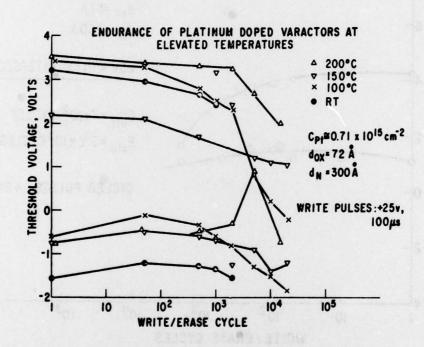

|          | Temperature Dependence of Endurance Cycling         | 94   |

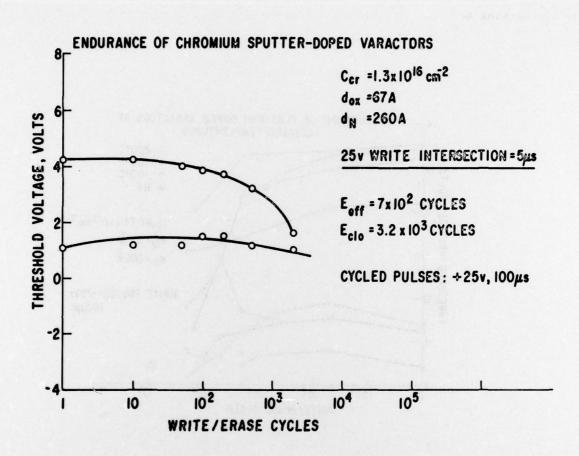

|          | Endurance of Devices Doped by Sputtering            | 94   |

|          | Comparison of Endurance for Various Dopants         | 99   |

| x        | CONCLUSIONS                                         | 105  |

| REFERENC | DES                                                 | 109  |

## LIST OF ILLUSTRATIONS

| FIGURE |                                                             | PAGI |

|--------|-------------------------------------------------------------|------|

| 1      | Conventional vs. Interface-Doped MNOS                       | 2    |

| 2      | Stepped Oxide Varactor Wafer and Evaporated Dopant Profile  | 5    |

| 3      | Oxide Thickness vs. Time                                    | 11   |

| 4      | E-Beam Evaporation Method of Interface Doping               | 19   |

| 5      | Top View of Wafer Holder                                    | 20   |

| 6      | Auger Spectrum of Tungsten Doped Surface                    | 24   |

| 7      | Tungsten Auger Peak Amplitude vs. Quartz Crystal Coverage   | 25   |

| 8      | Threshold Voltage Changes in Interface-Doped MNOS           | 28   |

| 9      | Schematic of Write Characteristics                          | 29   |

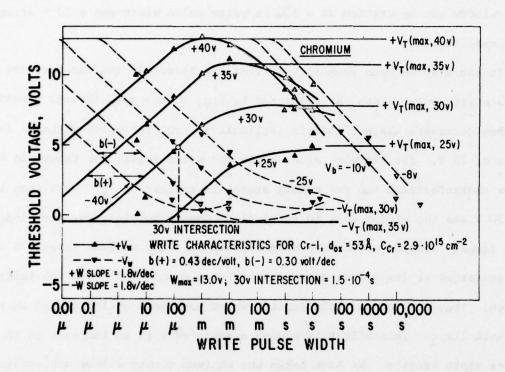

| 10     | Write Characteristics of Chromium Doped Varactors           | 31   |

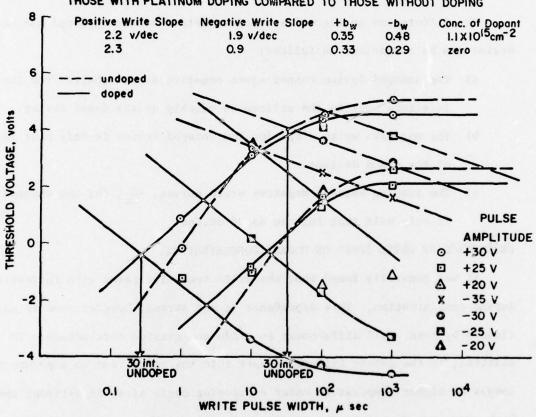

| 11     | Write Characteristic Curves of Doped and Undoped Devices    | 33   |

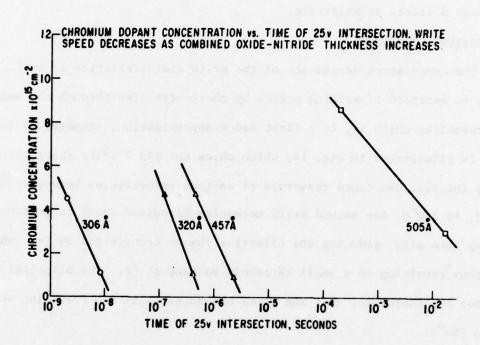

| 12     | Cr Dopant Concentration vs. Time of 25V Intersection        | 35   |

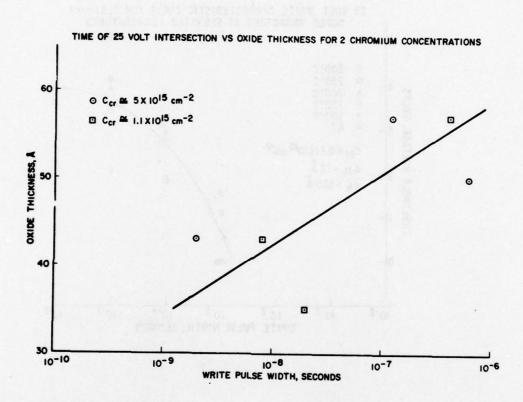

| 13     | Time of 25V Intersection vs. Oxide Thickness                | 37   |

| 14     | 25V Write Characteristic Curve at Elevated Temperatures     | 38   |

| 15     | Write Characteristics of Varactors Doped with Sputtered     |      |

|        | Nickel                                                      | 40   |

| 16     | Write Characteristics of Varactors Doped with Sputtered     |      |

|        | Chromium                                                    | 41   |

| 17     | Platinum Saturation Memory Window vs. Dopant Concentration  | 46   |

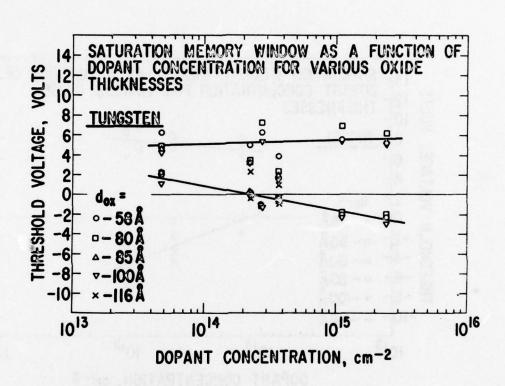

| 18     | Tungsten Saturation Memory Window vs. Dopant Concentration  | 47   |

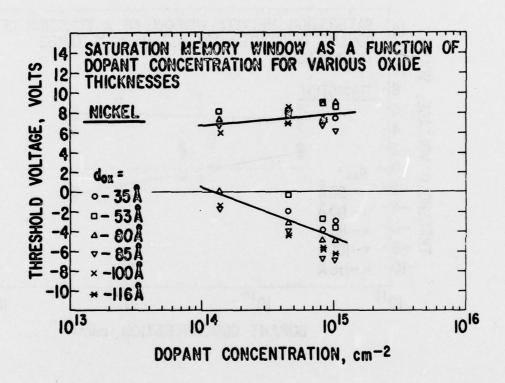

| 19     | Nickel Saturation Memory Window vs. Dopant Concentration    | 48   |

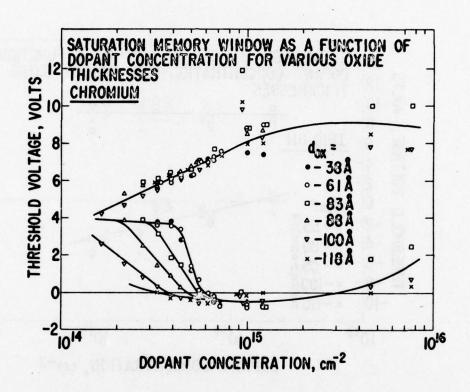

| 20     | Chromium Saturation Memory Window vs. Dopant Concentration  | 49   |

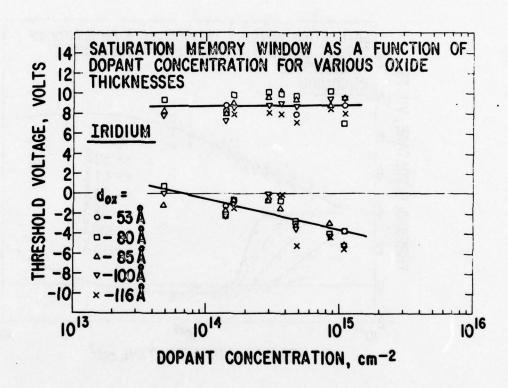

| 21     | Iridium Saturation Memory Window vs. Dopant Concentration   | 50   |

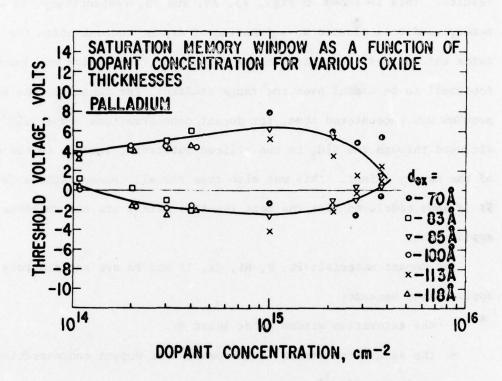

| 22     | Palladium Saturation Memory Window vs. Dopant Concentration | 51   |

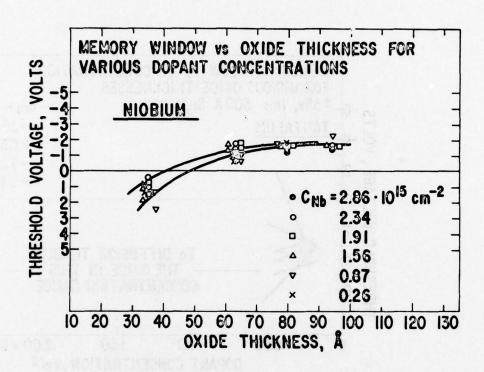

| 23     | Niobium Memory Windows vs. Oxide Thickness                  | 53   |

## LIST OF ILLUSTRATIONS (Cont'd)

| FIGURE |                                                                     | PAGE |

|--------|---------------------------------------------------------------------|------|

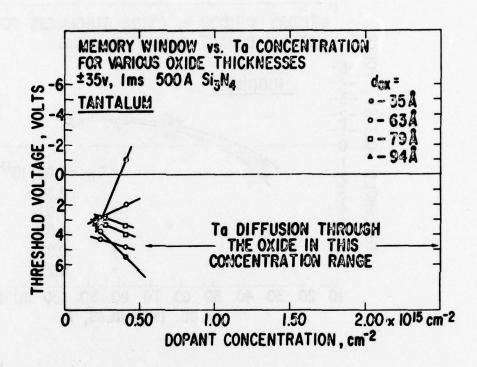

| 24     | Memory Window vs. Tantalum Concentration                            | 54   |

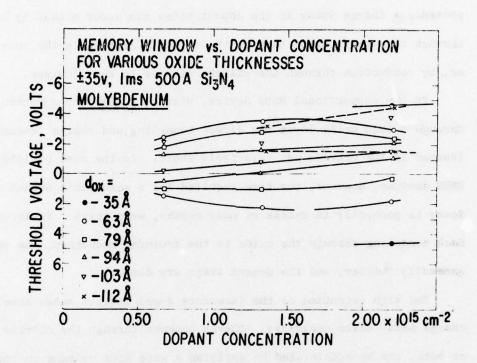

| 25     | Molybdenum Memory Window vs. Dopant Concentration                   | 55   |

| 26     | Retention of Chromium                                               | 58   |

| 27     | $t_{R}$ and $	au_{relax}$ vs. Oxide Thickness                       | 65   |

| 28     | τ <sub>relax</sub> (V <sub>app</sub> ) vs. Dopant Concentration     | 69   |

| 29     | Chromium Retention at Four Temperatures                             | 71   |

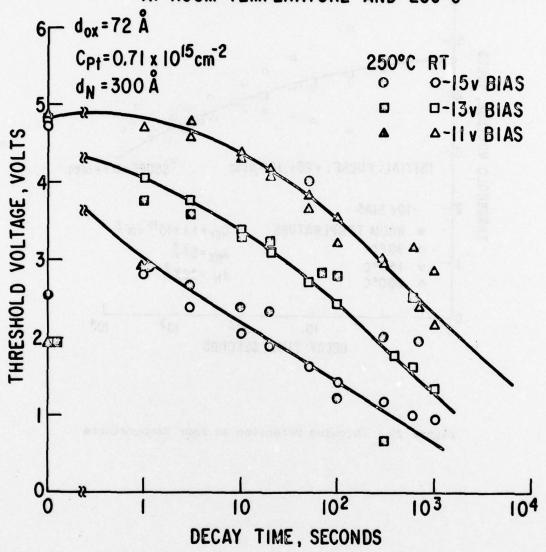

| 30     | Platinum Retention at Room Temperature and 250°C                    | 72   |

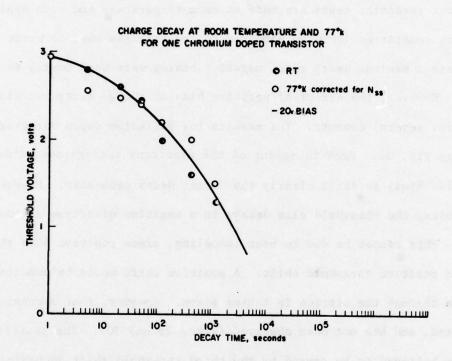

| 31     | Charge Decay at Room Temperature and 77°K                           | 73   |

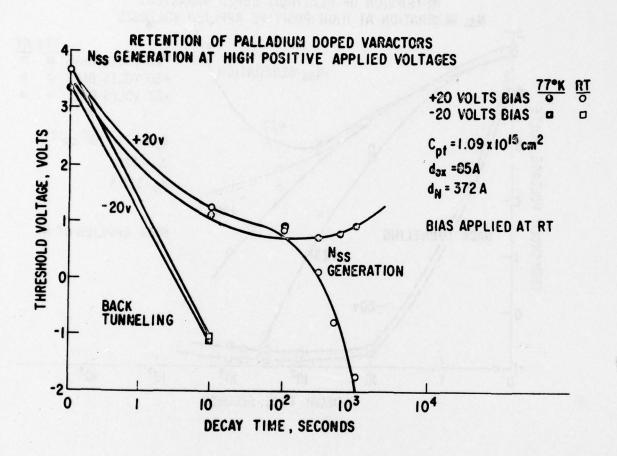

| 32     | Palladium Retention at High Positive Applied Voltages               | 75   |

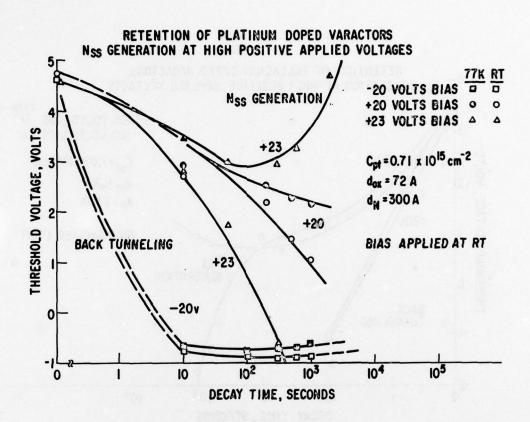

| 33     | Platinum Retention at High Positive Applied Voltages                | 76   |

| 34     | Platinum Retention Before and After Endurance Cycling               | 78   |

| 35     | N Generation at High Bias for Voltages Below 20V                    | 80   |

| 36     | N <sub>SS</sub> Generation at High Bias for Voltages Above 20V      | 81   |

| 37     | N <sub>ss</sub> Generation at High Positive Bias for Tungsten Doped |      |

|        | Varactors                                                           | 82   |

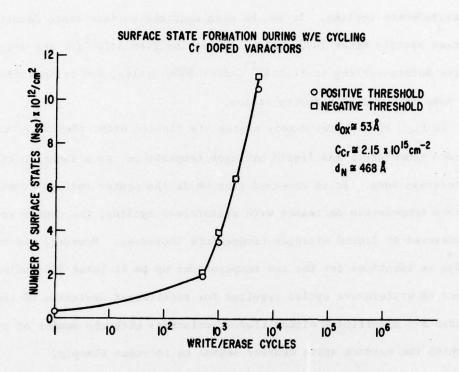

| 38     | Surface State Formation During Write Erase Cycling                  | 84   |

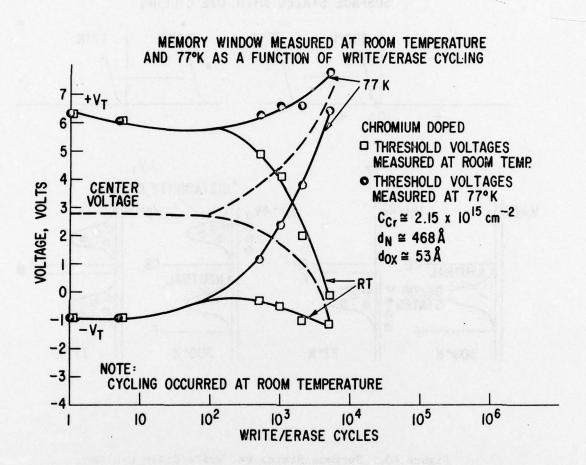

| 39     | Memory Window Measured at Room Temperature and 77°K                 |      |

|        | vs. Write/Erase Cycles                                              | 85   |

| 40     | Surface States vs. Write/Erase Cycling                              | 86   |

| 41     | Endurance of Platinum Doped Varactors                               | 89   |

| 42     | Endurance of Cr Doped Varactors for Different Cycled Windows        | 90   |

| 43     | Endurance of Ni Doped Varactors for Four Cycled Windows             | 92   |

| 44     | Endurance of Cr Doped Varactors for Various Oxide Thicknesses       | 93   |

| 45     | Endurance of Cr Doped Varactors for Several Dopant                  |      |

|        | Concentrations                                                      | 95   |

## LIST OF ILLUSTRATIONS (Cont'd)

| FIGURE |                                                          | PAGE |

|--------|----------------------------------------------------------|------|

| 46     | Endurance Window Center Voltage vs. Dopant Concentration | 96   |

| 47     | Endurance of Platinum Doped Varactors at Elevated        |      |

|        | Temperatures                                             | 97   |

| 48     | Endurance of Cr Sputter-Doped Varactors                  | 98   |

## LIST OF TABLES

| TABLE |                                                          | PAGE |

|-------|----------------------------------------------------------|------|

| 1     | MNOS Memory Transistor Fabrication Sequence - Phase I    | 6    |

| 2     | Oxide Growth vs. Time                                    | 12   |

| 3     | Reactivities of Potential Dopants                        | 16   |

| 4     | Multipliers to Calculate Dopant Concentration            | 21   |

| 5     | Write Parameters                                         | 43   |

| 6     | Retention Parameters for the Six Most Promising Dopants  | 61   |

| 7     | Variation of Decay Slope with Concentration              | 67   |

| 8     | Variation of "b <sub>R</sub> " with Dopant Concentration | 67   |

| 9     | Typical Endurance Parameters                             | 101  |

| 10    | Endurance x Retention Product                            | 106  |

| 11    | Optimum Devices                                          | 107  |

#### SECTION I

#### INTRODUCTION

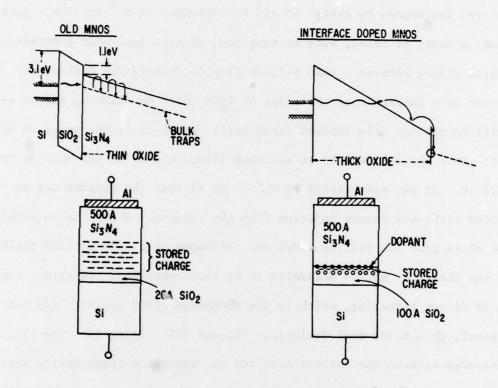

Interface doping of dual dielectric charge storage cells of the IGFET types was introduced by Kahng et al. and Thomber et al. in 1974. In this method, a layer of metal, such as tungsten, usually less than a monolayer thick, is placed between a thin silicon dioxide film (first dielectric), which is grown to a thickness of the order of 100A thick on silicon, and an alumina or silicon nitride film (second dielectric), which is of the order of 400A thick. This was followed by an aluminum film, to make up the MAOS or MNOS structure. It was established by Kahng et al.that the dopants act as trapping sites for charge injected from the silicon. Charge is injected into these sites from the silicon under the influence of a high applied field. Here the charge motion mechanism is by Fowler-Nordheim tunneling, rather than by direct tunneling, which is the mechanism which operates for the conventional, thin oxide dual dielectric storage cells (Fig. 1). The principal differences between the conventional and the interface doped device are:

- The stored charge is separated from the silicon by a much thicker oxide film,

- 2) The stored charge resides principally at the dopant sites, and not 100-200A inside the nitride film, as it does in the conventional MNOS.

D. Kahng, W. J. Sundburg, D. M. Boulin, and J. R. Ligenza, <u>Bell System Technical Journal</u>, Vol. 53, 1974, p. 1723.

K. K. Thornber, D. Kahng, and C. T. Neppell, <u>Bell System Technical Journal</u> Vol. 53, 1974, p. 1741.

Figure 1. Conventional vs. Interface-Doped MNOS

This has the following important consequences:

- 1) The stored charge is retained for very long times.

- 2) The cell is very insensitive to read-disturb.

- 3) Device degradation mechanisms associated with charge motion in the nitride are less important.

The charge retention in interface-doped MAOS devices has been studied extensively by Thornber et al<sup>2</sup>. It was found by them that charge loss could be accelerated at elevated temperatures and applied bias voltages; the extrapolated charge retention was 500 years at 80°C. The charge decay mechanism at temperatures between 150 to 300°C was found to be by activated conduction through the alumina to the gate electrode.

In this previous work, emphasis was placed on tungsten as the interface dopant and alumina as the second dielectric, although other dopants such as Pt, Ta, Ir, and silicon nitride as the second dielectric were also explored. A lower limit of the doping concentration of  $10^{14}$  cm<sup>-2</sup> and an upper limit of  $5 \cdot 10^{15}$  cm<sup>-2</sup> was identified. Device endurance toward write/erase cycling was not reported.

Since the dopant deposition is an easily controllable step, the interface-doped memory device represents an advance in the state-of-the-art. In this report, we describe the use of ten different interface dopant metals in MNOS memory cells. Included are the write/erase characteristics as a function of the dopant concentration and oxide thickness, memory window as a function of dopant concentration and oxide thickness, write speeds as a function of write pulse width and amplitude, the charge retention as a function of doping concentration and oxide thickness, and finally, the endurance. The goal of this investigation is to enable an optimum choice to be made among types of dopants, deposition method, range of doping concentrations, and oxide thicknesses.

#### SECTION II

#### **APPROACH**

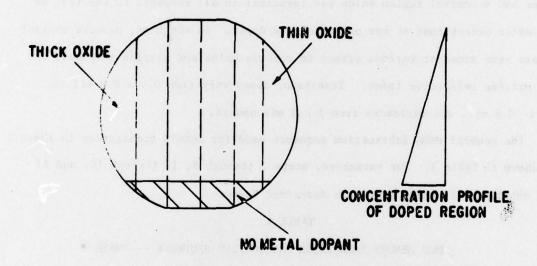

In order to survey as many dopant concentrations and oxide thicknesses as quickly as possible and without interfence from processing artifacts, a large number of varactor cells of varying concentrations and oxide thicknesses were prepared on a single silicon wafer. This was accomplished by preparing 5 to 6 oxide stripes across the wafer of increasing thickness (usually from 50 to 140A) by alternate thermal growth and subsequent partial removal of the oxide film by etching. This gives rise to a step pattern in the oxide thickness. The interface dopant is now deposited in such a way that its concentration varies from zero on one end of the wafer to a pre-determined level such as 1015 or 10 to m on the other, giving a wedge-like thickness distribution in between. The dopant concentration gradient is perpendicular to the oxide thickness gradient, thus giving a full range of dopant concentrations with each oxide thickness. In practice, this method is applicable if the variation in the doping concentration does not greatly exceed one order of magnitude. As a result, a concentration range of about one order of magnitude and six oxide thicknesses can be evaluated on one wafer. This is illustrated in Fig. 2.

For transistors, only the dopant concentration was varied over the wafer, at a constant oxide thickness.

The nitride thickness was between 300 and 600A.

Accelerated test methods were used wherever possible. Thus, to measure charge retention after writing, high gate bias voltages were applied to force an observable charge decay within several minutes. Extrapolation to zero bias voltage gives the expected retention under real use conditions. Since the endurances measured in this program have not exceeded 10<sup>7</sup> cycles so far, accelerated measurements have not been necessary.

# (SIX) STEPPED OXIDE VARACTOR WAFER AND EVAPORATED DOPANT PROFILE

Figure 2. Stepped Oxide Varactor Wafer and Evaporated Dopant Profile

#### SECTION III

#### INTERFACE-DOPED MNOS DEVICE FABRICATION

In this section, the MNOS process which was used to fabricate devices for Phase I of this program is described. During Phase I, only varactors and discrete memory transistors were fabricated. The devices are p-channel, on 2" (100) silicon wafers of 3 to 8 ohm-cm n-type resistivity (phosphorus). Aluminum gates are used.

In order to properly assess the effect of interface doping, each processed wafer had a control region which was identical in all respects to the rest of the wafer except that it was not interface doped. In addition, process control wafers were added at various stages to measure oxide and nitride thickness and the nitride refractive index. Transistor sizes vary from 0.4 x 0.4 mil to 12 x 0.6 mil, and varactors from 1 x 1 mil upward.

The general MNOS fabrication sequence used for memory transistors in Phase I is shown in Table 1. For varactors, steps 2 through 8, 12 through 14, and 17 are omitted. All these steps are described below.

TABLE 1

MNOS MEMORY TRANSISTOR FABRICATION SEQUENCE -- PHASE I

| Step No. | Description                |  |

|----------|----------------------------|--|

| 1        | Initial cleaning           |  |

| 2        | Wafer oxidation            |  |

| 3        | Source drain mask          |  |

| 4        | Source drain predeposition |  |

| 5        | Source drain drive-in      |  |

| 6        | Stable gate mask           |  |

| 7        | Stable gate oxide          |  |

| 8        | Memory gate mask           |  |

| 9        | Memory gate oxidation      |  |

| No. | Description (contd.)                 |

|-----|--------------------------------------|

| 10  | Interface doping                     |

| 11  | Nitride deposition                   |

| 12  | Oxide deposition (SiO <sub>2</sub> ) |

| 13  | Contact mask (SiO <sub>2</sub> )     |

| 14  | Nitride oxide etch                   |

| 15  | Metal deposition                     |

| 16  | Interconnection mask                 |

| 17  | Interconnection sinter               |

## (1) Initial cleaning

The initial cleaning process removes any surface contaminants that may remain on the wafers in the as-received condition.

The silicon wafers are first immersed in a 50/50 mixture of hydrofluoric acid (HF) and deionized water. They are next rinsed with deionized water and blown dry with nitrogen. In a quartz tube furnace at 1050°C, a thermal oxide is grown on the wafers. With pure oxygen flowing at 1 cubic ft./hr., 30 minutes is sufficient to grow a layer 180 Å thick. At this point, the dilute hydrofluoric acid bath is repeated. The oxide layer and any trapped impurities are stripped away. The cleaning step ends with a final rinse in deionized water and drying with nitrogen.

## (2) Wafer oxidation

Wafer oxidation occurs in two parts. First a layer of thermal oxide 1100 Å thick is grown on the wafers in the manner described in step 1. At 1050°C and an oxygen flow rate of 1 cubic ft/hr, three hours are needed.

Second, 5200 % of SiO<sub>2</sub> are deposited on the wafers by chemical vapor deposition in a silox reactor. The silox reactor is purged for 15 minutes with

line nitrogen. During this time, the heater block in the furnace is heated to  $450^{\circ}$ C. After the purge, the line nitrogen is turned off. Bottled nitrogen, oxygen and silane (SiH<sub>4</sub>) diluted in argon flow through the reactor tube at the rates listed below:

Oxygen

0.211 liters/min.

Nitrogen

0.066

5.4% SiH, in Argon 0.45

After thus clearing the gas feed lines, the silane-in-argon is vented directly to the exhaust, and the oxygen is turned off. At this time, the wafers are inserted into the reactor. During a two-minutenitrogen purge, the wafers heat to the reaction temperature. The furnace now automatically begins a deposition run. Twelve minutes at the specified flow rates is sufficient to deposit 5200 Å of SiO<sub>2</sub>. Thickness is determined by referring to a color/thickness table.

The 6300 Å (total thickness) of  $SiO_2$  will act as a diffusion stop during the source/drain diffusion.

One of the by-products of the silox reaction is water vapor. Because of the harmful effect of water on photoresist, the wafers are baked for 30 minutes at 175°C in a nitrogen atmosphere prior to the next step.

## (3) Source drain mask

The diffusion stop SiO<sub>2</sub> layer must be etched in this step to expose the source drain regions of the wafers. Photoresist is spun on to the wafers at 5000 rpm with a photoresist spinner. The resist is dried for 30 minutes in a nitrogen atmosphere at 80°C. The source-drain mask is then aligned on the wafers and the wafers are exposed to ultraviolet light. Resist developer is now used to wash away the photoresist that was not exposed to the UV light at the source and drain regions. The wafers are now baked for 30 minutes in a

nitrogen atmosphere at 175°C in preparation for the oxide etching step. The etchant is composed of 1 part hydrofluoric acid and 9 parts NH<sub>4</sub>F. Three minutes are sufficient to remove the oxide above the source and drain without appreciable undercutting of the photoresist. After rinsing in deionized water, the remaining photoresist is removed in microstrip heated to 95°C (5 minutes) and boiling deionized water (3 minutes). Finally, the wafers are cleaned in a vapor degreaser with a solvent mixture of equal parts of isopropyl alcohol, acetone and trichlorethylene and blown dry with nitrogen.

Periodic microscope checks are made during this step to insure correct alignment and proper etching.

## (4) Source drain predeposition

The p-dopant which we use is boron. The wafers to be doped are arranged vertically in a quartz rack, interspersed with wafers of boron nitride. The rack is then inserted into a tube furnace (1000°C) with a nitrogen atmosphere for 15 minutes. Boron is transferred to the silicon wafers, where a thin layer of silicon at the source and drain regions becomes very highly doped.

## (5) Source drain drive-in

Before the boron dopant is driven into the silicon surface, the silicon dioxide and boron residing on wafer surfaces are stripped away in 50/50 HF.

The wafers are then inserted into the 1000°C tube furnace for 3 hours in oxygen.

The junction depth is about 1.5 microns. Simultaneously, 1100 Å of thermal oxide are grown on the wafers.

#### (6) Stable gate mask

Fifty-two hundred \$\hat{A}\$ of \$\sio\_2\$ are again deposited on top of the thermal oxide layer. This oxide layer, which totals 6300 \$\hat{A}\$, is masked and etched to give the stable gate mask pattern.

The stable gate oxide, which is 500 R thick, is a thermal oxide grown at (7) Stable gate oxidation 1000°C for 1½ hrs with an oxygen flow of 1 cu.ft/hr.

In the great majority of our devices, the stable gate oxide was not used. In these cases, the stable gate mask served to expose the memory region. Those wafers which had stable gates, however, employed a memory gate mask for the

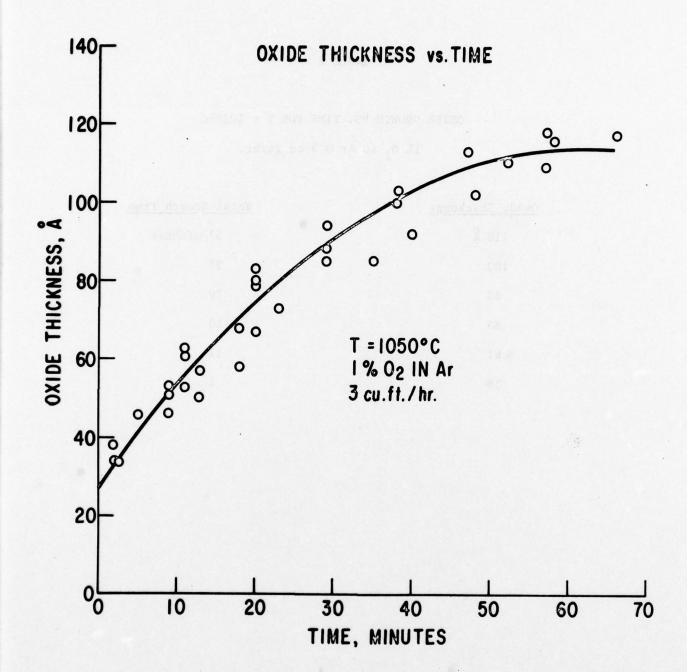

The memory gate oxides ranged in thickness from 30 % to 134 %. They were grown in a tube furnace at 1050°C. To more closely control the growth process, thinner memory oxide. the flow gas is 1% oxy gen in argon. Figure 3 shows the relationship between oxide thickness and time.

For much of the initial survey of interfacial dopants, varactors were used instead of transistors because of their much more rapid producibility. The use of varactors enablesus to vary the gate oxide thickness within a single wafer, further minimizing the effect of wafer-to-wafer differences, as illustrated in Fig. 2. It required oxidizing the wafers 6 separate times. After each oxidation, the wafers were partly immersed in 50/50 HF and water to remove a portion of the oxide layer. For instance, after the first gate oxidation, all but the leftmost strip of the wafer would remain. Table 2 contains the thickness vs. total oxidation time data for one particular six step oxide run.

Figure 3. Oxide Thickness vs. Time

TABLE 2

## OXIDE GROWTH VS. TIME FOR T = $1050^{\circ}$ C 1% O<sub>2</sub> in Ar @ 3 cu.ft/hr.

| Oxide Thickness | Total Growth Time |

|-----------------|-------------------|

| 118 🎗           | 57 minutes        |

| 100             | 38                |

| 88              | 29                |

| 83              | 20                |

| 61              | 11 8              |

| 38              | 2                 |

## (10) Interface doping

This important process step is covered in section IV.

## (11) Nitride deposition

Silicon nitride is deposited in an epitaxial reactor by the  $\mathrm{SiH_4/NH_3}$  reaction at a wafer temperature of  $850^{\circ}\mathrm{C}$ . The reactor is first given a 10 minute nitrogen purge. During this time, the silane, ammonia and hydrogen flow rates are set. The ratio of silane to ammonia is 1/1000. After the purge, the wafers are inserted into the reactor and brought to temperature in the presence of the hydrogen flow gas. Fast write devices have a nitride thickness in the neighborhood of 300 Å, and most slow write devices have 450 - 600 Å nitride layers. Deposition times are from 1/2 min. to 1 min. long.

## (12) Oxide deposition (SiO<sub>2</sub>)

For a third time, 5200 Å of SiO<sub>2</sub> are deposited by the chemical vapor method. This oxide will remain on the wafers as a field oxide.

## (13) Contact mask

This mask allows windows to be etched down to sources and drains, so that they can be contacted with aluminum, which will be deposited in a later step.

### (14) Nitride oxide etch

The 5200 Å of oxide are first etched by immersing the wafers for three minutes in buffered HF (NH<sub>4</sub>F/HF:9/1) as described earlier. The photoresist is removed and wafers cleaned, degreased and dried. The wafers are then boiled for 45 minutes in phosphoric acid to etch the nitride layer

## (15) Metal deposition

Au aluminum layer is deposited by electron beam evaporation. The wafers are placed in a bell jar which is evacuated to  $10^{-6}$  torr. An aluminum slug is melted with an electron beam and the wafers are coated to a thickness of 1 to 1.5  $\mu$ m. The thickness is monitored by quartz crystals.

### (16) Interconnection mask

Photoresist is patterned on the wafers as before, using the interconnection mask. The aluminum is etched in a solution of 76% phosphoric acid, 15% acetic acid, 5% water, and 4% nitric acid heated to 45°C. Etching time is 1 to 2 minutes. The photoresist is stripped and the wafers are again boiled in deionized water and vapor degreased.

## (17) Interconnection sinter

Processed wafers are annealed at 500°C for 25 minutes in an annealing oven.

Nitrogen and hydrogen are used at the following flow rates:

Nitrogen - 2 cubic ft/hr.

Hydrogen - 0.1 cubic ft/hr.

#### SECTION IV

#### INTERFACE DOPING

The interfacial doping step is carried out after the memory gate oxidation.

In this section the selection of dopants, dopant concentration, and doping conditions are given.

#### SELECTION OF DOPANTS

In the selection of dopants, the following criteria were applied:

- The vapor pressure of the element or its oxide must be negligible at 850°C.

- The diffusion coefficient of the dopant at 850°C in SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>

must be low.

- The dopant must not be subject to ionic motion in SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>

under bias temperature stress.

- The melting point of the deposited species must be above 900°C.

- · Depositing reproducibly must not be too difficult.

These criteria eliminate the alkali and alkaline earth metals because of their high ionic mobility, Au, Ag, and Cu, which have high diffusivities in SiO<sub>2</sub>, Zn, Cd, Hg, Ga, and In, because of high vapor pressures or low melting points. Primarily the elements in group VII, I-VIIB, the rare earth elements and perhaps Al remain. The reactivities of some of those elements are given in Table 3. They fall into four classes, according to their oxide-free energy of formation:

- Elements that will not oxidize on exposure to air (Ru, Rh, Pd, Os, Ir and Pt).

- Elements that oxidize in air but can be readily reduced by hydrogen at 850°C (V, Cr, Mo, W, Fe, Co, and Ni).

- Elements that oxidize in air and are not reducible by hydrogen at 850°C (Nb and Ta).

- Elements that react with SiO<sub>2</sub> to form the oxide, reduce the SiO<sub>2</sub> to form Si (Y, Ti, Zr, and La), and are not reducible by hydrogen at 850°C.

TABLE 3

REACTIVITIES OF POTENTIAL DOPANTS

| Element | Group            | Oxidizes in Air | Oxide Reducible      | Reduces SiO <sub>2</sub> |

|---------|------------------|-----------------|----------------------|--------------------------|

| La      | III B            | Yes             | No                   | Yes                      |

| Ti      | - TV D           | Yes             | No                   | Yes                      |

| Zr      | IV B             | Yes             | No                   | Yes                      |

| v ]     |                  | Yes             | Yes                  | No                       |

| Nb }    | VВ               | Yes             | No                   | No                       |

| Ta      |                  | Yes             | No                   | No                       |

| Cr      |                  | Yes             | Yes                  | No                       |

| Mo      | VI B             | Yes             | Yes                  | No                       |

| w       |                  | Yes             | Yes                  | No                       |

| Fe      |                  | Yes             | Yes                  | No                       |

| Co      |                  | Yes             | Yes                  | No                       |

| Ni      |                  | Yes             | Yes                  | No                       |

| Ru      | 9 (8 <u>) (8</u> | No              | . wasting            | keran <del>a</del> sa s  |

| Rh      | VII              | No              |                      | (M) 100 -1 0             |

| Pd      |                  | No              | net gra r== anchino  | na ka <del>n</del> ala   |

| Os      |                  | No              | Cr. 180, 177 Fo. Co. | ,000° <b></b> 000        |

| Ir      |                  | No              |                      |                          |

| Pt      |                  | No              |                      |                          |

At least one metal was included from each of these classes. The metals in the fourth class will react to give a layer of metal oxide. For the initial survey, the following elements were selected: Ir, Pd, Pt, Nb, Ta, W, Mo, Cr, Ni, and Ti.

#### DOPANT CONCENTRATION

It is of interest to calculate the charge stored in a MNOS device to give a threshold shift of  $\Delta V_{\rm T}$ , if the charge is located near the silicon/insulator interface. This situation is given by:

$$Q_{stored} \approx C_o \Delta V_T$$

where  $C_0$  is the gate insulator capacitance. For  $\Delta V_T = 10$  volts,  $Q_{\text{stored}} \approx 1.6 \times 10^{10} \, \text{C/cm}^2$ , or about  $10^9$  electronic charges/cm<sup>2</sup>.

Kahng et al. have indicated that the effective doping range for tungsten in thick oxide MNOS devices was between  $10^{14}$  to  $5 \cdot 10^{15}/\text{cm}^2$ . There are then  $10^5$  to  $10^6$  available dopant sites for each stored charge.

In Phase I of this program, dopant concentrations ranged between 0 and  $5 \times 10^{16}$  cm<sup>-2</sup>.

## DOPING CONDITIONS

Methods that have the potential of introducing precise amounts of dopant are:

- a. Vacuum deposition by evaporation or sputtering.

- b. Adsorption of metal ions from solution.

- c. Electroplating by current flow through the thin oxide.

- d. Exposure to a gas bearing the dopant at high temperature or in electrical discharge.

- e. Growing the last portion of the oxide film in the presence of small additions of dopants to the flow gas.

- f. Ion implantation.

Doping by vacuum deposition, sputtering, and adsorption from solution were employed in this investigation.

## VACUUM DEPOSITION OF METAL DOPANTS BY EVAPORATION

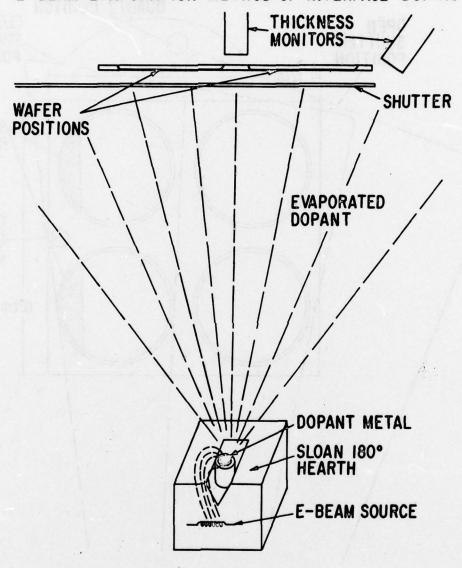

Vacuum deposition of the metal dopants is the most generally applicable technique available. Evaporation by electron gun is readily controlled and the use of quartz crystal monitors provides a reliable relative thickness standard.

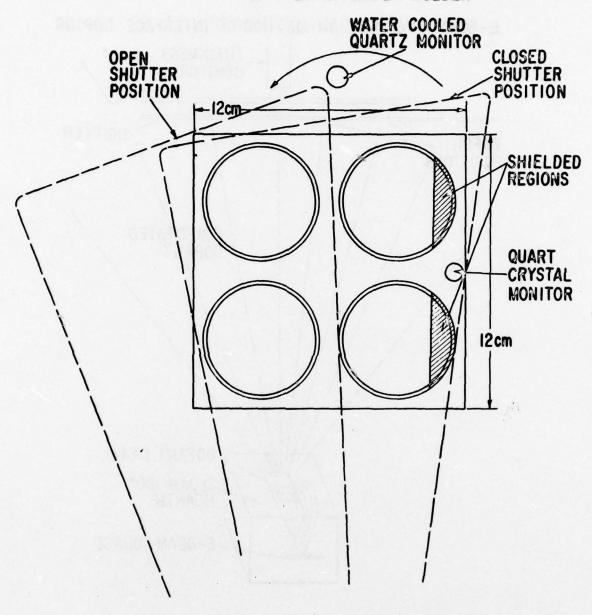

Figures 4 and 5 are schematics of the deposition equipment. Figure 4 indicates the relationship between the wafer holder, the Sloan  $180^{\circ}$  electron gun, the flying shutter, and the two quartz crystal monitors. Figure 5 is a top view of the wafer holder. The open and closed shutter positions are shown by the dotted lines.

The wafer holder has a capacity of four-two inch wafers. However, only during the deposition of aluminum does it hold more than 2 wafers. During a dopant evaporation only two wafers are placed at the points marked A and B in Figure 5. The darkened areas indicate the position of shields used to prevent deposition on those portions of the wafers. A small slug of the dopant metal is placed in the electron gun and the system evacuated to below 10<sup>-5</sup> torr. The shutter covers the wafers and the inner oscillator.

The dopant metal is slowly heated to its melting point by the magnetically focused electron beam. The water cooled outer oscillator monitors the gradually increasing rate of evaporation.

## E-BEAM EVAPORATION METHOD OF INTERFACE DOPING

Figure 4. E-Beam Evaporation Method of Interface Doping

## TOP VIEW OF WAFER HOLDER

Figure 5. Top View of Wafer Holder

Once this rate has stabilized at a predetermined level, the shutter begins to open. If the rate of evaporation of a metal is high or a low dopant concentration is desired, the shutter is set to turn through the 27 degrees necessary to expose the wafers completely in 1 second. For lower evaporation rates, the shutter is allowed 5 seconds to rotate through this angle. As the shutter opens, the inner oscillator measures the evaporated metal thickness. By noting the oscillator frequency before the shutter opens and after it closes again, we can calculate the amount of dopant on those parts of the wafers exposed for the longest time.

When the wafers have been fully exposed (save for the shielded regions), the shutter is released from motor control and swings shut instantly.

Table 4 shows the multipliers necessary to calculate dopant concentration from the frequency change of the oscillator recorded during the evaporation.

TABLE 4

MULTIPLIERS TO CALCULATE DOPANT CONCENTRATION

| <u>Dopant</u>                       | Maximum Dopant Concentration, x 10 <sup>15</sup> cm <sup>-2</sup> |

|-------------------------------------|-------------------------------------------------------------------|

| Tungsten                            | 0.0717 x Δf                                                       |

| Iridium                             | 0.0686 x Δf                                                       |

| Palladium .                         | 0.1236 × Δf                                                       |

| Platinum Baraning Baraning Baraning | 0.0674 × Δ£                                                       |

| Niobium                             | 0.1416 × Δf                                                       |

| Tantalum                            | 0.070/ 45                                                         |

| Molybdenum                          | 0.1369 x Δf                                                       |

| Chromium                            | 0 0506 AF                                                         |

| Nickel                              | 0.2252 x Af                                                       |

| Titanium                            | 0.2740 x \Deltaf                                                  |

#### TUNGSTEN OXIDE EVAPORATION

Of the six most promising dopants, tungsten proved to be the most difficult one to deposit by electron beam evaporation. It was difficult to maintain a constant rate of evaporation for the required length of time. As a result, we investigated the possibility of evaporating tungsten trioxide from a ribbon of the metal.

A tungsten ribbon of dimensions .003" x 3/8" x 5" is clamped between two current leads from a step-down current transformer. The strip is oxidized in air by passing a large current through it. By observing the colors on the ribbon, the resulting oxide thickness can be controlled and is highly reproducible. The system is then evacuated and the oxide flashed off and deposited on the wafers by resistance heating the strip.

## DOPANT DEPOSITION BY SPUTTERING

Sputtering was carried out in a vacuum system filled with argon to a pressure of  $1.8 \cdot 10^{-2}$  torr., after having been previously evacuated to  $10^{-6}$  torr. Sputtering targets were 6 in. in diameter, and the distance between targets and substrates was 1.5 inches. A sputtering power of 50 watts was used. This resulted in a deposition rate of 6 A/min. Only Cr and Ni were sputtered.

#### DOPANT DEPOSITION BY SOLUTION DOPING

Very dilute solutions (0.00018M) of Cr or Ni were prepared. From 1 to 3 cm<sup>3</sup> of solution were then metered out and the solvent evaporated on the wafer surface. The resulting dopant concentration was not uniform over the wafer, however, the dopant concentration being higher at the wafer edges due to the accumulation of solute at the edges where the solvent evaporated last.

#### ANALYTICAL PROCEDURES

When the dopant was evaporated, the deposited dopant concentration was monitored by the frequency change of a 4 MHz quartz crystal. The quartz crystal, in turn, was calibrated in blank runs in which metal was deposited on an oxidized Si wafer to a coverage of about 100 monolayers, which was accurately determined by atomic absorption measurements. This was then compared to the corresponding frequency change. The sensitivity of the quartz crystal used was .0078 microgram/Hz.

When the dopant was sputtered, the dopant concentrations were determined from the sputtering time at a sputtering voltage and current for which the sputtering rate has been previously determined in blank experiments using dopant thicknesses of 500 to 1000 A.

In experiments involving solution doping, very dilute (0.00018M) solutions of the dopants (Cr and Ni only) were prepared. From 1 to 3 cm of solution were then metered out and the solvent evaporated on the wafer surface. The average dopant concentration was then calculated from the quantity of solute contained in the solution, which was known to three significant figures.

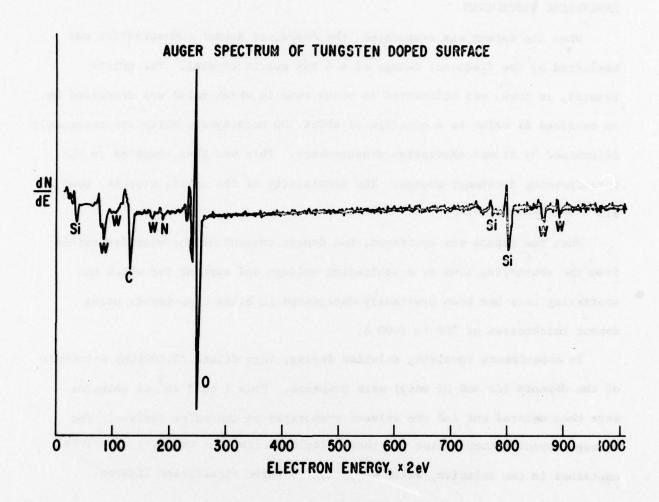

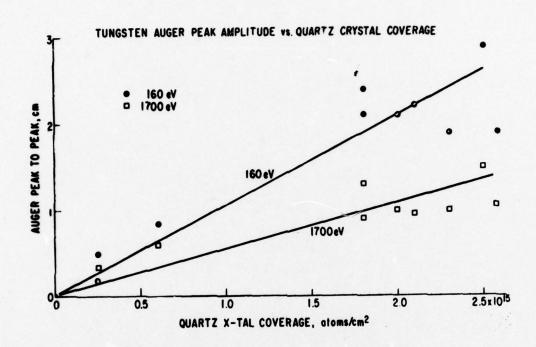

Auger analysis of the wafer surface after dopant deposition clearly shows the presence of the dopant. This is illustrated in Fig. 6 for tungsten. In addition to the expected elements, a strong carbon peak is always visible, probably due to the long storage time before analysis. The Auger peak-to-peak distance for the various W lines obtained for a number of W concentrations corresponds reasonably well to the surface concentration calculated from the quartz crystal frequency change. This is illustrated in Fig. 7 for tungsten

Figure 6. Auger Spectrum of Tungsten Doped Surface

Figure 7. Tungsten Auger Peak Amplitude vs. Quartz Crystal Coverage

as the dopant, for the tungsten lines corresponding to 160 and 1700 ev Apger electron energy.

#### SECTION V

#### WRITE CHARACTERISTICS

#### WRITE MECHANISMS AND WRITE CURVES

The three mechanisms by which the threshold voltage in interface doped MNOS devices can be changed are illustrated in Figure 8. First, charge can be transferred through the thin oxide by a tunneling process (direct tunneling if the oxide is thin, and F-N tunneling if thick). Application of a positive write voltage on the gate will shift the threshold voltage in a positive direction (forward shift). Second, charge can be transferred from the gate electrode through the Si<sub>3</sub>N<sub>4</sub> to the storage sites, probably by Poole-Frenkel conduction. Here, application of a positive voltage to the gate electrode shifts the threshold voltage in a negative direction (reverse shift). Third, the threshold voltage can change irreversibly due to effects associated with wear-out (lack of endurance) which is caused by the prolonged application of a high write voltage of either polarity, and is normally associated with the generation of a large number of fast surface states.

The first mechanism is responsible for writing the two memory states. It is essentially temperature independent. The second mechanism, which is strongly temperature dependent, has not been found to be the predominant one in this investigation. Note, however, that Thornber<sup>2</sup> et.al.have reported that the second mechanism is important in determining retention.

To write, a sufficiently high write voltage must be applied for a sufficient length of time. The lower the write voltage, the longer the time required to transfer the charge to the storage sites and change the threshold voltage.

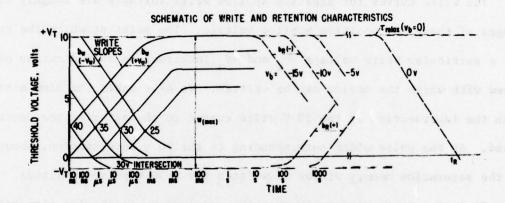

This is schematically indicated in Fig. 9, where the expected threshold voltage shift is shown as a function of the write pulse width for various write pulse amplitudes (full lines). The expected behavior is shown for initial memory

#### THRESHOLD VOLTAGE CHANGES IN INTERFACE-DOPED MNOS CAN OCCUR DUE TO: (111) (1) (11) CHARGE MOTION THROUGH THE CHARGE MOTION THROUGH IRREVERSIBLE SURFACE POTEN-OXIDE AND STORAGE AT THE THE NITRIDE AND STORAGE TIAL CHANGES DUE TO WEAR-OUT AT THE INTERFACE. EFFECTS (ENDURANCE). INTERFACE. A) RICHARDSON-SCHOTTKY MECHANISM UNKNOWN A) DIRECT TUNNELING B) FOWLER-NORDHEIM B) POOLE-FRENKEL TUNNELING Si3N4 VT SiO2 Si log W/E cycles TEMPERATURE-INDEPENDENT TEMPERATURE-DEPENDENT CAN BE ANNEALED

Figure 8. Threshold Voltage Changes in Interface-Doped MNOS

Figure 9. Schematic of Write Characteristics

states for which the threshold voltage is -1 V and also + 10 V, and to which a positive and negative write voltage is applied, respectively. When the write voltage is first applied, the threshold voltage changes rapidly due to the high field across the thin oxide. However, the threshold voltage must be expected to saturate soon as more and more charge is stored at the dopant sites and the field is reduced. The time at which the threshold voltage levels out with time depends on the write pulse amplitude.

The write curves for negative applied write voltages are roughly mirror images of those for positive applied voltage. The point at which the curves for a particular write voltage -V and +V intersect is an indication of the speed with which the device can be written. We have taken the time associated with the intersection of the 30 V write curves to characterize the device write speed. At the pulse width corresponding to the 30 V intersection, about half of the saturation memory window is written for a 30 V pulse amplitude.

It is found experimentally that the spacings, b on the log time axis, between write characteristic curves expressed in decades of write time per volt of write voltage are approximately equal in the range of voltages from 20 to 40 V, which were normally used for writing. Also, the slopes of the write curves, expressed in volts of threshold voltage change per decade of applied write pulse time, are approximately equal for all write voltages of the same polarity. The same is true for both polarities, except that the sign of the slopes are changed.

The schematic behavior indicated in Fig. 9 is actually followed quite well, as indicated in Fig. 10 where actual experimental write curves are plotted for a chromium interface doped varactor for write voltages of  $\pm$  25V to  $\pm$  40V and

Figure 10. Write Characteristics of Chromium Doped Varactors

pulse widths between  $5\mu s$  and 10s. The write behavior of this device can be characterized by a write slope of 1.8 V/dec, a spacing  $b_w$  between write curves of 0.43 dec/volt for positive write voltages and -0.30 dec/volt for negative write voltages, and a "30 V intersection" of  $100 \mu s$ , meaning that approximately a 5 V window can be written at a  $100 \mu s$  write pulse width and a 30 V write pulse amplitude.

It can also be seen from Fig. 10 that the threshold voltage does not saturate with pulse width, as predicted by Fig. 9, but goes through a maximum and then decreases again. This is particularly true for write voltages in excess of 25 V. For example, after a 100 sec write pulse, the threshold voltage window characterizing the two memory states is smaller at  $V_W = 40$  V than it is at 30 V, and the window may, in fact, close down completely for very long write times. Devices which have been written past the maximum threshold window have sustained at least some permanent wear-out damage and cannot be fully rewritten. They act instead like devices which have been cycled beyond their endurance limit. This effect is always associated with an increase in the surface state density. We have taken the maximum memory window achievable for any write pulse width or amplitude (up to 40V) as the "saturation memory window." The saturation memory window of the device in Fig. 10, for instance, is from +12.5 to -0.5, for a maximum window of 13 V, at  $V_W = \pm 40$  V.

#### COMPARISON WITH UNDOPED DEVICES

It is in the write characteristics where the beneficial role of interface doping can be demonstrated best. Figure 11 illustrates the write characteristic curves of two devices which differed from each other only in that one was doped with 1.1·10<sup>15</sup> cm<sup>-2</sup> of Pt, and the other was undoped. (They were adjacent on the same wafer.) Writing with both polarities gives the curves shown in Fig. 11,

# WRITE CHARACTERISTIC CURVES OF ADJACENT DEVICES THOSE WITH PLATINUM DOPING COMPARED TO THOSE WITHOUT DOPING

Figure 11. Write Characteristic Curves of Doped and Undoped Devices

starting from the opposite saturated memory state. It can be seen that the write curves are essentially identical for the doped and undoped devices when the write voltage is positive. However, for negative write voltages, the undoped device needed much longer pulse widths to bring about the same threshold voltage change which was obtained for much shorter pulse widths in the doped device. Thus, a 1 ms pulse at -35 V gives the same threshold voltage change for the undoped device as a 0.1 ms pulse at -20 V for the doped device.

The differences in the write characteristics between a doped and undoped device can be summarized as follows:

- a) The undoped device cannot eject negative stored charge from the interface back to the silicon as quickly as the doped device.

- b) The negative write slope for the undoped device is only half that of the doped devices.

- c) The spacing between negative write curves, -b, for the undoped device is only half that for the doped device.

# DEPENDENCE OF WRITE SPEED ON DOPANT CONCENTRATION

It was generally found that the write speed increased with increasing dopact concentration. This dependence is not strong, however, and is easily clouded by even small differences in oxide and nitride thicknesses. In addition, if the dopant diffused deeper into the oxide, due to exposure to a longer or higher temperature wafer processing cycle after deposition, then high write speeds can be observed even at relatively low concentrations.

Fig. 12 shows the normally observed behavior. Here the 25 volt intersection is plotted as a function of the chromium dopant concentration for a set of increasing oxide/nitride thicknesses. The write speed increases by about two orders of magnitude for an increase in the doping by one order of magnitude.

Figure 12. Cr Dopant Concentration vs. Time of 25V Intersection

#### DEPENDENCE OF WRITE SPEED ON OXIDE THICKNESS

The oxide thickness has a strong influence on write speed. Although this influence is again clouded somewhat by the varying degrees of diffusion of the dopant in the oxide, the dependence of write speed on oxide thickness is generally as shown in Fig. 13, which displays the dependence for fast-write devices. An increase in the oxide thickness of 20 A decreases the write speed by about 3 orders of magnitude.

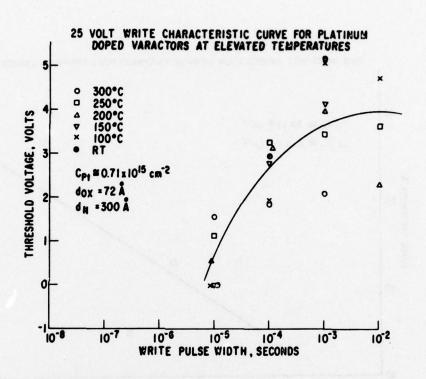

#### TEMPERATURE DEPENDENCE

The temperature dependence of the write characteristics is small. This is to be expected if writing occurs by charge transfer through the oxide by F-N tunneling which is, to a first order approximation, temperature independent. This is illustrated in Fig. 14, which shows the +25 V write characteristic curve for platinum doped varactors at various temperatures between 25°C and 300°C. At 300°C, the second write mechanism discussed above is perhaps coming into play, reducing the effective charge transferred by F-N tunneling, and thus resulting in a small threshold voltage shift. The principal conclusion is, therefore, that the write mechanism is by F-N tunneling at least up to 250°C.

Figure 13. Time of 25V Intersection vs. Oxide Thickness

Figure 14. 25V Write Characteristic Curve at Elevated Temperatures

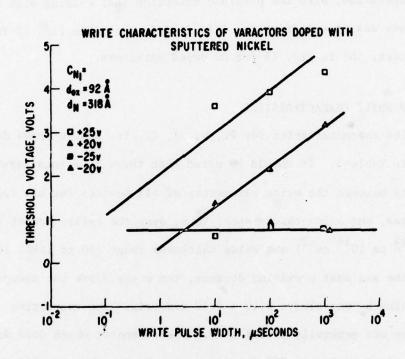

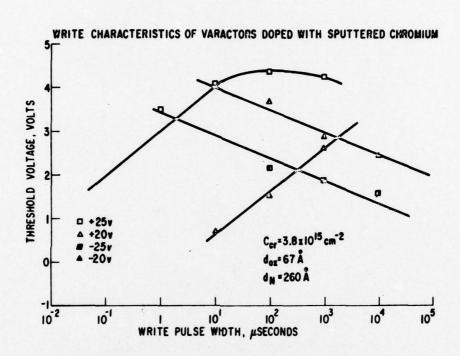

### WRITE CHARACTERISTICS OF DEVICES DOPED BY SPUTTERING

Devices doped by sputtered Cr cr Ni generally behaved similarly to those doped by evaporation, with the possible exception that writing with negative write voltages was more difficult. This is illustrated in Fig. 15 for Ni doped varactors, and in Fig. 16 for Cr doped varactors.

#### SUMMARY OF WRITE CHARACTERISTICS

The write characteristics for Pt, W, Ni, Cr, Ir, and Pt doped devices are summarized in Table 5. It should be noted that there is a considerable degree of similarity between the write parameters of all devices for all dopants, concentrations, and oxide thicknesses. Thus, over the entire dopant concentration (10<sup>14</sup> to 10<sup>16</sup> cm<sup>-2</sup>) and oxide thickness range (40 to 140A) studied, and all of the six most promising dopants, the write slope was always 2.0 ± 0.5 V/dec, and the spacing b was always 0.40 ± 0.10 dec/volt. The saturation (maximum) memory window was generally around 10 V. The parameter which does differ the most between devices is the "30 V intersection." The shortest "30 V intersections" are obtained for the thinnest oxide films and the highest dopant concentrations. The lowest value is 2·10<sup>-9</sup> sec, obtained for a 48 A oxide film and a Cr dopant level of 4.5·10<sup>15</sup> cm<sup>-2</sup>, and a 58 A oxide film and a WO<sub>3</sub> concentration of 1.94·10<sup>15</sup> cm<sup>-2</sup>. For the thicker oxide films and lower dopant concentrations, values as long as 100 msec have been obtained. This covers the range of write speeds required for fast and slow write devices.

Figure 15. Write Characteristics of Varactors Doped with Sputtered Nickel

Figure 16. Write Characteristics of Varactors Doped with Sputtered Chromium

# Write Parameters

| Fast                        |            |            |            |            |                      |            | ŭ           | E4          | E4                    | E                     | ſ±,                   | C4                    |            |          |                        |                        |            |            |                      |            |                        |            |                      |                        | <u>r</u>    |            |            |

|-----------------------------|------------|------------|------------|------------|----------------------|------------|-------------|-------------|-----------------------|-----------------------|-----------------------|-----------------------|------------|----------|------------------------|------------------------|------------|------------|----------------------|------------|------------------------|------------|----------------------|------------------------|-------------|------------|------------|

| 30 volt intersect.          | 1.5 × 10-4 | 1.1 × 10-4 | 1.8 × 10-6 | 4.0 × 10-4 | $3.1 \times 10^{-4}$ | 3.2 × 10-6 | 8.0 × 10-9* | 2.0 × 10-8* | $4.0 \times 10^{-7*}$ | $2.0 \times 10^{-9*}$ | $3.5 \times 10^{-7*}$ | $1.2 \times 10^{-7*}$ | 3.2 × 10-6 | 7 × 10-8 | 1.4 × 10 <sup>-8</sup> | 4.0 × 10 <sup>-5</sup> | 8.0 × 10-4 | 5.6 x 10-5 | $4.0 \times 10^{-3}$ | 4.0 × 10-5 | 2.5 × 10 <sup>-6</sup> | 3.5 × 10-5 | $2.5 \times 10^{-7}$ | 2.0 × 10 <sup>-5</sup> | 1.5 x 10-7* | 4.5 x 10-4 | 1.8 × 10-3 |

| W max'                      | 13.0       | 9.1        | 10.7       | 6.3        |                      | 6.4        | 5.8         | 5.8         | <b>7.9</b> <          | 0.9                   | 8.6                   | 6.7                   | 4.9        | 5.8      | 7.1                    | 11.0                   | 11.5       | 13.0       | 12.1                 | 11.0       | 5.4                    | 3.6        | 9.2                  | 6.2                    |             | 9.6        | 9.3.       |

| + V <sub>T,max</sub>        | 12.5       | 8.8        | 10.4       | 5.9        | 10.5                 | 5.0        | 3.8         | 3.9         | > 4.1                 | 4.1                   | 5.4                   | 4.6                   | 5.0        | 4.1      | 5.4                    | 8.0                    | 8.5        | 10.0       | 9.6                  | 8.0        | 3.2                    | 5.2        | 4.6                  | 5.0                    | 4.4         | 0.6        | 9.0        |

| bw,<br>dec/volt<br>+ Vw     | 0.43       | 0.43       | 0.43       | 0.27       | 0.31                 | 0.31       | 0.43        | 0.36        | 0.53                  | 0.35                  | 0.36                  | 0.37                  | 0.31       | 0.38     | 0.36                   | 0.37                   | 0.35       | 0.41       | 0.34                 | 0.32       | 0.48                   | 0.33       | 0.35                 | 0.32                   | 0.48        | 0.33       | 0.44       |

| Write slope<br>V/dec<br>+ V | 1.80       | 1.80       | 1.70       | 1.80       | 1.80                 | 1.80       | 1,45        | 1.62        | 1.72                  | 1,65                  | 2,55                  | 2.0                   | 1.8        | 1.5      | 1.48                   | 1.95                   | 1,95       | 1.95       | 1.95                 | 1.80       | 1.3                    | 2.27       | 2.2                  | 1.8                    | 1.3         | 2.6        | 2.3        |

| d <sub>Nit</sub> '          | 452        | 452        | 452        | 452        | 372                  | 372        | 263         | 263         | 263                   | =                     | =                     | :                     | 372        | =        | :                      | 452                    | 452        | 452        | 452                  | 372        | 372                    | 372        | 372                  | 372                    | 320         | 897        | =          |

| A od                        | 53         | 134        | 53         | 134        | 88                   | 85         | 43          | 35          | 57                    | 43                    | 20                    | 57                    | 85         | :        | =                      | 02                     | 113        | 70         | 134                  | 88         | 85                     | 85         | 85                   | 85                     | 28          | 53         | 80         |

| Dopant conc.                | 2.95       | 2.95       | 8.6        | 8.6        | 1.32                 | 1.59       | 1.1         | 1.1         | 1.1                   | 4.5                   | 5.4                   | 4.7                   | 1.59       | 0.81     | 3.9                    | 0.51                   | 0.42       | 2.28       | 2.10                 | 0.40       | 0.27                   | 0          | 1.1                  | 96.0                   | 0.12        | 0.081      | 0.081      |

| Var. or<br>Transistor       | >          | >          | >          | ٨          | ٥                    | H          | н           | н           | H                     | H                     | П                     | ı                     | T          | н        | 1                      | Δ                      | ^          | Δ          | Λ                    | Λ          | H                      | ı          | T                    | H                      | ц           | ۸          | Λ          |

| Dopant                      | Chromium   |            |            |            |                      |            |             |             |                       |                       |                       |                       |            |          |                        | Platinum               |            | 4          | 42                   |            |                        |            |                      |                        |             | Iridium    |            |

1

43

|      |                        |            |                        |                        | <b>P4</b>   |            |            |            |            | 14         |                      |            |            |                        |            |            |   |                 | <b>P4</b>  |            |            |            |            | (z,         |            |   |        |            |            |      | £4         |

|------|------------------------|------------|------------------------|------------------------|-------------|------------|------------|------------|------------|------------|----------------------|------------|------------|------------------------|------------|------------|---|-----------------|------------|------------|------------|------------|------------|-------------|------------|---|--------|------------|------------|------|------------|

|      | 2.5 × 10 <sup>-6</sup> | 3.5 × 10-5 | 2.5 × 10 <sup>-7</sup> | 2.0 × 10 <sup>-5</sup> | 1.5 × 10-7* | 4.5 x 10-4 | 1.8 × 10-3 | 1.1 × 10-3 | 1.0 × 10-5 | 4.0 × 10-7 | $2.0 \times 10^{-3}$ | 8.0 × 10-4 | 1.0 × 10-1 | 2.0 × 10 <sup>-1</sup> | 2.0 × 10-4 | 3.0 × 10-5 | • | 6.0 × 10"       | 2.0 × 10-9 | 1.0 × 10-3 | 4.0 × 10-3 | 4.0 × 10-5 | 1.0 × 10-2 | 1.7 × 10-5* | 6.5 x 10-8 |   | 10 5   | 4.0 × 10-4 | 2.0 × 10-4 | 10-3 | 2.0 × 10-6 |

|      | 5.4                    | 3.6        | 9.5                    | 6.2                    |             | 9.6        | 9.3        | 14.0       | 7.8        |            | 6.7                  | 0.6        | 7.5        | 7.3                    | 8.6        | 9.1        |   | 9.5             |            | 9.5        | 7.5        | 7.0        | 4.0        | 5.3         | 4.3        |   | 2.0    | 10.0       | 12.0       | •    |            |

| - K  | 3.2                    | 5.2        | 9.4                    | 5.0                    | 4.4         | 0.6        | 0.6        | 0.6        | 8.9        | 6.2        | 5.5                  | 8.0        | 7.0        | 6.5                    | 8.8        | 8.8        |   | 9.4             | 7.7        | 7.5        | 5.5        | 7.0        | 4.0        | 3.3         | 2.4        |   | 9.5    | 8.0        | 9.5        | 7.5  | 6.1        |

| 25.0 | 0.48                   | 0.33       | 0.35                   | 0.32                   | 0.48        | 0.33       | 0.44       | 0.50       | 0.30       | 0.48       | 0.32                 | 0.43       | 0.45       | 0.41                   | 0.32       | 0.36       |   | 07.0            | 0.92       | 0.32       | 0.34       | 07.0       | 0.33       | 0.33        | 7.0        |   | 67.0   | 0.464      | 0.33       | 0.34 | 0.34       |

| 1 80 | 1.3                    | 2.27       | 2.2                    | 1.8                    | 1.3         | 2.6        | 2.3        | 2.1        | 2.2        | 1.6        | 2.2                  | .1.3       | 1.25       | 1.0                    | 2.8        | 2.7        |   | 1.12            | 6.0        | 1.93       | 1.93       | 1.93       | 1.75       | 1.63        | 1.6        |   | 2.0    | 2.6        | 2.5        | 3.4  | 1.8        |

| 377  | 372                    | 372        | 372                    | 372                    | 320         | 468        | =          | =          | =          | 320        | 372                  | 450        |            | =                      | 897        | :          |   | 280             | 320        | 452        | 452        | 452        | 452        | 372         | 372        |   | 895    | 468        | 468        | 897  | 320        |

| 88   | 85                     | 85         | 85                     | 85                     | 28          | 53         | 80         | 80         | 53         | 28         | 85                   | 63         | . 63       | 76                     | 85         | 53         |   | 48              | 58         | 70         | 134        | 70         | 134        | 85          | 85         |   | 53     | 85         | 53         | 85   | 28         |

| 070  | 0.27                   | •          | 1.1                    | 0.98                   | 0.12        | 0.081      | 0.081      | 1.09       | 0.49       | 0.21       | 09.0                 | . 0.55     | 2.52       | 2.52                   | 0.363      | 0.363      |   | 1.79            | 1.94       | 0.47       | 0.47       | 4.2        | 4.2        | 0.86        | 1.58       |   | 0.266  | 0.266      | 1.22       | 1.22 | 99.0       |

| Λ    | > н                    | H          | H                      | H                      | н           | >          | >          | >          | >          | >          |                      | ۸          | ۸          | ۸                      | Λ          | Λ          |   | ı               | Λ          | Δ          | ^          | Λ          | Λ          | I           | н          | , | >      | Λ          | Λ          | Λ    | >          |

|      |                        |            |                        |                        |             | Iridium    |            |            |            |            | Tungsten             |            |            |                        |            |            |   | WO <sub>3</sub> | WO3        | Palladium  |            |            |            |             |            |   | Nickel |            |            |      |            |

\* Time of 25 V intersection instead of 30V intersection.

#### SECTION VI

## DOPANT CONCENTRATION DEPENDENCE OF MEMORY WINDOW

Dopants were selected in accordance to their reactivity with oxygen. One metal, Ti, has an oxide more stable than SiO<sub>2</sub>. No and Ta have oxides which are not reducible by hydrogen, while Cr, Mo, W, and Ni have oxides which are reducible by hydrogen. Three metals were chosen for their inertness toward oxidation: Pd, Ir, and Pt.

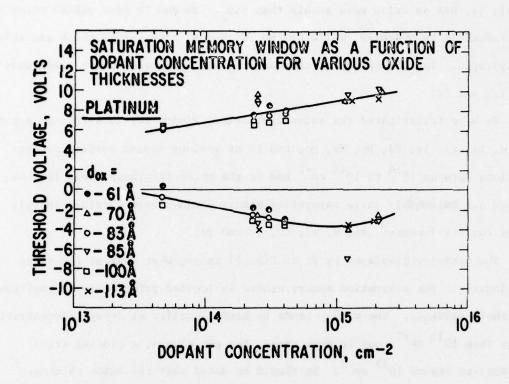

We have investigated the saturation memory window for 10 different dopants, namely, Pt, W, Ni, Cr, Ir, Pd, Nb, Ta, Mo, and Ti at various dopant surface concentrations between 10<sup>14</sup> to 10<sup>16</sup> cm<sup>-2</sup> and in the oxide thickness range from 40 to 140 A. Reasonably large saturation memory windows were obtained in this range for six dopants: Pt, W, Ni, Cr, Ir and Pd.

The behavior displayed by Pt in Fig. 17 is somewhat typical for these six dopants. The saturation memory window is located principally at positive threshold voltages. The window tends to become smaller at dopant concentrations lower than 10<sup>14</sup> cm<sup>-2</sup>, and in some cases, but not always, a closing trend is observed beyond 10<sup>15</sup> cm<sup>-2</sup>. It should be noted that the oxide thickness has relatively little effect on the saturation memory window. The write voltage required to achieve the saturation window is higher for the thicker oxide devices, of course, but the maximum achievable window is not.

Behavior similar to Pt was found for W (Fig. 18), Ni (Fig. 19), Cr (Fig. 20), Ir (Fig. 21), and Pd (Fig. 22). An especially detailed picture was obtained for chromium at dopant concentrations between  $10^{14}$  and  $10^{15}$  cm<sup>-2</sup>. It was found that in this range, somewhat surprisingly, the thinner oxide windows close faster with decreasing dopant concentration than the thicker oxides.

Figure 17. Platinum Saturation Memory Window vs. Dopant Concentration

Figure 18. Tungsten Saturation Memory Window vs. Dopant Concentration

Figure 19. Nickel Saturation Memory Window vs. Dopant Concentration

Figure 20. Chromium Saturation Memory Window vs.

Dopant Concentration

Figure 21. Iridium Saturation Memory Window vs.

Dopant Concentration

Figure 22. Palladium Saturation Memory Window vs. Dopant Concentration

These dopants give satisfactory memory windows for applications in arrays.

It should be noted that the center voltage of the window indicates that they should be most useful as N-channel devices.

The use of niobium, tantalum, and molybdenum did not lead to satisfactory results. This is shown in Figs. 23, 24, and 25, respectively, in which the memory window is plotted as a function of dopant concentration for various oxide thicknesses. For niobium and molybdenum, the window was judged to be too small to be useful over the range studied. For tantalum, the additional problem was encountered that, for dopant concentrations above  $5\times10^{14}$  cm<sup>-2</sup>, Ta diffused through the  $5i0_2$  to the silicon substrate, leading to the disappearance of the memory effect. This was also true for all concentrations of Ti used. It is thus concluded that the more reactive metals are not suitable for memory application.

The dopant materials Pt, W, Ni, Cr, Ir and Pd are satisfactory for memory applications because:

- the saturation window is at least 8V

- the saturation window is independent of dopant concentration over at least a decade.

- there is minimum diffusion through the oxide

- there is no reaction with the oxide.

Figure 23. Niobium Memory Windows vs. Oxide Thickness

Figure 24. Memory Window vs. Tantalum Concentration

Figure 25. Molybdenum Memory Window vs. Dopant Concentration

#### SECTION VII

#### MEMORY RETENTION

After writing, the charge stored at the dopant sites tends to leak away from the oxide nitride interface in order to decrease the field created by its presence. Charge decay at the dopant sites can occur either by conduction through the memory oxide back to the silicon (writing in the reverse direction) or, by conduction through the silicon nitride to the aluminum.

In the conventional MNOS device, virtually all charge motion occurred through a thin oxide layer via direct tunneling, and charge retention in traps located in the nitride was relatively short. In the case of interface doped MNOS devices, however, the time required for a measurable amount of charge to decay is generally in excess of many months, even years. Fowler-Nordheim back tunneling through the oxide is the dominant mechanism, the oxide is generally thicker, and the dopant traps are deeper.

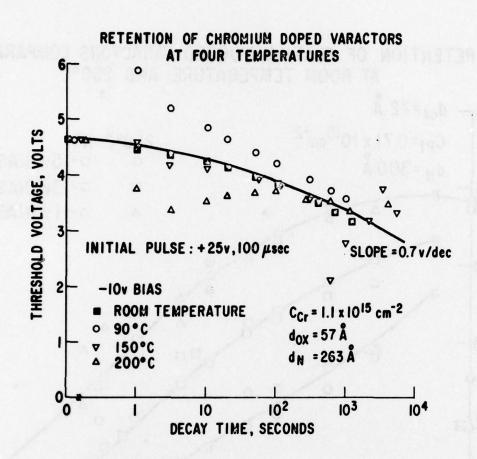

The high retention of the interface doped devices makes accelerated charge decay tests necessary. Charge leakage through the nitride or oxide, or both, can be accelerated by applying a gate bias voltage to increase the electric field. Conduction through the nitride alone can be accelerated by raising the temperature since it is an activated mechanism.

STORED CHARGE DECAY AS A FUNCTION OF TIME

In general, retention behavior parallels write behavior. It is characterized by a set of curves describing the decay of the threshold voltage as a function of time. The curves are linear on a log time plot over a considerable portion of the memory window. The following parameters are used to describe retention behavior. First there is the decay slope measured in volts/decade, which is analogous to the write slope, and which describes the rate at which the memory states change from one into the other with time for a specific accelerating bias. A second parameter is the spacing between the linear regions

of the characteristic curves,  $b_R$ , measured in decades of time per applied bias voltage difference. Thus  $b_R$  is quite analogous to  $b_W$ , the spacing between the write characteristic curves described earlier. Retention is further characterized by  $\tau_{\rm relax}$ , the extrapolated charge relaxation time for zero applied bias. The retention time itself,  $t_R$ , is the time after writing when memory is finally lost, i.e., the window is closed.

The procedure to estimate  $\tau_{\rm relax}$ , the time beyond which noticeable charge decay is observed, and also  $t_{\rm R}$ , is as follows. After writing into a device to give a certain threshold voltage shift, normally 6 to 10 volts, an accelerating bias is applied to the gate. The bias is of a polarity opposite that of the writing voltage. In most cases, the retention of the positive threshold voltage state only was studied, since here the negative applied bias voltage adds to the internal field in the oxide due to the electrons stored at the interface. The positive memory state is then the most vulnerable to decay.

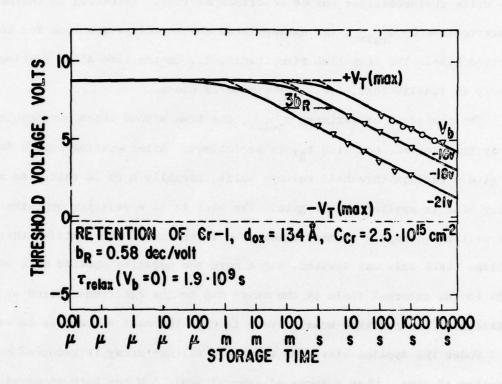

Under the applied bias, the threshold voltage decay is recorded as a function of time. When a decay of approximately 5 V has been observed, the measurement is repeated on a similar, neighboring device with a different bias voltage. One such measurement will yield the decay slope, but two are necessary to measure  $b_R$ . This procedure is illustrated in Fig. 26. The decay of the threshold voltage was followed for bias voltages of -21 V, -18 V and -16 V. It can be seen that  $\tau_{\rm relax}$  moves rapidly towards longer times as the bias voltage becomes smaller. Assuming that  $b_R$  remains constant down to  $V_b = 0$ , an extrapolated  $\tau_{\rm relax}$  ( $V_b = 0$ ) is obtained by displacing  $\tau_{\rm relax}$  ( $V_b = 16$ )

Figure 26. Retention of Chromium

to the right on the log time scale by the amount 16 x  $b_R$ . If it is also assumed that the decay slope is the same between 0 and -21 V,  $t_R$  can be estimated by drawing a line of the same decay slope from  $\tau_{\rm relax}$  ( $V_b$  = 0) to the  $V_T$  = 0 axis. The time marked by that intersection is taken to be  $t_p$ .

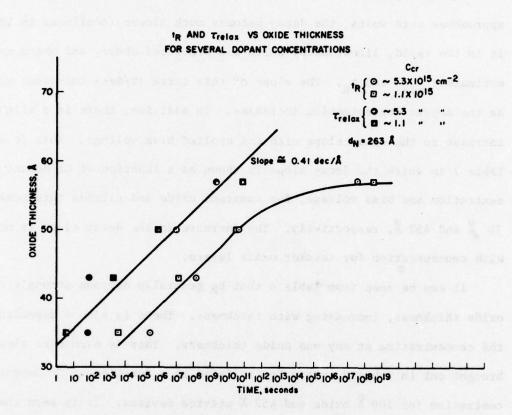

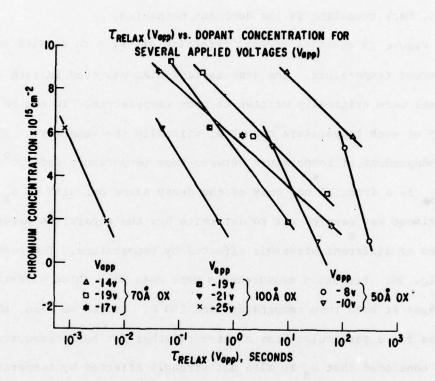

It should be noted that several of the measurements in Fig. 7-1 were carried out at  $100^{\circ}$ C instead of room temperature. These points coincide with the room temperature measurements indicating that at  $100^{\circ}$ C activated charge conduction through the nitride does not yet play a major role in these devices. As was found for the write characteristics curves, the decay slopes and spacings do not differ greatly from device to device over the range of dopants, concentrations, and oxide thicknesses investigated. Thus, the decay slopes are of the order of 2V/dec for poorly retaining devices and 1 V/dec for highly retaining ones. The spacing  $b_R$  varies from about 0.30 dec/volt for the less retentive devices to about 0.60 dec/volt for the more retentive ones. By far the most sensitive parameter is  $\tau_{\rm relax}$  ( $V_{\rm b}$  = 0), which has been found to vary over nearly 20 orders of magnitude depending on doping and oxide thickness. THE EFFECT OF OXIDE THICKNESS

$au_{

m relax}$  ( $V_{

m b}$  = 0) for the chromium doped device described in Fig. 7-1 is 1.9 x 10<sup>9</sup> seconds, or 60 years. This is not an uncommonly high value. Table 7-1 contains a list of the four important retention parameters, including  $au_{

m relax}$  ( $V_{

m b}$  = 0), for devices studied in the course of Phase I of this program.  $au_{

m relax}$  ranges from a low of 5.3 seconds to 8.5 x 10<sup>9</sup> years. This extreme variation in charge retention is largely a function of oxide thickness. If devices are compared in Table 7-1 which have the same dopant and concentration, there are many examples where the device with the thicker oxide has the higher retention.

TABLE 6

Retention Parameters for the Six Promising Dopants

|         | Dop. conc.                          | •   | , p      | Decay    |                        | Retention               |                        |

|---------|-------------------------------------|-----|----------|----------|------------------------|-------------------------|------------------------|

| pant    | x 10 <sup>15</sup> cm <sup>-2</sup> | d x | dec/volt | volt/dec | Trelax, secs           | V <sub>T</sub> initial* | tR' sec                |

| -       | 8.6                                 | 53  | 0.18     | 2.1      | $3 \times 10^1$        | 100                     | $3.2 \times 10^{5}$    |

|         | 2.95                                | 23  | 0.36     | 2.7      | 3.5 × 10 <sup>4</sup>  | 100                     | 4.2 × 107              |

|         | 8.6                                 | 134 | 0.48     | 1.1      | $3.0 \times 10^{5}$    | 100                     | $5.7 \times 10^{14}$   |

| •       | 2.95                                | 134 | 0.58     | 1.1      | 5.0 × 10 <sup>8</sup>  | 10v                     | 4.7 × 10 <sup>17</sup> |

| -5      | 0.77                                | 19  | 0.62     | 1.2      | 1.0 x 10 <sup>10</sup> | 7                       | $1.2 \times 10^{15}$   |

|         | 0.77                                | 134 | 0.50     | 1.2      | 5.0 × 10 <sup>9</sup>  | 77                      | 3.2 × 10 <sup>14</sup> |

| -14 in  | 5.2                                 | 36  | •        | 1.18     | 8 × 10 <sup>1</sup>    | Λ7 ~                    | 4.0 × 10 <sup>5</sup>  |

| -14 in  | 1.1                                 | 36  | •        | 1.18     | 5.3                    | 3.50                    | $5.0 \times 10^3$      |

| -15 tn  | 1.1                                 | 20  | 0.45     | 1.13     | 8.7 × 10 <sup>5</sup>  | 5.30                    | 4.0 × 10 <sup>10</sup> |

| -15 in  | 5.4                                 | 20  | 0.45     | 1.4      | 1.0 × 10 <sup>7</sup>  | 5.2V                    | 4.6 × 1010             |

| -14 out | 5.2                                 | 43  | •        | 1.0      | 8.5 × 10 <sup>1</sup>  | 5.40                    | 1.1 × 10 <sup>8</sup>  |

| -14 out | 1.1                                 | 43  | 0.38     | 1.34     | $3.1 \times 10^3$      | 5.15v                   | 1.2 × 107              |

| -15 out | 1.1                                 | 57  | 1.0      | 0.68     | 8.0 × 10 <sup>10</sup> | 5.20                    | 4.0 × 10 <sup>18</sup> |

| -15 out | 5.4                                 | 57  | 1.0      | 0.72     | 3.0 × 109              | 5.70                    | 4.1 × 10 <sup>17</sup> |

| 11      | 1.4                                 | 59  | 0.15     | 3.8      | $8.3 \times 10^2$      | 6.5v                    | 4.0 × 104              |

|         | 0.23                                | 59  | 0.13     | 3.8      | $3.2 \times 10^{3}$    | 6.5V                    | $1.7 \times 10^5$      |

| 39      | 0.55                                | 63  | 09.0     | 1.0      | $3.1 \times 10^{12}$   | 6.00                    | 1.0 × 10 <sup>18</sup> |