# AD A 053269

ODC FILE COPY

BUS INTERFACE UNIT DESIGN FOR THE DISTRIBUTED PROCESSOR/MEMORY SYSTEM

THESIS

AFIT/GE/EE/77-24

Leslie T. Konno Captain USAF

Approved for public release; distribution unlimited.

AFIT/GE/EE/77-24

## BUS INTERFACE UNIT DESIGN FOR THE DISTRIBUTED PROCESSOR/MEMORY SYSTEM

#### THESIS

Presented to the Faculty of the School of Engineering of the Air Force Institute of Technology Air University in Partial Fulfillment of the Requirements for the degree of Master of Science

by

Leslie T. Konno, B.S.E.E. Captain USAF

Graduate Electrical Engineering December 1977

Approved for public release; distribution unlimited.

PREFACE

This study was sponsored by the Air Force Avionics Laboratory, System Technology Branch, Software and Processor Group, as part of the development of the Distributed/Processor Memory (DP/M) system. This is a system to integrate the avionics on board an aircraft with a group of processor/ memory elements (microprocessors) in a distributed (decentralized) network. The purpose of the study is to design the Bus Interface Unit (BIU) for the processor/memory element. The BIU is designed as an interrupt driven microprocessor.

I want to express my appreciation to Captain J. B. Peterson, my thesis advisor, for his guidance throughout this study, and to Deiter Schiller from the Avionics Laboratory for his help in understanding the DP/M system. I want to also express my appreciation to Flight Lieutenant Ejaz Muhammad. He was involved in the design of the central processor unit for the processor/memory element; and together we learned the DP/M system and the Am2900 Bipolar Microprocessor Family, which was used in the design. Finally, I want to pay tribute to the patience and understanding of my wife, JoAnn, and daughters, Christine and Cheryl, during the time spent on this study and during my tour at the Air Force Institute of Technology.

Leslie T. Konno

ACCESSION for .... 326 UNARNOUNCE. INSTIFICAT BISTRIBUTO"/ CARLENDY GOURS STIL SERVER SPLITAL

0

ii

# Contents

0

0

| <u> </u>                                                  | age      |

|-----------------------------------------------------------|----------|

| Preface                                                   | ii       |

| List of Figures                                           | v        |

| List of Tables                                            | iii      |

| Abstract                                                  | x        |

|                                                           |          |

| I. Introduction                                           | 1        |

| Background                                                | 1        |

| DP/M System Concept                                       | 3        |

| BIU Functional Description                                | 5        |

| The Problem and Approach                                  | 7        |

| Thesis Outline                                            | 8        |

|                                                           |          |

| II. BIU System Description                                | 10       |

| Introduction                                              | 10       |

| Introduction.                                             | 10       |

| Global/Local Message Structure                            | 10       |

| Bus Data Translation Function                             | 14       |

| Message Reception Control Function.                       | 17       |

| Message Transmission Control Function                     | 23       |

| Bus Access Control Function                               | 23       |

| Processor/Memory Interface Function                       | 25<br>26 |

| I-Bus Description.                                        | 20       |

| Direct Memory Access Function.                            | 28       |

| Program-Command Response Function.                        | 33       |

| Interrupt Interface/Control Function                      | 33       |

| Summary.                                                  | 38       |

|                                                           | 50       |

|                                                           |          |

| III. BIU Design                                           | 40       |

| Introduction                                              | 40       |

| Am2900 Bipolar Microprocessor Family General Description. | 40       |

| BIU Architecture.                                         | 42       |

| Control Section                                           | 47       |

| Interrupt Control Unit                                    | 47       |

| Vector Mapping PROM                                       | 52       |

| Microprogram Controller                                   | 52       |

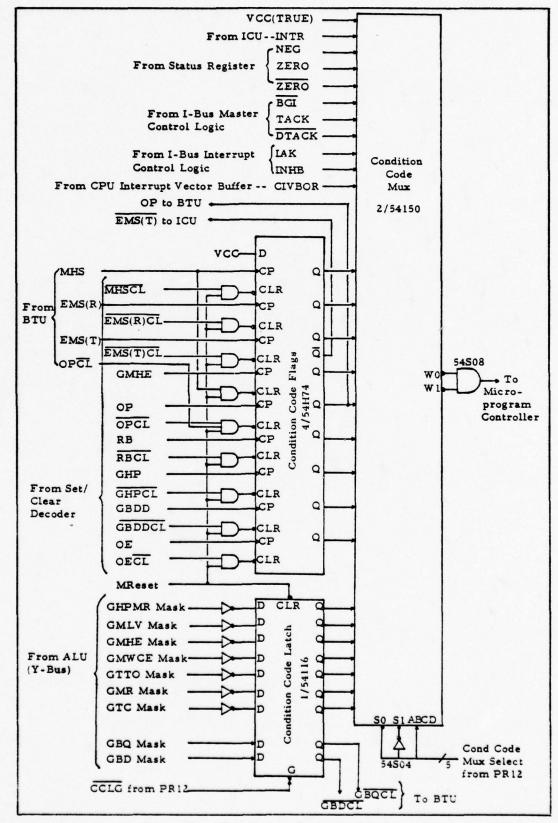

| Condition Code Multiplexer                                | 54       |

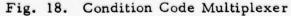

| CAW Mapping PROM                                          | 56       |

| Microprogram PROM                                         | 58       |

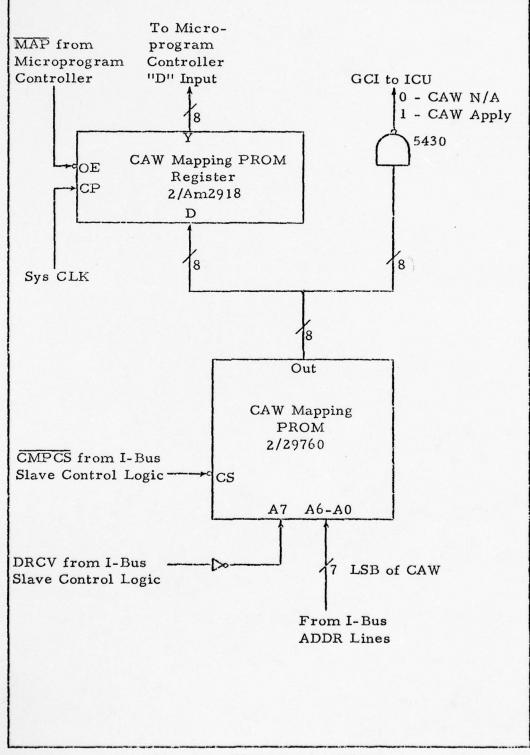

| Pipeline Register                                         | 58       |

| Set/Clear Decoder                                         | 60       |

| BIU Stack.                                                | 60       |

## Page

|          | Data     | Manipulati   | on Sec   | ctio | n.   |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 60  |

|----------|----------|--------------|----------|------|------|-----|-----|-----|-----|---|---|---|---|----|---|---|---|---|---|---|-----|

|          | A        | rithmetic L  | ogic l   | Jnit |      |     |     |     |     |   |   |   |   |    |   |   |   |   | - |   | 60  |

|          | S        | tatus Regis  | ter .    |      |      |     |     |     |     |   |   |   |   |    | - |   |   |   |   |   | 65  |

|          | B        | IU PROM and  | PROM     | Add  | res  | s F | lea | ist | ter | - |   | - |   |    |   |   | • | • | • | • | 65  |

|          | R        | esponse Bit  | Regis    | ter  | an   | d i | )ec | ode | ar  |   | • |   |   | •  | • | • | • | • | • | • | 65  |

|          | I-Ru     | s Interface  | Sect     | ion  |      |     |     | ou  |     | • | • | • | • | •  | • | • | • | • | • | • | 66  |

|          | I Du.    | -Bus Regist  | ore      |      | •    | • • | •   | •   | •   | • | • | • | • | •  | • | • | • | • | • | • | 66  |

|          | T.       | -Bus Master  | Conto    |      | 1.00 | i.  | •   | •   | •   | • | • | • | • | •  | • | • | • | • | • | • |     |

|          | T        | -Dus Master  | Contro   | 11   | LUY  | 10. | •   | •   | •   | • | • | • | • | •  | • | • | • | • | • | • | 70  |

|          | 1        | -Bus Slave   | t Contro |      | Ugi  | с.  | •   | •   | •   | • | • | • | • | •. | • | • | • | • | • | • | 73  |

|          | Clob     | PU Interrup  | LUI      | croi | LO   | gic | •   | •   | •   | • | • | • | • | •  | • | • | • | • | • | • | 75  |

|          | GIOD     | al Bus Inte  | rtace    | Sec  | τ10  | n.  | •   | •   | •   | • | • | • | • | •  | • | • | • | • | • | • | 75  |

|          | B        | us Length R  | egiste   | er.  | •    | • • | •   | •   | •   | • | • | • | • | •  | • | • | • | • | • |   | 77  |

|          | B        | us Position  | Regis    | ster | •    | • • | •   | •   | •   | • | • | • | • | •  | • | • | • | • | • |   | 77  |

|          | 0        | utput Data   | Buffer   | °    | •    |     | •   |     | •   |   |   |   |   |    | • |   |   |   |   |   | 79  |

|          | Summa    | ary          |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 79  |

|          |          |              |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   |     |

|          |          |              |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   |     |

| IV M     | icroco   | ding         |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 81  |

|          |          |              |          |      |      |     |     | •   |     |   |   |   |   |    |   |   |   |   |   |   |     |

|          | Intro    | oduction .   |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 81  |

|          | Micro    | oword Forma  | t        |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 81  |

|          | Micro    | oroutines.   |          |      |      |     |     |     |     |   |   | - |   |    |   |   |   |   |   | • | 95  |

|          | Summa    | ary          |          |      |      |     |     |     |     |   |   |   | • | •  | • | • | • | • | • | • | 97  |

|          | C Chinan |              |          | •••  | •    | • • | •   | ·   | •   | • | • | • | • | •  | • | • | • | • | • | • | 51  |

|          |          |              |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   |     |

| V D      | iscuss   | ion And Con  | clusic   | ne   |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 98  |

|          | 150455   | ion mild con | crusic   |      | •    | • • | •   | •   | •   | • | • | • | • | •  | • | • | • | • | • | • | 90  |

|          | Dicc     | uccion       |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 00  |

|          | DISCI    | ussion       |          | • •  | •    | • • | •   | •   | •   | • | • | • | • | •  | • | • | • | • | • | • | 98  |

|          | De       | esign Summa  | ry       |      | •    | • • | •   | •   | •   | • | • | • | • | •  | • | • | • | • | • | • | 98  |

|          | 5        | pecificatio  | n Devi   | ati  | ons  | • • | •   | •   | •   | • | • | • | • | •  | • | • | • | • | • | • | 99  |

|          | A        | dditional W  | ork Ke   | rupe | red  | • • | •   | •   | •   | • | • | • | • | •  | • | • | • | • | • | • | 104 |

|          | Re       | ecommendati  | ons.     | • •  | •    | • • | •   | •   | •   | • |   |   | • | •  |   | • |   | • | • | • | 105 |

|          | Conc     | lusions      |          | • •  | •    |     | •   | •   | •   | • |   |   | • | •  |   | • | • | • | • |   | 110 |

|          |          |              |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   |     |

| Bibliog  | raphy.   |              |          | • •  |      |     | •   |     |     |   |   |   | • |    |   |   |   |   |   |   | 111 |

|          |          |              |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   |     |

| Appendi  | x A: (   | Glossary of  | Abbre    | evia | tio  | ns. |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 112 |

|          |          |              |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   |     |

| Appendi  | x B: 1   | BIU Microro  | utines   | i    |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 120 |

|          |          |              |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   |     |

| Appendi  | x C: I   | BIU Microco  | des .    |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 195 |

|          |          |              |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   |     |

| Appendi. | x D: 1   | Microword F  | ields    |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 207 |

|          |          |              |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 207 |

| Vita     |          |              |          |      |      |     |     |     |     |   |   |   |   |    |   |   |   |   |   |   | 220 |

|          |          |              | -        |      |      |     |     |     | -   | - | - | - | - | -  | - | - | - |   |   |   |     |

0

0

0

## List of Figures

0

0

| Figure |                                                                               | Pag | e |

|--------|-------------------------------------------------------------------------------|-----|---|

| 1      | DP/M System Architecture                                                      |     | 4 |

| 2      | BIU Functional Block Diagram                                                  |     | 6 |

| 3      | Manchester II Data/Synchronization Signal Waveforms                           | . 1 | 2 |

| 4      | Message Format                                                                | . 1 | 3 |

| 5      | Message Header Fields                                                         | . 1 | 3 |

| 6      | Message Identify Associative Addressing                                       | . 1 | 9 |

| 7      | Message Header Input                                                          | . 2 | 0 |

| 8      | Message Input Initialization                                                  | . 2 | 2 |

| 9      | Message Transmission Initialization                                           | . 2 | 4 |

| 10     | Timing for DMA Write Operation                                                | . 3 | 1 |

| 11     | Timing for DMA Read Operation                                                 | . 3 | 2 |

| 12     | Global/Local Interrupt Status Register                                        | . 3 | 7 |

| 13     | Timing for Interrupt Operation                                                | . 3 | 9 |

| 14.    | BIU Block Diagram                                                             | . 4 | 3 |

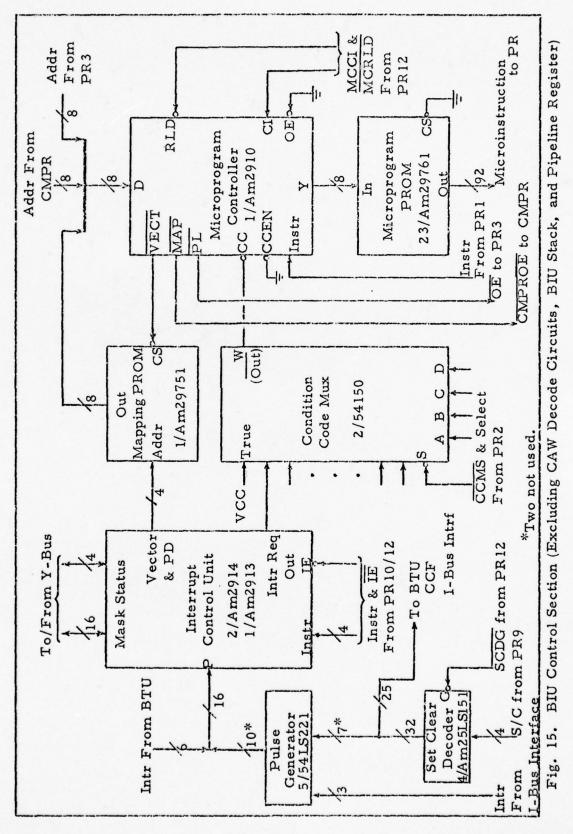

| 15     | BIU Control Section (Excluding CAW units, BIU Stack, and<br>Pipeline Register | . 4 | 5 |

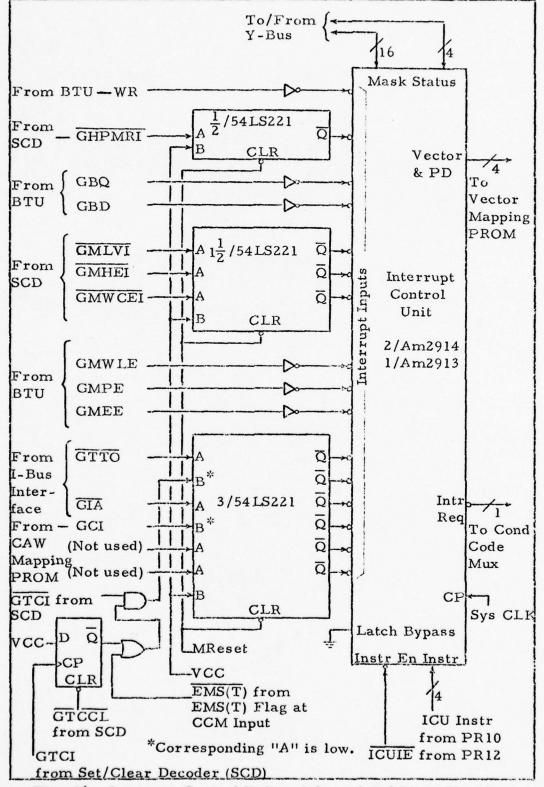

| 16     | Interrupt Control Unit and Associated Input Circuitry                         | . 4 | 8 |

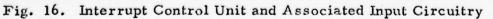

| 17     | Interrupt Control Unit and Vector Mapping PROM                                | . 4 | 9 |

| 18     | Condition Code Multiplexer                                                    | . 5 | 5 |

| 19     | CAW Mapping PROM                                                              | . 5 | 7 |

| 20     | Pipeline Register                                                             | . 5 | 9 |

| 21     | Set/Clear Decoder                                                             | . 6 | 1 |

| 22     | Data Manipulation Section (Excluding BIU Stack)                               | . 6 | 2 |

| 23     | Arithmetic Logic Unit                                                         | . 6 | 3 |

| 24     | I-Bus InterfaceI-Bus Registers                                                | . 6 | 7 |

| Figure |                                                                 | Page |

|--------|-----------------------------------------------------------------|------|

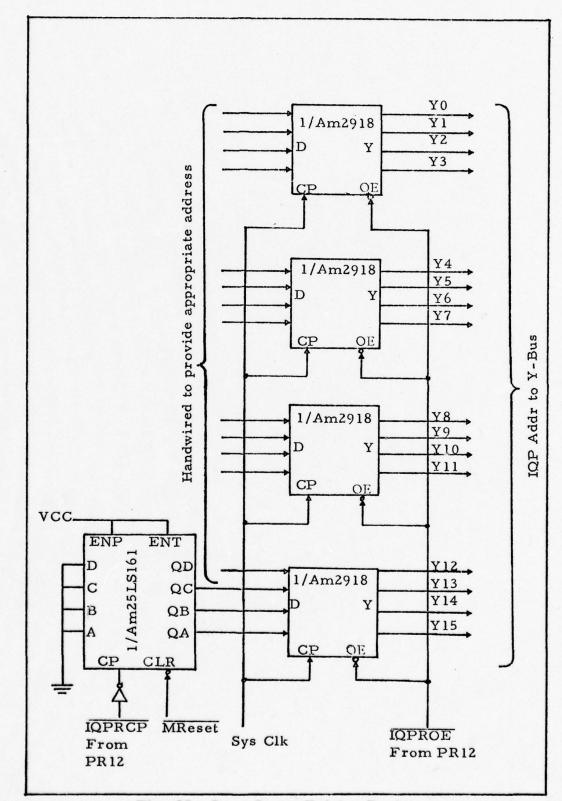

| 25     | Input Queue Pointer Register                                    | 69   |

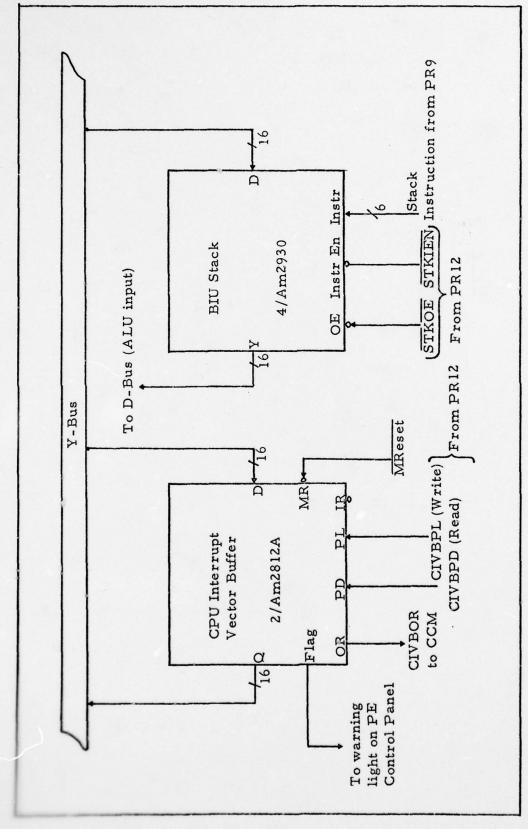

| 26     | CPU Interrupt Vector Buffer and BIU Stack                       | 71   |

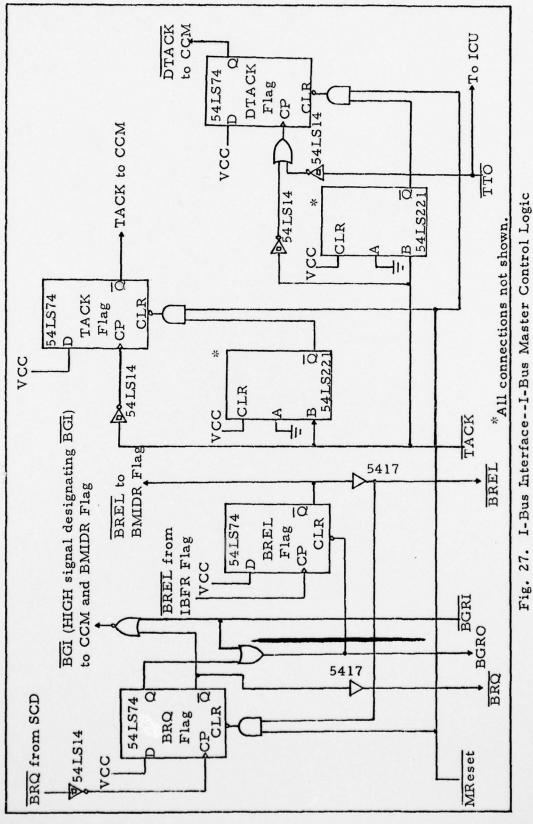

| 27     | I-Bus InterfaceI-Bus Master Control Logic                       | 72   |

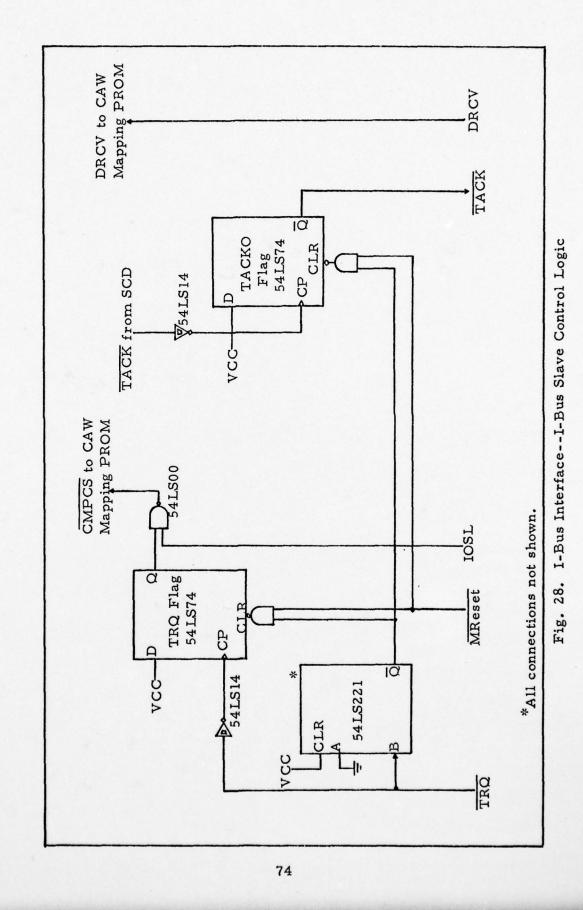

| 28     | I-Bus InterfaceI-Bus Slave Control Logic                        | 74   |

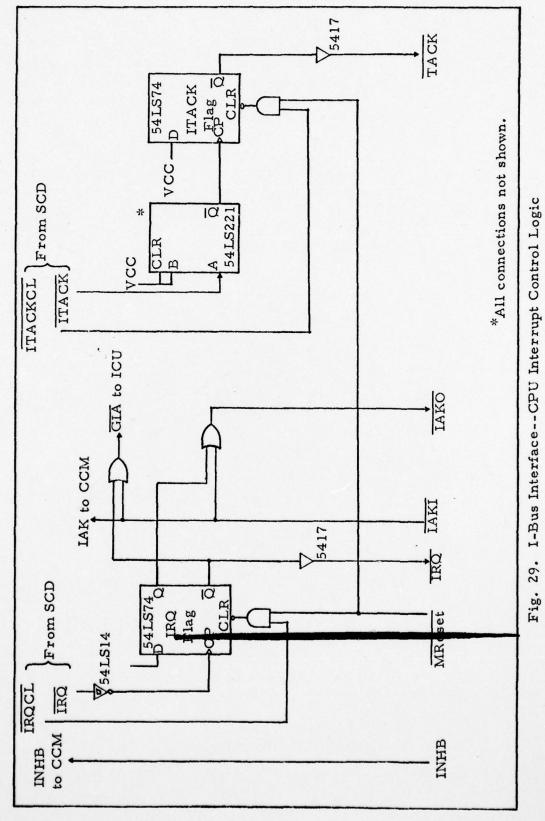

| 29     | I-Bus InterfaceCPU Interrupt Control Logic                      | 76   |

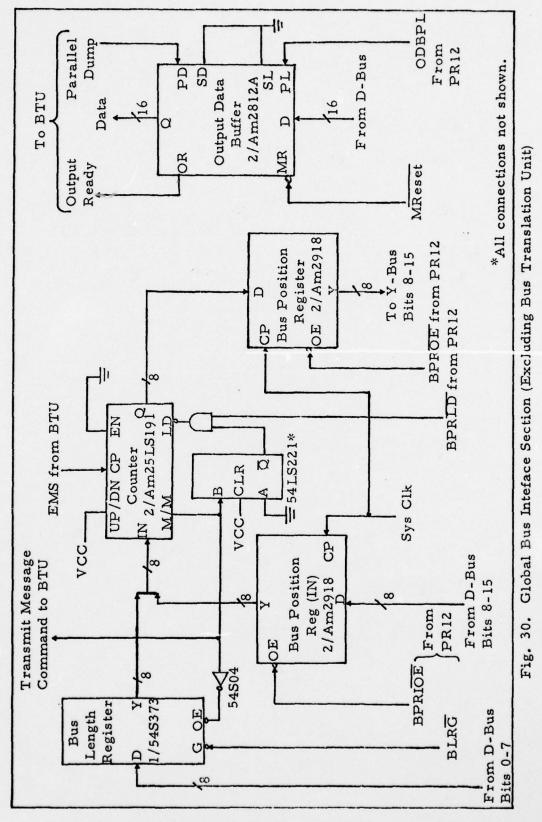

| 30     | Global Bus Interface Section (Excluding Bus Translation<br>Unit | 78   |

| 31     | Microword Format                                                | 82   |

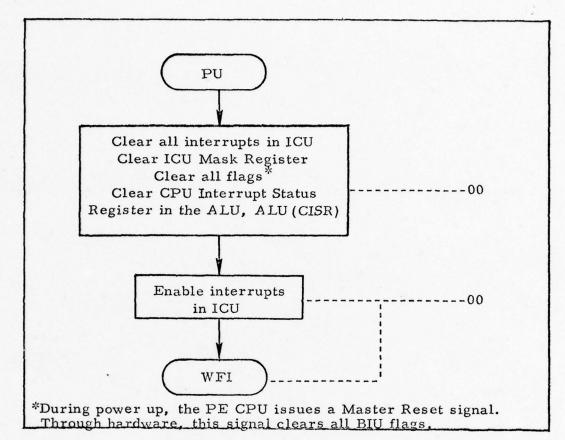

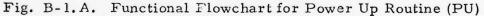

| B-1    | Power Up Routine                                                | 123  |

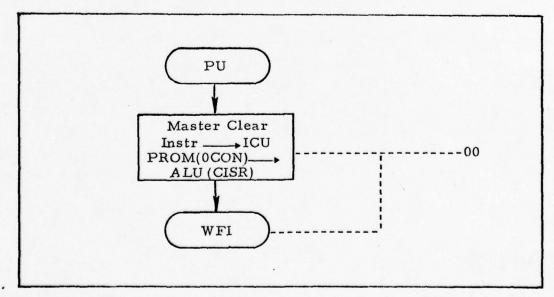

| B-2    | Wait for Interrupt Routine                                      | 124  |

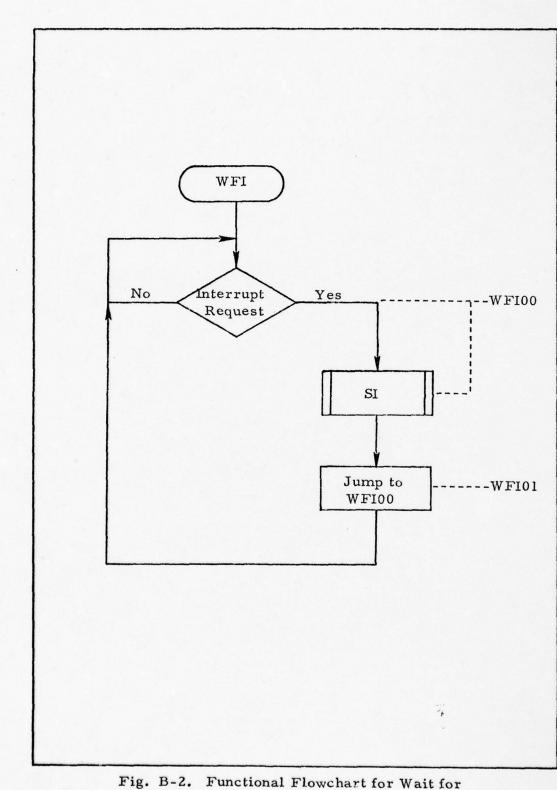

| B-3    | Service Interrupt Routine                                       | 125  |

| B-4    | Return Routine                                                  | 127  |

| B-5    | Interrupt CPU Routine                                           | 129  |

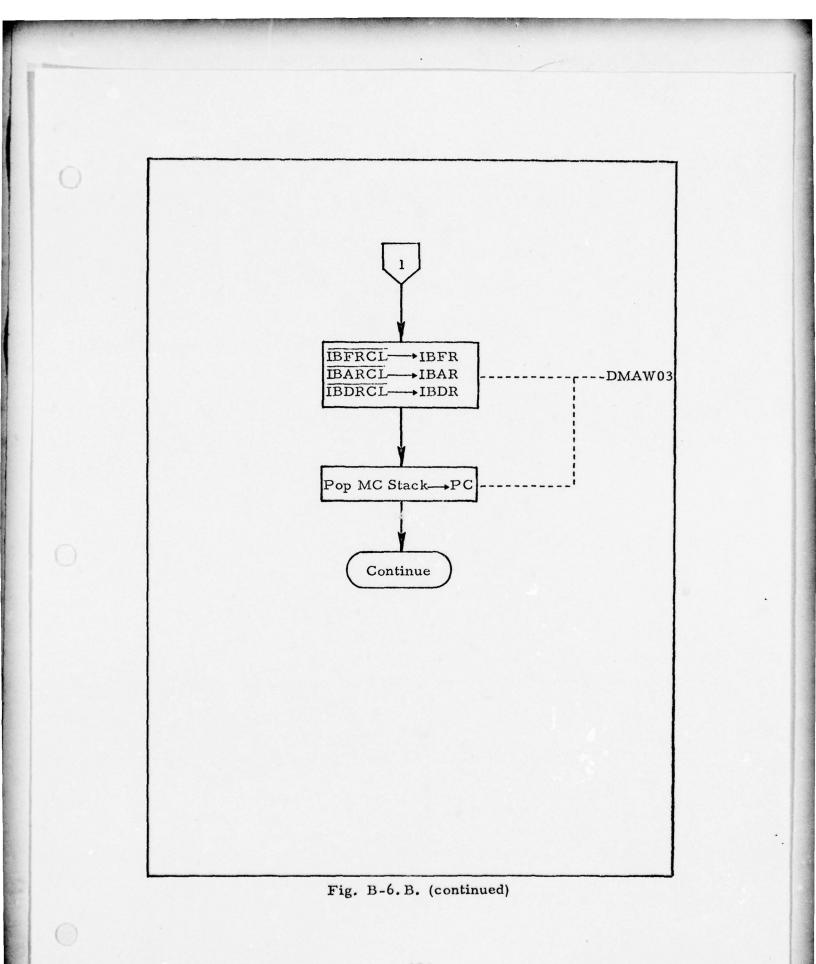

| B-6    | Direct Memory Access Write Routine                              | 131  |

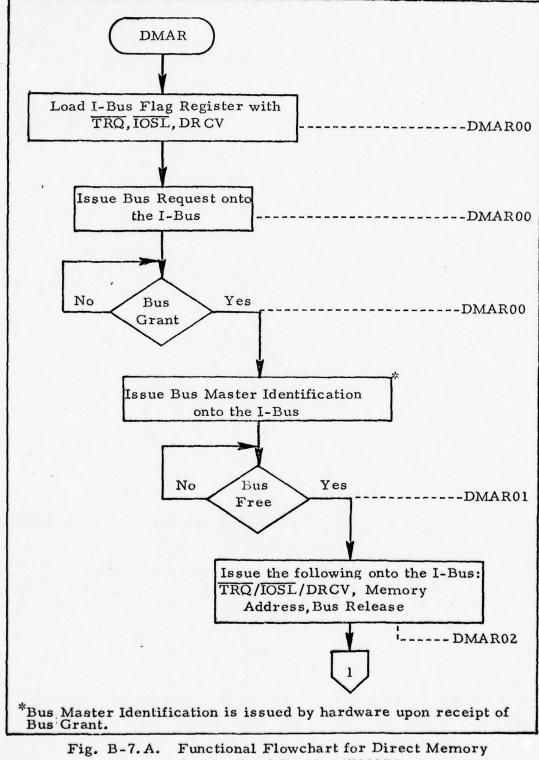

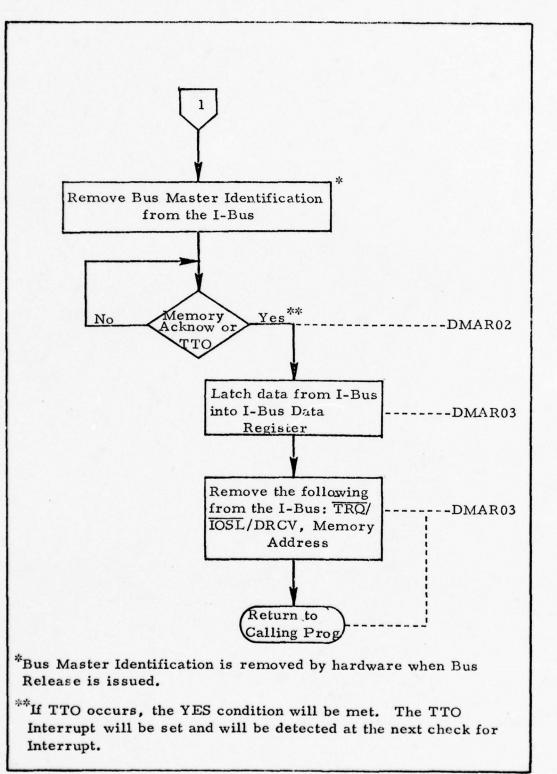

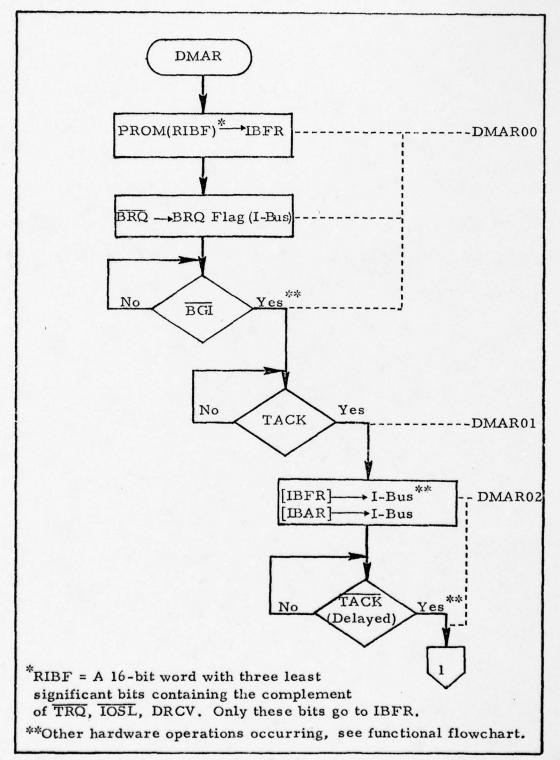

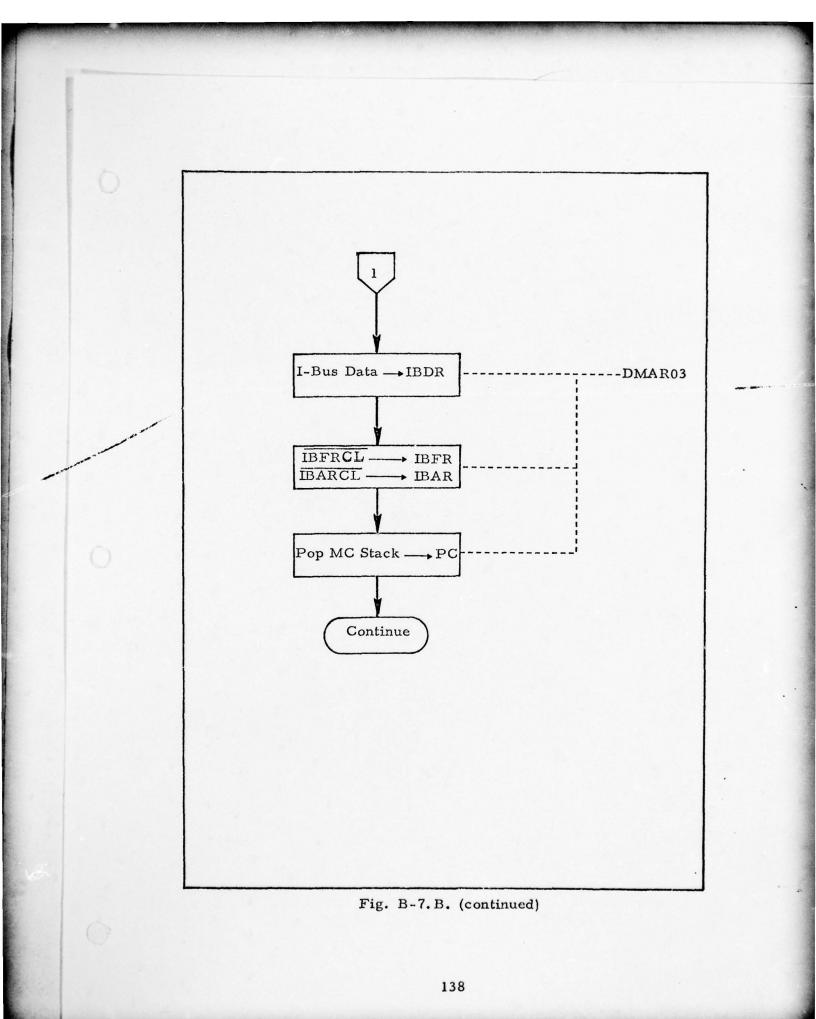

| B-7    | Direct Memory Access Read Routine                               | 135  |

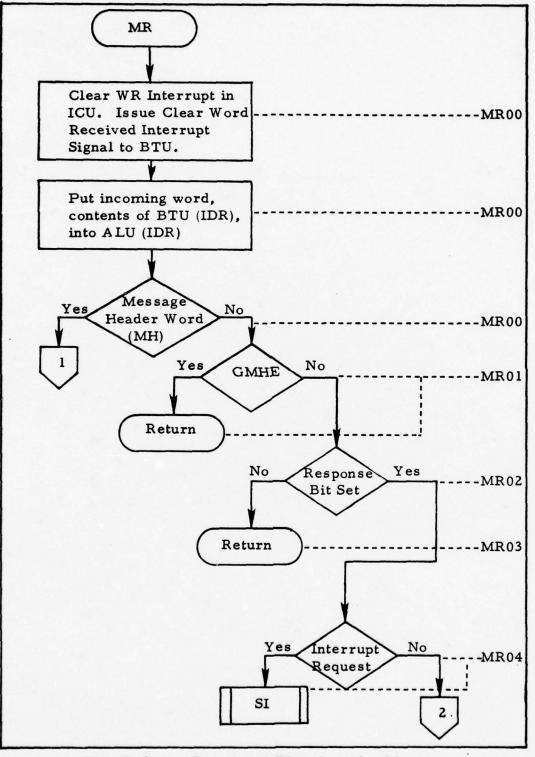

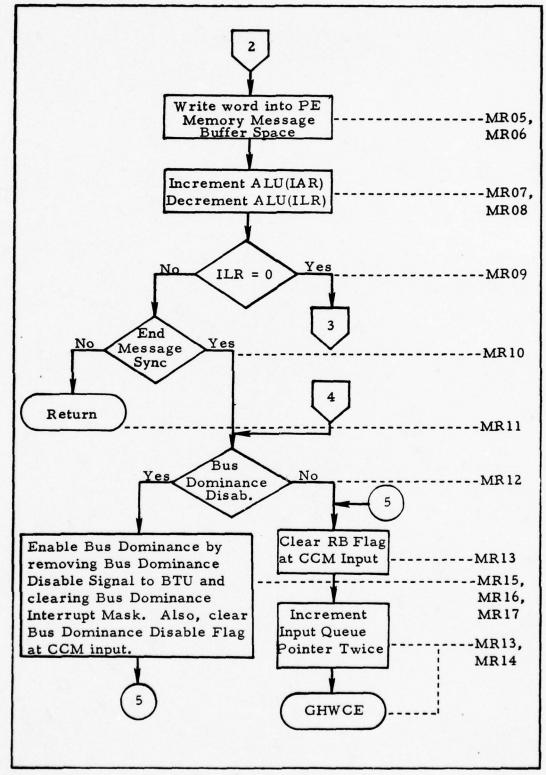

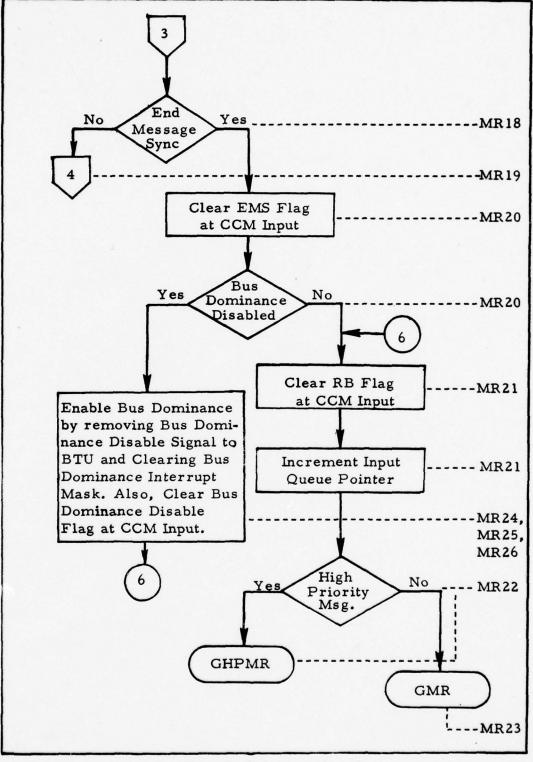

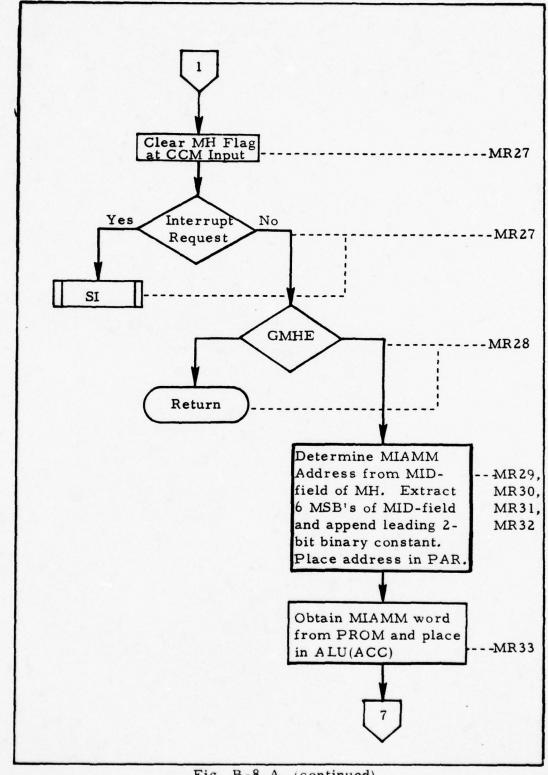

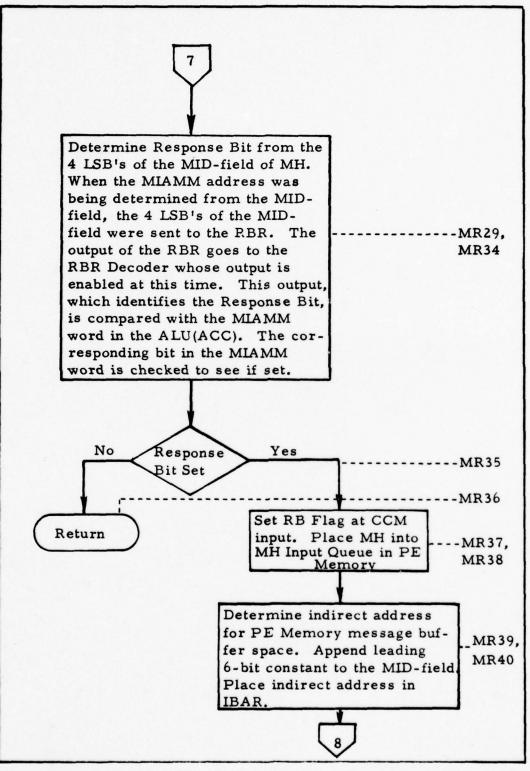

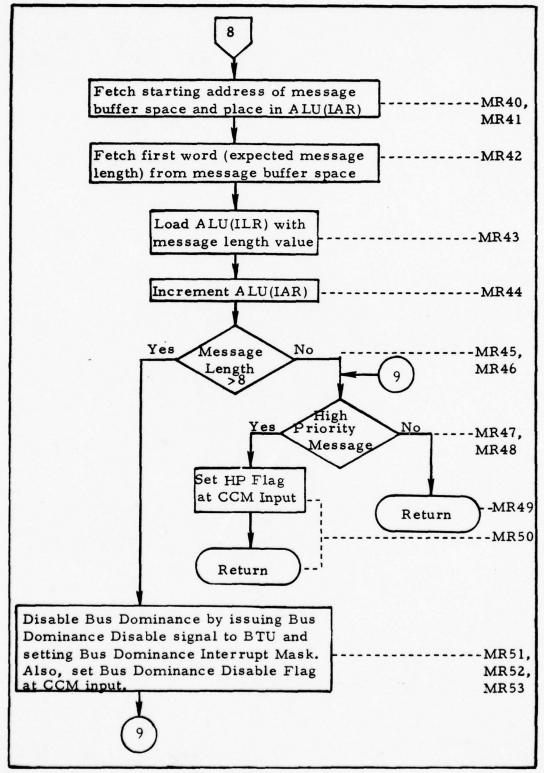

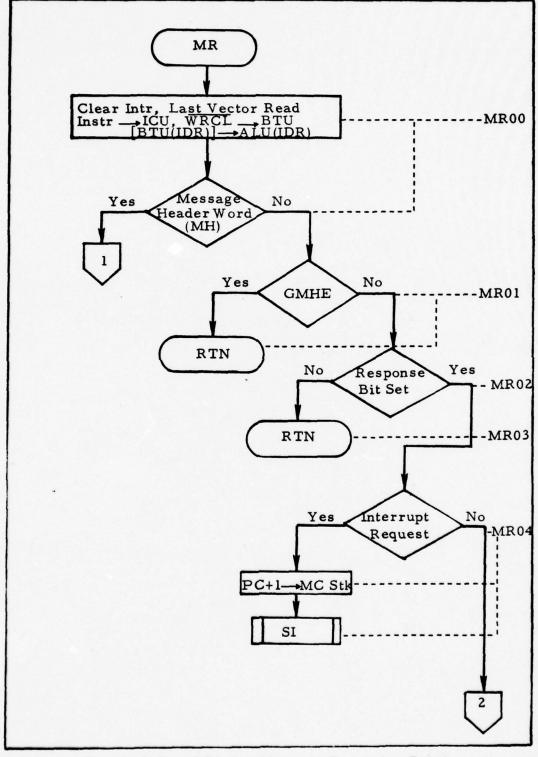

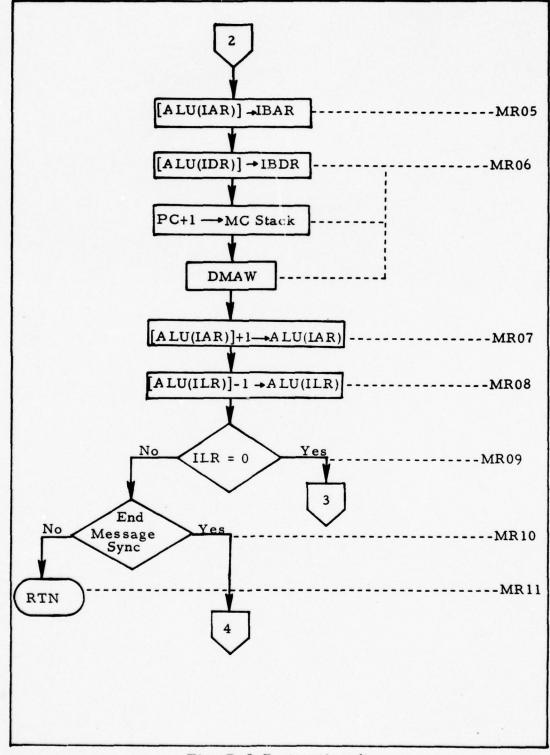

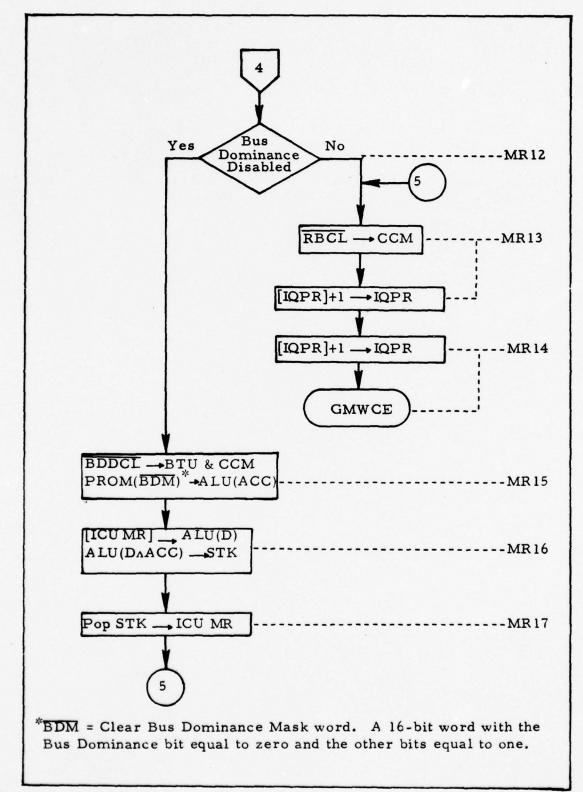

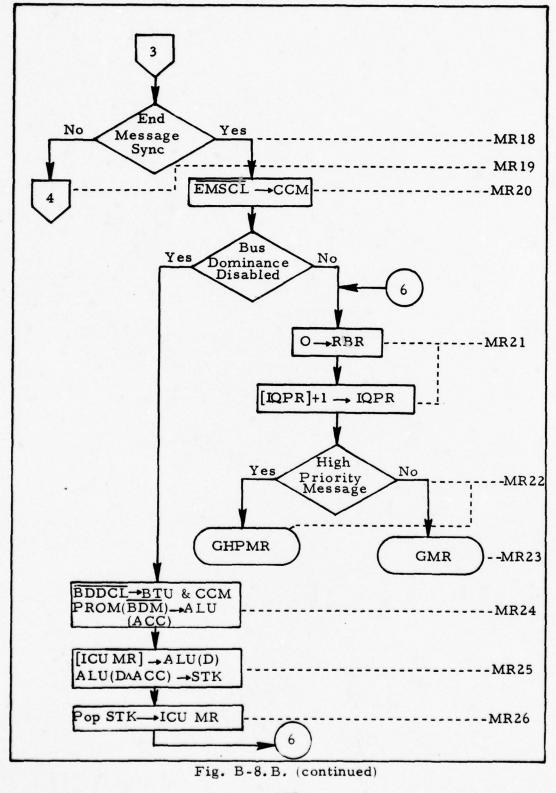

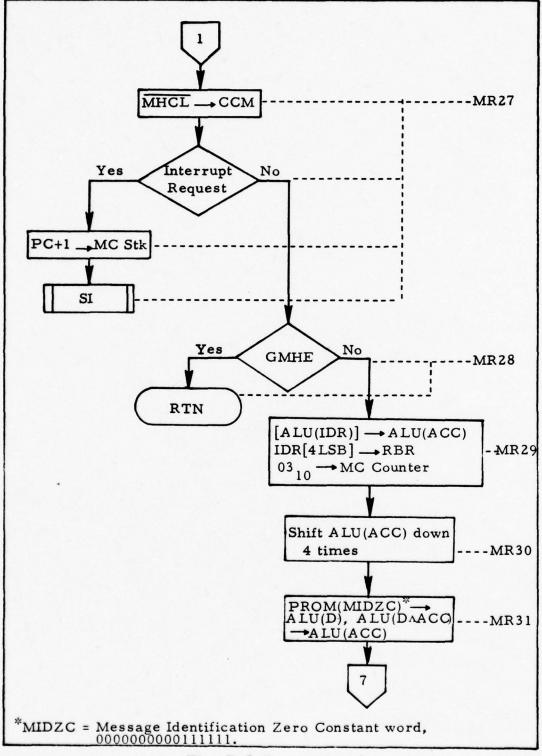

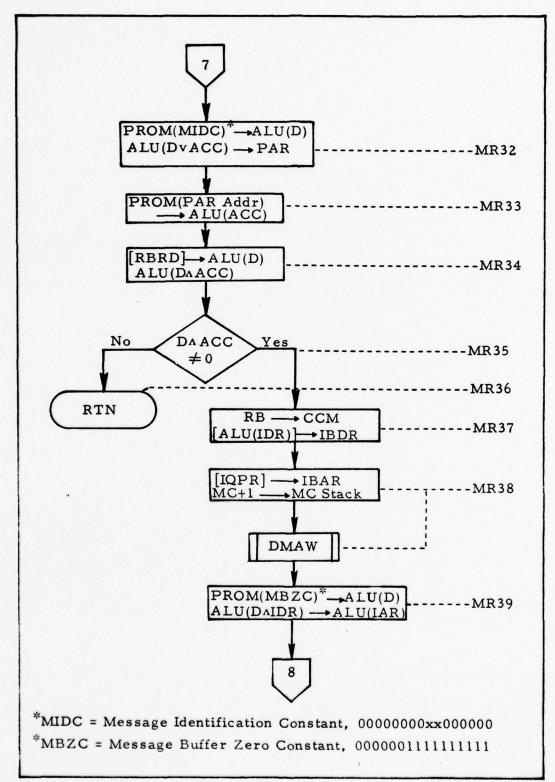

| B-8    | Message Reception Routine                                       | 139  |

| B-9    | Global Bus Quiescent Routine                                    | 153  |

| B-10   | Global Bus Dominance Routine                                    | 154  |

| B-11   | Global Message Wrod Length Error Routine                        | 155  |

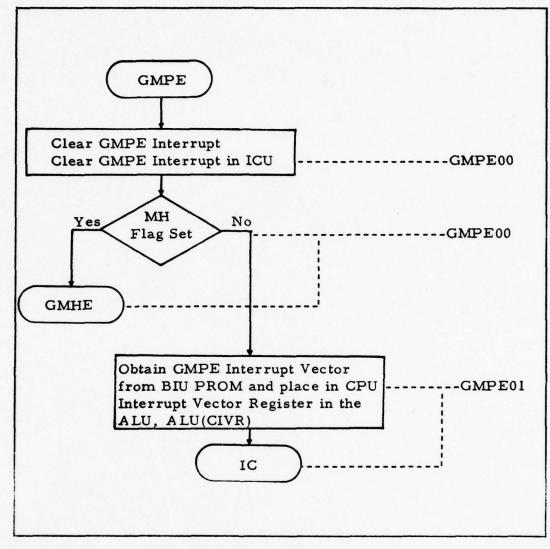

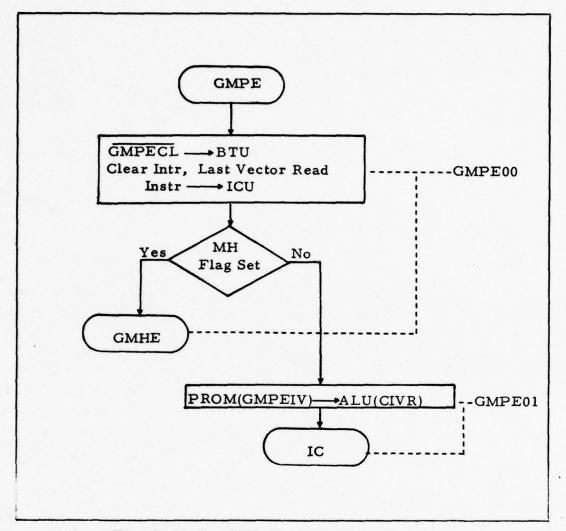

| B-12   | Global Message Parity Error Routine                             | 157  |

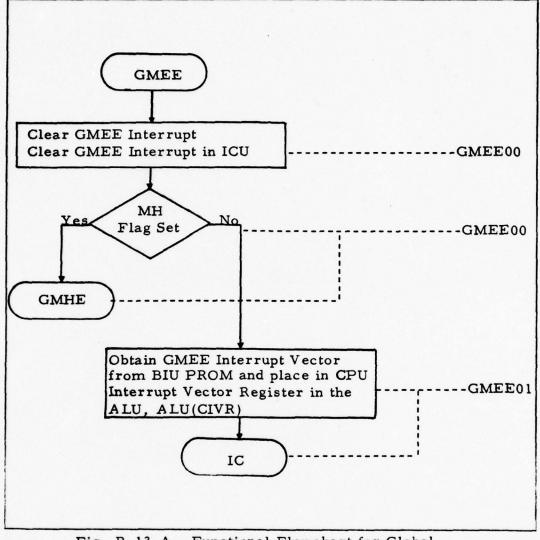

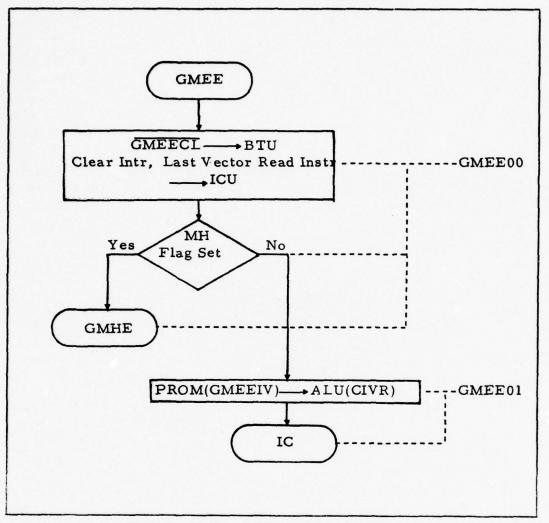

| B-13   | Global Message Encoding Error Routine                           | 159  |

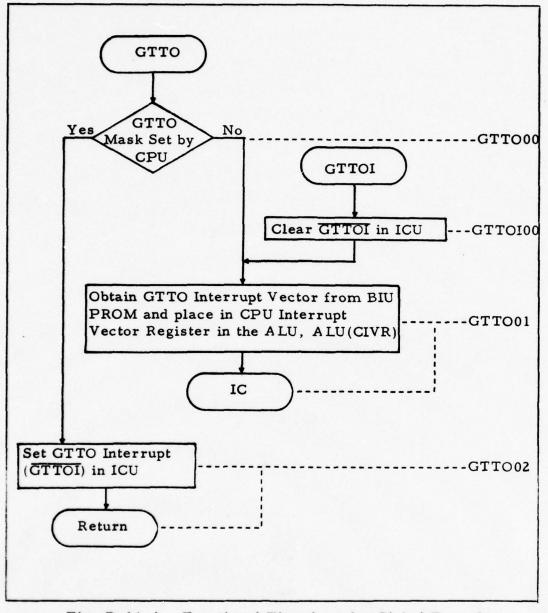

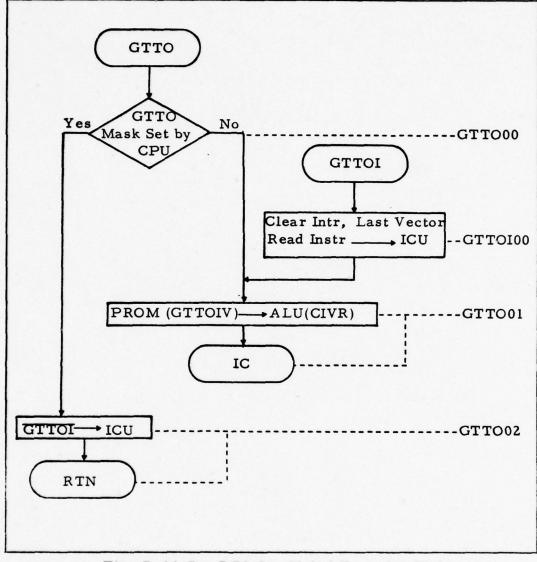

| B-14   | Global Transfer Time Out Routine                                | 161  |

| B-15   | Global CAW Interrupt Routine                                    | 163  |

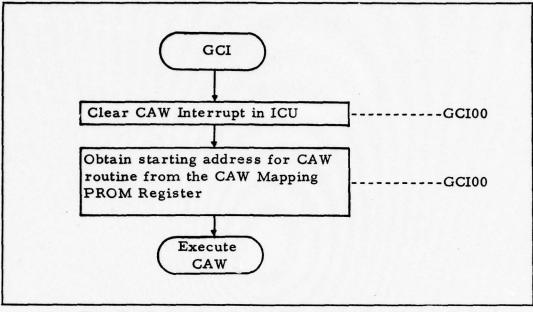

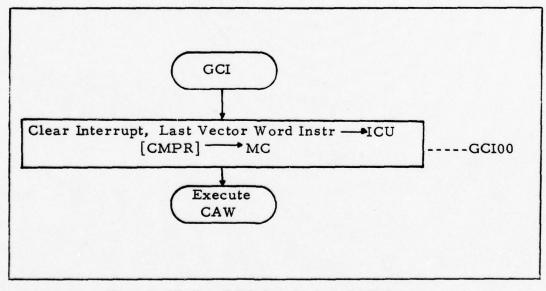

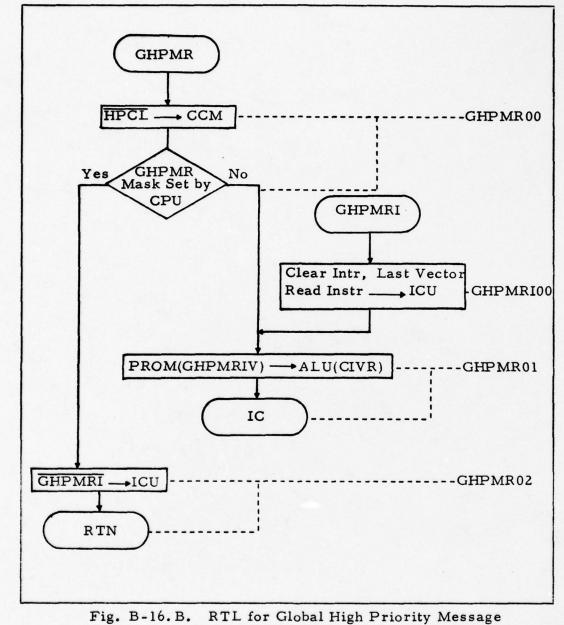

| B-16   | Global High Priority Message Received Routine                   | 164  |

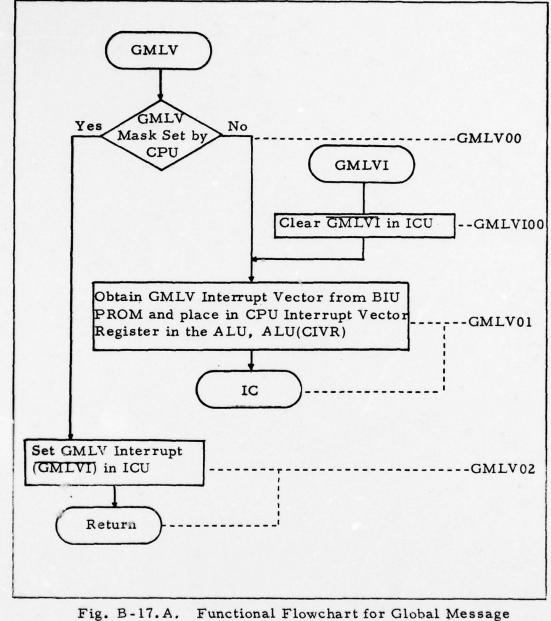

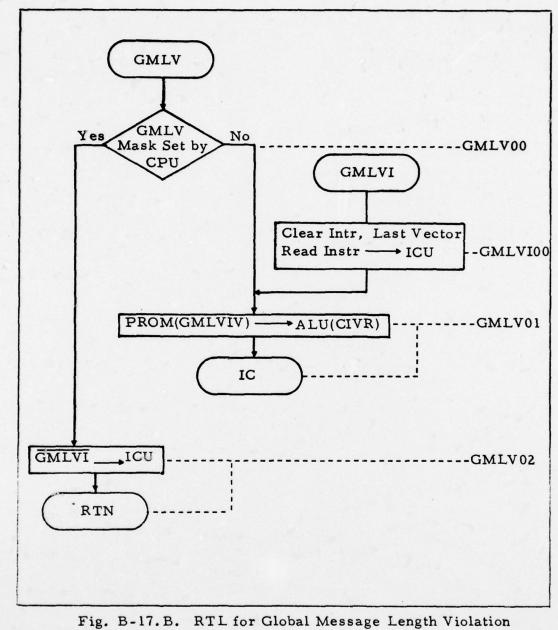

| B-17   | Global Message Length Violation Routine                         | 166  |

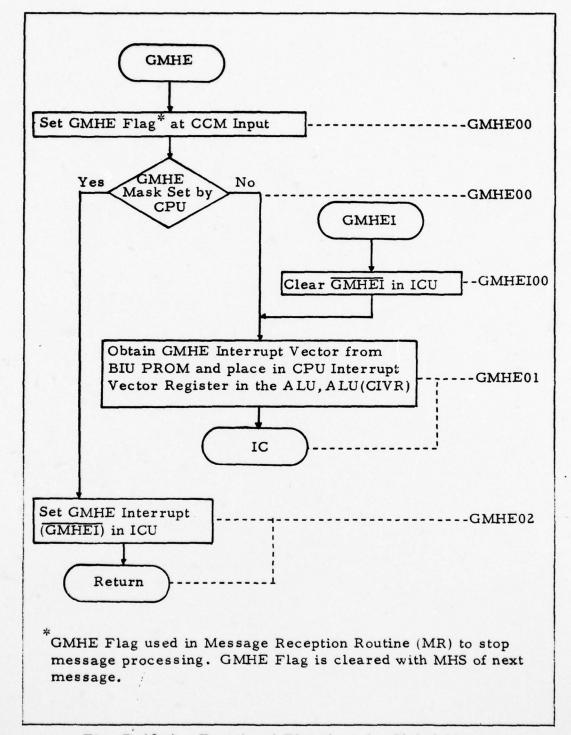

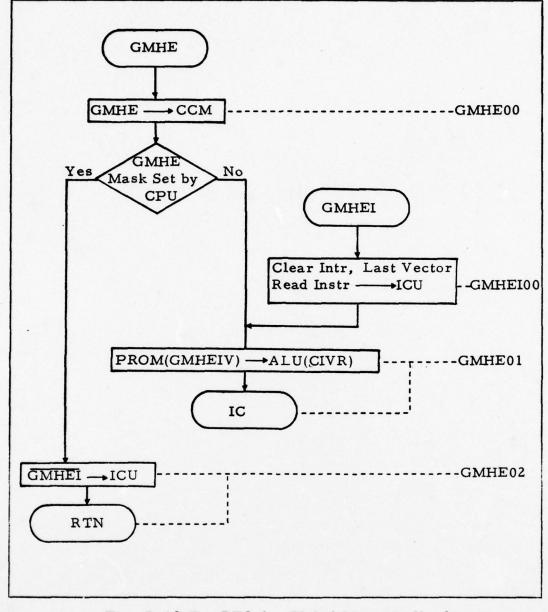

| B-18   | Global Message Header Error Routine                             | 168  |

| Figure |        |                                   |       |   |   |   |   |    |  | Page |

|--------|--------|-----------------------------------|-------|---|---|---|---|----|--|------|

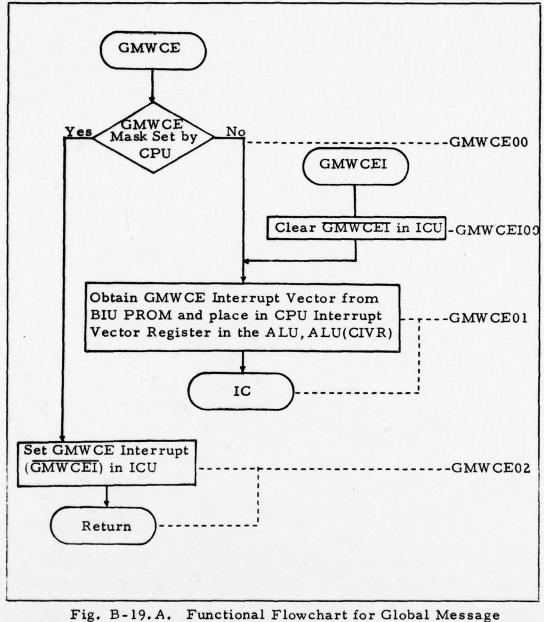

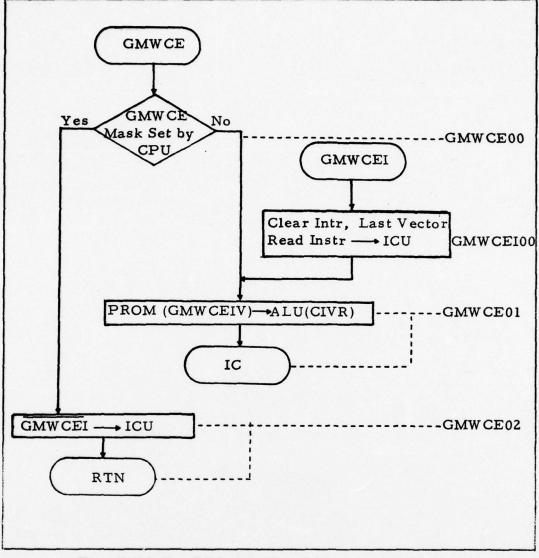

| B-19   | Global | Message Word Count Error Routine. |       | • | • | • | • |    |  | 170  |

| B-20   | Global | Message Received Routine          |       | • | • |   |   |    |  | 172  |

| B-21   | Global | Transmission Completed Routine.   |       | • |   |   |   | •  |  | 173  |

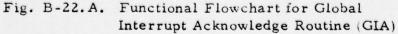

| B-22   | Global | Interrupt Acknowledge Routine     |       |   |   | • |   |    |  | 175  |

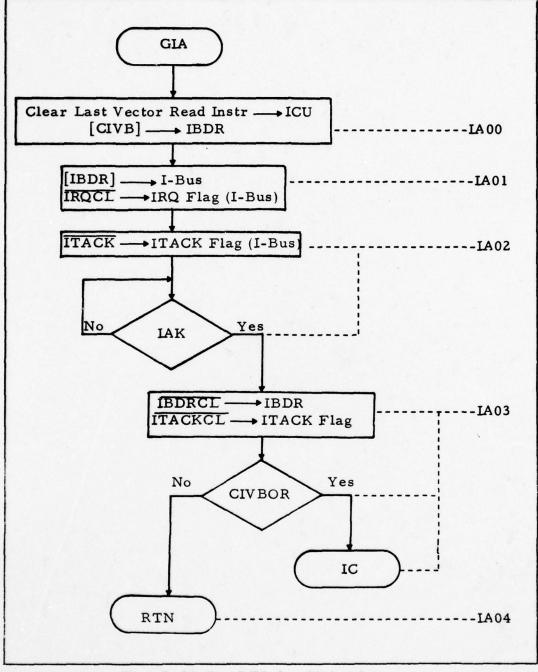

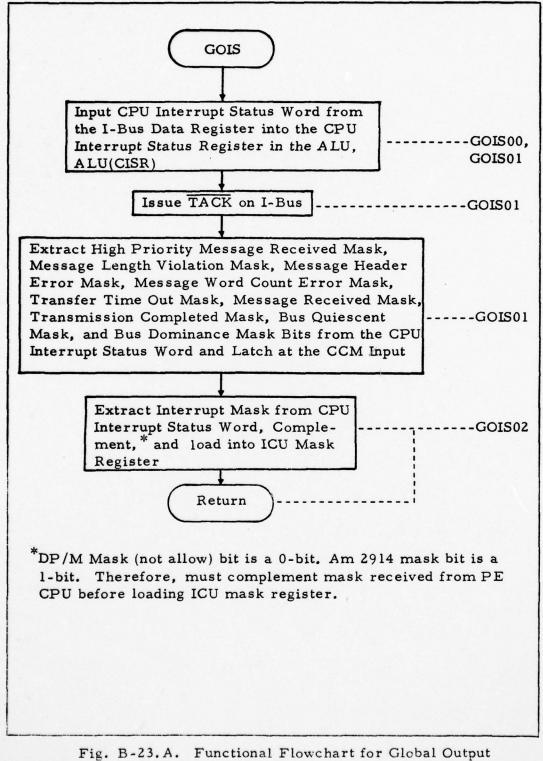

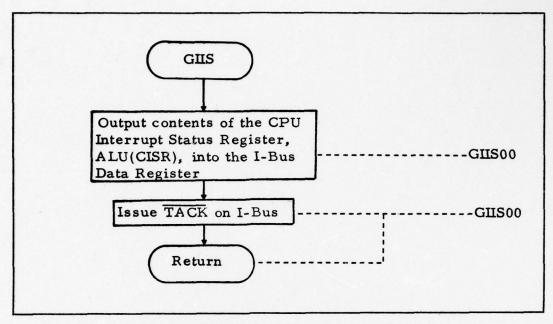

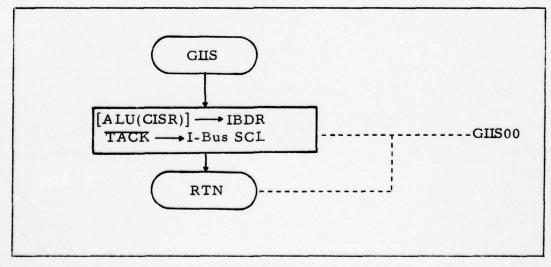

| B-23   | Global | Output Interrupt Status Routine . |       |   |   |   |   | •  |  | 177  |

| B-24   | Global | Input Interrupt Status Routine    |       |   |   |   | • | •  |  | 179  |

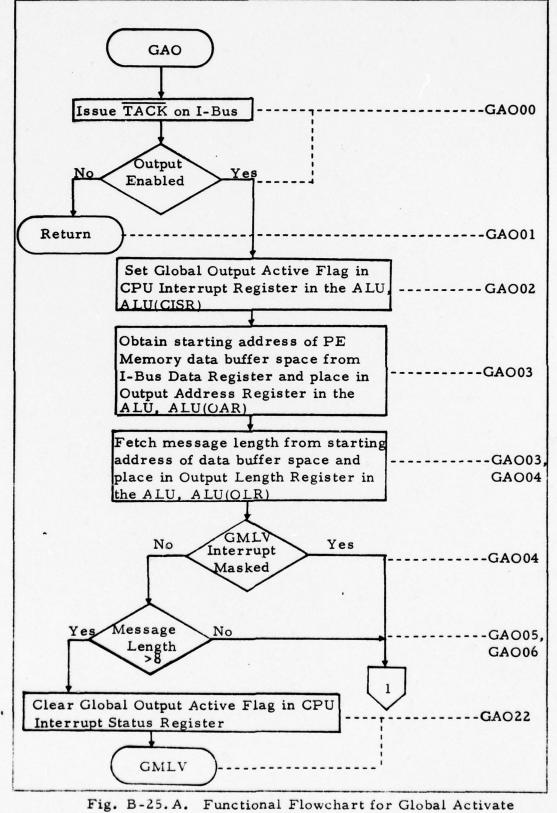

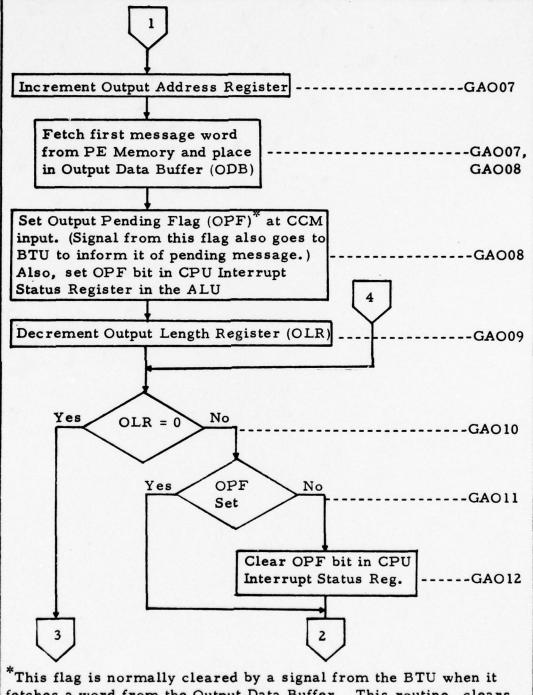

| B-25   | Global | Activate Output Routine           |       | • | • |   |   |    |  | 180  |

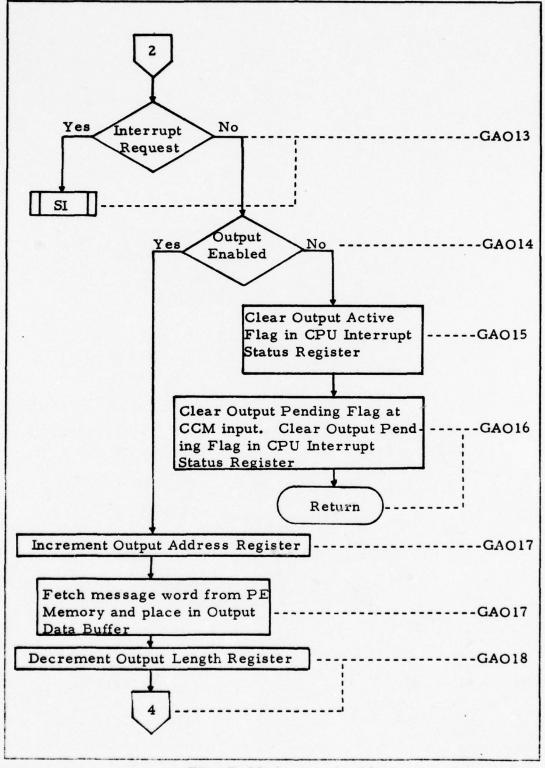

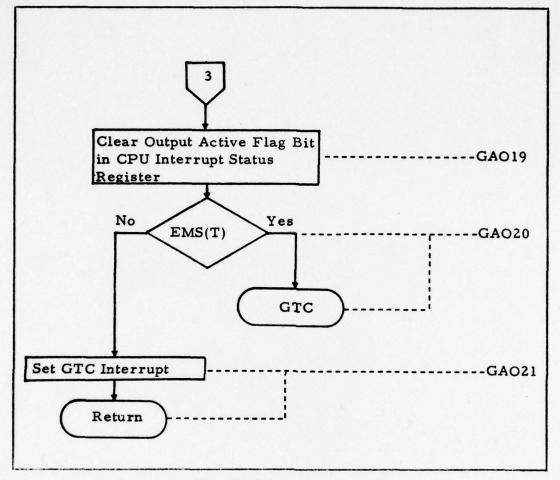

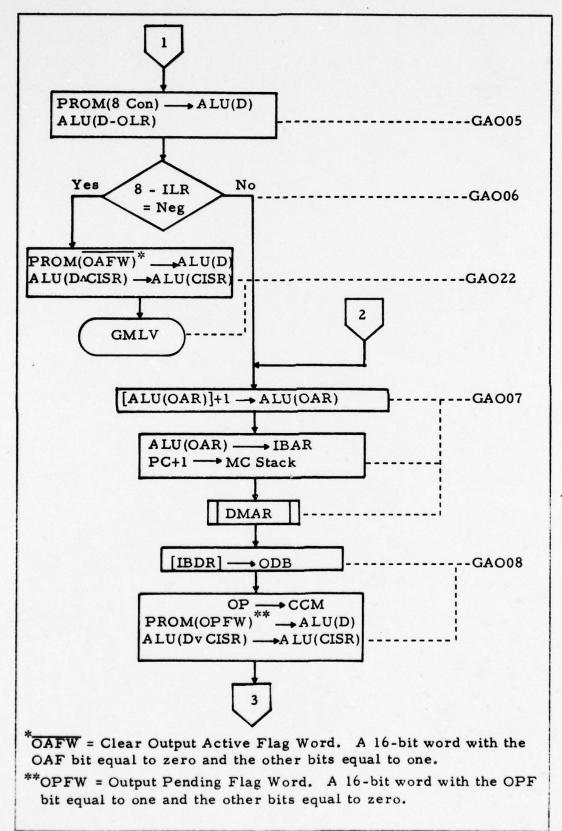

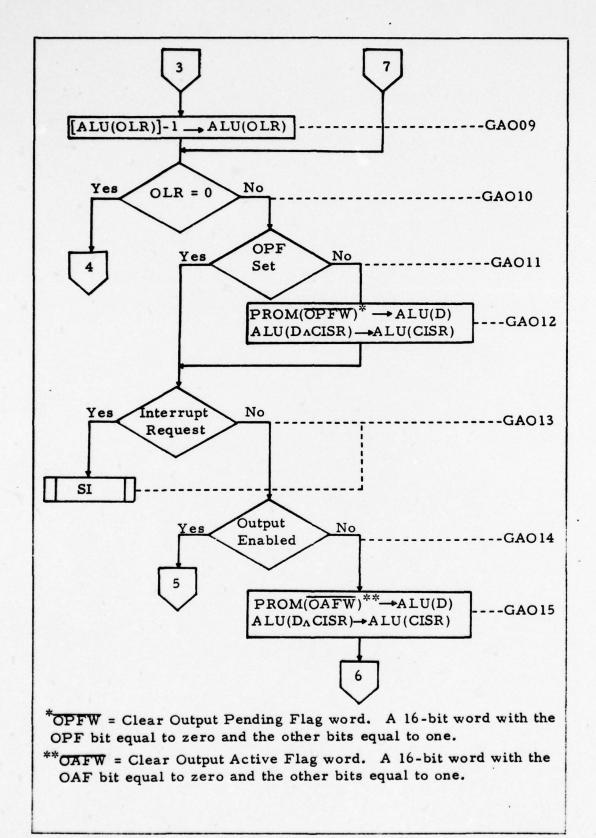

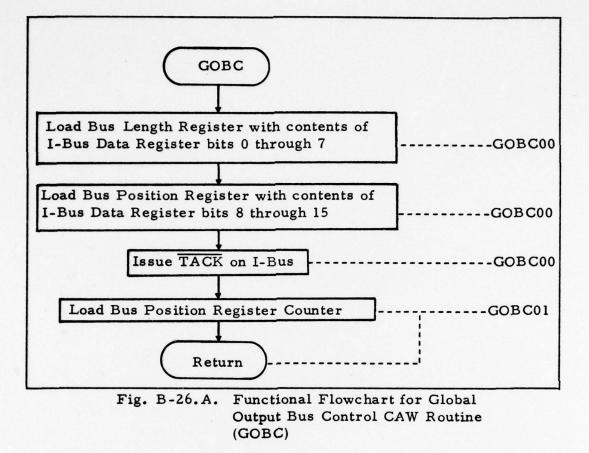

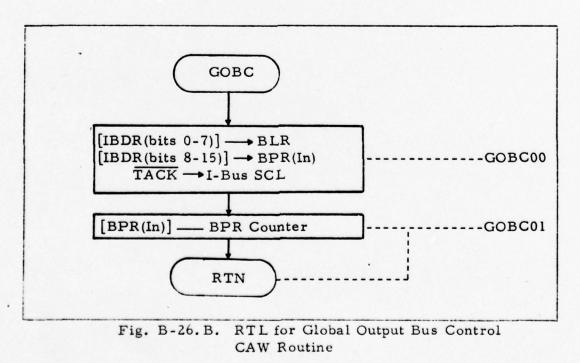

| B-26   | Global | Output Bus Control Routine        | <br>• | • |   |   |   |    |  | 189  |

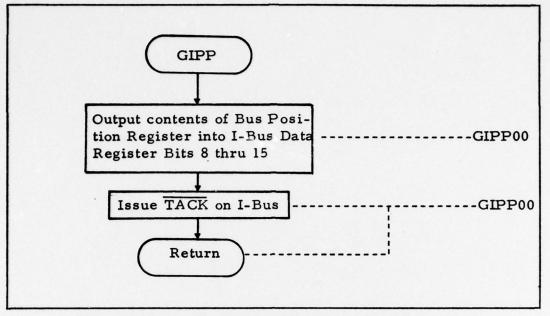

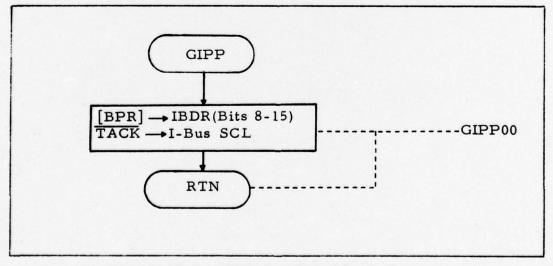

| B-27   | Global | Input Present Position Routine    |       |   |   | • | • | •. |  | 190  |

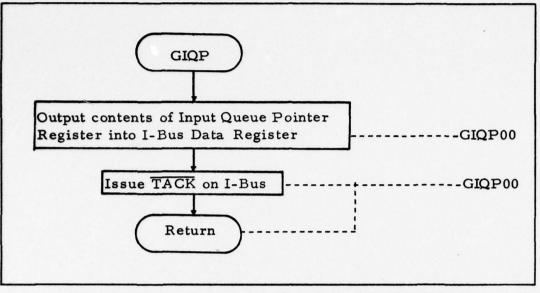

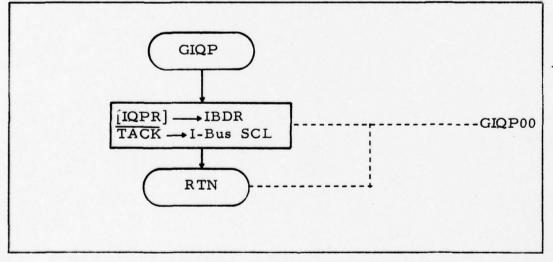

| B-28   | Global | Input Queue Pointer Routine       |       |   |   |   |   |    |  | 191  |

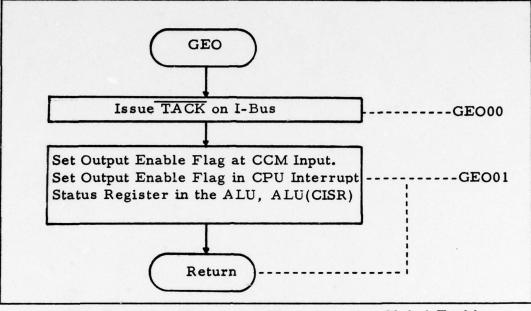

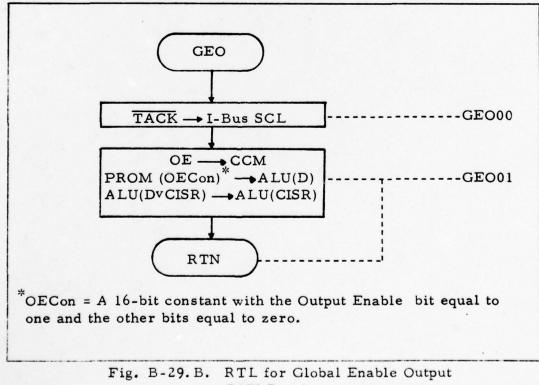

| B-29   | Global | Enable Output Routine             |       | • |   |   |   | •  |  | 192  |

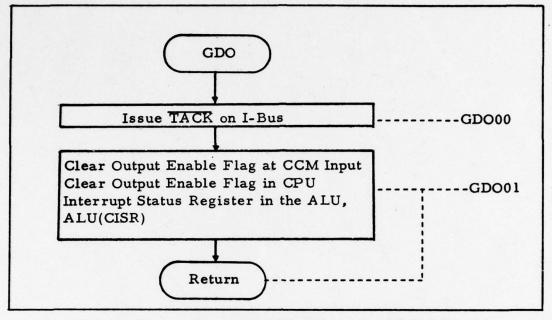

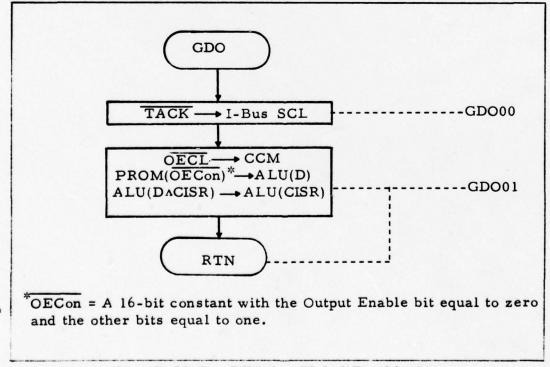

| B-30   | Global | Disable Output Routine            |       | • | • |   |   | •  |  | 193  |

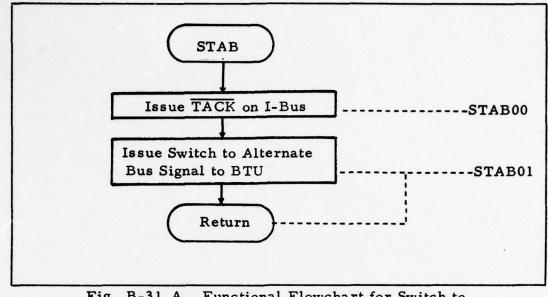

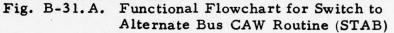

| B-31   | Switch | to Alternate Bus Routine          |       |   |   |   |   |    |  | 194  |

# vii

# List of Tables

0

0

| Table | Page                                                    |

|-------|---------------------------------------------------------|

| I     | BTU Interface Signals                                   |

| II    | BIU CAW Assignments                                     |

| III   | CPU Interrupts                                          |

| IV    | Registers in ALU RAM                                    |

| ۷     | Next Address Select Instruction Field                   |

| VI    | Condition Code Multiplexer Select Field                 |

| VII   | ALU Source Operand Field                                |

| VIII  | ALU Function Field                                      |

| IX    | ALU Arithmetic Mode Functions                           |

| x     | ALU Destination Control Field                           |

| XI    | PROM Address/Stack Instruction Field                    |

| XII   | Interrupt Control Unit Instruction Field                |

| XIII  | Set/Clear Field Signals                                 |

| XIV   | Control Field Signals                                   |

| xv    | BIU Microroutines to be eliminated                      |

| B-I   | Primary BIU Functions and Supporting Microroutines 121  |

| B-II  | BIU Microroutines                                       |

| C-1   | Microcodes for Service Routines                         |

| C-II  | Microcodes for External Interrupt Routines              |

| C-III | Microcodes for Program Generated Interrupt Routines 202 |

| C-IV  | Microcodes for CAW Routines                             |

| D-I   | Next Address Select Instruction Field                   |

| D-II  | Condition Code Multiplexer Select Field                 |

| D-III | ALU Source Operand Field                                |

| Tubic |

|-------|

|-------|

Non-second and the second second

0

0

0

| D-IV   | ALU Function Field                       |

|--------|------------------------------------------|

| D-V    | ALU Destination Control Field            |

| D-VI   | PROM Addr/Stack Instruction Field        |

| D-VII  | Interrupt Control Unit Instruction Field |

| D-VIII | Set/Clear Field Signals                  |

| D-IX   | Control Field Signals                    |

Page

## ix

#### ABSTRACT

This report describes the design of the Bus Interface Unit for the Distributed Processor/Memory (DP/M) System. The DP/M System, which is being developed by the Air Force Avionics Laboratory, is a concept to integrate avionics on board an aircraft by utilizing a number of programmable processor/memory elements (PE's) in a distributed (decentralized) network. All the PE's in the system are interconnected by a pair of redundant global buses and PE's in an affinity group are additionally interconnected by a local bus.

This effort involves the design of the Bus Interface Unit (BIU) of the PE. The BIU interfaces the parallel-data PE processor with the two redundant serial global buses and the serial local bus. The BIU has been designed as an interrupt driven microprogrammed processor. The design uses a bipolar bit-slice microprocessor, specifically the Am2900 Bipolar Microprocessor Family, for emulating the BIU functions.

This report starts with a brief description of the DP/M System, followed by a detailed description of the BIU functions. Then the hardware, the microword format, and the microroutines are described. A discussion on the design effort is presented at the end, and recommendations are made for system improvement.

X

#### BUS INTERFACE UNIT DESIGN

### FOR THE DISTRIBUTED PROCESSOR/MEMORY SYSTEM

#### I Introduction

#### Background

The complex avionic and control systems required for modern Air Force aircraft have required the development of new concepts for integrating these systems. Modern sophisticated aircraft require a large amount of in-flight data processing for effective mission performance. Previously, most avionic systems on an aircraft operated independently of each other and employed analog devices. As aircraft became more complex, the onboard systems became integrated, and these systems increased aircraft weight and required more space and electrical power. Better methods were needed to process and to provide the data required to achieve optimal aircraft and mission performance. This resulted in new concepts using digital processors for integrating these aircraft systems.

The development of Large Scale Integrated (LSI) circuitry and small digital processors has led to many new methods for integrating aircraft avionics. These new processors provide fast, accurate, reliable, and light weight systems which are ideal for avionics use. To meet the size, weight, and power requirements, many current avionic systems are highly centralized, relying on one central computer to process and distribute information to various actuators, sensors, and displays. This concept relies heavily on the central computer, and if it fails or the interface to it fails the aircraft mission performance may degrade drastically.

If the system could be decentralized by using a group of smaller processors (microprocessors), the resulting system would not be highly dependent on one specialized central computer. Each microprocessor or group of microprocessors would receive raw data from one aircraft sensor (e.g., airspeed, loran, radar, doppler), process it, format it, and make it available on a "global" bus to all the other microprocessors that need it. This system concept should be highly reliable, since the loss of one microprocessor would not result in total system failure. System performance would be degraded but still highly effective and the mission could continue.

()

To overcome the limitations of the centralized digital processor system and still meet the requirements for reduced size, weight, and power for airborne equipment, the Air Force Avionics Laboratory formalized the concept of the Distributed Processor/Memory (DP/M) System. This system uses a number of programmable processor/memory elements in a distributed (decentralized) system to integrate the avionics on board an aircraft. As part of the development program, the Air Force Avionics Laboratory awarded a contract to Texas Instruments (TI) Incorporated to determine whether this type of decentralization was functionally feasible. The TI program consisted primarily of four major objectives: (1) functional design of the DP/M hardware and high level simulation analysis, (2) functional design of the DP/M executive software, (3) study of the possible construction methods for the system hardware and software, and (4) fault tolerance analysis. The DP/M System concept as conceived by the TI program is presented in the next section (Ref 1).

#### DP/M System Concept

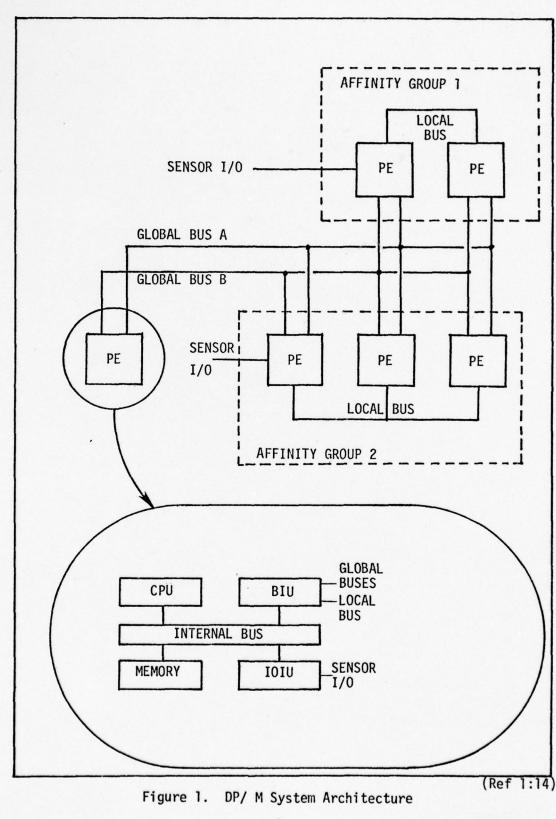

The DP/M System concept utilizes a varying number of simple processor/memory elements (PE) for a wide range of avionic system processing applications. These PE's can be used as stand alone uniprocessors, or they can be configured in a distributed network as shown in Figure 1. The network consists of two levels of busing between PE's. A dualredundant global bus is used to interconnect each PE in a system communication network. A local bus is used to interconnect multiple PE's clustered together to perform a given function. A cluster of PE's, called an Affinity Group, would be required when a single PE could not process all the data available from one aircraft sensor or actuator (e.g., hydraulic system, control surface). Both the global and local buses use a serial time-division-multiplex (TDM) communication system with a distributed round-robin bus protocol scheme where each PE has a predefined bus allocation. This allocation mechanism is programmable, which allows super-commutation (multiple bus access time slots within one round-robin cycle) of bus transmissions. Each transmitted message begins with a message identification header, which allows all recipient PE's to determine whether the message is for them.

Since the global busing facility is the only "central" resource of the DP/M system, dual-redundant TDM communication lines interconnect each of the PE's. Every PE on the global bus can participate in primary bus transfers and simultaneously listen on the secondary bus for a "switch to back-up bus" command when a fault or error is detected on the primary bus.

As shown in Figure 1, each PE is made up of four functional modules: the Bus Interface Unit (BIU), the Central Processor Unit (PE CPU), the

PE memory, and the Input/Output Interface Unit (IOIU). The BIU is the basic TDM data transfer interface to the PE CPU and PE memory. It translates bit serial data into parallel data words, and transfers data and status information to the PE CPU and PE memory. The PE CPU is the instruction-sequencing and data processing portion of the PE. Its computational capabilities are equivalent to present minicomputers. The PE memory provides the necessary program instruction and data storage. Memory access is local to a PE; it can be accessed by the other modules of the PE but not by another PE. Shared memory is not part of the DP/M concept. The IOIU is the interface between the PE and external devices in the avionic system. It permits digital data, command, and status information transfers between the PE and the external devices.

The four PE modules are interconnected with an Internal Bus (I-BUS). It provides intra-PE communication for data, address, and various control, status, and clock signals.

#### **BIU Functional Description**

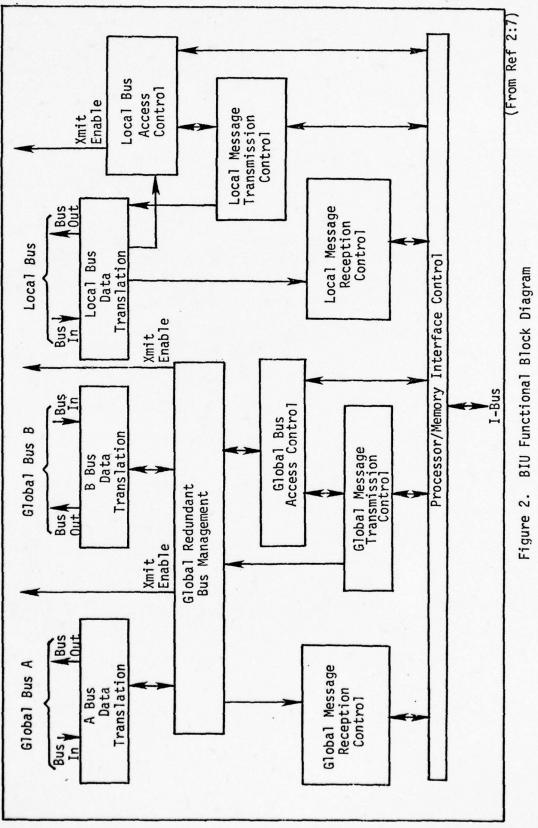

The BIU design is based on functional modularity to provide the two levels of interfacing required (global and local). The unit is divided into six functional modules for global bus management, five of which are duplicated for local bus management. As shown in Figure 2, these functional modules are the Bus Data Translation (two required in the global area), Message Reception Control, Message Transmission Control, Redundant Bus Management (global only), Bus Access Control, and the Processor/ Memory Interface Control (Ref 2).

The BIU contains the necessary functions to support a distributed round-robin bus scheme with message broadcast capability to other PE's.

It contains the necessary hardware to match associatively logical input message identification headers and to vector automatically these messages into software-selectable PE memory locations. This data vectoring feature (Direct Memory Access) relieves the CPU from continually setting up and servicing the BIU hardware. This significantly speeds up the response time which is important when both the global and local buses are processing messages.

In addition to providing an interface with the global and local buses, the BIU is instrumental in aiding fault recovery in the DP/M System. Since the integrity of various system processing functions is dependent upon the correct transmittal of data between PE's, the BIU contains certain fault-detection mechanisms to monitor all communications between PE's and to alert the system upon the detection of data errors or faults.

#### The Problem and Approach

The TI study on the DP/M concept was completed in February 1975. The Air Force Avionics Laboratory then modified the TI functional design and issued a preliminary design specification (Ref 3). In 1976, a preliminary design of the BIU was made in a Master's thesis (Ref 2). In the TI study, the BIU was to be realized with random logic hardware. However, the feasibility of using bipolar bit-slice microprocessors for emulating the hardware functions of the BIU was demonstrated in Reference 2.

The work done in Reference 2 is primarily a feasibility study, and as such the design presented does not provide the detail required to go directly into system implementation. Devices from the Am2900 Bipolar

Microprocessor Family were used in the design, and there were several areas in the application of the chip set that could not be covered thoroughly because of lack of detailed specifications and functional descriptions on these new devices. Functional flowcharts for the BIU were developed, and the design provides a basic configuration on which a final design of the BIU can be based.

The objective of this thesis is to perform a complete design of the BIU using the Am2900 Bipolar Microprocessor Family. In addition to the hardware design, the thesis includes the functional flowcharts for all the BIU microroutines, the register transfer language (RTL) description for each of the microroutines, and the microcodes (in Mnemonic form) for these microroutines.

The development of the thesis involved seven major tasks. The first task was to study the functions of the BIU and to define the detailed BIU requirements. The second task was to evaluate and to modify or add to the functional BIU microroutine flowcharts that are presented in Reference 2. The third task was to develop a register layout for the BIU. The fourth task was to research the Am2900 Bipolar Microprocessor Family. The fifth task was to design the BIU hardware. As part of this task, the microword was developed and a decision was made to divide the global and local functions into separate units. The sixth task was to develop the RTL description for the BIU microroutines, and the seventh task was to develop the microcodes for the microroutines.

#### Thesis Outline

The body of this report represents a sequential description of the tasks performed in designing the BIU. Chapter II and Appendices A and B

provide a detailed description of the BIU functions. Chapter III details the hardware design. Chapter IV describes the microword and discusses the microroutines and microcodes presented in Appendices B and C. Chapter V summarizes the work done, identifies additional work that needs to be accomplished, identifies departures from the BIU specification, and discusses recommendations for system improvement.

#### II BIU System Description

#### Introduction

This chapter provides a general description of the BIU functions as specified in Appendix C, Bus Interface Unit Specification, of Reference 3. Departures from the specification, which were required during the design, are identified in the discussion.

The BIU provides the interface between a PE and any of three data buses--a redundant pair of global buses and a local bus. As stated in Chapter I, the BIU performs the following primary functions:

- a. Bus data translation

- Message reception control

- c. Message transmission control

- d. Bus access control

- e. Redundant bus management (global only)

- f. Processor/memory interface

With the exception of the redundant bus management function, the above functions are identical for the global and local bus interfaces. Therefore, the descriptions that follow apply to both global and local bus interfaces. Prior to the functional description, the global/local message structure will be discussed.

#### Global/Local Message Structure

The message routing procedure of the DP/M System requires that each transmitted message be recognized by all PE's on the bus. To accomplish this, each message transmitted on the bus is preceded with a message header which identifies the message. Each potential receiver on the bus actively checks the message header to determine if the message is one which is to be received. A Message Identity Associative Address technique is used to decode the message header and identify the messages to be received.

Due to considerations of physical distribution of bus wiring, distance variations between PE's (bus lengths up to 300 feet), and to conform to the data code specified in Military Standard 1553, Manchester II binary data encoding is used for global/local communications. The message synchronization signals and data format are shown in Figure 3. Unique invalid Manchester waveforms are used for synchronization signals so that synchronization information can be discriminated from data patterns (Ref 1:40).

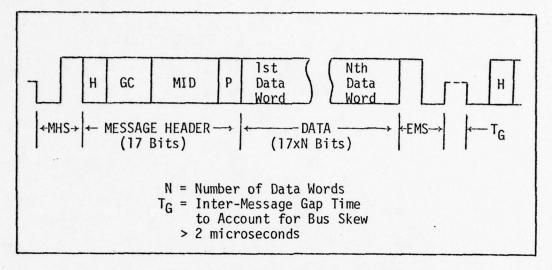

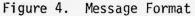

The message format of the DP/M System is shown in Figure 4. The Message Header Synchronization (MHS) denotes the start of a message (required for Manchester II decoding). The message header (MH), which has the same length as the basic data word (17 bits), contains all the message routing and control information. It is divided into four fields. The 1-bit High Priority Message field (H-field) alerts the message recipient(s) that the message requires immediate attention. The 5-bit General Control field (GC-field) allows specification of special control/ status information which further defines or alters the interpretation of the message. The 10-bit Message Identify field (MID-field) specifies the identify of the associated message data. This field specifies the transmitter/receiver link during message data transmission. The Parity field (P-field) determines odd-parity for the MH. The MH fields are shown in Figure 5.

---- Logic High - Logic Low ---- Logic High ---- Logic High - Logic Low ---- Logic Low | + 1.5 Bit Times + | +1.5 Bit Times + 0 0 Bit Time Message Header Synchronization (MHS) End Message Synchronization (EMS) Data -

Figure 3. Manchester II Data/Synchronization Signal Waveforms (From Ref 1:41)

Figure 5. Message Header Fields

The actual data of the message immediately follows the MH. Message transfers are block oriented; accordingly, the message data content is organized into fixed-length, 16-bit data words. A parity bit is added to each data word, resulting in an overall 17-bit message data word length. Each message may contain a variable number of data words. Global bus messages, however, can be optionally limited to a maximum length of eight data words to guarantee global communication responsiveness. The unique length of each message is placed in main memory during system implementation (Ref 1:51).

Message transmission termination is denoted by the End Message Synchronization (EMS). This signal is used as the dynamic cueing mechanism which activates and controls sequencing of the distributed bus control logic throughout the DP/M System. If a PE has no data to transmit when given bus control, it "passes on" the bus control by emitting a "zero-length" message represented by an isolated EMS signal (Ref 1:51).

#### Bus Data Translation Function

The portion of the BIU which performs the bus data translation function was named the Bus Translation Unit (BTU) in Reference 2. The Air Force Avionics Laboratory is working on its design; accordingly, the BTU design was not included in this design effort.

The BTU is responsible for providing the interface between the global/local serial data buses and the parallel-data oriented BIU. During message reception, the BTU detects the synchronization signals MHS and EMS and notifies the BIU of an incoming message or of message termination. It converts the bi-phase encoded serial data into parallel binary

data which is placed in the Input Data Register. It notifies the other parts of the BIU that a word has been received (WR signal) when its Input Data Bit Counter counts the last data word bit, bit 17. During this time, the BTU also performs error detection functions. It notifies the BIU of Manchester II encoding errors, parity errors, and word length errors.

During message transmission, the BTU converts the parallel binary data in the Output Data Buffer (Output Data Register in the BIU Specification) to bi-phase encoded serial data and appends MHS, parity bits, and EMS to the outgoing message. The BTU transmits the outgoing message when the PE's allocated time slot arrives on the bus. If the BTU is not ready to transmit or does not have anything to transmit, it passes control of the bus by immediately issuing an EMS.

Also included in this funcitonal area are two "watchdog timer" mechanisms. The Bus Quiescence Watchdog Timer (BQWT) monitors the presence of data transfer activity on the bus. If a "no-activity" time of 50 microseconds occurs, an interrupt stimulus is generated and bus access is disabled. The Bus Quiescence Watchdog Timer can be indirectly enabled or disabled by its associated interrupt mask, which is under PE CPU control.

The Bus Dominance Watchdog Timer (BDWT) monitors the length of each message on the bus. If a PE transmits a message of more than eight words, an interrupt stimulus is generated and bus access is disabled. Like the Bus Quiescence Watchdog Timer, the Bus Dominance Watchdog Timer can be enabled or disabled by its associated interrupt mask, which is under PE CPU control.

The signal transfers between the BTU and the other parts of the BIU are shown in Table I.

0

## TABLE I

## BUT Interface Signals

| Signals from BTU to BIU                   |

|-------------------------------------------|

| Message Header Synchronization            |

| Word Received                             |

| Parallel Data                             |

| Message Encoding Error Interrupt          |

| Message Parity Error Interrupt            |

| Message Word Length Error Interrupt       |

| End Message Synchronization (Received)    |

| End Message Synchronization (Transmitted) |

| Bus Quiescence Interrupt                  |

| Bus Dominance Interrupt                   |

|                                           |

| Signals from BIU to BTU                   |

| Parallel Data                             |

| Output Pending                            |

| Transmit Message Command                  |

| Switch to Alternate Bus Command           |

| Clear Message Encoding Error Interrupt    |

| Clear Message Parity Error Interrupt      |

| Clear Message Word Length Error Interrupt |

| Clear Bus Quiescence Interrupt            |

| Clear Bus Dominance Interrupt             |

| Disable Bus Quiescence Interrupt          |

| Disable Bus Dominance Interrupt           |

|                                           |

In the BIU Specification, the serial-to-parallel data conversion, parallel-to-serial data conversion, and the watchdog timer mechanisms are part of the message reception control function, message transmission control function, and bus access control function respectively. These tasks have been included in the BTU by the Air Force Avionics Laboratory.

#### Message Reception Control Function

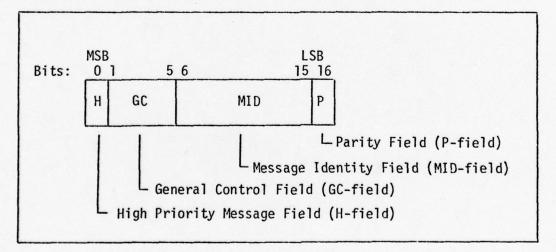

After the message header (first message word) has been assembled in parallel-data form, the message header is transferred from the BTU Input Data Register to the Input Data Register. If a message header error (word length, parity, or encoding error in the message header word) is detected during the assembly and transfer of the message header, a message header error interrupt stimulus is generated. The complete message is then ignored and further BIU message reception activity is deferred until the next message header is detected. If there are no message header errors, the BIU decodes the message header to determine if the message is for the PE. This is accomplished by extracting the six most significant bits of the Message Identity field, appending a leading 2-bit binary constant to generate a BIU PROM address which is placed into the PROM Address Register, PAR, (Figure 22). This address is used to access a word in a 64-word area defined as the Message Identify Associative Match MAP (MIAMM). Each MIAMM word consists of 16 bits and each bit is associated with a unique message header (64 words x 16 bits represent 1,024 unique messages). The appropriate response bit (RB) is determined by the binary value of the four least significant bits of the Message Identity field. The response bit of the MIAMM word

is tested and if "set," the message is received. If the response bit is "not set," the message is not relevent to the PE, and the remainder of the message is ignored and further BIU message reception activity is deferred until the next message header is detected (Ref 1:64). The message identity operation is illustrated in Figure 6.

The BIU Specification requires that the MIAMM be located in the PE memory. This design places the MIAMM in the BIU PROM to increase BIU speed and to reduce traffic on the I-bus. Further discussion of this change is presented in Chapter V.

Following message recognition, the BIU places the message header into a Message Header Input Queue, a first-in-first-out modulo-8 queue located in PE memory. This action provides automatic hardware queue posting of input message identities, which are subsequently scanned and processed by the PE CPU local executive software at its convenience and throughput capability. This operation eliminates interrupt response execution time overhead which would otherwise be incurred after each individual message reception (Ref 1:64).

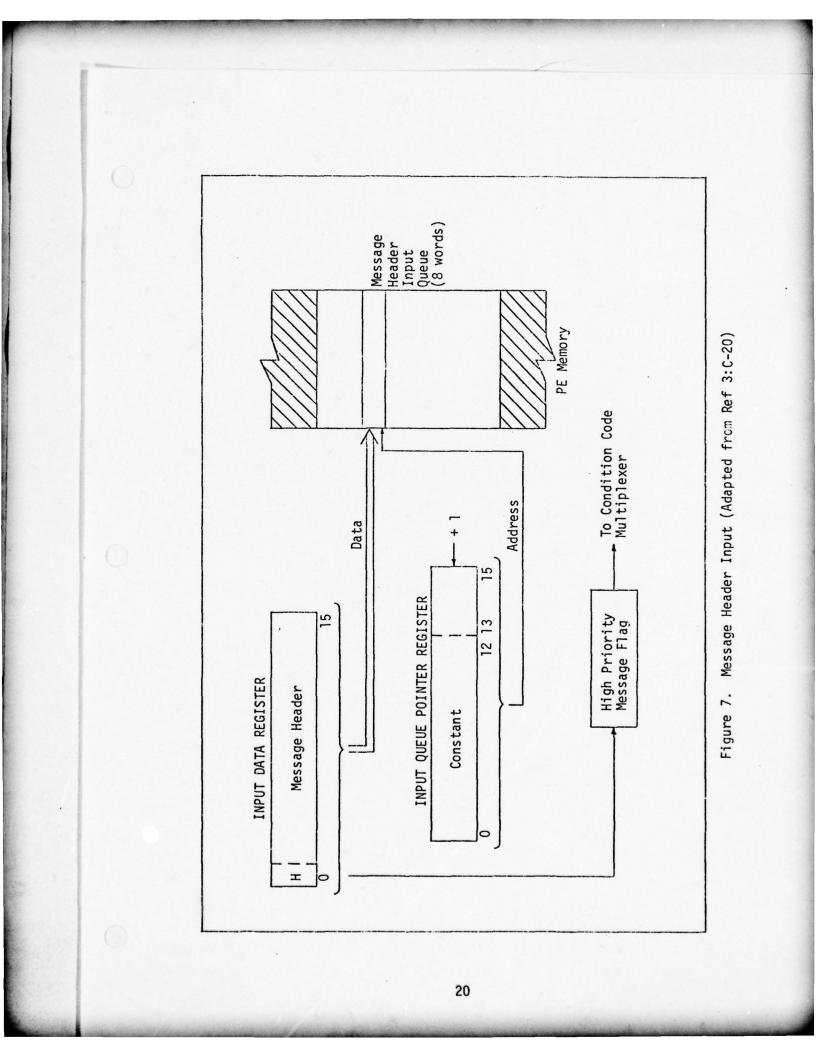

The address of the Message Header Input Queue is obtained from an Input Queue Pointer which is a 3-bit modulo-8 counter appended with a leading 13-bit constant. The Input Queue Pointer is incremented after each message input. The message header input operation is illustrated in Figure 7.

The data words of the incoming message are transferred to the PE memory using a procedure called "message vectoring" (Ref 1:52). Basically, each identified message is passed or "vectored" to an area in PE memory (data buffer) where it is stored for later use by an applications

Figure 6. Message Identity Associative Addressing (Adapted from Ref 3:C-19)

software process. Data buffering is reuqired since the DP/M System operates in a loosely-coupled, asynchronous mode with respect to interprocess communication.

Message vectoring is accomplished using a hardware message vectoring technique similar to a conventional direct memory access (DMA). Conventional DMA data channels require processor (program) initialization, or "set-up" of the channel before beginning data transfers to memory. In the hardware message vectoring technique, the BIU derives a buffer storage area in PE memory from information in the message being received and then autonomously transfers the message data content to this area. No program intervention is required in setting up the input channel before each transfer (Ref 1:53).

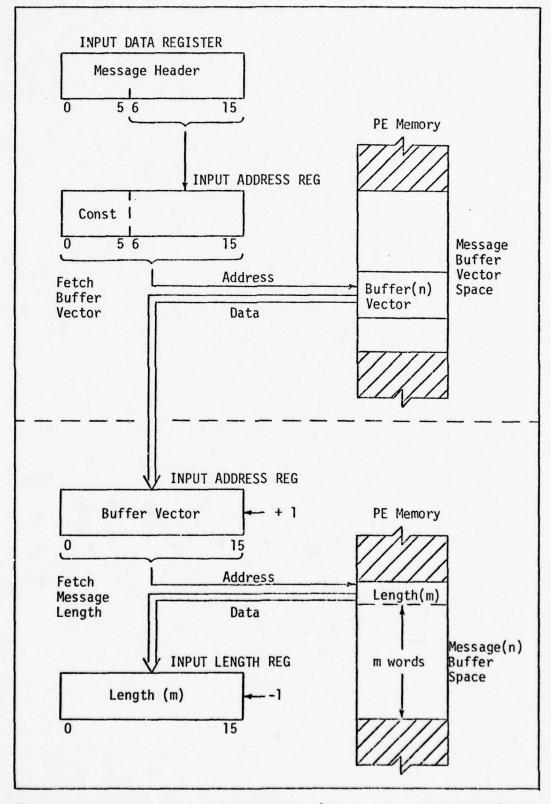

The BIU derives the indirect address of the message buffer space by appending a leading 6-bit constant to the 10 bits of the MID-field of the message header. The derived address is placed in the Input Address Register (IAR) and a message Buffer Vector word is accessed from the PE memory. The Message Buffer Vector word is placed in the Input Address Register and is used as the PE memory address which corresponds to the first location in the message buffer space. The first word in the buffer is then accessed. This word contains the expected length of the incoming message and is placed in the Input Length Register, (ILR) (Figure 8). The Input Address Register is then incremented, preparing the BIU for the first message data word input. The BIU transfers the incoming message data words contiguously into PE memory, incrementing the Input Address Register and decrementing the Input Length Register as each word is stored. The message data input operation terminates when the Input Length Register decrements to zero.

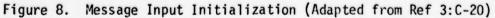

#### Message Transmission Control Function

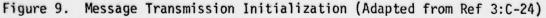

The message transmission control function retrieves output message data from PE memory and transfers them to the Output Data Buffer. This function effectively operates as a conventional direct memory access output channel. The operation is set up and initiated under program control by means of a Command Address Word (CAW) sent from the PE CPU which loads the Output Address Register with the beginning address of the block of data to be sent on the global/local bus. The first word accessed contains the message length which is placed into the Output Length Register. The actual output message follows, with the initial word in the message being the message header. This operation is illustrated in Figure 9. After each word is transferred from PE memory, the Output Address Register is incremented and the Output Length Register is decremented. The message transmission operation terminates when the Output Length Register decrements to zero (Ref 1:69).

The message transmission operation is under program control. Transmission is allowed when the PE CPU sets an Output Enable flag in the BIU (Ref 3:C-28).

#### Bus Access Control Function

The bus access control function controls PE access to the global/ local bus for data transmission. Bus access control is based on a hardware implemented round-robin circular priority sequence which allows the PE to control the bus when its appropriate allocation slot is detected. Bus access control is program initialized by a Command Address Word from the PE CPU. A Command Address Word tells the BIU to load two BIU 8-bit

registers, the Bus Length Register and the Bus Position Register, with the values it is sending on the I-Bus. The Bus Length Register contains the "length" in units of allocation time-slots between the PE's allocated time slot. The Bus Position Register contains the current position of the PE's allocated time slot in the bus control chain. The Bus Position Register is decremented after each EMS and when decremented to zero, it generates a Transmit Message Command signal to the BTU. The Bus Position Register is then reinitialized with the value in the Bus Length Register and the cycle is repeated.

With 8 bits, up to 256 bus allocation time slots can be defined. Since most envisioned systems will contain fewer than 32 PE's, a satisfactory degree of supercommutation (multiple allocated time slots within one round-robin cycle) is provided. This characteristic is important in reducing bus access latency time for "high-priority" bus users (Ref 1:69).

# Redundant Bus Management Function

The redundant bus management function provides the necessary control elements required to interface a single BIU to dual-redundant Global buses. The redundant bus management logic continuously monitors the currently designated "alternate" bus (i.e., the bus not currently in use) for a valid switchover command issued by the Global Executive. (The Global Executive, which resides in a monitor PE, is the system monitor and scheduler.) The command is a fixed-value message, one data word in length. When the switchover command is detected, the BIU immediately terminates any message reception activity in progress by internally generating an EMS signal and a Message Encoding Error signal to the

message reception function. The BTU input is transferred to the alternate bus and all future message receptions are received on this bus which now becomes the primary bus. The BIU output is under PE CPU control and is switched when the appropriate Command Address Word is issued. The switching activity can be performed as many times as directed by the Global Executive. Thus "primary" and "alternate" Global bus identities can be established dynamically and interchanged as many times as required during system operation. This switching activity is used to remove a malfunctioning PE from the primary bus (Ref 1:72; 2:29).

As stated previously, this function has been incorporated by AFAL into the BTU. Therefore, except for the function of decoding the Command Address Word for switching the output to the alternate bus, this function was not included in this design.

# Processor/Memory Interface Function

The processor/memory interface performs the necessary control operations associated with providing interface protocol compatibility between the BIU and the I-Bus, which interconnects each functional unit of the PE. This function performs DMA operations and recognizes, decodes and executes Command Address Words from the PE CPU. A list of the Command Address Words is shown in Table II, page 34. This function also contains the logic required to retain and present the various BIU interrupt stimuli to the PE CPU via the I-Bus. Table III, page 35, lists the global/local interrupts generated by the BIU and sent to the PE CPU (CPU interrupts). Subfunctional responsibilities of this function are discussed in the following paragraphs. Before their discussion, a brief description of the I-Bus is given.

<u>I-Bus Description</u>. The I-Bus serves to transfer data between all modules of the PE (BIU, PE CPU, PE memory, and IOIU). Data transfers are handled as demand/response sequences. As such, all signals are transmitted and received between an I-Bus master device, which controls data transfer, and an I-Bus slave device, which generates or accepts data in response to the master device.

The modules of the PE compete for I-Bus access on a priority basis. the BIU is assigned the highest priority and the CPU the lowest priority.

The I-Bus consists of control lines, information lines, and general facilities lines. There are seven lines for bus control activities, three control lines and a set of four identification lines. The three bus control signals are Bus Request (BRQ), Bus Release (BREL), and Bus Grant (BGR). The Bus Request signal is used to initiate a bus master assignment, while the Bus Release signal is used to terminate the assignment. The Bus Grant line is threaded through each module (daisy chain) and is used to resolve conflicts when two or more masters request the bus simultaneously. The four identification lines, Bus Master Identification (BMID), are associated with the maintenance function, and are used to identify the module in control of the bus.

Thirty-seven lines are utilized for data transfer operations on the bus. Sixteen lines are used for address (ADDR), 16 lines for data (DATA), and the remaining lines for data transfer control. These control lines are I/O Select (IOSL), Data Receive (DRCV), Transfer Request (TRQ), Transfer Acknowledge (TACK), and Transfer Time Out (TTO).

There are three I-Bus control lines associated with CPU interrupt activities. They are Interrupt Request (IRQ), Interrupt Inhibit (INHB),

and Interrupt Acknowledge (IAK). The Interrupt Acknowledge line, like the Bus Gran line, is threaded through each module in a daisy chain fashion and is used to resolve conflicts when two or more modules attempt to interrupt the CPU simultaneously.

The general facilities lines are composed of a free running clock (FCLK), a master clock (MCLK), a Master Stop (MSTP), a Clear/Reset (MRESET), power, and ground.

With the exception of the BMID, IOSL, and DRCV, all signals on the I-Bus are transmitted as complements. Positive logic is employed, i.e., a high voltage is a logic "1" (True) and a low voltage (ground) is a logic "0" (False).

The I-Bus is asynchronous. The speed of data transfers over the bus is determined by the speed of the modules interfaced to it.

Direct Memory Access Function. The BIU requests PE memory access on a cycle-stealing-by-priority basis in response to the memory requests of the message reception control and message transmission control activities. As stated previously, the BIU possess the highest memory access priority (I-Bus access) among all the modules of the PE. Within the BIU, the BIU specification establishes the following priority in decending order:

- 1. Global Bus input activity

- 2. Global Bus output activity

- 3. Local Bus input activity

- 4. Local Bus output activity

In this design, the global and local functions have been separated into separate modules. The Global BIU has the highest priority and the Local BIU has the next highest priority.

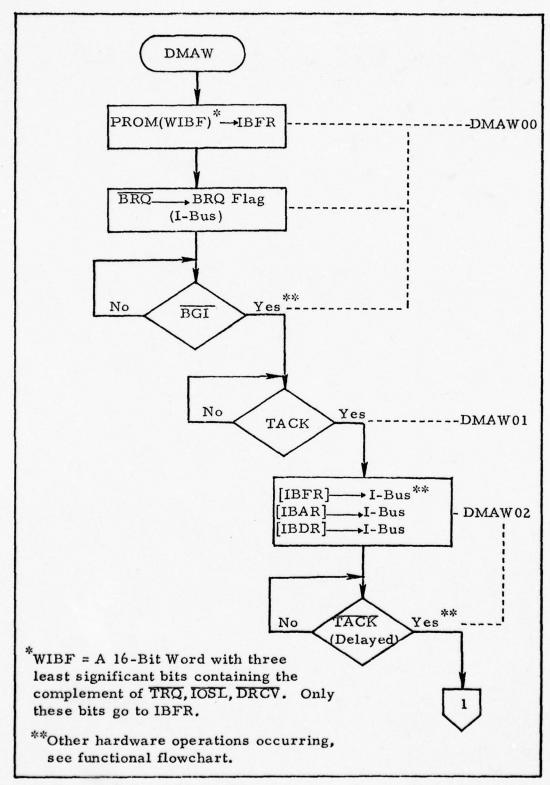

In performing direct memory access (DMA), the BIU acts as a master device on the I-Bus. It initiates bus control by issuing  $\overline{BRQ}$  (BRQ low designates bus request). When it receives  $\overline{BGRI}$  (Bus Grant signal into the BIU), it becomes bus master, and it blocks the Bus Grant signal from propagating to any lower priority module which may also be requesting the bus. This is done by making the Bus Grant line high beyond the BIU (Bus Grant signal out of the BIU is redesignated BGRO). After obtaining control of the bus, the BIU issues BMID and waits until the previous data transfer is completed (TRQ and TACK lines high) before it starts its data transfer operation.

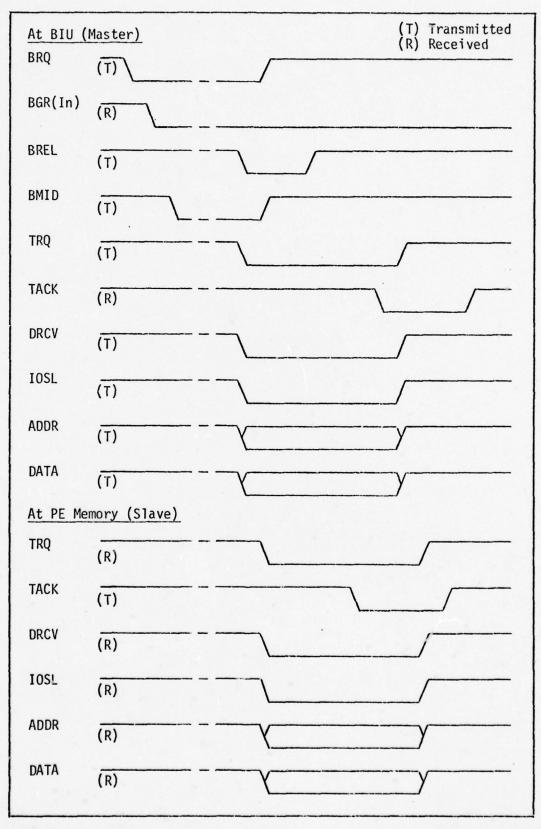

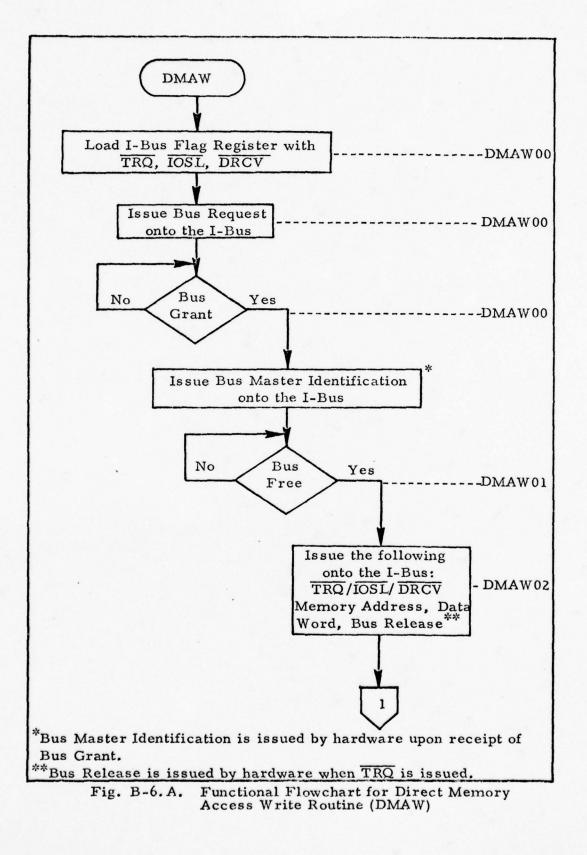

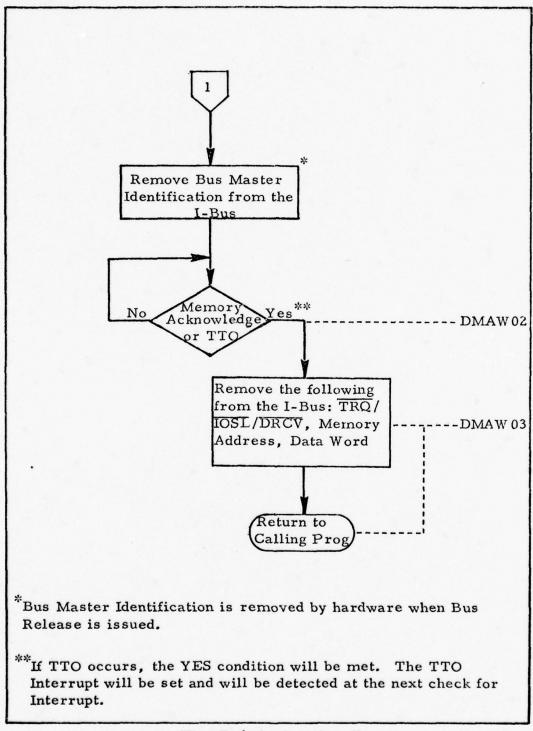

For a write-into-memory operation, the BIU initiates the data transfer operation by issuing BMID,  $\overline{TRQ}$  (TRQ low designates transfer request to the slave, which is memory),  $\overline{IOSL}$  (IOSL low designates memory),  $\overline{DRCV}$  (DRCV low designates master to write, send operation), ADDR, DATA, and  $\overline{BREL}$  (BREL low designates bus release). When  $\overline{BREL}$  is issued, all bus masters, including the BIU, remove their bus requests. With the BIU's bus request removed, BGRO goes low (Bus Grant signal now available to all masters), and  $\overline{BREL}$  is then released, allowing all masters including the BIU, to request the bus. This sequence of releasing the bus at the start of an I-Bus data transfer operation allows bus mastership resolution to be overlapped with I-Bus data transfers. The BIU performs block transfers by immediate rerequest of the bus. When a lower priority module is performing a block transfer, the BIU can always pre-empt between transfers by requesting the bus when BREL goes high.

When the BIU issues  $\overline{TRQ}$ ,  $\overline{TOSL}$ ,  $\overline{DRCV}$ , ADDR, and DATA, the PE memory receives  $\overline{TRQ}$  and decodes IOSL and ADDR to determine if it is being addressed. The PE memory internally delays the  $\overline{TRQ}$  signal to allow for valid address data reception and worst case address decode time. The internally delayed  $\overline{TRQ}$  signal and a valid address code is then used to generate a memory start signal. When the memory write cycle is complete the PE memory issues  $\overline{TACK}$  (TACK low designates transfer acknowledge). The BIU receives the asserted transfer acknowledge and it removes  $\overline{TRQ}$ ,  $\overline{TOSL}$ ,  $\overline{DRCV}$ , ADDR, and DATA. When the PE memory detects the removal of  $\overline{TRQ}$ , it removes  $\overline{TACK}$ , at which time the I-Bus is relinquished to the next I-Bus master. The DMA write operation is illustrated in Figure 10.

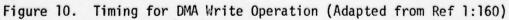

For a read-from-memory operation, the BIU, after obtaining bus access and after previous I-Bus operations are complete, issues  $\overline{TRQ}$ ,  $\overline{IOSL}$ , DRCV (DRCV high designates master to receive, read operation), ADDR, and  $\overline{BREL}$ . The PE memory, after it determines that it is to be read, starts a read cycle. When the data (DATA) is valid, the PE memory issues  $\overline{TACK}$ . The BIU receives the asserted transfer acknowledge and after a delay to assure receipt of valid data, latches DATA and removes  $\overline{TRQ}$ ,  $\overline{IOSL}$ , DRCV, and ADDR. When the PE memory detects the removal of  $\overline{TRQ}$ , it removes  $\overline{TACK}$  and DATA, at which time the I-Bus is relinquished to the next I-Bus master. The DMA read operation is illustrated in Figure 11.

In addition to the normal transfer request/acknowledge sequence, there is one way in which the DMA operation can be terminated abnormally. A Transfer Time Out (TTO) is generated by a watchdog timer on the memory controller when the BIU (or any master) attempts to address a

nonexistent memory location (or slave). When the time out occurs, the BIU uses the time out signal in the same manner as a transfer acknowledge signal, except it sets the Transfer Time Out interrupt and proceeds (Ref 3:C-34, B-3 to B-6). The Transfer Time out Interrupt has been added in this design and is discussed further in Chapter V.

<u>Program-Command Response Function</u>. This function deals with processing program commands which the PE CPU issues in the form of Command Address Words (CAW), Table II. In performing this function, the BIU acts as a slave device on the I-Bus.

In a write-into-BIU command, the BIU receives  $\overline{TRQ}$  (TRQ low designates transfer request to the slave), IOSL (IOSL high designates input/output device),  $\overline{DRCV}$ , (DRCV low designates master to write), ADDR (contains the CAW), and DATA. The BIU decodes these signals and if it is determined that the CAW is for the BIU, the content of the I-Bus Data Register is clocked into the BIU and Transfer Acknowledge (TACK) is issued. When the PE CPU removes  $\overline{TRQ}$ , the BIU removes  $\overline{TACK}$ .

In a read-from-BIU command, the procedure is similar to the above except that DRCV (DRCV high designates master to read) is received instead of  $\overline{DRCV}$ . If it is determined that the CAW is for the BIU, the requested information is clocked onto the I-Bus and  $\overline{TACK}$  is issued. When the PE CPU removes  $\overline{TRQ}$ , the BIU removes  $\overline{TACK}$ .

<u>Interrupt Interface/Control Function</u>. This function deals with CPU interrupts, interrupts generated within the BIU which are passed to the PE CPU (See Table III). This function performs program-controlled masking of each of the interrupts for the PE CPU and provides protocol compliance with the CPU interrupt-related operations.

TABLE II

0

BIU CAW Assignments

| CAM<br>L/LOCAL<br>MRITE/READ<br>decimal) FUNCTION<br>MRITE/READ<br>(DRCV/DRCV)   02 DRCV Output* G/L Interface Status   02 DRCV Input G/L Interface Status   03 DRCV Input G/L Bus Control   04 DRCV Output* G/L Queue Pointer   05 DRCV Input G/L Queue Pointer   06 DRCV Input G/L Queue Pointer   08 DRCV Input G/L Queue Pointer   08 DRCV Enable G/L Output   07 DRCV Bisable G/L Output   08 DRCV Disable G/L Output   07 DRCV Switch to Alternate Bus   07 DRCV Switch to Alternate Bus   08 DRCV Switch to PE CPU reading | DN ACTION                                  | face Status [IBDR] → ALU(CISR) | ce Status [ALU(CISR)] → IBDR | t 1 → ALU(CISR/OAF bit)<br>[IBDR] → OAR | itrol [IBDR/bits 0-7] + BLR<br>[IBDR/bits 8-15] + BPR | Position [BPR] + IBDR/bits 8-15 | ointer [IQPR] → IBDR | 1 + ALU(CISR/OEF bit) | : 0 → ALU(CISR/OEF bit) | e Bus | refer to<br>ito BIU.<br>and Read<br>eading     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------|------------------------------|-----------------------------------------|-------------------------------------------------------|---------------------------------|----------------------|-----------------------|-------------------------|-------|------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I TE/READ<br>RCV/DRCV)                     |                                |                              |                                         |                                                       |                                 |                      |                       |                         |       | *Output<br>PE CPU<br>Simila<br>refer<br>from B |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CAW<br>GLOBAL/LOCAL WR<br>(Hexadecimal) (D | 02                             | 02                           | 04                                      | 90                                                    | 90                              | 08                   | OA                    | 00                      | •     |                                                |

| TABL | E | II | I |

|------|---|----|---|

|      |   |    | _ |

CPU Interrupts

| CLASS          | INTERRUPTS IN DESCENDING PRIORITY            |

|----------------|----------------------------------------------|

| Arm/Disarm     | Global High-Priority Message Received (GHMR) |

| Enable/Disable | Global Bus Quiescent (GBQ)                   |

| Enable/Disable | Global Bus Dominance (GBD)                   |

| Arm/Disarm     | Global Message Length Violation (GMLV)       |

| Arm/Disarm     | Global Message Header Error (GMHE)           |

| Arm/Disarm     | Global Message Word Count Error (GMWCE)      |

| Arm/Disarm     | Global Message Word Length Error (GMWLE)     |

| Arm/Disarm     | Global Message Parity Error (GMPE)           |

| Arm/Disarm     | Global Message Encoding Error (GMEE)         |

| Arm/Disarm     | Global Transfer Time OUt (GTTO)              |

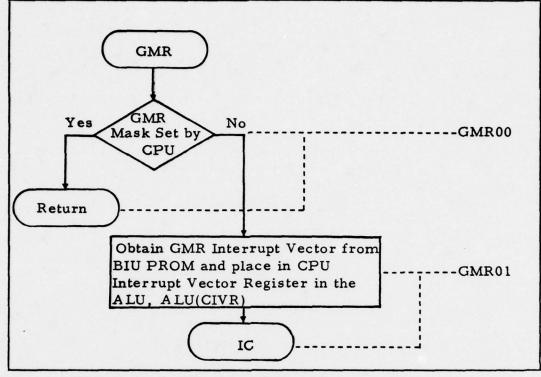

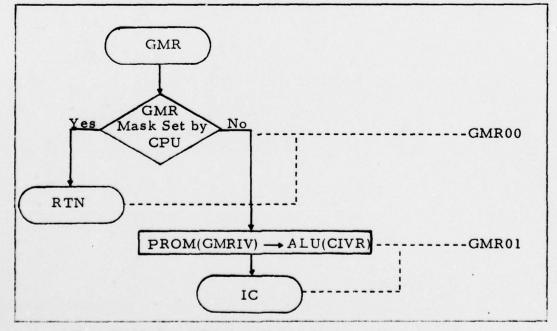

| Enable/Disable | Global Message Received (GMR)                |

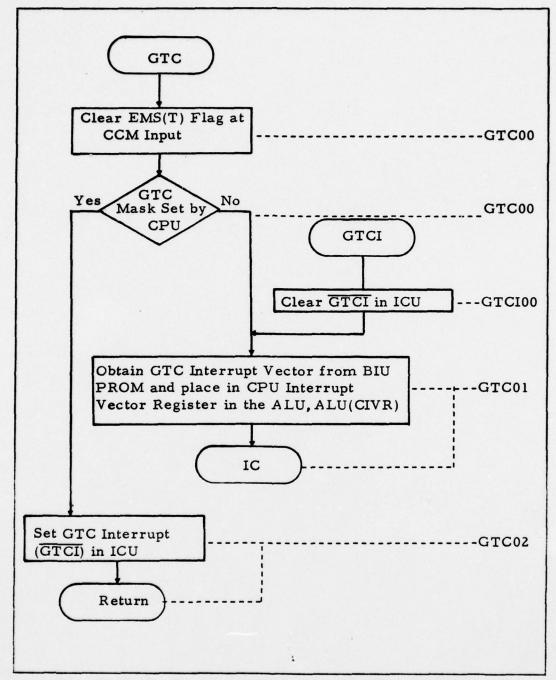

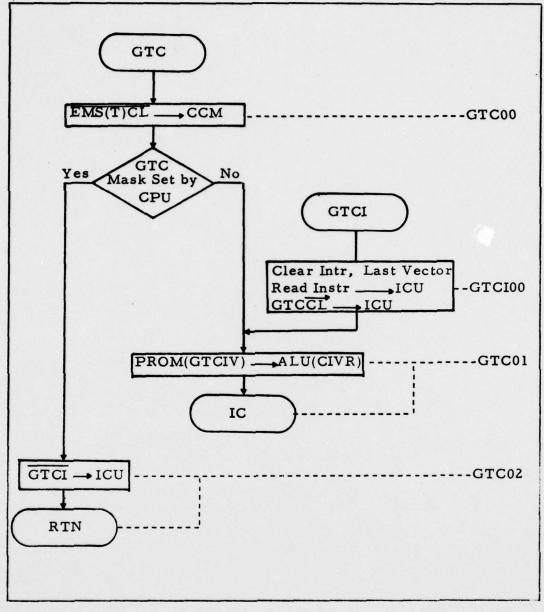

| Arm/Disarm     | Global Transmission Completed (GTC)          |

| Arm/Disarm     | Local High-Priority Message Received (LHMR)  |

| Enable/Disable | Local Bus Quiescent (LBQ)                    |

| Enable/Disable | Local Bus Dominance (LBD)                    |

| Arm/Disarm     | Local Message Length Violation (LMLV)        |

| Arm/Disarm     | Local Message Header Error (LMHE)            |

| Arm/Disarm     | Local Message Word Count Error (LMWCE)       |

| Arm/Disarm     | Local Message Word Length Error (LMWLE)      |

| Arm/Disarm     | Local Message Parity Error (LMPE)            |

| Arm/Disarm     | Local Message Encoding Error (LMEE)          |

| Arm/Disarm     | Local Transfer Time Out (LTTO)               |

| Enable/Disable | Local Message Received (LMR)                 |

| Arm/Disarm     | Local Transmission Completed (LTC)           |

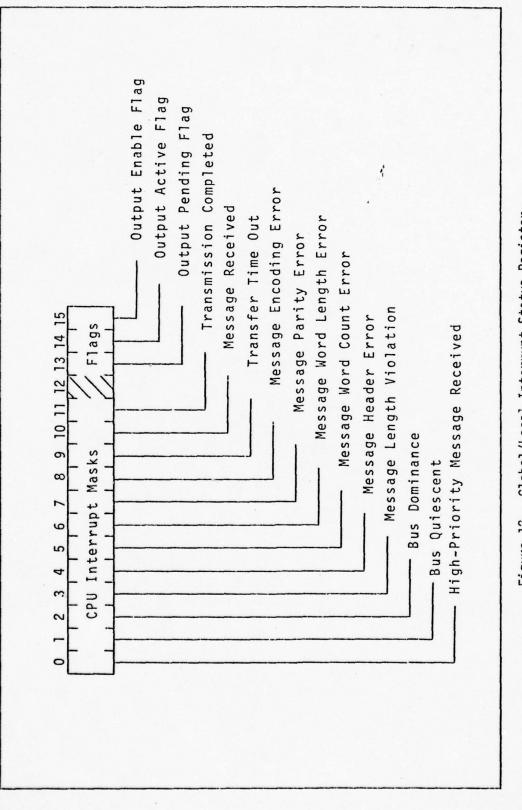

In the present DP/M scheme, the BIU does not simultaneously relay all pending CPU interrupts to the PE CPU. As shown in Table III, the interrupts are prioritized. They are serially relayed to the PE CPU with the highest priority interrupt being relayed first. Before relaying an interrupt, the BIU must first determine if the PE CPU is presently accepting the specific interrupt. This is done by checking an interrupt mask which the PE CPU sets under program control. The PE CPU places the mask in the Interrupt Status Register, ISR (Figure 12). In addition to the interrupt mask, the BIU Specification requires three other bits of information in the register: an Output Pending Flag and Output Active Flag, both of which the BIU sets, and an Output Enable Flag which the PE CPU sets.

If the mask for a particular pending interrupt is set (Interrupt not allowed), the BIU does one of two things depending on the class of the interrupt. If the interrupt is of the enable/disable class, the interrupt is discarded; the interrupt stimulus is cleared and the BIU proceeds with its other operations. If the interrupt is of the arm/disarm class, the interrupt is retained by the BIU until the interrupt's associated mask is cleared by the PE CPU, at which time the interrupt is processed to the PE CPU (Ref 3:C-35 to C-38).

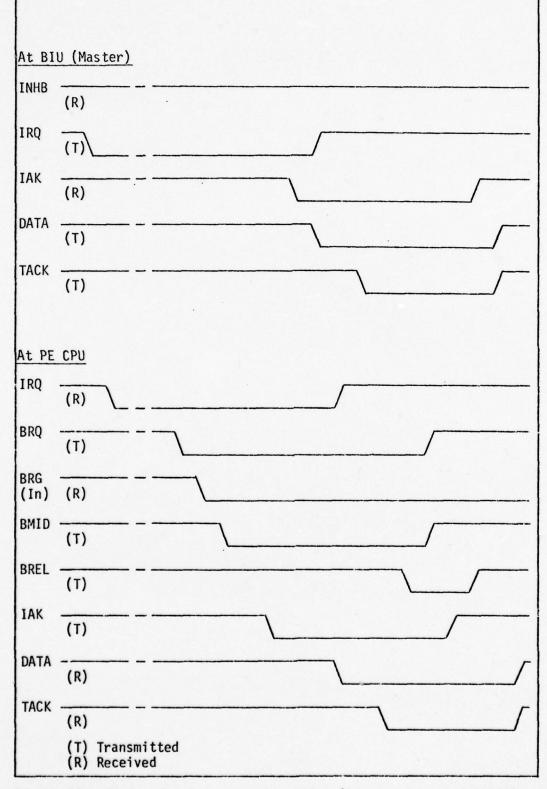

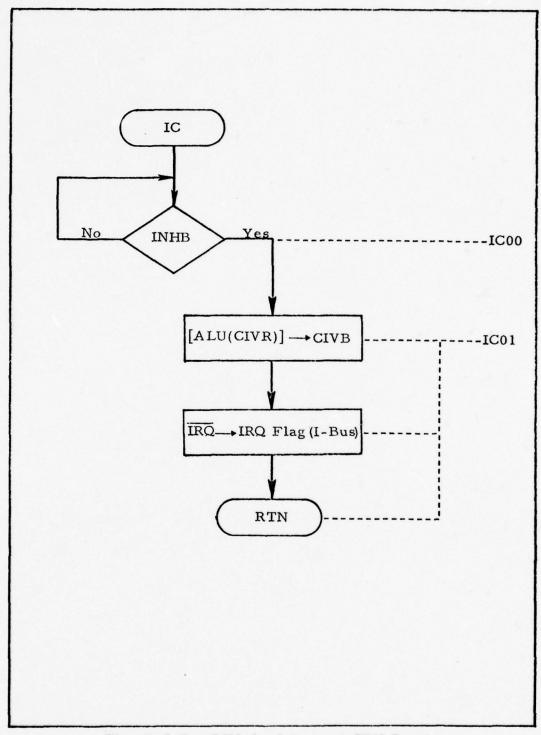

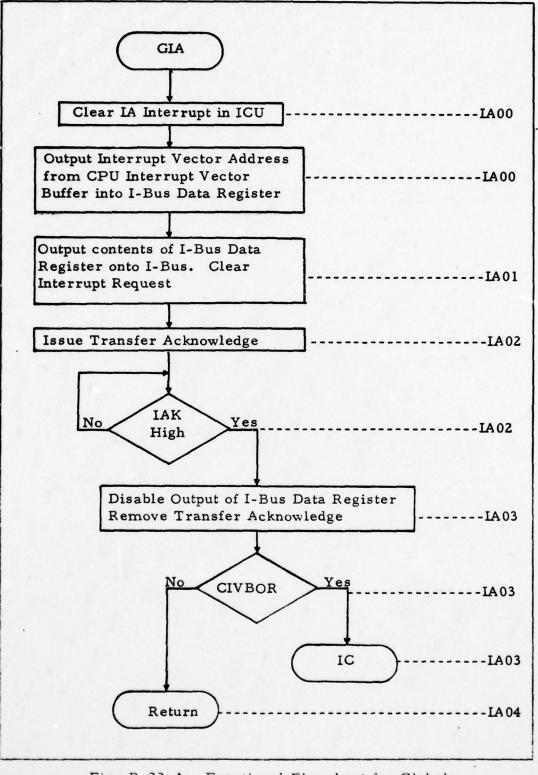

In relaying an interrupt to the PE CPU, the BIU first checks the status of the I-Bus interrupt Inhibit (INHB) line, which is used by the PE maintenance panel to inhibit all PE modules from interrupting the PE CPU when the PE CPU is operating in the maintenance panel mode. If there is no Inhibit signal (INHB high), the BIU proceeds with interrupting the PE CPU by issuing an  $\overline{IRQ}$  on the I-Bus (IRQ low designates interrupt

Figure 12. Global/Local Interrupt Status Register

request). When the PE CPU completes the execution of its current macro instruction, it detects an interrupt, then gains control of the I-Bus and honors the interrupt by issuing  $\overline{IAK}$  (IAK low designates interrupt acknowledge). When the BIU receives  $\overline{IAK}$ , it inhibits the  $\overline{IAK}$  signal from propagating to the lower priority modules. It then removes  $\overline{IRQ}$ and places the interrupt trap vector address on the data lines, DATA. After at least a 150 nano second delay, the BIU indicates that it has placed the trap vector address on the lines by issuing  $\overline{TACK}$  (TACK low designates transfer acknowledge). The processor latches the trap vector address into an internal register and then removes  $\overline{IAK}$ . When the BIU detects the removal of  $\overline{IAK}$ , it completes the interrupt operation by removing the trap vector address from the data lines and removing  $\overline{TACK}$ (Ref 3:B-6). The interrupt operation is illustrated in Figure 13.

The BIU Specification requires the BIU to provide the PE CPU with an interrupt level trap vector address instead of the trap vector address for the specific interrupt. The specification change to provide the specific interrupt trap vector address is discussed in more detail in Chapter V.

# Summary

This chapter presented the functional description or the BIU. Functional requirements definition was the first step in the design of the BIU. The next step was to define the hardware and microword required to implement the BIU functions. These are presented in the next chapter.

## III BIU DESIGN

## Introduction

The BIU designed is a laboratory test model to be used in demonstrating the DP/M concept. This design uses a bipolar bit-slice microprocessor, specifically the Am2900 Bipolar Microprocessor Family, for emulating the BIU functions. In the TI DP/M report, the BIU was to be realized with random logic hardware, and the unit was divided into functional modules (Ref 1:72-94). The feasibility of utilizing a bipolar bit-slice microprocessor for the BIU has since been demonstrated (Ref 2). With a microprocessor, it is not possible to physically maintain the functional modules proposed in the TI DP/M report, but the functional modularity is maintained in the software. Table B-1 lists the microroutines that were developed to perform the primary functions of the BIU.

Although this design uses a bit-slice microprocessor as proposed in Reference 2, a different design philosophy is used. In this design, more functions are accomplished in hardware to meet the timing requirements of the system. In the design presented in Reference 2, most of the BIU operations are accomplished in software. The philosophy was that software implementation provided greater flexibility during initial system construction and testing. Most changes could be made in software which would not require major engineering redesign. If the required speed could not be obtained, the laboratory DP/M system could be slowed down to demonstrate the feasibility of the DP/M system. Since the system was envisioned for the 1980 time-frame, it was felt that the stateof-the-art would advance sufficiently at that time to provide a microprocessor to meet all BIU timing requirements (Ref 2:11, 12, 76).

A more convincing demonstration of the DP/M concept can be made if the laboratory system operates at its specified speed. In this design, the use of a microprocessor is maintained because of the flexibility feature that it provides. To meet the speed requirements, it was necessary to implement some of the functions in hardware. In addition, it was necessary to have two separate BIU's, one for global operations and one for local operations (Ref 1:93; 2:73). The BIU is required to simultaneously transmit and receive on one global bus, monitor the alternate global bus, and transmit and receive on the local bus. In addition, communication with the PE CPU and PE Memory must be performed on a common (shared) I-Bus. Since it appeared to be impossible to perform these functions simultaneously, separate global and local BIU's are proposed.

With the exception of the redundant bus management function, the Local BIU is identical to the Global BIU. In the remainder of the chapter, only the Global BIU will be described. The hardware design and software apply to both units. For the Local BIU, where the term "Global" is used, the term "Local" can be substituted.

Because the global bus interface operations and internal bus interface operations are asynchronous operations (essentially demand/response operations) the BIU is designed as an interrupt driven microprocessor. Its detailed description is presented in this chapter. First a general description of the Am2900 Family is given, then the BIU architecture is discussed. The detailed system description begins with the Control

Section then continues with the Data Manipulation Section, I-Bus Interface Section, and the Global Bus Interface Section. Descriptions of the microroutines required to operate the BIU are presented in Appendix B.

#### Am2900 Bipolar Microprocessor Family General Description

..

The Advanced Micro Devices Incorporated Am2900 Bipolar Microprocessor Family is a group of large scale integrated (LSI) circuits designed for use in microprogrammed computers and controllers. They consist of 4-bit bipolar bit-slice devices, each device designed to be expandable and flexible to allow construction of a wide variety of machine architectures. Designed to be fundamental system building blocks, the Am2900 Family consists of circuits designed to perform data manipulation, microprogram control, macroprogram control, priority interrupt, direct memory access, input/output control, memory control, and front panel control. Utilizing Low-Power Schottky TTL Technology, these devices are very fast. See References 4, 5, 6, and 7 for technical data on the Am2900 devices used in this design.

### **BIU** Architecture

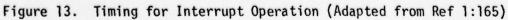

The block diagram of the BIU is shown in Figure 14. The BIU is a microprogrammed processor. Each BIU component performs a basic function and is driven by a set of control lines from a microinstruction in the Pipeline Register. The microinstruction is obtained from the Micro-program PROM.

The BIU can be divided into four major sections. First is the Global Bus Interface Section, which consists of the Bus Translation Unit (BTU), Bus Length Register (BLR), Bus Position Register (BPR), and

The Output Data Buffer (ODB). As the name implies, this section interfaces the BIU with the two global buses.

The second section is the Control Section (Figure 15), which consists of the Interrupt Control Unit (ICU), Vector Mapping PROM (VMP), Condition Code Multiplexer (CCM), Condition Code Flags (CCF), Condition Code Latch (CCL), CAW Mapping PROM (CMP), CAW Mapping PROM Register (CMPR), BIU Stack (STK), Microprogram Controller (MC), Microprogram PROM (MP), Pipeline Register (PR), and the Set/Clear Decoder (SCD). This section determines which microroutine is to be executed. Specifically, it selects the microinstruction to be executed which contains the bits to control each of the data handling components in the BIU.

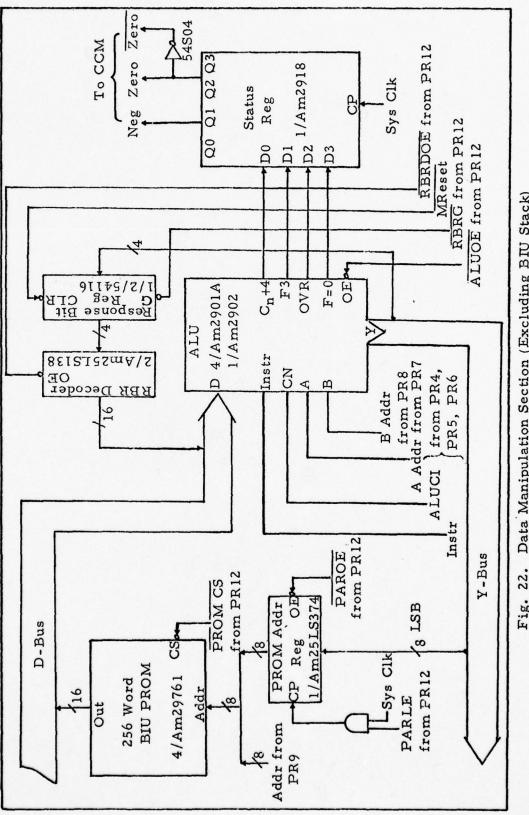

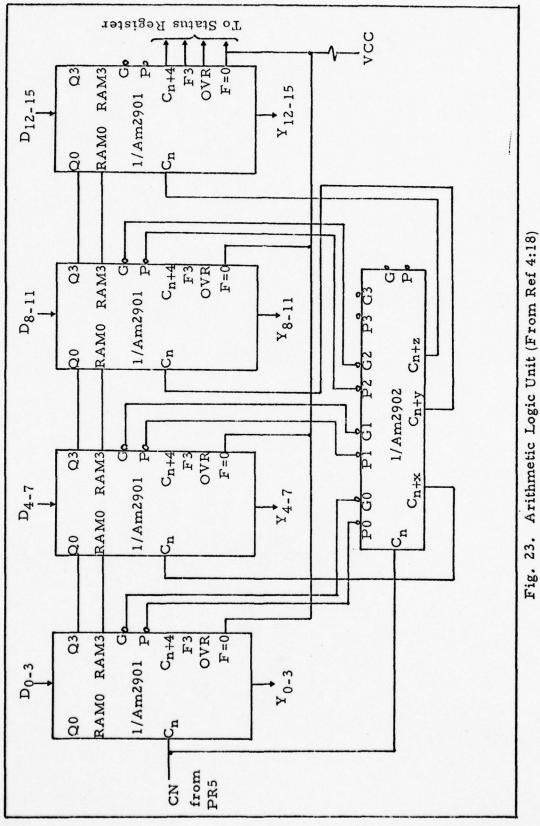

The third section is the Data Manipulation Section, which consists of the Arithmetic Logic Unit (ALU), Status Register (SR), BIU PROM (PROM), PROM Address Register (PAR), and the Response Bit Register (RBR) and decoder (RBRD). Data is processed by moving it from a register onto the D-Bus and into a working register in the ALU, performing the required operations on the data, and outputting the results onto the Y-Bus.

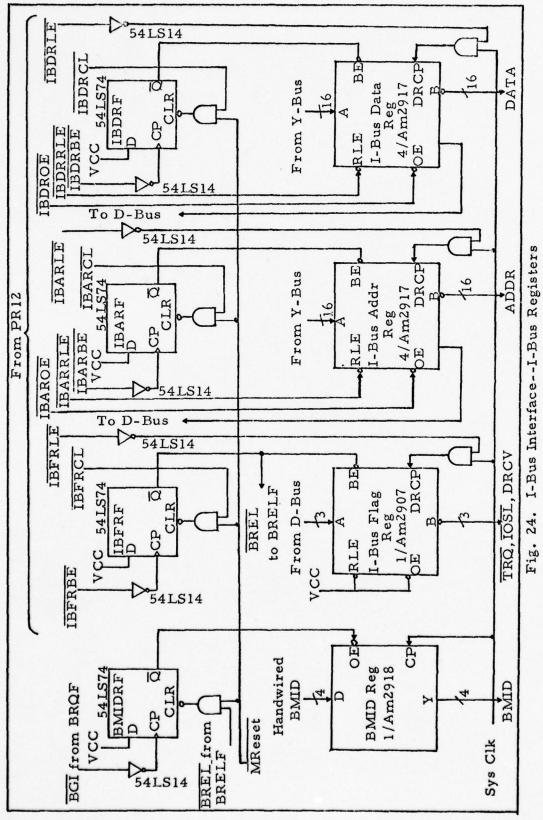

The four section is the I-Bus Interface Section, which consists of theBMID register (BMIDR), I-Bus Flag Register (IBFR), I-Bus Address Register (IBAR), I-Bus Data Register (IBDR), I-Bus Slave Control Logic (ISCL), I-Bus Master Control Logic (IMCL), and the CPU Interrupt Control Logic (CICL). Two other components associated with this section are the Input Queue Pointer Register (IQPR), and the CPU Interrupt Vector Buffer

(CIVB). As the name of the section implies, this section interfaces the BIU with the I-Bus.

There are two major buses internal to the BIU; a 16-bit wide D-Bus, primarily used for inputting data into the ALU, and a 16-bit wide Y-Bus, primarily used for outputting data from the ALU. All data transfers between registers are done via these two three-state buses.

First level pipelining is employed to improve the BIU performance. This is a technique in which the microinstruction for the next cycle is fetched from the Microprogram PROM on an overlapping basis with the execution of the current microinstruction. In this technique, the microprogram fetch, the current microinstruction being executed, and the results of the previous microinstruction are simultaneously available with respect to each other. The key hardware components are the Pipeline Register at the output of the Microprogram PROM which contains the microinstruction currently being executed and the Status Register at the output of the ALU which contains the results of the previous microinstruction.

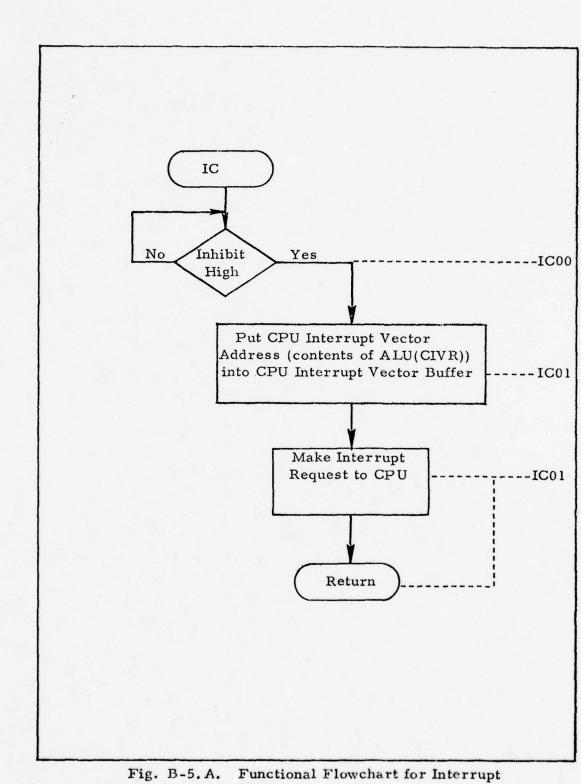

Being an interrupt driven microprocessor, the BIU does not operate from a set of machine instructions (macroinstructions). It is driven by interrupt stimuli which select the beginning address of the appropriate interrupt microroutine. Referring to Figure 14, the general operation of the BIU follows. When interrupt stimuli are received by the Interrupt Control Unit, the highest priority interrupt is determined, and an interrupt request signal is sent to the Condition Code Multiplexer and an associated 4-bit vector address is sent to the Vector Mapping PROM, which fetches the starting address for the appropriate interrupt microroutine in the Microprogram PROM. When the currently executing microinstruction

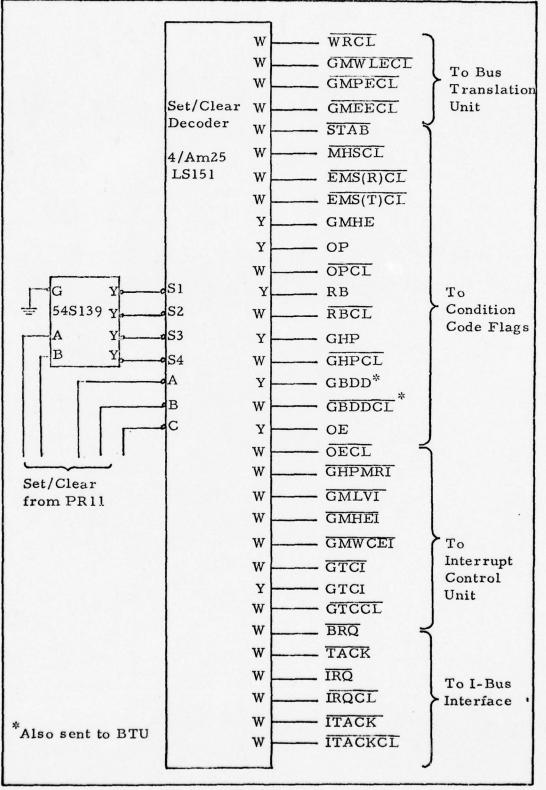

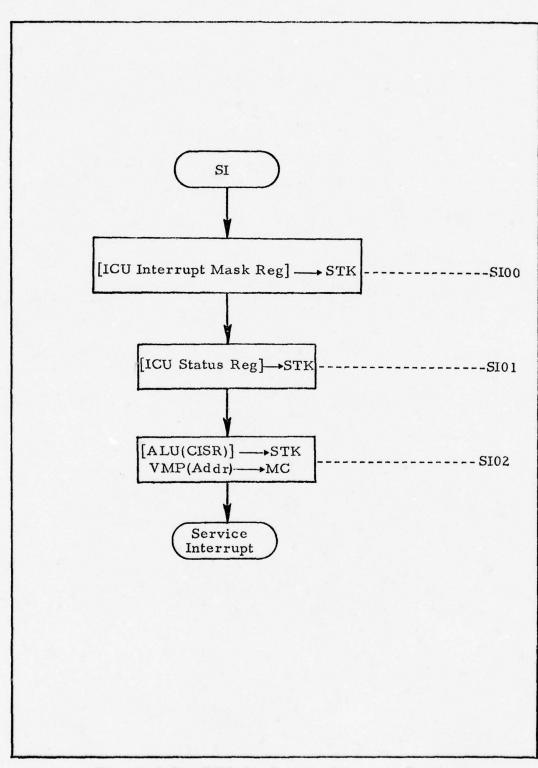

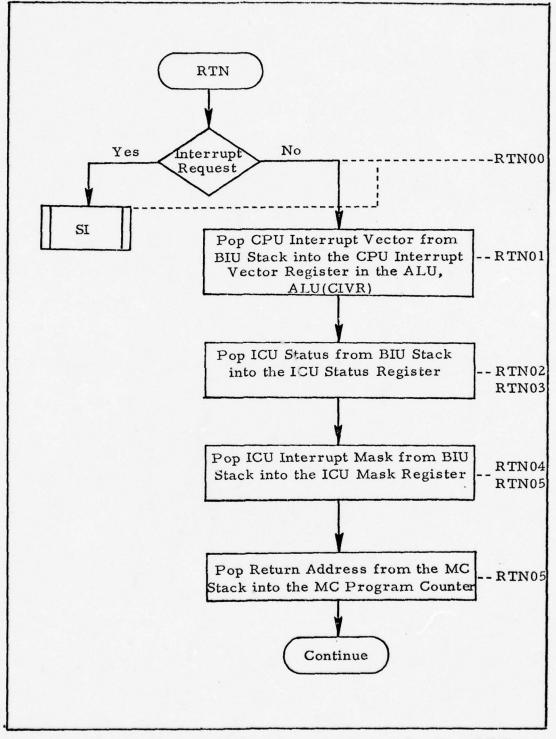

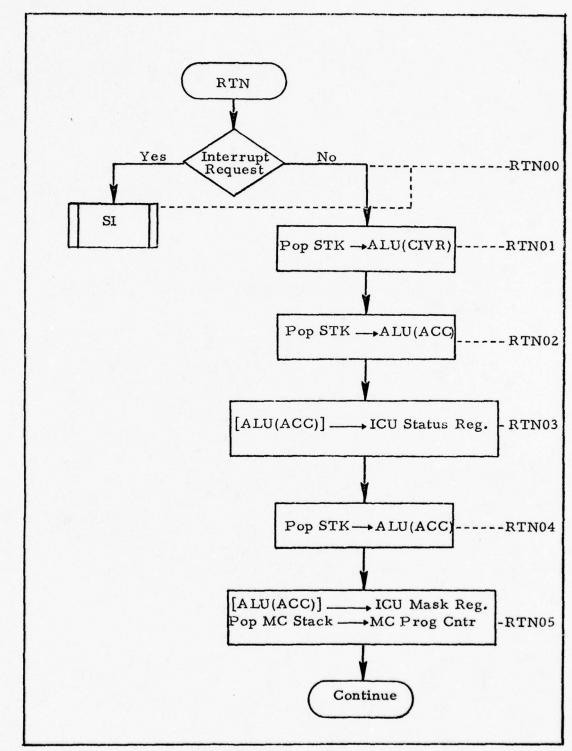

checks the Condition Code Multiplexer for interrupts, the interrupt is detected, the current microinstruction plus one is stored in the Microprogram Controller stack, and an interrupt service routine is executed. This routine stores, in the BIU Stack, the Interrupt Control Unit interrupt mask and status and the contents of the CPU Interrupt Vector Register (See Table IV). The last microinstruction of the interrupt service routine obtains from the Vector Mapping PROM the address of the first microinstruction of the appropriate interrupt routine. The microinstruction is fetched from the Microprogram PROM and placed in the Pipeline Register for execution. The microroutine may cause data to be obtained from the BUS Translation Unit, processed in the ALU, and sent to the I-Bus interface for processing to the PE memory.

### Control Section