AD A 0 48684

Stanford Artificial Intelligence Laboratory Memo AIM-304

September 1977

Computer Science Department Report No. STAN-CS-77-632

# HARDWARE VERIFICATION

by

Todd Jeffry Wagner

Research sponsored by

Advanced Research Projects Agency

COMPUTER SCIENCE DEPARTMENT

Stanford University

DISTRIBUTION STATEMENT A

Approved for public release; Distribution Unlimited

DD 1 JAN 73 1473

to the gate level.

EDITION OF 1 NOV 65 IS OBSOLETE

UNCLASSIFIED

S/N 0102-LF-014-6604 12 6 SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered)

Stanford Artificial Intelligence Laboratory

Memo AIM-304

Computer Science Department Report No. STAN-CS-77-632

# HARDWARE VERIFICATION

by

# Todd Jeffry Wagner

# ABSTRACT

Methods for detecting logical errors in computer hardware designs using symbolic manipulation instead of digital simulation are discussed. A non-procedural register transfer language is proposed that is suitable for describing how a digital circuit should perform. This language can also be used to describe each of the components used in the design. Transformations are presented which should enable the designer to either prove or disprove that the set of interconnected components correctly satisfy the specifications for the overall system.

The problem of detecting timing anomalies such as races, hazards, and oscillations is addressed. Also explored are some interesting relationships between the problems of hardware verification and program verification. Finally, the results of using an existing proof checking program on some digital circuits are presented. Although the theorem proving approach is not very efficient for simple circuits, it becomes increasingly attractive as circuits become more complex. This is because the theorem proving approach can use complicated component specifications without reducing them to the gate level.

This thesis was submitted to the Department of Computer Science and the Committee on Graduate Studies of Stanford University in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

This research was supported by the Advanced Research Projects Agency of the Department of Defense under ARPA Order No. 2494, Contract MDA903-76-C-0206. The views and conclusions contained in this document are those of the author(s) and should not be interpreted as necessarily representing the official policies, either expressed or implied, of Stanford University or any agency of the U.S. Government.

Lee 1473)

Approved for public release;

Distribution Unlimited

### **PREFACE**

This thesis represents a first attempt at developing methods for proving the correctness of computer hardware designs. After several years of experience working with simulators i realized that some sort of symbolic manipulation program would be useful in detecting errors in hardware designs. Initially I decided to pursue hardware verification along program verification lines, but the inherent lack of sequential statement execution in hardware made this approach untenable. There is a point at which program verification techniques do apply, but not until a hardware device is a sequential machine with a well understood mechanism for determining the next instruction. To verify circuits at the gate and flip-flop level requires some very different tools.

One of my major desires was to do all of this in a context that engineers would understand and be willing to use. A very simple non-procedural register transfer language is presented that can be learned in a few minutes. I believe that it includes the minimum amount of control information needed to prove things about how a device will perform in conjunction with other devices. Naturally, the specific syntax is a function of the keyboard I am using and many equivalent languages are possible.

Transformations that can be applied to statements in this language include the basic boolean operations, definitions of arithmetic functions, and some special identities that enable us to determine the effects of signal transitions as they travel thru a circuit. The list of transformations is probably far from complete and will have to be expanded as special hardware problems are encountered. An important objective is to define the language and transformations in such a way that they can be modelled by existing proof checking programs. A major reason for developing hardware verifiers is that they provide a way to prove the correctness of complex devices for which exhaustive simulation would be impractical.

I wish to thank Lynn Quam, who first suggested the idea of a hardware verifier (in the context of a block structured design automation system) as a thesis project. Richard Weyhrauch helped me with using his FOL (First-order Logic) proof checker on hardware problems. Finally, director John McCarthy and the faculty, students, secretaries, and bureaucrats have all made working at the Stanford Artificial Intelligence Lab an exciting experience.

| <b>NCCESSION</b> | for          |               |  |  |

|------------------|--------------|---------------|--|--|

| KTIS             |              | White Section |  |  |

| DOC              | 1            | Buff Section  |  |  |

| JUSTIFICAT       |              |               |  |  |

|                  | ION/AYAILABI |               |  |  |

| Dist. A          | VAIL and/    | or SPECIAL    |  |  |

| 4                |              |               |  |  |

# **Table of Contents**

|    | Section                                          | Page |

|----|--------------------------------------------------|------|

| 1. | INTRODUCTION                                     | 1    |

|    | 1.1 Basic assumptions                            | 3    |

|    | 1.2 Relationship to design compilers             | . 3  |

|    | 1.3 Advantages over simulation                   | 4    |

| 2. | DESIGN AUTOMATION LANGUAGES                      | . 5  |

|    | 2.1 Procedural register transfer languages       | 5    |

|    | 2.2 Non-procedural register transfer languages   | 6    |

| 3. | HARDWARE VERIFICATION LANGUAGE                   | 9    |

|    | 3.1 Basic syntax                                 | 9    |

|    | 3.2 Variables and constants                      | 9    |

|    | 3.3 Expressions and operators                    | 10   |

|    | 3.4 Language examples                            | 11   |

| 4. | DEFINITIONS AND AXIOMS                           | 12   |

|    | 4.1 Boolean reductions                           | 12   |

|    | 4.2 Definitions for subscripts and concatenation | 14   |

|    | 4.3 Definitions of arithmetic operators          | 15   |

|    | 4.4 Miscellaneous transformations                | 17   |

| 5. | FEEDBACK                                         | 19   |

|    | 5.1 Implicit feedback                            | 19   |

|    | 5.2 Axioms for explicit feedback                 | 21   |

| 6. | TRANSITION ALGEBRA                               | 23   |

|    | 6.1 Basic axioms                                 | 23   |

|    | 6.2 Mathematical basis of transition algebra     | 25   |

|    | 6.3 Transitions thru combinational circuits      | 26   |

|    | 6.4 Transitions thru sequential circuits         | 28   |

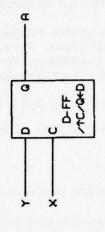

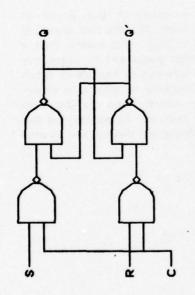

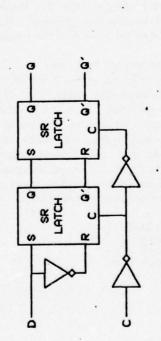

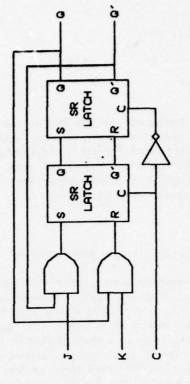

|    | 6.5 Flip-flop design and modelling               | 29   |

| 7. | ERROR CONDITIONS                                 | 31   |

|    | 7.1 Race and hazard jargon                       | 31   |

|    | 7.2 Race and hazard detection                    | 32   |

|    | 7.3 Oscillation                                  | 34   |

|    | 7.4 Other error conditions                       | 35   |

| 8. | MICROPROGAM VERIFICATION                         | 37   |

|    | 8.1 Microprogram vs. program verification        | 37   |

|    | 8.2 Hardware verification for microcoded devices | 38   |

| 9. | HARDWARE VERIFICATION USING FOL                  | 39   |

|    | 9.1 Syntax modifications                         | 39   |

|    | 0.2 FOI commands                                 | 40   |

# **Table of Contents**

|     | Section                                      | Page     |

|-----|----------------------------------------------|----------|

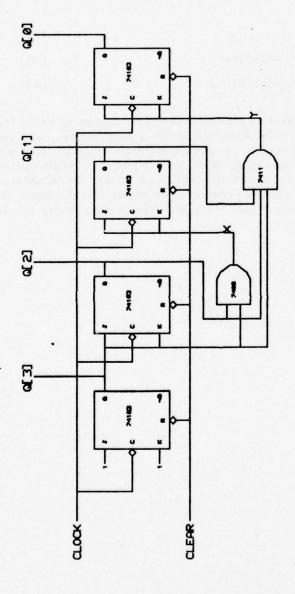

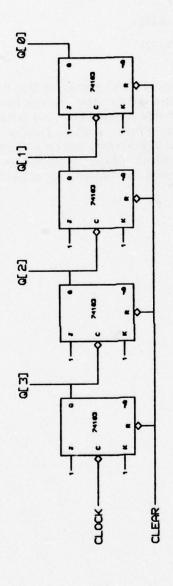

| 10. | SYNCHRONOUS COUNTER                          | 43       |

| 11. | RIPPLE COUNTER                               | 49       |

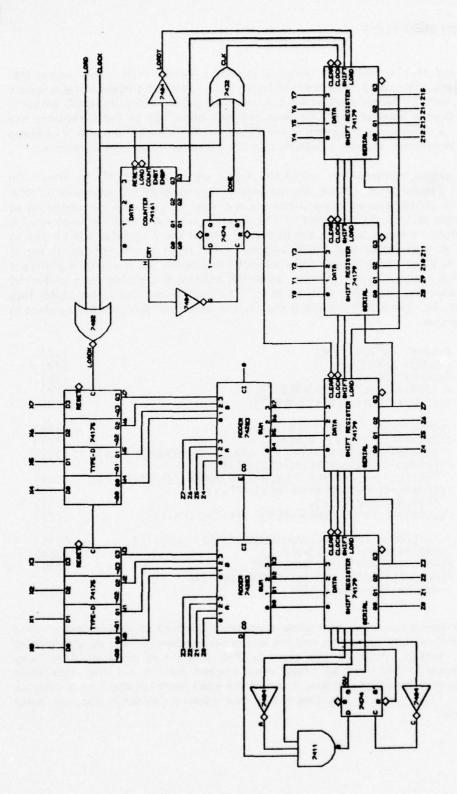

| 12. | 8-BIT MULTIPLIER                             | 59       |

| 13. | CONCLUSIONS                                  | 80       |

| 14. | REFERENCES                                   | 81       |

|     | 14.1 References on design verification       | 81       |

|     | 14.2 References on design languages          | 81       |

|     | 14.3 References on transitions               | 84       |

|     | 14.4 References on races and hazards         | 85<br>86 |

|     | 14.5 References on microprogram verification | 87       |

|     | 14.6 FOL references                          |          |

|     | Appendix                                     | Page     |

| Α.  | BNF LANGUAGE DESCRIPTION                     | 88       |

| В.  | LIST OF TRANSFORMATIONS                      | . 90     |

| c.  | TRANSITIONS THRU HAZARDS                     | 95       |

| D.  | FOL DECLARATIONS AND AXIOMS                  | 97       |

| F   | COMPONENT DEFINITIONS                        | 99       |

# 1. INTRODUCTION

This thesis discusses a method for detecting errors in digital hardware designs. A system, or module, is specified using a non-procedural register transfer language. The components that will be used to build the device are also specified in this language. A symbolic manipulation technique can then be used to determine if the interconnected components correctly satisfy the specifications for the overall system. Essentially, the process of hardware verification is based on boolean reductions and some methods for analyzing the consequences of signal transitions. The symbolic manipulation approach should be able to detect timing anomalies, such as races and hazards, in addition to logical inconsistencies.

The desirability of using proofs of correctness to detect errors in hardware designs has been discussed previously [1,4], but everyone has a different idea about what level of description should be used. Some authors think in terms of a finite state automaton that can accept or reject an input sequence depending on the algorithm it represents. Still others are interested in determining if a given algorithm correctly implements a complex mathematical function. In this paper a proof of correctness will based on showing that, for any single input change, equivalent state changes will take place in both logic descriptions. In other words, if both models of the logic are in equivalent states and the same input variable is changed on each of them, then they will change to new states that are also equivalent.

Hardware verification, as presented here, is entirely oriented to the register transfer level of system description. Problems such as validation of physical layout or design rule checking are not addressed. The circuit level, involving semiconductor physics and critical time constants, is also not discussed. Nevertheless, the register transfer level does cover a large spectrum of computer design activities. It can be used to determine if the specifications of an integrated circuit are fulfilled by the gates within the chip, or if a set of chips satisfy the definition of a complete backplane. These techniques can also be used to see if interconnected cards or backplanes correctly satisfy the requirements for whole computers.

The most important idea behind hardware verification is the concept of breaking down the specifications as little as possible. If a designer specifies the operation of binary addition in the system description and provides an adder chip in the actual circuit, then it will only be necessary to show that the correct data and control signals are sent to this chip. In this case, breaking the addition operation down to the gate level will not be necessary. This is especially useful with LSI components such as microprocessors. The microprocessor can supply the complex operations and the verifier will only have to show that the support circuitry sends it the correct control information.

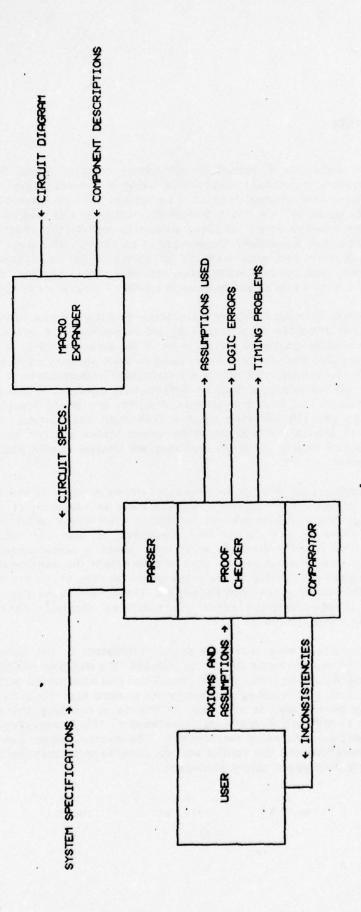

FIGURE 1.1 HARDWARE VERIFICATION

### 1.1 Basic assumptions

A couple of assumptions must be made regarding timing. Any circuit can be made to operate erroneously if certain external inputs are changed simultaneously, so race detection will not include these circumstances. If the circuit is to be used in conjunction with other circuits it will be possible to detect races in the composite device by verifying the overall circuit. Components will not have specific delays. When a possible race is detected a hardware verifier might be able to indicate which component(s) must be faster than which other component(s) to insure correct operation. The verification process does not say anything about how fast a circuit will operate, only that it will work correctly at some (slow enough) speed if the races and hazards are taken care of.

There is also the philosophical question of what to do about unspecified operations. The actual circuit will almost always include other operations and state variables in addition to those specified in the system description. If a designer uses an LSI device such as a microprocessor to perform only a few operations there will be a wealth of unspecified operations. A three bit counter can be implemented by using a four bit counter circuit and not connecting the high order bit. At the same time, it is easy to design a circuit in which the unspecified operations can mean disaster. It is important to be able to differentiate between additional operations that are acceptable and those that are not, since a circuit can satisfy its specifications without being equivalent to them. Some solutions to this problem are discussed in the section on feedback.

# 1.2 Relationship to design compilers

At present there are a number of design compilers that can take the specifications for a hardware device and generate the necessary circuitry. The resulting design will be correct and have a near minimal number of gates and flipflops because of the use of sophisticated state reduction techniques. Although fairly successful, design compilers have several shortcomings. In much the same way that good hand coding of software can beat an optimizing compiler, circuit designers can usually find novel ways to use components that a design compiler would miss. With current LSI components it is often cheaper to throw in a complex device than to build a circuit using the minimal number of gates and flipflops. A more serious problem is that it is virtually impossible to give a design compiler the ability to use more than a small fraction of the new components rapidly becoming available. Furthermore, the best component for a given application can depend on such varied factors as price, size, and shape as well as the usual electrical characteristics. Under these circumstances, it would seem more reasonable to use a program that lets the designer use whatever components he chooses and then checks for design errors.

A major advantage of a hardware verifier is that it can provide great flexibility when modifying a circuit. Suppose that a device has been in the field for a few years when a new component is developed that can replace several used in the original design. Using hardware verification it should be fairly simple to determine if using the new component will change the behavior of the device in any way. If the behavior is changed, the verification system can indicate what the differences are so they can be dealt with appropriately.

Incidentally, one approach to hardware verification has been to submit two specifications for the same device to a design compiler and see if it generates equivalent circuits [5]. It is unclear how this would be used when one description can satisfy the other without being equivalent to it.

# 1.3 Advantages over simulation

The most popular method for checking hardware designs is digital simulation. Earlier attempts at comparing high level and low level descriptions of digital devices based on simulation are discussed in [2,3]. Admittedly, digital simulation is much easier to implement on a computer than the symbolic manipulation techniques presented in this paper. Simulation methods are well understood, and are very useful for generation of fault tests that can be used to speed repairs after a device is in the field. On the other hand, simulation cannot determine if a design is correct unless it is exhaustive. It may be lucky enough to find some bugs, but others may go undetected.

The greatest disadvantage of simulation is that certain assumptions must be made about initialization, delays, and the possible values of signals. Unless the logic being designed has a reset signal it is impossible to determine the initial state of sequential elements at power-up time. Some simulators assume zero delay components, others give each component a unit delay, while still others give each component type a different delay value. These delay values may have little to do with the real world where two parts of the same type can have very different propagation delays. Simulators are generally two value or three value. Two value simulators use only zero and one, while three value simulators include an undefined state to be used during initialization and signal transitions. Three value simulators can detect races, even where they don't really exist, under certain delay assumptions.

Hardware verification can determine correctness of a circuit and produce a list of possible races and hazards, along with information on how to prevent them. There are no assumptions about circuit initialization since it is based on showing that a circuit satisfies its specifications regardless of initial state. Hardware verification will also generate results that are easier to interpret. It can show inconsistencies in the context of boolean expressions instead of the pages of ones and zeros output by most simulators. Symbolic manipulation techniques can often be much faster than simulation since they can handle arbitrarily complex devices without always breaking them down to the gate level.

# 2. DESIGN AUTOMATION LANGUAGES

An incredible number of hardware design languages have been proposed, many have been implemented, and several have become popular in the design community. Entire papers have been devoted to the philosophy of these languages [7,9,16,27,38,38,45,49] and to surveys comparing and contrasting some of the more popular ones [8,25,33,50,51]. Design automation languages are generally classified as structural or behavioral, although some attempt to be both. Structural languages are primarily intended to provide information such as where data paths go and where control information originates. A good example of a purely structural language is PMS [11,12,47], which is actually just a formalized notation for drawing block diagrams of computer systems.

Behavioral languages, on the other hand, attempt to describe what a system does without implying anything about the hardware structure. These languages are often used as simulation models and to help in software production. At a somewhat more detailed level behavioral languages can be organized to provide some inkling of how the system itself is organized, but they could just as easily imply an entirely different structure and still emulate the hardware correctly. Virtually all behavioral languages are register transfer languages, in which the basic unit of information is a vector of binary digits. Since they were first proposed by Reed [42] in the 1950's register transfer languages have developed into procedural and non-procedural types. Several of the procedural languages have complex control structures that permit them to operate in a non-procedural manner.

### 2.1 Procedural register transfer languages

Most procedural register transfer languages are programming languages modified to handle register operations. Instructions are executed sequentially, but in some languages special constructs are provided to permit parallel execution of blocks. Several procedural hardware languages are based on APL [13,26,28,30,31,32], whose advocates are quick to point out the tremendous power of the vector and matrix operations already in the language. Although very compact, hardware descriptions in APL-like languages are among the most difficult to read. Another large group of procedural hardware languages are based on Algol [9,11,12,22,29,35,46]. The block structure of Algol can often be used to help describe the system structure.

Still other procedural languages are based on state machines [14,15,23,24]. In state machine languages the logic is partitioned into blocks whose execution is controlled by state registers. Special instructions are provided to allow the state registers to be altered. Finally, there are some languages [34,39,44] that divide the logic into data manipulation blocks and a control microprogram. These are essentially the same as the state machine languages except that in the latter the control microprogram is embedded in the data manipulation blocks.

The major advantage of procedural register transfer languages is that algorithms are easy to read and understand. Many of the procedural languages provide subroutine and macro facilities. Since there is a definite order for executing statements, GOTO statements are acceptable. Procedural hardware languages are excellent for systems level simulation and are frequently used when producing software for new computers.

Unfortunately, the details of how the control and timing circuits operate are not revealed to the user. Since statements are executed more or less sequentially, it is implied that there is some control logic making sure things happen at the correct time. In many procedural languages specifying parallel operations and whether an operation is synchronous or asynchronous is very difficult. For these reasons, the hardware verification process described in this paper will be based on a non-procedural register transfer language.

### 2.2 Non-procedural register transfer languages

The most popular non-procedural register transfer language is called the Computer Design Language, or CDL [17,18,19,20,21]. This popularity is largely due to fact that CDL translators and simulators have been made available to the university community. Below is a CDL description of a stored program computer. First come the declarations which specify the names of all of the registers, switches, and circuit nodes.

| Register,    | PC(8-11),<br>IR(8-15),<br>ACC(8-15),<br>ADR(8-11),<br>CYCLE(8-1),<br>G,                                           | Sprogram counter Sinstruction register Saccumulator Saddress register Scontrol register Srun/halt flag                                                           |

|--------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Subregister, | IR(OP)=IR(8-3),<br>IR(MA)=R(4-15),                                                                                | Sopcode part of IR<br>Saddress part of IR                                                                                                                        |

| Memory,      | M(ADR)=M(6-4695,6-15),                                                                                            | Smemory and address register                                                                                                                                     |

| Decoder,     | C(0-3)=CYCLE,<br>I(0-15)=IR(OP),                                                                                  | \$decode control register<br>\$decode instruction opcode                                                                                                         |

| Terminal,    | STOP=C(0),<br>FETCH=C(1),<br>EX=C(2),<br>LD=I(0),<br>ST=I(1),<br>CLA=I(2),<br>ADD=I(3),<br>SUB=I(4),<br>JMP=I(5), | Shalt state Sinstruction fetch Sinstruction execute Sload accumulator Sstore accumulator Sclear accumulator Sadd instruction Ssubtract instruction Sjump command |

Switch, RUN(ON), Srun button Shalt button

Clock, T(1-2), Stwo-phase clock

Register declarations define the size and bit ordering (msb-lsb) for each register, while subregister declarations permit a group of bits to be given a special name. The memory declaration specifies both the size of a memory and which register will be used as the address register. Decoders are used to create a vector in which only one bit is true, selected by the value of a register. In the example above, C(0) will be true if CYCLE=0, C(1) will be true if CYCLE=1, and so on. Switch statements provide variables that can be controlled internally by the hardware and externally by data supplied to the CDL simulator. Terminal statements are used to rename terminals and describe logic networks. The clock statement can provide multiple clock phases, and in this example clock phases T(1) and T(2) will be repeated continuously.

There are also CDL declarations that permit several operations to be grouped into a block, creating a sort of subroutine/macro facility. Some of the declarations, such as subregisters and terminals, are not absolutely necessary. The same logic could be described by using subscripts and the original terminal names in the logic description. However, these declarations do tend to make the description easier to understand. Below are the statements describing the actual operations of a computer using the clocks and registers declared previously.

```

Comment, run and halt controls.

G+1,

/RUN(ON)/

G+Ø,

/HALT(ON)/

/STOP*T(2)/

IF (G=1) THEN (CYCLE+1),

IF (G=0) THEN (CYCLE+0) ELSE (CYCLE+1),

/EX*T(2)/

Comment, instruction and operand addressing.

ADR-PC.

/FETCH*T(1)/

/FETCH*T(2)/

IR+M(ADR), CYCLE+2, PC+countup PC,

ADR-IR(MA),

/EX*T(1)/

Comment, instruction execution.

/LD*EX*T(2)/

ACC+M(ADR),

/ST*EX*T(2)/

M(ADR)+ACC,

/CLA*EX*T(2)/

ACC+8.

/ADD*EX*T(2)/

A+A add M(ADR),

/SUB*EX*T(2)/

A+A sub M(ADR),

PC-IR(MA),

/JMP*EX*T(2)/

End

```

The expression enclosed in slashes is a conditional expression where the "\*" should be interpreted as a logical AND. Most statements contain one or more terminals and a clock phase. If all of the terminals are true, then the operation indicated will occur at the specified time. Although they make the description

more readable, the IF-THEN and IF-THEN-ELSE statements are not really needed. The same effects could be obtained by modifying the conditional expressions to include the information in the IF clauses. Arithmetic and logical operations are performed by predefined functions such as "shr" (shift right), "countup" and the like.

Although the specific syntax of declarations and statements may vary, virtually all non-procedural register transfer languages share the concept of permitting a conditional label to be attached to each statement. Obviously a non-procedural hardware description is more detailed than a procedural one. At the same time, algorithms become far less readable. Macro-like features can be provided, but true subroutines cannot because going to a routine and returning are sequential events. Parallelism is not a problem since any number of statements can be executed at the same time. CDL is good for describing synchronous logic but cannot be used for asynchronous circuits.

The Asynchronous Circuit Design Language, or ACDL [10], permits transitions such as  $X\rightarrow \emptyset$  or  $X\rightarrow 1$  in the conditional expressions. This means that events can be described as happening on the negative or positive edge of signal transitions. ACDL is a state machine language which uses these transitions to change states. For the purpose of hardware verification we will develop a language similar to CDL that also allows transition information in the conditional expressions.

# 3. HARDWARE VERIFICATION LANGUAGE

Since the purpose of this paper is to discuss hardware verification techniques and not to create yet another elegant design language, the language presented here is extremely simple. Such luxuries as macros and complex operators are not included at this time. As with most register transfer languages, the actual syntax is largely a function of the keyboard available to the author. A BNF description of this language will be found in Appendix A.

# 3.1 Basic syntax

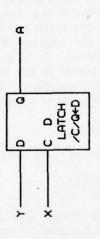

To begin with, there are no declarations. Hardware verification involves checking a higher level description of a device against a lower level description of the same device. In a sense, the higher level description can be thought of as providing the register declarations for the lower level description. In other computer design languages register declarations are used to allocate storage space for simulation. This is not necessary here because we are not going to simulate the logic. Subregisters and memories can be indicated by using subscripts in the actual statements. Clock declarations are not needed since any variable can be used as a clock. Every statement will be in one of the two forms shown below. The conditional expression is optional and will not be needed when describing combinational devices.

variable + expression;

/conditions/ variable + expression;

#### 3.2 Variables and constants

A variable name must begin with a letter and can contain letters, digits, single quotes, and underscores. The name can be any length. Variables may also have one or two subscripts enclosed in square brackets. If there are two subscripts, they are separated by a comma. The first subscript is a bit number and can be a constant, two constants separated by a colon, or an expression. The second subscript is a memory location and may be a constant or an expression. Additionally, variables can be joined using the "&" (concatenation) operator. Some examples of variables are shown below.

X123'

PROGRAM\_COUNTER

ACC[3]

INDEX[0:15]

REG1[BIT[0:3]]

MEMORY[0:15,PC[0:15]+BASE\_REG[0:15]]

A[0]&B[2:5]

For the time being constants are in decimal. Binary constants can be written as ones and zeroes concatenated together.

## 3.3 Expressions and operators

Expressions can consist of variables, constants, and other expressions joined by various logical and arithmetic operators. The result of an expression can be one bit or a vector of bits. Below is a list of the operators in order of their precedence. Parentheses can be used to alter precedence, and operations of equal precedence are evaluated from left to right.

| 7 |   |   |   |   |   | logical complement                  |

|---|---|---|---|---|---|-------------------------------------|

| + |   |   |   |   |   | transitions (conditional exp. only) |

| & |   |   |   |   |   | concatenation                       |

| + | - |   |   |   |   | arithmetic operations               |

| = | # | > | < | 2 | 5 | arithmetic relations                |

| ٨ |   |   |   |   |   | logical and                         |

| V |   |   |   |   |   | logical or/exclusive or             |

Conditional expressions are similar to other expressions except that they must have a one-bit (true/false) result. This means that conditional expressions can have the above operations (except concatenation) performed on one-bit operands, and may include arithmetic relations when comparing bit vectors.

The transition operators are "†" (8+1 transition) and "‡" (1+8 transition). These can only be used in conditional expressions, and must only be applied to one-bit operands or subexpressions. It is important to avoid constructs such as "¬†" and "¬‡" except to indicate feedback states in which the variable does not change. Otherwise it would imply that state changes can happen as a result of a transition not occurring. A basic assumption in hardware verification is that events are caused by other events, and it is unclear how we should handle events that are the result of non-events.

There is a special meta operator designated by the "\*" character. It is used in conjunction with subscript expressions to mean all values not equal to that expression. In other words, the expression

A[ \*B[0:7]]

might be used to indicate all of the bits in register A except the one pointed to by the value in register B. The reasons for having this operator, and some special rules for how to use it, are discussed in the section of feedback.

# 3.4 Language examples

Here are some examples of statements in the hardware verification language. Parentheses are added for clarity in some places where the precedence of operations would have done the correct thing. Note that some logical operations, such as shifts and rotates, can be accomplished thru subscript manipulation and do not require special operators. The first three examples represent very simple gates and flip-flops, while the other examples are what might be found in computer descriptions or LSI component specifications.

```

A+¬(BAC); (combinational)

/CLK/ Q+D; (asynchronous)

/+CLK/ Q+Q;

/+CLK/ Q+(JA¬Q)v(¬KAQ); (synchronous)

/¬+CLK/ Q+Q;

/(OPCODE[0:5]=0&1&0&0)A+T2/ A[0:15]+A[1:15]&A[0];

/(XA+PHASE1)v(YA+PHASE2)/ A[0:15]+B[15]&B[0:15]+B[15]&A[0:15]&B[0:14];

/FETCHA+(T1AENABLE)/ INSTR[0:15]+MEMORY[0:15,PC[0:11]];

/+P2v(+P3ACLOCK_ENAB)/ ACC[BIT[0:3]]+A[0]=OVERFLOW;

```

### 4. DEFINITIONS AND AXIOMS

In order to show that a lower level description of a device satisfies some higher level specification, we must develop ways to manipulate the statements in the descriptions. The identities in this section are those that the author has found useful in solving specific verification problems. This list is by no means complete, and additional transformations will have to be invented as more circuits are analyzed.

In the definitions of vector operations bit 0 is the most significant bit, although the opposite bit ordering can be implemented just as easily. Note that in most of these definitions X[i:j] and Y[i:j] are used only to make the notation simpler. These definitions are valid for arbitrary vectors (exp1&exp2&...&expn) whether they are part of the same register or not. Generally speaking, letters near the end of the alphabet such as X,Y, and Z will be used to denote arbitrary expressions, including variables. Letters at the beginning of the alphabet, namely A and B, will indicate variable names only.

Arithmetic operations are generally defined in the context of positive integers. Other arrangements, such as 2's complement or signed magnitude, can be developed from these with some extra logic in the user's circuit descriptions. It is also possible to implement definitions for other types of arithmetic in the verifier itself.

### 4.1 Boolean reductions

Switching algebra identities like those shown below can be found in most logic design texts. The list below is neither exhaustive nor is it minimal. A hardware verification program could use these transformations directly in a pattern matching routine, or it could use some iterative boolean minimization techniques based on only a few of them. The first few axioms define the basic nature of AND, OR, and NOT.

- T1. ¬θ ≡ 1 ¬1 ≡ θ

- T2. X∨1 ≡ 1 X∧0 ≡ 0

- T3. Xv0 = X X^1 = X

- T4. X∨X ≡ X X∧X ≡ X

- T5. ¬(¬X) € X

The next few transformations involve combinations of two or more variables. They can be derived from the identities above by substituting ones and zeros for the variables.

T8.

$$X\vee(X\wedge Y) \equiv X$$

$X\wedge(X\vee Y) \equiv X$

T9.

$$(X \lor \neg Y) \land Y \equiv X \land Y$$

$(X \land \neg Y) \lor Y \equiv X \lor Y$

T10.

$$(X \lor Y) \lor Z = X \lor (Y \lor Z)$$

$(X \land Y) \land Z = X \land (Y \land Z)$

T11.

$$X \land (Y \lor Z) \equiv (X \land Y) \lor (X \land Z)$$

$X \lor (Y \land Z) \equiv (X \lor Y) \land (X \lor Z)$

T12.

$$(X \lor Y) \land (\neg X \lor Z) \land (Y \lor Z) \equiv (X \lor Y) \land (\neg X \lor Z)$$

$(X \land Y) \lor (\neg X \land Z) \lor (Y \land Z) \equiv (X \land Y) \lor (\neg X \land Z)$

T13.

$$(X\vee Y)\wedge (\neg X\vee Z) \equiv (X\wedge Z)\vee (\neg X\wedge Y)$$

The last identity, DeMorgan's law, is valid for expressions of arbitrary length. However, the two variable version may be easier to implement and can acheive the same result by being applied repeatedly. It may also be convenient to define a series of transformations for the exclusive-or function.

X1.

$$(X \land \neg Y) \lor (\neg X \land Y) \equiv X \bullet Y$$

X7.

$$(X \oplus Y) \oplus Z \equiv X \oplus (Y \oplus Z)$$

# 4.2 Definitions for subscripts and concatenation

Definitions D1 thru D4 can be used to reduce several concatenated variables into a single register variable, or vice-versa. The first two are used to change register variables with only one or two subscripts into the full three subscript format. This is to make them compatible with D3 and D4. Another approach would be to develop identities like D3 and D4 for each combination of one or two subscripts. In a hardware verification program it would probably be easlest to have the input parser convert registers into the three subscript format automatically.

- D1. A[i] = A[i:i]

- D2. A[i:j] = A[i:j,0]

- D3. A[i:j,s]&A[j+1:k,s]  $\equiv$  A[i:k,s] where  $i \le j \le k$

- D4.  $\neg A[i:j,s] \& \neg A[j+1:k,s] = \neg A[i:k,s]$ where  $i \le j \le k$

The next definition points out that concatenation is associative, while the following three show that performing a logical operation on vectors (of equal length) and concatenating the result is equivalent to concatenating the vectors and then performing the logical operation. Keep in mind that these definitions are valid for arbitrary vectors which do not have to be part of the same register.

- D5. (X&Y)&Z = X&(Y&Z)

- D6.  $(X[i:j] \land Y[i:j]) & (X[j+1:k] \land Y[j+1:k]) = X[i:k] \land Y[i:k]$  where  $i \le j \le k$

- D7.  $(X[i:j] \lor Y[i:j]) & (X[j+1:k] \lor Y[j+1:k]) = X[i:k] \lor Y[i:k]$  where  $i \le j \le k$

- D8.  $(X[.i:j] \bullet Y[i:j]) & (X[.j+1:k] \bullet Y[.j+1:k]) = X[.i:k] \bullet Y[.i:k]$  where  $i \le j \le k$

Definitions D9 and D10 (decoder) show how to expand a variable with an expression as a subscript when it is used as the destination in a register transfer. The definitions are nearly identical, except that D9 is used when the first subscript is an expression and D10 is used to expand the second subscript. If a variable has expressions for both subscripts we can use D9 and then D10 or vice-versa. It would not be reasonable to expand a statement into several thousand using these definitions, but a theorem prover could use this information to determine the status of specific bits in a register or memory without generating statements for all possible values of n.

- D9. /X/ A[Y[i:j],s]+Z;

/X^(Y[i:j]=n)/ A[n,s]+Z;

- D18. /X/ A[s,Y[i:j]]+Z;

#

/X^(Y[i:j]=n)/ A[s,n]+Z;

Similarly, D11 and D12 (multiplexor) indicate how to expand a variable with an expression as a subscript when that variable is used as part of an expression. This includes conditional expressions as well as register transfer expressions. As before, there are versions for the first subscript and the second subscript.

- D11.  $A[Y[i:j],s] = (A[0,s] \land (Y[i:j]=0)) \lor (A[1,s] \land (Y[i:j]=1)) \lor ... \lor (A[n,s] \land (Y[i:j]=n))$ when A[Y[i:j],s] is used in an expression

- D12.  $A[s,Y[i:j]] = (A[s,0] \land (Y[i:j]=0)) \lor (A[s,1] \land (Y[i:j]=1)) \lor ... \lor (A[s,n] \land (Y[i:j]=n))$ when A[s,Y[i:j]] is used in an expression

# 4.3 Definitions of arithmetic operators

In this subsection we have the definitions for the various arithmetic operations and relations permitted in the language. The first two definitions are for the carry operation. Definition A1 puts it in terms of ANDs and ORs, while A2 provides a way to combine carries from vectors to determine the carry function for larger vectors. The second definition will probably find more use since most adder chips provide carry-in and carry-out pins but take care of their own internal carries.

- A1. X[i]\Y[i]\V(X[i]\Y[i])\CI = carry(X[i],Y[i],CI)

X[i]\Y[i]\V(X[i]\Y[i])\carry(X[i+1:j],Y[i+1:j],CI) =

carry(X[i:j],Y[i:j],CI)

Addition is a fairly sophisticated operation, but becomes much simpler using the carry functions defined above. It can be specified on a bit by bit level, as in A3, or as a concatenation of adders as in A4. Once again, the definition which permits us to concatenate small adder chips into big adders will be the most useful in real verification problems. The carry-in (CI) bit is included in the

addition definitions to facilitate working with adder chips which usually include this input.

- A3.  $(X[i] \bullet Y[i] \bullet CARRY(X[i+1:j], Y[i+1:j], CI) \& (X[i+1] \bullet Y[i+1] \bullet CARRY(X[i+2:j], Y[i+2:j], CI) \& ... \& (X[j] \bullet Y[j] \bullet CI) = X[i:j] + Y[i:j] + CI$

- A4.  $(X[i:j]+Y[i:j]+CARRY(X[j+1,k],Y[j+1,k],CI))\& (X[j+1:k]+Y[j+1:k]+CI) = X[i:k]+Y[i:k]+CI where <math>i \le j \le k$

We will also define two special cases of addition, subtraction and increment. Subtraction can be implemented in either ones-complement or twos-complement, and the carry-in bit defined above provides an easy way to select which. Although increment could be derived from the addition definition as needed, we will make it an axiom. This can make some verification problems much shorter since increment is a very popular function.

- A5. X[i:j]+¬Y[i:j]+1 = X[i:j]-Y[i:j] (for 2's complement) X[i:j]+¬Y[i:j]+0 = X[i:j]-Y[i:j] (for 1's complement)

- A6.  $X[i] \bullet (X[i+1] \land ... \land X[j]) \& X[i+1] \bullet (X[i+2] \land ... \land X[j]) \& ... \& \neg X[j]$  = X[i:j]+1

Next come the arithmetic relations. Only equal-to and greater-than are defined in detail because the others can be defined in terms of these two. Single bit comparisons for these are shown in A7 and A11, while bit by bit comparisons are provided in A8 and A12. The definitions in A9 and A13 show how individual comparator chips can be connected to form larger comparators.

- A7.  $\neg X[i] \bullet Y[i] \equiv X[i] = Y[i]$

- A8.  $(X[i]=Y[i])\wedge(X[i+1]=Y[i+1])\wedge...\wedge(X[j]=Y[j]) = X[i:j]=Y[i:j]$

- A9.  $(X[i:j]=Y[i:j]) \land (X[j+1:k]=Y[j+1:k]) = X[i:k]=Y[i:k]$  where  $i \le j \le k$

- A10.  $\neg (X[i:j]=Y[i:j]) = X[i:j] \neq Y[i:j]$

- All.  $X[i] \land \neg Y[i] \equiv X[i] \gt Y[i]$

- A12. (X[i])Y[i])v((X[i]=Y[i])AX[i+1])Y[i+1])v...v((X[i:j-1]=Y[i:j-1])AX[j])Y[j]) = X[i:j])Y[i:j]

- A13. (X[1:j]>Y[1:j])∨((X[1:j]=Y[1:j])∧X[j+1:k]>Y[j+1:k])

= X[1:k]>Y[1:k]

where 1≤j<k

A14. Y[i:j]>X[i:j] # X[i:j]<Y[i:j]

A15. ¬(X[i:j]>Y[i:j]) # X[i:j]≤Y[i:j]

A16. ¬(Y[i:j]>X[i:j]) # X[i:j]≥Y[i:j]

# 4.4 Miscellaneous transformations

There are several transformations that permit us to combine statements or expand one statement into several others. We will consider these to be "common-sense" axioms. The first axiom changes statements that do not have a conditional part into one where the conditions are always true. This is so they can be used with the other axioms in this section. It could be invoked automatically by the verifier's input parser. Axiom M2 lets us substitute the expression part of a combinational statement for the variable when that variable appears in other statements.

M1. A+Y; = /1/ A+Y; M2. /1/ A+Y; = (A = Y)

Axiom M3 allows two statements affecting the same variable to be combined, provided that their conditional expressions are identical except for one subexpression. This subexpression must be complemented in one statement and uncomplemented in the other. The next axiom, M4, shows how any variable or expression can be moved out of the register transfer part. This is done by creating two new statements, one showing what would happen if that variable were one and the other showing what would happen if it were zero. Axiom M5 allows us to divide statements having a logical OR in the conditional part into two separate statements, or to combine two statements with the same register transfer part. Similarly, M6 can be used to combine statements with the same conditional expression or to divide a statement involving vectors into two or more statements.

M3. /WA-X/ A+Y; /WA X/ A+Z; = /W/ A+(-XAY)v(XAZ); M4. /X/ A+...Y...; = /XA Y/ A+...1...;

/XA-Y/ A+...8...;

M5. /XvY/ A+Z;

/X/ A+Z;

/Y/ A+Z;

M6. /X/ A+Y; (note: A and Y must be the same /X/ B+Z; length, same for B and Z)

\*\*

/X/ A&B+Y&Z;

The next two transformations state that if a certain variable or subexpression appears in both the conditional expression and the register transfer expression, then it may be possible to determine what its value will be when that event occurs. Axiom M9 is similar except that another statement affected by the same conditions can control the value of a variable in the register transfer expression. Since there is the possibility of a critical race under some circumstances these should be used very carefully.

M7. /X/ A+...Y...;

and (X>Y)

| /X/ A+...1...;

M8. /X/ A+...Y...;

and (X>Y)

| /X/ A+...8...;

M9. /X/ A+...8...;

/Y/ B+Z;

and (X>Y)

| /X/ A+...Z...;

Axiom M10 can be used to introduce arbitrary expressions into the conditional part of a statement. This axiom will normally be used to convert statements into a form that can be used elsewhere. Finally, axiom M11 can be used when a variable appears ANDed with an expression that can control its value. It comes in two flavors, complemented and uncomplemented.

M18. /X/ A+Z; /XAY/ A+Z; M11. /X/ A+Y; XAA = XAY; XAA = XA-Y;

### 5. FEEDBACK

A major problem with describing components in the language used here is how to separate feedback from don't cares. Most component descriptions will not contain every possible combination of conditional expressions. Those undefined conditions can either be considered don't cares, in which the state of the device may change in some random manner, or feedback states in which the component's state variables do not change. Obviously it is necessary to differentiate between the two.

### 5.1 Implicit feedback

This subsection represents something of a digression because, after exploring the possibilities of making feedback implicit, the author decided to use explicit feedback for the proofs in this paper. Nevertheless, it may be reasonable to implement some of these ideas depending on the structure of the proof checker being used.

If feedback is to be implicit, then statements must be added to a circuit description to specify when a variable can enter a "don't care" state. This can become very messy when using a component having several undefined operations. In a microprocessor, for example, statements such as

```

/(OPCODE[0:7]="100)^tT1/ ACC[0:7]+ don't care;

/(OPCODE[0:7]="100)^tT1/ X[0:7]+ don't care;

/(OPCODE[0:7]="100)^tT1/ Y[0:7]+ don't care;

/(OPCODE[0:7]="100)^tT1/ PC[0:15]+ don't care;

```

will have to be added for each undefined opcode. Some of this might be circumvented by developing meta operators to cover large numbers of undefined operations.

On the other hand, using implicit feedback means that a component will not change state unless specifically changed by some statement. Statements of the form

/X/ A+A; /¬1X/ A+A;

are not needed in component descriptions. This is especially convenient when defining registers and memories. If one is writting data into a memory it will not be necessary to show that locations other than the one being addressed remain unchanged.

Since unspecified conditions imply that the system will not change state, statements with explicit feedback can be discarded from a logic description. Here are three transformations in which statements are completely eliminated:

| /X/ A←A; ≡ null    | (1) |

|--------------------|-----|

| /X∧A/ A+1; ≡ null  | (2) |

| /X∧¬A/ A+0: = null | (3) |

The first one permits us to remove a statement with explicit feedback because the language assumes that the variable will remain the same unless explicitly altered. The other two statement types can be removed because they don't do anything. In the second example the variable must already be one in order for it to be set to one. The third example is similar to the second and shows a case where a variable must be zero in order to be set to zero.

We can also derive some general rules for removing the variable being changed from the conditional expression. To do this we first need the following identities:

$$/X \wedge A / A + \theta$$

;  $\equiv /X / A + \theta$ ; (4)

$/X \wedge \neg A / A + 1$ ;  $\equiv /X / A + 1$ ; (5)

The left side of (4) says that if the expression is true and the variable is true, then the variable goes to zero. If the variable is already zero, then it will remain that way. Therefore, whenever the expression is true, the variable will be zero. Identity (5) uses similar reasoning. Using these transformations we can now derive the following general rules:

$$/X_{AA}/A_{+Y}; \equiv /X_{A-Y}/A_{+\theta};$$

(6)

$/X_{A-A}/A_{+Y}; \equiv /X_{AY}/A_{+1};$  (7)

$/X \wedge \neg A/A \leftarrow Y$ ;  $\equiv /X \wedge Y/A \leftarrow 1$ ;

The derivation for theorem (6) is shown below, and theorem (7) can be derived in exactly the same way with certain variables complemented.

> /XAA/ A-Y; given M4 /XAAAY/ A+1: /XAAA-Y/ A+8; other statement eliminated /XAAA-Y/ A-0; using (2) (4) /XA-Y/ A+8:

It is apparent that implicit feedback can provide some fairly compact component descriptions and that transformations (1-7) make it easy to simplify some statements. Unfortunately, when proving the correctness of a circuit it may be necessary to show that a given variable does not change state under certain circumstances. Using implicit feedback this would amount to checking all of the statements involving that variable to make sure none of them can cause a change. With many proof checkers, including the FOL system discussed in this paper, it is much easier to make feedback explicit and then verify statements like

/X/ A+A;

the same way other register transfers are verified. For this reason we will use explicit feedback for the remainder of this paper.

### 5.2 Axioms for explicit feedback

By using explicit feedback the problem of specifying don't care conditions is immediately eliminated. Any set of conditions not accounted for in a component description corresponds to a don't care state. On the other hand, some component descriptions may become somewhat longer since statements must be added to indicate conditions under which the state of a variable does not change.

The only major problem is in specifying registers and memories, in which large numbers of variables remain unchanged. To solve this we have the meta operator "\*", which is used to indicate all locations other than the addressed location. Using this, a typical random access memory might be defined as follows:

/WRITE/ MEMORY[0:7,ADDR[0:11]]←DATA[0:7];

/¬WRITE/ MEMORY[0:7,ADDR[0:11]]←MEMORY[0:7,ADDR[0:11]];

MEMORY[0:7,\*ADDR[0:11]]←MEMORY[0:7,\*ADDR[0:11]];

This would mean that the unaddressed locations represent feedback conditions whether the memory is being read or written. To completely formalize the notion of the "\*" operator we need a few more axioms. Axioms F1 and F2 permit all of the unaddressed bits to be set to the same expression, while F3 and F4 have the unaddressed bits remaining at their current value.

- F2. /X/ A[s,\*Y[i:j]]+Z; = /X^(Y[i:j]\*n)/ A[s,n]+Z;

- F3. /X/ A[\*Y[1:j],s]+A[\*Y[1:j],s];

#

/X^(Y[1:j]\*n)/ A[n,s]+A[n,s];

- F4. /X/ A[s,\*Y[i:j]]+A[s,\*Y[i:j]];

=

/X^(Y[i:j]\*n)/ A[s,n]+A[s,n];

Admittedly the "\*" operator is a kluge designed to solve the problem of defining memories with explicit feedback. It would be very undesirable to actually expand a memory into several thousand statements using the above axioms. They can, however, be set up in a proof checker so that the user can ask if a given set of locations change or remain the same under specific circumstances. The "\*" operator should only be used in context shown above. It is unclear what we would do with expressions containing several "\*" terms combined with logic operators.

### 6. TRANSITION ALGEBRA

In this section we will develop some identities that permit us to study the effects of signal transitions as they travel thru a circuit. The concept of a transition algebra was first proposed by Talantsev [58] in 1958. Since then, these constructs have been applied to the problem of designing circuits using edge triggered flip-flops [53,54,57].

#### 6.1 Basic axioms

Figure 6.1 illustrates the nature of the transition operators. The expression "tX" refers to that incredibly short period of time during which variable X changes from 0 to 1, and is best thought of as a pulse. The fact that constants do not undergo transitions is illustrated in C1. Axiom C2 tells us that a signal cannot be changing from 0 to 1 and from 1 to 0 at the same instant. It will simplify things a great deal if we assume that two variables cannot change at exactly the same time. This assumption is reflected in axioms C3 and C4. If a transition is thought of as a pulse, going from 0 to 1 and back to 0, then it is possible to think of that pulse as having two transitions associated with it. This permits us to use axiom C5 to reduce multiple transition operators to just one (the innermost).

- C1. †0 = 0 †1 = 0 #8 = 8 #1 = 0

- C2. TXAIX E 8

- C3. †X^†Y = 0 †X^†Y = 0 ‡X^†Y = 0 ‡X^‡Y = 9

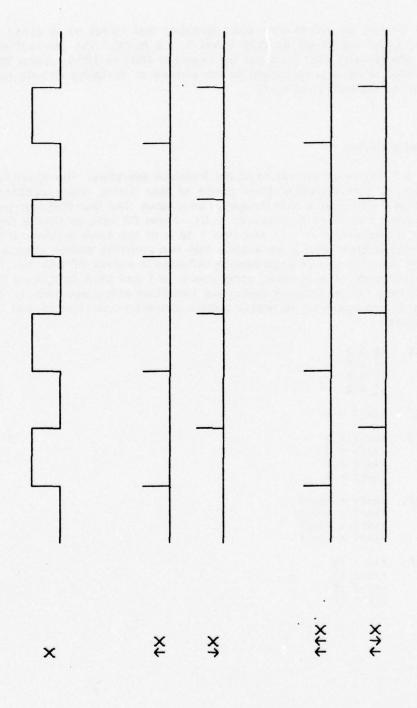

FIGURE 6.1 TRANSITION UARIABLES

# 6.2 Mathematical basis of transition algebra

This subsection contains the derivations that permit us to develop transition functions for switching circuits. To begin with, any variable in a logic function can be factored out by using Shannon's expansion theorem (very similar to M4). The resulting expression uses two new functions. They are the same as the original function except that the factored out variable is set to 1 in one of them and 0 in the other.

Whenever these two new functions can have complementary values (due to the values of other variables), a transition in the factored out variable will cause a transition in the original function. The direction of this transition depends on which of the new functions has the value of 0, which has the value 1, and the direction of the transition in the variable. The possible ways of obtaining positive or negative transitions are shown below.

$$tf = f_{i1}\overline{f}_{i0}tx_i \vee \overline{f}_{i1}f_{i0}tx_i$$

(2)

$$+f = f_{11}\overline{f}_{10}+x_1 \vee \overline{f}_{11}f_{10}+x_1 \qquad (3)$$

To find all possible transitions for a given function it is necessary to develop expressions like (2) and (3) for every variable in the original function, and OR the results. In the equations below, the Sigma should be interpreted as a logical OR.

$$f(x_1, x_2, ..., x_n) = \sum_{i=1}^{n} f_{i1} \overline{f}_{i0} + x_i \vee \overline{f}_{i1} f_{i0} + x_i$$

(4)

$$4f(x_1, x_2, ..., x_n) = \sum_{i=1}^{n} f_{i1}\overline{f}_{i8}4x_i \vee \overline{f}_{i1}f_{i8}4x_i$$

(5)

# 6.3 Transitions thru combinational circuits

Using (4) and (5) above we could derive transition functions for any combinational circuit. However, all we really need are the transition functions for AND, OR, and INVERT since other circuits can be defined in terms of these three. The transformations for AND and OR could be stated for arbitrary numbers of variables, but the same result will be obtained thru repeated application of the two variable versions. Remember that X and Y can be any expression.

- C6. +-X = +X

- C7.  $t(X_{\Lambda}Y) \equiv (tX_{\Lambda}Y) \vee (X_{\Lambda}tY)$  $+(X_{\Lambda}Y) \equiv (+X_{\Lambda}Y) \vee (X_{\Lambda}+Y)$

- C8.  $\uparrow(X\vee Y) \equiv (\uparrow X \land \neg Y) \lor (\neg X \land \uparrow Y)$  $\downarrow(X\vee Y) \equiv (\downarrow X \land \neg Y) \lor (\neg X \land \downarrow Y)$

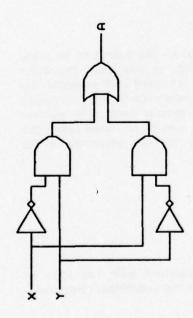

To show how the above transformations are applied to more complex circuits we have two examples. The circuit diagrams are shown in Figure 6.2. The example in Figure 6.2a is an exclusive-OR function.

Notice how terms having the same identifier as a transition variable and a non-transition variable, such as " $\dagger X_A Y_A \neg X$ ", were eliminated by using T8. Unfortunately, this does not always happen. Watch what happens when we derive the transition function for the circuit in Figure 6.2b.

```

t(XAY v ¬XAZ) =

t(XAY)A¬(¬XAZ) v t(¬XAZ)A¬(XAY) =

(tXAY v XAtY)A(X v ¬Z) v ($XAZ v ¬XAtZ)A(¬X v ¬Y) =

(tXAYAX)v(tXAYA¬Z)v(XAtY)v(XAtYA¬Z)v

($XAZA¬X)v($XAZA¬Y)v(¬XAtZ)v(¬XAtZA¬Y) =

(tXAXAY)v(tXAYA¬Z)v(XAtY)v($XA¬XAZ)v($XA¬YAZ)v(¬XAtZ)

```

0 /x/ A+Y; 1A = (x+fY) ~(¬A^Y^†X)

D) / TX/ A+Y; TA = ( -A-Y-+X)

FIGURE 6.2 TRANSITION EXAMPLES

Elements such as "tXAX..." indicate the possibility of a hazard. It can be shown (Appendix C) that any circuit having a hazard will have this sort of expression. The reverse is not true, and terms of this type are still present when the hazards have been corrected by consensus gates.

Another problem of this sort arises when trying to expand a non-transition thru a combinational circuit. The resulting terms seem to indicate the possibility of a hazard in a non-transition. We could add some axioms to make these extraneous terms vanish but it would no longer be true that ¬(¬†X) is equivalent to †X.

$$\neg \uparrow (X \land Y) = \neg (\uparrow X \land Y \lor X \land \uparrow Y) = (\neg \uparrow X \lor \neg Y) \land (\neg X \lor \neg Y) \lor (\neg \uparrow X \land \neg Y) \lor (\neg \uparrow Y \land \neg Y)$$

### 6.4 Transitions thru sequential circuits

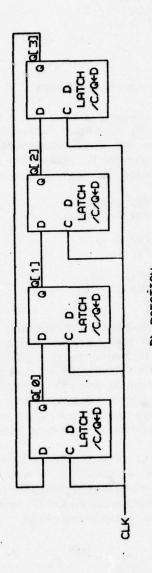

The last transformation in this group demonstrates how to obtain a transition at the output of a sequential component. Axiom C9 is easily explained if we think of a latch like the one in Figure 6.2c, in which the output follows the input as long as the clock is true. A transition will develop on the output of the latch if the data input undergoes a transition while the clock input is held true; Another way to get a transition is for the clock input to switch to true while the data inputs are set to switch the latch to a new state.

This becomes even simpler if we want a transition on the output of an edge triggered component like the flip-flop in Figure 6.2d. In this case the input changing while the clock is true does not apply, so we need only consider the second part of the expression: the clock going true when the inputs can cause an output transition. It is possible to handle this special case with another transformation similar to C9, but the desired results can be obtained using the identities we already have. This particular problem was the major reason for including C5 in the list of axioms.

/†X/

$$A\leftarrow Y$$

; given

†A = (†X $\wedge$ †Y) $\vee$ (††X $\wedge$ Y $\wedge$ ¬A) = C9

(†X $\wedge$ Y $\wedge$ ¬A) C3,C5

It should be noted that this is completely consistent with the idea of expressing combinational circuits as statements where the conditional expression is always true.

| /1/ A←Y;                                                | given |  |

|---------------------------------------------------------|-------|--|

| $tA = (1 \wedge tY) \vee (t1 \wedge Y \wedge \neg A) =$ | C9    |  |

| 17                                                      | Cl    |  |

Other problems can develop if the transition variable being expanded is controlled by several statements. Generally speaking, the correct approach would be to apply the transition identities to each of the statements and then OR the results together. This will work unless some of the statements are contradictory, which is an error anyway. Contradictory statements are discussed in the section on error conditions.

# 6.5 Flip-flop design and modelling

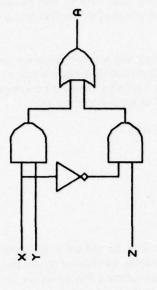

The transformations presented thus far are not sufficient to prove the correctness of some flip-flop designs. Simple latches such as those in Figure 6.3a and Figure 6.3b are easily verified. On the other hand, edge triggered devices like the ones in Figure 6.3c and Figure 6.3d cannot be verified using these methods because they depend on hazards being carefully adjusted to work correctly. The type-D flip-flop shown in Figure 6.3c, for example, will work correctly only if the delay thru the first latch is longer than the delay thru the inverter connecting the two clock inputs. The manufacturer will bias these delays to insure correct operation. Additionally, many circuits use capacitance instead of feedback to store data. For these reasons we will not attempt to verify the correctness of flip-flop designs. If a given flip-flop circuit is known to work correctly it can be added to the verification scheme as an axiom.

It is important that components be modelled carefully if the proof of correctness is to be valid. Some JK master-slave flip-flops, like the one drawn in Figure 6.3d, have the nasty habit of ones-catching [55,56]. This means that a short pulse on the J or K input while the clock is high could set or clear the master latch. This erroneous data would then be transferred to the slave latch during the clock transition. Many JK flip-flops are designed to eliminate ones-catching. At any rate, when using a JK flip-flop which does exhibit this characteristic it should be modelled as two sequential devices. By specifying the master part as a latch and the slave part as an edge triggered device the overall behavior can be properly described.

/CAJA-Q/ X+1; /CAKA Q/ X+8; / 4C/ Q+X; /-+C/ Q+Q;

RO SET ARESET LATCH

B) TYPE-D LATCH

C) D MASTER SLAVE FLIP-FLOP .

D) JK MASTER SLAVE FLIP-FLOP

FIGURE 6.3 FLIP-FLOP DESIGNS

#### 7. ERROR CONDITIONS

In this section we shall explore a variety of error conditions, such as races, hazards, and oscillations, that can be detected in the hardware descriptions. It is not completely clear how this fits in with the idea of comparing two descriptions of the same device since it is possible to include error conditions in higher level system specifications. If the user's system description includes a hazard, for example, then the actual circuit may need to have that hazard for the verifier to prove its correctness. Because of this conflict this section will not contain specific rules for what to do when an error is encountered. It is mainly intended to show under what conditions an error can exist, and why a verifier may have trouble proving the correctness of some circuits.

# 7.1 Race and hazard jargon

Now we come to the question of timing. To show correctness it is not really necessary to know specific delay times or to make any assumptions on how fast the device will go. Usually a device built from ECL will go faster than one built from MOS, but both can be logically correct. Nevertheless, it is possible to develop ways to detect timing anomalies such as races and hazards on an algebraic level without introducing specific delays.

Static and dynamic hazards [61,62,65,66,68,69,70,73,74,75] are logical conditions under which combinational circuits can produce spurious transitions. The actual transitions, created by a logic hazard and specific component delays, are called hazard pulses. Some authors use the term static-1 hazard to refer to a momentary 0 in an output that will normally be 1, and static-0 hazard to refer to a momentary 1 result. A typical example of a static-1 hazard was presented in the section on transition algebra. The term transient hazard is sometimes used to refer to a hazard that will not do any damage, while a steady state hazard can affect the final value of a state variable. A dynamic hazard is a momentary 0 and a momentary 1 occuring on an output as it changes from one state to the other. In other words, a dynamic hazard causes three transitions where only one was expected.

Some papers [59,60,63] have attacked the problem of detecting hazard conditions for specific multiple input changes. Such hazards are often referred to as M-hazards. These hazards are further divided into function hazards and logic hazards. A function hazard is inherent in the definition of the logic, while a logic hazard may exist in a particular implementation of a circuit which could otherwise be constructed without hazards. Although the problem of multiple input hazards will not be addressed in this paper, the concepts of function and logic hazards are closely related to the problem of comparing hazardous system specifications with their implementation.

An essential hazard [61,65,67,69,71,74,75] is a unique set of conditions in which the transition of an input variable causes a transition in a state variable, and the comparative delays in these transitions can determine the output of still another state variable. By Unger's definition [74] a circuit contains an essential hazard if the result after one input transition is different than the result after three input transitions. Essential hazards are not necessarily bad, and are required in counting circuits. The circuit delays must be adjusted to make sure the desired effect is achieved. A similar condition is a race [64,67,69,74,75], except that a race involves transitions of two state variables. A critical race is a race that can affect the final state of the circuit (like a steady state hazard).

Race and hazard terminology will be used somewhat differently in this paper as a matter of convenience. Since static and dynamic hazards can be thought of as a "race" between a variable and its complement (in a combinational circuit), and an essential hazard can be thought of as a "race" between an input variable and a state variable, all of these phenomena will often be referred to as races. This eliminates the problem of having to determine which variables are state variables when one of these problems is detected.

#### 7.2 Race and hazard detection

For purposes of hardware verification we are only interested in races that can cause a permanent change in the state of the system and hazard pulses on the outputs of a device that can cause a malfunction when the circuit is used in conjunction with other equipment. Output hazards tend to take care of themselves. If the output is from state variable an output hazard will appear as a race that can affect its final state. If the output is from a combinational circuit the hazard will usually show up in the boolean expression for that circuit.

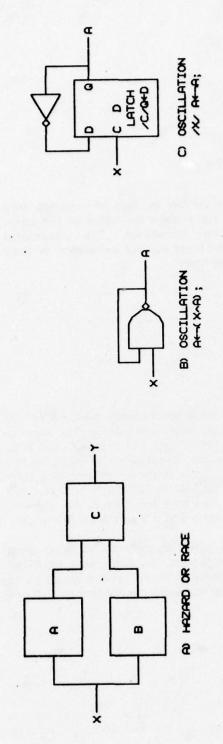

Figure 7.1a is a block diagram of a race condition. A transition in variable X passes thru circuits A and B, which might be combinational, sequential, or just wires. If the final state of circuit C can depend on whether path A is faster than path B, then we have race condition. After using the transition theorems on the circuit the statements describing circuit C will be in terms of the input variable X and the state variables (if any) of A and B. Races will then be apparent in one of the following forms:

1. A static-8 hazard in a conditional expression.

/...static-0 hazard.../ A+X;

Any static or dynamic hazard in a transition variable.

/...+(static hazard).../ A+X; /...+(static hazard).../ A+X; /...+(dynamic hazard).../ A+X; /...+(dynamic hazard).../ A+X;  X or ¬X ANDed with +X or +X in the conditional expression.

```

/...X^tX.../ A+Y;

/...X^tX.../ A+Y;

/...X^tX.../ A+Y;

/...X^tX.../ A+Y;

```

X, ¬X, †X or ↓X in the conditional expression with X or ¬X in the register transfer part.

```

/...X.../ A+...X..;

/...-X.../ A+...X..;

/...../ A+...X..;

/..../ A+...X..;

/..../ A+...X..;

/..../ A+...-X..;

/..../ A+...-X..;

/..../ A+...-X..;

/..../ A+...-X..;

```

Some of these conditions may not mean disaster. A dynamic hazard in a conditional expression does not matter if we are merely gating some data into a register. On the other hand, if something else can happen on the opposite transition, or the register transfer part involves counting or shifting, then it can be very important.

Although we have freely indicated where static and dynamic hazards can cause problems, we have not said anything about how to detect them. Static hazards are well understood, but dynamic hazards are extremely difficult to detect. There are, however, some fairly simple conditions under which static and dynamic hazards cannot exist [65,66,68,69,70,75]. This is not to say that they necessarily will exist if these conditions are not met, but these methods are easy to implement and will probably be adequate for a verification program. A very simple rule would be to say that hazards cannot exist unless a variable appears both complemented and uncomplemented in the same expression.

It should be noted that static hazards in transition expressions will become apparent when the expression is expanded. This will generate two subexpressions of the form "†XAX" and "‡XA¬X" (or "‡XAX" and "†XA¬X"). Adding a consensus gate will still produce two subexpressions of this form, but they will be in terms of two different variables such as "†YA¬Y" and "†ZA¬Z". It may be possible to develop some specific rules based on this, but for the time being it is probably easier to expand the minimal transition expression and then look for a consensus gate when a possible hazard is detected. Some results of expanding transition expressions containing static hazards are shown in Appendix C.

When a race is found a verification program may be able to indicate which portion of the circuit must be faster to insure correct operation. Another

approach would be to have the user indicate which branch is faster and let the verifier determine if the circuit is correct under that assumption. Eventually it may be possible to include statistical information on component delays so that hardware verifier can determine the probability of a race or hazard.

### 7.3 Oscillation

Another timing anomaly, oscillation, can also be detected thru careful examination of the circuit description. Oscillation can occur by a variable being repeatedly complemented or by a continuous bit rotation. Figures 7.1b and 7.1c illustrate circuits where variable Q will be complemented as long as X is true. The only difference between the gate circuit and the latch circuit is that the latch will remain in some random state after X goes low. Figure 7.1d shows a rotate circuit that will keep rotating as long as the CLK signal is true.

Although the illustrations show very simple circuits, an oscillation can occur thru arbitrary amounts of combinational and sequential logic. The only requirement is that a variable is repeatedly complemented, or that two or more state variables are exchanged or rotated continuously. In the latter case the variables can be complemented any number of times during the rotation. Here is an example of oscillation involving a few statements:

/X/ A←B; /Y/ B←C∧D; /Z/ C←¬A;

In this example, oscillation can occur only if X,Y,Z, and D are all true at the same time. A simple algorithm for detecting oscillation in a given variable would be to determine the conditions under which each of the variables in the register transfer expression are transferred into that variable. Then do the same thing for each of these variables, and so on until the original variable or its complement is detected, or until the process terminates. An oscillation will be indicated anytime a variable can be continuously complemented, or when a variable is rotated (complemented or not) thru at least one other state variable.

This algorithm may not be practical in that it can grow incredibly large trees and consume lots of computer time, but it is hoped that most branches will be pruned very quickly. Anytime the process reaches a variable that is controlled by a transition it can eliminate that variable as a possible oscillation path. Branches can also be eliminated when they require conditions that contradict other conditions farther up the tree. Below are two variations on the previous example in which an oscillation will not occur. In the first we have replaced Y with \$Y\$, and in the second oscillation is prevented because X and ¬X would both have to be true at the same time.

/X/ A+B; /+Y/ B+C^D; /Z/ C+¬A; /X/ A+B; /¬X/ B+C^D; /Z/ C+¬A;

## 7.4 Other error conditions

A more obvious problem for a hardware verifier is that of contradictory statements. By comparing statements which can change the value of the same variable one of three relationships will be discovered. The conditional expressions can be the same, they can be different but not exclusive, or they can be exclusive. An example of each is shown below.

- 1. /X/ A←Y; /X/ A←Z;

- 2. /W/ A+Y; /X/ A+Z;

- 3. /V∧X/ A+Y; /W∧¬X/ A+Z;

The first example is undoubtedly an error since the variable must be set to the results of two different expressions for the same conditions. The second case will be incorrect only if the circuit using this device can cause W and X to the true at the same time. This sort of problem can be detected by verifying the still larger circuit in which this device is used. If this larger circuit includes such things as an operator's console then there is no way to tell if the operator will push the wrong two buttons at the same time. The third condition is not problem, and can be reduced to a combinational circuit (using M3) if V and W are identical.

Many types of integrated circuit devices permit outputs to be connected together in a wired-AND or a wired-OR arrangement. An easy way to avoid getting into problems with contradictory statements on these circuits would be to include the appropriate AND or OR function in the hardware description as if there were additional gates in the circuit.

. D) ROTATION /CLK/G[0:3] + G[3] & G[0:2];

FIGURE 7.1 RACES AND OSCILLATIONS

### 8. MICROPROGAM VERIFICATION

This section on microprogram verification has been included for several reasons. To begin with, there are some interesting similarities between the problems of microcode verification and hardware verification. A hardware verification system should be able to handle descriptions of microprogrammed devices. Also, it should be possible to interface circuit descriptions in a hardware verification language to existing microprogram verifiers to determine the correctness of microprograms for that particular device.

## 8.1 Microprogram vs. program verification

Although work on program verification has been going on for about ten years, the specific problem of microprogram verification has only been discussed fairly recently. Much of this work was done at IBM using a hypothetical computer called the S-machine [77,78,81,82,83]. The S-machine is a very simple stack machine and problems involving the control structure and timing constraints were not considered.

The distinction between microprogram verification and program verification is often very hazy. One major difference is that microprogram verification concerns a program for a precisely defined piece of hardware instead of using generalized algebraic language. Details like word length and register structure are very important in microprogram verification. Additionally, each microprogram instruction usually specifies several internal operations that may happen simultaneously.

Microprograms are usually loop free or have very few loops. This makes the verification problem much simpler than for programs in general. The problem of verifying loopfree microcode is discussed in [85]. One other observation is that the desired operation of a microprogram is usually described as an algorithm rather than as a result. In program verification, for example, a sorting program might be specified by saying that it takes an array of numbers and returns them in numerical order. A microprogram verification problem, on the other hand, will usually involve showing that a specific algorithm is followed by a detailed program. For this reason most microprogram verifiers are based on proving that each statement in the algorithm description is satisfied by one or more microinstructions. For more background on microprogram verification techniques see [80,82].

Of particular interest is the STRUM (STRUctured Microprogramming language) system developed at UCLA[84]. This system uses a very popular procedural register transfer language, ISP (Instruction Set Processor), for describing the hardware to be microprogrammed. It also uses generalized program verification techniques rather than methods specifically tailored to microprogram problems. This means that loops cause fewer problems with STRUM than they do with some other microprogram verifiers.

# 8.2 Hardware verification for microcoded devices

Since the hardware verification language described here is non-procedural it is also loopfree. Microcoded devices can be specified in several ways. To define a circuit that fetches and executes instructions pointed to by a given register (the program counter) is fairly straightforward. Thus it is simple to prove that the hardware does the correct thing for an unspecified microprogram.