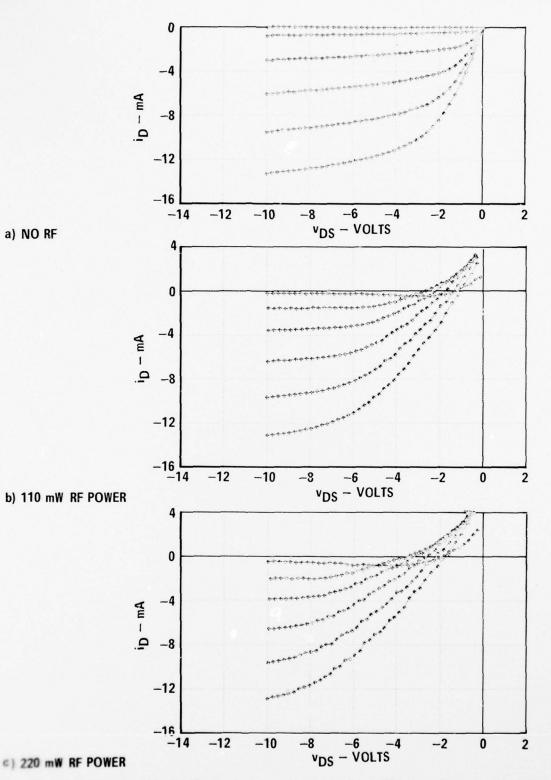

| UNCLA | SSIFIED |  |  | NSWC/D                                                                                                                                    | L-TR-36 |   | 21-76-0 | NL |  |

|-------|---------|--|--|-------------------------------------------------------------------------------------------------------------------------------------------|---------|---|---------|----|--|

|       |         |  |  |                                                                                                                                           |         |   |         |    |  |

|       |         |  |  | $\left\  \begin{bmatrix} 1 & 1 & 1 \\ \frac{1}{2} & 0 & \frac{1}{2} \\ \frac{1}{2} & 0 & \frac{1}{2} \\ 0 & 0 \end{bmatrix} \right\ _{t}$ |         |   |         |    |  |

|       |         |  |  |                                                                                                                                           |         | E |         |    |  |

|       | 1       |  |  |                                                                                                                                           |         |   |         |    |  |

|       |         |  |  |                                                                                                                                           |         |   |         |    |  |

|       |         |  |  |                                                                                                                                           |         |   |         |    |  |

COPY NO. 19

# INTEGRATED CIRCUIT ELECTROMAGNETIC SUSCEPTIBILITY INVESTIGATION PHASE III

3 JUNE 1977

JU po30 DI9 REPORT MDC E1667

# **TECHNICAL REPORT NO. 2**

APPROVED FOR PUBLIC RELEASE: DISTRIBUTION UNLIMITED

SUBMITTED TO THE CONTRACTING OFFICER, U.S. NAVAL SURFACE WEAPONS CENTER – DAHLGREN LABORATORY, DAHLGREN, VIRGINIA, 22448 UNDER CONTRACT NO. N60921-76-C-A030 🗸

MCDONNELL DOUGLAS ASTRONAUTICS COMPANY . EAST

Saint Louis, Missouri 63166 (314) 232-0232

MCDONNELL DOUG CORPORATION

# PREFACE

The work reported in this document was performed under Contract No. N60921-76-C-A030 for the U. S. Naval Surface Weapons Center, Dahlgren Laboratory Dahlgren, Virginia 22448. The McDonnell Douglas Astronautics Company personnel involved were:

J. M. Roe, STUDY MANAGER

J. R. Chott

C. R. Chubb

C. N. Kohlberg

C. E. Larson

R. D. Von Rohr

MCDONNELL DOUGLAS ASTRONAUTICS COMPANY . EAST

ii

I

I

+

[]

[]

[]

1

I

### TABLE OF CONTENTS

|    | Title                                                                                                                                                                  | Page                                                                                                           |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| ۱. | INTRODUCTION AND SUMMARY                                                                                                                                               | 1                                                                                                              |

| 2. | IC SUSCEPTIBILITY HANDBOOK REVISION                                                                                                                                    | 3                                                                                                              |

|    | <ul> <li>2.1 System Considerations</li></ul>                                                                                                                           | 3<br>6<br>12<br>12                                                                                             |

| 3. | INTERFERENCE EFFECTS                                                                                                                                                   | 15                                                                                                             |

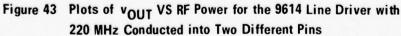

|    | <ul> <li>3.1 Large Signal Rectification in PN Junctions</li></ul>                                                                                                      | 15<br>16<br>25<br>25<br>28<br>44<br>48<br>48<br>57<br>57<br>58<br>66<br>71<br>74<br>78<br>78<br>78<br>89<br>89 |

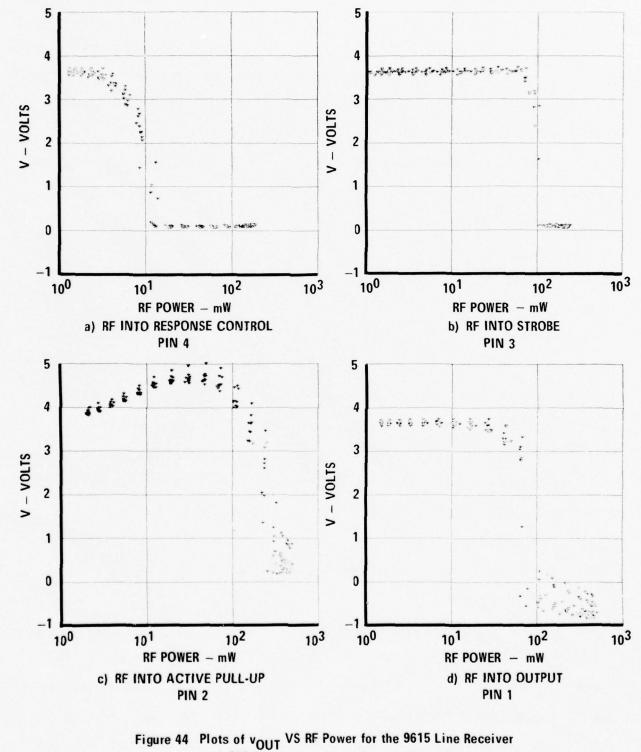

| 4. | DAMAGE EFFECTS                                                                                                                                                         | 97                                                                                                             |

|    | <ul> <li>4.1 Damage Mechanisms.</li> <li>4.1.1 Bond Wire Damage Model.</li> <li>4.1.2 Junction and Metallization Damage Models.</li> <li>4.2 Damage Summary</li> </ul> | 98<br>102<br>104<br>108                                                                                        |

|    | III         III         III         III         III         III         III         III         III                                                                    |                                                                                                                |

-----

# TABLE OF CONTENTS (Continued)

| 5.   | SUSC  | EPTIBILIT | Y REI | DUCTI | ON · | ٠    | • • |     | ·  | • • | • • | ·   | · | • •  | •   | • • | •  | • | • | • | · | • | • | • | 113 |

|------|-------|-----------|-------|-------|------|------|-----|-----|----|-----|-----|-----|---|------|-----|-----|----|---|---|---|---|---|---|---|-----|

|      | 5.1   | Practica  |       |       |      |      |     |     |    |     |     |     |   |      |     |     |    |   |   |   |   |   |   |   |     |

|      | 5 2   | Reduce S  | uscep | otibi | lity | •••• | • • | • • | •  | •   | • • | ÷   | ÷ | : :  | •.  | • • | •  | • | • | • | • | • |   | • | 113 |

|      | 5.2   | Present   | Limii | tatio | ns o | t tr | ne  | Los | sy | Ma  | ter | '1a |   | lecr | nnı | que | 5. | • | • | • | • | • | • | • | 114 |

| REFE | RENCE | s         | •••   |       | • •  | •    | • • | • • | ·  |     | •   | ·   | · |      |     |     | •  | • | • | • | • | • | • | • | 115 |

| DIST | RIBUT | ION LIST  |       |       |      |      |     |     |    |     |     |     |   |      |     |     |    |   |   |   |   |   |   |   | 117 |

| LIS | t of  | Page  | S |

|-----|-------|-------|---|

|     | Tit   |       |   |

|     |       | and   |   |

| 1 6 | iroug | gh 12 | 4 |

# 1. INTRODUCTION AND SUMMARY

The work described herein was performed by McDonnell Douglas Astronautics Company - East (MDAC-EAST) under contract to the U. S. Naval Surface Weapons Center/Dahlgren Laboratory (NSWC/DL). It is part of an ongoing program seeking to understand high power microwave effects in a cost effective manner. This Integrated Circuit Electromagnetic Susceptibility (ICES) contract is concerned with microwave effects in semiconductor integrated circuits (ICs). This report covers the work performed in the second of three increments which together form the third and last phase of this program. This effort is directed toward characterizing IC susceptibilities to microwave energy and identifying possible means of reducing these susceptibilities.

The primary output of the ICES effort is an ICES Susceptibility Handbook which provides IC susceptibility information to system designers. This information consists of susceptibility models and data. The handbook also contains a complete approach to the Electromagnetic Vulnerability (EMV) problem and a detailed example of using the IC information to determine the system shielding requirements. During the second increment, Draft 1 of the ICES Handbook<sup>1</sup>, which was issued after increment 1, was reviewed by potential users. Part of this review occurred at a seminar held in October 1976. In response to the comments received, the ICES Handbook has been revised and Draft 2 is being issued in parallel with this report. This revision includes new models and updated test data from the work performed during the second increment. The review cycle for Draft 2 of the ICES Handbook<sup>2</sup> will include an expanded mailing list, and all those who have shown interest in the IC susceptibility problem will receive a copy. Approximately 500 names are included in the mailing list. Another seminar is planned for the fall of 1977 for further review and comment of Draft 2.

MCDONNELL DOUGLAS ASTRONAUTICS COMPANY . EAST

1

During the second increment the bipolar junction transistor RF effects model was refined. This model is an Ebers-Moll model modified to include the RF effects observed during a large amount of RF testing of diodes and transistors. This model has been used with SPICE (Simulation Program with Integrated Circuit Emphasis) as an example of how RF effects in ICs can be modeled using a standard circuit analysis program.

The study of damage susceptibility was completed in the second increment. A large testing program was performed to study each damage mechanism - junction failure, metallization failure, and bond wire failure. Also a general worst case model was generated for each mechanism based on heat flow from the failure site.

The feasibility of various susceptibility reduction techniques was reviewed during this increment. The value of device screening and circuit design techniques require further study as the modeling effort continues. However the use of lossy material, such as ferrite, as a susceptibility reduction technique, appears to be impractical at this time.

2

#### 2. IC SUSCEPTIBILITY HANDBOOK REVISION

During increment one, Draft 1 of the ICES Handbook was designed. It was issued to potential users for their comments, criticisms, and suggestions as to content and format. During increment two, the users responded in a generally favorable manner to Draft 1 with specific comments and suggestions. Their responses have been incorporated into Draft 2 wherever possible. Also the modeling and test data have been updated to include the work performed during the second increment.

2.1 <u>System Considerations</u> - From initial comments it was obvious that a detailed example for using the IC Susceptibility Handbook was needed. Therefore, the following example showing how to determine the system shielding requirements with a given EM environment was created and presented at Seminar I.

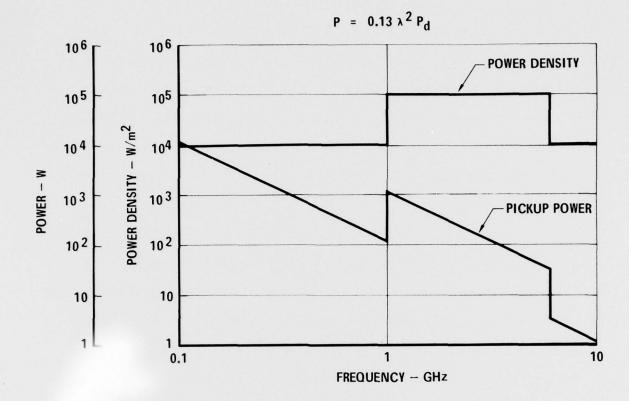

Electromagnetic environment levels (in terms of power density,  $P_d$ ) are determined according to the stockpile to end of service life cycle of the system of interest, and a table or graph of required test levels is usually included in contractual documents. A possible environment level for this example is shown in figure 1.

An unshielded wire or cable will pick up various amounts of power from such environments according to such variables as frequency, aspect angle, terminating impedance, etc. One method for determining the maximum amount an unshielded wire will pick up is given by the formula:

$$P = 0.13 \lambda^2 P_d$$

where  $\lambda$  is the wavelength of interest. From this formula, the maximum amount of power expected on system wiring in the given environment can be calculated. This result is also illustrated in figure 1.

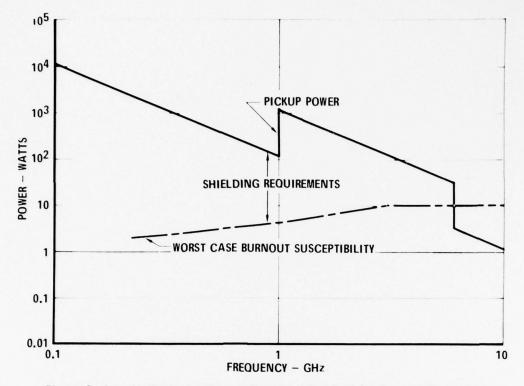

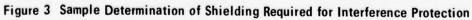

Figures 2 and 3 repeat the maximum power levels expected but also add component information which is available in the handbook. In particular, figure 2 shows the

REPORT MDC E1667 3 JUNE 1977

Figure 1 Sample Calculation of Pickup Power From Given Power Density

worst case burnout levels ever observed for IC burnout. It is clear that, <u>in the</u> <u>absence of any shielding</u>, burnout is quite possible across a large frequency range, and some sort of protection in the form of shielding (either enclosure or cable, or both) or filtering is required to guarantee that component burnout will not occur. The amount of protection required is indicated by the separation of the two curves on this logarithmic plot. Figure 3 shows similar results for interference effects.

The degree of overall system protection required for this example is summarized in figure 4. Many options are available to meet such requirements including: splitting the shielding requirements between enclosures and cables, filtering, isolation of particularly sensitive circuits, etc.

5

REPORT MDC E1667 3 JUNE 1977

Figure 4 Sample Requirements for System Shielding

2.2 <u>Component Susceptibility Information Requirements</u> - In the susceptibility information section of the revised handbook there have been several major changes while some things remained the same. In Draft I, use of a worst case approach to susceptibility was proposed. Potential users who were questioned concerning this approach approved it and so it will remain the cornerstone of the susceptibility information, both for the modeling and test data. Some of the items that have undergone changes in Draft 2 are: (1) the individual graphs showing the data spread by frequency have been removed; (2) all graphs and models have been changed from absorbed RF power to estimates of minimum RF power; (3) the susceptibility criteria for digital devices have been changed and (4) the composite graphs for digital devices with high and low output states have been combined into one graph.

6

The individual graphs which showed the data spread for each frequency have been removed in answer to several comments that they were confusing and unnecessary. Originally these graphs were provided to give the designers some idea of the best case susceptibility for the ICs but they were interested in the worst case susceptibility. Since the worst case susceptibility levels were shown on the composite graphs, the composite graphs were retained and the individual graphs deleted.

For the worst case approach adopted in the handbook, the quantity of interest is the minimum amount of power (defined as power available from the source) which will produce the unacceptable component response. The estimates of minimum power contained in the handbook are derived from measurements on statistical samples of ICs and on theoretical considerations based on physical models. The data measured with the measurement scheme described in Chapter 4 of the handbook must have the dependence on the measurement technique removed because it is recognized that the IC susceptibility level may depend upon the driving impedance of the microwave source (whether a laboratory source or a cable or wire exposed to a microwave field). One useful approach is to determine the amount of power dissipated within the package since it can be postulated that reflection losses and external dissipation losses could be minimized under suitable tuning conditions. Likewise, the failure models are derived in terms of power dissipated in the failure site. The use of absorbed power as an estimate of minimum power is conservative since it is probably not possible to match the driving source to a nonlinear load such as a semiconductor junction; and it is likely that losses in diverse parts of the IC chip are inevitable. To minimize the very real danger of producing over-cautious estimates, the degree of conservatism in the handbook predictions has been estimated and these estimates are made clear to the reader and user of the handbook.

The format of the composite graphs also brought comment from designers. It was suggested that whichever output state is susceptible for digital devices is irre-

MCDONNELL DOUGLAS ASTRONAUTICS COMPANY - EAST

7

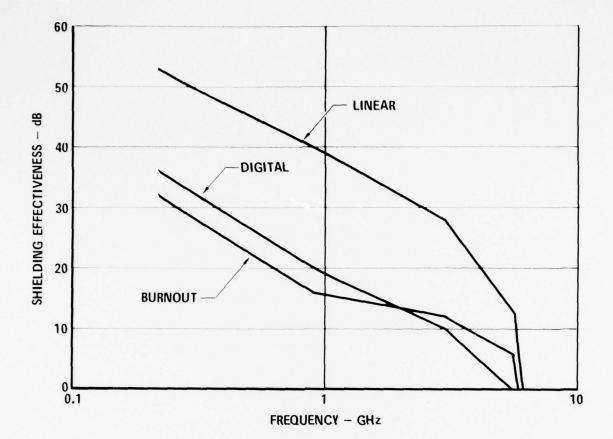

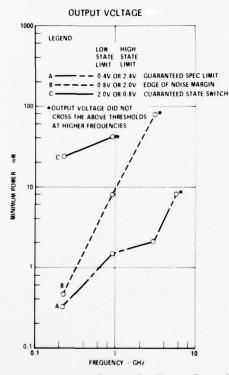

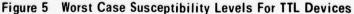

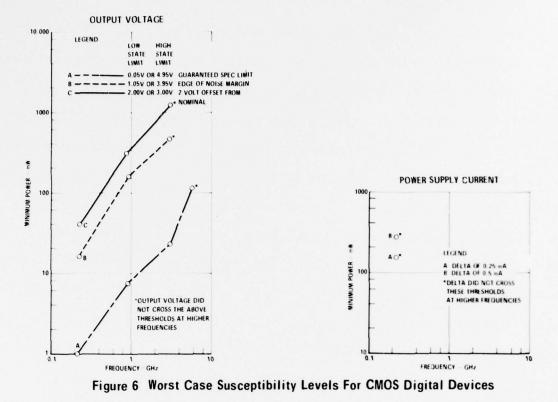

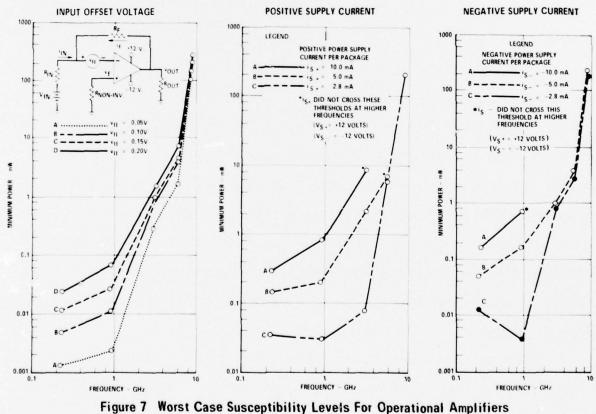

levant, anu only the worst case susceptibility is important. Therefore the composite graph for TTL devices and the composite graph for CMOS digital devices include both the high and low output states. Draft 1 had separate composite graphs for each output state, but Draft 2 has one graph which includes both states. The susceptibility criteria for these two-state composites have also been changed to reflect both states and to make the criteria more useful. The Draft 2 criteria are tied to specification limits wherever possible. For example, in the case of TTL devices the criteria were 0.4, 0.6 and 0.8 volt for the low output state and 2.4, 2.2 and 2.0 volt for the high output state in Draft 1. In Draft 2 the combined criteria values are 0.4 or 2.4 volts (the guaranteed specification limit for low or high state), 0.8 or 2.0 volts (the edge of the 0.4 volt noise margin), and 2.0 volts or 0.8 volt (which is a guaranteed switch from the low or high state), .respectively. Figures 5 through 7 show the revised composite graphs as they appear in Draft 2.

8

#### REPORT MDC E1667 3 JUNE 1977

# INTEGRATED CIRCUIT SUSCEPTIBILITY

0

REPORT MDC E1667 3 JUNE 1977

In Draft 2 several interference models have been presented, including a bipolar junction transistor model with RF effects, which can be used with a circuit analysis program to model ICs, and an op amp input model. These models are intended to serve as analysis tools for the designers who want to go more deeply into the susceptibility problem than is possible using the worst case data presented.

The bipolar transistor model with RF effects is an Ebers-Moll model modified to include the effects of the RF. This model is described in detail in Chapter 3. The op amp input model uses an offset generator in the inverting input lead to simulate the RF effects on the input circuitry. The translation from RF power to input voltage is empirical in Draft 2 and is presented in detail in Chapter 3.

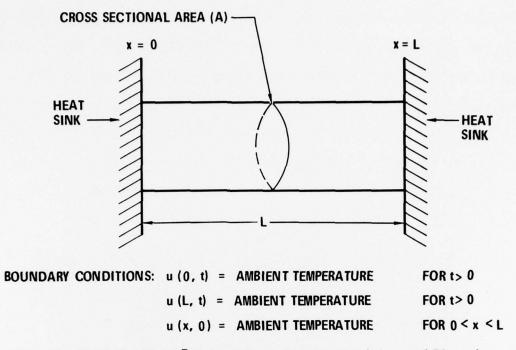

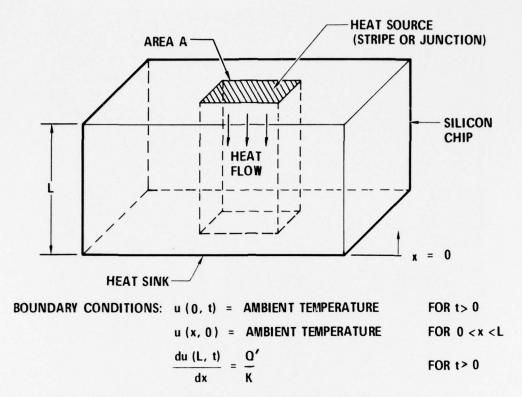

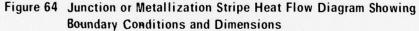

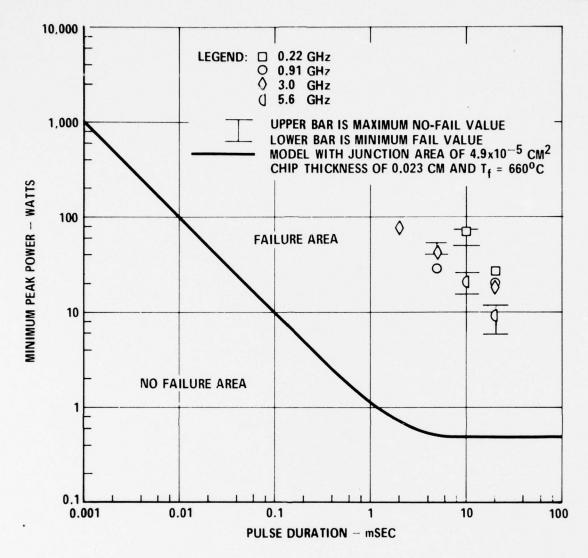

Damage models are also presented in Draft 2 which were not in Draft 1. There is a model for each damage mechanism - junction failure, metallization failure, and bond wire failure. Since these mechanisms are thermal, each model is derived from the heat flow equation with differing boundary conditions. These models are presented in Chapter 4.

Draft 2 of the handbook contains a statement recommending caution when making the complex measurements required to determine integrated circuit susceptibilities. Three Particularly error-prone areas are noted: uncertainty in calibrations due to the presence of harmonic signals, the problem of determining small differences between two large numbers when the uncertainties in the large numbers are on the same order as the difference, and instrumentation problems associated with changing RF impedances within the device under test (especially during failure testing). Different means of treating these problems in the measured data must be applied in order to obtain the best estimate of the quantity of interest (usually minimum power to produce a given effect).

Problems due to the presence of harmonic signals are particularly difficult to handle. Coupling coefficients, losses, and crystal detector calibrations are

10

REPORT MDC E1667 3 JUNE 1977

all frequency dependent. The magnitude and relative distribution among the various harmonics depends upon the device under test and the power level of the fundamental signal injected. It would seem possible to calibrate all couplers and losses at many frequencies and to measure the harmonic content of the reflected and transmitted signals, but such an approach appears to be prohibitively expensive. The most direct solution appears to be use of incident power actually measured as the best indicator of minimum power when harmonic problems are severe.

The task of determining the amount of power absorbed in the device under test is basically a matter of subtracting power reflected, transmitted, and absorbed in known losses in the test fixture from the incident power. Occasionally, a device is encountered which produces such mismatches in the system as to make the sum of the reflected, transmitted, and absorbed powers exceed the measured incident power. In such cases, the uncertainties in the measurements and calibrations (probably aided by the harmonic problem discussed above) overwhelm the expected result and a negative absorbed power is calculated. Two approaches are used to extract useful results from such data. The first is to estimate the amount of power absorbed in the device under test plus the test fixture. This method accounts for the power reflected and transmitted which is obviously not absorbed in the device. If the harmonic problem is still significant, the second option is to use measured incident power as the best estimate of minimum power.

During single pulse testing (as in the failure testing), it is necessary to sample and hold the values of the reflected and transmitted signals to permit acquiring the data. During failure testing especially, the impedance of the device under test can change (at failure) enough to cause the reflected and/or transmitted values to change during the pulse. Ideally, the test setup could be instrumented to provide either a time-history of each signal (as would be obtained from an oscillogram for example), or an adjustable-gate sample and hold could be

11

employed. Both of these schemes have been implemented in other programs, but the number of channels required (17) in the IC program makes such arrangements prohibitive.

For the pulse testing performed during the failure testing segment of the program, simple peak detectors were employed on the transient signals so that when impedance changes occurred at failure that caused larger signals than before failure, errors were introduced. This problem can be satisfactorily circumvented by performing additional data processing on the total data sample. The Bruceton test technique used in the failure testing typically produces failure in only 50% of the test sample. It is in this part of that data that the absorbed power is uncertain. By using the mean absorbed power in the no-fail data, the mean absorbed power in the failure data can be estimated.

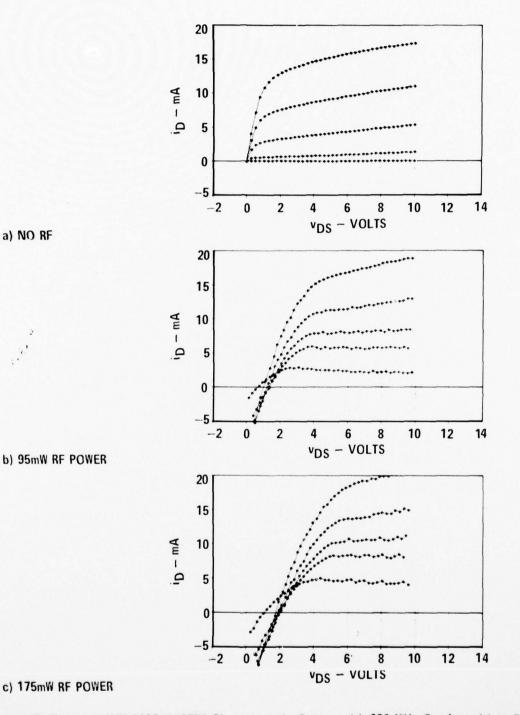

The preliminary MOSFET model presented in Chapter 3 is not ready for the handbook at this time. More effort is required to study the RF effects on the MOSFETs, both testing and analysis, before a final model is ready to be incorporated into the handbook.

2.3 <u>Outline Revisions</u> - There is one major outline revision in Draft 2 of the ICES Handbook which occurs in Chapter 2. The breakdown of Chapter 2 was by device class in Draft 1, (digital devices and linear devices). Each class of devices had its own interference and damage section. During the extensive testing performed in the second increment, all types of damage data were grouped together, and the next logical step was to revise the outline according to the type of susceptibility (interference and damage). This revision was accomplished with the class of device as the subheading for the interference section and the damage section covering all ICs.

2.4 <u>Further Review Planning</u> - In order to obtain the maximum number of reviewers for Draft 2, the external mailing list has been expanded. All those who have

12

[

T

expressed an interest in the IC susceptibility problem will receive a copy of Draft 2 of the handbook for review and comment. In addition another seminar is planned for the fall of 1977 to get comments of users firsthand along with any suggestions for the third and final draft of the handbook which will be issued in 1978.

13

#### 3. INTERFERENCE EFFECTS

The goals of the interference effects investigation are twofold: 1) to catalog the interference effects in integrated circuits to provide useful information to system designers, and 2) to gain a more complete understanding of the origin of these interference effects. Regarding the first goal, the susceptibility of the TTL family of digital devices and of bipolar operational amplifiers has been studied in detail in previous reports<sup>3,4,5</sup>. This report adds information on line driver/ receiver pairs and CMOS discul integrated circuits. In regard to the second goal, the understanding of observe' interference effects has increased to the point where it is now possible to form models for the interference effects in integrated circuits. The interference mechanism, which has been documented previously $^3$ , is the rectification of RF signals in the Pn junctions of the integrated circuits. Starting with the simplest semiconductor devices, models are shown for the rectification effects in diodes and transistors, then the models are extended to 4-layer integrated circuit construction devices and MOSFET devices. Using a computer program intended for circuit analysis, the transistor model is applied to model the case of RF entering the output of a TTL device, with the output in a low state. Op amps are modeled for the case of RF entering the input by using a small-signal type of approach.

3.1 <u>Large Signal Rectification in PN Junctions</u> - Previous investigation of the RF interference phenomenon in integrated circuits has identified rectification of the microwave signal in pn junctions to be the primary mechanism<sup>3</sup>. However, small signal detection theory does not adequately account for many of the effects observed since the microwave signal may be of large amplitude. A large-signal rectification theory has been developed, based on a time-domain analysis of junction waveforms.

15

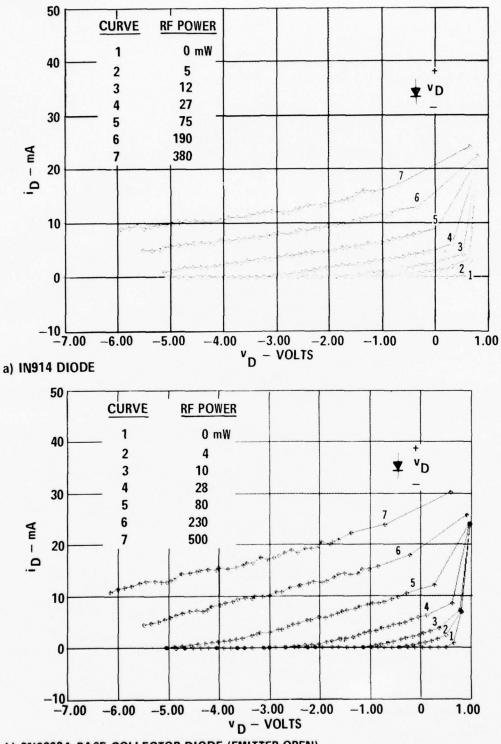

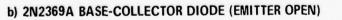

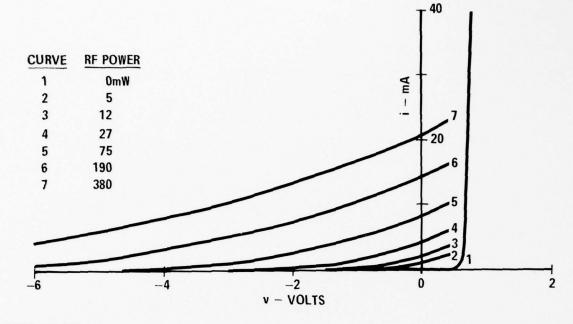

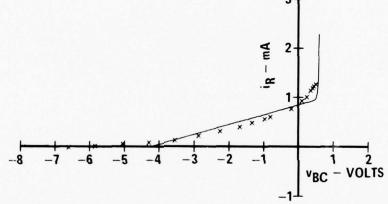

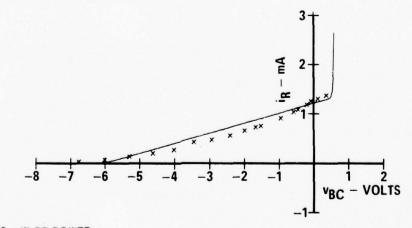

3.1.1 <u>Measured Rectification in Diodes</u> - Figure 8 shows a plot of the measured I-V characteristics of a 1N914 diode and the base-collector diode of a 2N2369A transistor (emitter open) for varying levels of RF power at 220 MHz. The effect of the RF power is to cause the portion of the diode curve below the knee to rise because of increased current flow due to rectification of the RF signal.

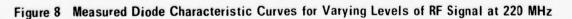

The diode characteristic curves were measured using the test setup shown schematically in figure 9. The diode was placed in a microwave test fixture during the test. Microwave energy was conducted into the diode through bias units, which allow the diode to be biased as desired.

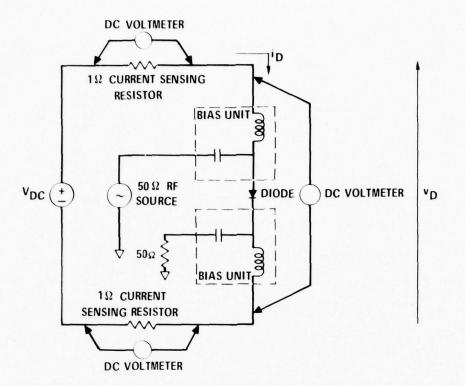

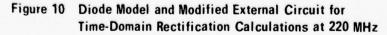

3.1.2 <u>Time-Domain Calculation of RF Effects in Diodes</u> - A time-domain calculation was performed to study large signal rectification in diodes. A suitable model was chosen for the diode, and the external circuit of the measuring system was modeled in a simplified manner to enable a computer calculation of the expected rectification in the diode.

The diode model and modified external circuit are shown in figure 10. The diode model consists of the series resistor  $R_S$ , junction leakage resistance  $R_p$ , a nonlinear diode junction D, and capacitance C. The relation between the current through D,  $i_i$ , and the junction voltage  $v_i$ , is

$$i_j = I_o(exp(Qv_j) - 1)$$

where  $I_0$  is the junction reverse saturation current, and Q is a constant with units of volts<sup>-1</sup>.

The capacitance of a diode junction varies with the junction bias. When reverse biased, this capacitance, primarily transition capacitance, is given by<sup>6</sup>

$$c = \frac{c_j}{(\phi - v_j)^n}$$

where  $C_i$  is a constant capacitance,

16

-----

17

1 4

#### Figure 9 Test Setup for Measurement of Diode Characteristics Curves Under RF Influence

18

$\phi$  is the junction contact potential (which is between 0.6 and 1 volt for most silicon devices, and

n is the junction grading constant (generally between 1/2 and 1/3).

When the diode is conducting, the capacitance (now mainly diffusion capacitance) is approximately proportional to the diode current and is given by  $^{6}$

$C = QT_d I_o \exp(Qv_J)$

where  ${\rm T}_{\rm d}$  is a constant with units of seconds.

When the diode is forward biased, the diffusion capacitance can become quite large. On the other hand, for the reverse biased diode, the transition capacitance is rather small for most devices, and does not vary greatly over the range of reverse bias voltages. Therefore, for the time domain model, the capacitance was simplified to

$$C = C_0 + QT_d I_0 exp (Qv_d)$$

where  $C_{o}$  is a constant capacitance that approximates the diode transition capacitance.

The relationship between the charge, q, stored in a capacitor and voltage across it,  $v_1$ , is

$q = Cv_{1}$ .

After differentiation, the capacitor current, ic, becomes  $i_{C} = \frac{dC}{dv_{J}} \frac{dv_{J}}{dt} v_{J} + C \frac{dv_{J}}{dt}$

S0,

$$i_{C} = (v_{J} \frac{dC}{dv_{J}} + C) \frac{dv_{J}}{dt}$$

The circuit external to the diode model consists of an ideal dc voltage source, an ideal sinusoidal RF voltage source, and a resistor and inductor in parallel. The RF source has a voltage waveform given by

$v_{source} = V_{s} sin_{\omega}t$

19

where  $V_s$  is the voltage amplitude,  $\omega$  is the angular frequency of the waveform, and  $V_s = \sqrt{8(50\Omega)P}$ , where P is the RF power.

Due to the widely different time constants of the two legs of the bias units used in measuring rectification, it is difficult to perform a time domain calculation without requiring large amounts of computer time. For this reason, the bias units were not modeled, but a circuit that performs a similar function as the bias units was implemented instead. Basically, the bias units separate the diode terminals into microwave and low frequency lines. The microwave lines have a microwave impedance of  $50\Omega$ , while the dc lines have an impedance of practically zero at low frequency. It was desired to retain this characteristic in the time-domain modeling. The parallel resistor and inductor combination shown in figure 10 does this. At the frequency of the RF source, the inductor has a high impedance, while at dc, the inductor acts as a short. The effect of this circuit is to have a resistance of  $50\Omega$  for the RF source, and a resistance of 0 at dc. The value of the inductor,  $0.43 \, \mu$ H, was chosen to yield high impedance at 220 MHz, yet give the circuit a settling time short enough to permit reasonably fast computer calculations.

The time-domain solution involves solving two simultaneous differential equations, since there are two charge-storage elements in the circuit. The Runge-Kutta method was used to find the time domain solution from two initial conditions. The values of interest are  $i_D$ , defined as the average current through the diode, and  $v_D$ , the average voltage across the diode. A trapezoidal integration was performed on these values over one period, after which the average  $i_D$  and  $v_D$  were computed. The value of  $v_D$  was compared with  $v_{DC}$ , and if the two were not within a given tolerance, generally 0.001 volt, the process was repeated until it could be assumed that the initial transient had died out.

A time domain calculation was performed on a 1N914 diode and the B-C diode of a 2N2369A transistor using the parameters shown in table 1 for the diodes. The

20

values of  $R_S$ ,  $R_P$ ,  $I_o$  and Q were obtained from reference 3. The value of  $C_o$  corresponds to values listed in semiconductor data books. The value of  $T_d$  was chosen for the lN914 diode to yield a value for  $i_D$  of 20.8 mA when  $v_D = 0$  and P = 380 mW, to agree with the observed case. The value of  $T_d$  for the 2N2369A base-collector diode was obtained similiarly.

| PARAMETER      | 1N914 DIODE              | 2N2369A BASE-<br>COLLECTOR DIODE |

|----------------|--------------------------|----------------------------------|

| RS             | 2.6 Ω                    | 4.6 Ω                            |

| Rp             | 347K Ω                   | <b>360K</b> Ω                    |

| I <sub>o</sub> | 7.4 nA                   | 60 nA                            |

| Q              | 19.9 VOLTS <sup>-1</sup> | 15 VOLTS -1                      |

| C <sub>o</sub> | 2 pF                     | 4 pF                             |

| т <sub>d</sub> | 0.43 nSEC                | 0.37 nSEC                        |

| Table 1 Mode | I Parameters for | <b>Time-Domain</b> | Rectification | Calculations |

|--------------|------------------|--------------------|---------------|--------------|

|              |                  |                    |               |              |

Figure 11 shows the diode I-V characteristics predicted by the time domain model for the 1N914 diode and the 2N2369A base-collector diode at 220 MHz. The curves have very nearly the same shape as the measured curve of figure 8, indicating that a time-domain calculation works well in analyzing large signal rectification of diode junctions.

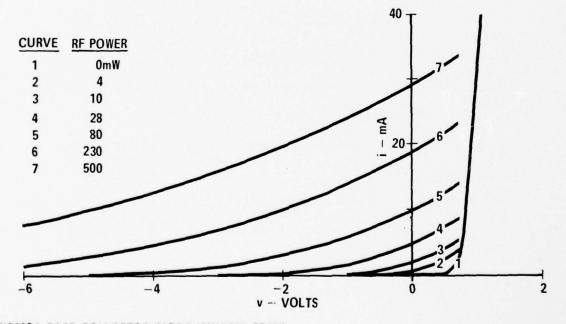

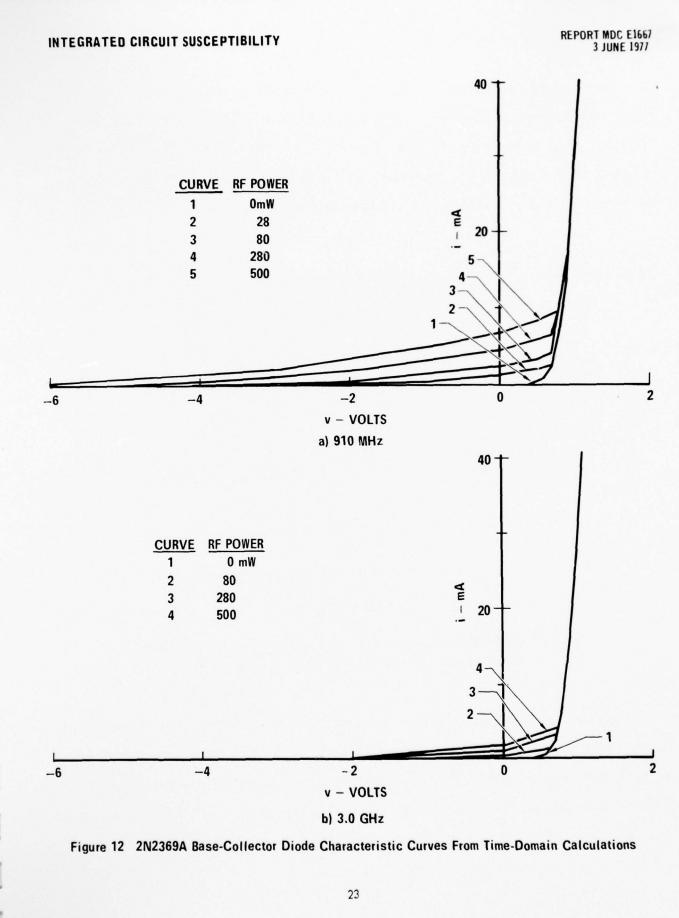

As the frequency increases into the gigahertz region, it has been observed that interference effects in integrated circuits generally decrease<sup>3</sup>. The timedomain model can be used to analyze the effect of frequency on rectification. Figure 12 shows the calculated diode characteristic curves at 910 MHz and 3 GHz for the 2N2369A base-collector diode (emitter open). The plots indicate that the amount of rectified current decreases as the frequency increases. They agree well with measured rectification of the 2N2369A base-collector diode at 910 MHz and 3 GHz (not shown).

21

REPORT MDC E1667 3 JUNE 1977

a) IN914 DIODE

# b) 2N2369A BASE-COLLECTOR DIODE (EMITTER OPEN)

Figure 11 Diode Characteristic Curves From Time-Domain Calculations at 220 MHz

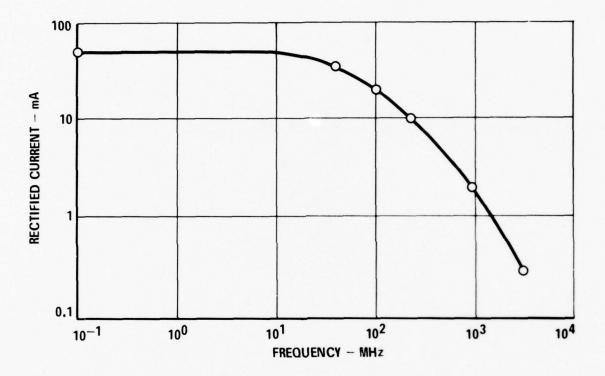

The decrease in rectified current with frequency is hown graphically in figure 13. Plotted is the amount of rectified current produced by a 2N2369A base-collector diode at an RF power of 80 mW and  $v_D = 0$ . The rectification can be computed for the new driving impedance. This has not been done, but some study of the effect of driving impedance is planned for the future.

Figure 13 Rectification Current as a Function of Frequency for the 2N2369A Base-Collector Diode (RF Power = 80 mW and  $V_{DC}$  = 0.V.)

The time-domain rectification model can also be used to study the effects of different RF driving impedances. By replacing the 50 ohm resistor with the observed or predicted RF driving impedance, and performing the calculations, the amount of rectification can be computed for the new driving impedance. This has not been done but some study of the effect of driving impedance is planned for the future.

3.2 <u>RF Erfects in Transistors</u> - Transistors respond to RF signals through rectification which occurs in the base-emitter and base-collector junctions. The effect of the rectification is to make the transistor characteristic curves appear to change. It is probable that a time-domain type of calculation would account for the effects, but this approach would be unwieldy and of little practical use. In the following sections a transistor model is developed which is both powerful and practical. It can be used with existing computer-aided circuit analysis programs to analyze interference in circuits. An extension of the method allows an analysis of RF effects in 4-layer pnpn structures.

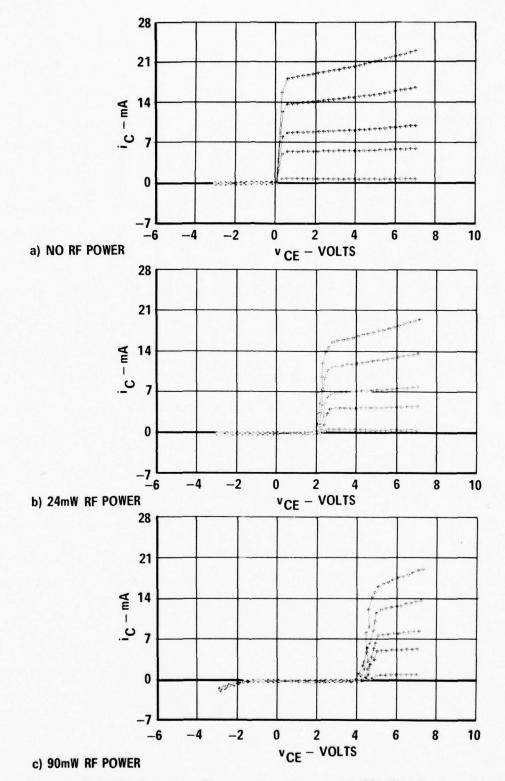

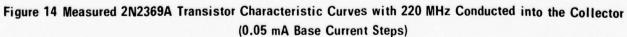

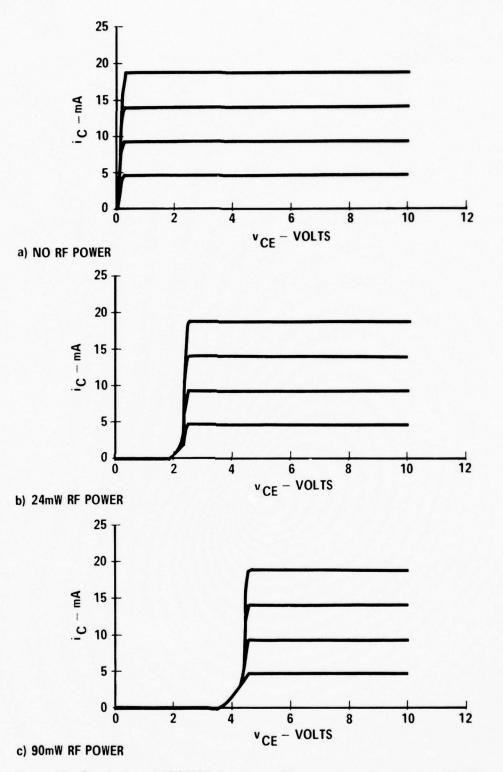

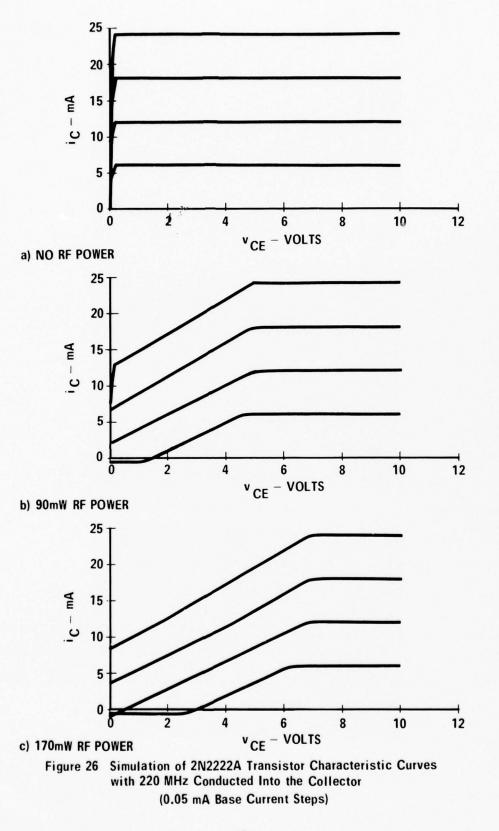

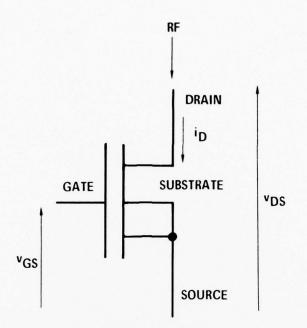

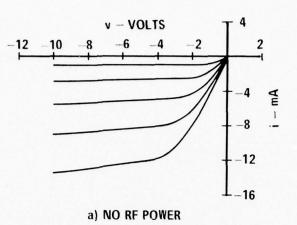

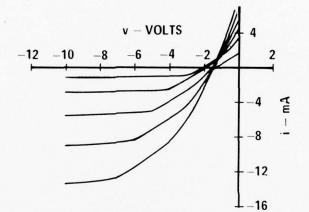

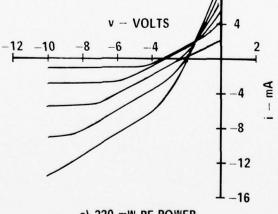

3.2.1 Interference Effects with RF Conducted into Collector - In order to understand the interference effects produced as RF enters the output of a TTL device, it is important to study the effects of RF conducted into a transistor collector lead. Figure 14 shows the  $i_C$  vs  $v_{CE}$  curves for a 2N2369A transistor with a 220 MHz CW signal conducted into its collector. Figure 15 shows a similar set of curves for a 2N2222A transistor. For both transistors, the effect is a decrease in collector current at low  $v_{CE}$ . At high  $v_{CE}$ , the collector current is relatively unchanged. For the 2N2369A, the collector current decreases nearly to zero at low  $v_{CE}$ , so that it appears that the  $i_C$  vs  $v_{CE}$  curves have moved to the right. For the 2N2222A, the collector current decrease is less rapid, so that the effect is to cause the curves to become more rounded in the saturation region. These two effects are typical of the response of all transistors observed to date for RF energy conducted into their collectors.

An observation can be made at this point. Since the greatest interference effect occurs at low  $v_{CE}$ , it appears that transistors biased at high  $v_{CE}$  are less susceptible to RF energy conducted into their collectors than transistors biased at low  $v_{CE}$ . This rule of thumb suggests that biasing transistors to operate at high collector-to-emitter voltages will result in circuits less likely to exhibit interference.

25

26

a) NO RF POWER

b) 90mW RF POWER

c) 170mW RF POWER

Figure 15 Measured 2N2222A Transistor Characteristic Curves with 220 MHz Conducted into the Collector (0.05 mA Base Current Steps)

27

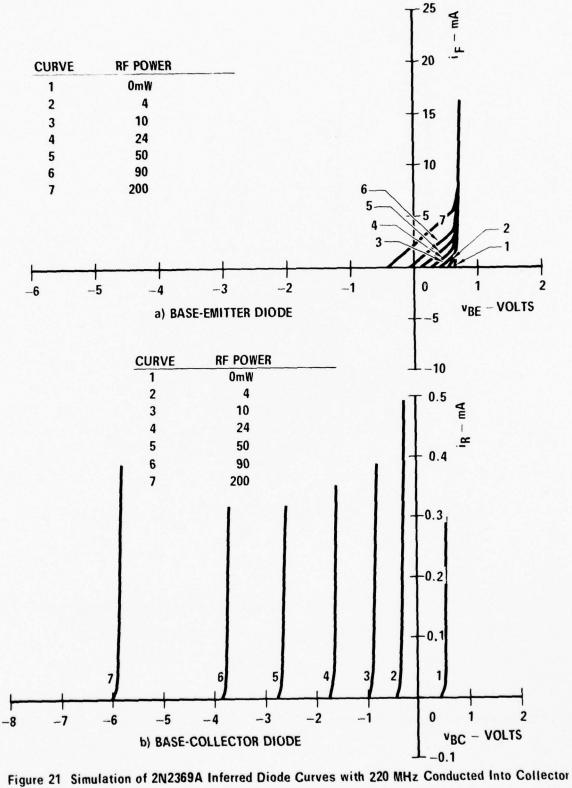

3.2.2 <u>Mcdeling Interference Effects with RF Conducted into Collector</u> - In modeling RF effects in transistors, the approach taken was to start with an existing transistor model, the Ebers-Moll representation, and modify it to account for the RF effects.

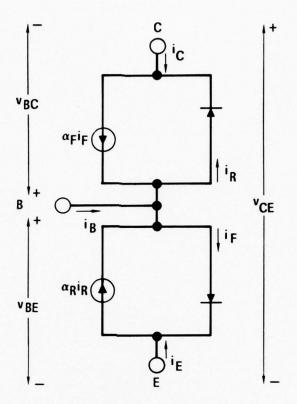

Figure 16 shows the standard Ebers-Moll model for an npn transistor, where the characteristics of the two diodes are given by

$$i_F = i_{OF}(exp (qv_{BE}/KT) - 1),$$

$i_R = I_{OR}(exp (qv_{BC}/KT) - 1),$

and  ${\rm I}_{\rm OF}$  and  ${\rm I}_{\rm OR}$  are the diode reverse saturation currents.

Little interference effect occurs at high  $v_{\mbox{CE}}^{},$  so it is approximately true in this region that

$$i_{\rm C} = \beta i_{\rm B},$$

where  $\beta$  is forward current gain measured when no microwave energy is present. This suggests that, in modifying the Ebers-Moll model, the values  $\alpha_F$  and  $\alpha_R$  be kept constant at their dc values.

Holding the alphas constant for varying values of RF power requires the I-V characteristics of the two diodes in the Ebers-Moll model to change to account for the observed effects.

The diode I-V characteristics can be calculated at a given RF power from measurements of  $i_{C}$ ,  $i_{B}$ ,  $v_{CE}$ , and  $v_{BE}$ . Referring to figure 16, node equations written at the base and collector of the transistor are

$$i_{B} = (1 - \alpha_{F}) i_{F} + (1 - \alpha_{R}) i_{R}$$

$i_{C} = \alpha_{F} i_{F} - i_{R}$ .

Solving for the two diode currents, i<sub>F</sub> and i<sub>R</sub>, yields

$$i_{F} = \frac{i_{B} + (1 - \alpha_{R}) i_{C}}{1 - \alpha_{F} \alpha_{R}},$$

$$i_{R} = \frac{\alpha_{F} \alpha_{B} - (1 - \alpha_{F}) i_{C}}{1 - \alpha_{F} \alpha_{R}}.$$

REPORT MDC E1667 3 JUNE 1977

Figure 16 Standard Ebers-Moll Model for NPN Transistor

Also, the base-collector voltage is given by:

I

Measurement of the dc components of  $i_{C}$ ,  $i_{B}$ ,  $v_{CE}$  and  $v_{BE}$  allows one point on each of two "inferred" diode curves to be calculated:  $(v_{BE}, i_{F})$  and  $(v_{BC}, i_{R})$ . Keeping the RF power constant and varying the transistor operating point allow both diode I-V curves at that power level to be determined.

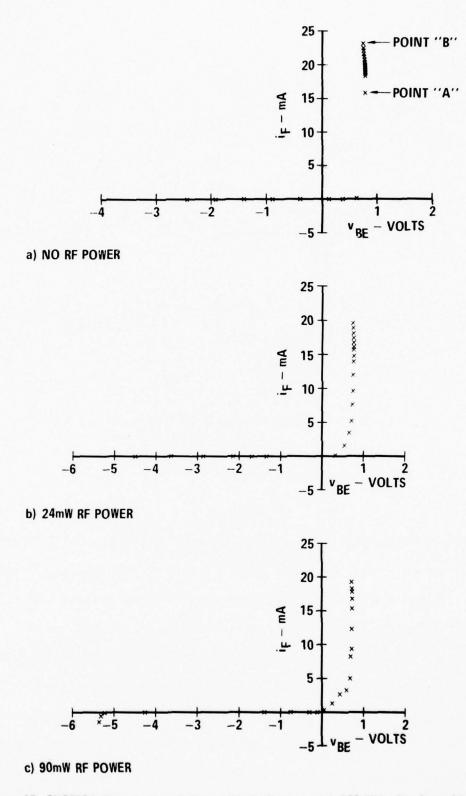

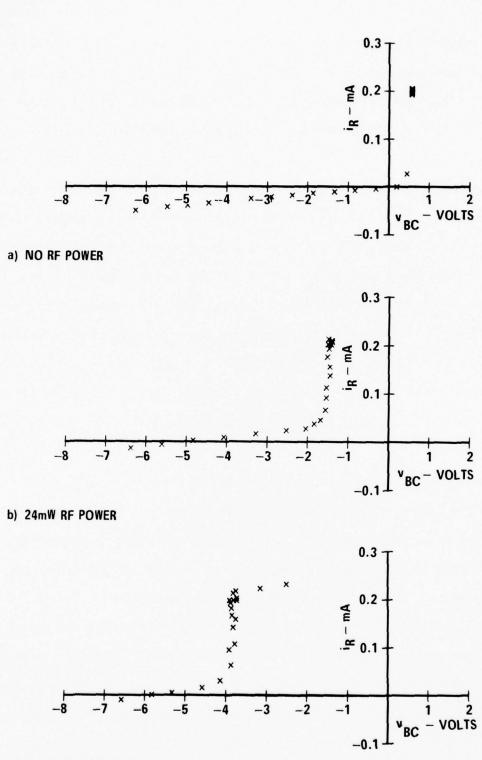

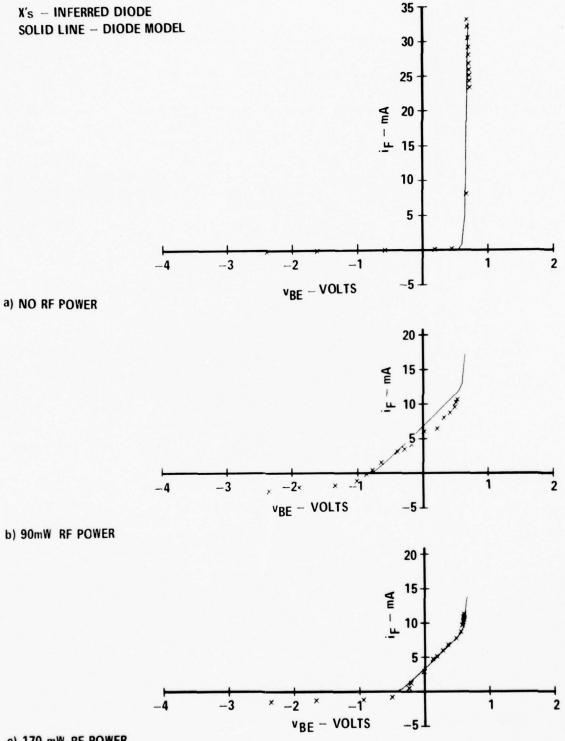

The 2N2369A and 2N2222A data of figures 14 and 15 were measured on an automated test system which simultaneously measures  $i_c$ ,  $i_B$ ,  $v_{CE}$ , and  $v_{BE}$ , as well as other parameters. Using the values of  $\alpha_F = 0.9895$  and  $\alpha_R = 0$  calculated from measurements of the 2N2369A forward and reverse betas, the inferred diode curves were determined from the 2N2369A data, and are shown plotted in figures 17 and 18. The curves are plotted as discrete points because each point is calculated from the transistor

29

REPORT MDC E1667 3 JUNE 1977

1

30

c) 90mW RF POWER

currents and voltages at a single bias condition. The points were calculated from the transistor curves where  $i_B = 0.2$  mA. The inferred diode curves show considerable heating effect because the automated test system is unable to "sweep" a curve as a curve tracer; it is much slower and causes considerably more heating in the transistor.

The 2N2369A base-emitter inferred diode curves of figure 17 show the diode at 24 mW and 90 mW of RF power incident on the collector. Figure 17a shows a typical diode characteristic, with a sharp turn-on at about 0.8 volt, and little conduction below that. The reverse slope between points "A" and "B" is a thermal effect and will be discussed later. As the RF power increases, the knee becomes less sharp, folding up in an almost linear region between the non-conducting and conducting regions of the diode. Notice also that at 90 mW of RF power (figure 17c) the base-emitter breakdown comes into view at about -5.4 volts. This breakdown occurs because the transistor avalanche breakdown point appears to move to the right with increasing RF power.

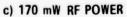

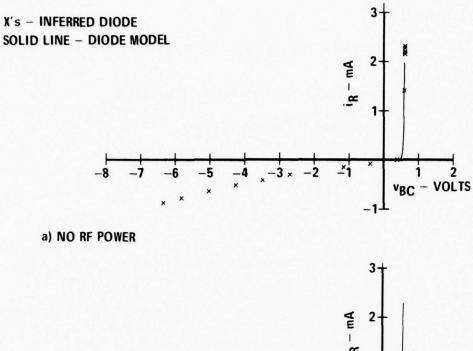

The 2N2369A base-collector inferred diode curves shown in figure 18 correspond to the same RF powers as the curves of figure 17. Figure 18a shows a sharp diode turn-on at about 0.5 volt. The rather large reverse currents (up to 0.05 mA) are partially a heating effect, and will also be discussed later. As the RF power is increased, the diode knee appears to move to the left. The heating effect is still present in the points to the left of the diode knee, evidenced by the slope in these points. At 90 mW of RF power (figure 18c) there is a second break point at -4 volts and 0.2 mA, where the curve appears to flatten out, giving the whole curve an "S" shape. The two points at the upper right of the curve occur when the transistor is breaking down, and correspond to the points when the baseemitter diode breaks down. Ordinarily the base-collector diode current becomes clamped at the base current because the base-emitter diode is reverse biased (and

32

$\alpha_{R} = 0$ ), and any  $v_{CE}$  change is reflected in a change in reverse voltage of the baseemitter diode. However, when the base-emitter diode breaks down, it conducts and its voltage becomes clamped at the breakdown voltage. A change in  $v_{CE}$  must therefore be reflected in a change in  $v_{BC}$ . Since the Ebers-Moll model does not account for breakdown, these points are artificial. For a transistor operating on a typical load line, the breakdown region will rarely be a region of operation, even considering RF stimulus. In view of this, the breakdown region of the diodes will not be modeled.

In analyzing the heating effects, consider first the reverse slope of the conduction region of the base-emitter diode (figure 17a). For a silicon diode conducting heavily in the forward region the current is

i ≈ I<sub>0</sub> exp (v/V<sub>T</sub>) where the reverse saturation current I<sub>0</sub> is given by<sup>7</sup>  $I_0 = K_1 T^{1.5} exp (-V_{60}/V_T)$

where  $K_1$  is a constant,

T is temperature in degrees Kelvin,

$V_T$  is  $\frac{kT}{q} = \frac{T}{11,600}$ , and

$\rm V_{GO}$  is a voltage which is numerically equal to the forbidden gap energy in electron volts. For constant i,

$$\frac{dv}{dT} = \frac{v - (v_{GO} + 1.5 v_T)}{T} .$$

(1)

Temperature measurements were made on the 2N2369A transistor when no RF energy was applied. When biased at  $v_{CE} = 7.00$  volts and  $i_C = 23.0$  mA, which corresponds to the largest power dissipated in figure 14a, 160 mW, the transistor reached a stable case temperature of 118°F (321°K). When the transistor was biased at a  $v_{CE}$  of 0.328 volt and  $i_C$  of 15.6 mA, only 5 mW was dissipated, and the transistor can be assumed to be at the ambient temperature, 72°F (295°K). The points labeled "B" ( $v_{BE}$  of 0.7519 volt,  $i_F$  of 23.2 mA) and "A" ( $v_{BE}$  of 0.79 volt,  $i_F$  of 15.6 mA)

in figure 17a correspond to these two temperatures, respectively. The voltage decrease from point A to B is 0.0381 volt, as the temperature increased  $46^{\circ}F$  ( $26^{\circ}C$ ). At "A" v is 0.79 volt and T =  $295^{\circ}K$ , so from (1)

$$\frac{\mathrm{d}\mathbf{v}}{\mathrm{d}\mathsf{T}} = -1.55 \ \frac{\mathrm{m}\mathsf{V}}{^{\circ}\mathsf{K}},$$

The predicted  $\Delta v$  would be

$$\Delta v = \frac{dv}{dT} \Delta T = 0.0403 \text{ volts},$$

which is very nearly the observed voltage change.

For a reversed biased silicon diode, the reverse current is composed mainly of transition-layer charge-generation current, which varies with both bias voltage and temperature. The current is proportional to the square of the reverse bias voltage<sup>8</sup>. The temperature dependence is given by

$I_{o} = K_2 T^{1.5} \exp(-V_{GO}/2V_T)$

where  $K_2$  is a constant.

As the temperature increases from  $72^{\circ}F$  to  $118^{\circ}F$ , this relation predicts that  $I_0$  will increase by a factor of 7.80. The large reverse current observed in figure 18a as the reverse bias voltage increases is probably due to both the voltage-squared variation and heating effects.

Since heating effects are not the subject of this report, little more will be said about them. However, an awareness of these effects helps interpret the inferred diode curves shown earlier.

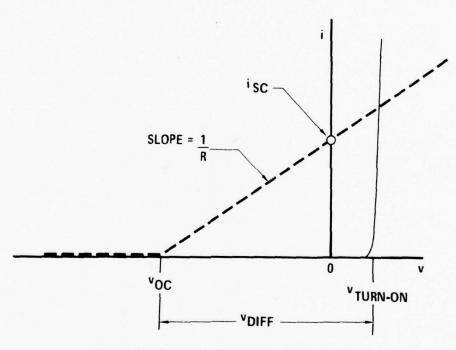

The approach used to model the inferred diode curves of figures 17 and 18 is shown in figure 19. Each of the diode I-V curves has a somewhat piecewise linear behavior which can be approximated by summing the two curves shown in figure 19. The solid line represents the dc diode characteristics, while the dashed line represents the effect of RF energy on the diode. The latter is piecewise linear in behavior and is defined as zero current for voltages below some voltage,  $v_{0r}$ ,

34

1

and increasing current with a slope of  $\frac{1}{R}$  for voltages greater than  $v_{OC}$ . The sum is a curve with approximately zero current below  $v_{OC}$ , increasing current with a slope of  $\frac{1}{R}$  between  $v_{OC}$  and  $v_{TURN-ON}$ , and sharply increasing current above  $v_{TURN-ON}$ . The curve intercepts the current axis at a value of short-circuit current,  $i_{SC}$ .

The similarity of the sum to the curves of figure 17 is evident, but the similarity to the curves of figure 18 is more difficult to see. The curves of figure 18 can be thought to have a large slope  $\frac{1}{R}$ , and a large  $i_{SC}$ , say 20 mA. In this way, both the base-emitter and base-collector inferred diodes of the 2N2369A can be modeled in the same fashion.

Figure 19 Approach Used to Model Diode Curves

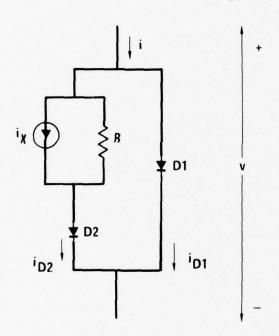

A circuit which realizes the curves of figure 19 is shown in figure 20. Diode D1 is assumed to be the dc diode, having a current-voltage characteristic given by

$$i_{D1} = I_{0} (exp (qv_{D1}/kT) - 1)$$

where I<sub>o</sub> is the diode reverse saturation current. Dl produces the solid line of figure 19, while the left branch of the circuit produces the dashed line. Diode

35

D2 acts as a switch, allowing current to flow through the Norton equivalent only when it is "on". The voltage at which the diode turns on is determined by the open circuit voltage of the Norton equivalent,  $i_{\chi}R$ . Diode D2 conducts when the voltage across it is greater than its own turn-on voltage,  $v_{TURN-ON_2}$ , which occurs when

$$v > v_{OC} = v_{TURN-ON_2} - i_X^R$$

.

When v is less than  $v_{0C}$ , the current through the left branch is essentially zero. For v greater than  $v_{0C}$ , the current through the left branch is

$$i_{D2} = i_{X} + (v - v_{TURN-ON_2})/R$$

Usually it can be assumed that diodes D1 and D2 have the same characteristics, so that

and the voltage,  $v_{\text{DIFF}}$ , of figure 19 is

$v_{DIFF} = i_X R.$

36

The Norton generator elements,  $i_{\chi}$  and R, are functions of RF power and frequency. Experimental results show that, in general, R is constant for different RF power levels at a given frequency, but that  $i_{\chi}$  varies with the microwave power level. A relation for  $i_{\chi}$  that gives good results is

$i_{x} = v_{DIFF}/R$ ,

where

## $v_{\text{DIFF}} = X\sqrt{8R_g}P_{RF}$

and  $R_g$  is the real part of the RF generator impedance in ohms, and  $P_{RF}$  is the available RF power in watts, and X is a constant of proportionality. Note that with no RF power,  $i_{\chi} = 0$ . In the forward conduction region with no RF power the model essentially acts as the dc diode, Dl, because resistor R limits the current that can flow through diode D2. In the reverse region, the reverse current will be approximately double that of the dc diode. This difference is not thought to be significant. The diode model is accurate both when RF energy is present and when it is removed.

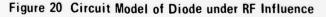

Table 2 lists the diode model parameters obtained from a best fit to the 2N2369A base-emitter and base-collector inferred diode curves at 220 MHz. The generator impedance,  $R_g$ , is 50 ohms. The diode curves that result when using these parameters are shown in figure 21 for a range of RF powers at 220 MHz. Comparison with figures 17 and 18 shows the accuracy obtained by using this simple diode model.

The diode model of figure 20 is adequate for modeling discrete diodes under RF influence, such as those discussed in Section 3.1 as well as the inferred diodes discussed here. This might be done, for example, when analyzing the interference effect that might be produced in a circuit containing diodes, where a time-domain calculation would be overly difficult and time-consuming.

37

Table 22N2369A Inferred Diode Model Parameters220 MHz CW RF POWER CONDUCTED INTO COLLECTOR

BASE-EMITTER DIODE:  $I_{OF} = 9.36 \times 10^{--16} \text{ AMPS}$   $R_E = 180 \Omega$   $X_E = 0.12$ BASE-COLLECTOR DIODE:  $I_{OR} = 7.55 \times 10^{-15} \text{ AMPS}$   $R_C = 190 \Omega$  $X_C = 0.72$

By inserting the diode model into the Ebers-Moll representation, a model for the transistor with RF stimulus is obtained. Figure 22 shows the modified Ebers-Moll transistor model. Using the parameters derived for the 2N2369A diodes, the transistor  $i_{\rm C}$  vs v<sub>CE</sub> curves can be retraced. The result is shown in figure 23. The agreement with the curves of figure 14 is good.

A similar analysis can be performed on the 2N2222A transistor. The inferred diode curves are shown in figures 24 and 25 for the 2N2222A base-emitter and basecollector diodes, respectively. Notice the heating effect evident in the reverse slope of the base-emitter diode forward conduction region, and the large reverse currents in the base-collector diode. Superimposed on these are the results of using the diode model of figure 20 using the parameters listed in table 3. The resulting transistor curves from the modified Ebers-Moll model are shown in figure 26. These curves are a fair approximation to those of figure 15. Notice that the saturation region does not show the continuous curve seen in figure 15, but is approximated by a straight-line region. This difference results from

38

-

-----

REPORT MDC E1667 3 JUNE 1977

39

REPORT MDC E1667 3 JUNE 1977

Concession of the local division of the loca

Figure 22 Modified Ebers-Moll Model for a Transistor Under RF Influence

modeling the inferred diode curves with a linear region at the knee due to the RF energy. The base-collector diode, especially, is insufficiently modeled by a linear region. The given transistor simulation is fairly accurate compared with the measured case, and is straightforward to implement. If desired, a better simulation could be obtained by approximating the diode curves with a more complex function.

40

[]

REPORT MDC E1667 3 JUNE 1977

Figure 23 Simulation of 2N2369A Transistor Characteristic Curves with 220 MHz Conducted Into Collector (0.05 mA Base Current Steps)

41

-

42

÷

T

1

1

c) 170 mW RF POWER

43

#### Table 3 2N2222A Inferred Dinde Model Parameters

## 220 MHz CW RF POWER CONDUCTED INTO COLLECTOR

BASE-EMITTER DIODE:  $I_{OF} = 2.2 \times 10^{-14} \text{ A}$   $R_E = 104 \Omega$   $X_E = 0.166$ BASE-COLLECTOR DIODE:  $I_{OR} = 3.3 \times 10^{-14} \text{ A}$   $R_C = 4.9 \text{K} \Omega$  $X_C = 0.80$

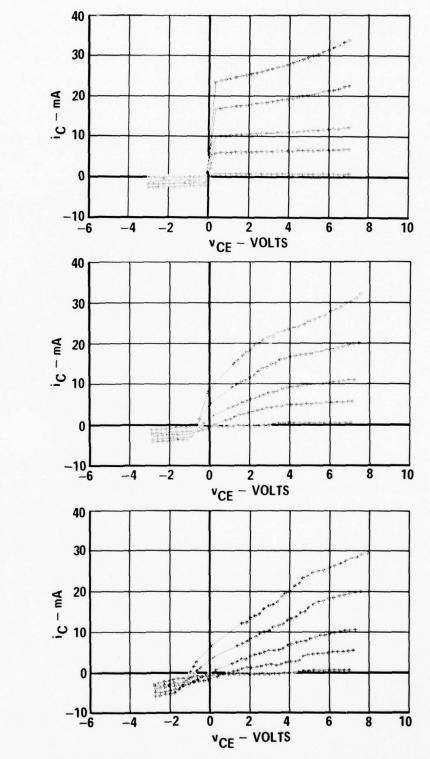

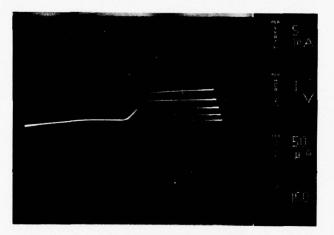

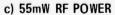

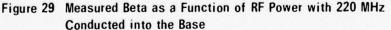

3.2.3 Interference Effects with RF Conducted into Base - Figures 27 and 28 show the 2N2369A and 2N2222A transistor  $i_C$  vs  $v_{CE}$  characteristics when a 220 MHz CW signal is injected into the base. The interference effect is different for this case than when RF energy is injected into the collector. The forward current gain (beta) decreases significantly with low levels of RF power; for the 2N2222A, only 5.4 mW of RF power reduces the beta to less than half of its original value. The curves appear to shrink uniformly; the ac and dc betas decrease at the same rate. At 55 mW, the 2N2369A curves show an additional effect by rising off the voltage axis with a current offset. The 2N2222A curves move to the left with increasing RF level.

44

REPORT MDC E1667 3 JUNE 1977

45

Citra I.

a) NO RF POWER

b) 2.8mW RF POWER

Figure 27 Measured 2N2369A Transistor Characteristic Curves with 220 MHz Conducted into the Base

46

T

a) NO RF POWER

b) 5.4mW RF POWER

c) 69mW RF POWER Figure 28 Measured 2N2222A Transistor Characteristic Curves with 220 MHz Conducted into the Base

47

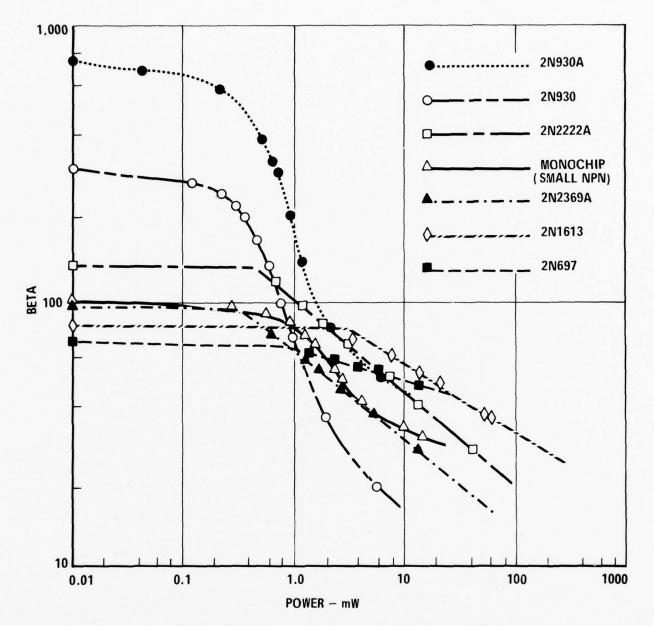

Figure 29 shows a plot of beta vs 220 MHz RF power incident on the base for several transistors. For the 2N930 and 2N930A, beta begins to decrease at less than 0.1 mW of RF power, and decreases quite rapidly, reaching one-tenth of its original value at approximately 3 mW. Other transistors do not show a significant beta decrease until about 1 mW of RF power is reached, and decrease less rapidly than the 2N930 and 2N930A. To date, no general quantitative relationship exists between beta and RF power level.

3.2.4 <u>Modeling Interference Effects with RF Conducted into Base</u> - The modified Ebers-Moll model can be applied to transistors with RF energy entering the base if  $\alpha_F$  and  $\alpha_R$  are allowed to vary as the RF power is increased. This means that the forward and reverse alphas (or equivalently, the betas) must be treated as functions of RF power. Once the betas or alphas ( $\alpha = \frac{\beta}{\beta + 1}$ ) are determined, the inferred diode curves can be obtained as outlined previously. At present, a logarithmic polynomial curve fit may be the best way to characterize beta vs RF power, since no general relation exists.

An interference effect not seen in the curves of figures 27 and 28 is a rapid decrease in  $v_{BE}$  as the RF power is increased. At high enough powers,  $v_{BE}$  becomes negative. This decrease is due to a rectified voltage in the base-emitter junction of the transistor. Depending on the transistor application, the decrease in  $v_{BE}$  may be the dominant interference effect. No special effort is required to model it, as the inferred diode curves contain the required information.

It is evident that modeling the transistor with RF energy entering the base is more difficult than when it enters the collector because the dependence of  $\beta$  on RF power must be obtained for a complete model.

3.2.5 <u>Interference Effects in Integrated Circuit Transistors</u> - The method used to infer diode rectification curves from transistors can be extended to include

REPORT MDC E1667 3 JUNE 1977

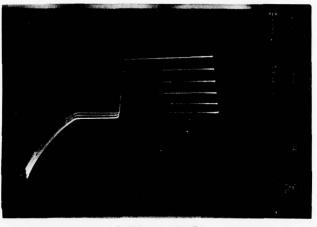

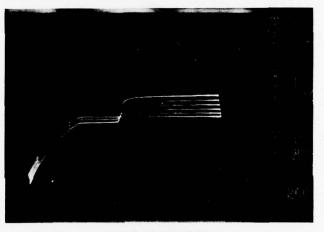

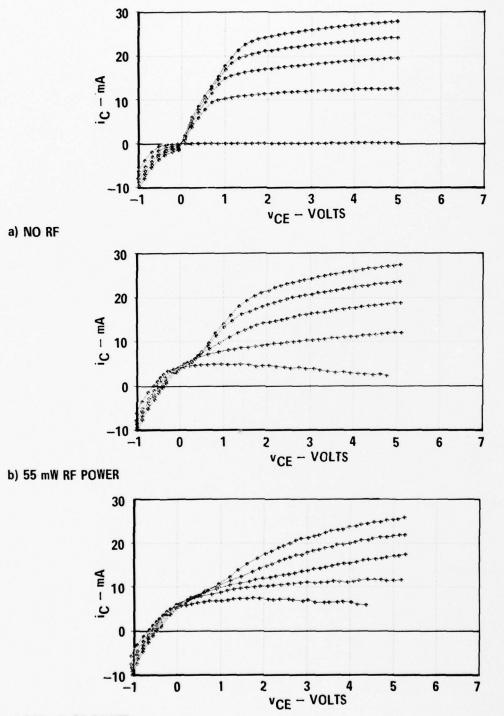

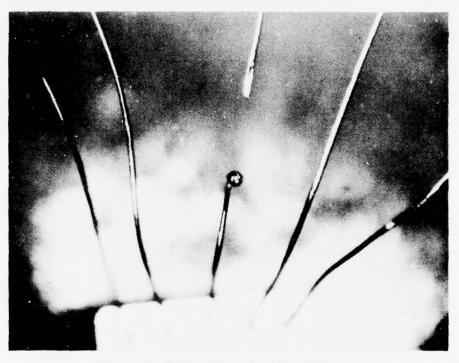

4-layer pnpn structures. The device chosen to illustrate this technique was a Monochip MO-OOl, which contains 4 "small npn" (Interdesign's designation) transistors on a p-type substrate. Transistor curves are shown in figure 30 for no RF and for 55 mW and 140 mW of RF power on the collector of one of the transistors.

49

REPORT MDC E1667 3 JUNE 1977

Î

Principal Party

Colescon .

c) 140 mW RF POWER

Figure 30 Measured Monochip MO-001 Transistor Characteristic Curves with 220 MHz Conducted into Collector (0.25 mA Base Current Steps)

#### REPORT MDC E1667 3 JUNE 1977

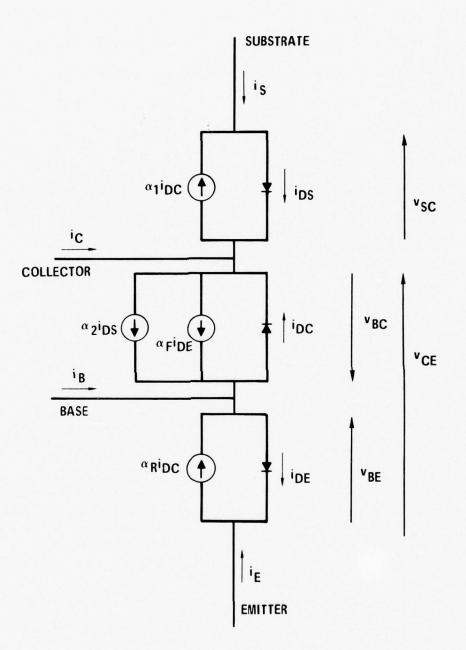

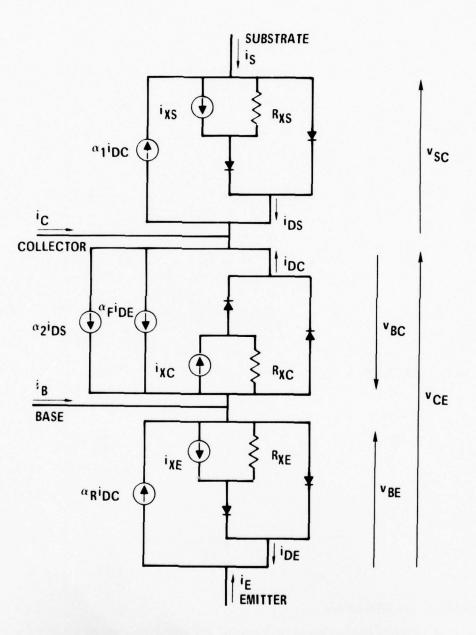

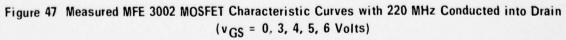

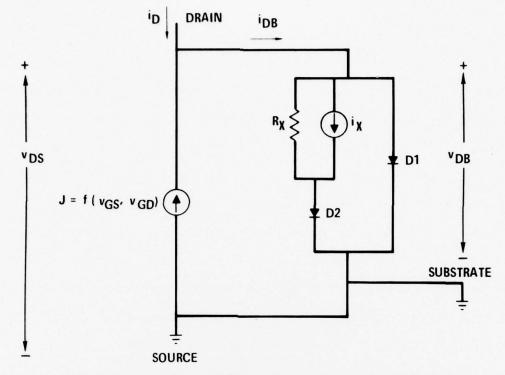

A proposed 4-layer structure model<sup>9</sup> is shown in figure 31. It is an expanded version of the Ebers-Moll transistor model, with an extra diode to account for the substrate-to-collector junction, and two extra current-controlled current sources to account for coupling between the substrate-to-collector and base-to-collector junctions. The values of  $\alpha_F$  and  $\alpha_R$  were measured by connecting the device as an npn transistor on a curve tracer using the collector, base, and emitter terminals, with the substrate shorted to the collector. The values of  $\alpha_1$  and  $\alpha_2$  were measured by connecting it as a pnp transistor using the base, collector, and substrate terminals, with the emitter shorted to the base. The measured values are:

$\alpha_{\rm F} = 0.9783$  $\alpha_{\rm R} = 0.231$  $\alpha_{\rm 1} = 0.737$  $\alpha_{\rm 2} = 0.074.$

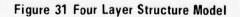

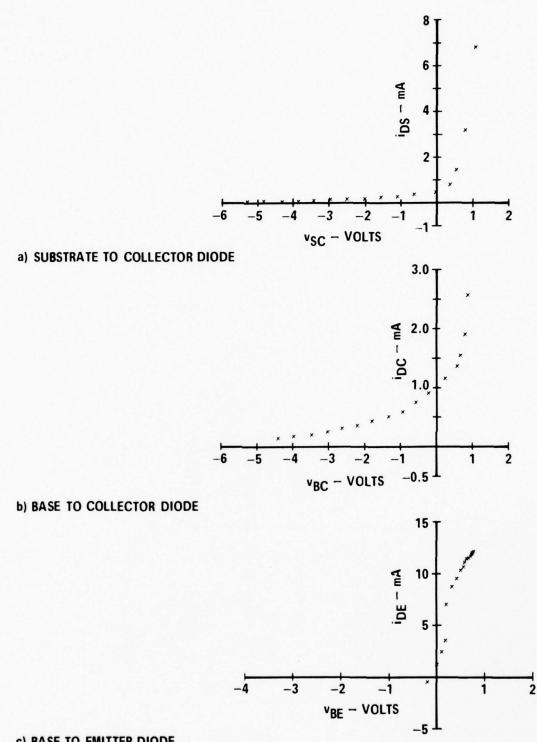

Rectification is possible in each of the three diode junctions. Using a procedure similar to that used to calculate transistor inferred diode curves, the three inferred diode curves were calculated for RF entering the collector terminal. Figure 32 shows the inferred diode curves for the no RF case. The substrate-collector and base-collector diodes look like typical diodes, while the base-emitter diode shows an unusual reverse conduction at voltages below its turn-on voltage. This is due to limitations in the model;  $\alpha_R$  may not be constant, or additional coupling terms may be necessary.

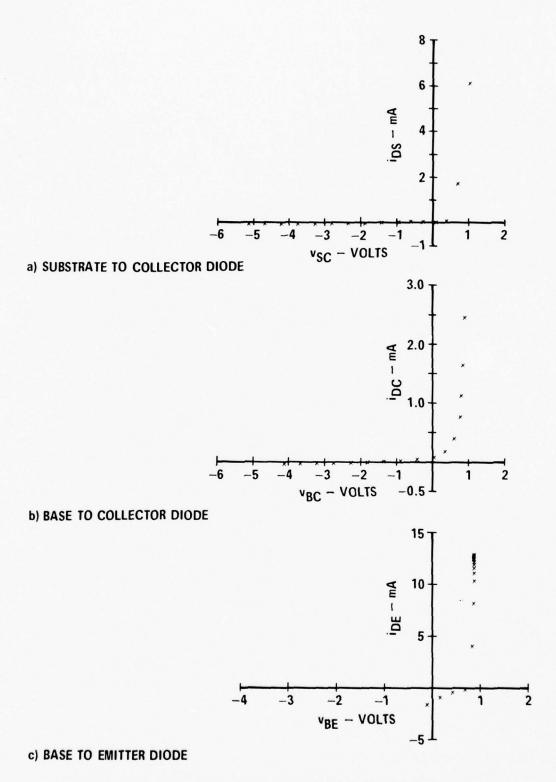

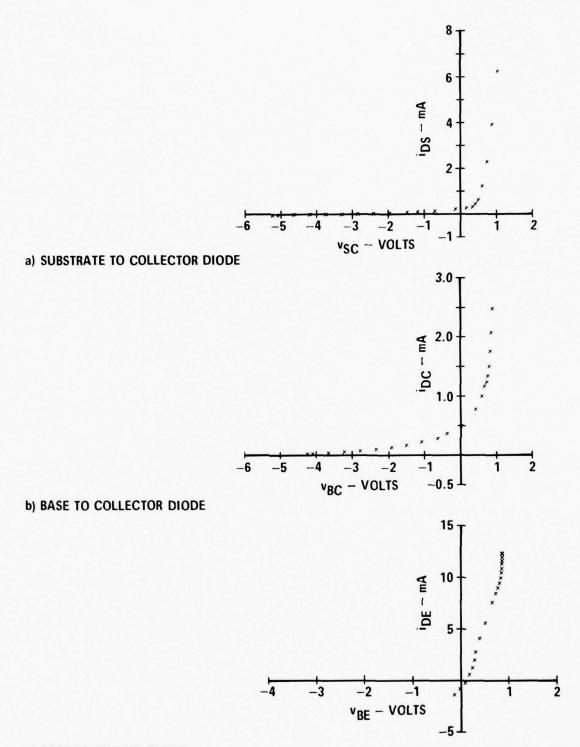

Figure 33 shows the inferred diode curves with 55 mW of RF power at 220 MHz entering the collector terminal. The curves are similar to those seen before for transistors, with the exception of the base-emitter diode which has an unusual "hump", again probably due to model limitations. Figure 34 shows the inferred diodes for 140 mW of 220 MHz RF power entering the collector, and they look similar to those for 55 mW.

51

52

Figure 32 Inferred Diode Curves for Monochip MO-001 Transistor With No RF

53

REPORT MDC E1667 3 JUNE 1977 -----

Tankar .

## c) BASE TO EMITTER DIODE

Figure 33 Inferred Diode Curves for Monochip MO-001 Transistor With 55 mW of RF Power at 220 MHz Conducted into the Collector

54

## c) BASE TO EMITTER DIODE

Figure 34 Inferred Diode Curves for Monochip MO-001 Transistor with 140 mW of RF Power at 220 MHz Conducted into the Collector

#### REPORT MDC E1667 3 JUNE 1977

These inferred curves suggest that the modified Ebers-Moll model for transistors can be extended to include a substrate junction by modeling the additional junction in the same manner as done before for the base-emitter and base-collector junctions. The proposed 4-layer modified model is shown in figure 35.

56

3.2.6 <u>Comments on Transistor Modeling</u> - The inferred diode curves obtained from a given transistor vary with transistor bias. For example, if the base current is changed, the inferred diode curves may also change. However, for small to moderate changes in transistor bias, the change in inferred diode curves is slight. Therefore, when modeling circuits using the modified Ebers-Moll transistor model (figure 22), the transistor parameters should be obtained at or near the transistor's operating point, for best accuracy.

The parameters  $R_C$ ,  $R_E$ ,  $X_C$ , and  $X_E$  (figure 22) can best be determined through the process described here: using transistor data to infer diode curves, from which the R and X parameters are obtained. However, we can estimate the expected range of these parameters. For the resistors  $R_C$  and  $R_E$ , lower values are seen at the lower frequencies, where the rectification is greatest; and larger values will occur at high frequencies where the rectification decreases due to diode capacitance.

The parameters  $X_{C}$  and  $X_{E}$  are essentially coupling factors which determine how much RF power is incident on each junction. Based on matching considerations, the expected range of  $X_{C}$  and  $X_{E}$  is from 0 to 1. The value of 0 indicates no RF power incident on the junction, while the value of 1 indicates a matched condition so that the maximum amount of RF power is incident on the junction. Table 4 summarizes the ranges of parameters.

3.3 <u>Modeling RF Effects in Integrated Circuits</u> - The semiconductor models developed earlier can be used to model RF effects in more complex circuits. Of special interest in this report is integrated circuit modeling. Integrated circuits typically contain many devices, including transistors, diodes, resistors, and capacitors, and their analysis can become quite complicated. For this reason, use can be made of any of several available computer programs intended for circuit analysis. These include CIRCUS, CORNAP, ECAP 2, NET 2, SCEPTRE, SLIC and SPICE.

57

1

|    | MINIMUM VALUE | MAXIMUM VALUE |

|----|---------------|---------------|

| RC | 5 Ω*          | ≈1/ωC −Ω      |

| RE | 5 Ω*          | ≈1/ωC-Ω       |

| ×c | 0             | 1             |

| XE | 0             | 1             |

Table 4 Ranges of Parameters in Modified Ebers-Moll Model

#### C = JUNCTION CAPACITANCE

$\omega$  = RADIAN FREQUENCY

\* = LOWER LIMIT IS SET BY LOSSES IN SYSTEM. VALUE SHOWN IS PROBABLE LOWER LIMIT.

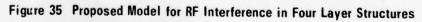

Modeling interference effects in integrated circuits is illustrated using SPICE in this report. The circuit investigated is the 7400 NAND gate, for the case when RF enters the output with the output low. This is its most susceptible configuration. The adaptation of the modified Ebers-Moll transistor model for SPICE is shown, while an RF effects model for the TTL output-low case is developed. 3.3.1 Computer-Aided Analysis of ICs with SPICE - SPICE<sup>10</sup>, an acronym for Simulation Program with Integrated Circuit Emphasis, is a versatile, general purpose circuit analysis program. It performs dc analysis, ac analysis, and transient analysis of linear or non-linear electronic circuits. Two versions are in use: SPICE1 has been available since 1972; SPICE2 is an improved version that has been available since 1975. The program is written in FORTRAN IV, and contains approximately 13,000 statements. Versions are available for several large computers, notably the CDC 6400 and the IBM 360. SPICE can be obtained from Prof. D. O. Pederson, c/o University of California at Berkeley, for handling charges only. A time-sharing version, ISPICE, is available commercially from National CSS, Norwalk, Connecticut.

58

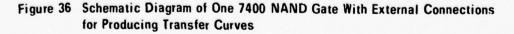

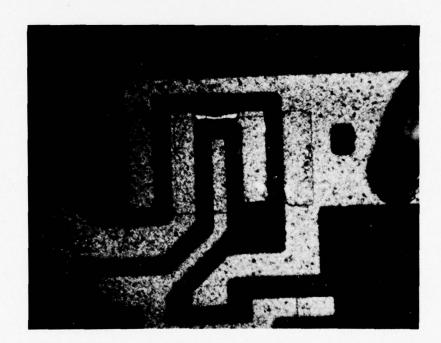

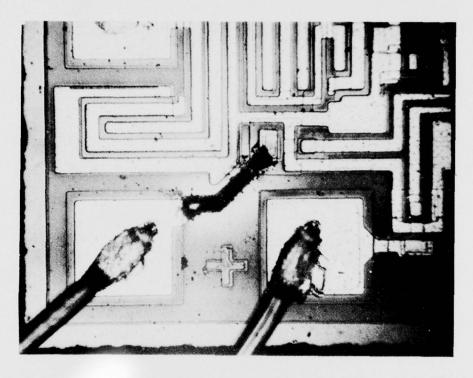

A schematic diagram of the 7400 NAND gate is shown in figure 36. The NAND gate is contained within the dashed box, and consists of 4 transistors (T1, T2, T3, and T4), 3 diodes (D1, D2, and D3), and 4 resistors (R1, R2, R3, and R4). Voltage sources  $V_{IN}$  and  $V_{CC}$ , and resistors  $R_L$  and  $R_{LL}$  simulate the external circuitry used in the 7400 NAND gate susceptibility testing. Information on element parameters was obtained from reference 11. The element values were measured from an actual 7400 by probing on the chip. The values obtained for resistors R1 through R4 are listed in table 5. The parameters measured for transistors T1 through T4 were not in a form immediately usable for SPICE, but were converted to a form suitable for SPICE.

| Table 5 Values of Resistors in 7400 WAND Gate |                  |  |  |  |

|-----------------------------------------------|------------------|--|--|--|

| RESISTOR                                      | VALUE            |  |  |  |

| R1                                            | 4.38Κ Ω          |  |  |  |

| R2                                            | 1.43K Ω          |  |  |  |

| R3                                            | <b>0.116</b> Κ Ω |  |  |  |

| R4                                            | <b>1.06K</b> Ω   |  |  |  |

|                                               |                  |  |  |  |

ups of Pasistors in 7400 NAND Gate

The measured parameters for T1 through T4 are for an Ebers-Moll transistor model as shown in figure 16. The collector and emitter currents are

$$i_{C} = \alpha_{F}i_{F} - i_{R}$$

<sup>(2)</sup>

$$i_{\rm E} = \alpha_{\rm R} i_{\rm R} - i_{\rm F} \tag{3}$$

where

$$i_F = [I_{ES}/(1 - \alpha_F^{\alpha}R)][exp (qv_{BE}/M_EkT) - 1)$$

(4)

$$i_{R} = [I_{CS}/(1 - \alpha_{F}\alpha_{R})][exp (qv_{BC}/M_{C}kT) - 1]$$

(5)

where  ${\rm I}_{\rm FS}$  - emitter-base diode saturation current

$\mathbf{I}_{\text{CS}}$  - collector-base diode saturation current

$v_{BF}$  - base-emitter voltage

$\alpha_{F}$  - common base normal mode dc current gain

$\boldsymbol{\alpha}_{\mathsf{R}}$  - common base inverted mode dc current gain

q - electron charge

k - Boltzmann's constant

T - junction absolute temperature in  $^\circ {\rm K}$

${\rm M}_{\rm E}$  - emission constant for emitter-base diode

$M_{\rm C}$  - emission constant for collector-base diode.

60

Values for the parameter elements  $I_{ES}$ ,  $I_{CS}$ ,  $\alpha_R$ ,  $\alpha_F$ ,  $M_E$ , and  $M_C$  for the four transistors in the NAND gate are summarized in table 6. Also given in table 6 are the diode saturation currents  $I_{SD}$  and emission coefficients  $M_D$  for the input diodes (D1 and D2 are assumed identical, and are called DIN in table 6), and for diode D3. The dc diode current  $i_D$  is given by

$$i_{D} = I_{SD}[exp (qv_{D}/M_{D}kT) - 1]$$

(6)

where  $\boldsymbol{v}_{D}$  - dc voltage across the diode

I<sub>SD</sub> - diode saturation current

$\rm M_{\rm D}$  - emission constant for diode.

| PARAMETER            | T1     | T2    | T3    | T4     | DIN  | D3   |

|----------------------|--------|-------|-------|--------|------|------|

| I <sub>ES</sub> (pA) | 2      | 3     | 8     | 20     | -    | -    |

| ICS (pA)             | 200    | 50    | 100   | 200    | -    | -    |

| I <sub>SD</sub> (pA) | -      | -     | -     | -      | 100  | 5    |

| ME                   | 1.70   | 1.70  | 1.67  | 1.80   | -    | -    |

| MC                   | 1.84   | 1.74  | 1.80  | 1.71   | -    | -    |

| MD                   | -      | -     | -     | -      | 1.64 | 1.31 |

| ۹F                   | 0.24   | 0.952 | 0.945 | 0.956  | -    | -    |

| ۳R                   | 0.0024 | 0.057 | 0.076 | 0.0956 | -    | -    |

| Table 6 | Summary of Ebers-Moll Parameter Values for the 7400 NAND Gate |

|---------|---------------------------------------------------------------|

|         | Transistors and Diodes from Reference 9                       |

The simulation program SPICE also has an Ebers-Moll model available for bipolar junction transistors. The SPICE Ebers-Moll model equations for the dc collector current  $i_{\rm C}$  and dc base current  $i_{\rm B}$  of an npn transistor are

$$i_{C} = I_{S}\left[\exp\left(\frac{qv_{BE}}{kT}\right) - \exp\left(\frac{qv_{BC}}{kT}\right)\right] \left[1 - \frac{v_{BC}}{V_{A}}\right] - \frac{I_{S}}{\beta_{r}}\left[\exp\left(\frac{qv_{BC}}{kT}\right) - 1\right]$$

(7)

61

REPORT MDC E1667 3 JUNE 1977

$$i_{B} = \frac{I_{S}}{\beta_{f}} \left[ \exp\left(\frac{qv_{BE}}{kT}\right) - 1 \right] + \frac{I_{S}}{\beta_{r}} \left[ \exp\left(\frac{qv_{BC}}{kT}\right) - 1 \right]$$

(8)

where q, k, and T have the definitions given previously and

$\boldsymbol{v}_{\text{BF}}$  is the base to emitter voltage,

$v_{BC}$  is the base to collector voltage,

- $\beta_{f}$  is the forward current gain,

- $\boldsymbol{\beta}_r$  is the reverse current gain,

- $I_{S}$  is the saturation current,

- $V_A$  is the Early voltage.

The values of  $I_S$ ,  $B_f$  and  $B_r$  are supplied by the user. The SPICE Ebers-Moll model also includes parasitic resistances  $R_E$ ,  $R_B$ , and  $R_C$  in series with the emitter, base, and collector terminals, respectively. If it is assumed that the Early voltage,  $V_A$ , takes on the default value of  $\infty$ , and that  $M_C$  and  $M_E$  equal 1 in equations (4) and (5), and the SPICE equations for  $i_C$  and  $i_B$  are substituted in equations (2) and (3), where

$-i_{E} = i_{B} + i_{C}$

the following relationships are obtained

$$I_{S} = \left[\alpha_{F}/(1 - \alpha_{F}\alpha_{R})\right] I_{ES}$$

(9)

$$\beta_{f} = \frac{\alpha_{FR}}{1 - \alpha_{F}}$$

(10)

$$\beta_r = \frac{\alpha_F}{1 - \alpha_R} . \tag{11}$$

From equations (9) through (11) and the values for  $I_{ES}$ ,  $\alpha_F$ , and  $\alpha_R$  given in table 6, the values for  $I_S$ ,  $\beta_f$ , and  $\beta_r$  were calculated for the four transistors in the 7400 NAND gate. These values are given in table 7. Also given in table 7 are non-zero values for the parasitic series base resistance  $R_B$ , and the default values used in SPICE for other transistor parameters which have not been discussed.

62

1

| PARAMETER | <u>11</u> | <u>12</u> | <u>T3</u> | <u></u>  | DIN    | <u>D3</u> |

|-----------|-----------|-----------|-----------|----------|--------|-----------|

| BF        | 0.316     | 19.8      | 17.2      | 21.7     |        |           |

| BR        | 0.0024    | 0.060     | 0.082     | 0.106    |        |           |

| RB        | 68.       | 75.       | 70.       | 80.      |        |           |

| RC        | 0         | 0         | 0         | 0        |        |           |

| RE        | 0         | 0         | 0         | 0        |        |           |

| CCS       | 0         | 0         | 0         | 0        |        |           |

| TF        | 0         | 0         | 0         | 0        |        |           |

| TR        | 0         | 0         | 0         | 0        |        |           |

| CJE       | 0         | 0         | 0         | 0        |        |           |

| CJC       | 0         | 0         | 0         | 0        |        |           |

| IS        | 0.5pA     | 3.pA      | 8.pA      | 20.pA    | 100.pA | 5.pA      |

| PE        | 1         | 1         | 1         | 1        |        |           |

| PC        | 1         | 1         | 1         | 1        |        |           |

| VA        | $\infty$  | $\infty$  | $\infty$  | $\infty$ |        |           |

| EG        | 1.11      | 1.11      | 1.11      | 1.11     | 1.11   | 1.11      |

| RS        |           |           |           |          | 60.    | 30.       |

| TT        |           |           |           |          | 0.     | 0.        |

| CJO       |           |           |           |          | 0.     | 0.        |

| N         |           |           |           |          | 1.     | 1.        |

| PHI       |           |           |           |          | 1.     | 1.        |

# Table 7 Parameter Values for the Transistors and Diodes in the 7400 NAND Gate for the SPICE Simulation

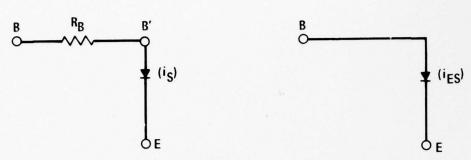

The procedure for calculating the values of  $R_B$  given in table 7 requires some additional explanation. Shown in figure 37 is the emitter-base junction of the Ebers-Moll model (figure 16) and the emitter-base junction of the SPICE Ebers-Moll model shown with the base resistance  $R_B$ .

From the SPICE model equations (7) and (8) with  $V_A = \infty$  and  $qv_{BC}/kT << 0$  and assuming  $\beta_F^{>>1}$ , the equation for the dc base-emitter voltage  $v_{BE}$  is

$$v_{BE} \approx (-i_E) R_B + (kT/q) \ln[-i_E/I_S].$$

(12)

From equations (2) through (5), assuming  $qv_{BC}^{/kT<<0}$  and assuming  $\beta_{f}^{>>1}$ , the dc base-emitter voltage  $v_{BE}^{}$  is

$$v_{BE} \approx (M_F kT/q) \ln [-i_F/I_{FS}].$$

(13)

63

From SPICE Ebers-Moll Model

Figure 37 Base-Emitter Junctions of Ebers-Moll and SPICE Ebers-Moll Transistor Models

By equating equations (12) and (13), the following equation is obtained for  $R_B$ :  $R_B = \frac{kT}{q(-i_E)} \left[M_E \ln \frac{(-i_E)}{I_{ES}} - \ln \frac{(-i_E)}{I_S}\right].$ (14)

Using the values for  $M_E$ ,  $I_{ES}$  and  $I_S$  given in tables 6 and 7,  $R_B$  was evaluated at  $i_F = -5 \text{ mA}$  and T = 27°C to obtain the values listed in table 7.

Also listed in table 7 are the diode parameters for diodes DIN and D3. The diode model equation in SPICE is

$$i_{D} = I_{S}[exp (\frac{qv_{D}}{nkT}) - 1]$$

(15)

From Ebers-Moll Model

where  $i_D$  and  $v_D$  are the diode current and voltage. Setting  $I_S = I_{SD}$  and the emission constant, n = 1 (rather than  $M_D$ ), the values of the diode parasitic series resistance  $R_S$  was obtained by using an equation similar to equation (14), which was evaluated at  $i_D = 5$  mA and T = 300°K. The values obtained for  $R_S$  are listed in table 7.

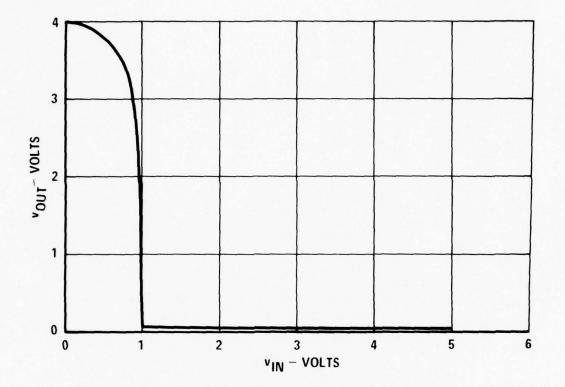

The NAND gate operation was tested for normal operation (no RF) by obtaining a dc transfer curve using SPICE. In modeling the NAND gate circuit, figure 36, it was assumed that transistor Tl has only a single emitter, and that diodes Dl and D2 were replaced by a single diode, DIN, in order to simplify the modeling.

Circuit elements are specified in SPICE by numbering the nodes in the circuit and specifying to which node each element is connected along with the element parameters. The node numbers used in the 7400 simulation are shown in figure 36.

64

As an example of specifying circuit elements, consider resistor R1. The input statement to place R1 in the circuit is

#### R1 9 2 4.38K

which tells that resistor R1 is connected between nodes 9 and 2, and that its value is 4.38K ohms. Transistors are inserted with a statement similar to the following statement for T1,

## QT1 3 2 1 MOD1

which indicates that transistor Tl (now only a single emitter transistor) has its collector, base, and emitter connected to nodes 3, 2, and 1 respectively, and that it is of transistor model type "MOD1". A separate statement defines the parameters of each model type. Transistors of type MOD1 are defined by

.MODEL MODI NPN 0.316 0.0024 68 IS = 5E - 13 which indicates that model MODI is an npn transistor with  $\beta_f = 0.316$ ,  $\beta_r = 0.0024$ ,  $R_B = 68$  ohms, and  $I_S = 5 \times 10^{-13}$  amps. Similar statements are used to insert the other elements used in the model, which includes voltage sources and diodes. See reference 10 for complete information on SPICE input statements.

Figure 38 shows the input statements required to obtain a transfer curve of the NAND gate. Resistors  $R_L$  and  $R_{LL}$  were set to  $200\Omega$  and  $9100\Omega$  to agree with their values during testing of the 7400. The dc control card

.DC TC VIN 0 5 0.05

causes the dc input voltage VIN to be stepped from 0 to 5 volts in 0.05 volt steps. The output card

## .OUT VOUT 8 0 PRINT DC PLOT DC

causes the dc output voltage between nodes 8 and 0 to be printed and plotted versus the dc input voltage VIN between nodes 1 and 0. The SPICE simulation values for  $V_{\rm OUT}$  vs  $V_{\rm IN}$  are plotted in figure 39. The transfer curve compares favorably with typical curves given by 7400 NAND gate manufacturers.

|                                   |     | •  |                                   |  |

|-----------------------------------|-----|----|-----------------------------------|--|

| VIN                               | 1   | 0  |                                   |  |

| VCC                               | 9   | 0  | DC 5                              |  |

| R1                                | 9   | 2  | 4.38K                             |  |

| R2                                | 9   | 4  | 1.43K                             |  |

| R3                                | 9   | 6  | 0.116K                            |  |

| R4                                | 5   | 0  | 1.06K                             |  |

| RL                                | 1   | 0  | 0.2K                              |  |

| RLL                               | 8   | 0  | 9.11K                             |  |

| QT1                               | 3   | 2  | 1 MOD1                            |  |

| QT2                               | 4   | 3  | 5 MOD2                            |  |

| QT3                               | 6   | 4  | 7 MOD3                            |  |

| QT4                               | 8   | 5  | 0 MOD4                            |  |

| DIN                               | 0   | 1  | MOD5                              |  |

| D3                                | 7   | 8  | MOD6                              |  |

| • MOE                             | DEL | MO | D1 NPN 0.316 0.0024 68 IS = 5E-13 |  |

| • MOD                             | DEL | MO | D2 NPN 19.8 0.060 75 IS = 3E-12   |  |

| . MOD                             | DEL | MO | D3 NPN 17.2 0.082 70 IS = 8E-12   |  |

| . MOD                             | DEL | MO | D4 NPN 21.7 0.106 80 IS = 2E-11   |  |

| • MODEL MOD5 D RS = 60 IS = 1E-10 |     |    |                                   |  |

|                                   |     |    | D6 D RS = 30 IS = 5E-12           |  |

| 101010-002                        |     |    | 0 5 0.05                          |  |

|                                   |     |    | OUT 8 0 PRINT DC PLOT DC          |  |

|                                   |     |    | JULO U PRINT DE PLUT DE           |  |

| <ul> <li>TEMI</li> </ul>          |     | )  |                                   |  |

| <ul> <li>END</li> </ul>           |     |    |                                   |  |

|                                   |     |    |                                   |  |

## Figure 38 Data Cards for Generating DC Transfer Curve for 7400 NAND Gate Using SPICE

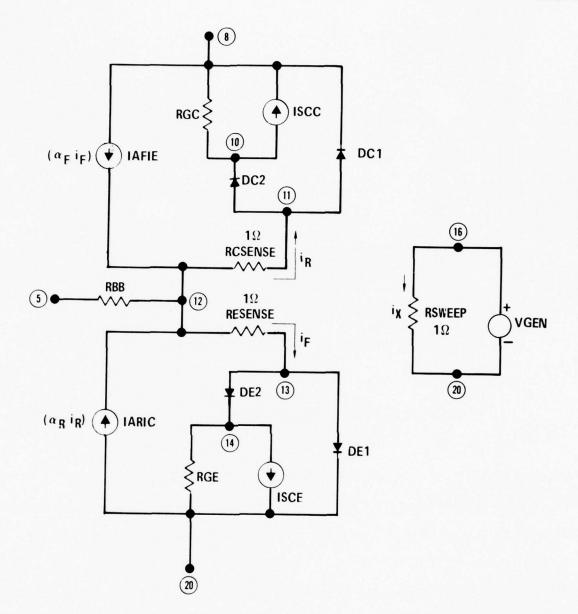

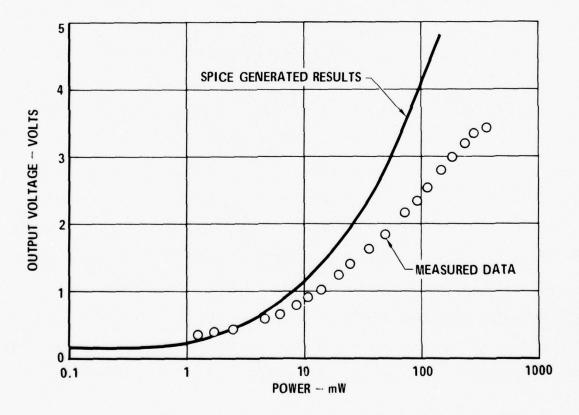

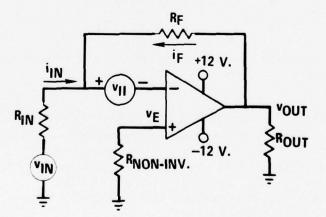

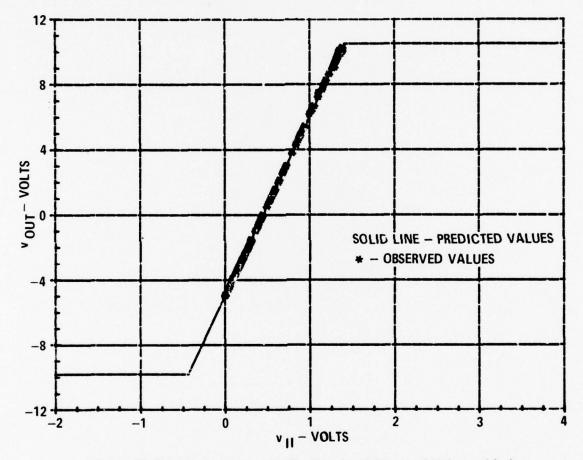

3.3.2 <u>Adaptation of Modified Ebers-Moll Transistor for Use with SPICE</u> - When RF energy is conducted into the NAND gate output, with output low, it is postulated that most of the interference effects occur in the output transistor, T4. In this case, the RF energy enters the collector of T4. The RF effects produced can be accounted for in the 7400 model by replacing the output transistor with the modified Ebers-Moll model shown earlier in figure 22.

Examination of transistor T4 on a 7400 chip revealed that it is similar in geometry to a 2N2369A transistor. The modified Ebers-Moll model for RF effects in a 2N2369A was thus chosen to replace transistor T4 in the NAND gate simulation in order to account for RF effects. The modified Ebers-Moll model parameters for

66

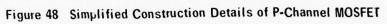

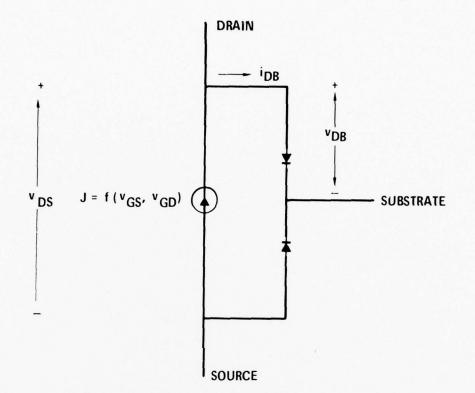

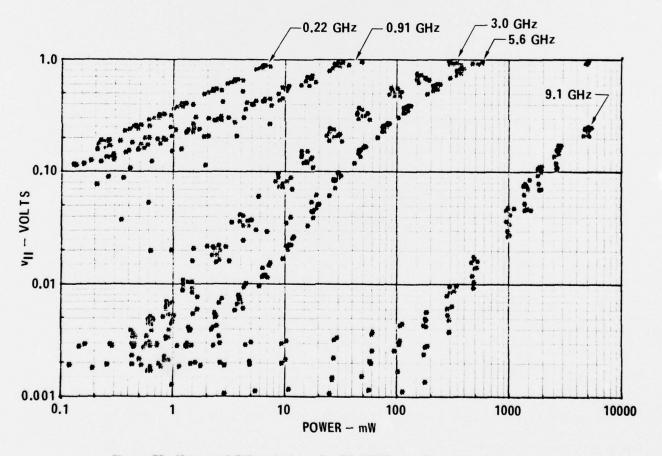

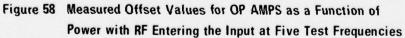

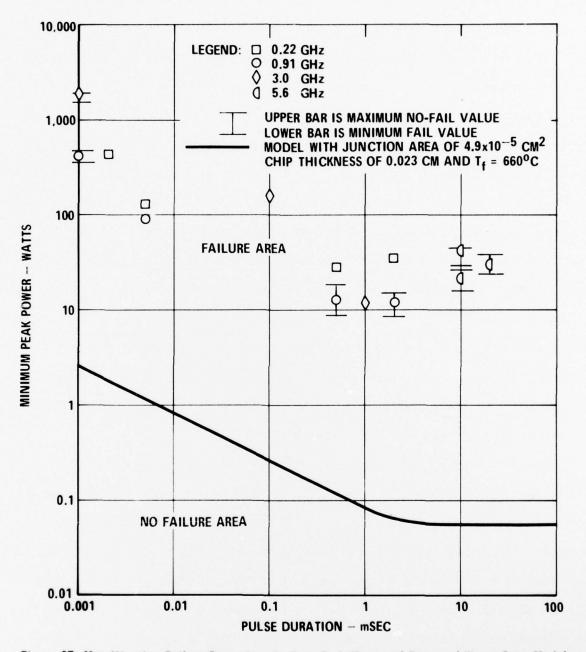

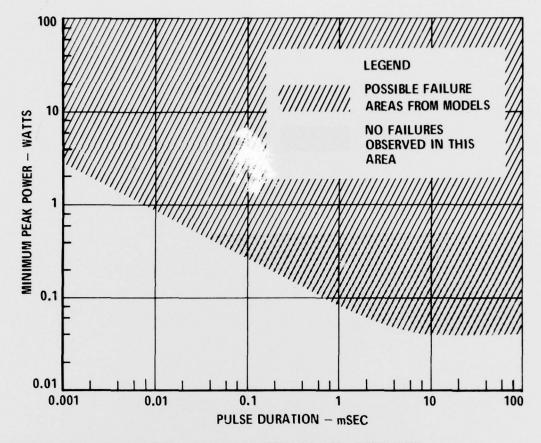

Figure 39 SPICE Simulation of 7400 NAND Gate Transfer Curve