**DNA 4130F**

# SCAN CONVERTER FOR LIQUID WATER CONTENT ANALYZER Raytheon Company Boston Post Road Wayland, Massachusetts 01778

Wayland, Massachusetts 01778

July 1975

Final Report

CONTRACT No. DNA 001-75-C-0050

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

THIS WORK SPONSORED BY THE DEFENSE NUCLEAR AGENCY UNDER RDT&E RMSS CODE X342075469 Q93HAXYX97503 H2590D.

> COPY AVAILABLE TO DOG DOES NOT PERMIT FULLY LEGISLE PROBLECTION

Prepared for Director DEFENSE NUCLEAR AGENCY Washington, D. C. 20305

There was a series of the seri

Destroy this report when it is no longer needed. Do not return to sender.

SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered)

| (19) REPORT DOCUMENTATION                                                                                                                                                                     | PAGE                                                                                | READ INSTRUCTIONS BEFORE COMPLETING FORM                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 1. REPORT NUMBER                                                                                                                                                                              | 2. GOVT ACCESSION NO.                                                               | 3. RECIPIENT'S CATALOG NUMBER                                                                                                 |

| DNA 4130F                                                                                                                                                                                     |                                                                                     |                                                                                                                               |

| 4, TITLE (and Subtitle)                                                                                                                                                                       |                                                                                     | 5. TYPE OF REPORT & PERIOD COVERED                                                                                            |

| SCAN CONVERTER FOR LIQUID WA                                                                                                                                                                  | TER 9                                                                               | Final Report                                                                                                                  |

| CONTENT AMERICA                                                                                                                                                                               | TI                                                                                  | 6. PERFORMING ORG. REPORT NUMBER ER75-4332                                                                                    |

| 7. AUTHOR(s)                                                                                                                                                                                  |                                                                                     | B. CONTRACT OR GRANT NUMBER(s)                                                                                                |

| A. J. Jagodnik<br>L. R. Novick<br>J. H. Turner                                                                                                                                                | 0                                                                                   | DNA 001-75-C-0050                                                                                                             |

| 9. PERFORMING ORGANIZATION NAME AND ADDRESS                                                                                                                                                   |                                                                                     | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS                                                                |

| Raytheon Company<br>Boston Post Road                                                                                                                                                          |                                                                                     | Subtask Q93HAXYX975-03                                                                                                        |

| Wayland, Massachusetts 01778                                                                                                                                                                  |                                                                                     | Subtask Q3311AA1 A373-03                                                                                                      |

| 11. CONTROLLING OFFICE NAME AND ADDRESS                                                                                                                                                       |                                                                                     | 12. REPORT DATE                                                                                                               |

| Director                                                                                                                                                                                      | (11)                                                                                | July 1975                                                                                                                     |

| Defense Nuclear Agency                                                                                                                                                                        |                                                                                     | 13. NUMBER OF PAGES                                                                                                           |

| Washington, D.C. 20305                                                                                                                                                                        |                                                                                     | 138                                                                                                                           |

| 14 MONITORING AGENCY NAME & ADDRESS(if differen                                                                                                                                               | t from Controlling Office)                                                          | 15. SECURITY CLASS (of this report)                                                                                           |

| (12)                                                                                                                                                                                          | 129 1                                                                               | UNCLASSIFIED                                                                                                                  |

| Q                                                                                                                                                                                             | 129p.                                                                               | 15a. DECLASSIFICATION DOWNGRADING                                                                                             |

| Sarye                                                                                                                                                                                         |                                                                                     | SCHEDULE                                                                                                                      |

| 16. DISTRIBUTION STATEMENT (of this Report)                                                                                                                                                   |                                                                                     |                                                                                                                               |

| Approved for public release; distrib                                                                                                                                                          |                                                                                     | m Report) AUG 18 1977                                                                                                         |

| 17. DISTRIBUTION STATEMENT (of the abstract entered                                                                                                                                           | in Block 20, if different fro                                                       | M Report) (1 AUS                                                                                                              |

| 18. SUPPLEMENTARY NOTES                                                                                                                                                                       |                                                                                     |                                                                                                                               |

| This work sponsored by the Defense X342075469 Q93HAXYX97503 H2590                                                                                                                             |                                                                                     | under RDT&E RMSS Code                                                                                                         |

| 19. KEY WORDS (Continue on reverse side if necessary ar                                                                                                                                       | nd identify by block number)                                                        |                                                                                                                               |

| Scan Converter                                                                                                                                                                                | Memory Int                                                                          | terface Unit                                                                                                                  |

| Liquid Water Content Analysis                                                                                                                                                                 | Cursor                                                                              |                                                                                                                               |

| Coordinate Converter                                                                                                                                                                          | Trackball                                                                           | 내기 왕내는 것이 내가 되었다면서                                                                                                            |

| Display Data Interface                                                                                                                                                                        |                                                                                     |                                                                                                                               |

| Angle Interface Unit                                                                                                                                                                          |                                                                                     |                                                                                                                               |

| 20. ABSTRACT (Continue on reverse side if necessary an                                                                                                                                        |                                                                                     | intenfece between an                                                                                                          |

| This report describes the work<br>Interdata 7/32 used as an analysis to<br>density along a rocket trajectory and<br>memory system developed as a tool<br>hardware description of the scan con | ool for the determ<br>d a digital scan co<br>for radar meteor<br>nverter and contou | ination of liquid water content<br>nverter and contour refresh<br>ological studies. A complete<br>or refresh memory system as |

| modified for operation with the Inter                                                                                                                                                         | rdata 7/32 is provi                                                                 | ded.                                                                                                                          |

DD FORM 1473 EDITION OF 1 NOV 65 IS OBSOLETE

UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered)

298 350

|       | UNCLASSIFIED                                |        |

|-------|---------------------------------------------|--------|

| SECUE | TY CLASSIFICATION OF THIS PAGE(When Data En | tered) |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

|       |                                             |        |

| 1     |                                             |        |

|       |                                             |        |

|       |                                             |        |

UNCLASSIFIED

SECURITY CLASS FICATION OF THIS PAGE(When Data Entered)

# TABLE OF CONTENTS

| Section                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                                                                |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                              | INT RODUCTION ACCESSION For                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-1-1                                                                                                               |

| 2<br>2.1<br>2.2<br>2.3<br>2.4                                                                                  | GENERAL DESCRIPTION Scan Conversion Processor Memory Interface Units Memories Displays                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-1<br>2-1<br>2-3<br>2-3<br>2-3                                                                                     |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                                                      | OPERATION Display Adjustment Contour Threshold Entry Mode and Range Cell Width Selection Scaling and Location of the Origin Marker Spacing Selection Time Code Crosshatch Liquid Water Content Analysis                                                                                                                                                                                                                                                                                                                                     | 3-1<br>3-1<br>3-3<br>3-3<br>3-4<br>3-4<br>3-4<br>3-4                                                                |

| 3.8 4 4.1 4.2 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.2.9 4.2.10 4.3 4.3.1 4.3.2 4.4 4.5 4.5.1 4.5.2 | Liquid Water Content Analysis  DETAILED CIRCUIT DESCRIPTION  Angle Interface Unit Coordinate Converter Angle Parameters Fixed Constant Multipliers PPI Mode - True 12 x 12 Multipliers Address Accumulators - Cards 2 and 3 Range and Altitude Markers CAPPI Mode Coordinate Converter/Integrator Interface Synchronizer Angle Interface Timing Earth Curvature Correction Display Control Unit Timing and Control Logic Ancillary Data Formatter Video Distribution Unit Memory Interface Units Memory Cycles Parallel-to-Serial Converter | 4-1<br>4-2<br>4-2<br>4-2<br>4-4<br>4-4<br>4-5<br>4-5<br>4-8<br>4-13<br>4-13<br>4-13<br>4-13<br>4-18<br>4-18<br>4-18 |

| 4.5.3<br>4.5.4<br>4.5.5<br>4.5.6<br>4.5.7<br>4.5.8                                                             | Color Encoder Modify/Restore Logic, Register and Multiplexers Contour Generator Write Data and Read Data Busses Cursor Interface Full-Screen Operation                                                                                                                                                                                                                                                                                                                                                                                      | 4-23<br>4-23<br>4-26<br>4-27<br>4-27                                                                                |

# TABLE OF CONTENTS (CONTINUED)

| Section                                                                     |                                                                                                                                                                                                     |                                           | Page |  |  |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------|--|--|

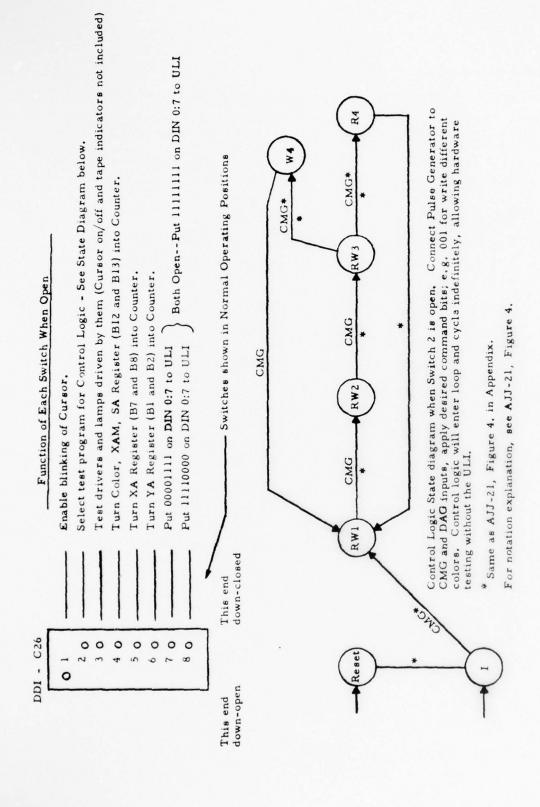

| 4.6<br>4.6.1<br>4.6.2<br>4.6.3<br>4.6.4<br>4.6.5<br>4.6.6<br>4.6.7<br>4.6.8 | Display Data Interface and LWCA Control Panel Cursor Position Cursor Generation Full-Screen Enable Address Multiplexer LWCA-DISPLAY Controls Computer Interface Data Transfers Hardware Test Switch |                                           |      |  |  |

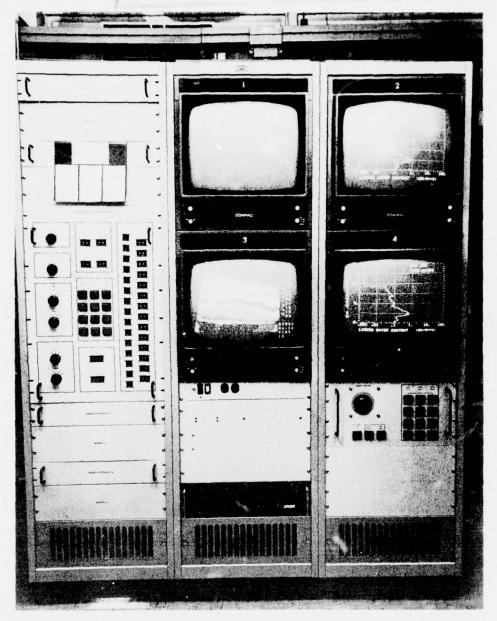

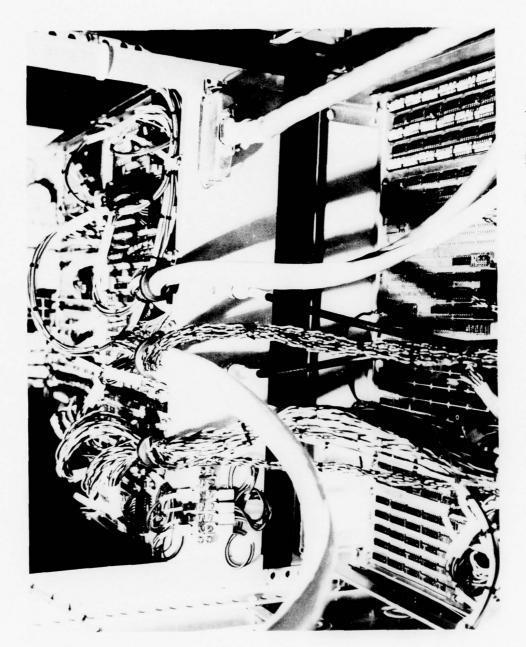

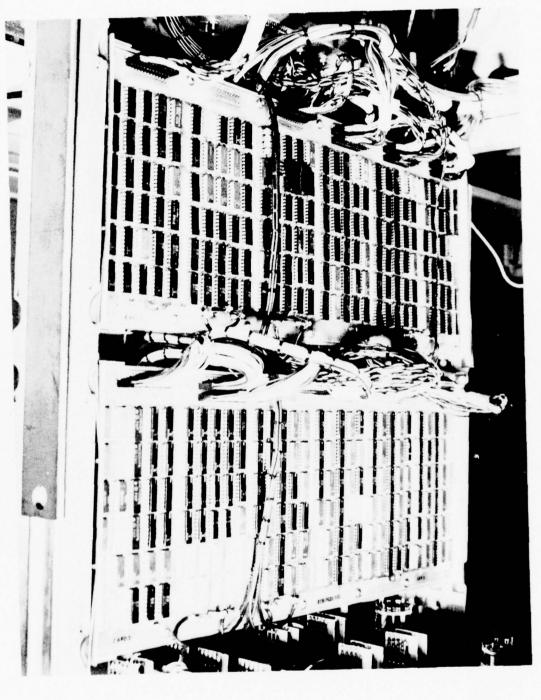

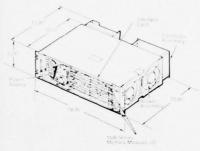

| APPENDIX                                                                    | A                                                                                                                                                                                                   | Scan Converter Photographs                | A-1  |  |  |

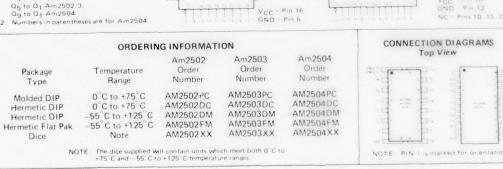

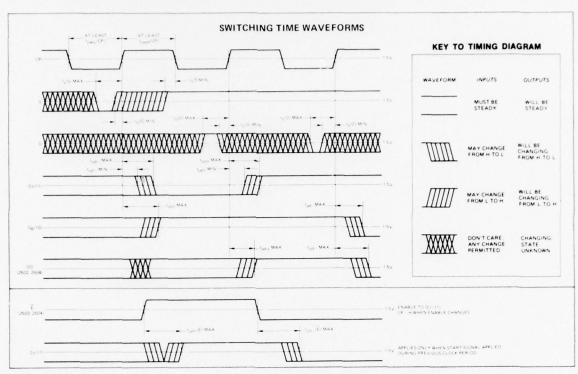

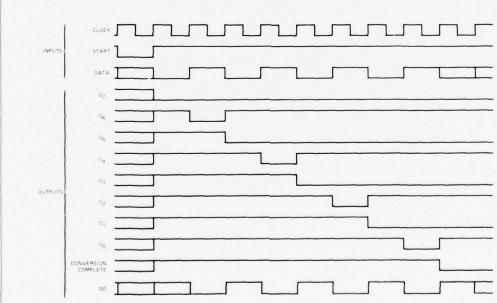

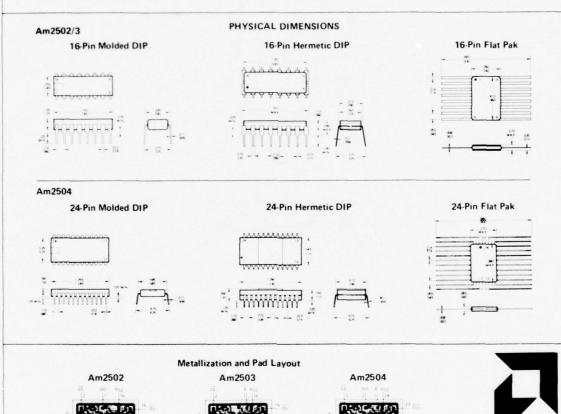

| APPENDIX                                                                    | В                                                                                                                                                                                                   | Product Information on Sub-System Modules | B-1  |  |  |

| APPENDIX                                                                    | С                                                                                                                                                                                                   | Read-Only-Memory Truth Tables             | C-1  |  |  |

| APPENDIX                                                                    | D                                                                                                                                                                                                   | Memoranda                                 | D-1  |  |  |

# LIST OF ILLUSTRATIONS

| Figure |                                                          | Page |

|--------|----------------------------------------------------------|------|

| 2-1    | Scan Converter Block Diagram                             | 2-2  |

| 3-1    | Scan Conversion Processor Front Panel                    | 3-2  |

| 4-1    | Coordinate Converter Block Diagram                       | 4-3  |

| 4-2    | CAPPI Address Selection                                  | 4-7  |

| 4-3    | Timing Interface for Coordinate Converter and Integrator | 4-9  |

| 4-4    | Integrator Coordinate Converter Timing Waveforms         | 4-10 |

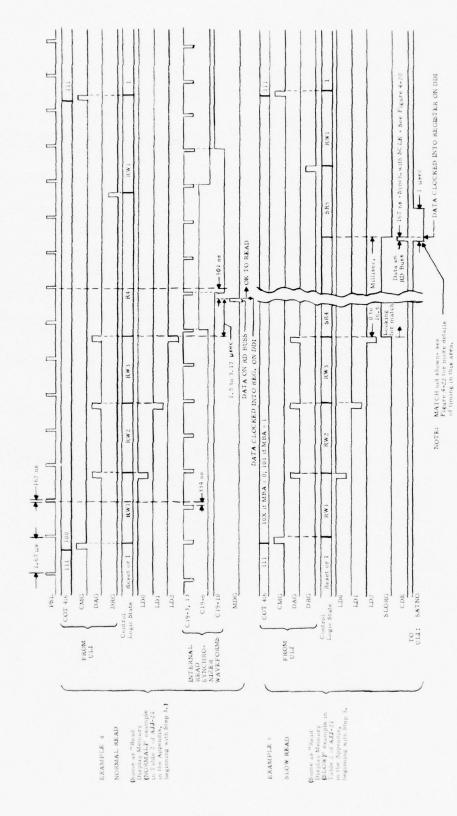

| 4-5    | Coordinate Converter Memory Buffer Timing Waveforms      | 4-11 |

| 4-6    | Earth Curvature Correction Term                          | 4-14 |

| 4-7    | DCU Block Diagram                                        | 4-15 |

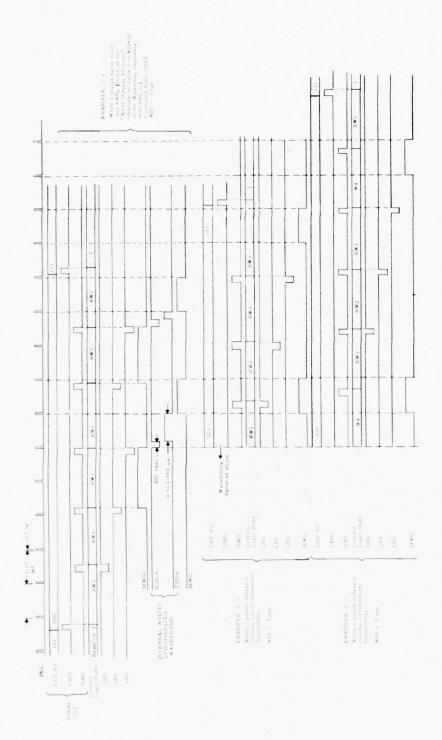

| 4-8    | Display Format and Timing Diagram                        | 4-16 |

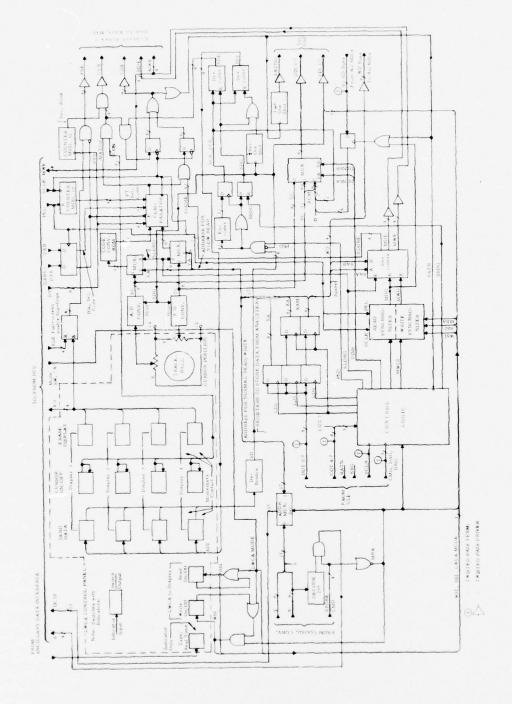

| 4-9    | Memory Interface Block Diagram                           | 4-20 |

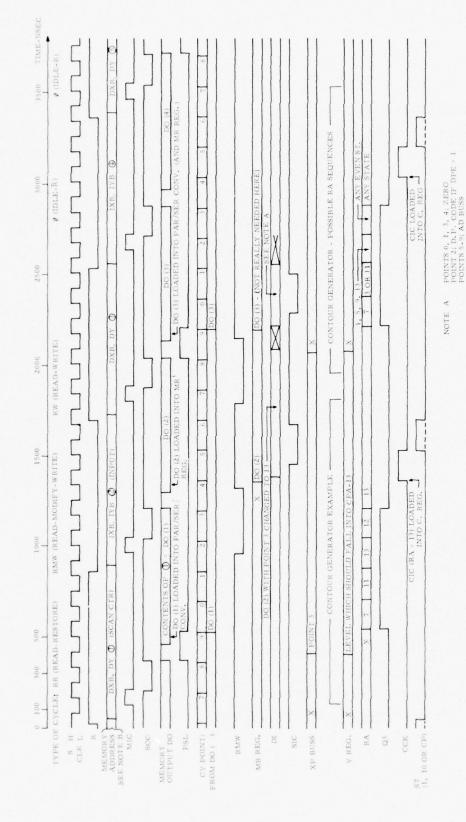

| 4-10   | Memory Interface Timing Diagram                          | 4-21 |

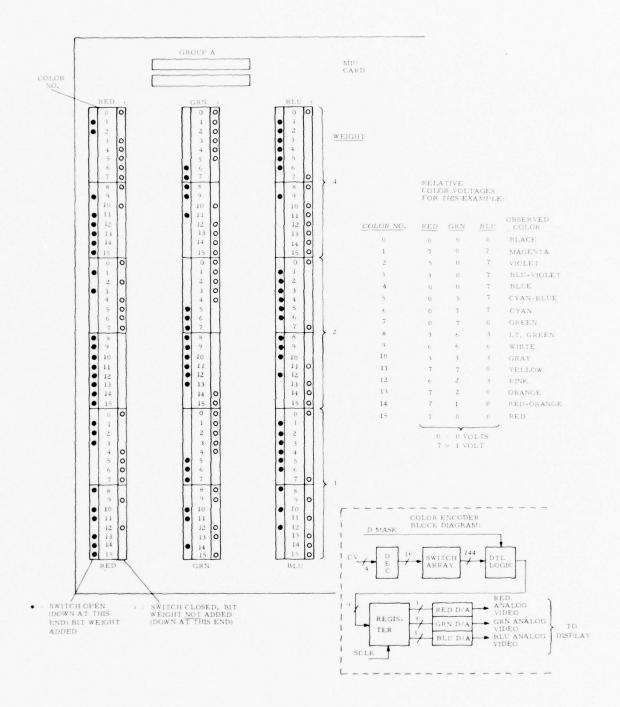

| 4-11   | Color Encoder Switches and Block Diagram                 | 4-24 |

| 4-12   | LWCA Control Panel and DDI Block Diagram                 | 4-28 |

| 4-13   | Write Timing                                             | 4-34 |

| 4-14   | Read Timing                                              | 4-36 |

| 4-15   | Cursor Data Entry Timing                                 | 4-38 |

| 4-16   | Hardware Test Switch                                     | 4-40 |

### SECTION 1. INTRODUCTION

This equipment converts the polar-coordinate outputs of a weather radar and signal processor to cartesian-coordinate form, contours the video, then stores the resulting data in four independent image-oriented memories, each of which refreshes one raster-scan color television monitor.

The most significant advantage of this system over conventional monochrome radar-image-storage devices lies in the ability of the operator to unambiguously recognize sixteen color-coded levels. Stored images of RHI or PPI radar scans can be retained indefinitely, updated, or erased independently of each other. When used with an appropriate radar scanning sequence, the system generates a constant altitude PPI (CAPPI) display for each of four selectable altitudes. Other front-panel controls determine distance scaling, origin location, range and altitude marker spacing and range cell width. Contour threshold colors - 0 (black) thru 15 (red) and levels (0 thru 99) having been set up on an array of thumbwheel switches can be entered into any or all of the displays in the form of a legend or color key.

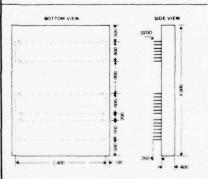

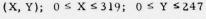

Memory requirements have been limited to about 328,000 bits per display by performing operations such as coordinate conversion, scaling, translation, introduction of markers, and video contouring prior to storage of the image. Each of the four memories contains a 248 x 255 array with a four-bit code to represent the color and/or intensity of individual points. In addition, the contour threshold colors and levels as well as parameters such as antenna angle, marker spacing, and time are presented within a 248 x 70 ancillary data area along the right edge of each picture.

An interface with an external minicomputer permits manual or automatic transfer of image data between the refresh memories and the computer. A trackball-positioned cursor enhances operator interaction with both the scan converter and the computer.

### SECTION 2. GENERAL DESCRIPTION

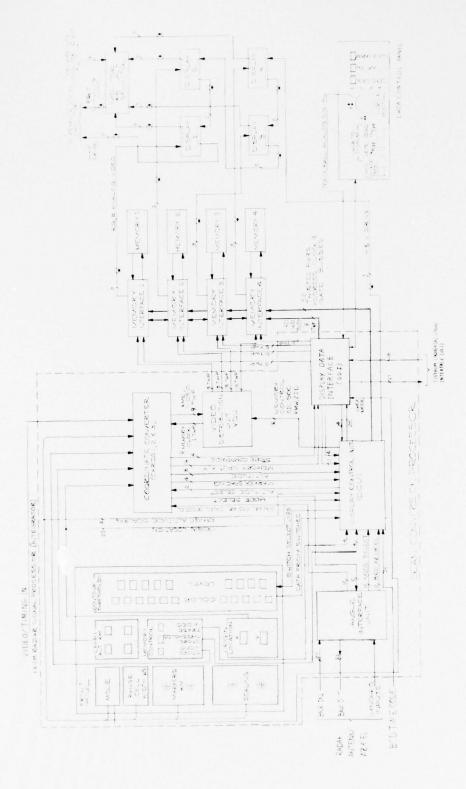

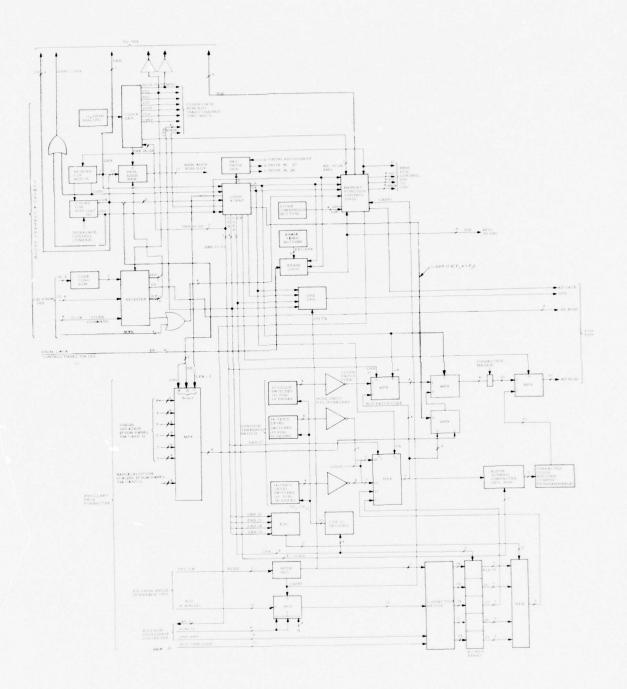

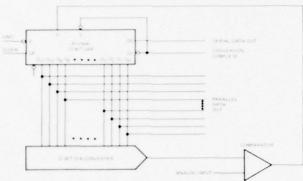

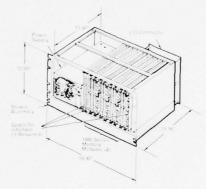

The block diagram presented in Figure 2-1 should be referred to while reading the following description of the scan converter.

# 2.1 Scan Conversion Processor

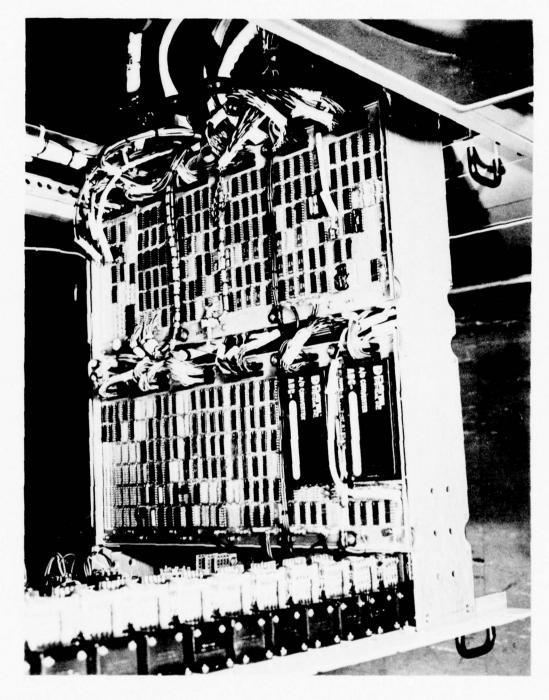

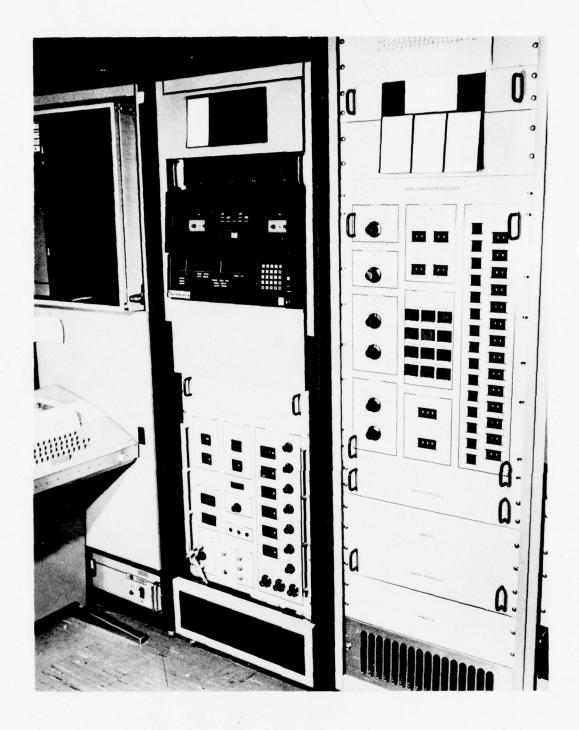

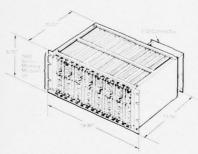

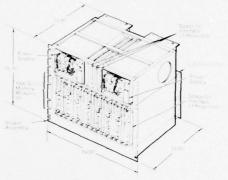

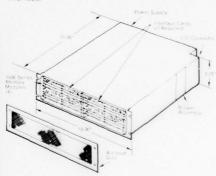

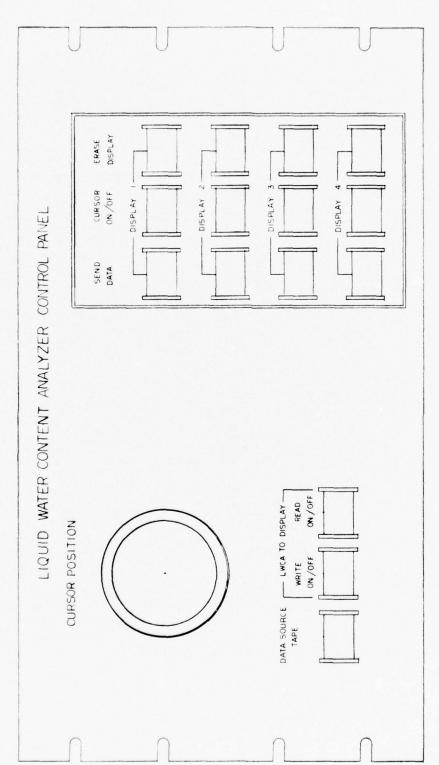

All front panel controls (except for those on the monitors and power control panel) are located on the Scan Conversion Processor or on the LWCA (Liquid Water Content Analyzer) control panel and are connected to various cards within the processor as shown. The Scan Conversion Processor accepts synchro or binary inputs for antenna azimuth and elevation angles as well as video and timing signals from a radar signal processor. The input information is converted in real time from its polar form to a rectangular form suitable for entry into the image-oriented memories. The processor also generates all memory addresses, timing, and control signals needed by the four memory-integration in the sunits, plus alphanumeric data and color patches.

thin the Scan Conversion Processor is a Display Data Interface (DDI) man permits communication between the Scan Converter and a Universal Logic Interface (ULI) of an Interdata 7/32 minicomputer. The minicomputer treats the Scan Converter as a peripheral and can perform data transfers to and from its refresh memories. A cursor can be switched on in any display, its position adjusted, and the data in the refresh memory at that position transmitted to the computer by operator interaction through the LWCA control panel.

Figure 2-1. Scan Converter Block Diagram

# 2.2 Memory Interface Units

Each Memory Interface Unit (MIU) performs parallel to serial and digital to analog conversions on its memory output to generate red, green and blue video signals for the corresponding display. These units also execute code conversion and contouring on the incoming video as a function of color patches and contour levels stored in the associated memory. Intermediate storage and logic in each MIU enables it to alter data in its memory as commanded by the Scan Conversion Processor.

# 2.3 Memories

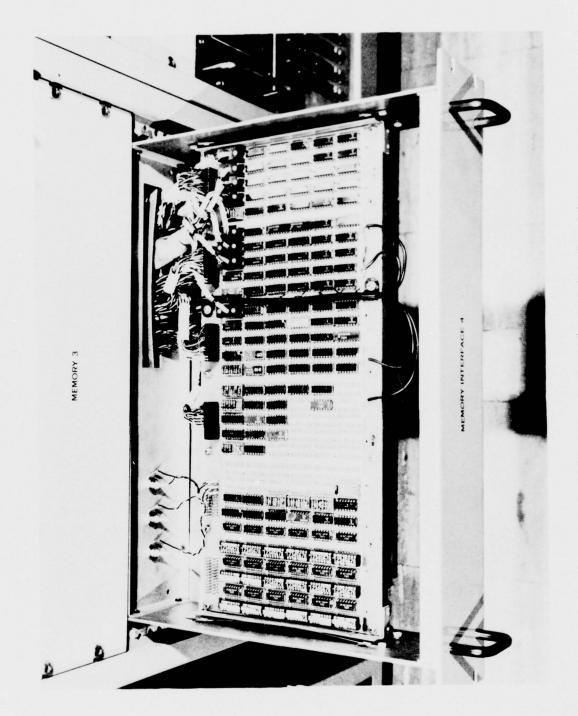

The image storage media are conventional AMPEX magnetic core memory systems having 8192 40-bit words for each display. They have split cycle times of 750 nanoseconds and self-contained power supplies which also power each associated MIU. Data sheets are included in the Appendix.

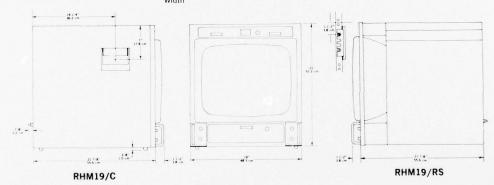

## 2.4 Displays

The displays are 19-inch CONRAC delta-gun color monitors of the type used in television studios. Each unit has red, green and blue video inputs driven by its MIU. All of the displays are synchronized by the same H and V drive pulses from the Scan Conversion Processor. A fifth monitor with remote selector can be switched to display the same image as any one of the four independent displays. Data sheets for the monitors have been included in the Appendix.

### SECTION 3. OPERATION

# 3.1 Display Adjustment

Each monitor should have its VIDEO switch in the 0 dB position for normal viewing. The MONO position may be helpful, in certain cases, for distinguishing colors. The OFF position might be useful as a standby mode in lieu of turning the power off.

The BRIGHTNESS control should be used to set the black background level (observe the area around the alphanumerics) to a point near the threshold of visibility. The CONTRAST control can then be used to obtain the desired intensity. The illuminated number at the top of each monitor is red when information is being stored in its memory.

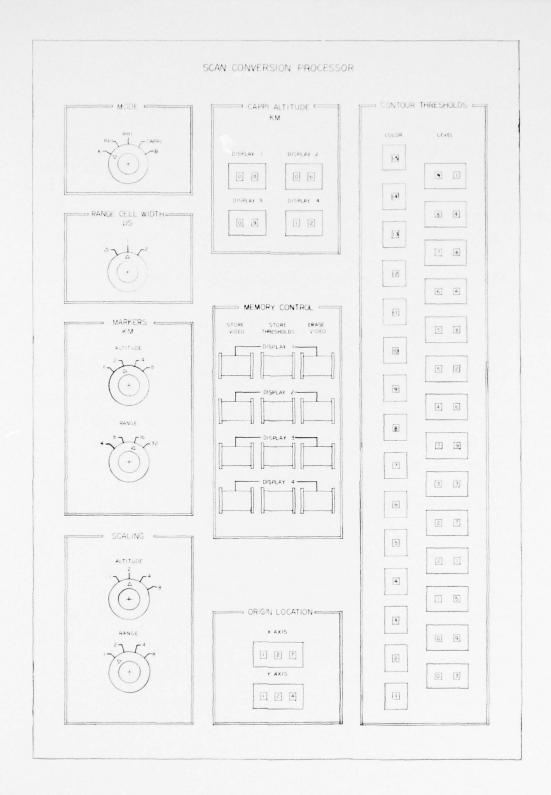

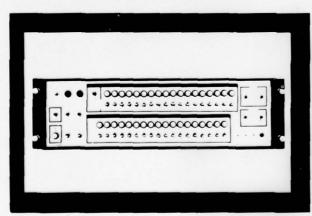

## 3.2 Contour Threshold Entry

The contour threshold switches are arranged in the same pattern on the front panel of the Scan Conversion Processor (see Figure 3-1) as on the actual displays. Any of the 15 color-selectors can be set to any color between 0 (black) and 15 (red).\* The 14 level-switches should be set up in ascending magnitude order from bottom to top. An area of the display will take on a color of a given patch if the corresponding signal processor output is equal to or greater than the level below the patch and less than the level above the patch. Should these levels be set to the same number, the color in the patch between them will never appear.

Having set up the contour threshold switches, the operator need only depress the STORE THRESHOLDS button for each display in which this set of contour thresholds is desired. The previous set of thresholds in that memory is then replaced by the new set without affecting the other display information which had been entered using the previous set of thresholds. (This situation, where the thresholds do not match the displayed information, can be avoided by pushing the appropriate ERASE VIDEO button before entering new contour thresholds.) All subsequent incoming video will be contoured according to the new set of thresholds.

<sup>\*</sup>Color 15, however, is reserved for range and altitude markers and has the property of not allowing itself to be written over. Patterns appearing in this color can only be removed by erasure.

Figure 3-1. Scan Conversion Processor Front Panel

\* The same of the

which the man was to be a second to the second

### 3.3 Mode and Range Cell Width Selection

These controls must be set to correspond with the radar scan sequence and the operating conditions of the radar signal processor. In the RHI (Range Height Indicator) mode, the display will present ground range along the X axis and height along Y. The antenna azimuth angle is shown after AZ, in the lower right corner, to the nearest degree.

The PPI (Plan Position Indicator) mode yields a plan-view display, with the Y-axis running North-South and the X-axis running East-West. The antenna elevation angle appears after EL to the nearest 0.1 degree.

Either RHI or PPI formats can be set up in any display or combination of displays by depressing the desired STORE VIDEO switches, which are active when lit. When a STORE VIDEO switch is on, the large number above the corresponding display is illuminated in red. The CAPPI (constant altitude PPI) mode, also permits use of any of the displays, with the CAPPI ALTITUDE switch settings appearing after AL at the lower right of each display. Each display represents a PPI at the altitude selected.

## 3.4 Scaling and Location of the Origin

The ORIGIN LOCATION switches provide a means of locating the point corresponding to the radar antenna at any position within the display area. The units employed correspond to display elements at (X,Y); (0,0) is in the upper left corner, while  $(\dot{2}49, 247)$  is in the lower right. The center, normally used for PPI formats, is (127, 124).

ALTITUDE (RHI only) and RANGE SCALING switches can be used to vary the scaling as listed in Table 3-1.

Table 3-1. Full Scale Range and Altitude vs Scale Switch Positions (RHI Mode)

| SWITCH POS: | 1      | 2      | 4     | 8     |  |

|-------------|--------|--------|-------|-------|--|

| ALTITUDE:   | 128 KM | 64 KM  | 32 KM | 16 KM |  |

| RANGE:      | 256 KM | 128 KM | 64 KM | 32 KM |  |

## 3.5 Marker Spacing Selection

MARKER switches are provided to select ALTITUDE (RHI only) or RANGE marker spacing. In PPI or CAPPI modes, the selected range marker spacing is indicated in kilometers after RM = at the lower right of the display. When the RHI mode is employed, the selected markers are indicated in the display in the following format: M (altitude marker spacing); (range marker spacing) in kilometers.

## 3.6 Time Code

The lower right corner of each display contains time information in the following format: T (day of the year); (hour of the day); (minute). The time readout of a particular display is updated only while information is being stored in the memory of that display.

### 3.7 Crosshatch

Mode switch position B is provided as a test position in which a cross-hatch is developed for monitor alignment purposes. The crosshatch appears in the color corresponding to full-scale video (the top patch), while the background appears in the color corresponding to zero video (the bottom patch).

## 3.8 Liquid Water Content Analysis

Mode switch position A sets up conditions needed for LWCA operation, covered by AJJ-21 in the Appendix where LWCA control panel operation is also described.

### SECTION 4. DETAILED CIRCUIT DESCRIPTION

The descriptions appearing in these sections generally refer to diagrams included among the text. In some cases; however, it might be helpful to refer to the actual schematics. A complete listing of drawings applicable to the LWCA scan converter can be found in AJJ-26 of Appendix D.

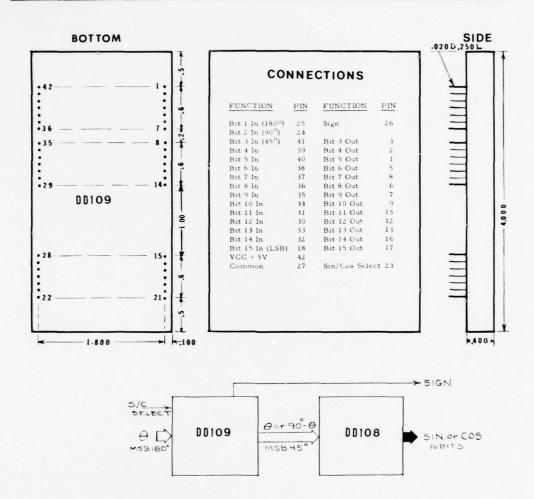

## 4.1 Angle Interface Unit

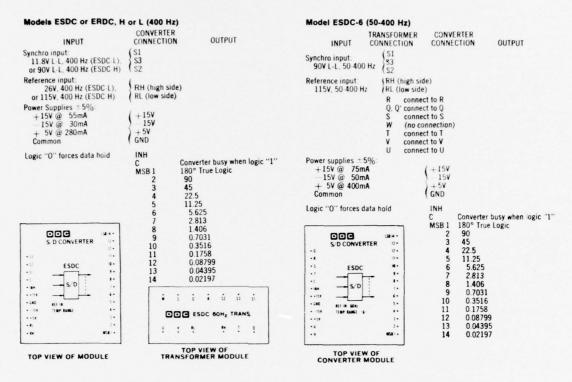

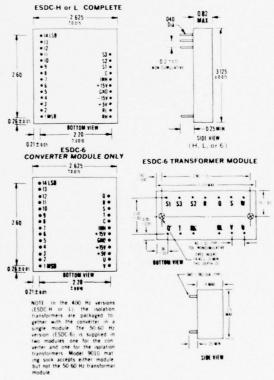

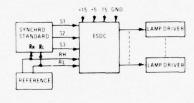

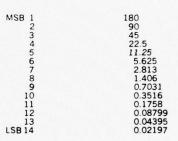

The Angle Interface Unit, located in the upper-rear position of the coordinate converter drawer, accepts synchro azimuth and elevation data in standard  $R_1$ ,  $R_2$  and  $S_1$ ,  $S_2$ ,  $S_3$  format and converts these data to the following outputs:

Scaled BCD azimuth angle, 1° resolution Scaled BCD elevation angle 0.1° resolution Sine/cosine azimuth 13 bits Sine/cosine elevation 13 bits Elevation greater than 12.65° flag

Azimuth and elevation synchro inputs are converted to 14-bit binary numbers (MSB=180°) in Data Device Corporation synchro to digital converters model ESDC-6\*. (These converters are inhibited during sampling by the S/D inhibit command input.) The 14-bit binary outputs are fed both to rear panel connector J3 through line drivers and to multiplexers A21 through A24 and A7 through A10.\*\* These multiplexers select binary angle data from either a rear panel connector J4 or from the synchro to digital converters. They have been provided should the need arise to drive the system from a digitally generated angle source. If J4 is not connected, the multiplexer select line—is pulled up so that the converter outputs are selected.

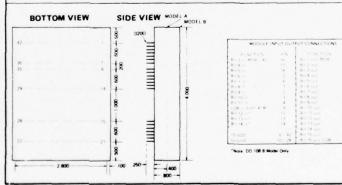

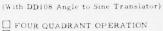

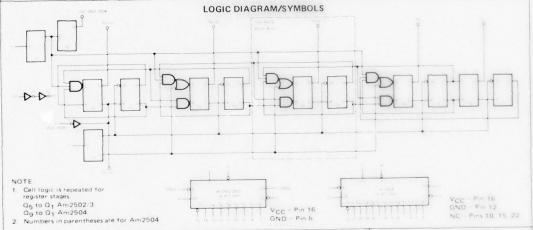

Binary angle data is next converted to sine and cosine in Interface Engineering sine/cosine controller model 109 and angle to sine converter model 108.\*

The controller adapts the angle to sine converter to full four quadrant sine and cosine operation. A logic zero on the controller input terminal 23 selects sine.

The sine/cosine converter channel is multiplexed once each PRF interval between azimuth and elevation inputs through multiplexers A16 through A18. This technique was employed to optimize the efficiency of the converters.

<sup>\*</sup>See Appendix for Data Sheets

<sup>\*\*</sup>Actually only 12 bits of Azimuth and Elevation are included in J3 and J4 at the rear panel; the two additional elevation bits, both input and output, are connected to J2 - See 897392.

An Interface Engineering binary angle to scaled BCD converter, model 107,\* provides the drive for the CRT antenna angle display. This converter is switched between azimuth and elevation by multiplexers All through Al4, controlled by the front panel mode switch. Azimuth is displayed in the RHI mode; while elevation is displayed in all other modes.

Multiplexers A3, A4 and A5 line shift the scaled BCD four lines down when displaying elevation to provide the increase in resolution from  $1^{\circ}$  to 0.1°.

The magnitude comparators, A20 and A25, generate a logic one when the antenna elevation angle exceeds 12.65°. This output is used by the coordinate converter in the CAPPI mode to initiate the 2° elevation step.

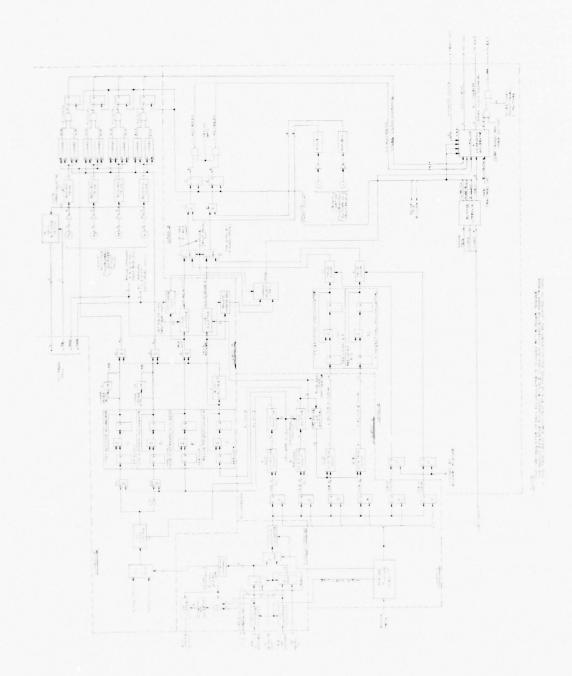

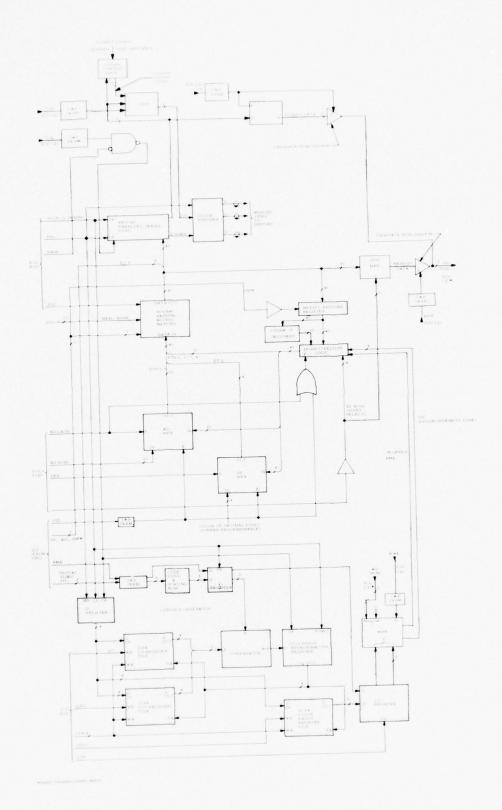

### 4.2 Coordinate Converter

The Coordinate Converter derives the cartesian memory address from the radar parameters of elevation angle, azimuth angle, radar trigger and the range gate clock. The azimuth angle and elevation angle are sampled once every radar period to form the basis of the coordinate transformation. The block diagram of the Coordinate Converter unit is shown in Figure 4-1.

### 4.2.1 Angle Parameters

In the angle interface unit, there are two synchro-to-digital converters; one dedicated to the azimuth angle,  $\theta$ , and the other dedicated to the elevation angle,  $\phi$ . The outputs of each S/D converter are multiplexed into a  $\sin/\cos$  converter such that by control of the multiplexer and function switch of the  $\sin/\cos$  converter, the following functions can be obtained and stored in a D type register:

sin Ø

cos Ø

$\sin \, \theta$

cos θ

### 4.2.2 Fixed Constant Multipliers

In the RHI display, the altitude is R  $\sin \varphi$ , and the projection of the range is R  $\cos \varphi$  where R is the range expressed in kilometers. Card number 1 has two 12 x 12 fixed constant multipliers which multiply the single function input by a fixed constant such that the output is expressed in kilometers with the binary point 12 bits from the LSB. For a 2  $\mu$ sec unit range cell, the conversion factor (radar distance) built into the multipliers is .2998046. All subsequent calculations following the fixed constant multipliers are done directly in kilometers which is a very useful simplification especially in determining the range markers.

<sup>\*</sup>See Appendix for Data Sheets

Figure 4-1. Coordinate Converter Block Diagram

The fixed constant multipliers are each composed of adders arranged in an array such that the input is multiplied by a constant. Groups of 4-bit adders are pyramided to form a subset of 4-bit numbers with all the carry-outs fed into the carry-inputs of the next higher order 4-bit array. The schematic diagram shows the array in detail and also in block diagram format. The line shifter following each multiplier array is controlled by the front panel switch that selects the range gate. The line shifter, in effect, multiplies the output by 1/4, 1/2 or 1 corresponding to the range gate widths of 1/2  $\mu$ sec, 1  $\mu$ sec or 2  $\mu$ sec. A secondary line shifter operates on the unit range vector R o cos  $\phi$  and is used for scaling in the PPI mode.

# 4.2.3 PPI Mode - True 12 x 12 Multipliers

In the PPI mode, the projected range,  $R_o \cos \theta$ , is broken up into its X (East-West) and Y (North-South) coordinates. The azimuth angle  $\theta$  is measured from the North-South line such that

$$X_{O} = R_{O} \cos \phi \cos \theta$$

and

$$Y_{O} = R_{O} \cos \phi \sin \theta$$

Since  $R_0 \cos \phi$  had already been established in one of the fixed constant multipliers, two other multipliers are used to establish  $X_0$  and  $Y_0$ , the unit component vectors for the PPI display.

The 12 x 12 true multipliers consists of an array of partial product terms added in a pyramid structure very similar to the fixed constant multiplier. The partial product terms and summation pyramid are detailed in the schematic drawing of the  $12 \times 12$  multipliers.

Card 2 of the coordinate converter thus develops the unit altitude  $R_o$  sin  $\theta$ , the unit range  $R_o$  cos  $\phi$ , and the component vectors of the unit range  $R_o$  cos  $\phi$  cos  $\theta$  and  $R_o$  cos  $\phi$  sin  $\theta$  all evaluated in kilometers.

### 4.2.4 Address Accumulators - Card 2 and Card 3

The unit coordinates have been derived for the first range cell. Coordinates for other range cells can be easily obtained by taking advantage of the fact that the range cell number increases linearly in a radar. Thus, the

coordinates for range cell j + l are the coordinates for range cell j added to the value of the respective coordinates of range cell l. This accumulator type structure is shown in the block diagram and is repeated 6 times in the coordinate converter. The unit vectors are loaded into each accumulator at the beginning of each radar period and at the same time the old data is cleared out. The accumulator is clocked by the range gate clock of the integrator to form the cartesian coordinate addresses.

For the RHI mode of operation, the Y address corresponds to the scaled altitude and the X address is the scaled range. For the PPI or CAPPI mode of operation, the Y address corresponds to the North-South component of the range vector and the X address corresponds to the East-West component of the range vector. The mode switch controls the multiplexer to select the appropriate coordinates as shown in the block diagram. After the multiplexer, constants controlled by thumbwheel switches can be added independently to the X and Y coordinates to affect translation in both directions. A hard limiter circuit is used to prevent overflow and erroneous addresses.

# 4.2.5 Range and Altitude Markers

The outputs of both the range and altitude accumulators are in kilometers (see para. 4.2.2) i.e., the 13th bit is 1 KM, the 14th is 2 KM, etc. Detection of the clock cycle at which time the bit corresponding to a preselected range changes state is used as the marker pulse. The circuitry consists of comparing the selected bit with the same bit delayed one clock period in an exclusive or circuit to form the marker pulse. The marker pulse goes through the synchronizer to produce the range mark enable (RME) signal.

### 4.2.6 CAPPI Mode

In the CAPPI mode, the antenna sweeps  $360^{\circ}$ , or a segment thereof, at a single elevation angle and upon reaching its starting or terminal position (for less than  $360^{\circ}$  sweep) the elevation angle is incremented and the process is repeated. A typical CAPPI will use the following elevation angles, 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 14, 16, 18 and  $20^{\circ}$ . This volume scan permits

the operator to crudely establish a map of a prescribed altitude or many altitudes, since, in general, each radar beam will pass through all possible altitudes. By carefully selecting and storing the incoming data, it is possible to develop a constant altitude PPI map at any given altitude. Because the elevation angle of the antenna is incremented in small steps, a map at precisely the desired elevation would provide very few sample points; it is the established procedure to sample the elevation at or near the desired elevation.

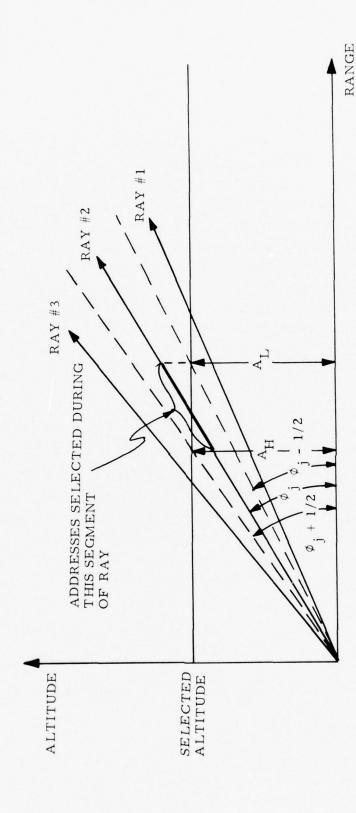

Figure 4-2 shows a constant altitude intersecting three different angle vectors or rays. The solid lines represent the CAPPI elevation angles and the dotted lines represent elevation angles between the CAPPI rays. For elevation angle  $\phi$ j, information is recorded when the altitude reached by the altitude vector associated with the ray at  $\phi$ j + 1/2 is equal to the preselected altitude, similarly the data recording is stopped when the altitude reached by the altitude vector associated with the ray at  $\phi$ j - 1/2 equals the preselected altitude. From the diagram, it can be seen that there are no gaps in obtaining all the altitude information for a preselected altitude as the beam increments discretely in elevation angle.

In the coordinate converter, the altitude is developed in the altitude accumulator from the unit altitude vector  $\mathbf{R}_0 \sin \phi$ . A unit high altitude vector  $\mathbf{R}_0 \sin (\phi + 1/2)$  and a unit low altitude vector  $\mathbf{R}_0 \sin (\phi - 1/2)$  are also developed and introduced into their respective accumulators to form the high and low altitude addresses respectively,  $\mathbf{A}_H$  and  $\mathbf{A}_L$ .

For small angles, the approximations

$$\sin (\phi + f) \approx \sin \phi + \sin 1^{\circ}$$

and

$$\sin (\phi - f) \approx \sin \phi - \sin 1^{\circ}$$

were used.

The selection criteria for a preselected altitude A; is the following:

$$A_L \le A_j \le A_H$$

; store data in j<sup>th</sup> memory

For each altitude, two comparators are used and are shown in the diagram of card 2.

Figure 4-2. CAPPI Address Selection

# 4.2.7 Coordinate Converter/Integrator Interface

The Coordinate Converter is slaved to the integrator by using the radar trigger and range gate clock from the integrator. Synchronization between the Coordinate Converter and the integrator is the major reason for slaving the coordinate converter to the integrator. However, synchronization is not sufficient in order to format data rates greater than 0.6 MHz, the fastest data rate the memories can accept. For instance, it would be impossible to accept  $1\,\mu$ sec range gates directly from the integrator, but it is possible to receive alternate  $1\,\mu$ sec range gates from the integrator during one radar period and the previously non-selected  $1\,\mu$ sec range gates during the second radar period. This is possible because the integrator has holding loops already built into its output circuitry and, simply by selecting the starting range gate in a sequence, it is possible to store all of them.

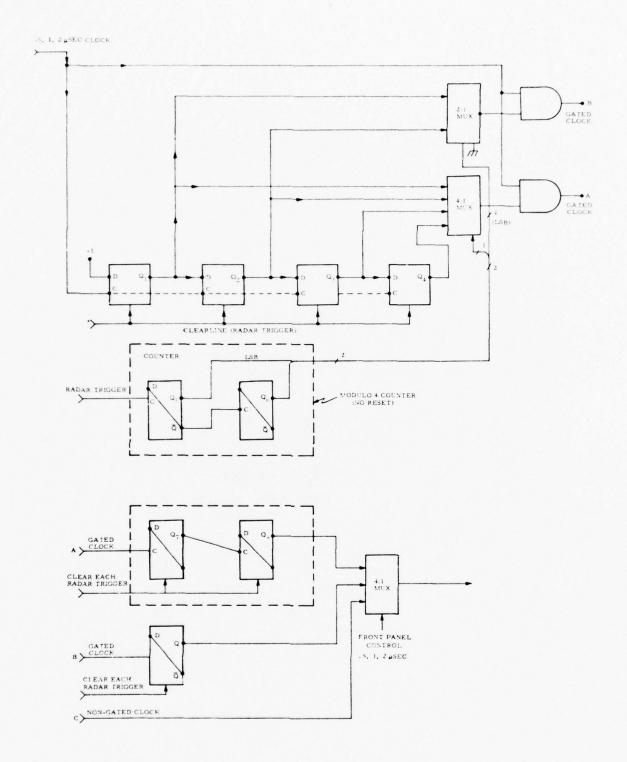

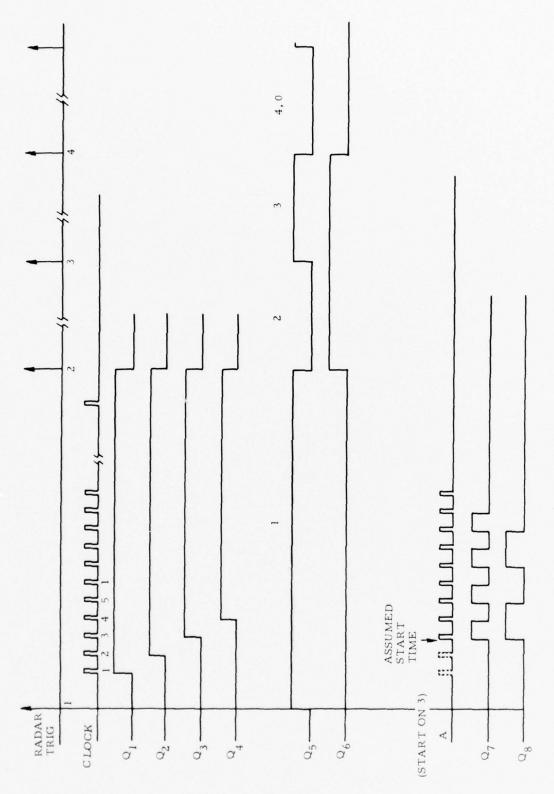

A simple block diagram and timing waveform is shown in Figures 4-3 and 4-4. The radar trigger passes through a modulo 2 and modulo 4 counter. The output of the counter controls a multiplexer, the inputs of which are gate pulses that start on either the first, second, third or fourth pulses. These gate pulses are used to gate the range gate clock that ultimately drives the accumulators. The coordinate addresses are strobed by means of a 2  $\mu$ sec clock into the synchronizer. The 2  $\mu$ sec clock is also derived from the gated range-gate-clock and a modulo n counter where n depends on the range gate width.

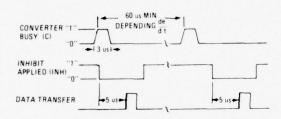

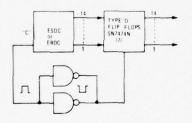

### 4.2.8 Synchronizer

The Coordinate Converter and the memory unit run on independent clocking signals and the synchronizer is the means for interfacing these two asynchronizers. The memory can accept data at a rate not to exceed 0.6 MHz, and the synchronizer will work at any input data rate provided the maximum 0.6 MHz rate is not exceeded.

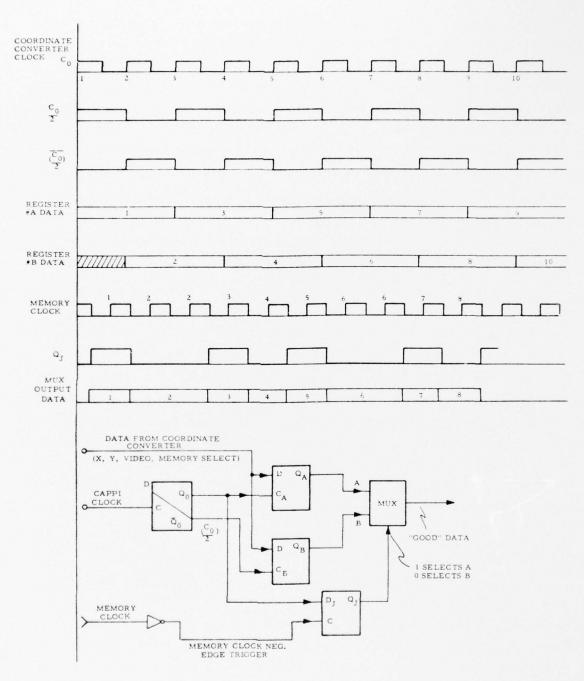

The synchronizer input data consist of 8 bits each of X, Y and video information, RME, and 4-bits of memory select information(the store commands). Since these 29 bits come in parallel, operation of the synchronizer can be understood by considering a single bit. Figure 4-5 is a simplified block

Figure 4-3. Timing Interface for Coordinate Converter and Integrator

Figure 4-4. Integrator Coordinate Converter Timing Waveforms

Figure 4-5. Coordinate Converter Memory Buffer Timing Waveforms

A street with the second secon

diagram of the synchronizer and the timing waveforms showing the operation of the system. Incoming data are stored in one of two D-type registers such that each DATA BIT is stored for 2 clocking cycles. The purpose of the synchronizer is to insure that the data are "good", i.e., there is no chance of a data edge or change during the time that the memory clock strobes out the data. It can be shown that at least one of the data inputs to the multiplexer will not change during the strobe time (pos. edge) of the memory clock. By strobing ( o ) into a D-EDGE register using the negative edge of the memory clock will provide an output signal  $Q_i$  that can control the multiplexer to select the signal that is guaranteed to be "good" by the time that the positive edge of the memory clock comes along. Notice that there can be an ambiguity in Q, itself, i.e., assume  $(\frac{C}{0})$  is changing at the time the negative edge of the memory clock arrives. This ambiguity, however, does not produce an ambiguity at the time the positive edge of the memory clock arrives, for regardless of which register was selected by the multiplexer, the data in either register cannot change for 2  $\mu$ sec (the C clock period) and the data will be strobed out in .8 µsec, hence, the data will be good.

If on the other hand, we look at the situation in which the data are changing in one of the storage registers at the time of a positive going edge of the memory clock, we find that the multiplexer always selects the other register. Data can be clocked out twice as shown in the example (data #2 and #6), but will cause no problems in the system since it implies that the same data will be reentered at the same memory location, causing no change. The synchronizer is on card 3.

# 4.2.9 Angle Interface Timing

On card 1 is the angle interface timing which operates the control lines of the multiplexer and the control line of the  $\sin/\cos$  converter as well as providing an inhibit line for the S/D converters. At the start of each radar period, a gated delay line oscillator is turned on and drives a counter. The counter is decoded to derive the approximate control line code to obtain the desired function of either  $\sin\theta$ ,  $\cos\theta$ ,  $\sin\phi$  or  $\cos\phi$ . When this function is available, it is strobed into the appropriate D-register shown in the block diagram.

This is done only once every radar period. The input to the coordinate accumulators are those unit vectors that have been determined on the previous radar period.

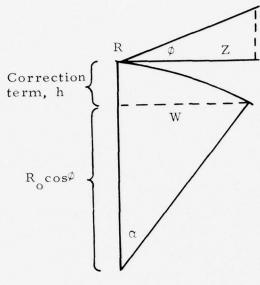

# 4.2.10 Earth Curvature Correction

A correction term is added to the altitude address to correct for earth curvature. This correction term is a positive function that depends on the flat earth range. A ROM is used to obtain the correction factor from the range. A derivation of the correction term is shown in Figure 4-6.

# 4.3 Display Control Unit

# 4.3.1 Timing and Control Logic

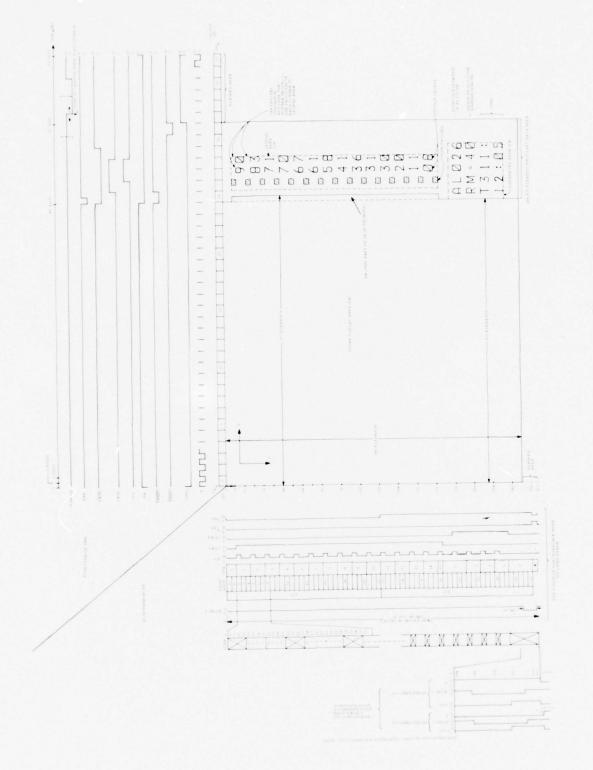

Figure 4-7 presents the DCU block diagram, where it can be seen that all timing waveforms are obtained by frequency division of the 11.958041 MHz crystal controlled clock. Discussion of the outputs of the clock generator, except for R, is postponed until the section on the MIU where these signals are used.

The square-wave R, with a period of 1.6725 microseconds, is illustrated along the X axis of Figure 4-8, which shows the display format along with waveforms. Along the X-axis, the display is organized into ten-point blocks designated DXBO through DXB31; each period of R corresponds to one block. Since each point requires four-bits for color/intensity coding, 40 bits are needed to specify each block. A memory with 40-bit words has been chosen so that one word in the memory represents each block, 32 words at consecutive addresses describe a line, and 8192 words contain the entire image.

In order to refresh the display, each memory is sequentially read while the CRT beam scans out a raster; this read cycle is always done while R is high, when the memory address multiplexer (see Figure 4-7) routes DXB and DY from the synchronous scan counters to the 13-bit memory address buss which drives all MIU's in parallel. During the remaining half cycle of R, if a store command is received from the DDI, data is written into the memory at an address IXB IYB. IYB is simply the input Y address from the DDI, IY, clocked into a register by PSL. In the code conversion ROM, IX is converted

Note: R<sub>o</sub> = 3900 smi (6275.1 Km) used in

**ROM**

$h = R_o - R_o \cos \alpha = R_o (1 - \cos \alpha)$ where  $R_o$  is radius of the earth.

But for small angles,

$$\cos \alpha = 1 \frac{\alpha^2}{2} \dots \text{ hence, } h = R_0 \left( \frac{\alpha^2}{2} \right)$$

Also for small angles  $\alpha \approx \frac{W}{R_{_{\mbox{\scriptsize O}}}}$

$$h = R_o \left(\frac{W}{R_o}\right)^2 \frac{1}{2} = \frac{W^2}{2R_o}$$

But  $W = R \cos \phi$

$$h \approx \frac{(R \cos \phi)^2}{2R_0} = K (R \cos \phi)^2$$

Figure 4-6. Earth Curvature Correction Term

Figure 4-7. DCU Block Diagram

Figure 4-8. Display Format and Timing Diagram

into a code consisting of IXB (block select) and XP (point select). As is described in the MIU section, XP determines which one of the ten points within the block is to be changed.

The logic array generates waveforms, shown in Figure 4-8, which are functions of the scan counter outputs, DXB or DY. Waveforms which need to be functions of both DXB and DY are derived from them; for example: PA = PA(X) · PA(Y). The logic array is implemented with two 32 x 8 PROM (Programmable Read Only Memories) and a collection of decoders and gates. A truth table for these PROM, C16 and D20, is tabulated in the appendix, while the addressing and output waveforms are illustrated in Figure 4-8.

Interlaced scanning, possibly useful to fill interline gaps for photographic purposes, can be enabled by removing the jumper-carrier which grounds C27-9. The waveforms which result are shown in Figure 4-8. Timing of the H-drive pulse is adjustable over a range of  $\pm 3$  microseconds by means of the potentiometer in F28. This adjustment can be used to center the image in the raster of the display.

The memory function control logic generates SIC, SOC and RMW signals (to be discussed in the MIU section) which initiate various types of cycles in the memory. The AD GATE enables entry of ancillary data (contour thresholds, color patches and parameters) into the MIU. The memory function control logic also contains a four-state counter which advances once per field. The outputs of this counter, AS, select one of the four CAPPI ALTITUDES from the front panel switches for entry into the parameter area of the corresponding display.

The erase logic generates properly timed ZID signals which cause all zeroes (black) to be written into the memory at all addresses in response to an ED signal from the LWCA control panel, or at all but the legend-area addresses in response to an ER signal. The decimal point required in the elevation angle is located in point two, whereas all other ancillary data falls into points five through nine; hence, it requires a separate signal developed by the DPE generator. The RLS signals, needed by the DDI, are simply the outputs of the STORE THRESHOLDS buttons clocked by DY8 (once per field).

### 4.3.2 Ancillary Data Formatter

In order to minimize wiring complexity of the array of contour threshold switches, encoding diodes are mounted on the switches themselves as indicated

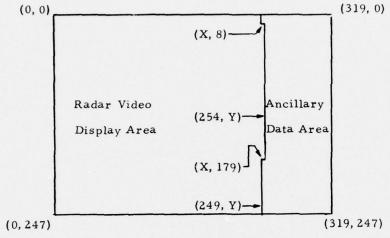

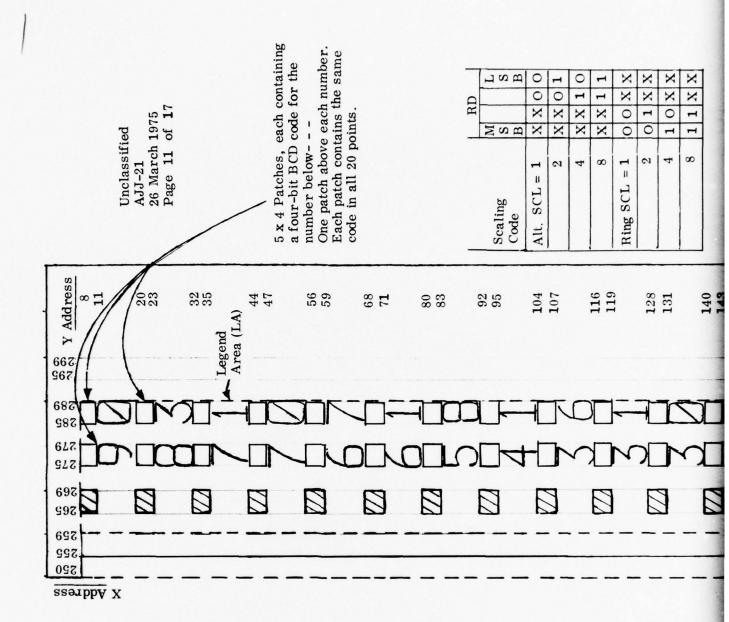

in Figure 4-7. One switch at a time is selected by CPI through CPI5 (CPA decoded, see Figure 4-8) as the display raster is scanned. The color switch outputs are applied to the AD BUSS (a 20-bit buss through which ancillary data can enter points five through nine of any block in memory) when the CRT scan is located in the color patch areas. Similarly stored above each number in the legend and parameter areas is a patch containing a BCD code for that number. The contour generator to be described in the MIU section makes use of these codes which are not visible on the display because a MASK waveform is applied to the MIU. The numbers themselves are generated in a row-select five-by-seven alphanumeric character generator ROM which outputs five bits in parallel to a character color encoder. This encoder generates a jumper-programmable four-bit code, now set up as green (0111) or black (0000) for each of the five points.

The ancillary data (angle, altitude, marker spacing and time) are entered into the character generator at the proper time by an array of multiplexers. The mode lines, from the front panel mode switch via the angle interface unit, drive a mode decoder which controls the multiplexers and applies the proper alphanumeric identifiers; AZ, EL, AL, M, RM, or T which are hard wired. Origin location and range/altitude scaling information is stored only in two unique color patches (See Appendix, AJJ-21, Figure 3) and not as alphanumerics.

Signals appearing on the AD BUSS or on DPE are not displayed directly, even though they are synchronous with the raster scan format. Rather, the data are stored in the memory when appropriate store commands are issued. Only the memory contents themselves are displayed.

### 4.4 Video Distribution Unit

The VDU card consists simply of an array of line drivers which serves to distribute the eight-bit video signal from the coordinate converter to all of the MIU in parallel. The memory control lines SIC, SOC, RMW, RME, and ZID for each MIU are also routed through the VDU, while the memory clock,  $\overline{\mathbb{R}}$ , passes through on its way to the coordinate converter (see Figure 2-1).

### 4.5 Memory Interface Units

The block diagram in Figure 2-1 contains four Memory Interface Units (MIU) which are identical rack-mounted drawers. Address, clock, and gate busses are supplied to the MIU in a daisy-chain configuration where each

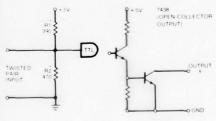

unit taps off of a twisted-pair cable which is resistively terminated only at the last MIU (No. 1). A block diagram of one MIU is presented in Figure 4-9; the detailed descriptions of various components within it are contained in paragraphs following a discussion of memory cycles.

### 4.5.1 Memory Cycles

The timing diagram in Figure 4-10 shows all significant waveforms for examples of the four types of memory cycles. Each cycle occupies one-half period of the square wave R (shown in both timing diagrams, Figure 4-8 and 4-10), and is initiated by manual or automatic commands listed in Table 4-1. The state of R determines whether the raster-scan address DXB, DY or the code-converted input address IXB, IYB appears on the memory address buss.

As listed in the table, each of the four types of cycles happens in response to commands when the raster scan address DXB, DY is in certain areas of the display.

Table 4-1. Memory Cycles

|   | Commands       |                 |       |                         |                           | Type of Memory Cycle<br>When DXB, DY is in each |     |     |         |

|---|----------------|-----------------|-------|-------------------------|---------------------------|-------------------------------------------------|-----|-----|---------|

| R | Video<br>Store | Legend<br>Store | Erase | Para-<br>meter<br>Store | Memory<br>Address<br>Buss |                                                 |     |     | Retrace |

| 1 | X              | 0               | X     | X                       | DXB, DY                   | RR                                              | RR  | RR  | φ       |

| 1 | X              | 1               | X     | X                       | 11                        | RR                                              | RW  | RR  | φ       |

| 1 | X              | X               | 0     | X                       | 11                        | RR                                              | RR  | RR  | Φ       |

| 1 | X              | X               | 1     | X                       | 11                        | RW                                              | RR  | RW  | Φ       |

| 1 | X              | X               | X     | 0                       | ti .                      | RR                                              | RR  | RR  | Ø       |

| 1 | X              | X               | X     | 1                       | 11                        | RR                                              | RR  | RW  | Φ       |

| 0 | О              | X               | X     | X                       | IXB, IYB                  | RR                                              | RR  | RR  | RR      |

| 0 | 1              | X               | X     | X                       | IXB, IYB                  | RMW                                             | RMW | RMW | RMW     |

Figure 4-9. Memory Interface Block Diagram

大二 国際国 にご

Figure 4-10. Memory Interface Timing Diagram

SEE MEMORY ADDRESS TIMING DIAGRAM FOR DETAILS

NOTE B

Table 4-1 (Cont)

# Listing of Types of Memory Cycles

| $\underline{R}$ | Cycle    | Description                                                |

|-----------------|----------|------------------------------------------------------------|

| 1               | RR       | READ-RESTORE. Data from memory address DXB, DY             |

|                 |          | is transferred to the parallel/serial converter. Unchanged |

|                 |          | data is restored at the same address. This cycle is used   |

|                 |          | for providing video information to refresh the raster-scan |

|                 |          | display.                                                   |

| l<br>or O       | <b>Ø</b> | IDLE. Do nothing.                                          |

| 1               | RW       | READ-WRITE. Data from memory address DXB, DY are           |

|                 |          | transferred to the parallel/serial converter. New data,    |

|                 |          | all zeroes for an erase operation or information from the  |

|                 |          | AD (ancillary data) buss for legend or parameter storage,  |

|                 |          | are written into the same address.                         |

| 0               | RMW      | READ-MODIFY-WRITE. Data from memory address                |

|                 |          | IXB, IYB is transferred to the modify/restore register     |

|                 |          | and logic, then is partially changed and written back into |

|                 |          | the same address. This cycle is used to enter data into    |

|                 |          | DA.                                                        |

## 4.5.2 Parallel-To-Serial Converter

Parallel data from the memory are loaded into this converter at a positive edge of SCLK during PSL - see the timing diagram in Figure 4-10. The converter is wired as a four-bit-wide, ten-bit shift register having a four-bit output CV which changes at positive transitions of SCLK. The timing diagram describes which point from which memory output appears at each time interval. The D MASK output (see Figure 4-9) is simply MASK, a signal which blacks out the undesired areas of the display, delayed by three SCLK periods so that it changes only at boundaries between points zero and nine.

#### 4.5.3 Color Encoder

The color encoder (see block diagram in Figure 4-11) accepts the fourbit output of the parallel-to-serial converter, and if DMASK is false, outputs three analog voltages to drive the red, green and blue video inputs on the color monitor. The three identical D/A converters only have three bits each, but nevertheless it is possible to generate 512 different color/intensity outputs. Voltages at each output take on eight different levels ranging from zero (black) to one volt (full intensity); the output loading must be 75 ohms through video coaxial cable.

The color encoder is programmable; that is, for each of the sixteen possible states of the input CV, an arbitrary set of analog output voltages can be programmed by means of switches. The switches are arranged in columns by colors, as shown in Figure 4-11, where an example of one possible program is shown. Within each column are three sub-columns which correspond to the bit weight 1, 2 or 4; finally, each switch in each sub-column in numbered from 0 to 15 to denote CPA (Color Patch Address-see Figure 4-8). In the example, the relative video values listed are obtained by simply adding the bit weights for each color at each CPA.

#### 4.5.4 Modify/Restore Logic, Register and Multiplexers

The RMW memory cycle is fundamental in that it provides the means by which new data are entered into the display area. During the time when R is False and IXB, IYB is on the memory address buss, if a store video command occurs, the following sequence of events takes place (refer to Figure 4-9). The 40-bit memory output DO is loaded into the modify/restore register at the positive edge of RMW. In the modify/restore logic, one point (four-bits) as selected by the XP buss, is changed to whatever CIC (Color-Intensity Code) happens to be. The other nine points are unchanged.

If DELAYED RME is true, the selected point is written back as 1111, the code reserved for range markers. If a point is found to contain code 1111 by the COLOR 15 DECODERS, it is written back as 1111. Since these events happen when R is False, the AD and DP multiplexers are switched so that all 40 bits from the modify/restore logic go right back into the memory where they are written, still at the same address, when SIC comes along.

Figure 4-11. Color Encoder Switches and Block Diagram

As is evident from Table 4-1, the intervals when R is False have been reserved for RMW cycles, no matter where the raster scan counters happen to be. Thus, a new input data point can be accepted once every period of R (1.6725 µsec). During the same period, ten adjacent points are output to the color encoder. This ten-to-one difference in data rates results from the memory organization employed and the fact that the input addresses are in random order, while the output addresses are in sequential order.

When ancillary data or zeroes for erase are being written into the memory in RW cycles, points two and five through nine can be changed simultaneously by means of the DP and AD multiplexers. Ancillary data enters through the 20-bit AD multiplexer when AD GATE is true, while DPE causes a 4-bit jumper-programmable code for the color of the decimal point to be applied to point two. ZID zeroes all 40 bits during erase.

#### 4.5.5 Contour Generator

The lower half of Figure 4-9 is the contour generator which accepts one 8-bit video word and RME every period of R and presents a corresponding fourbit CIC (color/intensity code) and delayed RME as its output. Contour thresholds, both colors and levels, are read from the memory when the raster scan is in the appropriate patch (see Figure 4-8) and are stored in register files -- small, fast memories capable of simultaneous reading and writing at different addresses. Data from the register files is used in a successive approximation algorithm to determine which CIC to assign to a given video input.

The incoming digital video is both scaled and converted to BCD in a ROM made up of two 256 x 4 PROM, D9 and D10 for which truth tables are included in the appendix. The ROM output is clocked by PSL into the V register where it remains available to drive the comparator during the remainder of the period of R. The example at the bottom of Figure 4-10 shows a digital video input which has a value such that it should be assigned the color which has been entered into CPA 13. The successive approximation register state RA always begins as seven whereupon the contents of the 1's and 10's register files at read address RA = 7 are compared with V. The decision made in the comparator determines that the next state for RA should be 11 (the other alternative is three), and the process continues to repeat in this manner until four decisions, corresponding to 16 bits, have been made. The final answer of RA = 13 then addresses

the Color Patch Register File which provides a four-bit code to be loaded into the CIC register by CCK. The second contour generator cycle at the lower right of Figure 4-10 shows all possible states of RA for each step.

The time interval after CCK is reserved for writing data into the three register files, as commanded by the three write strobe signals 1 ST, 10 ST and CPST. The write address applied to the register files is CPA, and the appropriate write strobe signal is gated-on when the raster scan is in the proper patch. Although each patch contains a five-by-four array of identically coded points, only one is needed to be written into the register files. Point eight has been arbitrarily chosen and is thus loaded into the D register (Figure 4-9) at PSL so that it can be entered into the proper register file when the corresponding write strobe signal occurs. Four write strobes appear during each field for every write address of the register files.

#### 4.5.6 Write Data and Read Data Busses

The WD and RD four-bit busses, daisy-chained through the MIU as are the other busses (see Figure 2-1), permit direct access to any image point in the memory.

When the MWE control line is active, the multiplexer at the bottom of Figure 4-9 connects the WD buss directly to the CIC inputs of the Modify/Restore Logic. The Range Marker Enable signal is simultaneously rendered inoperative.

When the MDE control line is active, a tri-state driver shown in Figure 4-9 drives the RD buss with a four-bit code corresponding to one of the ten points currently available at the memory output. The DDR multiplexer selects this point as a function of the state of the XP Buss. The RD buss differs from all others in that signals flow away from the MIU; more than one MDE or CDE control line cannot be active simultaneously lest the buss drivers perish.

#### 4.5.7 Cursor Interface

When the CUB (Cursor UnBlank) control signal is active, a cursor color code is applied to the CV inputs of the color encoder instead of the parallel/serial converter output. The color change logic ensures visibility of the cursor by defining its code as zero (black) except when the point being covered by the cursor (hence the background) is any of colors zero through three. In the latter case, the cursor appears as the jumper-programmed color, presently wired as color seven (light green).

The leading edge of the CDE (Cursor Data Enable) control signal enters the current four-bit word at the parallel/serial converter output into the cursor data register. As long as CDE remains active, this word appears on the RD buss. Individual MIUs are protected against simultaneous occurrence of MDE and CDE; CDE has priority.

#### 4.5.8 Full-Screen Operation

When the FSE (Full-Screen Enable) control line is active, the MASK which normally blanks certain areas among the ancillary data is inhibited. This condition permits use of the full screen for display of data written through the WD buss.

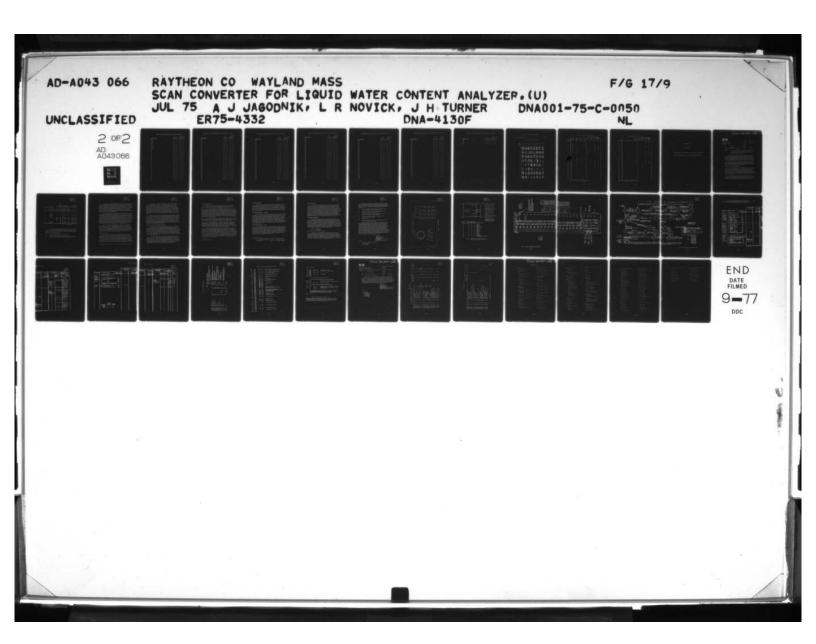

### 4.6 Display Data Interface and LWCA Control Panel

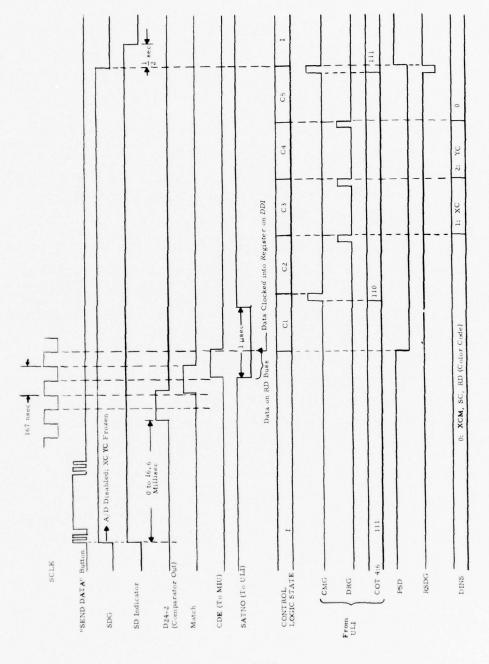

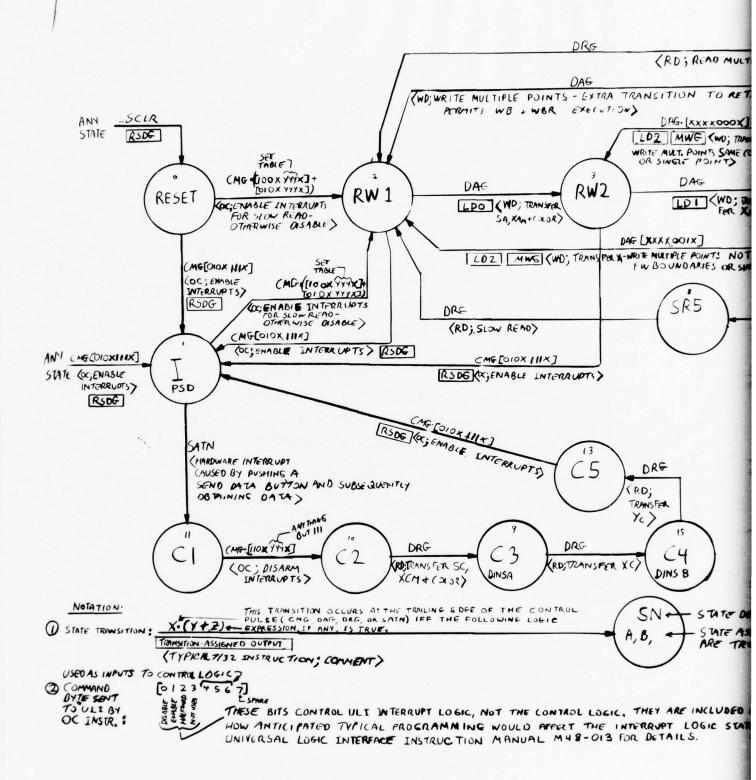

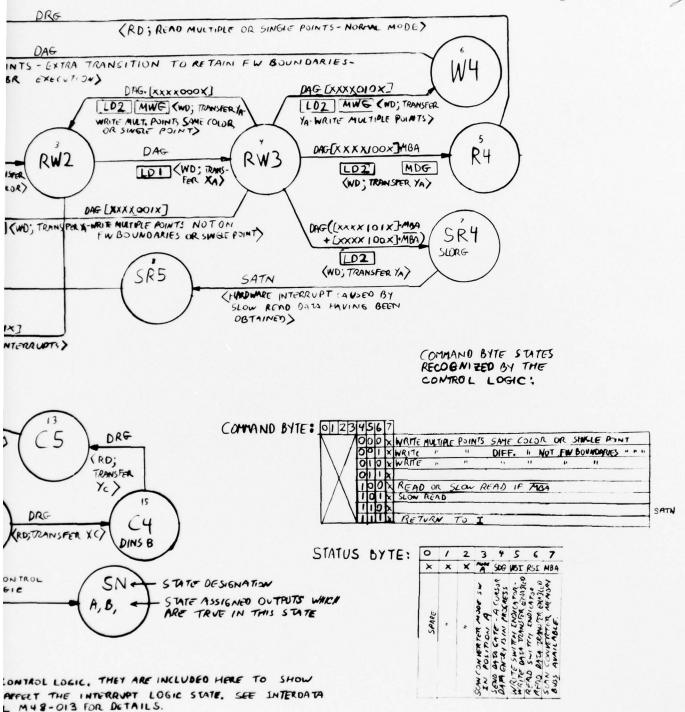

The Display Data Interface (DDI) includes a multitude of interfaces necessary so that the LWCA control panel, the Scan Converter (DCU and MIU), and the computer's Universal Logic Interface (ULI) can collectively communicate. These interfaces include A/D conversion of the trackball outputs, code-conversion, generation of precisely-timed control signals, temporary storage of data, routing of data, synchronization, and sequential control of data transfer operations. Reference to the DDI Block Diagram in Figure 4-12, unless otherwise specified, is implied in the following sections.

#### 4.6.1 Cursor Position

Digital binary-coded representation of cursor position (XC,YC) is derived from a mechanical trackball device\* on the LWCA control panel.

<sup>\*</sup>See Appendix for Data Sheet.

Figure 4-12. LWCA Control Panel and Display Data Interface (DDI)

Block Diagram

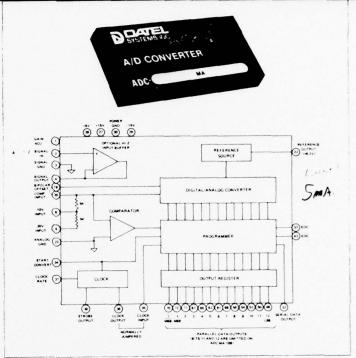

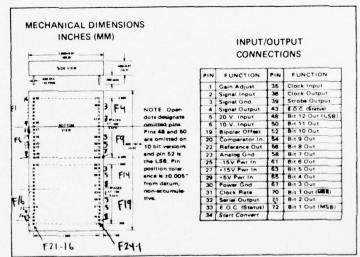

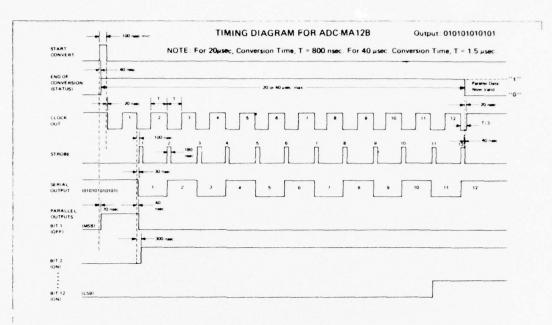

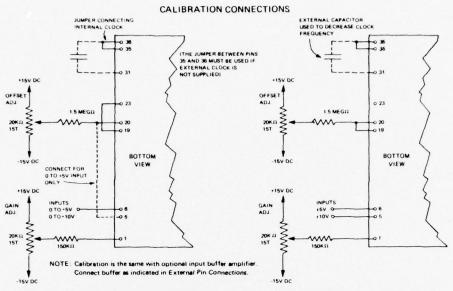

Bipolar voltages, obtained by zener regulation from the 15-volt supplies, are applied across the 10K trackball potentiometers. The resultant bipolar analog signals--one proportional to X-axis (left-right) displacement, the other to Y-axis displacement--are low-pass filtered and converted to binary-coded digital form in Datel ADC MA-10B modules\*.

The converter modules are set up so that an input voltage of -10 volts gives an all zeroes output, while +9.9951 volts yields all ones. Outside of this range, the converters limit. The Y-channel analog voltage range is +12 volts (the last two volts at either end is not used) and the most significant eight bits of the converter output are clocked into a register to become YC.

The X-channel analog voltage range has been limited by a series resistor to -12 to +3.4 volts, while the most significant <u>nine</u> bits of its converter output are clocked into a register to become XC. Although the X analog voltage is limited, it is possible to exceed XC = 319, which is beyond the right edge of the screen. This condition is discussed from an operational standpoint in AJJ-21, see appendix.

In order to remain compatible with Interdata notation, YC and the least-significant eight bits of XC are numbered with the most significant bit having the least subscript--just opposite to all other scan-converter documentation. The MSB of X is handled separately as XCM; for an illustration of display addressing convention, see Figure 2 of AJJ-21 in the Appendix.

The self-clocked, successive-approximation A/D converters begin a conversion once per raster-scan field, at the trailing edge of DY7. Conversion is inhibited when SDG, the send-data gate to be discussed later, is true. This feature prevents (XC, YC) from changing during a data transaction.

<sup>\*</sup>See Appendix for Data Sheet.

#### 4.6.2 Cursor Generation