# U.S. DEPARTMENT OF COMMERCE National Technical Information Service

AD-A034 856

DESIGN TOOLS FOR EVALUATING MULTIPROCESSOR PROGRAMS

CARNEGIE-MELLON UNIVERSITY PITTSBURGH, PENNSYLVANIA

JULY 1976

| SECOND & CLASSIFICATION OF THIS PAGE When Data butered                                                         |                                                                |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| REPORT DOCUMENTATION PAGE                                                                                      | READ INSTRUCTIONS BEFORE COMPLETING FORM                       |

| 1 REPORT NUMBER 2. GOVT ACCESSION                                                                              | N NO. 3. RECIPIENT & CATALOG NUMBER                            |

| AFOSR - TR - 77 - 0015                                                                                         |                                                                |

| 4 TITLE (and Subtitie)                                                                                         | 5. TYPE OF REPORT & PERIOD COVERED                             |

|                                                                                                                | Interim                                                        |

| DESIGN TOOLS FOR EVALUATING                                                                                    | 6. PERFORMING ORG. REPORT NUMBER                               |

| MULTIPROCESSOR PROGRAMS                                                                                        | 6. PERFORMING UNG. REPORT ROMBER                               |

| 7. AUTHOR(s)                                                                                                   | 8. CONTRACT OR GRANT NUMBER(#)                                 |

|                                                                                                                | 7//600 72 0 007/                                               |

| Philip Howard Mason                                                                                            | F44620-73-C-0074                                               |

| AND ADDRESS                                                                                                    | 10. PROGRAM FLEMENT PROJECT, TASK                              |

| 9 PERFORMING ORGANIZATION NAME AND ADDRESS Carnegie-Mellon Uniersity                                           | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS |

| Computer Science Dept.                                                                                         | 61101D                                                         |

| Pittsburgh, PA 15213                                                                                           | AO 2466                                                        |

| 11. CONTROLLING OFFICE NAME AND ADDRESS                                                                        | 12. REPORT DATE                                                |

| Defense Advanced Research Projects Agency                                                                      | 9 11 12 12 13                                                  |

| 1400 Wilson Blvd                                                                                               | 13. NUMBER OF PAGES                                            |

| Arlington, VA 22209                                                                                            | 203 (ice) 15. SECURITY CLASS. (of this report)                 |

| 14 MONITORING AGENCY NAME & ADDRESS(If different from Controlling Off                                          |                                                                |

| Air Force Office of Scientific Research (                                                                      | (NM) UNCLASSIFIED                                              |

| Bolling AFB, DC 20332                                                                                          | 15% DECLASSIFICATION DOWNGRADING                               |

|                                                                                                                | SCHEOULE                                                       |

| 16. DISTRIBUTION STATEMENT (of this Report)                                                                    |                                                                |

|                                                                                                                |                                                                |

| Approved for public release; distribution                                                                      | ı unlimited                                                    |

|                                                                                                                |                                                                |

|                                                                                                                |                                                                |

| 17 DISTRIBUTION STATEMENT (of the abstract entered in Block 20, If different                                   | ent from Report)                                               |

|                                                                                                                |                                                                |

|                                                                                                                |                                                                |

|                                                                                                                | ¶.                                                             |

| 18. SUPPLEMENTARY NOTES                                                                                        |                                                                |

| 18. SUPPLEMENTANT NOTES                                                                                        |                                                                |

|                                                                                                                |                                                                |

|                                                                                                                |                                                                |

|                                                                                                                |                                                                |

| 19 KEY WORDS (Continue on reverse side if necessary and identify by block no                                   | umber)                                                         |

|                                                                                                                |                                                                |

|                                                                                                                |                                                                |

|                                                                                                                |                                                                |

|                                                                                                                |                                                                |

| 20 ABSTRACT (Continue on reverse side if necessary and identify by block nu                                    | imber)                                                         |

| the designing programs for implementation                                                                      | - in a multiple instruction stream-                            |

| An approach to designing programs for implementation multiple data stream processing environment is presented. | n in a multiple instruction of our                             |

| multiple data stream processing environment is present directed graph consisting of two types of nodes: pr     | rocessing nodes and linking nodes.                             |

| Communication among nodes in the model is repres                                                               | cented by message tokens. Each                                 |

| processing node is similar in form to a semi-Mark                                                              | tou process. A simulation of the                               |

| operation of the model is nondeterministic, but is                                                             | hased on prescribed probabilistic                              |

| Operation of the model is notice terminated our is                                                             | Descu on Presentage Presentage                                 |

# DISCLAIMER NOTICE

THIS DOCUMENT IS THE BEST

QUALITY AVAILABLE.

COPY FURNISHED CONTAINED

A SIGNIFICANT NUMBER OF

PAGES WHICH DO NOT

REPRODUCE LEGIBLY.

24

ADA 034856

Design Tools for Evaluating

Multiprocessor Programs

Philip Howard Maser

approved for public release; distribution unlimited.

DEPARTMENT

of

COMPUTER SCIENCE

Carnegie-Midlion University

REPRODUCED BY

NATIONAL TECHNICAL

INFORMATION SERVICE

U.S. DEPARTMENT OF COMMERCE

SPRINGFIELD, VA. 22161

described and evaluation tools can be used to manipulate and act upon a model to predict performance of a program decomposition.

The design approach is to describe a multiprocessing program in terms of the modeling system. The model is examined to determine some analytic attributes of the model. The analysis available determines (a) whether the model is well formed, (b) whether the model contains deadlocks, (c) predictions of steady state properties of each process. In addition, without much difficulty, analysis functions external to STEPPS may be included as needed by a program designer.

Some analyses, that may be interesting, may be difficult to determine without resorting to simulation. Therefore the STEPPS system includes a model simulator with data collection facilities. The STEPPS data collection facilities include such measures as wait times and queue lengths. As in the case of analysis functions, STEPPS allows the inclusion of data collection facilities not originally provided by STEPPS.

As a system is designed, alternate models can be examined; and based on an individual designer's choice of performance attributes, a model can be chosen on which to base the construction of a multiprocessor program. As more is learned about the real system parameters, the model can be tuned to more closely predict ultimate system performance.

Several examples of communicating processes are modeled using STEPPS including pipeline processes, probabilistic processes, P/V synchronization, and reader/writer synchronization. Two experiments are presented as validation of the usefulness of the STEPPS tools. In the Bliss/11 experiment, the implications of restricting the numbers of available processors and using different scheduling algorithms were examined, and the effect of using alternate program structures was explored. In the Hearsay II experiment it was shown that, when a multiprocess program under development is sufficiently instrumented, the STEPPS model and system can be used to help tune the program's structure.

The use of the tools for predicting the performance of a multiprocessing program falls between purely analytic models, such as queueing theory or Petri-nets, and system simulations built in a general purpose simulation language. The STEPPS system is presented as a new approach to designing multiprocessing programs.

# Design Tools for Evaluating Multiprocessor Programs

Philip Howard Mason

Department of Computer Science Carnegie-Mellon University Pittsburgh, Pa. 15213 July, 1976

Submitted to Carnegie-Mellon University in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

This research was supported by the Defense Advanced Research Projects Agency of the Office of the Secretary of Defense (F44620-73-C0074) and is monitored by the Air Force Office of Scientific Research.

#### **Abstract**

An approach to designing programs for implementation in a multiple instruction stream-multiple data stream processing environment is presented. A program is modeled as a directed graph consisting of two types of nodes: processing nodes and linking nodes. Communication among nodes in the model is represented by message tokens. Each processing node is similar in form to a semi-Markov process. A simulation of the operation of the model is nondeterministic, but is based on prescribed probabilistic choice functions. A system, called STEPPS, has been built in which a model can be described and evaluation tools can be used to manipulate and act upon a model to predict performance of a program decomposition.

The design approach is to describe a multiprocessing program in terms of the modeling system. The model is examined to determine some analytic attributes of the model. The analysis available determines (a) whether the model is well formed, (b) whether the model contains deadlocks, (c) predictions of steady state properties of each process. In addition, without much difficulty, analysis functions external to STEPPS may be included as needed by a program designer.

Some analyses, that may be interesting, may be difficult to determine without resorting to simulation. Therefore the STEPPS system includes a model simulator with data collection facilities. The STEPPS data collection facilities include such measures as wait times and queue lengths. As in the case of analysis functions, STEPPS allows the Inclusion of data collection facilities not originally provided by STEPPS.

As a system is designed, alternate models can be examined; and based on an individual designer's choice of performance attributes, a model can be chosen on which to base the construction of a multiprocessor program. As more is learned about the real system parameters, the model can be tuned to more closely predict ultimate system performance.

Several examples of communicating processes are modeled using STEPPS including pipeline processes, probabilistic processes, P/V synchronization, and reader/writer synchronization. Two experiments are presented as validation of the usefulness of the STEPPS tools. In the Bliss/11 experiment, the implications of restricting the numbers of available processors and using different scheduling algorithms were examined, and the effect of using alternate program structures was explored. In the Hearsay II experiment it was shown that, when a multiprocess program under development is sufficiently instrumented, the STEPPS model and system can be used to help tune the program's structure.

The use of the tools for predicting the performance of a multiprocessing program falls between purely analytic models, such as queueing theory or Petri-nets, and system simulations built in a general purpose simulation language. The STEPPS system is presented as a new approach to designing multiprocessing programs.

#### **ACKNOWLEDGEMENT**

I sincerely thank my thesis committee who with their advice, guidance, and criticism of this thesis helped me to maintain their high standards: Bill Wulf (chairman), Sam Fuller, Charles Kriebel, Victor Lesser, and Mary Shaw. I am grateful for having been associated with the Carnegie-Mellon Computer Science Department and I must acknowledge the initial, and continuing, inspiration gleaned from Alan J. Perlis, my first computer science teacher, former Carnegie-Mellon department head and supervisor. In addition, I am grateful for the interest, support, and assistance from my friends, colleagues, family, and especially my parents.

Most of all, I thank my wife, Lee, for suffering through all the lonely nights (and days), for helping me to rewrite many pages, for learning to use the computer to type this thesis, for keeping me going, and for her understanding.

# TABLE OF CONTENTS

|     |                 | CHAPTER                                                        | PAGE       |

|-----|-----------------|----------------------------------------------------------------|------------|

| 1   | Problem Statem  | ment, History and Goals                                        |            |

|     | I.A             | Introduction                                                   | I-1        |

|     | I.B             | Diraction of this work                                         | I-5        |

|     | I.C             | Other work bearing on the problem                              |            |

|     | I.D             | The STEPPS System                                              | I-15       |

|     | I.E             | The STEPPS system and simulator                                | I-24       |

|     | 1.F             | Thesis contributions and outline of remainder of thesis        | I-29       |

| II  | The STEPPS M    | odel                                                           |            |

|     | II.A            | Modeling the behavior of a process                             | II-1       |

|     | II.B            | Data flow and links                                            | II-3       |

|     | II.C            | Notation and definitions                                       | II-6       |

|     | II.D            | STEPPS system capabilities                                     | II-11      |

| III | The Use of the  | STEPPS Approach to Program Design                              |            |

|     | III.A           | Use of the STEPPS model                                        | III-1      |

|     | III.8           | Using STEPPS during system design: A Bliss/11 compiler         | III-12     |

|     | III.C           | Using STEPPS during system construction and tuning: Hearsay II | îII-28     |

| IV  | Analysis of a S | STEPPS Model                                                   |            |

|     | IV.A            | Markov and semi-Markov processes                               | . , . IV-1 |

|     | IV.B            | Well-formed STEPPS models                                      | IV-6       |

|     | IV.C            | Deadlock structures and situations                             | IV-8       |

|     | IV.D            | Reducing a STEPPS model                                        | IV-13      |

|           | IV.E              | The recognition of deadlocks                    |

|-----------|-------------------|-------------------------------------------------|

| ٧         | The STEPPS Simu   | lator and STEPPS Interactive System             |

|           | V.A               | Simulation objectives V-1                       |

|           | V.B               | Simulation operation and data collected V-3     |

|           | V.C               | The implementation of the STEPPS system $V-10$  |

| VI        | Summary           |                                                 |

|           | VI.A              | Designing programs for multiprocessor computers |

|           | VI.B              | Experiments and results VI-5                    |

|           | VI.C              | Future research and refinements to STEPPS VI-9  |

|           | VI.D              | Conclusions VI-12                               |

| Α         | STEPPS System N   | Manual                                          |

|           | A.1               | Introduction                                    |

|           | A.2               | Model creation                                  |

|           | A.3               | Model analysis and system commands              |

|           | A.4               | Simulation commands                             |

|           | A.5               | Keyword commands                                |

| В         | Using the STEPP   | S System                                        |

|           | B.1               | Bliss/11 example protocol                       |

|           | B.2               | The STEPPS Hearsay II model                     |

| С         | Validation of Sim | ulation Results                                 |

| Bibliogra | iphy              |                                                 |

| Index .   |                   |                                                 |

# FIGURES .

|              | FIGURE                                                                 | PAGE     |

|--------------|------------------------------------------------------------------------|----------|

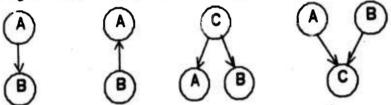

| Figure I-1   | Possible relationships between two proceses, A and B                   | I-5      |

| Figure I-2   | A marked graph                                                         | I-10     |

| Figure I-3   | A finite state atomaton                                                | I-10     |

| Figure I-4   | A Petri net that is neither a marked graph nor a finite state atomaton | I-11     |

| Figure I-5   | UCLA modei nodes                                                       | I-13     |

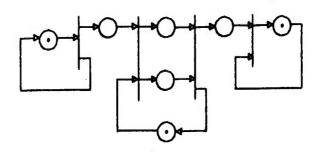

| Figure I-6   | Pipeline                                                               | I-17     |

| Figure I-7   | Registrar's data retrieval system                                      | I-20     |

| Figure I-8   | Process ALPHA                                                          | I-21     |

| Figure I-9   | Mapping between Petri nets and STEPPS model                            | I-23     |

| Figure I-10  | Mapping of UCLA model to STEPPS                                        | I-24     |

| Figure I-11  | Incompatible loop                                                      | I-27     |

| Figure I-12  | Incompatible non-loop                                                  | I-27     |

| Figure II-1  | Process and link graphical notation                                    | II-8     |

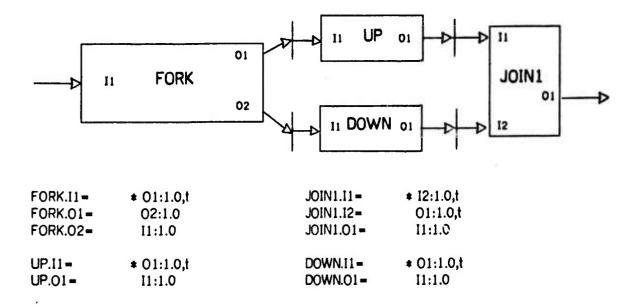

| Figure III-1 | Fork and join processes                                                | III-2    |

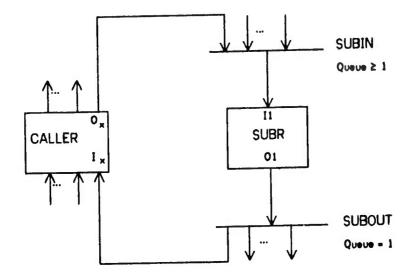

| Figure III-2 | Subroutine process                                                     | III-4    |

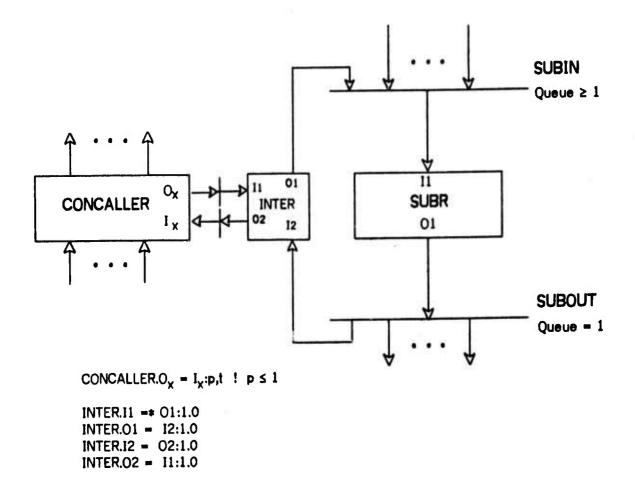

| Figure III-3 | Concurrent processing subroutine call                                  | III-5    |

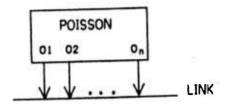

| Figure III-4 | Poisson arrival process                                                | III-6    |

| Figure III-5 | General service time process                                           | III-7    |

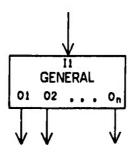

| Figure III-6 | Pipeline of processes                                                  | III-8    |

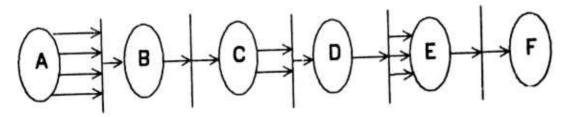

| Figure III-7 | Lock/Uniock synchronization                                            | . III-10 |

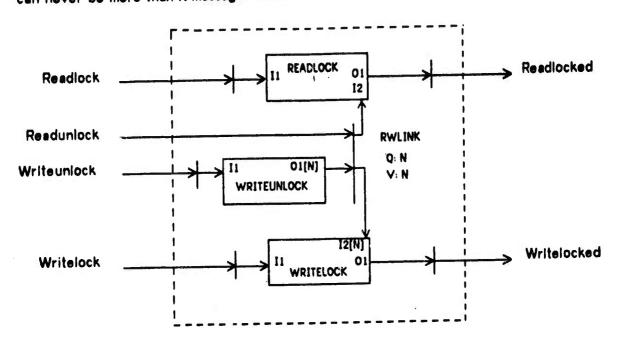

| Figure III-8 | Reader/Writer synchronization                                          | . III-11 |

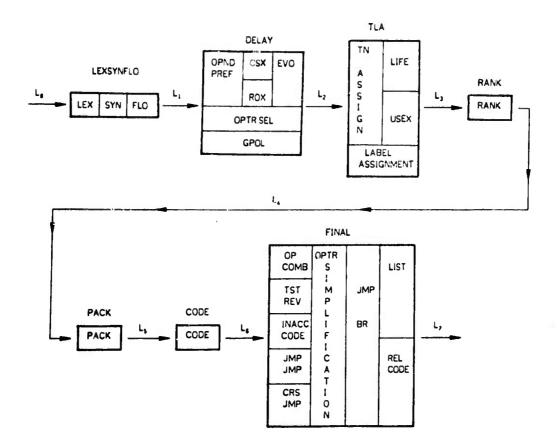

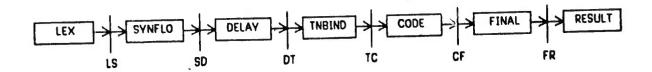

| Figure III-9 | Biiss/11 phase structure                                               | III-13   |

FIGURES

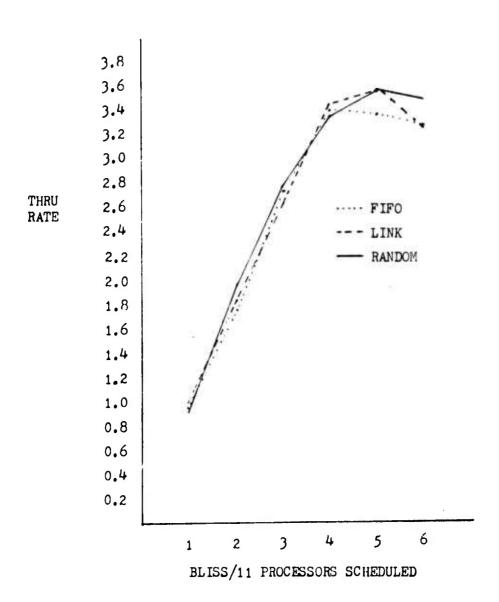

| Figure III-10 | Bliss/11 measured data                                         | 111-17 |

|---------------|----------------------------------------------------------------|--------|

| Figure III-11 | STEPPS Bliss/11 model commands                                 | III-17 |

| Figure III-12 | Bliss/11 graph model                                           | III-18 |

| Figure III-13 | Bliss/11 simulation FIFO table                                 | III-18 |

| Figure III-14 | Bliss/11 simulation LINK table                                 | III-19 |

| Figure III-15 | Bliss/11 simulation RANDOM table                               | III-19 |

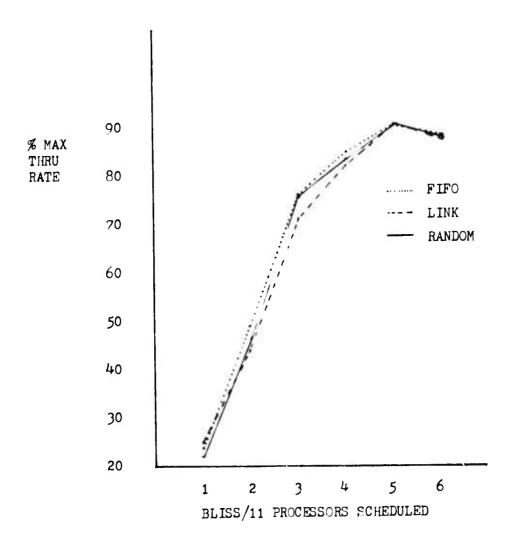

| Figure III-16 | Bliss/11 percentage maximum throughput                         | 111-20 |

| Figure III-17 | Graph of measured throughput                                   | III-21 |

| Figure III-18 | Bliss/11 simulation FIFO queue lengths                         | III-22 |

| Figure III-19 | Bliss/11 simulation LINK queue lengths                         | 111-23 |

| Figure III-20 | Bliss/11 simulation RANDOM queue lengths                       | 111-23 |

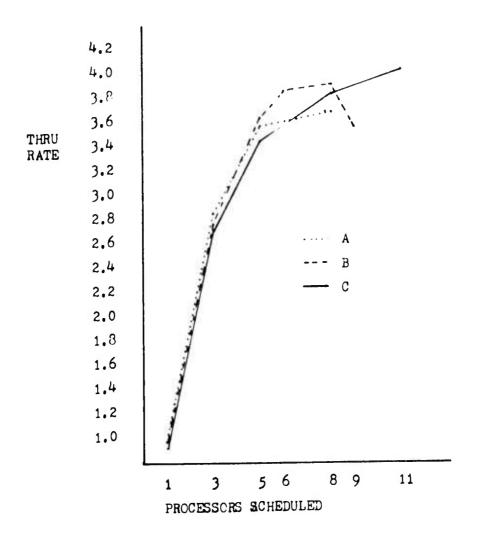

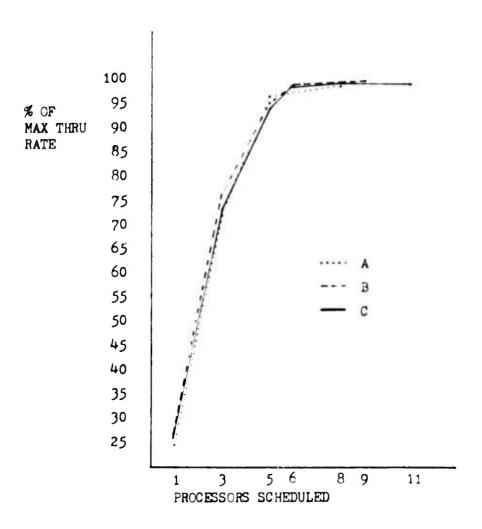

| Figure III-21 | Table of results of multi-copy Bliss/11 phase models           | 111-24 |

| Figure III-22 | Multi-copy Bliss/11 phase model Thru Rate graph                | III-25 |

| Figure III-23 | Multi-copy Bliss/11 phase model percentage Max Thru Rate graph | 111-26 |

| Figure III-24 | LEX decomposition results                                      | 111-27 |

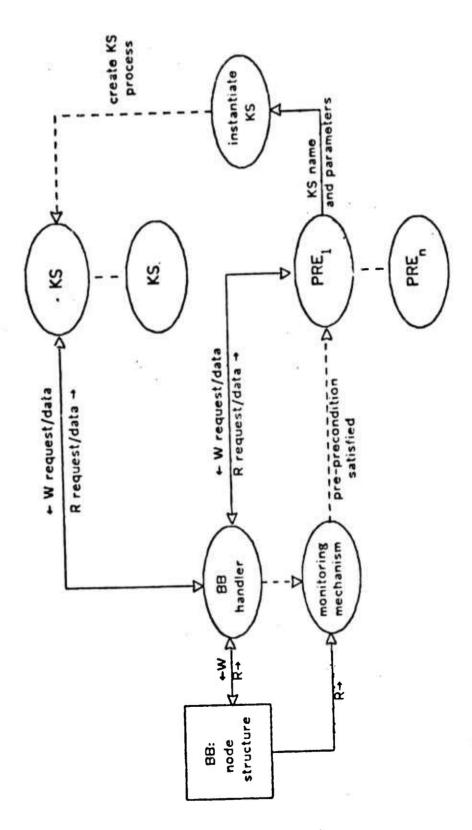

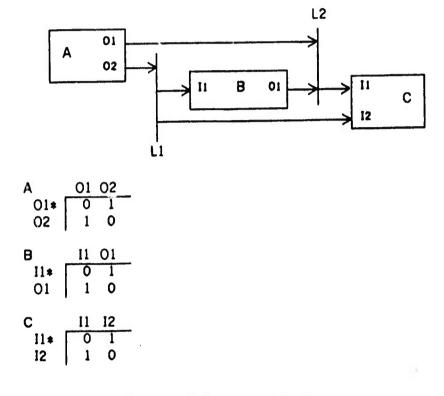

| Figure III-25 | Simplified HSII system organization                            | 111-32 |

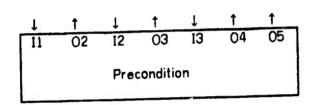

| Figure III-26 | Description of precondition process                            | 111-33 |

| Figure III-27 | STEPPS precondition model                                      | 111-33 |

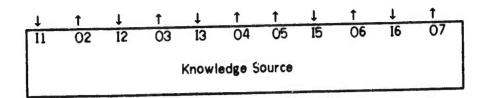

| Figure III-28 | Knowledge Source process description                           | III-34 |

| Figure III-29 | STEPPS Knowledge Source model                                  | 111-35 |

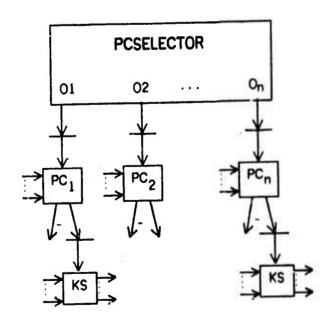

| Figure III-30 | PCSELECTOR process                                             | 111-35 |

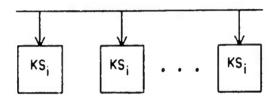

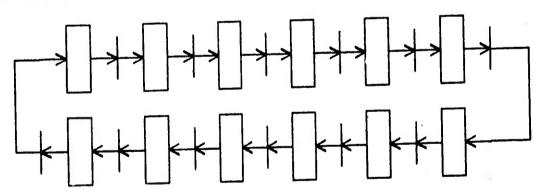

| Figure III-31 | Set of identical Knowledge Sources                             | 111-36 |

| Figure III-32 | Hearsay II locking structure matrix                            | III-40 |

| Figure III-33 | Hearsay II representative results                              | III-42 |

| Figure IV-1  | Markov processes                           | IV-3  |

|--------------|--------------------------------------------|-------|

| Figure IV-2  | Improper initial condition                 | IV-10 |

| Figure IV-3  | Loop with immediate-recurrent states       | IV-11 |

| Figure IV-4  | Incompatible sequence                      | IV-12 |

| Figure IV-5  | Link split paths                           | IV-13 |

| Figure IV-6  | Process split paths                        | IV-13 |

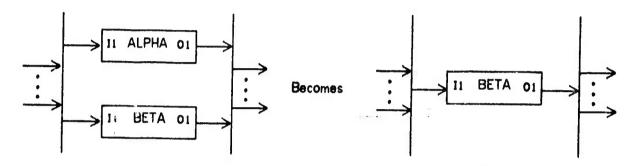

| Figure IV-7  | Process combinations                       | IV-18 |

| Figure IV-8  | Adjacent ports of a process                | IV-21 |

| Figure IV-9  | Ports attached to SOURCE/SINKS             | IV-23 |

| Figure IV-10 | Combining processes that are in-parallel   | IV-25 |

| Figure IV-11 | An irreducible graph                       | IV-29 |

| Figure V-1   | A ring of processes                        | . V-2 |

| Figure C-1   | Bliss/11 FIFO 6 processors evaluation data | C-2   |

# Chapter I

# Problem Statement, History and Goals

#### I.A. Introduction

This research develops both a methodology for enhancing the design of programs to be composed of concurrently executable subparts and a set of tools to support that methodology. The execution environment which we shall be concerned with consists of several processing units operating under the control of separate instruction streams. Intuitively, when parts of a program are processed in such an environment, the real time<sup>†</sup> required to execute the program should decrease<sup>‡</sup>. For this reason, as well as others, much current research effort addresses program structure for just such a multiprocessing environment. This thesis addresses the problem of decomposing programs for concurrent execution in such a way that the decompositions are efficient with respect to certain specifiable criteria. The approach is to provide a set of tools with which a system designer can manipulate and analyze a program model created to predict the performance of a system designed for a multiple asynchronous instruction stream environment. The tools are applicable to both the early design of a program and later tuning of a program under construction.

T"Real time" is the time elapsed between the start of computation and the time the final result is available. It is different from the total processing time since operations may be performed concurrently.

<sup>&</sup>lt;sup>‡</sup>This does not always occur. Graham [Graham 72] has shown that adding more processors can increase real time due to scheduling anomalies.

There are several reasons why many researchers are considering multiprocessing and problem restructuring in favor of merely building faster computer hardware without explicit concurrency. First, certain problems overwhelm current and projected technology when programmed for single Instruction stream computers. An example is the problem of weather forecasting for any single place on the earth. At present, this problem can not be solved with enough lead time to make the forecast useful. Another large problem is fast-response scheduling, cost accounting, and resource management for large corporations. In this problem the mathematical computations are not necessarily as complex as those for weather forecasting, but the amount of data processing required can be extremely large and, as for weather prediction, there is a time constraint on the answers. For each of these problems, a solution might be attainable in a reasonable period of time if some of the computations could be distributed and executed in parallel. Among the unknown factors are how the problems should be decomposed for distributed processing and what communication constraints and processing attributes elicit favorable computational attributes (such as real time speed and low cost).

There may also be economic incentives to implement a program in a multiprocessing environment. For example, it may be less expensive to implement a speech understanding system on a set of minicomputers than on one fast and relatively complex uniprocessing computer. The price benefits may occur because of

- 1. the use of so called off-the-shelf equipment making total processing power cheaper than large uniprocessing machines, and

- 2. economies of scale in manufacturing.

Perhaps the most compelling reason (possibly a consequence of the first two) for wanting to decompose programs for multiprocessing environments is that such

environments are now available and it is important to use them properly. C.mmp [Wulf 72b], BBN Pluribus IMP [Heart 73], the Burroughs D825 [Anderson 62], UC Berkeley's Prime [Quatse 72], and UC Irvine's DCS [Farber 75] all have some multiprocessing capabilities. Additionally Clark's macromodules [Clark 72], Bell's register transfer modules (DEC PDP-16) [Bell 72] and the similarly oriented projects of Fuller and Slewlorek [Fuller 73], and others offer multiprocessing on a very low level.

There are, at present, no guidelines for decomposing a problem for multiprocessing execution [Newell 75]. A number of questions related to the discovery of such guidelines have been investigated. These include:

- Can a problem be decomposed for solution in a multiprocessing environment? [Karp 66, Gosden 66, Miranker 71, Dennis 71, Anderson 65, Rosenfeld 69]

- 2. How can the algorithmic structure of a multiprocessing task be represented? [Adams 70, Baer 70, Bredt 70, Dennis 71, Dennis 73a, 73b, Karp 69, Lesser 72, Miller 73, Noe 73]

- 3. Will the same results always occur, namely will a multiprocessing system be deterministic? Can a multiprocessing system be proven correct? Are there potential deadlocks and unattainable states? This is somewhat analogous to discovering infinite loops and impossible conditions in a sequential program. [Karp 69, Keller 73a, 73b, Riddle 72]

- 4. When are two computations the same? [Karp 69, Keller 73a, 73b]

- 5. What measures are interesting about the computation? Some may be: speed, redundancy, (in)efficiency, resource utilization, and economies of the components. [Browne 73, Lehman 66]

- 6. How can the system be scheduled when there are scarce resources? [Adam 72, Graham 72]

- 7. How can bottlenecks be identified and their effects lessened or climinated? [Courtois 72, Dijkstra 74, Rice 73]

- 8. What are the effects of restructuring the communications among the cooperating processes? [Balzer 71, Horning 73]

- 9. What style of decomposition and machine structure would L st suit a particular programming system (eg. Illiac IV, STARAN, STAR-100, ASC, C.mmp, etc.)? [Flynn 66]

1-3

environments are now available and it is important to use them properly. C.mmp [Wulf 72b], BBN Pluribus IMP [Heart 73], the Burroughs D825 [Anderson 62], UC Berkeley's Prime [Quatse 72], and UC Irvine's DCS [Farber 75] all have some multiprocessing capabilities. Additionally Clark's macromodules [Clark 72], Bell's register transfer modules (DEC PDP-16) [Bell 72] and the similarly oriented projects of Fuller and Slewiorek [Fuller 73], and others offer multiprocessing on a very low level.

I.A Introduction

1

There are, at present, no guidelines for decomposing a problem for multiprocessing execution [Newell 75]. A number of questions related to the discovery of such guidelines have been investigated. These include:

- 1. Can a problem be decomposed for solution in a multiprocessing environment? [Karp 66, Gosden 66, Miranker 71, Dennis 71, Anderson 65, Rosenfeid 69]

- 2. How can the algorithmic structure of a multiprocessing task be represented? [Adams 70, Baer 70, Bredt 70, Dennis 71, Dennis 73a, 73b, Karp 69, Lesser 72, Miller 73, Noe 73]

- 3. Will the same results always occur, namely will a multiprocessing system be deterministic? Can a multiprocessing system be proven correct? Are there potential deadlocks and unattainable states? This is somewhat analogous to discovering infinite loops and impossible conditions in a sequential program. [Karp 69, Keller 73a, 73b, Riddle 72]

- 4. When are two computations the same? [Karp 69, Keller 73a, 73b]

- 5. What measures are interesting about the computation? Some may be: speed, redundancy, (in)efficiency, resource utilization, and economies of the components. [Browne 73, Lehman 66]

- 6. How can the system be scheduled when there are scarce resources? [Adam 72, Graham 72]

- 7. How can bottlenecks be identified and their effects lessened or eliminated? [Courtois 72, Dijkstra 74, Rice 73]

- 8. What are the effects of restructuring the communications among the cooperating processes? [Baizer 71, Horning 73]

- 9. What style of decomposition and machine structure would best suit a particular programming system (eg. Illiac IV, STARAN, STAR-100, ASC, C.mmp, etc.)? [Flynn 66]

The last question points out that there are several styles of multiprocessing.

Flynn [Flynn 66] described processing organization in four ways:

single instruction stream - single data stream(SISD),

single instruction stream - multiple data streams (SIMD),

multiple instruction streams - single data stream (MISD), and

multiple instruction streams - multiple data streams (MIMD).

These computing styles may be used to describe an entire computing environment and affect a problem's decomposition and algorithms. However those systems that do not allow a programmer to program explicitly for multiple streams of data or instructions will be considered as single stream machines. For example, any multiprogramming machine performs some operations concurrently (e.g. 1/O), but a programmer is usually unable to control this concurrency. In an array or associative processor a control unit specifies which operation is performed simultaneously on many data items simultaneously — these are SIMD machines. The current pipeline machines (CDC STAR-100, TI ASC) perform parts of single operations on several pieces of data. The programmer has no control over which operations are performed concurrently, so these are also single instruction stream machines. Even in multiple instruction stream processing there can still be a spectrum of communication schemes. Networks of computers and multiprocessing computers with common memory are are defined to be multiple instruction stream machines only when a programmer can specify concurrent operations and these operations can be performed concurrently.

A multiple Instruction stream program is defined to be a program in which two subparts of the program can be specified to execute concurrently. Since these are

<sup>&</sup>lt;sup>†</sup> A pipeline machine has multiple data streams as far as a programmer is concerned, but actually the stream of data comes into the pipe sequentially.

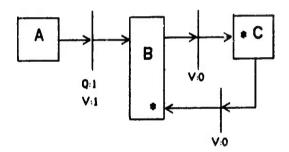

in the form of some common data communication and/or sharing. If the subparts are named A and B then at least one of the following must occur: data progress from A to B, from B to A, from some C to A and B, or from A and B to some C. (Figure I-1 shows the possible relationships between two processes in a directed graph notation) When data progress from one program to another it means that the second program uses some results of the first in its computations. Of course, other processing may manipulate the data between the processing of two subprograms and additional data may be provided to the second program from sources other than the first program (and the first program can provide data to other programs).

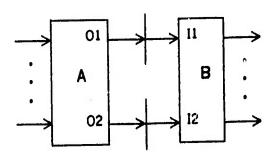

Figure I-1. Possible relationships between two processes, A and B

If A and B are related, one of these relationships must hold; otherwise A and B would be unrelated and thus not subparts of the same program. In the first and second cases one subprogram sends data to the other and continues to process after sending data to the second subprogram. In the third case, data can progress to both A and B from a common source and all three can be processed at the same time. In the last case, A and B can be processed simultaneously and each is able to send data to the same third process, C.

# J.B. Direction of this work

At present there are no proven guidelines on how to structure a problem for implementation in a multiple-instruction-stream multiprocessing environment. Rather than address the guidelines problem directly, this work presents a design environment, a set of evaluation tools, and a design approach whereby a system designer can explore attributes of alternative program decompositions. A major premise for this research is that the communication pattern among concurrent processes is critical to a system's performance. The goal is to identify issues and to make predictions which will provide some practical information to the system designer at an early stage and also during later program tuning. This research has been directed towards solving a more specific set of problems than those presented in the previous list, namely:

- 1. How can interactions among the concurrent computations be modeled?

- 2. Are the interactions safe, i.e. deadlock free? For example, can one show that a program never arrives at a state in which one process is trying to communicate with a second process while the second is waiting to send a communication to the first process?

- 3. When the structure is not deadlock free, what is the probability of a deadlock?

- 4. Where will most of the process and communication activity occur?

- 5. Where may bottlenecks occur, and how may they be relieved? For example, will the introduction of buffers or additional processes help?

- 6. Are there working sets of processes? If certain subsets of processes tend to be active at different times then fewer processors will be required for a program (and consequently less parallelism can be attained).

- 7. What are the effects of restricting the number of processors? What are the effects of alternative scheduling algorithms?

These questions were chosen because they may present hidden problems to

the system designer. Inexpensive and fast approximate answers to these questions should be useful when a program is being designed and also when it is being tuned to improve a program's performance.

Currently there are no generally accepted languages or graphical techniques for representing or modeling a multiprocessing computation and the communication interactions among processes. Thus problems that might be prevented by a clear algorithmic description technique may still occur. However a system designer has some understanding of the relationships among the parts of his system. He can implement the subparts in many different languages, but it is the interfaces between the subparts that are usually not well described. Parnas [Parnas 71] has suggested communication schema to be used while creating communicating modules, but has not described how to represent the communications in an entire system. This lack of global view may prevent the recognition of potential problems. This, then, illustrates the importance of discovering a method for the automatic detection of deadlocked structures and potential deadlocked structures. If the system designer can easily identify in advance where he may have made such an error, then he is spared the task of finding the problem later. It would be preferable to prevent such problems, since many of the criteria for preventing deadlocks are known; however, in complex systems it is increasingly difficult to be aware of all potential deadlock conditions.

If the system designer is able to estimate which particular subparts of his system will contain the largest amount of activity, then these subparts will be the most appropriate places to expend effort to improve performance.

The ability to compare the potential performance of alternate systems easily is extremely important. Almost all disciplines concerned with the creation of large

system and extrapolating the performance of this model to deduce properties of the large system. Examples of this technique range from the use of wind tunnels and analog simulation of fluid flow to discrete computer simulations of supermarket check-out counters. A tool for the prediction of computer system decomposition performance should be just as useful. An important aspect of a design system is how easily the designer can alter the attributes of his system and determine the effects of those changes.

We feel that important assets of design tools are that they:

- 1. be easy to use,

- 2. provide results quickly,

- 3. be interactive (when using a computer system), and

- 4. make it easy to perform design Iterations.

# I.C. Other work bearing on the problem

Several kinds of tools are available to a system designer. These tools include graph models, queueing theory models, simulation languages, programming languages and theories of design of complex systems. Each of these tools can be useful at some time during the design and construction of a multiprocessing program. Graph models are usually used to represent multiprocessing computations and for analysis of control flow within a program. Queueing theory is used to predict and study performance of simplified models of complex processes. Simulation is an approach to modeling more complex systems to obtain similar performance predictions. Programming languages

are tools for explicitly representing multiprocess algorithms. They also may contain primitive operators that can facilitate proofs of properties of programs. Design theories, such as that of Parnas, provide techniques that facilitate construction of complex systems and their understanding. No one tool is comprehensive enough to use as a quickly obtained predictor of the performance of a multiprocess program.

With sufficient instrumentation the behavior of a multiprocess program can be measured. These data can be used in several ways to predict behavior changes when some system parameters and structures are modified. Again queueling theory and simulation techniques are useful tools for these predictions. As before neither method necessarily provides fast predictions of the sensitivity of performance to changes in program parameter and structure.

The following are brief presentations of some tools that bear a relationship to those that will be presented later. It will be seen that the purely analytic techniques are often too restrictive on assumptions, not useful for overall program design, and of limited applicability due to computational complexity. The simulation techniques require too much effort both to construct a simulation and to modify it to achieve results concerning alternate program decompositions.

#### I.C.1. Petri neta

After the original formulation of Petri nets [Petri 62] several MIT researchers [Dennis 70, Holt 70, Paterson 70, Rodriguez 67] refined forms of the original model as useful tools for studying concurrent processes. A Petri net looks like a directed graph in which marks or tokens are placed on some of the arcs. (Only connected graphs are of interest.) These tokens move about the graph to represent flow of control. When

TO Other Mork Dominie on the broaden

tokens are present on all of the Input arcs to a node, that node is able to "fire." After a node fires, one token is removed from each input arc and a token is placed on each output arc of that node. In fact, a Petri net is not a directed graph [Berge 62] because it is possible for one arc to point to or come from more than one node. A restricted Petri net called a marked graph [Holt 70] permits arc initiation and termination only at single nodes (not necessarily the same). Multiple arcs can still be connected to each node. In contrast, a restricted Petri net becomes a finite state automaton (state transition diagram [Holt 70]) by only permiting one arc to enter each node and one arc to leave each node. (Arcs can have multiple starting points and terminal points.) In Figures I-2, I-3, and I-4 the nodes are represented by straight lines and the arcs are arrows with a circle that can contain the tokens (represented by dots).

Figure I-2. A Marked graph

Figure I-3. A finite state atomaton.

Figure I-4. A Petri net that is neither a marked graph nor a finite state atomaton.

Marked graphs are the only form of Petri nets that have been used to study concurrent processes. The general Petri net can be too complex and the state transition diagram can not be used to model concurrent processing. Marked graphs are used by modeling the potential flow of control in a system and then analyzing possible markings in order to make predictions about future markings. Issues investigated, for a particular inital marking, include:

- Determine whether nodes will eventually activate (fire). In Petrl net terminology the question is whether a node is "safe" [Holt 70]. If all nodes are safe the net is "safe," i.e. all nodes can be activated.

- 2. Count the number of activations of a node. The important counts are 0, n, and infinity.

- Determine whether the initial marking can lead to another particular marking.

- 4. Identify nodes that can fire concurrently.

There are several difficulties in using Petri nets. One is that interesting examples require a large number of nodes [Dennis 70, Merlin 75]. There are so many nodes that it is difficult to do any analysis. In addition, none of the analysis is mechanical. Another difficulty is that control flow in the graphs is completely determined with no accounting for rates of processing at each node.

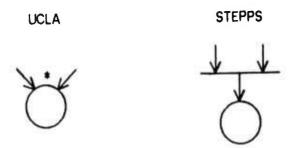

The original goal of the UCLA model was to "represent programs to be run on variable structure computers" [Baer 73, Estrin 63]. Thus its purpose was to help describe concurrent computations rather than to study the performance of algorithms. However some extensions of, and associated restrictions on, the original model allow for performance predictions in some restricted cases to determine the termination of loops, the determinacy of representations [Regis 72], and the reduction of graphical forms [Bovet 69]. In addition the UCLA model has been used to study the automatic conversion of FORTRAN-like programs to a parallel computation form.

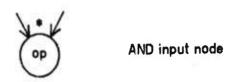

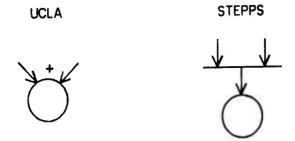

The basic form of the model is a directed binary graph. Most studies using this model use an acyclic structure. The graph shows processing dependencies and, as iong as an acyclic model is used, potentially concurrent operations can be easily identified. Each node may have at most two entry arcs and also at most two exit arcs. The rules for firing a node are defined as part of the node. The node's firing rule depends on the enabling of the input arcs and the node's result rule cause some of its output arcs to be enabled. A node will not fire if any of its output arcs are already enabled. Once a node fires the input arcs causing that node to fire are disabled. (See Figure 1-5)

In the UCLA model, branching and merging control flow are modeled with EOR type nodes. Concurrency is modeled by the use of AND type nodes.

Further restrictions are placed on the form of the UCLA graph model. There must be a unique initial vertex (only output arcs) and a unique terminal vertex (only input arcs). Another restriction is that all subgraphs must be AND type. This means that if a choice is made at an EOR output node then it must still be possible for the

AND input type fires only if both input arcs have been enabled.

**EOR** input node

EOR input type fires only if exactly one of the input arcs has been enabled.

AND output node

AND output type enables both of the node's output arcs after the node has fired.

EOR output node

EOR output type enables exactly one of the node's output arcs after a node has fired (which one is undetermined).

Figure I-5. UCLA Model Nodes.

Input node to fire. In addition it should not be possible for both arcs of an EOR input node to be enabled at once. The question of determinacy of a graph is subsumed by the question of legal graphs. Legal graphs are those that start at the initial node and are guaranteed to terminate at the terminal node. When loops are

allowed, any loop must be able to terminate. Most who have used the model have assumed acyclic structures in order to guarantee loop termination (naturally, no loops). The analytic technique used to ignore loops is to expand all loops by some finite repetition. The repetition factor is determined by a probabilistic argument [Martin 67].

The question of mean path length in a directed acyclic binary graph has been studied at UCLA. Probabilities are assigned to each arc and computation times are assigned to each node. These are used to determine the probability of traversing paths through a legal graph and to estimate the mean path time of a graph [Martin 69]. One may also determine the maximum number of processors required by the graph [Baer 69] under the same restrictions.

The difficulties with using the UCLA model also involve the need for a large number of nodes to represent interesting structures. This is particularly true since each node has at most two input arcs and at most two output arcs. Another problem is that most results have been dependent on acyclic models. Thus the mechanical techniques for proving legal graphs, etc. are only applicable to a restricted set of programs representable by the model.

### I.C.3. An algebraic model of interprocess communication

In his dissertation [Riddle 72], Riddle presented a methodology for modeling and analyzing supervisory systems, but the work can be applied to the problem of analyzing any complex asynchronous system. He found the same difficulties with Petri nets and other models as those reported in earlier sections of this chapter.

Riddle presented an explicit program-like description of the operation of a process. This description was only concerned with the interprocess communication

relationships of each process. However the description was close enough to being a program that each process required information concerning the type of interprocess messages. Therefore the descriptions of processes were themselves fairly complex.

The model was also based on a directed graph structure representing interprocess communication. A graph consisted of two types of nodes, process nodes and link nodes. The link nodes had properties that could require a certain amount of computation associated with them, e.g. queueing disciplines.

One of the goals of Riddle's research was the development of an algebra to describe interprocess communication. Algebraic expressions could be used to describe possible communication paths in a model. By using the graphical structure, the program-like descriptions, and the algebraic expressions, theorems were developed to analyze the behavior of a modeled system. The creation of all algebraic expressions is performed by the inspection of a graph. The proof of theorems concerning the behavior of a system, as described by the algebra, is not a mechanical process. Riddle did provide a set of theorems that can be used in a proof.

The examples that Riddle studied were based on communication paths of a given system. He determined what termination and deadlock meant for that system and was able to derive proofs showing that the system terminated and contained no deadlocks. The questions he posed were specific to the system being modeled and required the creation of algebraic expressions for each question concerning system behavior. These algebraic expressions were not necessarily easy to create and the proofs of theorems were not very easy to construct.

The tools that Riddle's research provides may be used for the design of multiprocessing programs. The drawbacks to his approach are the difficulty and effort

required to create the algebraic expressions needed to represent a model, and the expressions representing communication within a model. The expression proof process is also fairly tedious.

# I.D. The STEPPS System

All of the models discussed in the previous section are tools for the analysis of multiprocess programs. A common drawback of each model is that results must be obtained through detailed, non-mechanical analysis. A second drawback is that none contains the processing rates of the various processes of a multiprocess program as part of the model. The speed and ease of obtaining results and the ability to include expected timing of attributes of a program can be especially useful when making early design decisions concerning the structure of a program.

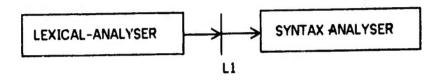

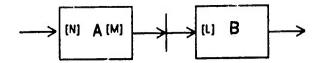

The design methodology presented in this thesis is based on an interactive system utilizing a particular model of muitiple instruction stream problem decomposition. The system and the model are called STEPPS (Some Tools for Evaluating Parallel Processing Systems). The methodology of designing a programming system has become an interesting and important question in the last few years [Brinch Hansen 74, Dahl 72, Mills 71, Parnas 72, Parnas 75, Weinberg 71]. The author subscribes to the "top down" approach to system design [Simon 62]. Thus a "natural" approach to building a system that will contain potentially concurrently executing subparts is to decompose a system into functionally independent subparts and describe the communication structure among the subparts before explicitly defining the operation of the subparts. For example, when designing a compiler one might say that

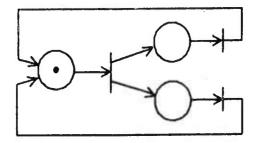

the LEXICAL-ANALYSER and the SYNTAX-ANALYSER could process in a pipeline manner with the LEXICAL-ANALYSER sending results to the SYNTAX-ANALYSER. A convenient notation is a directed graph notation with the restriction that the connections between two processes must go through an explicitly designated (and named) connecting LINK (see Figure I-6). At this stage of decomposition only potential communication is important and data dependent communication (i.e. decisions based upon data) is not considered at all.

Figure I-6. Pipeline.

Each of the previously discussed models considers interprocess communication patterns to be important for understanding the performance of multiprocess programs. Both the Petri-net and the LOLA model represent interprocess communication by means of the movement of untyped tokens. Queueing models of multiple processes elso use typeless tokens to represent flow of control. Riddle was able to simplify some interprocess connections in his model schema and to enhance analysis by introducing type identification for tokens.

The STEPPS model uses typeless tokens to represent flow among processes. The study of interprocess communication suggests several measures of multiprocess performance such as queue lengths, deadlocking, and potential concurrency. A difference between this model and the earlier models is that a STEPPS process must be ready for a message before "firing" (due to the arrival of a message) instead of its

firing being dependent on logical relations of the messages available on paths to It.

#### I.D.1. The STEPPS model: an informal description

The STEPPS model includes both probabilistic and timing expectations for describing individual process activity. Whereas a standard probabilistic model, i.e. Poisson, treats processes as operating on messages, the STEPPS model process includes a natural relationship between a process' input/output activities. In addition, the introduction of time parameters allows for better estimation of a program's operational concurrency instead of potential concurrency. The model represents multiprocessing at the message communication level and is not intended to represent other multiprocessing problems such as memory interference and specific programming techniques.

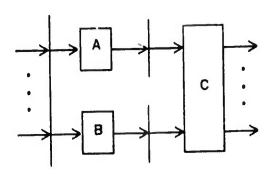

Concurrency can be modeled by having a single process send data to more than one other process. Data streams are explicitly merged when a process receives data from more than one other process. In the descriptions of processes, more than one arrow may leave a process node or enter a process node. If a process node is able to receive data from any of several processes, but the receiving process does not care which process sent the data, several arrows enter a linknode and only one leaves it. If one of several processes may operate on data produced by another process this is represented by more than one arrow emanating from a linknode and going to the separate process nodes.

<sup>†</sup>In Riddle's model a process must be explicitly programmed to accept a message.

#### Example I.D-1

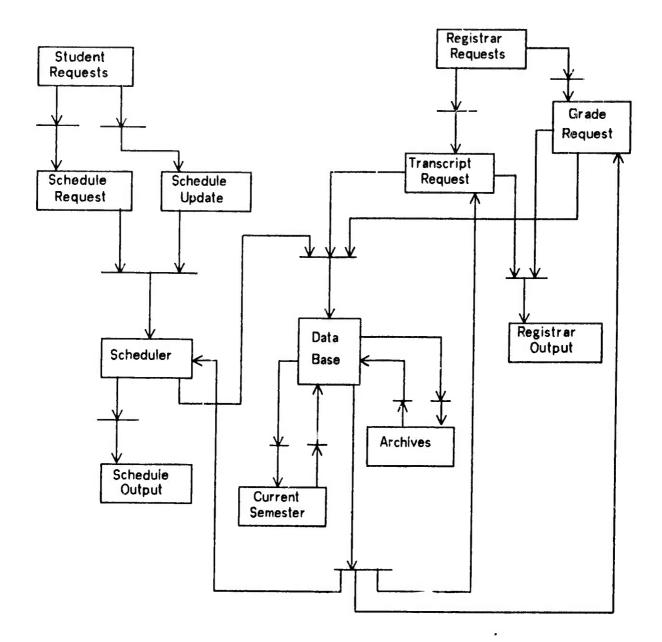

Consider the problem of building an online university registration system. This system would handle ail of the scheduling and student record keeping for a university. One might decompose the problem into the graph of Figure I-7. Students' requests are handled either by a Schedule Requester or Schedule Updater, each of which processes the request and sends data to a Scheduler. The Scheduler sends data to the Data Base and then sends results to a Schedule Output process. Requests to the system may also come from the Registrar. These requests may also go to the Data Base and on return data is sent to the Registrar Output by the Transcript request process. There also may be requests for grades. The data base may access data in either the Current Semester or its Archives.

All data travels through paths between nodes (the LINKS and the PROCESSES) in units called messages and all queueing of messages occurs at each LINK. Requests for data from a LINK are handled in a FIFO (First In, First Out) manner by the LINK. The next step is to describe the action of a PROCESS node. Since only the communication paths are important at this point of design, only the message handling properties of a process are described. The source of data is not identifiable, so a process neither knows which process sent the data to the LINK attached to any of its "input ports" nor does it know which processes are attached to the LINK that is ettached to any of its "output ports." The reason for this restriction is that messages contain no information such as sender or receiver identity. This will be shown not to cause difficulty in using the model.

The execution sequence of a process is:

- 1. perform an input or output operation,

- 2. choose which input or output port will be active next,

- 3. compute for some time, and

- 4. repeat 1 to 4.

Figure I-7. Registrar's Data Retrieval System

Each process is a uniprocess and can only perform one input or output operation at a time.

The method of describing how each process operates in the STEPPS model requires that each port be named. For convenience, the notation used is to assign a

each process defines the probability of succeeding the activation of one port with the activation of another port. The informal definition state of a process refers to the most recent port activation (in this thesis, states correspond to port activations). The process remains in the same state while it is computing and enters a new state at the next activation of a port. In most contexts the terms "state" and "port" are used interchangeably.

## Example I.D-2

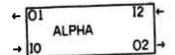

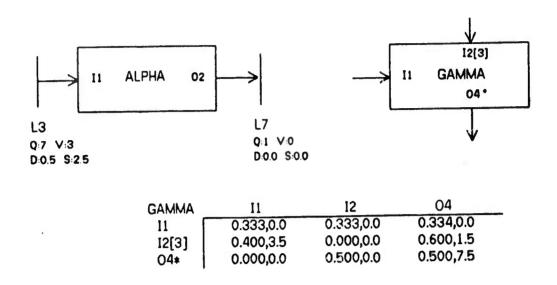

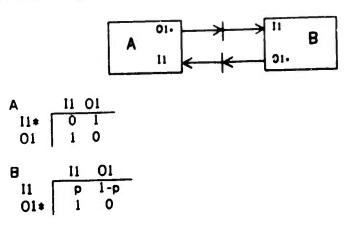

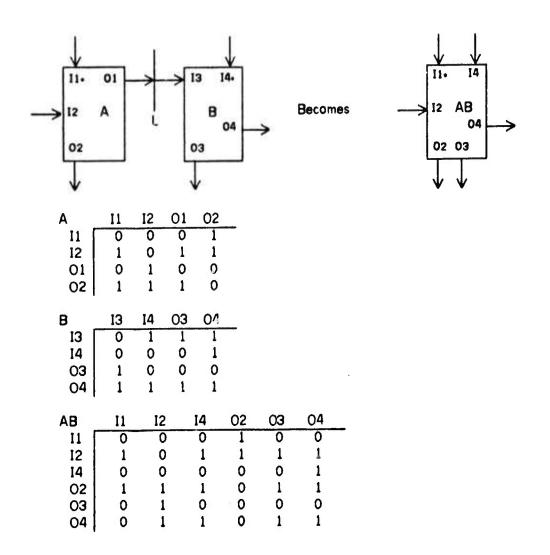

ALPHA is a process with two input ports, IO and I2, and two output ports, O1 and O2. IO may transfer to state O1 or O2. I2 may transfer to state O1 or O2. O1 may only transfer to state IO. O2 may transfer only to state I2. The graph and transition matrix for this process Is shown in Figure I-8.

#### Graph notation

Transition matrix (without timing)

| ALPHA | 10 | 12 | 01 | 02  |

|-------|----|----|----|-----|

| 10    | 0  | 0  | 8  | 1-a |

| 12    | 0  | 0  | b  | 1-b |

| 01    | 1  | 0  | 0  | 0   |

| 02    | 0  | 1  | 0  | 0   |

Figure I-8. Process ALPHA

The transition matrix makes it possible to describe the splitting of processing, the merging of processing, and the choice of alternate computation paths. In Example I.D-2, after an input from port IO, process ALPHA can enter either state O1 or O2 (with

probability of "a" to 01 and "1 - a" to 02). State 01 always enters state 10 as the next state.

Other features of a STEPPS model that can be specified are:

- 1. the initial state of each process,

- 2. the number of messages that a port may receive or send before the process changes state,

- the amount of computation time, defined for each transition, that a process computes before a transition takes place (this is fixed, but random variable computation times can be approximated),

- 4. the amount of computation time taken by a LINK to accept or send a message, or to restart when it is not already handling communication of messages, and

- the queue size limits for each link and the initial number of messages in each link.

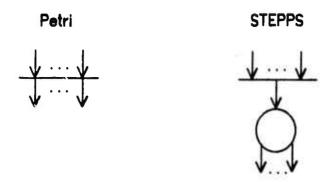

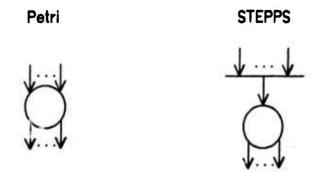

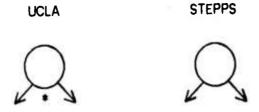

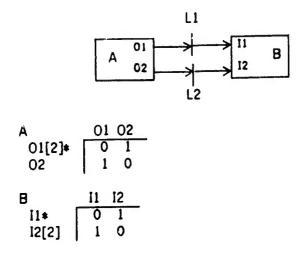

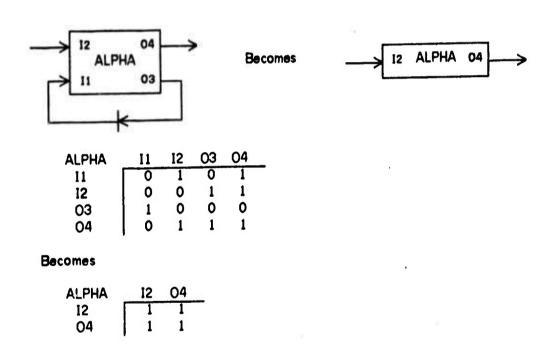

The model that has just been described subsumes both the Petri net and the UCLA model. The links and nodes of Petri net and STEPPS models are very similar; each is equivalent to the corresponding STEPPS model shown in Figure I-10 also shows the relationships between the UCLA model and the STEPPS model.

The STEPPS model allows for a more general specification of data flow than the earlier models since it is possible to describe the probabilities that particular data paths may be taken. When a message is accepted by a process it is easy to specify which data paths are more likely. As further information about the system being designed is learned or when the effects of alternate data path specification are taken into account, probabilities are altered by the system designers to fit the new structure.

The input port accepts N messages before changing state to an output port; the transition between the output ports occurs in a sequence; and the last output state transfers to the input port.

The input state accepts only 1 message and the transition to each output state is equally likely. Each output state transfers to the input state. The link may be able to hold more than one message.

Figure I-9. Mapping Between Petri nets and STEPPS model.

The input state accepts 2 messages before transferring to an output state.

The link has a limit of one message, so only one message can get to the process. The process input port accepts 1 message before transferring to an output state.

The transition matrix sequences through the two output ports.

The transition matrix shows an equal likelihood of transferring to each output port from the input ports. After an output the process will perform an input.

Figure I-10. Mapping of UCLA model to STEPPS.

## I.E. The STEPPS system and simulator

Once a proposed multiprocessing program has been modeled, the model can be implemented in the STEPPS interactive system in order to evaluate the particular decomposition. The data entry language for STEPPS has been designed for conciseness. A linear description of a directed graph and the associated transition matrices may require the entry of a fairly large amount of data. To facilitate the entry of these data, it is possible to recall previously stored data. The system designer can manipulate his model in any way he chooses, e. g. remove nodes, change parameter specifications, or display parts or all of his model. It is always possible to save the description of the model or parts of it externally in a form that may be recalled by the STEPPS system or examined on hardcopy.

Several useful tools are available to help the system designer evaluate the structure of his decomposition. As a basic step, a STEPPS model can be certified as being a well-formed model. A STEPPS model is well-formed when:

- For each process, every state is attainable from any other state (If a

process has N states, and X and Y are any two of them (possibly the

same), the probability of starting in state X and entering state Y in N or

fewer transitions is greater than zero. This restriction is discussed in

later chapters.); and

- 2. All ports of each process are attached to links;

- 3. All links are attached to both input and output ports;

- 4. The graph is connected. (When the directions of paths are ignored then there exists a path between every pair of nodes.)

At some point it should be possible to simulate the execution of the modeled program; thus the STEPPS system contains a model simulator. However, there remain problems which can prevent a successful simulation of a program structure. One

problem is that the initial state of the processes and the initial message capacities of the links might be incompatible. This would cause a simulation to halt almost immediately. Another problem is one of possible communication deadlocks. These problems are discussed in Chapter IV.

#### I.E.1. Deadlocks

A process may deadlock in either of two situations:

- no messages will ever be available at the link attached to an active input port, or

- 2. the capacity of the link attached to an active output port has been reached, and no messages will ever be able to leave the link.

Deadlocks may occur when a process can depend on itself improperly. They may also occur when a set of processes are incompatible for reasons other than data loops.

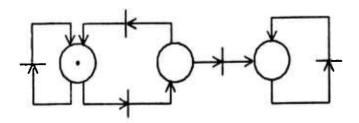

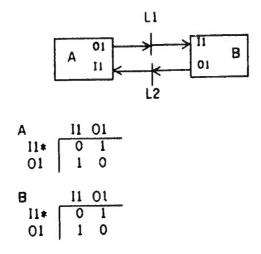

#### Example 1.E-1

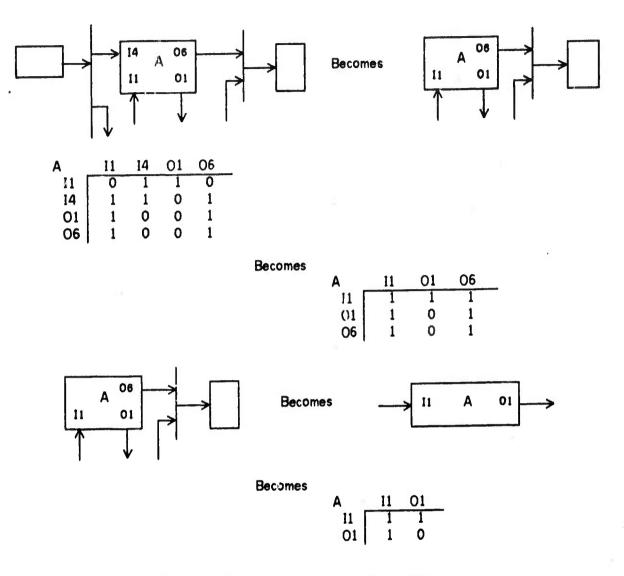

Figure I-11 shows process A waiting for data from B while B is waiting for data from A. If the initial state of A is changed to be O1 then the process has no deadlocks. If an additional change is made to A so that state O1 or I1 is activated more than once and B is not changed, then this is again unsafe because a link will eventually overflow or never have enough data.

#### Example I.E-2

Figure I-12 shows a non-loop structure where there will be a deadlock as soon as the L1 queue limit is reached.

None of the structures presented in Examples I.E-1 and I.E-2 showed problems that can occur when a process has a choice of successive states. There are other

Figure I-11. Incompatible loop.

Figure I-12. Incompatible non-loop.

deadlock producing structures. For example a process may be set up to produce either N or M messages and the safety of this structure must be recognizable.

<sup>&</sup>lt;sup>†</sup>The asterisk in the example means that this is the initial state.

<sup>&</sup>lt;sup>‡</sup>O1[2] means two occurrences of O1 before changing state.

The deadlock problem may be dealt with in two ways. One alternative is to require any program decomposition to be deadlock-free.

A second alternative is to determine where deadlocks may occur and the probability of a deadlock. The existence of deadlocks in real systems is not always bad as long as a suitable response can be made. For example, the ARPA network is not deadlock free [Kleinrock 75]. However, when a deadlock is suspected the system "times out" and requires reinitialization of a data message. This is a reasonable solution under some circumstances, but only when a system can lose information. STEPPS provides tools to recognize the possible occurrence of deadlocks.

The algorithms used to identify deadlocks are basically specialized graph reduction techniques. A model is viewed as a graph whose nodes are the processes and links. Under application of these reductions, a safe model will collapse to a graph containing no nodes. If the graph does not collapse then a deadlock is possible.

As already noted, a STEPPS model of a program can be quite general. If a model is acyclic and meets other criteria set by Martin [Martin 69] it is possible to estimate mean path time; however, these criteria are quite restrictive. In general, it is not possible to estimate mean path time through a STEPPS model without simulation. Ordinary systems analysis techniques such as queueing theory and dynamic programming models are intractable in all but the simplest cases [Fishman 73, Gordon 69]. It is for this reason that a simulator is a basic part of the STEPPS system.

The simulator is easy to use since it is a specialized system and requires no programming. Naturally, any STEPPS model can be simulated using GPSS, SIMSCRIPT, SIMULA, or any other simulation language. However the effort required to reprogram

<sup>†</sup>Chapter IV discusses the deadlock problem and past work in the area.

a general model is not well spent at the design stage of building a multiprocessing program. It is at this early stage of program development that the designer needs information about possible program decompositions, and the flexibility to be able to alter his design easily and make new evaluations. If variations in the decomposition needed to be reprogrammed, the understanding of alternative systems would be a more difficult process than comparing alternative models using the STEPPS system.

A variety of simulation parameters can be easily altered for comparing their effects on simulation results. These parameters include: restricting the number of available processors, identifying processor competing and noncompeting processes, and varying process scheduling algorithms.

The STEPPS simulator has a set of data gathering functions which help the designer evaluate a particular decomposition. Some of the estimations that are made based on the data are:

- 1. The expected time that each process is in each state. This can be determined without simulation if only the processing time is of interest, but when process wait time is included it is too difficult to estimate the time spent in each state.

- 2. The expected number of messages in each queue.

- 3. The expected number of processes waiting to send a message to each link.

- 4. The expected number of processes waiting for a message from each link.

- 5. The expected number of processes that will be executing simultaneously. This can be used to estimate the number of processors needed.

This list is not complete for all uses of the simulator. The system has been designed so that it is not difficult to include additional measurement functions.

The simulation times required to obtain these estimates vary with the complexity of a model. Usually, useful estimates can be obtained with a few minutes of

DEC PDP-10 compute time. The complexity of a graph is dependent on such attributes as the number of connections, choice of process states, and link delays.

# I.F. Thesis contributions and outline of remainder of thesis

The contributions of this thesis are tools that a system designer can use to enhance the overall design of a multiprocess program. These tools, presented as the STEPPS system, are based on a model that is described precisely in Chapter II. Chapter II also discusses the STEPPS system's capabilities (Appendix A is a manual for the STEPPS system). Examples of how the STEPPS model can be used to model a variety of multiprocess structures are presented in Chapter III. In addition, Chapter III presents two larger examples: one of the use of the STEPPS system in a user's early design stage and the other of the use of the STEPPS system in system tuning. The deadlock reduction algorithm is presented as a set of theorems with proofs in Chapter IV. Other model analysis capabilities are also discussed. The STEPPS simulator and data gathering facilities are discussed in Chapter V. Chapter VI contains a review of the thesis results, the limitations of this research, conclusions and directions for further research.

# Chapter II

# The STEPPS Model

This chapter provides some formalisms for later use and a precise definition of the STEPPS model. Chapter I presented an informal description of the model and the interactive design environment based on the model.

# II.A. Modeling the behavior of a process

The term process describes the utilization of the processing unit of a single instruction stream-single data stream computer (SISD). A "process" has sometimes been defined as the execution of a program. For the purposes of this research, that definition is too limited, since it does not take into account data transfers and accesses. A process, as defined for the STEPPS model, exists in one of the following conditions:

- 1. processing (computing) before performing an input or output operation,

- 2. waiting to access an external resource that must be accessed exclusively (simultaneous accesses are modeled by allowing zero time between accesses), and

- 3. waiting to complete an input or output operation.

A process is modeled as a processing unit which can perform operations internally, and which then must communicate with other units through one of several ports. The communication occurs when a process either requests or provides a unit of information. Each port belonging to a process has only one function: Input to the process or output from the process.

The internal operations of a process are unknown to an observer of a process.

All that can be determined is the relationships among the activities of the process's ports. Externally these relationships appear as probabilistic transfers of activity from one port to another, plus a computation time between port activities. In general, the computation time between any two successive port activations is dependent on the particular ports. Such process activities as accessing resources and sharing resources are modeled in terms of interprocess connections and message flow.

As defined in Chapter I, the state of a process refers to the most recent activation of or attempt to activate a port. This was an informal use of the term "state" since, more precisely, a process can be in the state of waiting to activate a port, activating a port (doing the port's activation), computing before the next port activation, etc. The imprecise definition of "state" will be used in most contexts, and it will be made clear when the more precise meaning is used.

This definition of the state of a process is an abstraction based on potential communications between a process and other processes. In addition, the concept of time is included in the model to allow a designer to include processing time for computation during simulations. An important abstraction is that STEPPS processes are not deterministic since port activations are based on probabilities and not on a data directed control structure. The disadvantage in this is the inability to represent programs on an instruction level. The advantage is that all potential communication alternatives are emphasized.

The complete operation of a process is described by the following loop (assuming the process starts in some initial state):

- Perform the input or output operation associated with the present state.

This may involve waiting to access an external resource and waiting for the input/output operation to complete. Both waiting times are considered as time spent in a state while not processing. This step can be repeated a specified number of times before the next step.

- Choose a new state. By a probabilistic method, described below, a successor state is chosen, but not yet entered.

- 3. Process (compute) for a length of time as determined by the transition from the present state to the next.

- 4. Enter the new state and repeat 1 through 4.

Given the knowledge of the present state, probabilities for entering any of the process's states are defined. Since the state of a process is related to the activity of a port, probabilities are defined for potential successive port activations from every port activation. Note that the choice of a successor state is dependent on the present state. In addition, step 3 above implies that a processing time parameter is associated with each transition and step 1 suggests that possible communication time is associated with a port activation.

Two restrictive assumptions are basic to this model. They are that (1) a process can not be interrupted (i.e. the transition matrix completely describes a process' activity) and (2) processes are neither created nor destroyed dynamically. These restrictions are used to keep the model relatively simple; they also make it possible to perform the deadlock test by graph reduction (Chapter IV). The lack of dynamic process creation and destruction can be approximated by including multiple copies of processes, but there is no way to use the STEPPS system to model process Interrupts and preemption.

#### II.E. Data flow and links