| AD-A03 | SIFIED              | CHARG | YSTEMS<br>E COUPL<br>6 T A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ED DEVI | CES IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SIGNAL | PROCES   | SSING S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | YSTEMS.<br>Nº00 | VOLUME<br>14-74-0 | F/G 9/<br>III<br>-0068<br>NL | /5<br>ETC(U) |   |

|--------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------------------|--------------|---|

|        | 1 OF 2<br>ADA031520 | -     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | 11日)<br>11日)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |          | - Inderson |                 | r<br>1994         |                              |              |   |

|        |                     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                   |                              |              |   |

|        |                     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                   |                              |              |   |

|        |                     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 10000000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                   |                              |              |   |

|        |                     |       | And the second s |         | internet<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Bioliti<br>Biolitta<br>Bioliti<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Biolitta<br>Bioli |        | E        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                   |                              |              |   |

|        |                     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                   |                              |              |   |

|        |                     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                   |                              |              |   |

| 1      |                     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | 6                 |                              |              | / |

9/dt 374

# CHARGE COUPLED DEVICES IN SIGNAL PROCESSING SYSTEMS

## VOLUME III. DIGITAL FUNCTION FEASIBILITY DEMONSTRATION

**MARCH 1976**

Prepared for NAVAL RESEARCH LABORATORY NAVAL ELECTRONICS SYSTEMS COMMAND

NAVY CONTRACT NO.: N00014-74-C-0068

DDC DECERTIEN NOV 3 1976 DECERTIEN A

ONE SPACE PARK . REDONDO BEACH, CALIFORNIA 90278

CONTENTS

I

I

The second

-

1

Π

[]

0

Π

[]

| 1. | INTRO | DUCTION                                            | AND SUMMARY                                                                                                                                                                                                                                                                      | 1-1                                  |

|----|-------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|    | 1.1   | Introdu                                            | ction                                                                                                                                                                                                                                                                            | 1-1                                  |

|    | 1.2   | Phase 1                                            | Report Summary                                                                                                                                                                                                                                                                   | 1-2                                  |

| 2. | CHARG | E DETECT                                           | ION FOR DIGITAL LOGIC PURPOSES                                                                                                                                                                                                                                                   | 2-1                                  |

|    | 2.1   | Operatio                                           | onal Requirements                                                                                                                                                                                                                                                                | 2-1                                  |

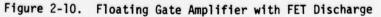

|    | 2.2   | Floatin                                            | g Gate Amplifier Design                                                                                                                                                                                                                                                          | 2-2                                  |

|    |       | 2.2.1<br>2.2.2                                     | Floating Gate Amplifier Design on LSM-1<br>Floating Gate Amplifier Design on DP-0 Mask Set                                                                                                                                                                                       | 2-5<br>2-5                           |

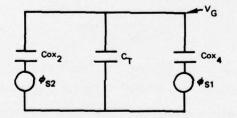

|    | 2.3   | Full Ad                                            | der Design                                                                                                                                                                                                                                                                       | 2-12                                 |

|    |       | 2.3.1<br>2.3.2<br>2.3.3<br>2.3.4                   | Original Full Adder Design on Mask Set LSM-1<br>Test Results<br>Full Adder Design on Mask Set DP-0<br>Three-Input Full-Adder Designs on Mask Set DP-1                                                                                                                            | 2-12<br>2-13<br>2-16<br>2-24         |

| 3. | COMPU | TATIONAL                                           | ALGORITHM TRADEOFFS                                                                                                                                                                                                                                                              | 3-1                                  |

| 4. | MASK  | SET DP-1                                           |                                                                                                                                                                                                                                                                                  | 4-1                                  |

|    | 4.1   | Overvie                                            | w                                                                                                                                                                                                                                                                                | 4-1                                  |

|    | 4.2   | Detail                                             | Description of Two-Input Full Adder                                                                                                                                                                                                                                              | 4-1                                  |

|    |       | 4.2.1                                              | Detail Analysis of Two-Input Adder                                                                                                                                                                                                                                               | 4-6                                  |

|    | 4.3   | Detail                                             | Description of Three-Input Adder Circuits                                                                                                                                                                                                                                        | 4-9                                  |

|    | 4.4   | Array F                                            | unctional Testing                                                                                                                                                                                                                                                                | 4-16                                 |

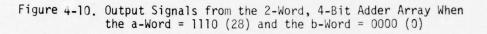

|    |       | 4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6 | Functional Testing of the 4-Bit Adder Array<br>Maximum Clock-Rate of the 4-Bit Adder Array<br>Operating Temperature Range of the 4-Bit Adder Array<br>Functional Testing of the 3-Bit Multiplier Array<br>Interfacing the CCD Devices to TTL Drivers<br>Characterization Summary | 4-16<br>4-25<br>4-27<br>4-27<br>4-27 |

| 5. | PROCE | SS                                                 |                                                                                                                                                                                                                                                                                  | 5-1                                  |

|    | 5.1   | Process                                            | Description                                                                                                                                                                                                                                                                      | 5-1                                  |

|    | 5.2   | Special                                            | Processes                                                                                                                                                                                                                                                                        | 5-2                                  |

|    |       | 5.2.3                                              | Clean Gate Oxide Technology<br>Ion Implantation<br>Polycrystalline Silicon Technology<br>TEOS                                                                                                                                                                                    | 5-2<br>5-3<br>5-4<br>5-4             |

|    | 5.3   | Basic P                                            | rocessing Steps                                                                                                                                                                                                                                                                  | 5-5                                  |

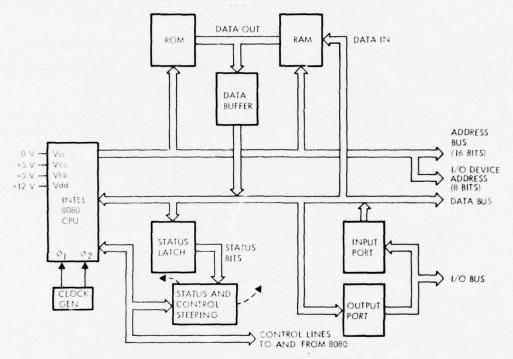

| 6. | SIGNA | L PROCES                                           | SING INTERFACE STUDIES                                                                                                                                                                                                                                                           | 6-1                                  |

|    | 6.1   | Introdu                                            | ction                                                                                                                                                                                                                                                                            | 6-1                                  |

|    |       | 6.1.1<br>6.1.2<br>6.1.3                            | Background<br>Overview<br>Summary                                                                                                                                                                                                                                                | 6-1<br>6-1<br>6-3                    |

|    | 6.2   | Descrip                                            | tion of Transparent Interface System                                                                                                                                                                                                                                             | 6-3                                  |

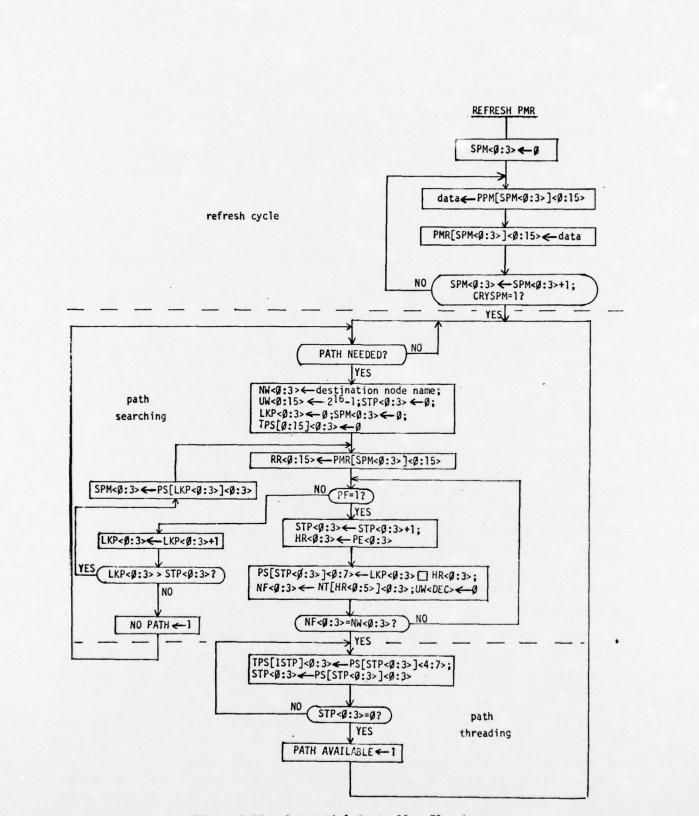

|    |       | 6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                   | Path Matrix Operations<br>Path Selection<br>Flowcharts<br>Path Selection                                                                                                                                                                                                         | 6-4<br>6-7<br>6-11<br>6-12           |

PRECEDING PAGE BLANK-NOT FILMED

## CONTENTS (Continued)

| 6.3  | Simulation Results                                     | 6-13         |

|------|--------------------------------------------------------|--------------|

|      | 6.3.1 Example<br>6.3.2 Recommendations for Future Work | 6-14<br>6-26 |

| 6.4  | Detailed Design Results                                | 6-27         |

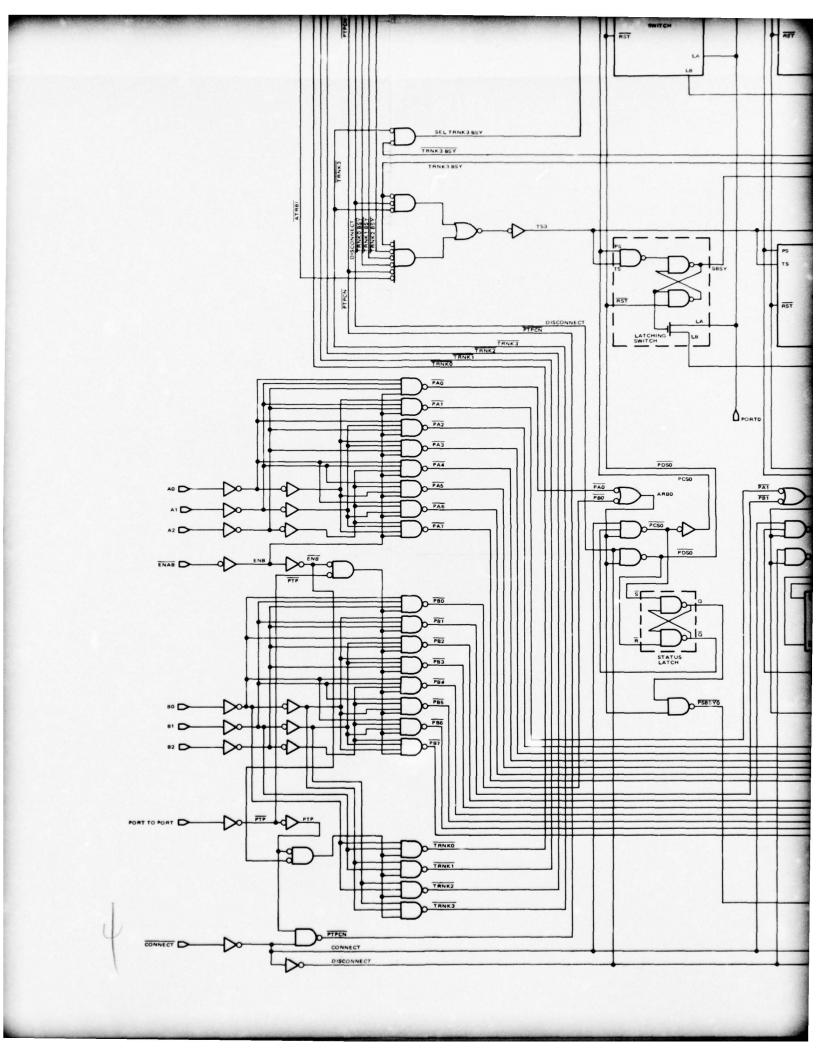

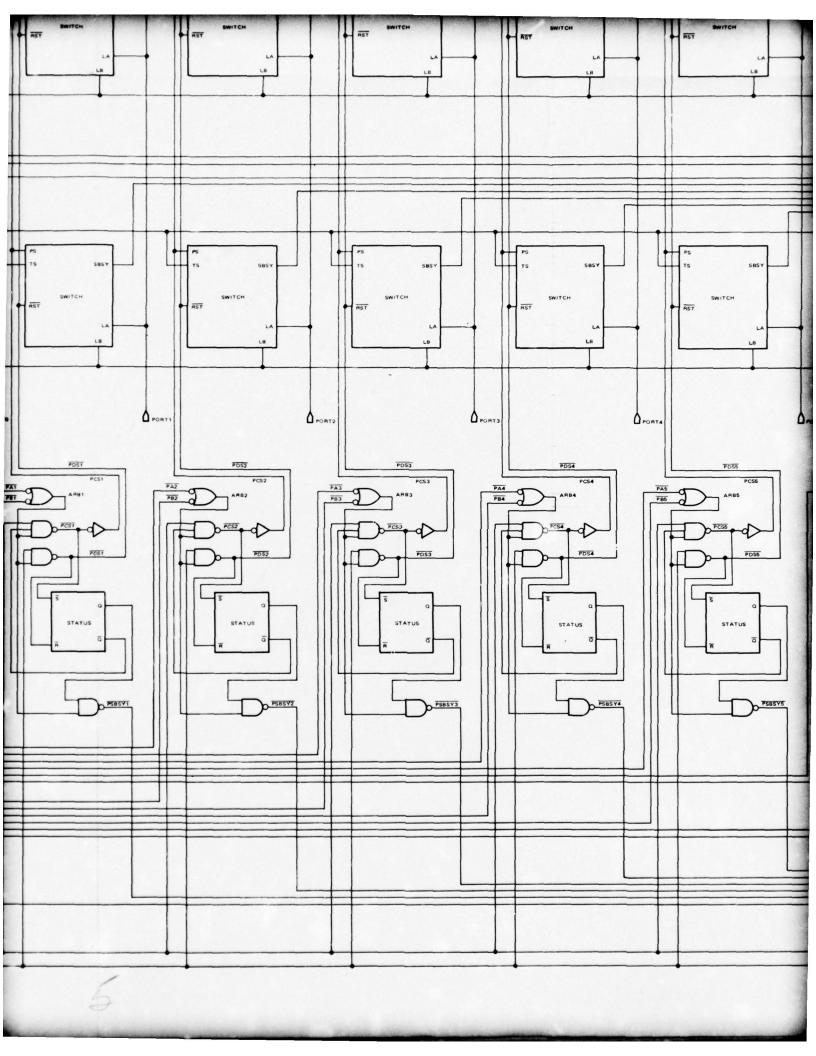

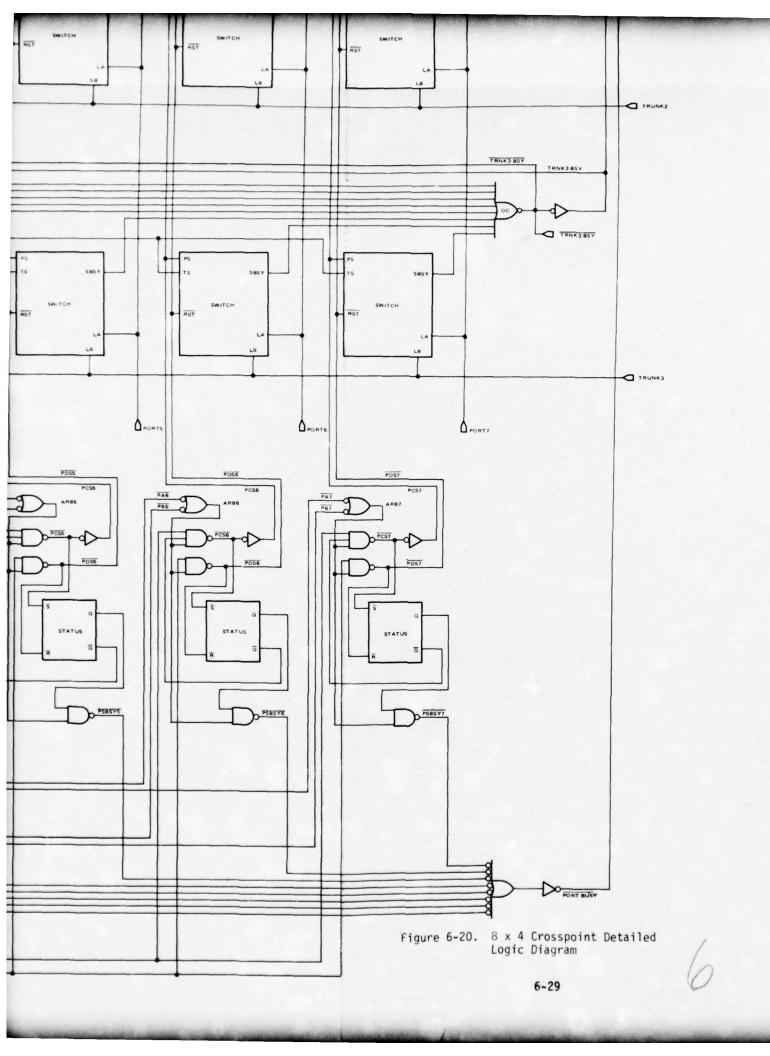

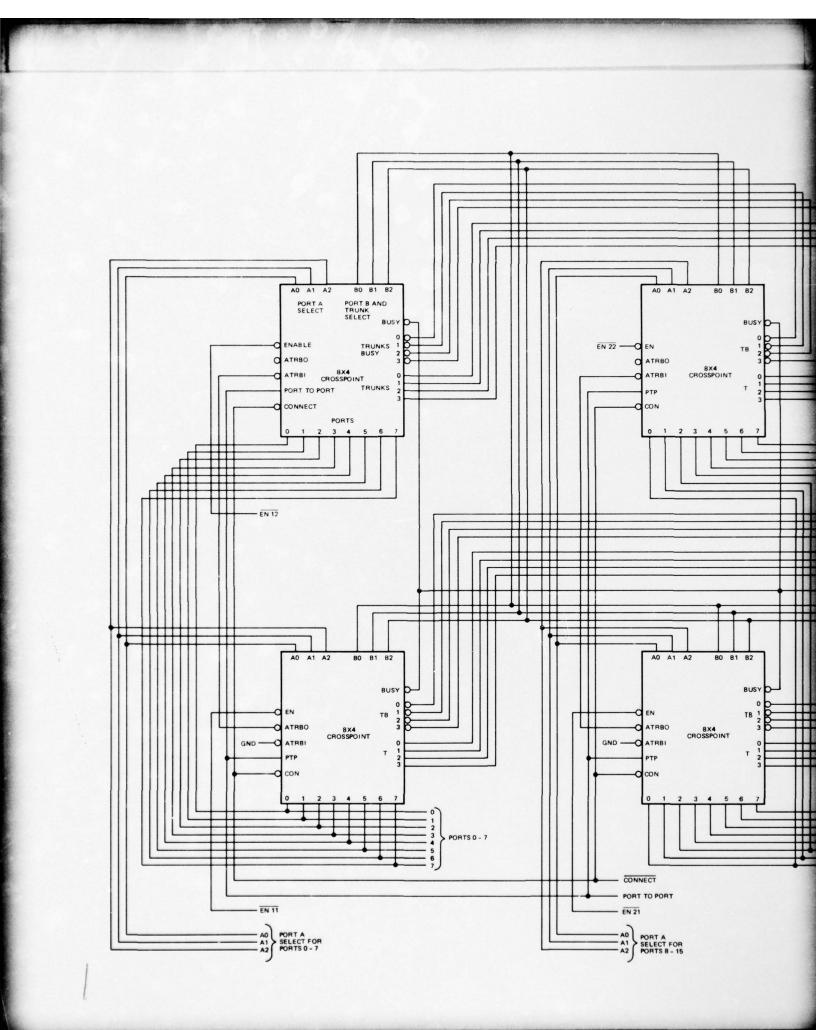

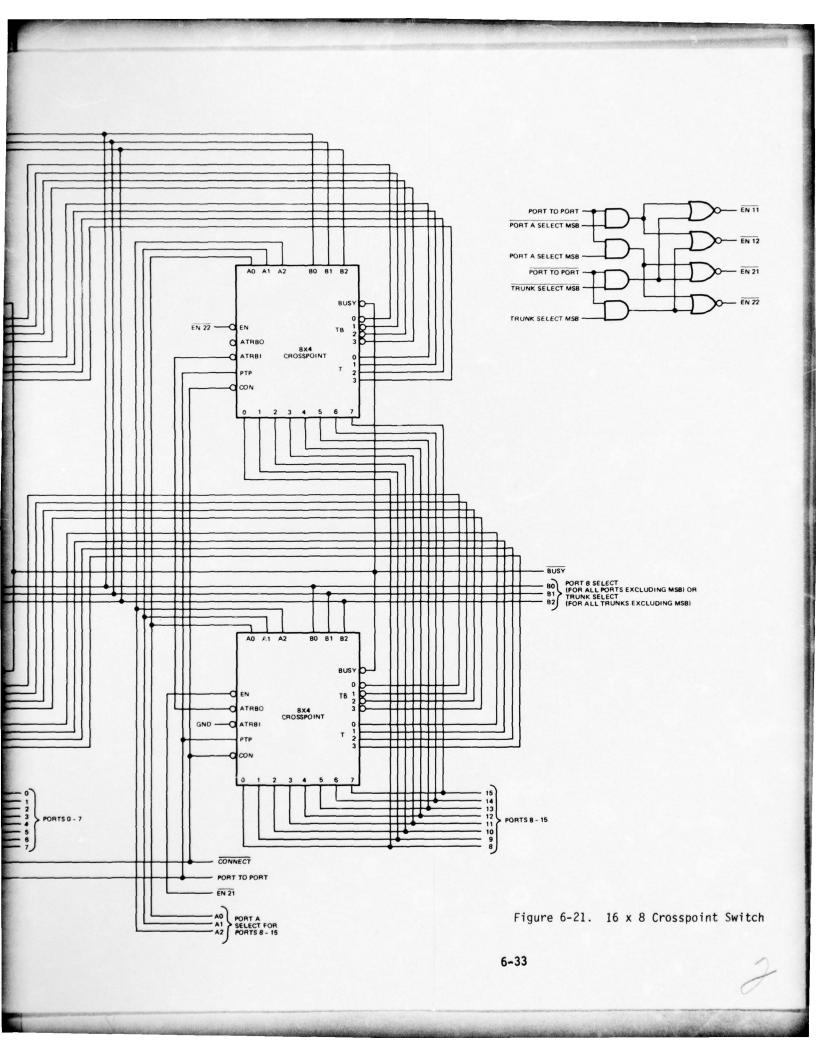

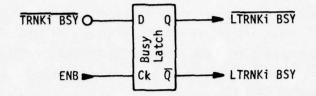

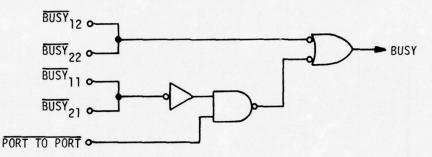

|      | 6.4.1 Crosspoint Switch<br>6.4.2 Path Selection Logic  | 6-27<br>6-35 |

| RECO | MMENDATIONS FOR FUTURE WORK                            | 7-1          |

ABCENSION for Atter on file 21 RECORPTION / AVAILABLE TO FORTERS TALL ENL & SPECIAL Bial.

the second second second

and the second second

7.

## ILLUSTRATIONS

|      |                                                                                                                  | Page |

|------|------------------------------------------------------------------------------------------------------------------|------|

| 1-1  | Chronology of Program                                                                                            | 1-2  |

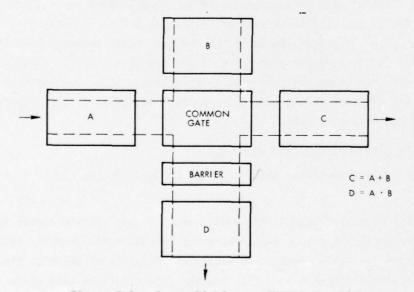

| 2-1  | Accomplishing an AND/OR Function                                                                                 | 2-1  |

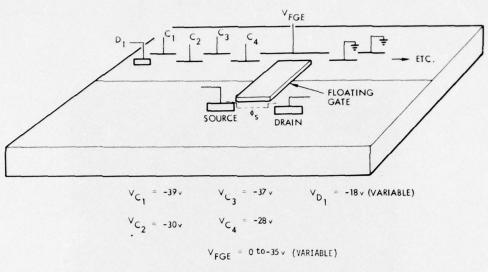

| 2-2  | Floating-Gate Test Configuration                                                                                 | 2-3  |

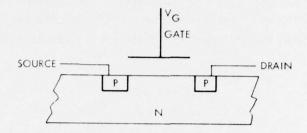

| 2-3  | Basic Test FET Configuration                                                                                     | 2-4  |

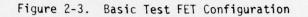

| 2-4  | IDS vs VDS with -10 VDC Applied to Gate of Floating Gate Amplifier                                               | 2-4  |

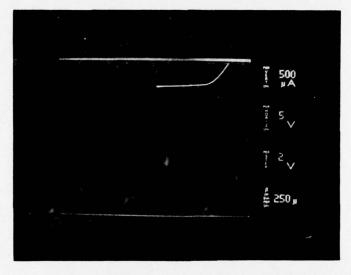

| 2-5  | $I_{DS}$ vs $I_{DS}$ Increase to Where Charge Accumulation is Observed on Gate of FET of Floating Gate Amplifier | 2-4  |

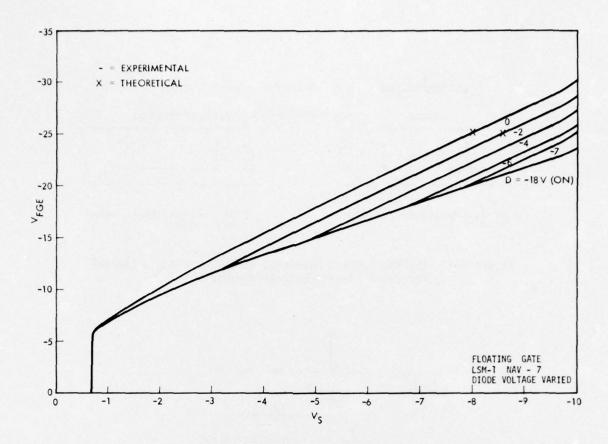

| 2-6  | V <sub>FGE</sub> NS vs Family of Curves for Floating Gate Configuration                                          | 2-5  |

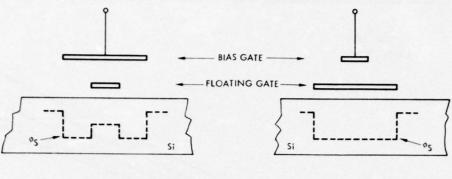

| 2-7  | Typical Surface Potential Variation Along a Channel for Two<br>Different Gate Arrangements                       | 2-6  |