| REPORT DOCUMENTATION PAGE                                                                                                                                                                        | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| . REPORT NUMBER Z. GOVI                                                                                                                                                                          | ACCESSION NO. 3. RECIPIENT'S CATALOG NUMBER                                                                                             |

|                                                                                                                                                                                                  |                                                                                                                                         |

| . TITLE (and Sublille)                                                                                                                                                                           | TYPE OF REPORT & PERIOD COVER                                                                                                           |

| PLURIBUS DOCUMENT 2: SYSTEM HANDBOOK                                                                                                                                                             | . Technical rept.,                                                                                                                      |

| 4 4 4 4                                                                                                                                                                                          | S PERECAMING ONS - REPORT NUMBER                                                                                                        |

|                                                                                                                                                                                                  | BBN Repest Nol-2930                                                                                                                     |

| AUTHOR(a)                                                                                                                                                                                        | (14) . CONTRACT OR GA IT NUMBER(*)                                                                                                      |

|                                                                                                                                                                                                  | F08606-73-C-0027                                                                                                                        |

| C.R./Morgan et al.                                                                                                                                                                               | F08606-75-C-0032                                                                                                                        |

| PERFORMING DEGANIZATION NAME AND ADDRESS                                                                                                                                                         | 10. PROGRAM ELEMENT, PROJECT, TAS                                                                                                       |

| Bolt Beranek and Newman Inc.                                                                                                                                                                     | (16) ARPA 1 Order No 2351;                                                                                                              |

| 50 Moulton Street                                                                                                                                                                                | Program Element Codes                                                                                                                   |

| Cambridge, Massachusetts 02138                                                                                                                                                                   | 62301E, 62706E, 627081                                                                                                                  |

| Advanced Research Projects Agency                                                                                                                                                                | 11) January 1975                                                                                                                        |

| 1400 Wilson Boulevard                                                                                                                                                                            | 13. NUMBER OF PAGES                                                                                                                     |

| Arlington, Virginia 22209<br>MONITORING AGENCY NAME & ADDRESS(II dillerent from Col                                                                                                              | 184                                                                                                                                     |

| 4. MONITORING AGENCY NAME & ADDRESS(II dillerent from Co                                                                                                                                         | ntrolling Office) 15. SECURITY CLASS. (of this report)                                                                                  |

| Range Measurements Laboratory                                                                                                                                                                    | Unclassified                                                                                                                            |

| Building 981                                                                                                                                                                                     | 15. DECLASSIFICATION/DOWNGRADIN<br>SCHEDULF                                                                                             |

| Patrick A.F.B., Florida 32925                                                                                                                                                                    | SCHEDULT                                                                                                                                |

| Disc.                                                                                                                                                                                            | 20, il dillerent (rom Report)                                                                                                           |

| 7. DISTRIBUTION STATEMENT (of the abetract entered in Block                                                                                                                                      | 20, il dillerent from Report)                                                                                                           |

| Disc.                                                                                                                                                                                            | 20, il dillerent from Report)                                                                                                           |

| Disc.                                                                                                                                                                                            | election Uniliation                                                                                                                     |

| Disc.                                                                                                                                                                                            | 20, il dillerent from Report)                                                                                                           |

| 7. DISTRIBUTION STATEMENT (of the obstract entered in Block                                                                                                                                      | 20, il dillerent from Report)                                                                                                           |

| 7. DISTRIBUTION STATEMENT (of the obstract entered in Block                                                                                                                                      | 20, il dillerent from Report)                                                                                                           |

| 7. DISTRIBUTION STATEMENT (of the obetract entered in Block                                                                                                                                      | 20, il dillerent from Report)                                                                                                           |

| 7. DISTRIBUTION STATEMENT (of the obstract entered in Block                                                                                                                                      | 20, il dillerent from Report)                                                                                                           |

| 7. DISTRIBUTION STATEMENT (of the obetrect entered in Block<br>18. SUPPLEMENTARY NOTES<br>19. KEY WORDS (Continue on reverse olde if necessery and identify<br>Multiprocessor CO                 | 20, il dillerent from Report)                                                                                                           |

| 17. DISTRIBUTION STATEMENT (of the obetrect entered in Block<br>18. SUPPLEMENTARY NOTES<br>19. KEY WORDS (Continue on reverse elde if necessery end identify<br>multiprocessor<br>Pluribus<br>fa | 20, il dillerent from Report)<br>20, il dillerent from Report)<br>y by b'ock number)<br>puter architecture<br>nult tolerant computation |

| 17. DISTRIBUTION STATEMENT (of the obetrect entered in Block<br>18. SUPPLEMENTARY NOTES<br>19. KEY WORDS (Continue on reverse elde if necessery end identify<br>multiprocessor<br>Pluribus<br>fa | 20, il dillerent from Report)                                                                                                           |

#### UNCLASSIFIED

٠

SECURITY CLASSIFICATION OF THIS PAGE (Then Data Entered)

.

Bolt Beranek and Newman Inc.

# PLURIBUS DOCUMENT 2: SYSTEM HANDBOOK

January 1975

| KTIS<br>D. C<br>Ultana (KED | White<br>Bert Sa | Saction 1 |

|-----------------------------|------------------|-----------|

| Statistication.             |                  | Ľ         |

| 9-0 <b>.0%43108</b><br>BA   |                  |           |

|                             | ait and a        | FRIAL     |

| A                           | 1                |           |

| 4-                          |                  |           |

Sponsored by:

The seasons

1 -

1

Advanced Research Projects Agency ARPA Order No. 2351 Contract No. F08606-73-C-0027

# PLURIBUS DOCUMENT 2: SYSTEM HANDBOOK

#### PREFACE

.1

"Pluribus Document 2: System Handbock" is one of a set of nine which, taken together, provide complete documentation of the Pluribus line of computer systems. In the present document, Part 1, entitled "Guide to Documentation," gives an overview of the entire set. Part 2, "System Description," contains an extensive discussion of the Pluribus line and the ways in which it can be used. This system description is the primary text for anyone seeking familiarity with the Pluribus, although, of course, there are many details which can only be found elsewhere in the set. Part 3 is a glossary of specialized Pluribus terms used throughout the set. Part 4 is an index to the present document. Part 5 contains reprints of several papers relevant to the Pluribus.

Of the five parts of "Pluribus Document 2," parts 1, 2, 3, and -5 are presently included here; part 4 is in production and will be added when it becomes ready.

D PAGE BLANK NOT FILMED

Bolt Beranek and Newman Inc.

# TABLE OF CONTENTS

## Preface

Sec 2 + 1 - -----

1 4

Part 1: Guide to Documentation . . . . . . . . . . . . . . . Guide

٧

Reprints

Index

Description

Glossary

PRECEDING PAGE BLANK-NOT FILMED

0

.

0

ŧ,

8

Bolt Beranek and Newman Inc.

PLURIBUS DOCUMENT 2: SYSTEM HANDBOOK

1

PART 1: GUIDE TO DOCUMENTATION

# GUIDE TO DOCUMENTATION

Update History:

Originally written - February 1975

0

9

Bolt Beranek and Newman Inc.

The Pluribus line of computer systems is documented in a series of nine volumes entitled as follows:

"Pluribus Document 1: Overview," BBN Report No. 2999

"Pluribus Document 2: System Handbook," BBN Report

No. 2930

"Pluribus Document 3: Configurator," BBN Report No. 3000

"Pluribus Document 4: Basic Software," BBN Report No. 3001

"Pluribus Document 5: Advanced Software," BBN Report

No. 2391

"Pluribus Document 6: Functional Specifications,"

BBN Report No. 3002

"Pluribus Document 7: Construction," BBN Report No. 3003

"Pluribus Document 8: Card Testing," BBN Report

No. 3004

"Pluribus Document 9: System Integration," BBN Report

No. 3005

The set of documents taken as a whole is intended to cover all aspects of the Pluribus; e.g., the decision to use a Pluribus, the design of systems involving the Pluribus, programming the Pluribus, actually fabricating the Pluribus hardware, and maintaining Pluribus systems. On the other hand, the set of documents is organized so that any one aspect of Pluribus endeavor (e.g., Pluribus manufacture) should be documented with a subset of the documents; thus, not everyone need carry all documents with him at all times--only those he needs.

The chart on the following page suggests which Fluribus documents will be useful for which areas of endeavor and for what types of people. Guide

SEE DOCUMENT NUMBER: δ 8 δ 8 7. 9 9 9 5 6, .9 5 3 6 4, 4, 8 4 4, 2 3 A Pluribus hardware maintainer....2, . . . . .2. A Pluribus factory worker......7, One considering buying a Pluribus...l, 1, Designing an opplication system based on the Pluribus.... Building a Pluribus Computer.. Using a Pluribus Computer... A Pluribus programmer... FOR (AREA OF FNDEAVOR) : FOR (TYPE OF PERSON) :

4

Table 1: Guide to Pluribus Documents

1

3,

Bolt Beranek and Newman Inc.

The documents have a loose-leaf format to facilitate updating.

Of the nine, documents 1 through 6 will be available in reasonably large quantities. Documents 7, 8 and 9 contain much detail of little general interest (e.g., wire lists, assembly drawings) and are extremely cumbersome to produce; therefore, their availability from BBN will be quite limited, although they will be submitted to the National Technical Information Service to allow general access.

In the following paragraphs, we discuss each of the nine documents in turn, presenting the contents of each and discussing its expected use.

Document 1: Overview. This document is meant to provide a quick summary of the Pluribus's capabilities, possible applications, and architecture, and is the first document one should read to determine if he is at all interested in using a Pluribus.

Document 2: System Handbook. This document is the primary text for one seeking familiarity with the Pluribus. The fundamental ideas of the Pluribus are introduced and then discussed in detail, including the structure of the hardware and guidance on how we think the hardware should be configured and programmed. In particular, after a brief general description of the Pluribus system structure, there are discussions of the processor structure and of the addressing structure for the system, an outline of how programs might be written to use the Pluribus structure effectively, a discussion of Pluribus device handling and I/O handling, a discussion of the structure of the Pluribus busses and how they are coupled together, summaries of the Guide

various devices which can be connected to the Pluribus, and a discussion of the Pluribus reliability mechanisms. While this document might best be thought of as a programmer's reference manual for the Pluribus, or alternatively, as the reference manual for Pluribus systems analysts, we think that everyone associated with any phase of Pluribus development and use will be likely to want it, with the possible exception of those concerned with only very local aspects of Pluribus construction.

This document is enhanced by the inclusion of a glossary, a guide to other documentation (which you are reading), an index, and some reprints of relevant papers written during the Pluribus development process which may give the reader greater insight into the use and structure of the Pluribus.

Document 3: Configurator. This document lists the various components that make up Pluribus systems (e.g., memories, processors, busses) and gives rules for configuring Pluribus systems. These rules are of two forms: rules of the firsu form are concerned with performance limitations; rules of the second form are concerned with physical limitations. An example rule of the first form tells how effectively multiple processors on a bus can share a memory on the same bus as a function of processor speed and memory speed. An example rule of the second form says that if more than some number of cards are to be used on a bus, then a bus extender will be needed. Of course, in some areas these two forms of rules are not independent; for instance, adding a bus extender may slow down the bus.

This document will be used primarily by the systems analyst or system architect for a computer system using the Pluribus. Further, it will be necessary in order to price Pluribus systems accurately, since only careful configuration will list all the system components actually needed.

Document 4: Basic Software. This document presents only enough about the Pluribus software to enable the reader to program in basic machine language for the Pluribus. The Pluribus instruction set is presented, the several different Pluribus assembly languages are introduced, and there is a discussion of the basic debugging package which allows Pluribus memory locations and machine state information to be inspected and changed.

Every Pluribus programmer will need to read this document as this is the software he will need to do "hands on" debugging of his program. Additionally, those building and maintaining Pluribus hardware systems will need to read this document because it describes the software they will need to operate hardware diagnostic programs.

Document 5: Advanced Software. This document describes software beyond that needed just to debug programs and operate hardware diagnostics. The software available for the Lockheed SUE, the processor used in the Pluribus, is listed. Detailed descriptions and operating procedures are given for the two cross-assemblers available to assemble programs for the Pluribus.

7

Guide

Bolt Beranek and Newman Inc.

1

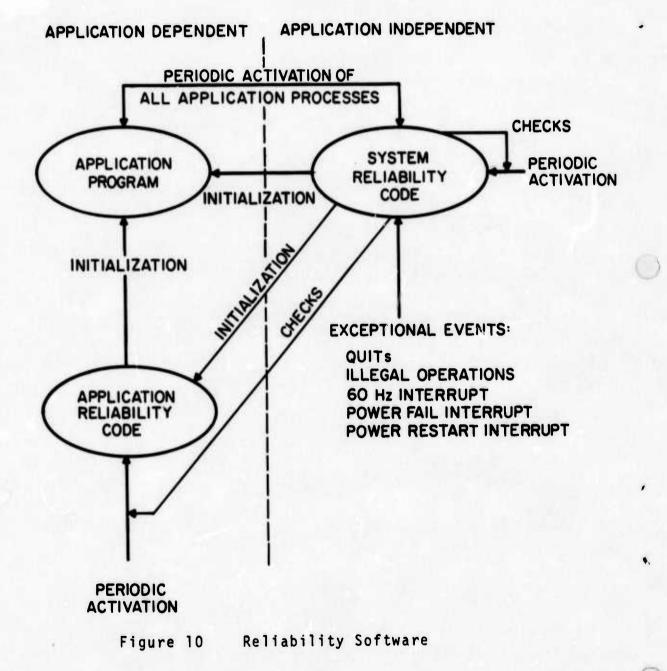

The somewhat unstructured "package" that has been developed to permit reliable operation of the Pluribus is also discussed.

Every Pluribus programmer, whether he is writing application programs, utility programs, or diagnostics, will need to refer to this document.

Document 6: Functional Specifications. This document provides the physical characteristics, operating characterisites, and necessary programming details for every Pluribus card. One way to think of this document is as an extension to Document 2, giving greater detail on specific devices.

Document 7: Construction. This document provides the information necessary to build the components of Pluribus systems. For every Pluribus card, the following are included: parts list, wire list, art work, assembly drawing, and assembly procedure. For every mechanical part and cable used in a Pluribus, this document includes the following: parts list, assembly drawing, and assembly procedure. In addition, this document contains a section which includes detailed instructions for any modifications and option selections for Pluribus cards.

Document 8: Card Testing. This document gives instruction for testing every card that can be used in a Pluribus system. For Pluribus cards obtained from Lockheed, the Lockheed maintenance bulletin and diagnostic procedure are provided. For every card specially designed and constructed for the Pluribus,

Solt Beranek and Newman Inc.

this document includes the following: schematic diagrams, logic description, wire lists, test program, and test procedure.

This document is necessary for anyone debugging cards, either after initial construction in the Pluribus factory or after failure in the field.

Document 9: System Integration. This document describes how the components of a Pluribus system are assembled into a complete hardware system; e.g., how chassis mount in racks, how cards mount in chassis, and how to test the whole thing once it is together. Included in the document are an overview of the hardware system assembly process and the hardware system assembly procedure; option selection information; system test programs; and finally, system quality control and acceptance porcedures for newly constructed systems.

This document is necessary for anyone debugging Pluribus systems, either after initial construction in the factory or after failure in the field. Guide

Bolt Beranek and Newman Inc.

Ceport No. 2930

0

.

-----

1.

PLURIBUS DOCUMENT 2: SYSTEM HANDBOOK

PART 2: SYSTEM DESCRIPTION

Bolt Beranek and Newman Inc.

.

÷

.

4

SYSTEM DESCRIPTION

Update History:

Originally written by C. R. Morgan and G. Falk, December 1974

".

Bearles new

1 "

8

Bolt Beranek and Newman Inc.

.

# TABLE OF CONTENTS

| 1. | INTRODUCTION                                          |

|----|-------------------------------------------------------|

| 2. | PLURIBUS SYSTEM STRUCTURE                             |

| ۷. |                                                       |

| 3. | PRUCESSORS                                            |

|    | a i Instruction Set and Format Summary                |

|    | 3.1 Instruction Section                               |

|    | 3.3 QUIT Handling                                     |

|    | ADDRESSING                                            |

| 4. | ADDRESSING                                            |

|    | 4.1 References to Common Memory                       |

|    | 4.2 References to System I/O Space                    |

|    | 4.3 References to Maps, Processor Registers, and      |

|    | 4.4 References to hups, 1.0000                        |

|    | Local 170 Space. I v v                                |

| -  | PLURIBUS PROGRAM STRUCTURE                            |

| 5. | c l Pacie Control Structure                           |

|    | r a suctom Response Time and Strips                   |

|    | r a shawed Data Structures, Shared Code, and Locks 20 |

|    | r A Using the Man Registers                           |

|    | 5.5 Using Multiple PIDs                               |

|    |                                                       |

| 6  | DDEVICE HANDLING AND 1/0                              |

| 0  | a 1 Address Structure                                 |

|    | c o Bucanamming RBN DMA I/O Devices                   |

|    | C 2 DBN Non-DMA I/O Devices                           |

|    | 6.4 Lockheed SUE I/O Devices                          |

|    | U.Y LUCKICCO COL -/-                                  |

Description

Bolt Beranek and Newman Inc.

0

.

0

Report No. 2930

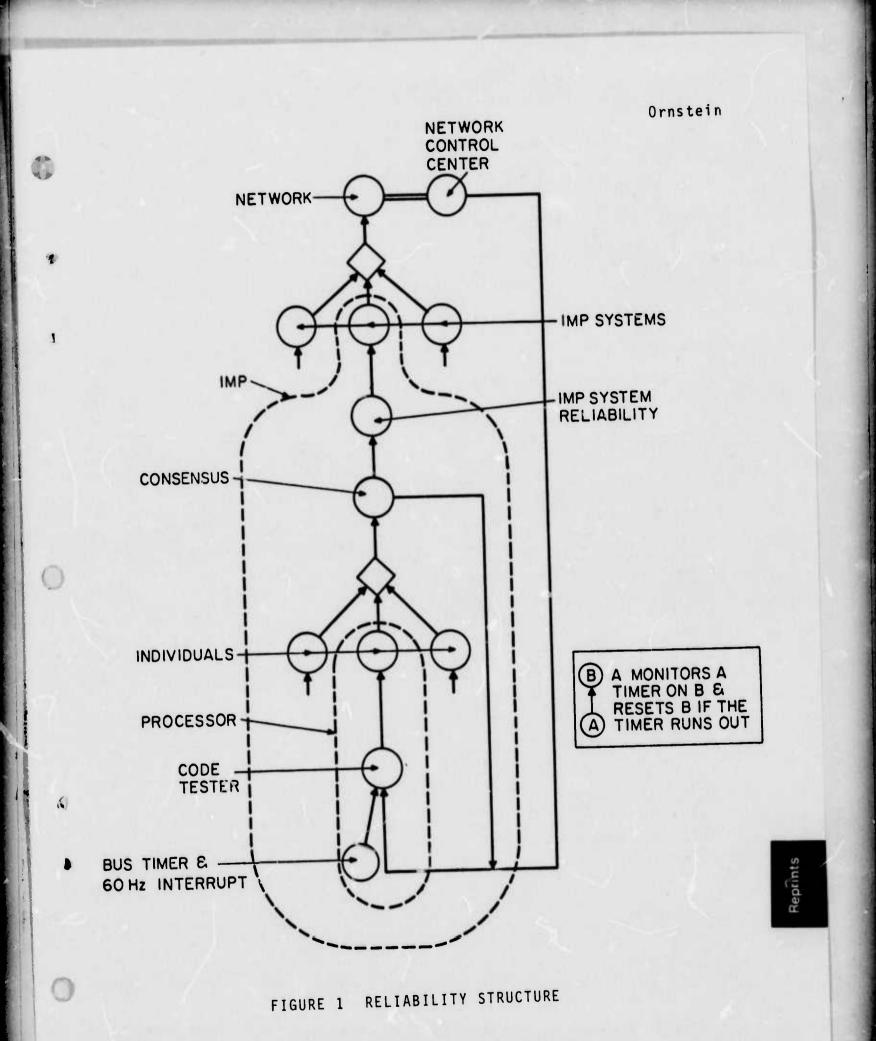

| _  | SYSTEM RELIABILITY MECHANISMS                                            | 3   |

|----|--------------------------------------------------------------------------|-----|

| 7. | 7.1 Hardware Reliability Mechanisms                                      | )   |

|    | 7.1 Hardware Reffabring Mechanisms                                       | )   |

|    | 7.1.1 Power Failure/Restart Interrupts 1 1 4                             | )   |

|    | 7.1.2 Hardware Timeouts                                                  | 1   |

|    | 7.1.2.1 Infibus Timeout                                                  | 1   |

|    | 7.1.2.2 Device Timeout and Multiple Interfaces . 5                       |     |

|    | 7.1.3 Remote Reference/Control of Devices on a                           | 2   |

|    | Processor Bus                                                            | 2   |

|    | 7.1.3.1 Backwards Bus Coupling 5                                         | 2   |

|    | 7.1.3.2 Remote Resetting of a Processor Bus 5                            | 0   |

|    | 7.1.3.3 Bus Amputation                                                   | /   |

|    | 7.1.4 Externally Initiated Reloads 5                                     | 9   |

|    | 7.1.5.Parity Generation/Checking 6                                       | 0   |

|    | 7.1.6 Transfers Between Private Memories on                              |     |

|    | the Same Processor 6                                                     | 1   |

|    | 7.2 Software Reliability Mechanisms 6                                    | 3   |

|    |                                                                          |     |

| 8. | INFIBUSSES                                                               | 57  |

| 0. |                                                                          |     |

| 9. | BUS COUPLERS                                                             | 0 1 |

| 5. | 9.1 BCP                                                                  | 70  |

|    | 9.2 BCM                                                                  | 73  |

|    | 9.3.BCI                                                                  | 77  |

|    | 9.3. BC1                                                                 |     |

|    | . DEVICES                                                                | 79  |

| 10 | 10.1 Pseudo Interrupt Device (PID)                                       | 79  |

|    | 10.1 Pseudo Interrupt Device (1207 · · · · · · · · · · · · · · · · · · · | 80  |

|    | 10.2 Real-time Clock (RTC)                                               | 82  |

|    | 10.3 Low Speed Modem Interface (MLC)                                     | 86  |

|    | 10.4 Local Host Interface (HLC)                                          | 88  |

|    | 10.5 Checksum/Block Transfer Device (CBT)                                | 90  |

|    | 10.6 External Reload Device (RLD)                                        | 00  |

|    | 10.7 Synchronous Line Interface (SLI)                                    | 99  |

# LIST OF ILLUSTRATIONS

.

| Figure | 1  | Typical Pluribus System Configuration 5        | ; |

|--------|----|------------------------------------------------|---|

| Figure | 2  | Processor Address Space                        | 5 |

| Figure | 3  | Address Mappings                               | 5 |

| Figure | 4  | Processor Bus Shared Address Space • • • • • 2 | 1 |

| Figure | 5  | System I/O Space                               | 6 |

| Figure | 6  | Allocations of Primary System I/O Space 3      | 8 |

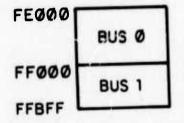

| Figure | 7  | DMA Registers                                  | 4 |

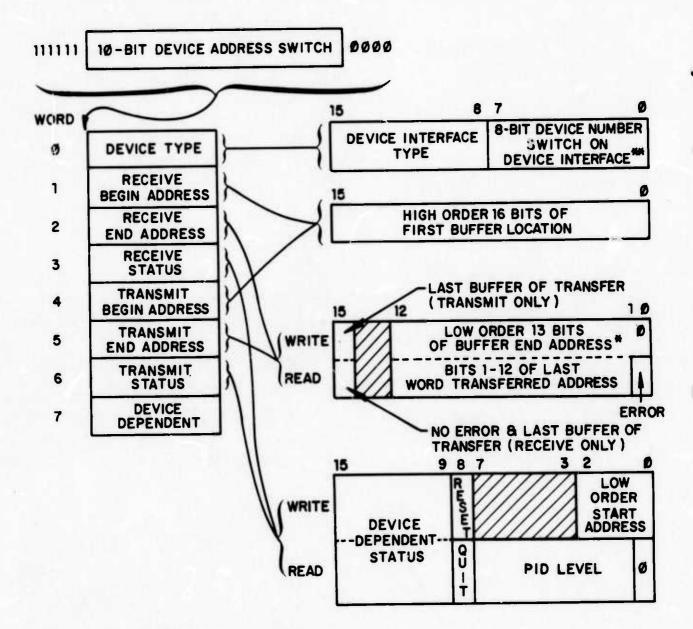

| Figure | 8  | Backwards Bus Coupling 5                       | 3 |

| Figure | 9  | Bus Amputation Example • • • • • • • • • • 5   | 8 |

| Figure | 10 | Reliatility Software • • • • • • • • • • • • 6 | 6 |

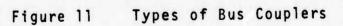

| Figure | 11 | Types of Bus Couplers                          | 1 |

۷

Description

#### 1. INTRODUCTION

The Pluribus\* system is a general-purpose multiprocessor computer suitable for applications ranging from those normally identified with minicomputers to those typically associated with larger machines. Pluribus hardware has been designed so as to provide a suitable basis for the development of ultra-reliable hardware/software systems.

Pluribus systems contain an arbitrary number of identical processors each of which has access both to its own private memory and to a common memory accessible by all processors. I/O devices which are part of the system can be controlled by any processor. The number of processors, size of common memory, and amount of I/O gear on a Pluribus system can be quite large.

The Pluribus system achieves modularity and reliability by making all the processors equivalent. Any processor can perform any system task or control any device. Since each subsystem of the Pluribus system (processor, memory, and I/O) is expandable, systems can tasily be configured to meet the throughput requirements of a particular job. The scheme for interconnecting system components is also modular; hence, interconnection costs vary smoothly with system size.

The Pluribus system was originally developed to serve as a modular reliable packet-switching node for the ARPA Network [1]. A node consisting of a 13-processor system is currently operational. The Pluribus approach is appropriate, however, for many other applications where reliability, modularity, or large logical computing power is required.

1

\*Trademark of Bolt Beranek and Newman Inc. (BBN)

12

This handbook will describe the structure and operation of the Pluribus system. It will emphasize utilization of the Pluribus architecture in the manner for which it was originally designed, although additional possibilities will become clear as the discussion progresses. The handbook is oriented both to the programmer who will use it as a basic reference document and to the system designer who will have to determine if the Pluribus is appropriate for his particular application. Section 2 presents an overview of the Pluribus architecture. Section 3 contains a brief description of the processor. Sections 4, 5, and 6 present the basic information concerning the Pluribus system; addressing, programming, and device handling. Section 7 discusses reliability machanisms in the Fluribus system, both hardware and software, in detail. Sections 8 and 9 discuss the Infibusses and bus couplers. Finally, Section 10 describes many device dependent features and bits and will be useful most likely for reference purposes only.

The Pluribus is constructed out of components manufactured both by BBN and by Lockheed Electronics Company, Inc. (LEC). The BBN-produced hardware is described in detail in this document. LEC hardware from the SUE minicomputer line is discussed only in sufficient detail to make the description of the Pluribus coherent. More complete information on the SUE components can be found in the Lockheed product literature [2,3,4,5].

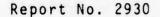

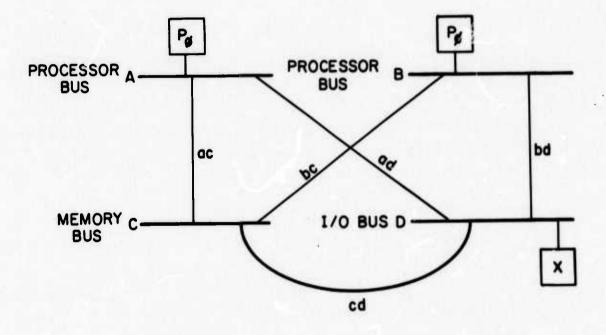

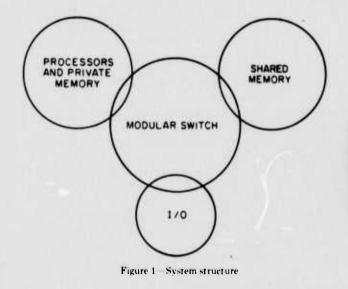

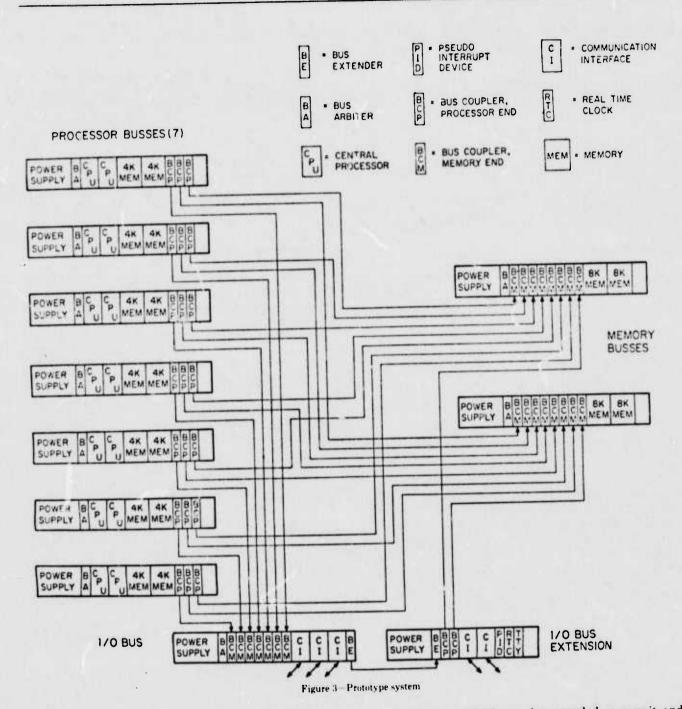

#### 2. PLURIBUS SYSTEM STRUCTURE

A Pluribus system consists of a number of components (processors, memory modules, and I/O devices), a number of busses over which these components communicate, and a number of bus couplers which provide the mechanism for interconnecting the individual busses. Within this framework a wide variety of systems can be configured ranging from small single bus systems to large multi-bus systems with tens of processors, up to 1024K bytes of main memory, and a large assortment of I/O gear. The subsequent discussion will focus on a medium sized Pluribus configuration. Very small and very large systems both involve additional considerations not discussed in detail here.

The basic skeletal unit of the Pluribus system is the SUE Infibus<sup>\*</sup> onto which all BBN and LEC devices are connected. The Infibus not only serves as a chassis into which device cards are plugged but also provides a means for communication among all attached devices. In general, a single Infibus can have an assortment of cards on it: processors, memories, or I/O devices. However, only one device can be in control of the Infibus at any given instant. An Infibus arbiter (Bus Control Unit Card or BCU) which must be present on the Infibus guarantees that this is the case. The total number of components which can be plugged onto a single Infibus is dependent on the number of slots available for cards and the type of power supply used (see section 8.). 'Froughout the remainder of this document the word "bus" will be used as a shorthand for Infibus.

3

\*Trademark of Lockheed Electronics Company, Inc.

Description

A small Pluribus system (even a single processor system) can be built using only a single bus. For many applications, however, the bandwidth capability and/or card capacity of a single bus is exceeded and a multi-bus structure is required. In addition, applications which take advantage of the full capabilities of the Pluribus hardware for bandwidth and reliability will require multi-bus configurations.

With more than one bus, the question becomes how to assign processors, memory, and I/O devices to the individual busses and how to connect them together. A typical configuration is illustrated in Figure 1. Lines between busses represent bus couplers. Typically, busses in a Pluribus system are configured as one of three types: processor busses, memory busses, or I/O busses. Processor busses support processors and private memory associated with each of the processors. Up to four processors (numbered 0-3) can logically be put on a single bus although contention for the bus is likely to reduce the effective processor bandwidth. In the ARPA Network application, for example, four processors with contention produce the same computational capacity as would three processors if there were no interference among the processors (i.e., if the processors were actually independent). Although the contention is application-dependent, Fluribus systems will generally be configured with one, two, or three processors per processor bus. Two processors are indicated for the system illustrated in Figure 1. The other components normally residing on the processor bus are the processor private memories. These memories will contain the "hot code" (i.e., those routines most frequently referenced) so as to reduce competition for the pool of shared (common) memory, and other code which is important to protect by removing it from shared memory. One useful technique

.

47

Bolt Beranek and Newman Inc.

Figure 1 Typical Pluribus System Configuration

Description

4

is for all private memories to contain identical copies of the same code. Much of the system reliability software will be held in the private memories to guarantee that redundant copies exist in case of any memory failure. The maximum amount of private memory addressable by each processor is 16K bytes. Not shown in Figure 1 but existing on every bus is the BCU (bus arbiter) card. In certain cases it may be desirable to have some I/O devices on the processor bus, but this will be the exception rather than the rule and is discussed further in section 6.4.

Memory busses contain common memory shared by all processors. Up to 1008K bytes of common memory can be added in 8K or 16K byte increments. The common memory will typically contain code which is referenced less frequently than the "hot code". Generally, shared data structures, variables, and buffers will also be held in common memory.

The configuration of common memory, that is, the assignment of memory modules to memory busses, depends on considerations of reliability and memory contention. For both reasons it is desirable to have multiple memory modules on a bus, multiple busses, and redundant copies of code and data structures. The details are application dependent and relate to the cost/performance (reliability) trade-offs which the system designer must consider. For reliable operation at least two memory busses, two processor busses, and two I/O busses will be required.

The I/O busses contain I/O devices and the Pseudo Interrupt Device (PID) central to the Pluribus system operation. The PID keeps in hardware a list of what to do next. A number can be written to the PID at any time and it will be remembered. When read, the PID returns (and deletes) the highest number it has stored. By coding the numbers to represent tasks, and keeping the parameters of the tasks in memory, a processor can access the PID at the end of each task and determine very rapidly which task to do next. This approach is an important departure from the use of conventional interrupts and avoids the costs associated with saving and restoring machine state.\* Further, this approach neatly sidesteps the problem of routing interrupts to the proper processor. More detail on the use of the PID is given in section 5.

There can be no more than four PIDs in a Pluribus system. Even though some I/O busses may conceivably not contain a PID, or a bus may contain more than one, the usual configuration is one PID per I/O bus.

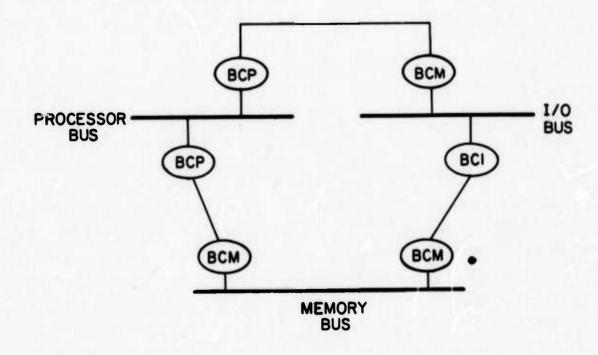

In a Pluribus system, processor, memory, and I/O busces are connected by devices called bus couplers. The different types of bus couplers required to connect different bus pair types together are discussed in more detail in section 9. For moderate sized systems, there will generally be a bus coupler between any two busses between which communication is required. Usually this implies a coupler from each bus to all busses of other types. Thus the total number of bus couplers for such a Pluribus system with P processor busses, M memory busses, and I I/O busses is  $P \cdot M + M \cdot I + P \cdot I$ . For smaller systems it is possible for one or more Infibusses to serve as combined memory and I/O busses, reducing the number of required bus couplers. For applications requiring large numbers of components (processors, memories and I/O devices) it will be possible to reduce the required number of bus couplers by building hierarchical Pluribus systems where

\*Although not used within application software, conventional interrupts can result from errors and are used for special purposes. See section 3.3.

7

escription)

4

11

busses are not completely connected. A more detailed discussion of the issues and procedures for configuring a Pluribus system can be found in a separate document [6].

Several distinct processor models are available. The SUE is a relatively slow and inexpensive processor. Typical memoryto-register instructions have execution times on the order of 4 microseconds. For a given application, the required processor power can be attained by using as many processors as are necessary. This approach to generating high throughput systems has the advantage of permitting extreme modularity and high reliability as well as graceful degradation.

Bolt Beranek and Newman Inc.

Report No. 2930

#### 3. PROCESSORS

# 3.1 Instruction Set and Format Summary

Lockheed SUE processors are used as processor components for Pluribus systems. The basic processor is a microprogrammed general purpose 16-bit minicomputer with 8 general registers (one of these registers is the program counter), and a status and a control register. These registers (general purpose, status, and control) may be accessed externally by other devices via the Infibus. In a multiprocessor this allows one processor to stop another, examine and change its registers, and restart it. There are 8 general instruction classes: MOVE, ADD, SUBTRACT, INCLUSIVE OR, EXCLUSIVE OR, AND, COMPARE, and TEST. Each of these instructions can use a variety of addressing modes including register-toregister, memory-to-register, register-to-memory, indexed, indirect, and auto-indexed. Also available are rotate, shift, conditional branch, unconditional branch, and subroutine calling instructions. The conditions tested for branching are bits in the status register of the SUE. There are tests for result being zero, result being negative, carry on last arithmetic instruction, register value odd, overflow, value greater-than on last comparison, value equal on last comparison, and loop completion. The branch can occur on either value TRUE or FALSE. Instructions are either one or two words long. The processor also contains 3 programmable flags, contained in the status register, that can be manipulated directly by instructions. The SUE processor recognizes and generates 16-bit addresses. In addition it contains a 2-bit KEY register which is settable by the SKEY instruction in the processor. The contents of this register are appended to the most significant end of the 16-bit address to generate an 18-bit address. Every memory access by a processor has these two bits appended.

Description

Certain of these 18-bit addresses are mapped into 20-bit system addresses as described in section 4. The processor operates on either 16-bit words or 8-bit bytes of data. Bit  $\emptyset$  is identified with the low order bit and bit 15 with the high order bit. Details of the SUE instruction set and the various processor types may be found in reference 4.

## 3.2 PROCESSOR STATES

SUE processors can be in one of three states: halted, running, or idle. Transitions between these states may be effected either by the processor itself or by external manipulation. The implications of each of these three states are as follows:

- Halt: No instructions executed, interrupts disabled, registers externally accessible

- Run: Instructions executed, interrupts enabled, registers not externally accessible except control register.

- Idle: No instructions executed, interrupts enabled, registers not externally accessible except control register.

External references to registers which are not accessible will result in a QUIT, as described in sections 5.6.1 and 9.2. The Idle state is entered from the running state by executing a WAIT instruction; the HALT state, by a HALT instruction. The Run state is entered from the Idle state by the occurrence of an interrupt. External manipulation of these states operates as follows:

The processor control register is the only register accessible while the processor is running. To halt a processor, a one is written to its control register. The processor will normally halt

Bolt Beranek and Newman Inc.

when the instruction it is currently executing is completed. However, if the control register is read between the time that a zero is written to the control register and the time that the processor completes its current instruction, the halt signal will be lost. Hence, some algorithm such as the following should be used to guarantee that a processor does in fact halt:

L: Write 1 to the processor control register. Read some other processor register. If QUIT results go to L (see section 3.3). At this point the processor is halted.

To start a processor, one must initialize all important registers to needed values and store the number two into the control register. This is done as follows: First it must be assured that the processor is halted. The program counter is initialized to the address of the program to be executed. The general registers are loaded with any values to be passed to the program. The status register is initialized to specify the enabled interrupt levels, initial status flags, and programmable flags. Bit 11 (hexadecimal constant  $\emptyset 8 \emptyset \emptyset$ ) should be set to activate the processor. Finally, writing a 2 to the control register starts the processor. An additional feature of the SUE processor is the ability to single step through an instruction sequence. The procedure for doing this is identical to that of starting a processor except that a 3 is written to the control register rather than a 2. Description

Bolt Beranek and Newman Inc.

Report No. 2930

## 3.3 QUIT Handling

Processors requesting access to memory locations or I/O registers do so by directly or indirectly placing the desired address on the appropriate bus along with the required operation (e.g. read, write) and any data required (for a write operation). When the requested operation is complete, the processor will receive a signal called DONE. If no device on the destination bus recognizes the address provided or if the device recognizing the address malfunctions, no DONE signal will be returned to the processor. Instead, after a fixed period of time, the bus arbiter on the requesting processor bus will send a QUIT signal to the processor, causing a conventional interrupt. (An equivalent thing happens to requests by I/O devices from I/O busses.)

In many applications a programmer will want to take some action based on the presence or absence of QUIT interrupts. In the ARPA Network application, for example, a device discovery routine in the reliability software searches system address space and determines if known devices have disappeared or new ones appeared by attempting to read the devices' registers and checking for resulting QUITS. To provide this mechanism the interrupt level routine which responds to QUITs should be written so that control will be passed back to the application program

Description

if the application programmer has indicated that he wishes this to happen. He indicates this wish by surrounding the instruction which potentially causes the QUIT by an "unusual pattern" of other instructions. For example, if a programmer wants to check for a QUIT occurring when location ABC is referenced he might write the following:

> LDA A2, ABC NOP BR · + 4 L: QUIT BRANCH ADDRESS

> > If no QUIT, program continues here.

The QUIT interrupt service, upon receiving control, would check to see if the two instructions following the one which caused the QUIT were NOP and BR  $\cdot$  +4. If they were, it would simply store the two bytes starting at location L (the address of the instruction causing the QUIT plus 8) in the program counter and dismiss the interrupt. If the two instructions at L-4 and L-2 do not match the NOP BR  $\cdot$  +4 pattern, the interrupt service routine would take its usual action in handling the QUIT. Of course, references to ABC which do not cause QUITs cause execution to continue at L+2 as indicated.

Bolt Beranek and Newman Inc.

#### Report No. 2930

#### 4. ADDRESSING

A typical Pluribus configuration incorporating both private memory associated with each processor and a pool of common memory shared among all processors has been presented in section 2. In this section the Pluribus address structure is described in more detail. The application of this address structure to Pluribus program structures will be discussed in section 5.

In Pluribus systems all devices communicate with one another by writing into or reading from addresses. These addresses may be memory locations, locations for controlling or interrogating I/O devices, or they may have some other special function. In any case it is important to understand two things; first, how addresses are generated and routed through the system and second, what things are referenced by what addresses.

Addresses are generated by active devices, that is devices wanting to read or write some location. This includes both processors and I/O devices. Consider first a processor.

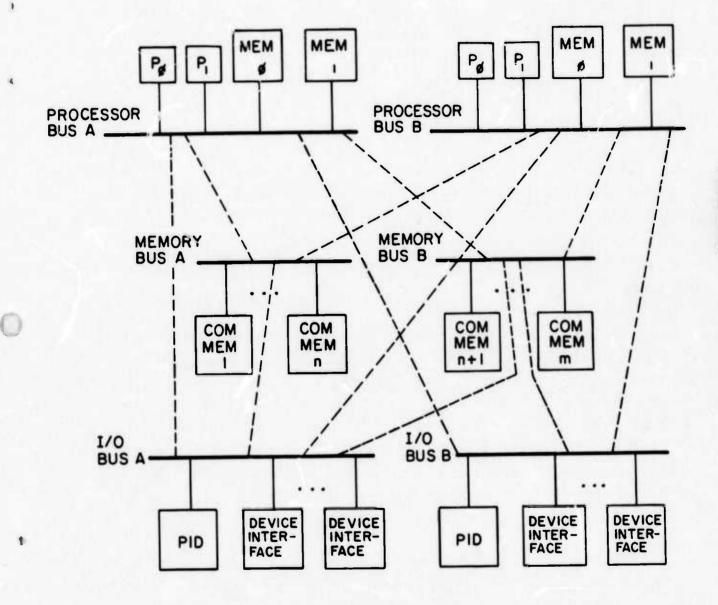

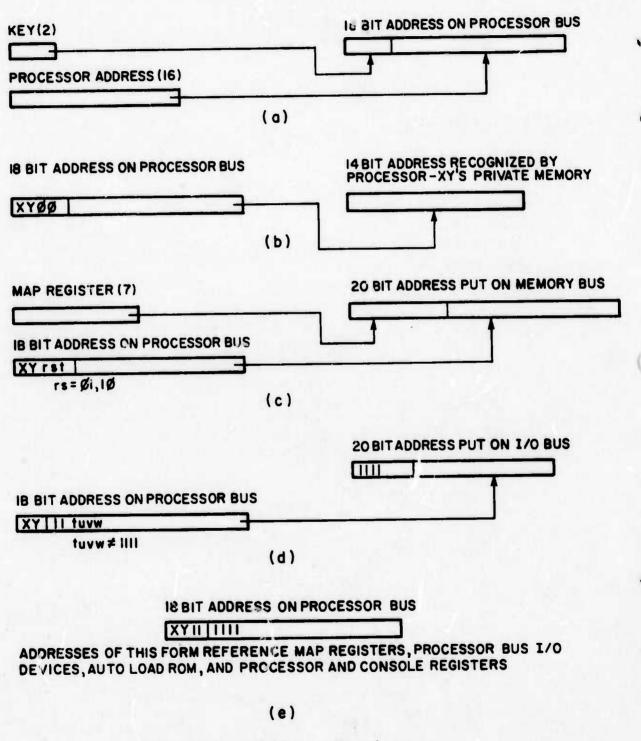

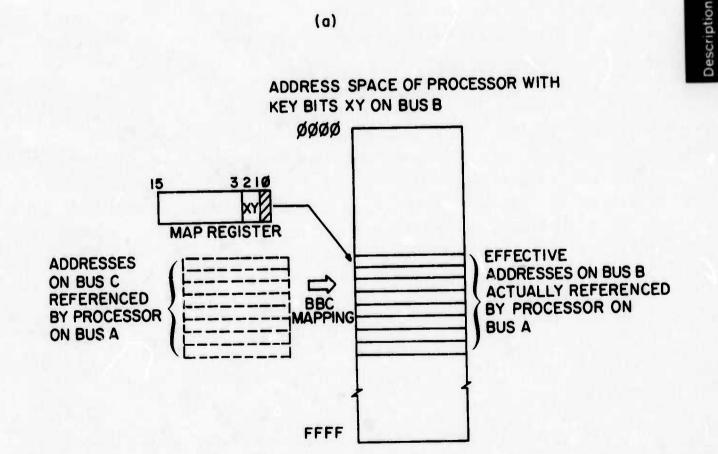

As indicated in Figure 3(a), SUE processors normally generate 16-bit addresses. With the addition of the 2-bit KEY register in the SUE, however, the Pluribus processors actually generate 18-bit addresses which are put on the processor bus. The KEY register can be changed under program control by execution of the SKEY instruction. For the class of applications being considered in this document, however, each processor on a bus will initially set its KFi register to a distinct value indicating its physical processor number and will not

10.

0

Bolt Beranek and Newman Inc.

Description

# Figure 2

Processor Address Space

Bolt Beranek and Newman Inc.

normally change this setting.

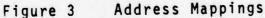

The KEY bits thus serve to differentiate the address spaces of the various (up to four) processors on the bus. The rightmost bit of the 16 left to ach processor is used to select left or right byte in byte mode instructions, allowing  $2^{15} = 32K$ addressable words. In order to allow larger common memory and I/O space than this, provision has been made for mapping portions of this 32K processor address space onto a 512K word system address space.

The addresses shown at the left in Figure 2 are the 16-bit addresses generated by a typical processor (processor j). The manner in which the address space is accessed by any processor generated address depends on the range in which that address lies. The four types of access will be discussed individually below. With all 4 types of access being discussed, the 18-bit address is simply put on the processor bus. Devices (memory, bus couplers, and I/O gear) able to recognize that address will respond and all others will ignore the address.

## 4.1 References to Private Memory (0000-3FFF):

Any processor generated address in this range refers to a location in the private memory associated with processor j on its processor bus. Up to 16K bytes of private memory can exist. As shown in Figure 3 (b), the high order two bits of the 18-bit address are used to select the proper memory module and the low order 14 bits select the location within the private memory. escription

## 4.2 References to Common Memory (4000-BFFF):

Any processor generated address in this range refers to a location in common memory, that is, memory on one of the memory busses. There are 4 distinct sub-ranges within this range, each associated with a distinct hardware mapping register. This association is indicated in Figure 2. Each map register allows a contiguous set of 8K bytes of commom memory locations to be referenced. A separate set of 4 map registers is associated with each processor on a processor bus. The map registers are physically located in the bus couplers (see section 9.1.)

Figures 2 and 3(c) illustrate how this mapping into common memory is accomplished. An address in the range  $4\emptyset\emptyset\emptyset$ -5FFF implicitly refers to map register  $\emptyset$ . A 2 $\emptyset$ -bit system address is developed at the processor end of the coupler by appending 7 bits from the map register to the low order 13-bits of the 18-bit address on the processor bus. This address is then forwarded to the common memory bus with the access request.

Addresses in the range 6000-7FFF, 8000-9FFF, and A000-BFFF implicitly refer to map registers 1, 2, and 3 respectively and the identical type of mapping occurs when these sub-ranges are referenced. The only special feature in the way that the four maps work is related to memory read operations via map register 3 which are transformed into read-modify-write accesses to common memory where the data rewritten is always zero. This allows the implementation of multiprocessor locks in the Pluribus system. More detail on the use of this feature is discussed in section 5.3 where Pluribus program structures are considered.

Description

Report No. 2930

One final complication arises from the fact that a few of the first addresses on every memory and I/O bus are allocated for accessing the bus coupler control registers. The amount of this allocation depends on the number of couplers connected to the bus. In general, the memory words at these addresses should not be used. For more detail on the bus coupler control registers see section 9.2.

# 4.3 References to System I/O Space (CØØØ-FBFF):

Any processor generated address in this range refers to a location in system I/O Space. In general, each Pluribus system device on an I/O bus appears to the processor as a set of 8 contiguous registers (locations) in system I/O space. This block of registers is referred to as the device register block. A processor can activate a device by writing commands or data to certain (device dependent) addresses within the device register block. A processor can interrogate a device by reading data or status registers within the 16 byte device register block. More detail about the allocation of system I/O space to multiple I/O busses and about the internal structure of the device register block can be found in section 6 where device handling and I/O is discussed further.

As indicated in Figure 3(d), the way that system I/O space addresses are developed is by appending four ones to the low-order 16 bits of the 18-bit address on the processor bus. This is done automatically as is the appending of the map registers (discussed above) by hardware in the bus couplers.

Report No. 2930

## 4.4 References to Maps, Processor Registers, and Local I/O Space (FCOO-FFFF):

Any processor generated address in the range FCOO-FFFF (see Figure 3(e)) refers either to the map registers for that processor (in all the bus couplers attached to the processor bus) or refers to a part of the address space shared by all processors on a processor bus. The map registers must be addressable, of course, so that a processor can dynamically modify the portions of the potentially large common memory to which it has access. Map registers  $\emptyset$ , 1, 2, and 3 can be referenced via addresses FCOO, FCO2, FCO4, and FCO6 respectively.

The local (to the processor bus) shared address space is assigned as shown in Figure 4. In general, I/O devices will be attached to an I/O Infibus in a Pluribus system. In some cases, however, it may be desirable or necessary to connect I/O devices directly on a processor bus. Addresses in the range FCO8 to FDFF will be used in such a configuration to refer to the device registers, similar to the way that the device register block is used for referencing devices on the I/O Infibus. The auto load ROM is an optional hardware device attached to the processor bus which contains a program that when executed will cause a processor to load memory from a paper tape reader on the processor bus. The registers of all the processors and the processor bus console are accessible at addresses above FFOO. A processor should be halted before an attempt to read any of its registers occurs. Halting a processor is described in section 3.

0

-----

1 "

.

14

Description

Figure 4 Processor Bus Shared Address Space

## 5. PLURIBUS PROGRAM STRUCTURE

In most current computer systems a hardware priority interrupt mechanism is used to inform the program of the occurrence of asynchronous external events. Since Pluribus systems do not generally use interrupts for this purpose, Pluribus programs tend to be structured differently from programs developed for conventional machines. The fact that Pluribus programs are designed to operate in a multiprocessor environment imposes additional constraints on the program structure. This section presents some of the issues and programming techniques which we believe are useful in developing Pluribus programs.

#### 5.1 Basic Control Structure:

Before giving an example of a typical Pluribus program control structure, the basic operation of a PID will be reviewed (more detail on the PID can be found in section 10.1). The PID is a priority ordered memory device. It has a read address and a write address. When an even 8-bit number is written to a PID, the number is stored. When a PID is read, the largest 8-bit number stored in the PID will be returned and the number deleted from the PID. If nothing has been written to the PID, the read will return a value of zero. Numbers may be written to the PID both by hardware I/O devices and by software. Processors poll the PID for tasks to be executed. As a simple example of a Pluribus control structure, consider a system consisting of a number of tasks which service a set of I/O devices. The following assembly language code could provide the framework for the required program.

Bolt Beranek and Newman inc.

escription

TASKDISPATCHTABLE: MAINLOOP, TASK1, TASK 2, ..., TASKN

MAINLOOP: LDA Al, PIDREADADDRESS JMP @ TASKDISPATCHTABLE (Al)

TASK1:

## JMP MAINLOOP

The main loop of the program simply reads the PID and jumps to the appropriate task indirectly through TASKDISPATCHTABLE (i) where i is the value obtained by reading the PID. At the end of any task (e.g. TASKi), a jump to the main loop returns the processor to look for the next task to perform. If there is nothing in the PID, zero is returned and the processor simply cycles at MAINLOOP. Note that it is useful to have the PID store even numbers only since the number retrieved will be used as an index into a table with two-byte entries.

To allow tasks to be initiated by the software (e.g. TASK. to be initiated by TASKj), the following type of structure would be used:

TASKj:

LDA A1, TASKIPIDLEVEL STA A1, PIDWRITEADDRESS JMP MAINLOOF

## 5.2 System Response Time and Strips:

As indicated in the above example, the way that I/O devices obtain service in a Pluribus system is to write the priority level of their service routine to the PID when they need attention, and wait for some processor to return to the main loop and pick up the associated task. Since the time that a device can wait for service before losing data may be critical, it is essential to configure systems and design software so that response time requirements can be met.

The two main factors which influence the rate at which a Pluribus system can respond to high priority external events are the total number of processors in the system and the duration of task servicing instruction sequences. For example, in a single processor system where the tasks are all of the form illustrated by the two previous examples, if the longest task execution time were T milliseconds, the maximum time which it could take to respond to an external event (i.e., notice that it had occurred) would also be T milliseconds. This worst case would happen only when the event occurred just after the single processor had picked up the longest task to run. Since in a Pluribus system there are no interrupts, the entire task currently being executed runs to completion before there is a reaction to the event (even though it may be c' higher priority than the task currently being run).

In the multiprocessor case, things are slightly more complicated. Considering the worst case response time as above, if the ordered task execution times are  $T_1$  (smallest),  $T_2$ ,  $T_3$ , ... Th (largest) and there are P processors, the maximum time to respond to an external event assuming n>p will be between between  $T_{n-p}$  and  $T_n$  depending on the number of incarnations of

Bolt Beranek and Newman Inc.

escription

a particular task which can exist simultaneously. Of course, the probability of such worst response times may be exceedingly small if the large tasks are run less frequently than the smaller tasks.

Typical (average) rather than worst case response times will depend on three factors: (1) average task execution time, (2) number of processors P, and (3) average number of tasks, <sup>N</sup>Q, queued on the PID. If the average task execution time is  $T_{av}$  and  $N_Q \ge P$ , the typical time taken to service a high priority event will be  $T_{av}/2$ . If P>N<sub>Q</sub> then there will usually be an idle processor which will immediately react to the external event and average response time will be essentially zero.

In general, the application will dictate where strict real-time response must be guaranteed or if more flexible system response characteristics are adequate. If strict real-time response is required, then some program structure which permits both logical tasks of arbitrary length and fast response to critical external events may be required. To accomplish this, Pluribus program tasks can be partitioned into code segments referred to as strips. A strip is simply a sequence of instructions within a task. A task can give up control of its processor at the end of each strip so that any higher priority tasks may be run. Of course, if the task is incomplete at the end of a strip, the task queues itself on the PID for further execution before yielding its processor. The idea is illustrated by the example below where TASKk is broken down into two strips.

Bolt Beranek and Newman Inc.

DISPATCHk: K1 /INITIALIZE TO THIS VALUE. TASKk: JMP @ DISPATCHk K1 · LDA A2, = K2STA A2, DISPATCHk Al, TASkPIDLEVEL LDA Strip 1 STA A1, PIDWRITEADDRESS JMP MAINLOOP K2: LDA A2, = K1STA A2, DISPATCHk Strip 2 JMP MAINLOOP

The first instruction of TASKk is a dispatch to the segment (strip) of the code to be executed. This dispatch is initialized to Kl so when TASKk is first initiated, execution will begin at K1. At the end of strip 1, the task stores a new dispatch address (K2) in the subtask dispatch location, DISPATCHk, writes its own PID level back into the PID and gives up the processor. The next time this PID level is serviced, the task will be resumed in strip 2 starting at K2. At the end of Strip 2, the subtask dispatch location is restored so that strip 1 will be executed the next time that TASKk is activated. It must be kept in mind that a task writing its own level to the PID will prevent the processor which is executing the task from picking up a waiting task with lower priority. In certain situations it may be desirable for a task to yield the processor and also "sleep" a specified period prior to getting rewritten to the PID. This can be accomplished by the task setting a software timer which

gets counted down by a periodic clock routine. When the timer reaches zero, the clock routine can write the sleeping task's level to the PID. The 5 instructions at the end of strip 1 in the above example might, therefore, be replaced by the following:

> LDA A2, = K2 STA A2, DISPATCHK LDA A2, SLEEPTIME STA A2, TIMERK JMP MAINLOOP

Then after TIMERk has been counted down, the timer routine will execute the instruction:

LDA A1, TASKkPIDLEVEL STA A1, PIDWRITEADDRESS

The decision of precisely where to segment a task into strips is somewhat arbitrary; the main rule is that the strips must be short enough so that the proper response characteristics can be guaranteed. In the ARPA Network application of the Pluribus, for example, it turned out that the proper typical strip size was on the order of 100 instructions (although a few infrequently run ones are much longer). As a rule of thumb, it will generally be sufficient to segment a task into strips assuming each instruction takes 4 µsec for execution.

Two other related practical issues relevant to strip size selections are convenience and overhead. In general, tasks should be broken into strips at convenient points in the code; that is, points at which little information (e.g. in the registers) needs to be preserved. It may occasionally be desirable to have strips somewhat smaller or larger than the nominal size so that such a Descriptior

partitioning will be possible. Data which must be saved and restored across strip boundries adds to the already existing overhead associated with breaking the code into strips. In many applications it is likely that little or no breaking of tasks into strips will be required. In the ARPA Network application, for example, multi-strip logical tasks are the exception rather than the rule.

The fractional overhead associated with breaking a task into strips depends directly on the strip size since the number of instructions required for strip switching is essentially fixed. For example, in TASKk presented above 8 overhead instructions are associated with switching from one strip to another (6 in TASKk and 2 in the main loop). If the strip size were 100 instructions as is typically the case in the ARPANET -plication, then the processor overhead due to using strips would be 8%. In applications where larger strips are acceptable, of course, the overhead will be even smaller. Experience with a number of Pluribus system applications has indicated that the processor overhead and programmer effort associated with breaking tasks into strips is not a serious problem and is a relatively small price to pay for the increased reliability and performance of the novel Fluribus architecture.

#### 5.3 Shared Data Structures, Shared Code, and Locks

In a multiprocessor care must be exercised when a piece of data may be referenced (read and/or written) simultaneously by more than one processor. In this context, "simultaneously" means that a process running on one processor desires access to the data while another process running on a second processor already has access to the data. Consider, for example, two processors that are concurrently executing processes which

Description

obtain buffers from a common free storage list. If some interlock is not used, it would be possible for both processors to get the same buffer since the second processor could access the list after the first processor had accessed it but before the pointer was updated.

To avoid this and a multitude of similar situations involving shared resources, a lock mechanism is typically used in programs for multiprocessors. Before a shared resource is accessed by a process, a logical lock is set. All processes determine if the lock is set prior to accessing the resource, and if so, then the process will wait. Only one process can, therefore, have access to the shared resource at any one time.

To be effective it must be possible to test and set a lock in a single operation. A typical implementation provides the ability to read, test, and provisionally modify a memory location in a single interruptable operation. In Pluribus systems this feature is provided by turning memory reads through map register 3 into read-modify-write accesses where the data rewritten is all zeros.

To implement a lock on a shared resource one simply assigns a location (LOCKVAR), addressed through map register 3, to the lock. The resource is unlocked if the lock is non-zero and locked otherwise. A segment of code which accesses a locked resource might look as follows:

L: LDA A2, LOCKVAR (Lock and continue) or (WAIT) BZ L access to shared resource

Ll:

STA

PC, LOCKVAR / Unlock Lock

If a processor falls through the loop at L, the resource was unlocked but is now locked by the process running on this processor. If a processor loops at L, then the shared resource is in use and the processor waits until the lock is released. To unlock the resource at Ll any non-zero quantity could have been stored in LOCKVAR. The current program counter (PC = general register 0) contains one such value which has the additional advantage of leaving a partial trace of the program execution in the lock registers. This trace may be helpful for debugging purposes.

Wher a process encounters a locked resource, it may take one of two actions. As in the above example, it can remain in a tight loop checking the lock until it is unlocked. This type of waiting will be called busy waiting since the processor running the process remains occupied while waiting. Alternatively, a form of non-busy waiting may be implemented where the process may either write itself to the PID or set a timer so that a clock routine will later write it to the PID as described earlier. In either case the processor then is free to seek other tasks while waiting. The busy form of a lock is appropriate in situations where the resource will be locked for only a short period. An example of this is the free buffer list accessing mentioned at the beginning of the discussion on locks. The lock implementation which dispatches the processor to do other useful work will be more suitable in situations where the shared resource is likely to remain locked for a relatively long time. A paper tape reader shared by two processors might be such a resource.

The preceding discussion leaves considerable latitude with respect to what should be locked and when. For example, if each incarnation of a piece of shared code references a set of shared variables, it may be more efficient to associate a single lock

with the set of shared variables than a lock with each of the individual variables. What needs to be balanced against this goal of fewer locks is the desire to keep locked segments short. Large locked segments, while reducing the total number of locking/ unlocking operations required, will tend to increase overhead due to increased busy waiting or processor task switching. This overhead can become quite large on the percentage utilization of the shared resource increases beyond 60 - 70%. For this reason, the system designer must use considerable judgement in deciding on the extent of locked segments. In addition, locks should not remain locked across strip boundaries. Locked segments should also be executed with interrupts disabled so that prompt unlocking of the shared resource is assured.

One further consideration is that a processor may fail while executing a locked segment. Two problems can arise in this case, (1) the locked resource will be unavailable to other tasks and (2) if busy waiting is implemented, processors may be executing infinite loops. Therefore, a processor should only be allowed to wait for the maximum amount of time which the lock can legitimately be set before deciding that a malfunction has occurred and activating a recovery procedure.

Cooperation with respect to the use of shared variables is required between tasks corresponding to different code segments and especially tasks corresponding to different incarnations of the same reentrant code segment. In general, reentrant coding is particularly appropriate in a multiprocessor such as the Pluribus system. The shared code may exist in common memory or multiple copies of the code may exist in the private processor memories to reduce contention. In the ARPA Network application, for example, shared code is used to transmit data from the IMP to each of a number of modems. In this case, the control structure Description

Bolt Beranek and Newman Inc.

illustrated earlier in this section is modified to look as follows:

TASKDISPATCHTABEL: MAINLOOP, TASK1, ..., MODEMOUT, MODEMOUT, ...TASKN

CONTROLBLOCKS: Ø, BLOCK1, ···, MBLOCK1, MBLOCK2, ··· BLOCKN

| MAINLOOP: |     | Al, PIDREADADDRESS<br>@T <b>ASK</b> DISPATCHTABLE (Al) |

|-----------|-----|--------------------------------------------------------|

| MODEMOUT: |     | A2, CONTROLBLOCKS (A1)<br>A3, MODEMLOCK (A2)           |

|           | STA | PC, MODEMLOCK                                          |

|           | JMP | MAINLOOP                                               |

The modem interfaces each write different levels to the PID when output of a buffer is complete but all these levels activate the same piece of shared code, MODEMOUT. The PID levels are used, however, to select the address of a control block which contains the variables specific to the modem being serviced. At the start of MODEMOUT, an instruction is executed which loads an accumulator, (A2), with the address of this control block. One of the words in this block is a lock used to lock all the other shared variables in the block. These variables remain locked for the duration of the modem output tasks.

#### 5.4 Using the Map Registers:

The map registers allow four independent 8K byte segments of the common memory to be referenced by each processor. The only constraint is that a read done through map register 3 will be a read and clear. The other three map registers may be used to

point to program or data as required by the application. It is possible to have two map registers point to the same segment of memory. In the ARPA Network application, for example, map 3 and one of the other map registers point to a segment containing system variables which can be accessed normally or used as lock variables.

In Pluribus systems with small memory configurations little of no map changing may be required. For applications requiring large primary memories, map changing will be more frequent. Of course, it is desirable to design a system so that as little map changing as possible will be required. To change the area of common memory addressed through a particular map register, one simply stores into the map register a constant whose high order 7 bits are to become the contents of the map. As already mentioned in section 4.4, the four maps have addresses FC00, FC02, FC04, and FC06. The code which changes a map must not itself be referenced through that map/ One way to make sure that this does not occur is to execute all map changing code out of private memory.

#### 5.5 Using Multiple PIDs

The PID is the heart of the Pluribus system. Essentially all task dispatching is done via this device. It is important, therefore, that reliability provided by redundancy in the remainder of the Pluribus system components not be jeopardized by availability of only a single PID.

In a multi-PID system, the PIDs will themselves be priority ordered. Typically, the control program in such a system will read the highest priority PID first. If a PID other than the lowest priority PID returns zero, the next lower priority PID will be read. If all PIDs return zero, the control program simply

4

Report No. 2930

cycles by reading the highest priority PID again.

As indicated earlier, a Pluribus system can have up to 4 PIDS, one on each of 4 I/O busses. A hardware device on an I/O bus is associated with a PID on that bus. Software tasks, on the other hand, may write to any of the PIDs in the system. Redundant I/O devices will generally be on different I/O busses and associated with different PIDs.

### 6. DEVICE HANDLING AND I/O

Pluribu's systems may be comprised of two types of I/O devices, BBN-developed devices and Lockheed-developed devices. The primary distinctions between the two are that BBN devices interpret 20-bit addresses and use the PID while Lockheed devices interpret 16-bit addresses and utilize the standard SUE priority interrupt mechanism. Since SUE I/O programming is discussed at length in [2], most of this section will be devoted to the specifics of programming BBN-developed devices. Special considerations relevant to the programming of Lockheed I/O devices in a Pluribus environment are given at the end of the section.

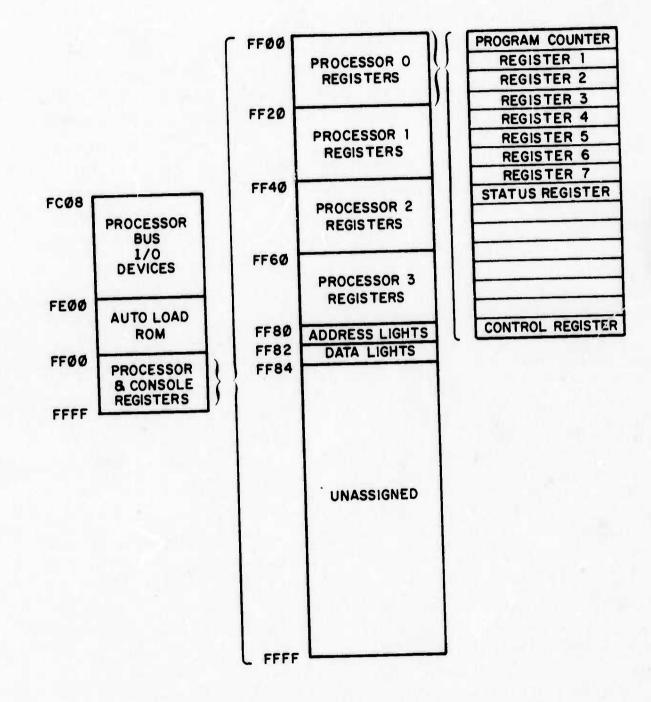

#### 6.1 Address Structure

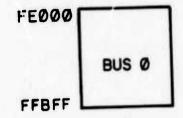

As shown in Figure 2, system addresses FC000 to FFBFF are reserved for Pluribus system I/O space. The detailed structure of this space depends on the allocation of addresses to I/O busses. Figure 5 shows one possible allocation of addresses in the case of a Pluribus with 2 I/O busses. Possible variations on this structure will be indicated later.

The total system I/O space in Figure 5 is divided into four almost equal parts, two of which are assigned to each bus. The high address segment for each bus will be referred to as the primary I/O space and the low address segment as the auxiliary I/O space. Note that the primary address space of bus 1 (from address FF000 to FFBFF) is shorter than the other 3 segments by 1024 bytes because these 1024 addresses are allocated to individual processor maps, registers, and local I/O space as shown in Figure 2. At the beginning of each primary address space are 144 bytes of reserved addresses. These locations are associated with the clock (RTC) and PID on the bus (see sections 10.1 and 10.2), contain the bus coupler (BCM) control registers bescription

-

Bolt Beranek and Newman Inc.

Figure 5

System I/O Space

(see section 9.2), and provide mapping for backwards bus coupling (see section 7.1.3) using this bus.

The remainder of the system I/O space is divided into 16-byte blocks where each block is associated with an I/O device (other than the clock and PID) attached to the bus. These blocks are called device register blocks. A processor activates an I/O device by writing to a certain address within the device register block. A processor can interrogate a device by reading the contents of status registers contained in this block. More detail on the structure of device register blocks is given below and is also contained in section 10. where individual I/O devices are discussed.

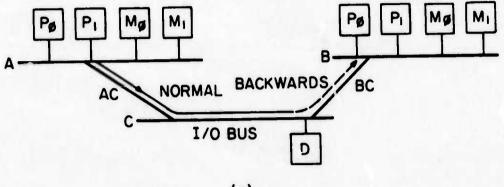

Variation of the structure shown in Figure 5 depends on the number of I/O busses and the allocation of system I/O addresses among them. This allocation is determined by switches on the bus couplers (see section 9.2). Figure 6 indicates allocations of system I/O space for 1, 2, 3, and 4 I/O busses. Only the primary I/O space allocations are shown; the auxiliary allocations are identical to these except that the highest address segment of auxiliary is the same size as the rest of the segments, that is, it is not reduced in size by 1024 bytes. The low 144 bytes of each primary segment is reserved on each bus as indicated in Figure 5. While other allocations are possible, the ones shown in Figure 6 constitute all of the reasonable ones. Switch settings resulting in non-contiguous primary and auxiliary segments for individual busses, while possible, are not considered here.

Bolt Beranek and Newman Inc.

0

.

(a) ONE BUS

(b) TWO BUSSES

| FEOOD |       | FE000 |

|-------|-------|-------|

|       | BUS Ø | FE800 |