ESD-TR-75-303

MTR-3061

**83745** MIDS NETWORK CONTROL AND DIGITAL DATA SUBSYSTEM DESIGNS

DECEMBER 1975

Prepared for

DEPUTY FOR DEVELOPMENT PLANS ELECTRONIC SYSTEMS DIVISION AIR FORCE SYSTEMS COMMAND UNITED STATES AIR FORCE Hanscom Air Force Base, Bedford, Massachusetts

Project No. 7040 Prepared by THE MITRE CORPORATION Bedford, Massachusetts Contract No. F19628-76-C-0001

Approved for public release; distribution unlimited.

ADA 019967

When U.S. Government drawings, specifications, or other data are used for any purpose other than a definitely related government procurement operation, the government thereby incurs no responsibility nor any obligation whatsoever; and the fact that the government may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data is not to be regarded by implication or otherwise, as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture, use, or sell any patented invention that may in any way be related thereto.

Do not return this copy. Retain or destroy.

#### REVIEW AND APPROVAL

During 1972-73 a Base Communications Mission Analysis (BCMA) was conducted at ESD to examine requirements and options for improving and/or replacing Air Force base level communications systems. Several alternatives in two main categories were identified: (1) to optimize wire-pair/ switched systems in current use or (2) use a coaxial cable system to provide a "bus" multimode transmission facility in which channelization is achieved by frequency/time division multiplexing techniques rather than by switched wire pairs.

The BCMA concluded that the second alternative would be more economical on a life cycle basis for the anticipated increase in "desk top" workstation data terminals. As a result, a follow-on project called the Air Force Base Information Transfer System (AFBITS) was undertaken at ESD to examine the multimode system alternatives in greater technical detail. This is the terminal report of the MITRE technical support to the AFBITS project.

Since the concept is applicable to many types of communication complexes, commercial as well as military, the title "Multimode Information Distribution System" (MIDS) is more descriptive of the design concept set forth in this report. This technical report has been reviewed and is approved for publication.

(hustley

ALPH L. WESTLEY, GS-13 Project Engineer

Vare a. Legen m

CARL A. SEGERSTROM Technical Advisor, Programs

FOR THE COMMANDER

the J. Dem

THORNTON T. DOSS, Colonel, USAF Deputy for Development Plans

UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered)

| REPORT DOCUMENTATION PAGE                                                                                                                                                |                                    | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------|

| 1. REPORT NUMBER                                                                                                                                                         | 2. GOVT ACCESSION NO.              |                                                                |

| ESD-TR-75-303                                                                                                                                                            |                                    | ·                                                              |

| 4. TITLE (and Subtitie)                                                                                                                                                  |                                    | S. TYPE OF REPORT & PERIOD COVERED                             |

| MIDS NETWORK CONTROL AND DIGI                                                                                                                                            | TAL DATA                           |                                                                |

| SUBSYSTEM DESIGNS                                                                                                                                                        |                                    | 6. PERFORMING ORG. REPORT NUMBER                               |

|                                                                                                                                                                          |                                    | MTR-3061                                                       |

| 7. AUTHOR(3)                                                                                                                                                             |                                    | 8. CONTRACT OR GRANT NUMBER(s)                                 |

| H.R. Clark                                                                                                                                                               |                                    | F19628-76-C-0001                                               |

|                                                                                                                                                                          |                                    |                                                                |

| 9. PERFORMING ORGANIZATION NAME AND ADDRESS                                                                                                                              |                                    | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS |

| The MITRE Corporation                                                                                                                                                    |                                    |                                                                |

| Box 208<br>Bedford, MA 01730                                                                                                                                             |                                    | Project No. 7040                                               |

| 11. CONTROLLING OFFICE NAME AND ADDRESS                                                                                                                                  |                                    | 12. REPORT DATE                                                |

| Deputy for Development Plans                                                                                                                                             |                                    | DECEMBER 1975                                                  |

| Electronic Systems Division, AFSC<br>Hanscom Air Force Base, Bedford, M                                                                                                  | 14 01791                           | 13. NUMBER OF PAGES 96                                         |

| 14. MONITORING AGENCY NAME & ADDRESS(if differen                                                                                                                         |                                    | 15. SECURITY CLASS. (of this report)                           |

|                                                                                                                                                                          |                                    | UNCLASSIFIED                                                   |

|                                                                                                                                                                          |                                    | 15e. DECLASSIFICATION DOWN GRADING                             |

|                                                                                                                                                                          |                                    | SCHEDULE                                                       |

| 16. DISTRIBUTION STATEMENT (of this Report)                                                                                                                              |                                    |                                                                |

| Approved for public release; distribution                                                                                                                                | ion unlimited.                     |                                                                |

|                                                                                                                                                                          |                                    |                                                                |

|                                                                                                                                                                          |                                    |                                                                |

|                                                                                                                                                                          |                                    |                                                                |

| 17. DISTRIBUTION STATEMENT (of the ebstrect entered in Block 20, if different from Report)                                                                               |                                    |                                                                |

|                                                                                                                                                                          |                                    |                                                                |

|                                                                                                                                                                          |                                    |                                                                |

|                                                                                                                                                                          |                                    |                                                                |

| 18. SUPPLEMENTARY NOTES                                                                                                                                                  |                                    |                                                                |

|                                                                                                                                                                          |                                    |                                                                |

|                                                                                                                                                                          |                                    |                                                                |

|                                                                                                                                                                          |                                    |                                                                |

| 19. KEY WORDS (Continue on reverse side if necessery an<br>COAXIAL CABLE DATA DISTRIBUT)                                                                                 | d identify by block number)<br>ION |                                                                |

| INTERACTIVE TERMINALS                                                                                                                                                    |                                    |                                                                |

| MICROPROCESSOR APPLICATIONS                                                                                                                                              |                                    |                                                                |

| MULTIMODE INFORMATION DISTRIBUTION                                                                                                                                       |                                    |                                                                |

| SIGNALING AND SUPERVISION                                                                                                                                                |                                    |                                                                |

| 20. ABSTRACT (Continue on reverse side if necessery end identify by block number)<br>The Multimode Information Distribution System (MIDS) is a local area telecommunica- |                                    |                                                                |

| tions system capable of simultaneously handling digital data, video and voice traffic                                                                                    |                                    |                                                                |

| for a multitude of subscribers in a variety of connectivity patterns on wideband media                                                                                   |                                    |                                                                |

| such as coaxial cable. The designs for a MIDS data distribution subsystem and a                                                                                          |                                    |                                                                |

| multimode network control subsystem based on time division multiplexed techniques                                                                                        |                                    |                                                                |

|                                                                                                                                                                          |                                    |                                                                |

|                                                                                                                                                                          |                                    |                                                                |

\_

SECURITY CLASSIFICATION OF THIS PAGE(When Date Entered)

20. ABSTRACT

are described. The use of a novel, adaptive data rate feature provides high-speed service to any terminal as required without dedicating excessive amounts of capacity to particular terminals. These designs are oriented toward maximum use of current microprocessor technology.

#### FOREWORD

The system and subsystem designs for a local area multimode information distribution system described in this report have been developed in response to needs for improved and modernized telecommunications on military bases. This design for a common-user communication system is based on the multiplex-bus architecture. The numbers of subscribers, data rates and specific design techniques described have been selected solely for the purpose of conducting a technical feasibility demonstration and do not necessarily represent the service parameters and techniques that would be applicable for an operational system design.

The purpose of the technical feasibility demonstration is to provide sufficient technical data to assess the technical risks of an operational implementation, to provide cost factors for life cycle costing and to establish technical parameters for preparing system specifications.

This project was performed by The MITRE Corporation under sponsorship of the Electronic Systems Division, Air Force Systems Command.

# TABLE OF CONTENTS

.

|                                 |                                                                                                                                                                                                                                                      | Page                             |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| LIST OF FIGU                    | IRES                                                                                                                                                                                                                                                 | 5                                |

| GLOSSARY OF                     | ABBREVIATIONS AND ACRONYMS                                                                                                                                                                                                                           | 7                                |

| SECTION I                       | INTRODUCTION                                                                                                                                                                                                                                         | 9                                |

| 1.2                             | BACKGROUND<br>OPERATIONAL ASPECTS<br>DATA SYSTEM TRAFFIC CHARACTERISTICS                                                                                                                                                                             | 9<br>10<br>10                    |

| SECTION II                      | MIDS SYSTEM DESCRIPTION                                                                                                                                                                                                                              | 12                               |

| 2.2<br>2.3<br>2.4<br>2.5        | GENERAL<br>INFORMATION TRANSFER SERVICES<br>NETWORK CONFIGURATION SYSTEM DESIGN<br>SIGNALING AND SUPERVISION (S&S) CHANNEL DESIGN<br>DATA DISTRIBUTION CHANNEL DESIGN<br>DESIGNING WITH MICROPROCESSORS                                              | 12<br>12<br>14<br>16<br>18<br>20 |

| SECTION III                     | SIGNALING & SUPERVISION (S&S) SUBSYSTEM                                                                                                                                                                                                              | 29                               |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6 | GENERAL<br>USER/SYSTEM CONTROL INFORMATION FLOW<br>SIGNALING AND CHANNEL TIMING<br>NETWORK CONTROL PROCESSOR (NCP)<br>SIGNALING AND SUPERVISION CHANNEL CONTROLLER<br>SIGNALING AND SUPERVISION KEYPAD CONTROL UNIT<br>KEYPAD S&S CONTROL UNIT MODEM |                                  |

| SECTION IV                      | DIGITAL DATA DISTRIBUTION SUBSYSTEM                                                                                                                                                                                                                  | 59                               |

| 4.2<br>4.3<br>4.4<br>4.5        | MULTIPORT DATA BUFFER UNIT                                                                                                                                                                                                                           | 59<br>65<br>79<br>81             |

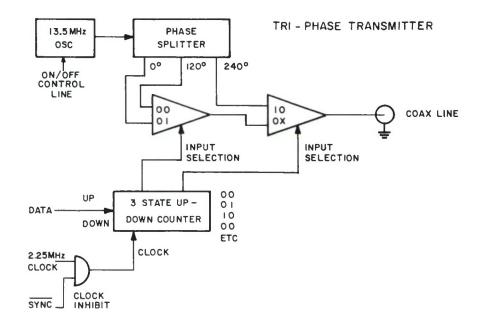

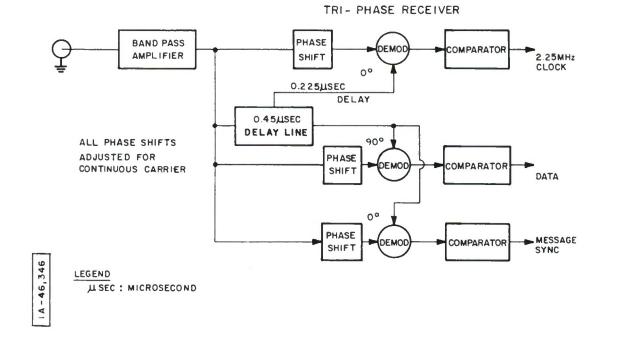

| 4.6                             | DATA DISTRIBUTION SUBSYSTEM MODEM                                                                                                                                                                                                                    | 84                               |

| SECTION V                       | IMPLEMENTATION                                                                                                                                                                                                                                       | 88                               |

| APPENDIX A                      | ADAPTIVE DATA RATE TRAFFIC ANALYSIS                                                                                                                                                                                                                  | 89                               |

.

3

# REFERENCES

Page

95

# LIST OF FIGURES

Page

.

# Figure Number

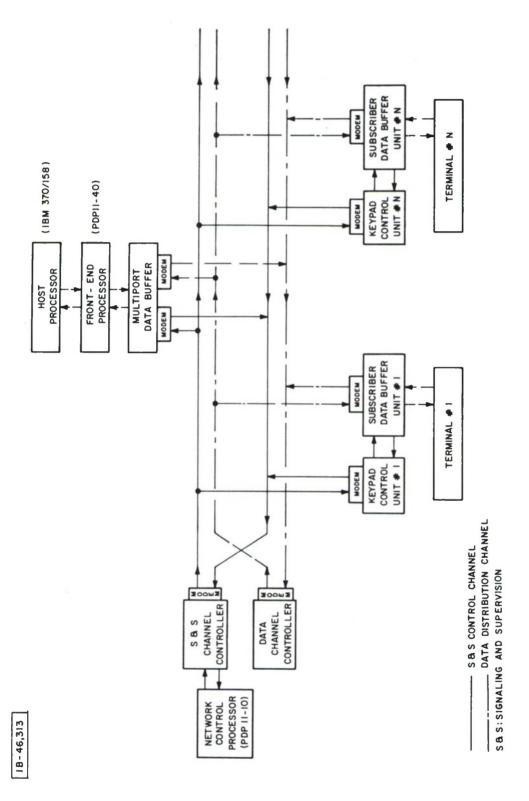

| 1        | Data Distribution and Control Network                                    |    |

|----------|--------------------------------------------------------------------------|----|

|          | Configuration                                                            | 15 |

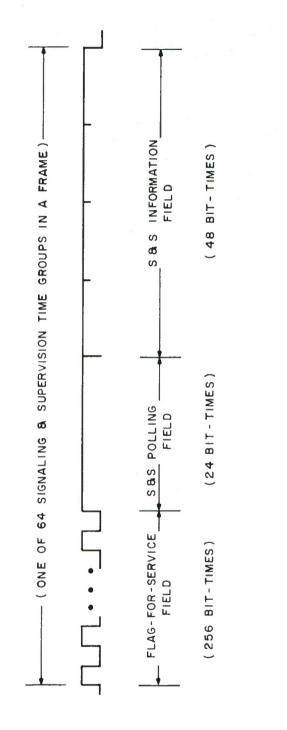

| 2        | Signaling and Supervision Subsystem Message                              |    |

| -        | Fields                                                                   | 17 |

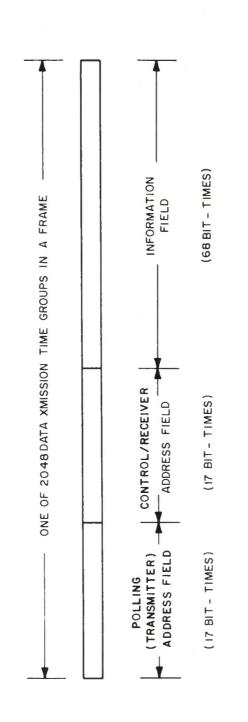

| 3        | Data Distribution Subsystem Message Fields                               | 19 |

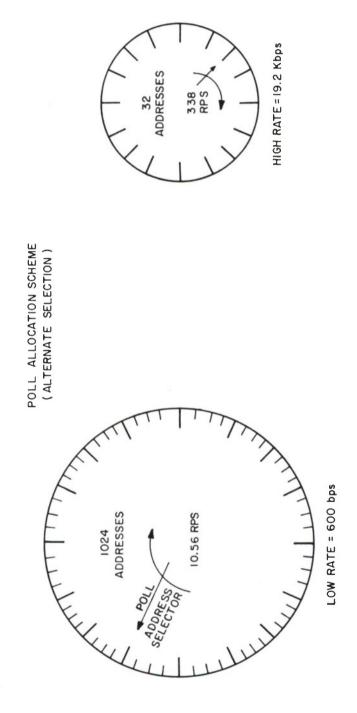

| 4        | Self-Adaptive Data Rate Polling Analogy                                  | 21 |

| 5        | Digital System Functional Blocks                                         | 23 |

| 6        | Microcomputer Chip Set                                                   | 25 |

| 7        | Simplified Microcomputer Architecture                                    | 27 |

| 8        | Keypad and Indicator Layout                                              | 31 |

| 9        | Dialing Sequence                                                         | 33 |

| 10       | Keypad Lamp Indicator State Diagram                                      | 35 |

| 11       | Signaling and Supervision Subsystem Message Time                         |    |

| 10       | Frame                                                                    | 37 |

| 12       | Signaling and Supervision Message Timing                                 |    |

|          | Sequence                                                                 | 39 |

| 13       | Signaling and Supervision Subsystem Channel                              |    |

| 2.11     | Controller                                                               | 42 |

| 14       | Keypad Control Unit                                                      | 44 |

| 15       | Flag-for-Service Logic                                                   | 46 |

| 16       | Signaling and Supervision Data Receiver                                  |    |

| 17       | and Transmitter                                                          | 48 |

| 17       | Operator Interface                                                       | 51 |

| 18       | Keypad Control Unit Microprocessor                                       | 53 |

| 19       | Subscriber Data Buffer Interface                                         | 55 |

| 20       | Keypad Control Unit Modem                                                | 57 |

| 21       | Data Distribution Subystem Polling and                                   |    |

| 22       | Timing<br>Data Subauatan Masaaga Farmat                                  | 60 |

| 22       | Data Subsystem Message Format                                            | 62 |

| 23<br>24 | Data Transmission Time Group                                             | 64 |

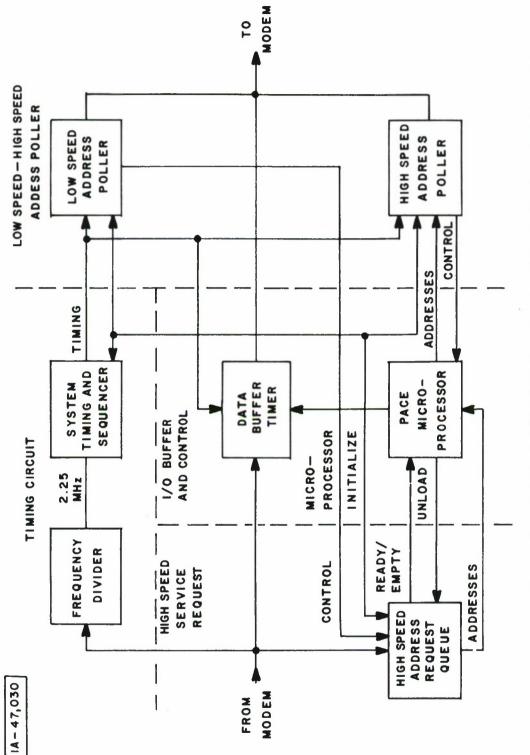

|          | Data Distribution Subsystem Channel Controller                           | 66 |

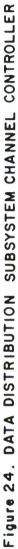

| 25       | Data Channel Controller Timing Circuits                                  | 68 |

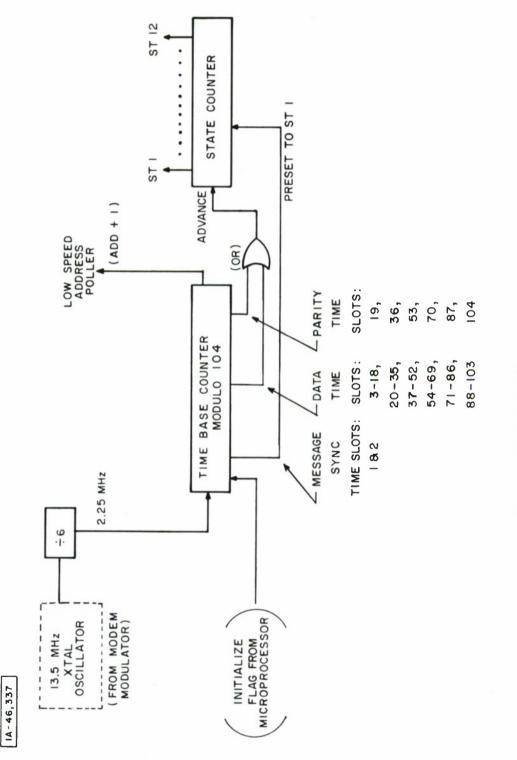

| 26       | Low Speed and High Speed Address Poller                                  | 69 |

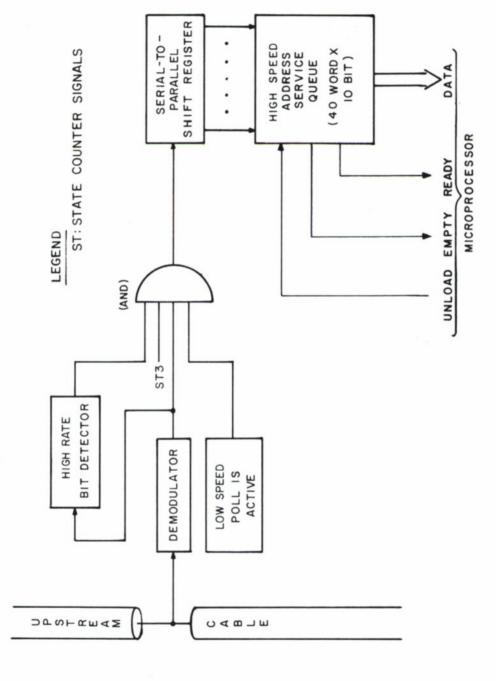

| 27<br>28 | Request for High Speed Service<br>Data Channel Controller Microprocessor | 71 |

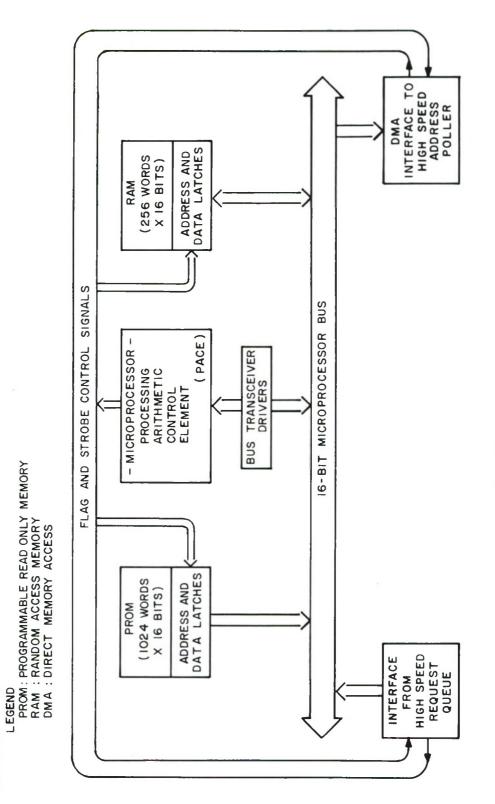

| 29       | Microprocessor Software for Data Channel                                 | 72 |

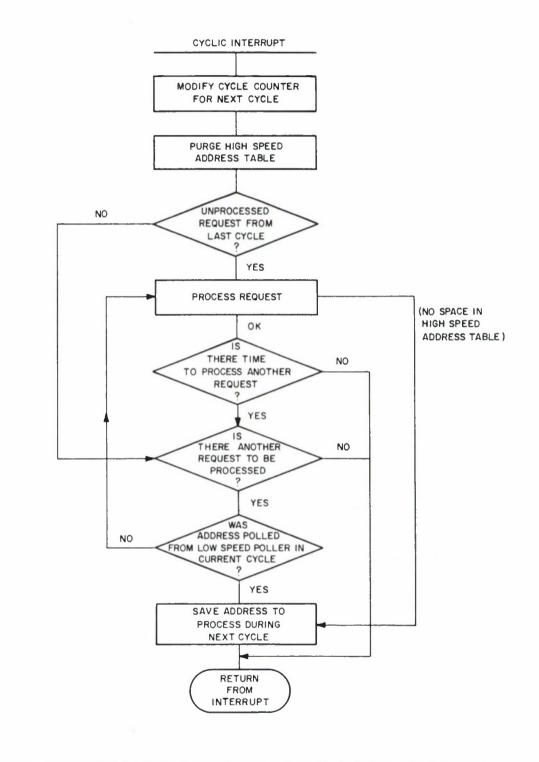

| 27       | Controller                                                               | 75 |

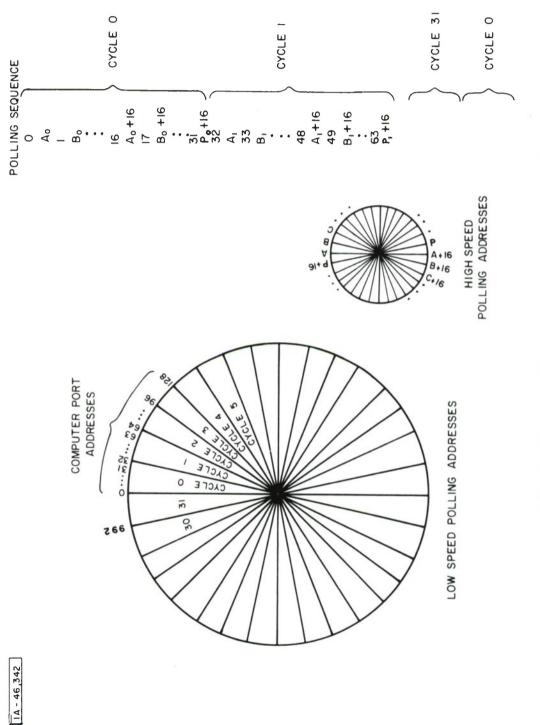

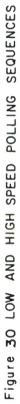

| 30       | Low and High Speed Polling Sequences                                     | 75 |

| 20       | TOM SUG ITEN PRESS LOTITIE PERMENCEP                                     | 76 |

|                                                                                                                                                                | Page                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <ul> <li>31 Software Timing</li> <li>32 Subscriber Data Buffer Unit</li> <li>33 Multiport Data Buffer Unit</li> <li>34 Digital Data Subsystem Modem</li> </ul> | 77<br>80<br>82<br>85 |

# GLOSSARY OF ABBREVIATIONS AND ACRONYMS

| ACC    | Accumulator                                        |

|--------|----------------------------------------------------|

| ADR    | Asynchronous Data Receiver                         |

| ASCII  | American Standard Code for Information Interchange |

| bps    | bits per second                                    |

| CATV   | Community Antenna Television                       |

| CCIS   | Common Channel Interoffice Signaling •             |

| CCITT  | Consultative Committee of International Telegraph  |

|        | and Telephone                                      |

| CPU    | Central Processing Unit                            |

| CVSD   | Continuous Variable Slope Delta                    |

| dbmv   | decibels with respect to 1 millivolt (0 dbmv=lmv)  |

| DMA    | Direct Memory Access                               |

| EBCDIC | Extended binary Coded Decimal Interchange Code     |

| EPROM  | Erasable and Programmable Read Only Memory         |

| FDM    | Frequency Division Multiplex                       |

| FIFO   | First-in First-out                                 |

| IIL    | Integrated Injection Logic                         |

| IR&D   | Independent Research and Development               |

| KBD    | Keyboard                                           |

| kbps   | kilobits per second                                |

| LSI    | Large Scale Integrated                             |

| MIDS   | Multimode Information Distribution System          |

| MOS    | Metal-oxide semiconductor                          |

| mv     | millivolt                                          |

| PACE   | Processing and Control Element                     |

| PFEP   | Programmed Front-End Processor                     |

| PROM   | Programmable Read Only Memory                      |

| RAM    | Random Access Memory                               |

| RF     | Radio Frequency                                    |

| RMS    | Root Mean Square                                   |

| ROM    | Read Only Memory                                   |

| S&S    | Signaling and Supervision                          |

| TDM    | Time Division Multiplex                            |

| TPM    | Tri-Phase Modulation                               |

| TTL    | Transistor-transistor logic                        |

| UART   | Universal Asynchronous Receiver Transmitter        |

#### SECTION I

#### INTRODUCTION

## 1.1 BACKGROUND

The communications facilities that interconnect the various sensors and information processors are an important element of Command and Control systems. These communications facilities must be capable of handling a wide variety of analog and digital signals for voice, data and video traffic. During the last few decades substantial improvements have been made in the capabilities of long haul wideband trunk communications systems by employing microwave and troposcatter radio links and communications satellite links. For local signal distribution on an air base, within a local operating area or in command center complexes, communications were handled primarily by means of individual pairs of wires, cables or radio links interconnecting each user or equipment. Flexibility of interconnection is provided by means of patch panels and/or electromechanical circuit switches.

Recent advances in digital technology and broadband transmission media now permit the development of Multimode Information Distribution Systems (MIDS) employing "multiplex bus" techniques for local distribution communications. Multiplex refers to combining many different signals on a single transmission system. This technique is commonly used for long haul communications. The term "bus" indicates the capability to serve a number of geographically distributed terminals in a local area. These multiplex bus systems offer improved performance, versatility and portability at less cost, bulk and weight than current local distribution communications facilities.

Broadband communications over coaxial cable and through optic fibers are now state-of-the-art. Technological advances in digital technology permit the implementation of low cost frequency division and time division multiple access to a broadband bus. A variety of communication services then becomes possible for many users. Command and control communications in the future should be capable of handling multi-megabit data rates and multi-channel secure telephone and video transmission. The presentation of remote radar and other surveillance signals, as well as the standard visual display terminal information, will be accomodated. The technical capability of accomplishing these multiple services under a single communication control utilizing a single transmission medium will permit the dynamic reallocation of communication resources in accordance with demand.

### 1.2 OPERATIONAL ASPECTS

A multimode communications system will provide the connection between a user's terminal and information sources such as minicomputers, large host processors, microfiche storage, and other data, video and audio information sources. For example, a user visual display terminal may be used as a monitor for a surveillance or command situation and may also be used for entering text into a word processing system for preparation of messages, status reports and correspondence. The same terminal may also be used to query an information bank in a host processor or it may be connected into a distributed-processing system consisting of minicomputers with each having a specialized processing function. Since the digital data distribution and control subsystems occupy only two channels of the multi-channel coaxial cable, many other uses of the cable are simultaneously possible as described in References 1 and 2.

The principal technical capability required for the implementation of a multimode information distribution system is a supervision and signaling subsystem to control connectivity and a digital data distribution subsystem for data transfer. The experimental work to date therefore as described in this report has been specifically addressed to the data interconnection and control aspects of a MIDS using coaxial cable as the transmission medium.

## 1.3 DATA SYSTEM TRAFFIC CHARACTERISTICS

Data traffic is a function of the transmission rate of the subscribers' terminals and the number of subscribers requesting simultaneous use of the service. Terminal transmission rates can vary from as low as 110 bits per second for electromechanical printers to tens of kilobits/sec for visual display terminals. The number of user terminals performing transactions simultaneously can vary from a low value in slack periods to a high value during peak activity periods. Not all terminals however need the capability for simultaneous transmission or reception. For example, if a visual display terminal is supplied with one or more pages of storage, the terminal operator may begin entering data into the terminal's storage without actually transmitting any information to another computer or terminal. After entering a page of information, many terminals allow the operator to make text-editing changes, again without transmitting to a central computer. When the terminal operator has entered the information correctly, the entire screen of information needs to be transferred at high speed to its destination. The requirement, then, is for a system capable of handling bursts of information at high speed for short periods of times.

The MIDS design accommodates this requirement by providing a standard low speed of 600 bps capable of automatically switching to 19.2 kbps in accordance with the transmission requirements of the individual terminals. The dynamic switching is automatic and does not require any user action. Since only a small number of users are actually transmitting at any one time, the overall system transmission rate may be kept to a reasonable upper value.

#### SECTION II

#### MIDS SYSTEM DESCRIPTION

#### 2.1 GENERAL

A Multimode Information Distribution System (MIDS) is a telecommunications facility capable of simultaneously handling digital data, video and voice traffic multiplexed on a single transmission system that serves a multitude of geographically distributed subscribers. For local information distribution in areas ranging in size from a command center complex or shelter to an airbase or similar size operational area, broadband coaxial cable of the type extensively used by the CATV industry is currently the most economical transmission media. Future developments in fiber optics will also be applicable for MIDS transmission links.

A MIDS must be able to provide a variety of connectivities including:

- o Point-to-Point (terminal-to-terminal/person-to-person)

- o One-to-many (multipoint or broadcast)

- Many-to-one (remote terminals to Automatic Data Processing computer)

## 2.2 INFORMATION TRANSFER SERVICES

The information transfer services possible with a MIDS may be provided by using an integrated set of subsystems. Pertinent characteristics of each subsystem are described in the following subsections.

#### 2.2.1 Common Channel Network Control Subsystem

The network control subsystem for a MIDS is provided by a separate out-of-band, polled, asynchronous, time-division-multiplex (TDM) signaling and supervision channel capable of handling multimode connectivity for up to 16,000 addresses. A separate channel is used because it provides net control flexibility and improved efficiency for multimedia services and permits in-process call modificaton without the need to break down established connectivities. It is conceptually compatible with the Common Channel Interoffice Signaling (CCIS) being implemented by the common carriers in accordance with CCITT signaling system No. 6 recommendations. The polled asynchronous S&S technique is being employed because it provides response to service requests in less than one second yet minimizes the complexity and cost of each terminal interface device.

# 2.2.2 Digital Data Distribution Subsystem

Digital data distribution in a MIDS can be provided by a polled TDM subsystem which provides connectivity to those individual terminals which have requested digital data service by means of the common control channel. Up to 1024 data ports (i.e., terminals) can be simultaneously serviced at 600 bps with an automatically adaptive data rate in bursts up to 19.2 kbps.

The polled TDM technique is being employed for digital data distribution because it offers the capability to minimize the subscriber connect cost while providing flexibility for handling various message formats. It also permits implementation of the automatically adaptive data rate feature.

#### 2.2.3 Video Distribution Subsystem

Video distribution in a MIDS can be accomplished in several ways. The simplest method is to establish a number of fixed channels with frequency multiplex equipment. The subscriber then selects which channel he will receive with a tuner on his terminal. This technique, which is employed in CATV systems, is satisfactory only when a limited number of video channels are required.

The multiplexing of many video channels on a single coaxial cable is being successfully accomplished daily in hundreds of CATV systems. Almost all of these systems, however, have no interactive communication capability since they lack suitable network control/signaling and supervision subsystems.

A much larger traffic handling capacity can be provided by dynamic allocaton of frequency channels only for the duration of each video transmission. Subscriber connections are established by the network control assignment of channels and digital tuning of each subscriber's remotely controlled video modem to the assigned frequency channel. The principal development required for this system is a digitally controlled broadband subscriber modem. Additional capacity increases can be obtained through use of local video framegrabbers for static video or character display images so that trunk channels can be released for reuse immediately upon transfer of each video image.

#### 2.2.4 Voice Service Subsystem

Telephone service in a MIDS can be provided by means of either Frequency Division Multiplex (FDM) or Time Division Multiplex (TDM) techniques. The frequency multiplexing of many voice channels on a single coaxial cable has been demonstrated on a limited scale by the Collins Radio ATX-101 Decentralized Switching Telephone System.

For military applications a TDM system, however, would probably be more desirable since digitized speech signals are more amenable to the application of security techniques. A telephone subsystem for use in a MIDS could be developed using either the Bell System 64 kbps T-Carrier standards or the DoD 16/32 kbps continuous variable slope delta (CVSD) standards.

# 2.3 NETWORK CONFIGURATION SYSTEM DESIGN

The control and data distribution elements for a MIDS are illustrated in Figure 1. The transmission path is a wideband coaxial cable of 300 MHz bandwidth. Separate upstream and downstream cables are used to minimize mutual interference. If a single cable were used for a two-way system, carefully-engineered bi-directional amplifiers containing expensive filters to minimize amplitude and frequency distortions over long cable runs would have been required. In addition a large number of two-way interactive terminals accessing a single cable would have collectively presented a potential high source of noise to the system.

Control and data distribution signals are transmitted on separate frequency channels of the same multi-channel cable. The control channel performs the signaling and supervision function. The data distribution channel transmits messages to their proper destinations. Each Subscriber Data Buffer Unit contains a propagation-delay equalizer that is adjusted during the initial system line-up procedure. The time delay equalizers compensate for the difference in distance that exists between terminals close-in to the channel controller as compared to terminals at the far-end of the cables. The combination of the delay equalizers plus the provision of an inter-message frame gap prevents messages in one time slot from overlapping messages in adjacent time slots.

The signaling and supervision control channel terminates in a network control processor such as a PDP-11 minicomputer or equivalent. A minicomputer is required since the network is planned to eventually provide many more services than just data transmission and distribution (References 1 and 2).

#### 2.4 SIGNALING AND SUPERVISION (S&S) CHANNEL DESIGN

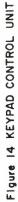

The S&S control channel provides the path for accepting requestfor-service signals from subscribers' terminals and for sending status and address information back to subscriber terminals. The S&S subsystem uses a form of polled, asynchronous, time-divisionmultiplex transmission. The polling from the S&S channel controller is initiated by a flag-for-service request from the subscriber's terminal.

The information flow over the S&S channel is illustrated in Figure 2. There are 64 signaling and supervision time groups in a time frame. The time group is divided into a flag-for-service field, a polling field and an information field. The flag-forservice field contains 256 bit times. This quantity of bit-times repeated over 64 time groups yields 16,384 bit positions. A flagfor-service technique is used to handle requests for service from any of 16,384 subscribers. Each subscriber's keypad is assigned a code (directory address) which corresponds to a unique bit position in the field of 16,384 bits in the time frame. Starting with the beginning of each time frame, the keypad logic counts each bit received on the downstream cable until its assigned bit position is reached. At this point in time, the keypad logic sends a flag-forservice pulse on the upstream cable. In the meantime the subscriber may enter his service request by depressing the appropriate keys on the keypad.

The channel controller recognizes the flag-for-service pulse because of its time position and then polls that subscriber by sending the address of his keypad in the next available polling field. When the keypad recognizes its polling address on the downstream cable, it responds by transmitting the stored keystrokes and status information on the upstream cable during the time occupied by the 48-bit information field. The channel controller accepts the keystroke/status information which conveys the subscriber's request and forwards it to the network control processor. The remaining 63 time groups in the same time frame are available for "simultaneous" servicing of other subscribers.

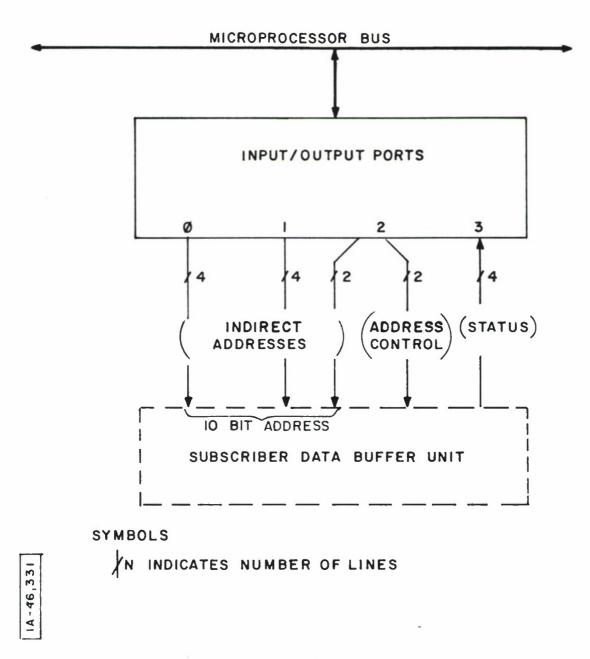

The network control processor then checks availability of equipment involved in the desired connection. Presuming availability, the network control processor sends the necessary indirect-address information to the keypad control unit for transfer to the Subscriber Data Buffer Unit. Data transmission between subscribers may then begin on the data distribution channel.

IA-46,314

The message format for the S&S polling field and information field uses an 8-bit character structure. Character transmission is performed on a conventional start-stop asynchronous basis. The design of the S&S channel is described in detail in Section 3.

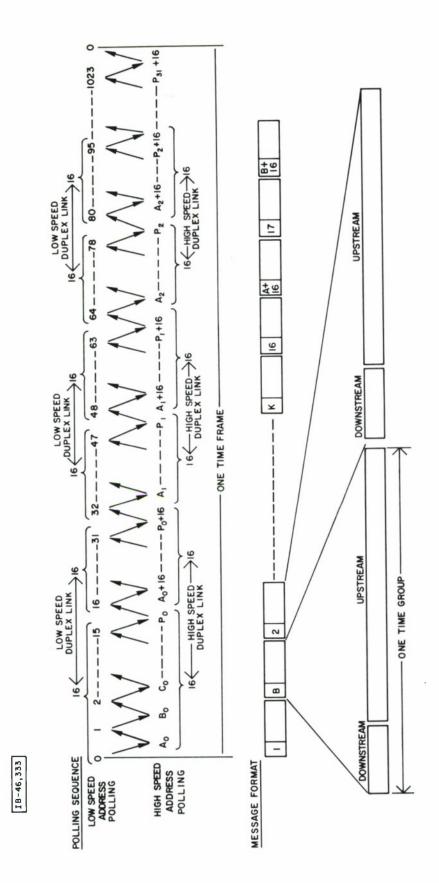

#### 2.5 DATA DISTRIBUTION CHANNEL DESIGN

The digital data distribution subsystem is based on a form of polled, time-division multiplexing. This subsystem will accommodate up to 1024 simultaneous data users. The data distribution channel controller sequentially polls all 1024 addresses in its polling table. These addresses are not permanently assigned to any particular terminal and do not correspond to the fixed address of the terminal's keypad. For this reason the addresses used in the digital data distribution subsystem are called indirect addresses. The indirect addressing feature is used to allow up to 1024 terminal connections to time-share the data channel out of a population of 16,384 subscribers.

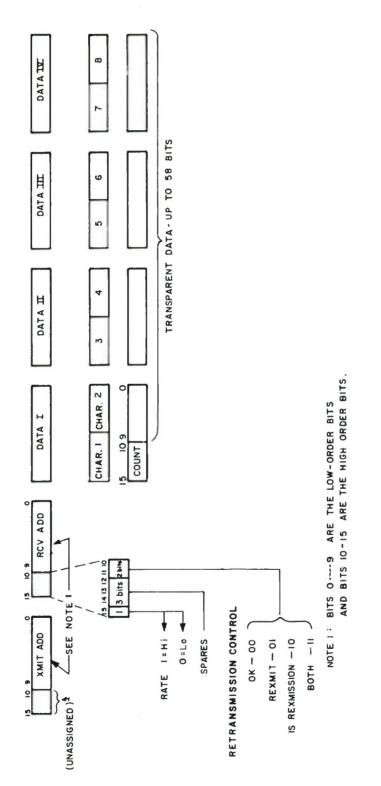

The structure of the message fields used on the data channel is illustrated in Figure 3. During the polling (transmitter) address field time the data channel controller sends on the downstream cable the address of the terminal which is expected to transmit. When the polled terminal recognizes its address, it uses the remaining 85 bit-times to send its data message on the upstream cable. The data message contains a control/receiver address field followed by an information field. The information field contains the remaining 68 bits which consist of four 16-bit words with each word followed by a single parity bit. The data channel controller passes the upstream data message to the downstream cable following the next available polling address field. During this downstream transmission the receiving terminal accepts the data messages previously inserted by the transmitting terminal. This completes a typical transmit-to-receive cycle.

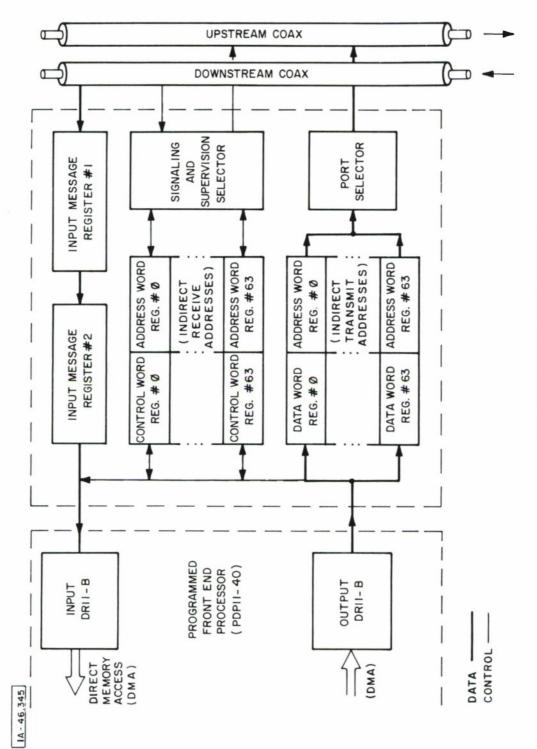

In order to provide simultaneous multiple terminal access to common-user facilities such as a data processing computer, a multiport data buffer unit is being developed (see Figure 1). This multiport data buffer design is capable of providing communication between 64 terminals on the cable and a large host-processor computer. The host processor would interface to the multiport data buffer through a front-end-processor such as a PDP 11-40 minicomputer. The advantage of using the multiport data buffer unit over individual subscriber data buffer units for such access is that common circuits may be used. For example, only one set of modems is required by the multiport data buffer unit to interface the cable.

Thus, the many-to-one connectivity of multiple terminals to a host computer is economically achievable.

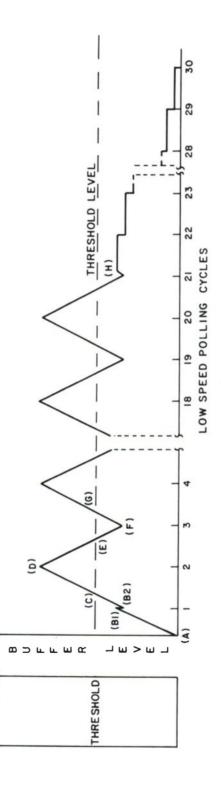

A unique feature of the digital data distribution system is that the data rate to any particular terminal is automatically adapted to fulfill the traffic activity demands of each terminal. The adaptive data rate permits the system to automatically switch a terminal from a basic 600 bps data rate to a higher speed of 19.2 kilobits per second as demanded by terminal traffic activity. Of the 1,024 simultaneous on-line terminals any 16 pairs of terminals are permitted the higher data rate as required. The interaction of the 600 bps and 19.2 kbps data rates can be visualized as two circular polling queues shown in Figure 4. The poll address selectors within the circular queues rotate at a different speed. The 600 bps data rate terminal devices are on the low-speed selector rotating at 10.56 revolutions per second. Terminal devices requiring 19.2 kbps data rate service are temporarily assigned to the high speed selector rotating at 338 revolutions per second. Alternate interleaving of poll addresses from the two queues provides the TDM servicing of all terminals which may be active. Automatic adaptive data rate service is provided by monitoring the output buffer in each terminal interface device, thereby permitting efficient dynamic allocaton of capacity. As the output buffer fills up, the polling rate to that terminal is increased providing a high data rate transfer and a rapid screen fill time for visual display terminals. As the buffer is emptied, the polling rate decreases to a lower effective data rate. This lower data rate is sufficient to handle normal keyboard activity of 15 characters/second yet maintains terminal connectivity so that rapid data transfer can take place without need for reestablishing a connection for each transmission. The design of the data distribution channel is described in detail in Section 4 and the traffic-handling capacity is analyzed in Appendix A.

#### 2.6 DESIGNING WITH MICROPROCESSORS

#### 2.6.1 Logic Design Considerations

From the preceding system description and the diagram in Figure l it is evident that both the signaling and supervision control channel and the data distribution channel will involve a large number of logic functions. The traditional design approach used to implement these functions would be either with hard-wired logic, a minicomputer, or a combination of both to perform the various system element functions. The minicomputer approach would be used when there was sufficient arithmetic computation and storage required. The hard-wired logic approach provides an intrinsically faster logic

IA-46,315

system. This is based on the fact that hard-wired logic is not limited to serial implementation of logic as in stored-program computers. Thus, there can be many parallel processes being performed simultaneously with hard-wired logic. The disadvantage of hard-wired logic is the duration and cost of the design, procurement, fabrication, and test cycles. If the unit is to be used in very high volume production, then custom large scale integrated (LSI) circuits may be used to overcome some of the costliness of the hard-wired logic approach. However, if day-to-day operation in the "field" later produces a requirement to change the logic, the expense of the manufacturing modification to the LSI chip may easily offset the initial gain. Changes in etched-foil circuit cards are likewise difficult and expensive.

An attractive economical alternative to the hard-wired logic approach or the minicomputer approach has recently become available with the introduction of microprocessors. Although microprocessors are implemented with serial logic as in any computer, their very small size and low cost make them a first choice consideration as a desirable system design element. Where speed of processing is critical, a few conventional integrated-circuit logic elements may be interfaced with the microprocessor to handle the high speed functions or alternatively, two or more microprocessors may be used. The low cost of the microprocessors makes this practical. Even if the hardware cost of the multiple microprocessors came up to the level of the hard-wired logic assemblage, the overall implementation cycle from design to test is, in general, much shorter using the microprocessor approach. Additionally, the microprocessor approach offers ease of system modification. The judicious use of microprocessor elements therefore offers the distinct possibility of improved designs with lower overall costs and smaller package size.

#### 2.6.2 Digital System Functional Blocks

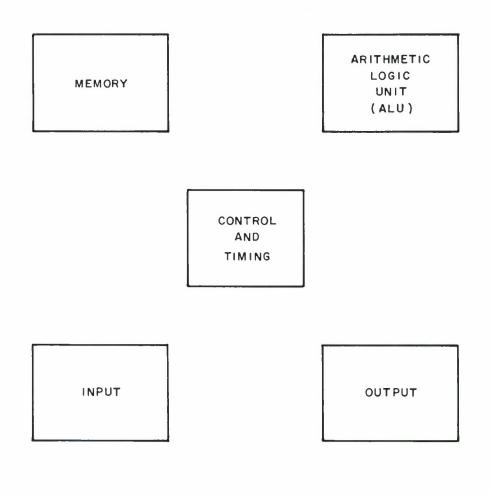

Digital microprocessor systems are characterized by five basic functional building blocks. As illustrated in Figure 5 these blocks include the following functions: Memory, Arithmetic Logic Unit, Input, Output, and Control and Timing. Memory is used to store both data files and program sequences. The Arithmetic Logic unit performs the arithmetic and the Boolean logic functions required by the system application. The input functional block is used to interface such input devices as keyboards, data demodulators, transmission line receivers, etc. The output functional block interfaces such output devices as printers, indicators, data modulators, transmission line drivers, etc. The control and timing block operates the steering circuits that interconnect the other system elements. The control sequence causes the actual digital

Figure 5 DIGITAL SYSTEM FUNCTIONAL BLOCKS

control algorithm for the particular system application to be executed. The timing circuits assure that the information will be gated between the various system elements in a non-hazardous fashion, e.g., so that flip-flops will only change state at the time of a clock pulse. As the program memory contains the complete instruction sequence, the digital system is said to be a storedprogram machine and the operations can be readily modified by changing the contents of memory.

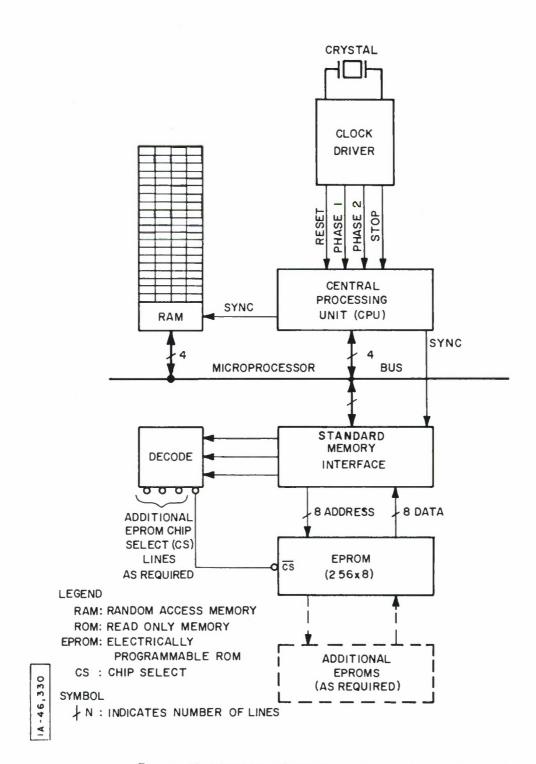

## 2.6.3 Microcomputer Chip Set

In digital computers the arithmetic logic unit and the control and timing circuits are generally grouped together in the same hardware area. This grouping is called the central processing unit (CPU) of the computer.

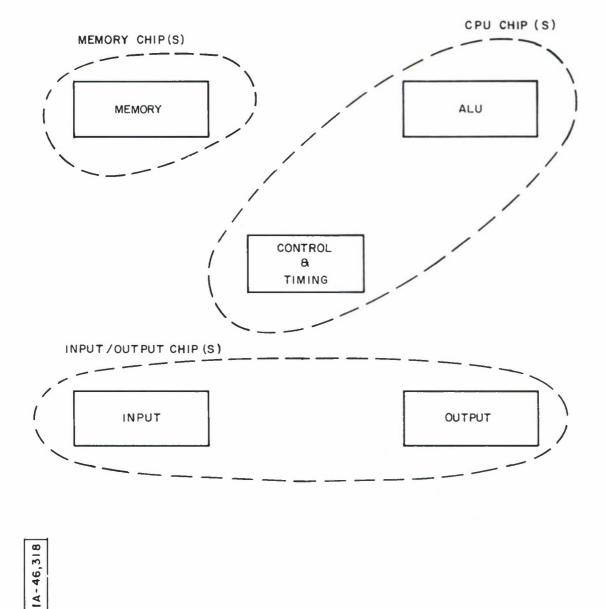

The term microprocessor has both a narrow and a broad connotation. In its narrow connotation it means central processing unit. In its broad connotation it means the entire microcomputer set. Most microprocessor manufacturers offer a family of integrated circuits to perform the entire digital system function. Since the integrated circuit is formed from a silicon chip, the circuits are often called "chips". The grouping of the digital system functions into a typical microcomputer chip set is illustrated in Figure 6. One of the chips is the CPU chip. This chip is often referred to as the microprocessor chip. Another chip is the memory chip. Depending on memory storage requirements several memory chips may be needed to satisfy a system application. A third chip is the input/output chip. Depending upon the number of peripherals to be interfaced, this could be one or more chips.

It is interesting to note that the memory chip provided the impetus for the entire microprocessor development. The chip manufacturers achieved a very large reduction in size for the memory circuits. In order to promote the use of these memory circuits, their development effort was turned to the task of producing a central processing unit on a chip which employed the same technologies and production facilities. This development started with a four-bit central processing unit for hand-held calculators, then advanced to an 8-bit CPU unit; even 16-bit CPU units are available today.

### 2.6.4 Microcomputer Architecture

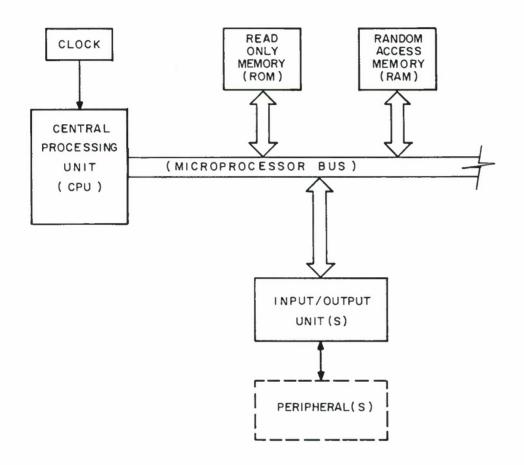

The microprocessor architecture has followed the trend established by modern minicomputers. It uses a bus structure to interconnect the various digital system functional elements as

# Figure 6 MICROCOMPUTER CHIP SET

illustrated in Figure 7. The microprocessor bus, itself, is merely a set of parallel lines used to transfer the data and control signals. For example, in a 4-bit microprocessor configuration, four lines are utilized on a time-sharing basis to distribute memory address, instructions, and data in 4-bit groups, each in its own sub-cycle of time.

In most microprocessors the input/output units have an interrupt capability that permits the CPU to perform logic and arithmetic operations without checking the state of the peripherals. When a peripheral device requires service, the input/output unit signals the central processing unit via an Interrupt line. The CPU then suspends its normal operation and services the peripheral unit.

A separate clock-circuit chip is often used as the source of accurate timing for the CPU which in turn maintains the synchronism for the entire set of microcomputer elements.

In the memory area the microprocessor architecture usually distinguishes between Random Access Memory (RAM) requirements and Read Only Memory (ROM) requirements. The random access memory chip contains volatile data that will be entered into memory at the start or during execution of the program. Most of this data is of a variable nature that will be changed during the processing of the various transactions. Microprocessors, in replacing hardwired logic systems, require not only an immediate start up with application of power, but also require a permanent program memory which will not change unintentionally with the passage of time. Hence, the need for Read Only Memory (ROM) elements is dictated for program storage.

The integrated circuit devices use a metal oxide silicon (MOS) fabrication technique. MOS is a technique that consumes minimum power thus providing the ability to put up to 2,000 logic gates on a chip. The older and more conventional TTL logic, although faster, uses more power because it has resistive components in the chip. Some vendors are offering TTL CPU chips in four-bit slices. The slices can be assembled into 8-bit or 16-bit central processing Since each slice is an individual chip, the heat dissipated units. in a 16-bit CPU is distributed among 4 chips. The choice of using a MOS CPU chip or a set of TTL bit-slice chips is a design trade-off between speed and quantity of chips. Recently a new technology called integrated injection logic (IIL) has been developed (Reference 3). This technology combines the low power dissipation of MOS with the high speed performance of TTL and promises to permit even more applications for microprocessors in the future.

Figure 7 SIMPLIFIED MICROCOMPUTER ARCHITECTURE

#### 2.6.5 Microprocessor Application to MIDS

In the MIDS network configuration of Figure 1, there are system logic elements that process 4 bits, 8 bits, or 16 bits with various speed or throughput requirements. A range of microprocessors is now available to meet these applications. For example the keypad control unit transmits 15 different keystrokes. Since up to 16 keystrokes can be encoded by 4 bits, this is an obvious application for a 4-bit microprocessor. Furthermore, and perhaps most importantly, a 4-bit microprocessor has sufficient speed characteristics to process the major control activities associated with the keypad unit. The MIDS laboratory development system is using the Intel 4040 four-bit MOS microprocessor system for the Keypad S&S subsystem (Reference 4).

At the headend of the cable, a PDP-11 minicomputer provides the signaling and supervision control for up to 16,000 subscribers. In earlier designs the hardware interface between the cable and the minicomputer was performed by a hard-wired logic controller. In the MIDS laboratory development system a 16-bit microprocessor is being used to interface with the 16-bit PDP-11 minicomputer. A National Semiconductor Corporation 16 bit MOS microprocessor called the Processing And Control Element (PACE) is being used for this application (Reference 5).

The MIDS system connects a terminal to the cable through a Subscriber Data Buffer Unit. Since data transmission is character oriented, an 8-bit microprocessor could be used. In a large-scale commercial network an 8-bit microprocessor would probably be chosen for this application. However, for the MIDS laboratory development effort the same 16-bit microprocessor used for the channel controller is being used for the data buffer unit in order to compress the system development cycle. The use of the 4-bit and the 16-bit microprocessor is sufficiently versatile to provide the technical information necessary to establish meaningful system specifications and to illustrate the application of microprocessors as system design elements.

#### SECTION III

#### SIGNALING AND SUPERVISION SUBSYSTEM

3.1 GENERAL

The Signaling and Supervision Subsystem provides the control for the MIDS network. The following basic control functions are performed:

- o Handle requests for connectivity

- o Authenticate request and requestor

- o Ascertain availability of equipments

- o Establish connectivity

- o Monitor connectivity

o Report status

The Signaling and Supervision subsystem operates over a channel of the cable that is separate from the channels providing the subscribers information distribution services. This feature is equivalent to out-of-band, common-channel signaling in the commercial telephone network. The S&S channel permits the MIDS subscriber to modify connections without disturbing any information distribution transaction already in progress. Similarly changes in equipment status are monitored and reported automatically over the S&S channel regardless of the state of the subscriber's connections.

The S&S subsystem contains several major functional elements including the Network Control Processor (NCP) and its operational software, the Channel Controller, and Keypad Control Units that provide the interface to the subscribers' terminal equipments. The Channel Controller is collocated with the Network Control Processor at the "headend" of the cable. Communication between the Channel Controller and the Keypad Control Units is based on a form of polled, asynchronous time-division-multiplex transmission.

Several improvements have been made in the details of the S&S subsystem design as described in Reference 1. The User/System Control Information Flow description has been expanded to include the addition of two new status lamps, i.e., the Dial lamp and the Call Active lamp. The S&S Channel Timing description has been revised due to the addition of a flag-for-service field in the S&S message structure. The use of the flag-for-service technique reduces the bandwidth required for the S&S channel. The Network Control Processor description contains two minor changes to the software. The original timing and sizing analyses included in Reference 1 have not been affected. The S&S Channel Controller is being redesigned around a 16-bit microprocessor. Only a summary description is provided since the design is still in progress. The S&S Keypad Control Unit also is being redesigned to employ a 4-bit microprocessor and this is essentially complete; a detailed description is presented. The Keypad Control Unit Modem is also briefly described.

This section describes the following aspects of the MIDS network control subsystem:

- o User/System Control Information Flow

- o Signaling and Supervision Channel Timing

- o Network Control Processor

- o S&S Channel Controller

- o S&S Keypad Control Unit

- o Keypad Control Unit Modem

3.2 USER/SYSTEM CONTROL INFORMATION FLOW

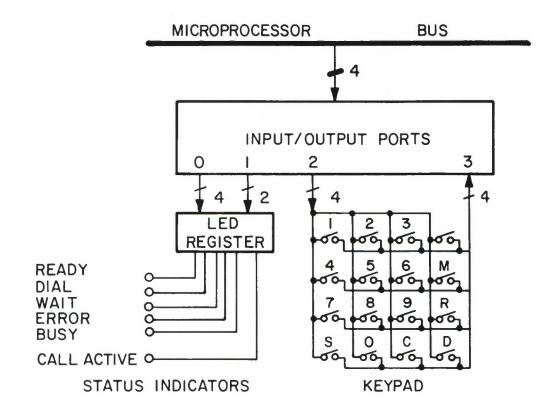

The keypad with its associated status lamps is the primary interface between the user and the signaling and supervision subsystem. The layout and markings of the keypad are illustrated in Figure 8. A conventional 10-button keypad with six additional function keys is utilized. The six status lamps indicate the progress of the dialing sequence. The lamps are color coded for ease of reference by the user. In addition to the ten numeric keys the following function keys are provided:

- S: Service Package

- C: Clear Keystrokes

- D: Disconnect

- R: Redial Call

- M: Modify Call

The sixth function key is unassigned and is available for future use.

# IA- 46,320

| 1 | 2 | 3 |   |

|---|---|---|---|

| 4 | 5 | 6 | М |

| 7 | 8 | 9 | R |

| S | 0 | С | D |

| READY | 0 | (GREEN)  |

|-------|---|----------|

| DIAL  | 0 | (YELLOW) |

| WAIT  | 0 | (YELLOW) |

| ERROR | 0 | (RED)    |

| BUSY  | 0 | (RED)    |

| CALL  | 0 | (GREEN)  |

LEGEND

S: SERVICE PACKAGE

C: CLEAR KEYSTROKES

M: MODIFY CALL

R: REDIAL

D: DISCONNECT

Figure 8 KEYPAD & INDICATOR LAYOUT

Six indicators are used to present status and guide user response. Four are similar to the existing system, that is, READY, WAIT, ERROR, and BUSY. Two new indicators for Dial and Call Active have been added. The use of the indicators is summarized as follows:

READY: S&S system ready for user input. DIAL: User to continue to dial. WAIT: Call being processed. ERROR: Dialing error. BUSY: Called party busy.

CALL ACTIVE: Data connection complete and acknowledged.

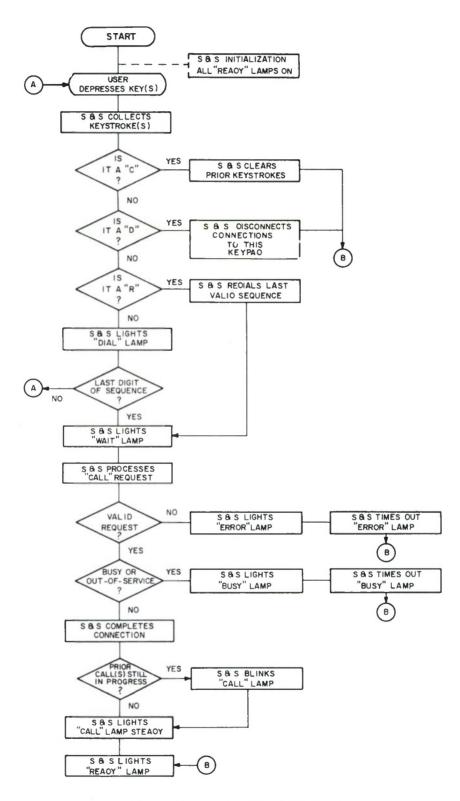

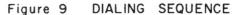

The sequence of actions between the user and the keypad is illustrated in Figure 9. When the S&S subsystem is initialized by the Network Control Processor, the READY lamps at all of the keypads are turned on. When a user depresses a key, the resulting keystroke is collected by the S&S subsystem poll. The Keypad Control Unit may store many keystrokes in its own buffer before transmitting to the Network Control Processor, hence, the designation keystrokes in the flow diagram. The S&S subsystem checks first to see if the user has dialed either a CLEAR, a DISCONNECT, or a REDIAL. If a user has dialed a CLEAR, the S&S subsystem clears all prior keystrokes from memory and turns the READY lamp on. If a subscriber presses DISCONNECT, the S&S subsystem disconnects all prior connections and lights the READY lamp. When a subscriber presses REDIAL, the S&S subsystem will attempt to make the connection previously requested by the user. As each keystroke is received the S&S subsystem checks to see if it is the last keystroke of a legitimate dialing sequence. When the last keystroke is so received, the S&S subsystem lights the WAIT lamp which is an indication to the user that he is working into an active system. It does not necessarily mean that the subscriber has to wait to do anything else. The S&S Network Control Processor then processes the call request. If a user has made an invalid request or a detectable error in dialing, the ERROR lamp is lit. The ERROR lamp however is timed out by the system so that the READY lamp will illuminate after a predetermined time. If the called party is busy or out of service, the S&S subsystem will light the BUSY lamp on the calling party's keypad. It will then proceed to time out this busy lamp, and after a predetermined time, it will again light the READY lamp. If, however, the necessary equipments are available the S&S subsystem will complete the connection at both

33

18-46,321

the calling and called party's keypads. If this connection is the initial call from this keypad, the CALL ACTIVE lamp would be lit by the S&S subsystem. Before lighting the CALL ACTIVE lamp however the S&S subsystem checks to see whether a previous call from this Keypad is still in progress. If a previous connection has already been established for a different service package, then the CALL lamp would already be lit. If so, the S&S subsystem will cause the CALL lamp to blink before returning it to a steady state. The S&S subsystem also lights the READY lamp to indicate to the user that it is ready for another dialing sequence.

Another diagram for describing states and transitions is the state diagram. The state diagram for the six indicator lamps associated with the keypad is illustrated in Figure 10. Starting with the READY lamp illuminated (1), the user may depress a digit key, service package key "S", or the call modification key "M". This action will cause the DIAL lamp to illuminate (2). It will stay on during the dialing sequence unless the CLEAR or DISCONNECT button is depressed which returns the keypad unit to the READY state. When the keystroke sequence is complete, the WAIT lamp comes on (4). However, during the dialing sequence, if an invalid character is dialed or if the inter-digit arrival time is determined by the processor to be too long, the user is timed out and an ERROR lamp comes on (3). After a short interval the ERROR lamp is turned off and the READY lamp is turned on by the Network Control Processor. Assuming the dialing sequence has advanced to the WAIT lamp being illuminated, the call is processed and if it cannot be completed due to called party or common equipment in a busy condition or out of service, the BUSY lamp comes on (5). The BUSY lamp is eventually timed out and the READY lamp illuminates (1). The user may redial the previous sequence by pressing the REDIAL Key ("R") while the BUSY lamp is still on or even after it goes off. The keypad unit will return to the WAIT state and the processor will automatically attempt to complete the connection again. Assuming the processor has completed the call, then the CALL ACTIVE lamp illuminates (6). For simplicity in the state diagram the blinking of the CALL ACTIVE lamp for additional dial sequences is not indicated since it has already been described in the flow chart sequence. The CALL ACTIVE state is terminated when the user depresses the DISCONNECT button. The S&S system then extinguishes the CALL ACTIVE lamp and turns on the READY lamp if it is not already on.

# 3.3 SIGNALING AND CHANNEL TIMING.

As described in Section 2.2, the Signaling and Supervision subsystem uses message time frames for transmitting information on

- S: SERVICE PACKAGE

- M: MODIFY CALL

- #: DIGITS Ø THROUGH 9

- R: REDIAL

IA - 46,322

# Figure 10 KEYPAD LAMP INDICATOR STATE DIAGRAM

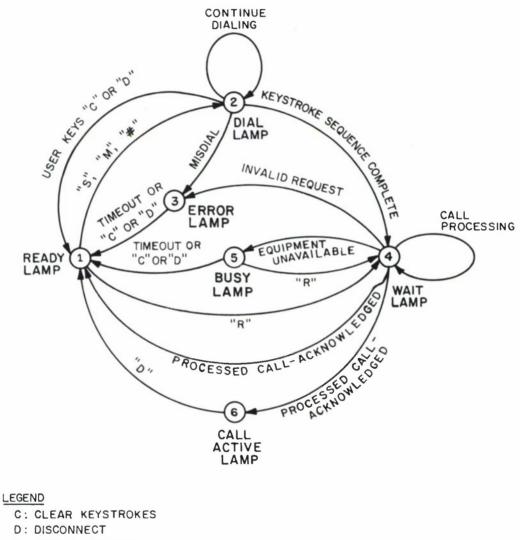

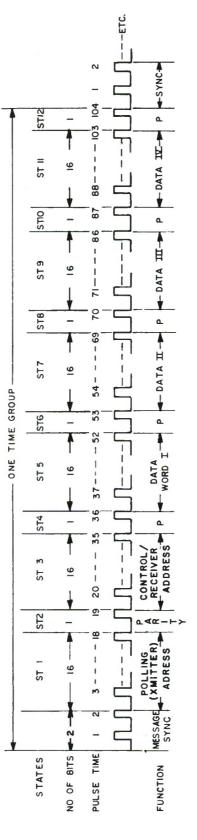

the downstream cable and receiving information on the upstream cable. The details of this message structure are illustrated by the telescoping levels in Figure 11. The top level of the diagram shows three message time frames interposed by two frame gaps. Each time frame is 0.839680 seconds in duration and contains 64 time groups. The intermessage frame gap is 960 microseconds. The transmission rate is 25 kbps.

The middle level of the diagram shows a single time group subdivided into its three constituent fields. The first field is designated the "flag-for-service" field and contains 256 symmetrical square-wave pulses. The second field is the polling field containing 16 bit positions. The first two bits of this field are control bits while the last fourteen bits are the address bits for the keypad being polled. The control bits are decoded as follows:

- 00 Interrogation Poll: Send your keystroke/status information.

- 01 Command Poll: Set receiver and transmitter address.

- 10 Command Poll: Set status lights.

- 11 Unassigned: (Available for future

use.)

The third field is the S&S information field which contains 48 bit times consisting of 32 information bits , 4 parity bits, 4 start bits and 8 stop bits.

The bottom level of the diagram shows one of the two 16-bit words in the S&S information field received by the S&S Channel Controller from the PDP-11 Network Control Processor. The actual transmission of the S&S information field, however, is organized on a character basis. Each character contains eight information bits of 40 microseconds duration which corresponds to one byte of a twobyte minicomputer word. Character transmission is performed on a conventional start/stop asynchronous basis. Each character also contains a parity bit for error checking purposes. The information field contains such items as the data buffer receiver and transmitter addresses or status light controls, depending on which command poll was used. In the case of an interrogation poll the information field is essentially void on the downstream cable; however, it does contain the keystroke and station status (in or out of service, etc.) on the upstream cable.

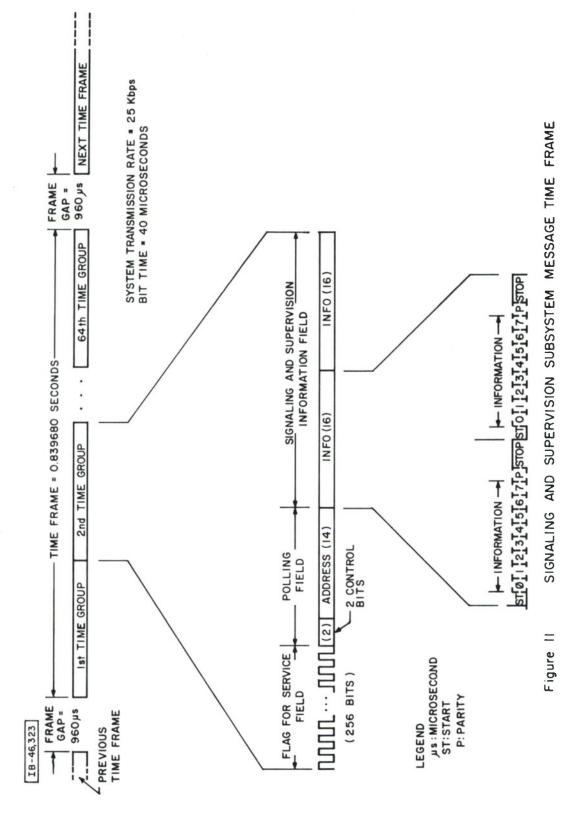

The sequence of operations between the S&S Channel Controller and a keypad control unit is illustrated in Figure 12. The diagram is divided into three subsequences to emphasize that the flag-forservice field and the polling address fields are not part of the same time group. These illustrations visualize the waveforms as they would appear to move past an observer at a specific keypad. In addition the diagram shows what information is sent on the upstream cable by the keypad control unit in response to signal information received on the downstream cable.

During the flag-for-service subsequence all keypad control units receive the 256 square wave pulses as indicated in Figure 12a. If Keypad Number 27 is requesting service, the flag-for-service logic counts up to pulse number 27 and causes a flag pulse to be sent on the upstream cable, completing the flag-for-service subsequence.

When the S&S Channel Controller detects the flag-for-service pulse from Keypad #27, it initiates an interrogation poll subsequence (Figure 12b) by inserting the polling address of keypad number 27 in the next available time group. It also sets the two control bits in the polling field to "00". The tail-end of a flagfor-service field is shown in the diagram followed by the two control bits and polling address number 27. The data receiver circuitry in the Keypad Control Unit receives the address and control bits and interrupts the microprocessor to process the information. The address recognition function is performed in the microprocessor software. To permit time for executing this compare function, transmission on the upstream cable is delayed until detection of the subsequent polling field. The keystroke and/or status information is sent via the upstream cable to the S&S Channel Controller which transfers this information to the Network Control Processor, that is, the PDP-11/10 minicomputer.

After the PDP-11/10 processes the information, it sends a command-poll message to the Keypad Control Unit. The command poll subsequence is illustrated in Figure 12c. When the Keypad Control Unit sees the tail end of the flag-for-service pulse stream it decodes the polling field and recognizes its polling address, Number 27. The control bits "Ol" are decoded as a command poll containing information for its own status indicators, such as turning on the "dialing-in-progress" light or the WAIT light.

Once all the keystrokes have been collected and assuming that data service was requested, the Network Control Processor will then send a command poll to the Keypad Control Unit similar in format to that indicated in Figure 12c. However the code will be "10" and the information portion of the message will contain the transmit and

receive indirect addresses for use by the MIDS data distribution subsystem.

# 3.4 NETWORK CONTROL PROCESSOR (NCP)

The network control processor function is performed by a PDP-11/10 minicomputer. The equipment configuration and software programs used by the PDP-11/10 for the network control function are based on a modification of the Network Control Program (NETCOP) extensively described in Reference 1. Since only minor modifications have been made to NETCOP, a complete description is not reprinted in this document.

The software modifications are as follows: The first change is implementation of the terminal equipment status reporting feature. The original NETCOP had provision for storing the status of each terminal; however, the program code to perform the status monitoring was not developed. Specifically, as each keypad is interrogated as part of the system initialization procedure the status of each terminal is stored in the existing User Data Table. In addition when a terminal goes off line, runs out-of-paper, etc., the terminal's keypad control unit sends the change-of-status information to the Network Control Processor for updating the User Data Table. Another change is required by the introduction of indirect addressing in the data distribution subsystem design. Since the S&S subsystem must store 512 indirect addresses, a 512 word table is required. The 512 indirect addresses in the table actually represent 1024 terminals. Only 512 words need be stored because connections are made on a duplex basis and the addresses of the duplex pair are always separated by the numeric 16. The addition of the DIAL and CALL ACTIVE lamps at the keypads also require minor changes in the network control program. Similarly the S&S input program, SASI, also requires minor revisions to handle an input message with up to three keystrokes instead of just one as in the previous system. The addition of status reporting plus other system features were anticipated in the original NETCOP design. As a result ample storage was allocated to these features in the original sizing and timing analysis. Hence the changes described above do not affect the sizing and timing analysis described in Reference 1.

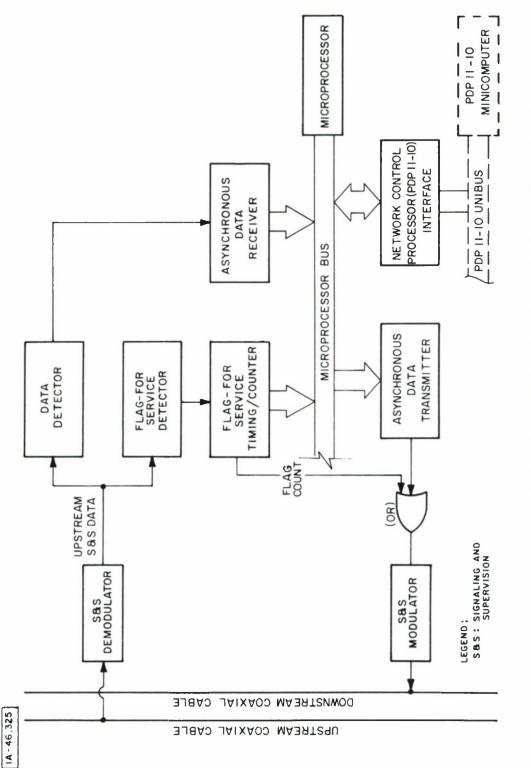

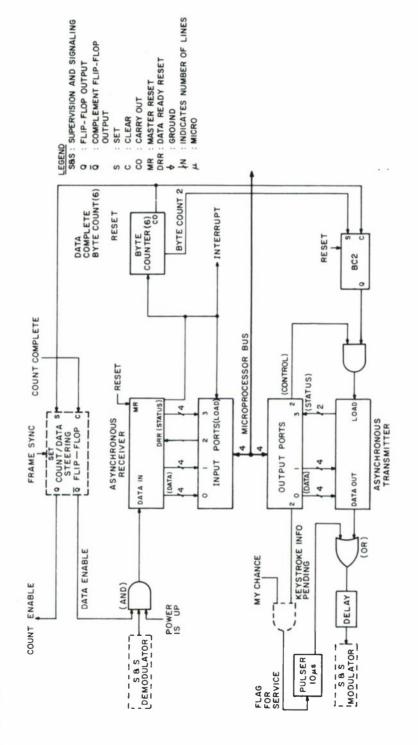

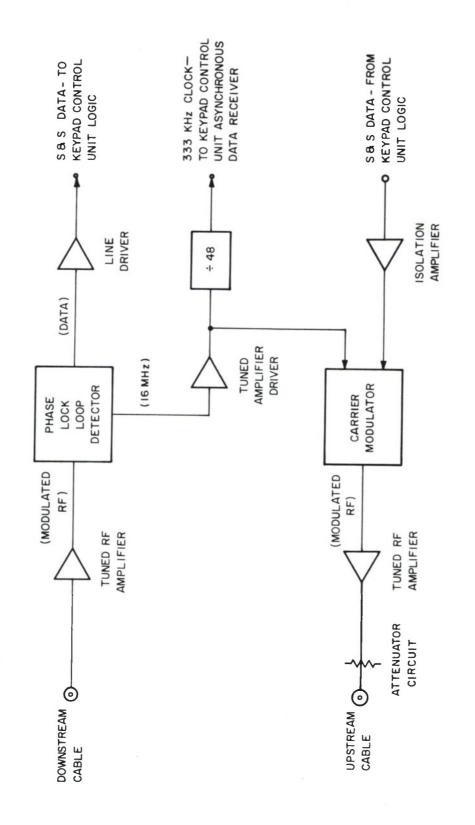

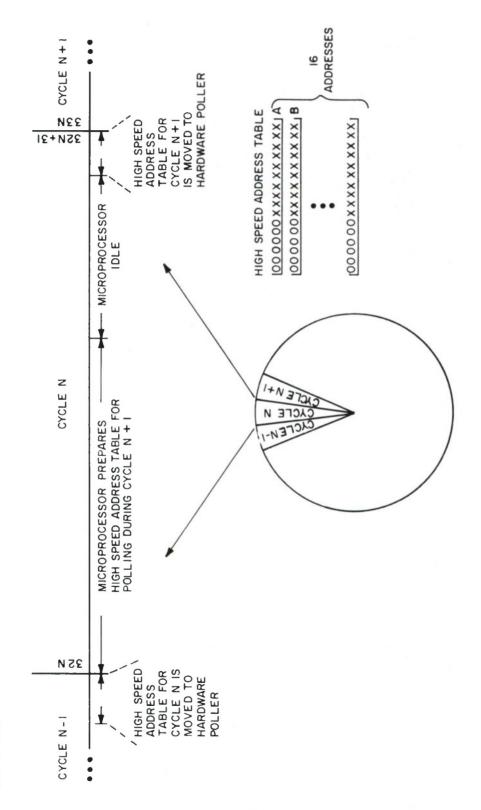

# 3.5 SIGNALING AND SUPERVISION CHANNEL CONTROLLER

The Signaling and Supervision Channel Controller provides the interface between the Network Control Processor (PDP-11) and the upstream and downstream coaxial cables as shown in Figure 1. The S&S Channel Controller shown in Figure 13 is structured around a 16-

bit microprocessor which was chosen for ease of interfacing with the 16-bit PDP-11 minicomputer. The Channel Controller provides the following functions:

- o Performs the flag-for-service sequence

- o Performs the initial interrogation poll sequence

- o Manages the data transfer between the network control processor and the digital data channel for all subsequent polling sequences

The flag-for-service subsequence is controlled by the Flag-For-Service Timing/Counter block as indicated in Figure 13. The Flag-For-Service Timing/Counter circuit sends a pulse train of 256 pulses (flag counts) via the OR gate and Modulator to the downstream coaxial cable. The Flag-For-Service Detector monitors the upstream cable to detect "flag" pulses sent by Keypad Control Units. The pulse arrival times are matched against a counter to determine which Keypad Control Unit generated the upstream "flag" pulse. The pulse count is then converted to a keypad address and transferred to the microprocessor via the microprocessor bus. The microprocessor then initiates polling of that specific keypad by sending the address downstream in the next available time group. This is accomplished by transferring the address in bit-parallel form to the asynchronous data transmitter. With each 14-bit address, two control bits are also sent. For the initial polling sequence the control bits are both zeros as described in Section 3.2. The asynchronous data transmitter accepts the 16-bits in parallel from the microprocessor bus and for convenience in transmission divides the 16-bits into two 8-bit information characters and transmits the characters, bitserial, in the start-stop asynchronous mode. Up to this point the operation of the Channel Controller is independent of the Network Control Processor, thus permitting the Network Control Processor to execute its own internal programs without excessive interrupts.

Upon receipt of the initial addressed poll the Keypad Control Unit sends back keystroke or status information to the S&S Channel Controller. The information is detected by the S&S Data Detector and transferred to the Asynchronous Data Receiver. The Asynchronous Data Receiver then interrupts the microprocessor and transfers the information to the microprocessor which in turn interrupts the Network Control Processor (PDP-11) to transfer the keystroke information or status information. Subsequent keystroke or status information is accepted by the Channel Controller and continues to be passed to the Network Control Processor PDP-11 until enough information has been received to act on a subscriber's request. At that point the PDP-11 processes the request and sends the

SIGNALING & SUPERVISION SUBSYSTEM CHANNEL CONTROLLER Figure 13 appropriate control and status information downstream via the S&S Channel Controller.

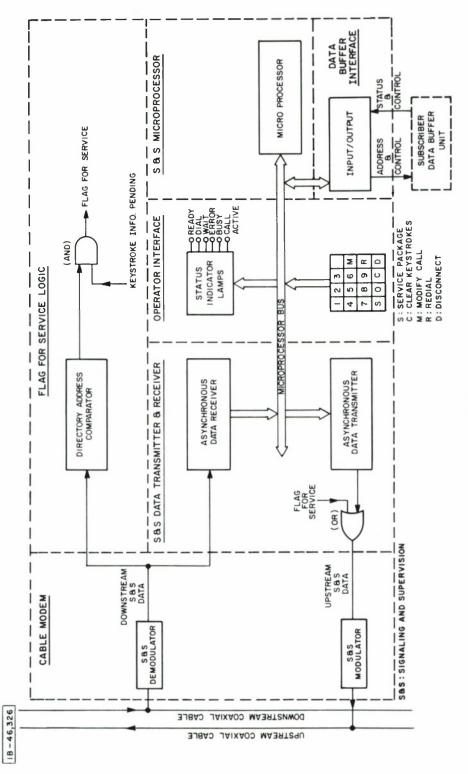

3.6 SIGNALING AND SUPERVISION KEYPAD CONTROL UNIT