## REPORT DOCUMENTATION PAGE

2. REPORT TYPE

1. REPORT DATE (DD-MM-YYYY)

#### Form Approved OMB No. 0704-0188

3. DATES COVERED (From - To)

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing this collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden to Department of Defense, Washington Headquarters Services, Directorate for Information Operations and Reports (0704-0189), 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to any penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number. PLEASE DO NOT RETURN YOUR FORM TO THE ABOVE ADDRESS.

|                                                                                         |                                                                                                                                                                        | Final Technical R                                                                                                                                         | eport                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5/01/2015-08/15/2017                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4. TITLE AND SU                                                                         |                                                                                                                                                                        |                                                                                                                                                           |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CONTRACT NUMBER                                                                                                                                                                                                                                 |

|                                                                                         |                                                                                                                                                                        | oller Architecture                                                                                                                                        | for SiC Based Pov                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ODANI WWW.                                                                                                                                                                                                                                      |

| Electronic Bu                                                                           | ilding Blocks                                                                                                                                                          |                                                                                                                                                           |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GRANT NUMBER<br>0014-15-I-2346                                                                                                                                                                                                                  |

|                                                                                         |                                                                                                                                                                        |                                                                                                                                                           |                                                                                                                                                  | 5c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PROGRAM ELEMENT NUMBER                                                                                                                                                                                                                          |

| 6. AUTHOR(S)                                                                            |                                                                                                                                                                        |                                                                                                                                                           |                                                                                                                                                  | 5d.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PROJECT NUMBER                                                                                                                                                                                                                                  |

| Dr. Herbert Gin                                                                         | n                                                                                                                                                                      |                                                                                                                                                           |                                                                                                                                                  | Fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TASK NUMBER                                                                                                                                                                                                                                     |

|                                                                                         |                                                                                                                                                                        |                                                                                                                                                           |                                                                                                                                                  | Je.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TASK NUMBER                                                                                                                                                                                                                                     |

|                                                                                         |                                                                                                                                                                        |                                                                                                                                                           |                                                                                                                                                  | 5f.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | WORK UNIT NUMBER                                                                                                                                                                                                                                |

|                                                                                         | ORGANIZATION NAME                                                                                                                                                      | S) AND ADDRESS(ES                                                                                                                                         |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PERFORMING ORGANIZATION REPORT                                                                                                                                                                                                                  |

| niversity of South Carolina                                                             |                                                                                                                                                                        | ,                                                                                                                                                         | NUMBER                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                 |

|                                                                                         |                                                                                                                                                                        |                                                                                                                                                           |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                 |

| 9. SPONSORING<br>Office of Naval                                                        | / MONITORING AGENCY<br>I Research                                                                                                                                      | NAME(S) AND ADDR                                                                                                                                          | ESS(ES)                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SPONSOR/MONITOR'S ACRONYM(S)<br>NR                                                                                                                                                                                                              |

|                                                                                         |                                                                                                                                                                        |                                                                                                                                                           |                                                                                                                                                  | 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SPONSOR/MONITOR'S REPORT NUMBER(S)                                                                                                                                                                                                              |

| 13. SUPPLEMEN                                                                           | TARY NOTES                                                                                                                                                             |                                                                                                                                                           |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                 |

| 14. ABSTRACT                                                                            |                                                                                                                                                                        |                                                                                                                                                           | Alexander of the same                                                                                                                            | A-1-A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                 |

| Power Elect beginning to order of mag conventiona converter sy trends preservalizations | ronic Building Blo<br>yield PEBBs with<br>gnitude reduction<br>I IGBT based PE<br>estems with hundrent the need to eve<br>of the Universal Converters. The converters. | ock (PEBB) converse for greater swing far greater swing of the control tire. BBs. In addition leds of PEBBs, saluate architectic controller Architectics. | verters. Recent de<br>tching frequencie<br>ne scales as com<br>there have also be<br>such as the Modu<br>ure tradeoffs and<br>ecture for control | evelopments in the street of power electrical street of the street of th | ure suitable for SiC based in SiC power devices are ed devices resulting in an verter systems utilizing ements in highly modularized Converters. Both of those on requirements for hardware etronic converters and himal round-trip latency and |

| 15. SUBJECT TEI                                                                         |                                                                                                                                                                        |                                                                                                                                                           |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                 |

|                                                                                         |                                                                                                                                                                        |                                                                                                                                                           |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                 |

| 16. SECURITY CLASSIFICATION OF:                                                         |                                                                                                                                                                        | 17. LIMITATION                                                                                                                                            | 18. NUMBER                                                                                                                                       | 19a. NAME OF RESPONSIBLE PERSON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                 |

| Inclassified                                                                            | L ABOTELOT                                                                                                                                                             | - THE 2105                                                                                                                                                | OF ABSTRACT                                                                                                                                      | OF PAGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Dr. Herbert Ginn                                                                                                                                                                                                                                |

| a. REPORT                                                                               | b. ABSTRACT                                                                                                                                                            | c. THIS PAGE                                                                                                                                              |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19b. TELEPHONE NUMBER (include area code)<br>803-777-5598                                                                                                                                                                                       |

|                                                                                         |                                                                                                                                                                        | -                                                                                                                                                         |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Standard Form 298 (Rev. 8-98)                                                                                                                                                                                                                   |

## Final Report

## Development of Universal Controller Architecture for SiC Based Power Electronic Building Blocks

30 October 2017

#### SUBMITTED BY

DR. HERBERT L. GINN, PI

DEPT. OF ELECTRICAL ENGINEERING

UNIVERSITY OF SOUTH CAROLINA

DR. Jason Bakos, Co-PI

DEPT. OF COMPUTER SCIENCE AND ENGINEERING

UNIVERSITY OF SOUTH CAROLINA

| Award Number           | N000141512346                                                                                      |

|------------------------|----------------------------------------------------------------------------------------------------|

| Title of Research      | Development of Universal Controller Architecture for SiC<br>Based Power Electronic Building Blocks |

| Principal Investigator | Herbert L. Ginn                                                                                    |

| Organization           | University of South Carolina                                                                       |

Technical POC

Dr. Herbert L. Ginn

Dept. of Electrical Engineering

University of South Carolina

Columbia, SC 29208

ginnhL@cec.sc.edu

phone: 803-777-8045

Administrative POC

Danielle McElwain

Sponsored Awards Management

901 Sumter Street

Columbia, SC 29208

dmcelwai@mailbox.sc.edu

phone: 803-777-1119

# **Table of Contents**

| 1. Scientific and Technical Objectives                                            | 2    |

|-----------------------------------------------------------------------------------|------|

| 2. Approach                                                                       | 2    |

| 3. Accomplishments                                                                | 4    |

| 4. Expanded Accomplishments                                                       |      |

| 4.1 Technology transfer of USC modular digital control platform to CPES           | 6    |

| 4.2. Evaluation of digital control platform partitioning and module development b | elow |

| the application level                                                             | 7    |

| 4.3 System to application layer interface definition development and upper laye   | r    |

| module development for the modular digital controller                             | 13   |

| 4.4 Evaluation of system to application level partitioning and communication      | 19   |

| 5. Productivity                                                                   | 27   |

| 6. Award Participants                                                             | 27   |

| 7. Works Cited                                                                    | 28   |

#### 1. Scientific and Technical Objectives

The objective of this project was to develop a Universal Controller Architecture suitable for SiC based Power Electronic Building Block (PEBB) converters. Recent developments in SiC power devices are beginning to yield PEBBs with far greater switching frequencies than Si based devices resulting in an order of magnitude reduction of the control time scales as compared to converter systems utilizing conventional IGBT based PEBBs. In addition there have also been advancements in highly modularized converter systems with hundreds of PEBBs, such as the Modular Multilevel Converter (MMC). Both of those trends present the need to evaluate architecture tradeoffs and communication requirements for hardware realizations of the Universal Controller Architecture for control of power electronic converters and systems of converters. The control network should be designed to have minimal round-trip latency and maximal scalability.

In order to accomplish the primary project objective a key secondary objective was to conduct a study to determine the most appropriate communication architecture and routing for networked PEBB control systems. In doing so we have considered all of the control layers from the lowest hardware layers up to ship-wide system control. The appropriate partitioning and interface requirements between the various control layers is considered for power electronic systems with particular focus on the system and application control layers for systems of power electronic converters so that the minimum set of application level control interfaces is compatible across all power electronic controllers. This provides flexibility of system design and operation for distributed converter systems so that a more flexible energy management capability is achieved for naval electric distribution systems.

### 2. Approach

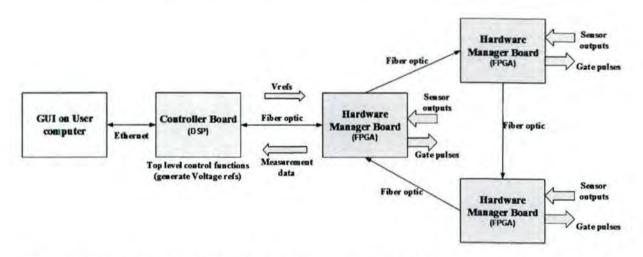

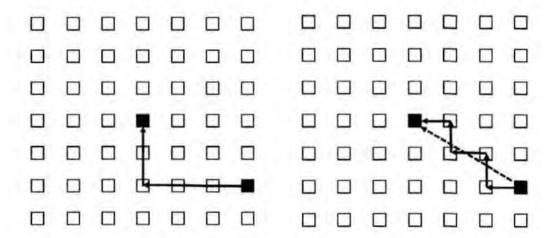

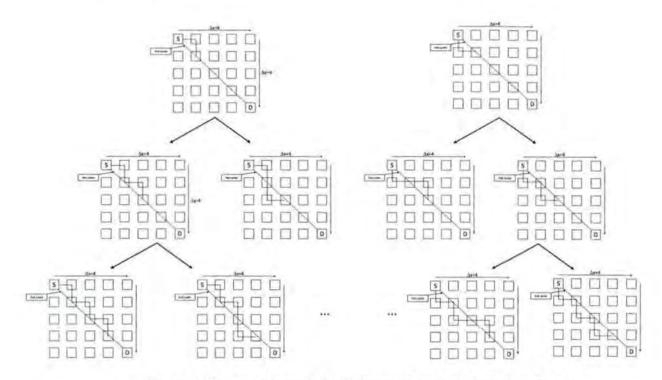

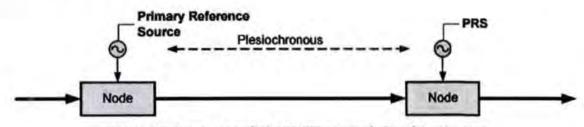

In a ship-wide PEBB-based power distribution system, control and measurement modules are spatially distributed. While modules that form the control system for a single converter may be somewhat co-located, modules at the application level of control and above will be distributed throughout the overall system. Therefore, it is generally not feasible to connect them all directly into a single central controller. Instead, it is more practical to distribute control among the modules within converters and at layers above individual converter control, such as zonal or bus level controls. Using a multi-hop network, each control module should contain a small integrated router that can both serve as a network interface and serve as an intermediate forwarding point for other messages sent among other control modules. In these types of networks, the worst-case message latency is determined by the longest possible path between two control modules. This worst-case latency serves as a constraint for the overall control system design. As such, both the physical topology of the communication network and the routing algorithm are important considerations for the system design.

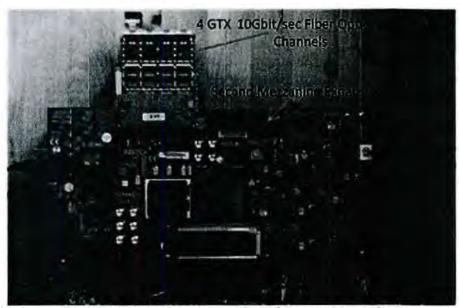

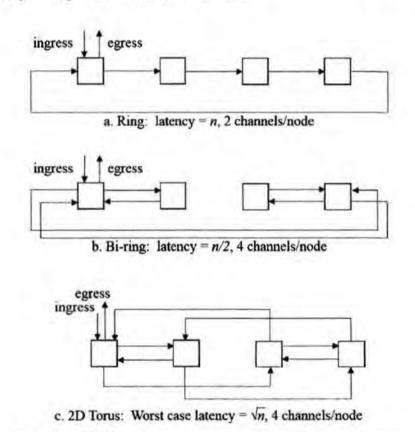

FPGA based designs are used with increasing frequency for power electronic converter designs due to modular design approaches and performance requirements imposed by increasing switching frequencies. Recent generations of FPGAs include multiple high performance serial transceivers that support speeds in excess of 10Gbit/sec. This opens up possibilities beyond the simple ring communication network topology common up to now in power electronic control systems. Other network topologies were explored in this project given that inclusion of multiple Gigabit serial links per control node is viable.

In performing control module development at any control level there are several design challenges that must be addressed. The key design focus areas and approach toward each at the beginning of this project were specified as follows:

#### 1. Bounding Control Loop Delay

The stability and performance of the PEBB modules is affected by the delay between when measurements are taken and when updated references are received from the controller. Since each level of the PEBB hierarchy is connected in a local topology, transitioning packets between levels also contributes to the delay. Each FPGA-based endpoint will be designed to contain multiple integrated gigabit channel interfaces. In a ring topology only two channels are used. By using additional channels alternative topologies can be explored. The delay can be reduced by exploring alternative network topologies at each control level and between control levels considering a range of system scales.

#### 2. Library of Reusable IP Blocks

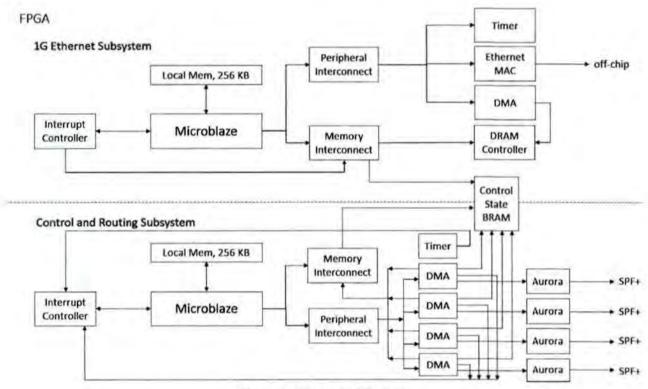

Recurring control design costs is reduced by development of a module library of commonly-needed measurement and control behaviors that can be easily added to the FPGA design for each PEBB module. Use of standard bus architectures such as the Xilinx-standard AXI4 bus for interoperability and integration, allows them to be easily instantiated into a design using the latest FPGA platform tools (ex: Xilinx Vivado). These modules include channel interfaces and associated error control and routing logic, measurement and control interfaces, and online diagnosis and system health monitoring modules. Diagnosis modules will incorporate softcore microcontrollers and associated software that can be individually contacted on each module to assess performance counters and access low level status information during runtime.

#### 3. Fault Tolerance

Each channel connecting modules at every PEBB level utilizes a MAC layer protocol (Xilinx Aurora), which includes 8b/10b encoding that facilitates channel synchronization. We will add support for forward error correction (FEC) at the link layer to guarantee recovery from communication errors.

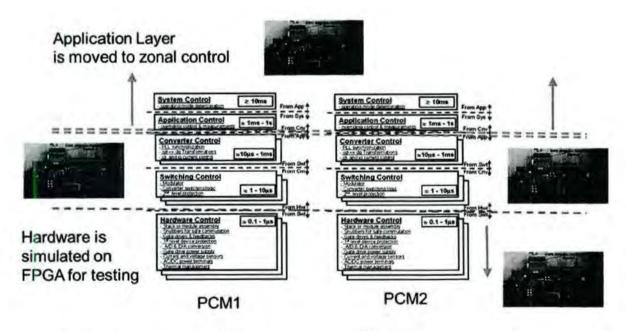

#### 4. Application Layer Partitioning

For system level design, a standardized interface or set of interfaces between the application level and system level control functions is needed. An objective of the research is to determine the appropriate partitioning and interface requirements between the system and application control layers so that the minimum set of system level to application level control interfaces is compatible across all power electronic controllers. The application level control dictates the operation of a power electronics system in order to meet the mission determined by the system level control. In order to meet the research objective, the components and function of both the system layer of control and the application layer of control must be determined for the various classes of power electronic systems and their applications. The commonalities across applications will be explored in order to define the minimum set of interface requirements.

#### 5. Top System Control Layer Considerations

A Shipboard Wide Area Network (SWAN) has been developed for the LPD-17 transport class as well as DDG-1000. There is also a high probability that future ships will have a similar SWAN. The SWAN design is expected to be an open architecture employing current network technology and commercial equipment. Connection of the PEBB-1000 controllers over a SWAN provides an

infrastructure that supports further development and validation of the interface between the power system converters' network and top system control. A minimum of two control systems will be connected to a three-node SONET/ATM network that will represent the SWAN. Performance restrictions due to network communication bandwidth and latency times will be investigated. Tradeoffs between communication requirements and variations of the system level to application level control interface architecture will be explored. This activity will aid in optimizing the partitioning and interface requirements of the control boundaries at the topmost system interface.

Significant progress was made in each of the focus areas as outlined in the accomplishments section and described in detail in the expanded accomplishments section below.

#### 3. Accomplishments

The project focus areas are interrelated challenges that must be overcome to achieve the overall objective. In order to organize execution along a project timeline the work was conducted under four tasks. Major accomplishments achieved during the course of this research project are presented below by task.

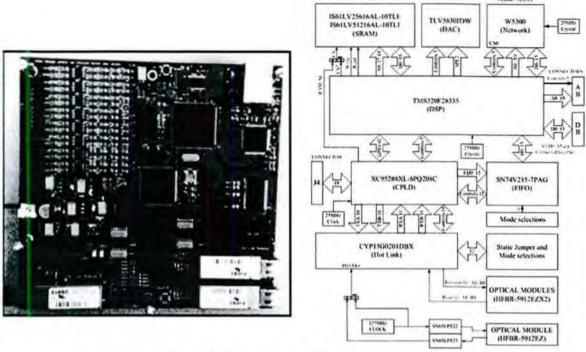

Task 1. Technology transfer of USC modular digital control platform to CPES

The latest design of the Universal Controller Architecture at the time of the project start was used as an initial design point. It was also shared with researchers at CPES to assist with ongoing PEBB-1000 control efforts. Detailed design documents, notes and schematics were sent to CPES.

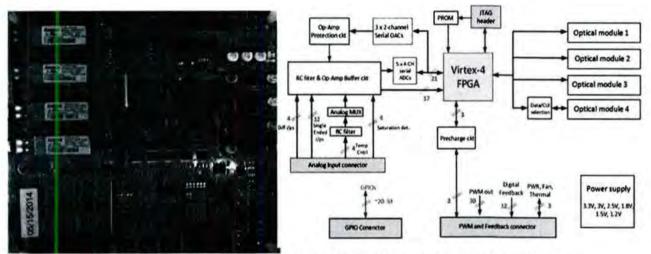

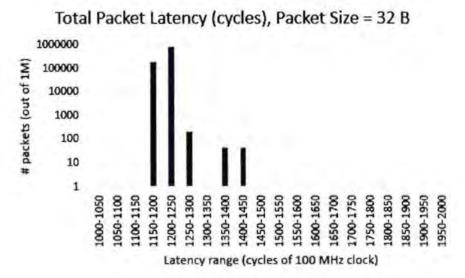

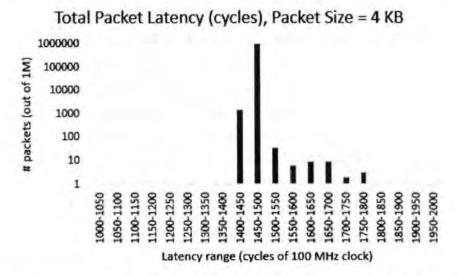

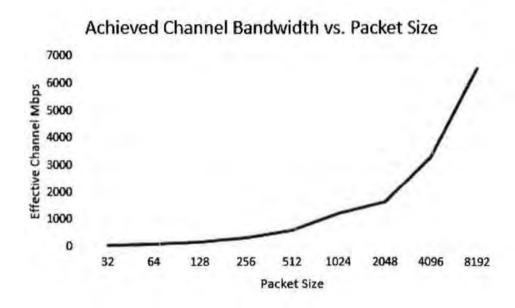

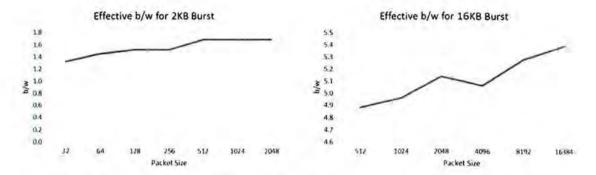

Task 2. Evaluation of digital control platform partitioning and module development below the application level